(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6539149号

(P6539149)

(45) 発行日 令和1年7月3日(2019.7.3)

(24) 登録日 令和1年6月14日(2019.6.14)

(51) Int.CI.

HO4N 5/378 (2011.01)

F 1

HO4N 5/378

請求項の数 12 (全 16 頁)

(21) 出願番号 特願2015-159788 (P2015-159788)

(22) 出願日 平成27年8月13日 (2015.8.13)

(65) 公開番号 特開2017-38315 (P2017-38315A)

(43) 公開日 平成29年2月16日 (2017.2.16)

審査請求日 平成30年6月20日 (2018.6.20)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100101498

弁理士 越智 隆夫

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100128668

弁理士 斎藤 正巳

(72) 発明者 桜木 孝正

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置及び撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換により入射光に応じた信号を生成する画素と、

前記画素からの信号に基づく電圧が入力される第1の入力端子と、基準電圧が入力される第2の入力端子とを有する差動増幅器と、

前記差動増幅器にバイアス電流を供給する電流供給部と、

前記差動増幅器の前記第1の入力端子の電圧としきい値電圧との比較を行い、比較結果に基づく制御信号を前記電流供給部に出力する比較部と、を有し、

前記電流供給部は、前記比較部から入力される前記制御信号に応じて、前記差動増幅器に供給する前記バイアス電流の大きさを異ならせ、

前記制御信号が、前記画素からの信号に基づく電圧が変動したことを示す場合に、前記電流供給部は、前記差動増幅器に供給する前記バイアス電流を大きくすることを特徴とする撮像装置。

## 【請求項 2】

前記電流供給部は、第1の電流源と、第2の電流源と、スイッチとを有し、

前記電流供給部は、前記制御信号に応じて前記スイッチを切り替えることにより、前記第1の電流源のみが前記バイアス電流を供給する第1の状態と、前記第1の電流源及び前記第2の電流源の双方が前記バイアス電流を供給する第2の状態とを切り替えることを特徴とする請求項1に記載の撮像装置。

## 【請求項 3】

10

20

前記しきい値電圧は、前記差動増幅器の第2の入力端子の電圧に相当することを特徴とする請求項1又は2に記載の撮像装置。

【請求項4】

前記比較部は、

比較器と、

前記比較器の入力オフセット電圧及び前記差動増幅器の入力オフセット電圧の差をキャンセルするオフセット電圧キャンセル部と

をさらに有することを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。

【請求項5】

前記オフセット電圧キャンセル部は、クランプ容量を有し、

10

前記オフセット電圧キャンセル部は、前記クランプ容量に前記比較器の入力オフセット電圧と前記差動増幅器の入力オフセット電圧との差に相当する電圧を保持させて入力オフセット電圧のキャンセルを行うことを特徴とする請求項4に記載の撮像装置。

【請求項6】

前記比較部は、前記しきい値電圧をシフトするしきい値電圧シフト部をさらに有することを特徴とする請求項4又は5に記載の撮像装置。

【請求項7】

前記しきい値電圧シフト部は、前記入力オフセット電圧のキャンセルが行われた後に、前記しきい値電圧のシフトを行うことを特徴とする請求項6に記載の撮像装置。

【請求項8】

前記比較部は、インバータと、クランプ容量とを有し、

20

前記クランプ容量は、前記差動増幅器の前記第2の入力端子の電圧と、前記インバータの論理しきい値と、前記差動増幅器の入力オフセット電圧とに基づく電圧を前記しきい値電圧として保持し、

前記差動増幅器の前記第1の入力端子の電圧が、前記クランプ容量を介して前記インバータに入力されることにより、前記比較が行われることを特徴とする請求項1又は2に記載の撮像装置。

【請求項9】

前記比較部は、前記インバータの論理しきい値をシフトするしきい値電圧シフト部をさらに有することを特徴とする請求項8に記載の撮像装置。

30

【請求項10】

前記しきい値電圧シフト部は、前記クランプ容量への電圧の保持が行われた後に、前記しきい値電圧のシフトを行うことを特徴とする請求項9に記載の撮像装置。

【請求項11】

複数の画素と、

前記複数の画素が接続された信号線と、

前記信号線に電気的に接続された第1の入力端子と、基準電圧が入力される第2の入力端子とを有する差動増幅器と、

前記差動増幅器に接続された第1の電流源と、

前記差動増幅器にスイッチを介して接続された第2の電流源と、

40

前記差動増幅器の前記第1の入力端子に電気的に接続された第1の入力端子、しきい値電圧が入力される第2の入力端子、及び、前記スイッチに接続された出力端子を有する比較部と、を有することを特徴とする撮像装置。

【請求項12】

請求項1乃至11のいずれか1項に記載の撮像装置と、

前記撮像装置から出力される信号を処理する信号処理部と

を有する撮像システム。

【発明の詳細な説明】

【技術分野】

【0001】

50

本発明は、撮像装置及び撮像システムに関する。

【背景技術】

【0002】

C M O Sイメージセンサ等の撮像装置において、撮像処理の高速化の要求がある。そのため、撮像装置に用いられる増幅回路にも、処理の高速化が要求される。増幅回路においてより高速に増幅処理を行うための一手法として、増幅回路の出力スルーレートを大きくすることが挙げられる。

【0003】

非特許文献1には、第1の差動入力段の出力が第2の差動入力段のバイアス電流を増加させることにより、その結果、第2の差動入力段の出力のスルーレートが増加する差動増幅回路が記載されている。

10

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】G. Nicollini, F. Moretti, and M. Conti, "High-frequency fully differential filter using operational amplifiers without common-mode feedback", IEEE Journal of Solid-State Circuits, vol. 24, no. 3, pp. 803-813, June 1989

【発明の概要】

【発明が解決しようとする課題】

【0005】

20

しかしながら、非特許文献1の差動増幅回路では、常時大きなバイアス電流が供給されるため、消費電力が大きい。このように、増幅回路はスルーレートを大きくすると消費電力が増大する傾向がある。そのため、撮像装置の高速化にあたり、低消費電力化との両立が課題となり得る。

【0006】

そこで、本発明は、高速化と低消費電力化を両立した撮像装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一観点による撮像装置は、光電変換により入射光に応じた信号を生成する画素と、前記画素からの信号に基づく電圧が入力される第1の入力端子と、基準電圧が入力される第2の入力端子とを有する差動増幅器と、前記差動増幅器にバイアス電流を供給する電流供給部と、前記差動増幅器の前記第1の入力端子の電圧としきい値電圧との比較を行い、比較結果に基づく制御信号を前記電流供給部に出力する比較部とを有し、前記電流供給部は、前記比較部から入力される前記制御信号に応じて、前記差動増幅器に供給する前記バイアス電流の大きさを異ならせ、前記制御信号が、前記画素からの信号に基づく電圧が変動したことを示す場合に、前記電流供給部は、前記差動増幅器に供給する前記バイアス電流を大きくすることを特徴とする。

30

本発明の別の観点による撮像装置は、複数の画素と、前記複数の画素が接続された信号線と、前記信号線に電気的に接続された第1の入力端子と、基準電圧が入力される第2の入力端子とを有する差動増幅器と、前記差動増幅器に接続された第1の電流源と、前記差動増幅器にスイッチを介して接続された第2の電流源と、前記差動増幅器の前記第1の入力端子に電気的に接続された第1の入力端子、しきい値電圧が入力される第2の入力端子、及び、前記スイッチに接続された出力端子を有する比較部と、を有することを特徴とする。

40

【発明の効果】

【0008】

本発明によれば、高速化と低消費電力化を両立した撮像装置が提供される。

【図面の簡単な説明】

【0009】

50

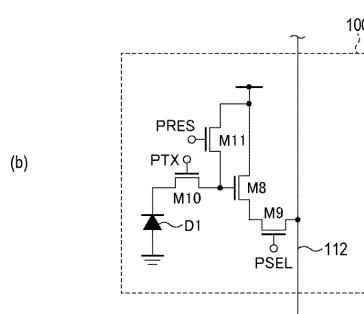

【図1】(a)は、第1実施形態に係る撮像装置の構成を示すブロック図であり、(b)は、第1実施形態に係る画素の構成を示す回路図である。

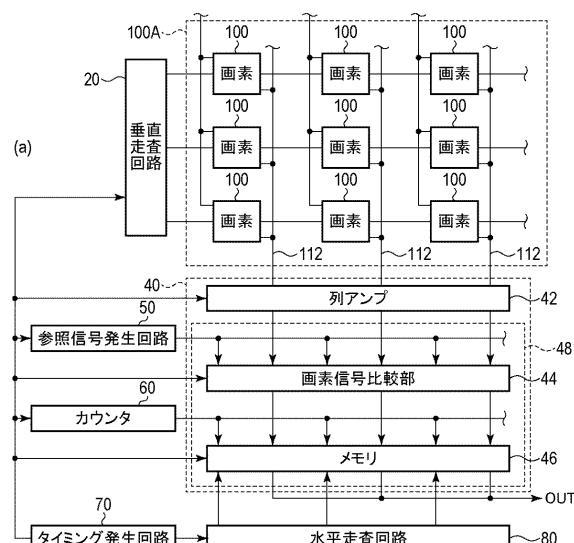

【図2】第1実施形態に係る列アンプの構成を示す回路図である。

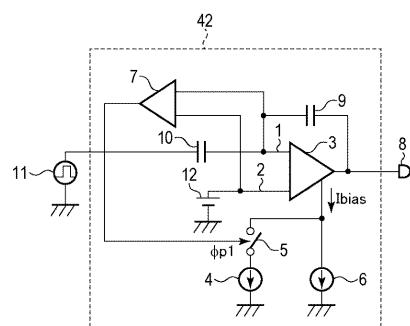

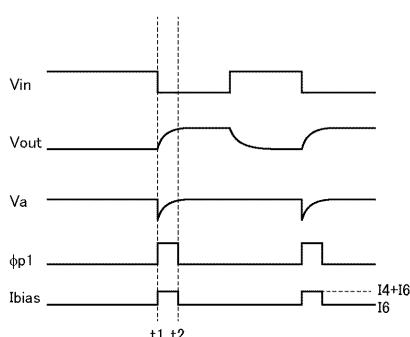

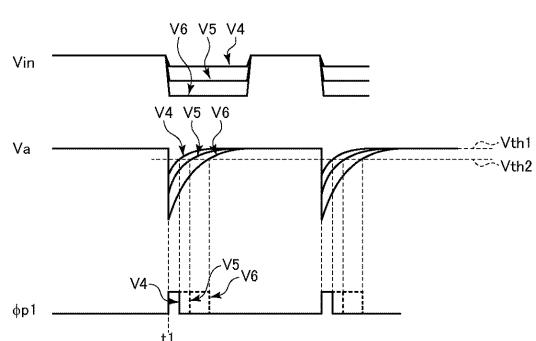

【図3】第1実施形態に係る列アンプの動作タイミングを示す図である。

【図4】第2実施形態に係る列アンプの構成を示す回路図である。

【図5】第2実施形態に係る列アンプのより具体的な構成を示す回路図である。

【図6】第2実施形態に係る列アンプの動作タイミングを示す図である。

【図7】第3実施形態に係る列アンプの構成を示す回路図である。

【図8】第3実施形態に係る列アンプの動作タイミングを示す図である。

【図9】第3実施形態に係る列アンプの別の構成を示す回路図である。

【図10】第3実施形態に係る出力電圧のシミュレーション結果である。

【図11】第3実施形態に係るバイアス電流のシミュレーション結果である。

【図12】第3実施形態に係るシミュレーション結果と動作タイミングを対比した図である。

【図13】第4実施形態に係る撮像システムの構成を示すブロック図である。

【発明を実施するための形態】

【0010】

[第1実施形態]

図面を参照しながら本発明の第1実施形態を説明する。図1(a)は、第1実施形態による撮像装置の構成を示すブロック図である。撮像装置は、画素アレイ100A、垂直走査回路20、信号処理回路40、参照信号発生回路50、カウンタ60、タイミング発生回路70及び水平走査回路80を有する。

【0011】

画素アレイ100Aは、行列状に配列された複数の画素100を含む。画素100は、光電変換により入射光に応じたアナログ信号を生成して出力する回路である。図1(a)には、画素アレイ100Aのうちの3つの画素行と3つの画素列を抜き出した9個の画素100が示されている。1つの画素列に含まれる複数の画素100は、対応する出力線112(信号線)に共通に接続される。垂直走査回路20は、各画素行に含まれる複数の画素100に対し、行ごとに駆動信号を送信する。垂直走査回路20からの駆動信号に基づいて、選択された1つの画素行に含まれる複数の画素100は、並行して複数の出力線112にアナログ信号を出力する。垂直走査回路20がこのような制御を行ごとに順次行うことにより、画素アレイ100Aに含まれる各画素100からの信号が出力線112に出力される。なお、複数の画素100の個数、画素行の行数、画素列の列数等の画素アレイ100A内の画素100の配置は任意であり、図1に示されたものに限定されない。

【0012】

信号処理回路40は、列アンプ42及びアナログデジタル(Analog-to-Digital)変換回路(以下、A/D変換回路)48を含む。A/D変換回路48は、画素信号比較部44及びメモリ46を含む。信号処理回路40は、画素アレイ100Aの各画素列に対応した各出力線112から入力された信号を列ごとに処理する。信号処理回路40は、各列の出力線112から入力された信号に対して、列ごとに、増幅、バッファリング、比較、サンプルホールド、A/D変換などの信号処理を行う。

【0013】

なお、各列の出力線112と信号処理回路40との間の電気経路に、バッファ、スイッチ、増幅回路、クランプ回路などの回路素子が配されていてもよい。また、上述のように信号処理回路40はその内部に画素アレイ100Aの各画素列に対応して処理を行う回路を備え得るが、各画素列に対応しない回路を備えてもよく、複数の画素列から共通して信号が入力される回路を備えてよい。

【0014】

列アンプ42は、出力線112から入力された信号を増幅して画素信号比較部44に出力する。参照信号発生回路50は、参照信号を生成して画素信号比較部44に出力する。

10

20

30

40

50

参照信号は、例えば経過時間に応じて電圧が増加又は減少するランプ信号とすることができる。ランプ信号は時間に対して電圧が階段状に変化する信号であってもよい。画素信号比較部44は、列アンプ42からの信号と、参照信号とを比較し、比較結果を示す信号をメモリ46に出力する。カウンタ60は、時間に応じたカウント値をメモリ46に出力する。画素信号比較部44の出力信号が示す比較結果が変化したタイミングで、そのときのカウント値が、画素100からの出力信号に対応するデジタル信号として、メモリ46に記憶される。メモリ46は、水平走査回路80からの駆動信号に基づいて、保持しているカウント値を撮像装置の外部に出力する。

【0015】

タイミング発生回路70は、垂直走査回路20、列アンプ42、画素信号比較部44、メモリ46、参照信号発生回路50、カウンタ60及び水平走査回路80にクロック信号を出力し、各部の動作タイミングを制御する。 10

【0016】

なお、図1(a)に示された信号処理回路40は、アナログ信号である画素100からの信号を、デジタル信号に変換するA/D変換回路48を含んでいる。しかしながら、変形例として、信号処理回路40は、画素100からの信号をアナログ信号のまま撮像装置の外部に出力する構成であってもよい。この場合、A/D変換回路48は省略される。

【0017】

次に、画素100の構成について説明する。図1(b)は画素100の等価回路を示す図である。図1(b)は1つの画素100のみを示しているが、他の画素100も同様の構成である。 20

【0018】

画素100は、フォトダイオードを含む光電変換部D1、増幅トランジスタM8、選択トランジスタM9、転送トランジスタM10及びリセットトランジスタM11を含む。光電変換部D1は、入射された光に基づく電荷を生成し、蓄積する。転送トランジスタM10は、光電変換部D1と増幅トランジスタM8のゲートとの間に設けられる。転送トランジスタM10がオンになると、光電変換部D1に蓄積された電荷が増幅トランジスタM8のゲートに転送される。リセットトランジスタM11は、リセット電圧を供給する電源線と、増幅トランジスタM8のゲートとの間に設けられる。リセットトランジスタM11がオンになると、増幅トランジスタM8のゲートの電圧がリセットされる。選択トランジスタM9は増幅トランジスタM8と出力線112との接続を制御する。選択トランジスタM9のゲート、転送トランジスタM10のゲート及びリセットトランジスタM11のゲートには、各トランジスタのオン又はオフを制御するための駆動信号PSEL、駆動信号PTX、駆動信号PRESがそれぞれ供給される。 30

【0019】

画素100の増幅トランジスタM8は、出力線112を介して、不図示の電流源に接続される。このような構成により、増幅トランジスタM8はソースフォロア回路を構成する。選択トランジスタM9がオンのときに、増幅トランジスタM8は、光電変換部D1で生じた電荷に基づく信号を出力線112に出力する。本明細書では、光電変換部D1で生じた電荷に基づく信号を、画素100からの信号とも呼ぶ。 40

【0020】

以下、本発明の第1実施形態に係る列アンプ42に適用可能な増幅回路及びその駆動方法について図2及び図3を用いて説明する。図2は、本実施形態に係る差動増幅回路の構成の一例を示す回路図であり、図3は、図2の回路構成の動作タイミングの一例を示すタイミング図である。後述の増幅回路は、一例として列アンプ42に対応するものとするが、画素100からのアナログ信号を増幅する用途であれば任意の箇所に適用可能である。よって、第1乃至第3実施形態で開示される増幅回路は列アンプ42に適用する用途に限定されない。特に断りがない限り、上述の撮像装置についての説明は、全ての実施形態及びその変形例に適用されうる。また、上述の撮像装置の構成は一例であり、適宜変更されうる。また、以下に説明するいすれかの実施形態の一部の構成を、他の実施形態の一部と 50

置換してもよく、あるいは、他の実施形態に付加してもよい。

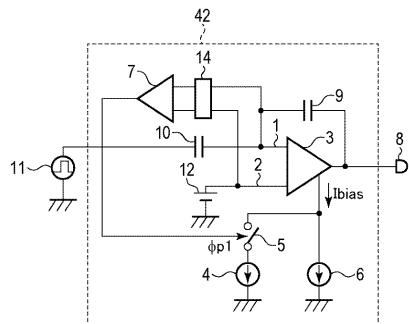

【0021】

図2において、列アンプ42は、差動増幅器3、ブースト用電流源4、スイッチ5、バイアス電流源6、比較器7、帰還容量9、入力容量10及びバイアス電圧源12を含む。画素100から列アンプ42に入力される信号は、図2においては、等価的に入力電圧源11として示されている。また、以下の説明及び後述するシミュレーションでは、入力電圧源11は、簡略化のため矩形波電圧源として扱うものとするが、本実施形態は画素100から出力され得る任意の信号波形に対して同様に適用可能である。

【0022】

差動増幅器3は、第1の入力端子である反転入力端子1及び第2の入力端子である非反転入力端子2を備える。差動増幅器3の出力端子は列アンプ42の出力端子8と接続される。入力電圧源11から列アンプ42に入力される電圧は入力容量10を介して反転入力端子1に入力される。すなわち、複数の画素100からの出力信号が伝送される信号線に相当する入力電圧源11は、入力容量10を介して反転入力端子1に電気的に接続されている。非反転入力端子2には、バイアス電圧源12からバイアス電圧が入力される。ここで、バイアス電圧は、差動増幅器3の増幅動作のための基準電圧となる電圧である。差動増幅器3の出力端子と反転入力端子1の間には、帰還容量9が接続される。列アンプ42の電圧ゲインは帰還容量9及び入力容量10の容量値により決定される。

【0023】

ブースト用電流源4、スイッチ5及びバイアス電流源6は、差動増幅器3を駆動するためのバイアス電流Ibiasを供給する電流供給部として機能する。バイアス電流源6はバイアス電流Ibiasを供給する第1の電流源であり、ブースト用電流源4はバイアス電流Ibiasを供給する第2の電流源である。ブースト用電流源4はスイッチ5を間に介して差動増幅器3と接続され、バイアス電流源6は差動増幅器3と直接接続される。スイッチ5は、比較器7から出力される制御信号p1によりオン又はオフに制御される。スイッチ5がオフとなる第1の状態においては、バイアス電流Ibiasはバイアス電流源6のみにより供給される。スイッチ5がオンとなる第2の状態においては、バイアス電流Ibiasはブースト用電流源4及びバイアス電流源6の双方により供給される。

【0024】

比較器7の2つの入力端子は、差動増幅器3の反転入力端子1及び非反転入力端子2とそれぞれ接続される。すなわち、比較器7は、反転入力端子1の電圧と非反転入力端子2の電圧とを比較し、比較結果を示す信号を出力する。換言すると、比較器7は、画素100からの信号に基づく反転入力端子1の電圧を所定のしきい値電圧である非反転入力端子2の電圧と比較する比較部としての機能を有する。この比較結果を示す信号はスイッチ5に入力され、オン／オフの制御に用いられる。本実施形態では、反転入力端子1の電圧が非反転入力端子2の電圧よりも低い場合に比較器7の出力信号がハイレベルになり、スイッチ5がオンになるものとする。

【0025】

本実施形態では差動増幅器3は反転増幅回路として動作する。しかしながら、本発明は反転増幅回路の構成に限定されず、非反転増幅回路にも適用可能である。

【0026】

次に図3を参照して本実施形態の列アンプ42の動作を説明する。図3内のVinは入力電圧源11から列アンプ42に入力される電圧を示す。Voutは出力端子8からの列アンプ42の出力電圧を示す。Vaは反転入力端子1の電圧を示す。p1は比較器7の出力信号のレベルを示す。Ibiasは差動増幅器3を駆動するバイアス電流を示す。

【0027】

時刻t1以前の初期状態において、電圧Vinはハイレベルである。このとき、電圧Vaは、差動増幅器3の入力オフセット電圧をゼロとすると、負帰還の効果によりバイアス電圧源12の電圧と等しい電圧となる。よって、制御信号p1はローレベルであり、スイッチ5はオフである。そのため、ブースト用電流源4は差動増幅器3と非接続である。

10

20

30

40

50

したがって、バイアス電流  $I_{bias}$  はバイアス電流源 6 が供給する電流  $I_6$  に一致する。

【0028】

時刻  $t_1$  において、電圧  $V_{in}$  がハイレベルからローレベルに移行する。これは、例えば画素 100 から入射光に基づく画素信号が出力されて電圧変動が生じた状態を示している。これにより、差動増幅器 3 の仮想接地の状態が破れ、電圧  $V_a$  が低下する。これとともに、電圧  $V_{out}$  が上昇し始める。反転入力端子 1 の電圧  $V_a$  が低下すると、制御信号  $p_1$  はローレベルからハイレベルに移行し、スイッチ 5 がオンになる。スイッチ 5 がオンになることで、ブースト用電流源 4 は、差動増幅器 3 に接続される。このとき、ブースト用電流源 4 が供給する電流  $I_4$  は、バイアス電流源 6 が供給する電流  $I_6$  と加算され、差動増幅器 3 のバイアス電流  $I_{bias}$  は  $I_4 + I_6$  となる。すなわち、スイッチ 5 がオンになり、ブースト用電流源 4 が差動増幅器 3 に接続されることにより、バイアス電流  $I_{bias}$  が  $I_6$  から  $I_4 + I_6$  に増大する。

【0029】

時刻  $t_2$  において、電圧  $V_a$  が上昇し元のレベルに戻ると、差動増幅器 3 は再び仮想接地の状態となり、制御信号  $p_1$  はハイレベルからローレベルに移行し、スイッチ 5 がオフになる。これにより、差動増幅器 3 のバイアス電流  $I_{bias}$  は  $I_6$  に戻る。このようにして、本実施形態の列アンプ 42 は、バイアス電流  $I_{bias}$  を時刻  $t_1$  から時刻  $t_2$  の期間において一時的に増大させることができる。

【0030】

差動増幅器 3 の出力スルーレートは、大信号振幅時においては、バイアス電流  $I_{bias}$  と増幅器内部の位相補償容量  $C_f$  (不図示) に依存する。具体的には、バイアス電流  $I_{bias}$  が大きいほど出力スルーレートは大きくなるという関係がある。よって、ブースト用電流源 4 の接続 / 非接続を制御することにより、差動増幅器 3 の出力スルーレートを変化させることができる。

【0031】

本実施形態の列アンプ 42 は、差動増幅器 3 の反転入力端子 1 の電圧と非反転入力端子 2 の電圧とを比較する比較器 7 とを備え、その比較結果に基づいてブースト用電流源 4 の接続 / 非接続が制御されている。これにより、列アンプ 42 に入力される電圧  $V_{in}$  の振幅が大きい場合にバイアス電流  $I_{bias}$  を増大させることができ、差動増幅器 3 の出力スルーレートを大きくすることができる。したがって、差動増幅器 3 のセトリング時間が短縮される。

【0032】

撮像装置の列アンプ 42 にこのような差動増幅回路を用いることにより、撮像装置の高速動作が可能となる。また、電圧  $V_{in}$  のレベルに応じてバイアス電流  $I_{bias}$  を変化させているので、電圧  $V_{in}$  のレベルによらずバイアス電流  $I_{bias}$  を大きくした場合と比べて消費電力を低減することができる。

【0033】

[第2実施形態]

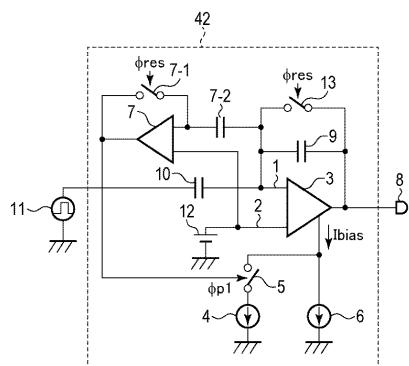

図 4、図 5 及び図 6 を用いて第2実施形態を説明する。本実施形態は、第1実施形態の列アンプ 42 の構成を変形したものである。その他の部分の構成は第1実施形態と同様であるため説明を省略する。また、第1実施形態と同様の機能を有する構成要素には同一の符号を付し、その説明を省略又は簡略化することもある。

【0034】

図 4 は、本実施形態に係る列アンプ 42 の回路構成を示す回路図である。本実施形態の列アンプ 42 は、第1実施形態の各回路要素に加え、オフセット電圧キャンセル部 14 をさらに含む。本実施形態では、比較器 7 及びオフセット電圧キャンセル部 14 が比較部として機能する。

【0035】

図 4 におけるオフセット電圧キャンセル部 14 は、差動増幅器 3 の差動入力端子間オフ

10

20

30

40

50

セット電圧と、比較器 7 のオフセット電圧の差をキャンセルする機能を有する。これにより、差動増幅器 3 及び比較器 7 のオフセット電圧に起因して生じうるバイアス電流  $I_{bias}$  の変化タイミングのずれを低減することができる。

#### 【0036】

図 5 は、図 4 におけるオフセット電圧キャンセル部 14 の具体的な構成の一例を示す図である。図 4 のオフセット電圧キャンセル部 14 は、図 5 のスイッチ 7-1、スイッチ 13 及びクランプ容量 7-2 に対応する。スイッチ 7-1 及びスイッチ 13 は、いずれも制御信号  $res$  により制御される。制御信号  $res$  がハイレベルのとき、スイッチ 7-1 及びスイッチ 13 はオンになり、制御信号  $res$  がローレベルのとき、スイッチ 7-1 及びスイッチ 13 はオフになる。スイッチ 7-1 は、比較器 7 の第 1 の入力端子と出力端子との間に設けられる。クランプ容量 7-2 は、比較器 7 の第 1 の入力端子と、差動増幅器 3 の反転入力端子 1 との間に設けられる。スイッチ 13 は、差動増幅器 3 の反転入力端子 1 と、差動増幅器 3 の出力端子との間に設けられる。

#### 【0037】

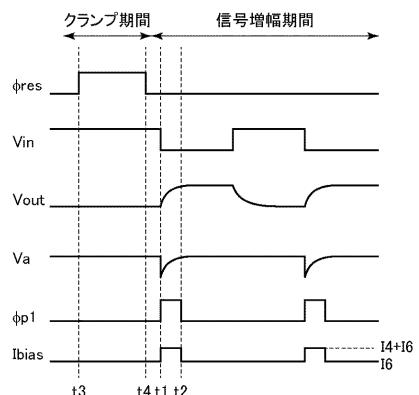

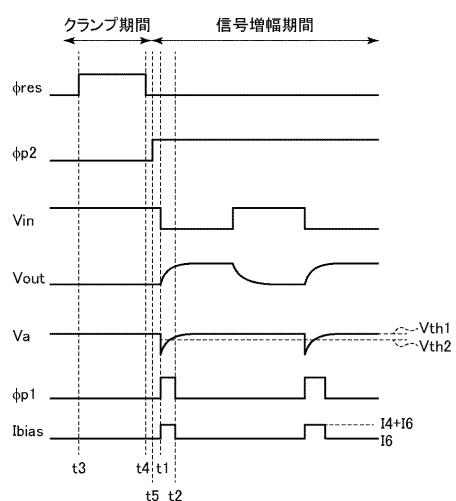

図 6 は、図 5 の回路構成の動作タイミングの一例を示すタイミング図である。図 6 のタイミング図には、図 3 に示した各電圧に加え、制御信号  $res$  の動作が示されている。図 6 の動作タイミングは、時刻  $t_3$ 、 $t_4$  を含むクランプ期間と、時刻  $t_1$ 、 $t_2$  を含む信号増幅期間との 2 つに大別される。クランプ期間は、オフセット電圧の影響を低減するために、クランプ容量 7-2 に差動増幅器 3 及び比較器 7 のオフセット電圧差をクランプする期間である。信号増幅期間の動作は図 3 と同様であるため説明を省略する。

#### 【0038】

時刻  $t_3$  以前の初期状態において、制御信号  $res$  はローレベルであり、スイッチ 7-1、13 はともにオフである。その後、クランプ期間に入り、時刻  $t_3$  になると、制御信号  $res$  がローレベルからハイレベルに移行し、スイッチ 7-1、13 がともにオンとなる。このとき、クランプ容量 7-2 には差動増幅器 3 のオフセット電圧と、比較器 7 のオフセット電圧との差に相当する電圧が印加される。時刻  $t_4$  において、制御信号  $res$  がハイレベルからローレベルに移行し、スイッチ 7-1、13 がともにオフとなる。これにより、上述のオフセット電圧差がクランプ容量 7-2 に保持される。その後の信号増幅期間の動作は図 3 のタイミング図と同様である。

#### 【0039】

信号増幅期間において、クランプ容量 7-2 に保持された電圧は、差動増幅器 3 のオフセット電圧と、比較器 7 のオフセット電圧の差をキャンセルするように作用する。そのため、オフセット電圧の差に起因する出力スルーレートが増大するタイミングのずれが、第 1 実施形態の構成よりも低減され、セトリング時間がさらに短縮される。したがって、本実施形態によれば、第 1 の実施形態の効果に加え、撮像装置の動作をより高速化する効果が得られる。

#### 【0040】

##### [第 3 実施形態]

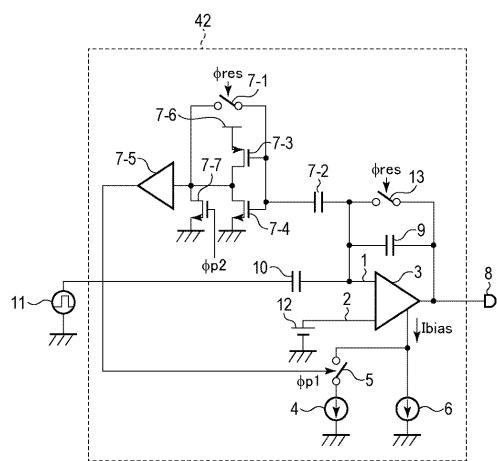

図 7 乃至図 10 を用いて第 3 実施形態を説明する。本実施形態は、第 2 実施形態の列アンプ 4-2 の構成を変形したものである。その他の部分の構成は第 2 実施形態と同様であるため説明を省略する。また、第 2 実施形態と同様の機能を有する構成要素には同一の符号を付し、その説明を省略又は簡略化することもある。

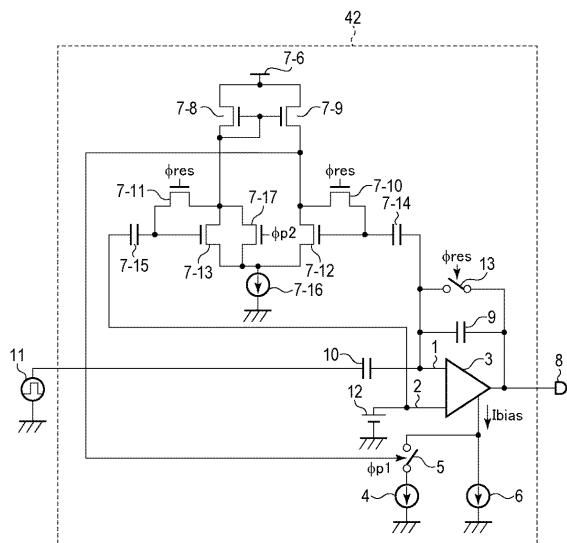

#### 【0041】

図 7 は、第 3 実施形態に係る差動増幅回路の構成の一例を示す回路図である。図 7 が図 5 と異なる点は、比較部が、PMOS トランジスタ 7-3、NMOS トランジスタ 7-4、7-7、バッファ 7-5 を用いた回路で構成されている点である。

#### 【0042】

PMOS トランジスタ 7-3 及び NMOS トランジスタ 7-4 は CMOS インバータとなっている。すなわち、差動増幅器 3 の反転入力端子 1 の電圧は、クランプ容量 7-2 を介して、CMOS インバータの入力端子である PMOS トランジスタ 7-3 及び NMOS

10

20

30

40

50

トランジスタ7-4のゲートに入力される。PMOSトランジスタ7-3のドレインと及びNMOSトランジスタ7-4のドレインは互いに接続され、CMOSインバータの出力端子となる。PMOSトランジスタ7-3のソースは電源線7-6に接続され、NMOSトランジスタ7-4のソースはグラウンド（あるいは負電源）に接続される。スイッチ7-1は、CMOSインバータの入出力端子間に接続される。このようにして構成されるCMOSインバータは、入力電圧が所定の論理しきい値を超えている場合にローレベルの電圧を出力し、入力電圧が所定の論理しきい値を下回っている場合にハイレベルの電圧を出力する論理反転回路である。

【0043】

CMOSインバータの出力端子は、NMOSトランジスタ7-7のドレイン及びバッファ7-5の入力端子と接続される。NMOSトランジスタ7-7のゲートには制御信号p2が入力される。NMOSトランジスタ7-7のソースはグラウンド（あるいは負電源）に接続される。すなわち、NMOSトランジスタ7-4とNMOSトランジスタ7-7は、並列接続の関係になっている。バッファ7-5の出力は制御信号p1としてスイッチ5に入力される。

【0044】

NMOSトランジスタ7-7はしきい値電圧シフト部としての機能を有する。すなわち、CMOSインバータ内のNMOSトランジスタ7-4に並列に接続されたNMOSトランジスタ7-7のオン又はオフを制御することにより、CMOSインバータの入力しきい値電圧をシフトさせることができる。この動作について、図8のタイミング図を参照して説明する。

【0045】

図8は、図7の回路構成の動作タイミングの一例を示すタイミング図である。図6と同様の動作については説明を省略又は簡略化する。時刻t3において、制御信号resがローレベルからハイレベルに移行し、スイッチ7-1、13がともにオンとなる。このとき、クランプ容量7-2には、差動増幅器3のオフセット電圧と、差動増幅器3の非反転入力端子2の電圧と、CMOSインバータの論理しきい値電圧Vth1とに基づく電圧が印加され、保持される。

【0046】

本実施形態の比較部では、このようにして電圧が保持されたクランプ容量7-2を介して差動増幅器3の反転入力端子1の電圧が入力される。これにより、保持された電圧と差動増幅器3の反転入力端子1の電圧との比較が行われる。

【0047】

その後時刻t5において、制御信号p2がハイレベルになり、NMOSトランジスタ7-7がオンになる。これにより、CMOSインバータの論理しきい値電圧がVth1からVth2に低下する。

【0048】

時刻t1において、電圧Vinがハイレベルからローレベルに移行すると、反転入力端子1の電圧Vaは低下する。この低下電圧が、CMOSインバータのしきい値電圧の低下量(Vth1 - Vth2)を超えるとCMOSインバータの出力は反転し、バッファ7-5の出力である制御信号p1がハイレベルになる。これにより、スイッチ5がオンになる。このようにして、図7に示す本実施形態の回路構成においても第2実施形態と同様の動作が可能であるとともに、しきい値電圧を任意に調整することができる。例えば、しきい値電圧の低下量(Vth1 - Vth2)をノイズの振幅よりも大きく設定することにより、スイッチ5がノイズによりオン/オフを繰り返すチャッタリングを抑制することができる。

【0049】

また、本実施形態では、差動増幅器3が大信号振幅時にのみバイアス電流Ibiasを増大させることが可能である。この場合、小信号振幅時にはバイアス電流Ibiasは小さい。そのため、位相補償回路の設計が容易になり得る。また、差動増幅器3の小信号帶

10

20

30

40

50

域幅を狭くすることで低ノイズとする設計と高速動作との両立もなし得る。したがって、これらの追加的な効果を有するよう設計された増幅回路を撮像装置に搭載した場合、設計自由度の向上及び低ノイズ化もなし得る。

#### 【0050】

図9は、本実施形態に係る差動増幅回路の構成の別の例を示す回路図である。図9の回路は、差動増幅器3の入力端子間の電圧を比較するための比較部を構成する回路が差動回路になっている点が図7と異なる。この差動回路は、PMOSトランジスタ7-8、7-9と、NMOSトランジスタ7-10、7-11、7-12、7-13、7-17と、クランプ容量7-14、7-15と、電流源7-16とを含む。NMOSトランジスタ7-10、7-11のゲートには制御信号resが入力され、オン又はオフに制御される。NMOSトランジスタ7-17のゲートには制御信号p2が入力され、オン又はオフに制御される。

10

#### 【0051】

差動増幅器3の反転入力端子1はクランプ容量7-14を介してNMOSトランジスタ7-12のゲートに接続される。差動増幅器3の非反転入力端子2はクランプ容量7-15を介してNMOSトランジスタ7-13のゲートに接続される。NMOSトランジスタ7-12、7-13のソースには電流源7-16が接続される。これにより、NMOSトランジスタ7-12、7-13は差動対を構成する。

#### 【0052】

PMOSトランジスタ7-8、7-9のゲートは互いに共通接続されており、この共通接続されたノードはPMOSトランジスタ7-8のドレイン及びNMOSトランジスタ7-13のドレインとも接続される。PMOSトランジスタ7-9のドレインはNMOSトランジスタ7-12のドレインと接続されており、このノードは、スイッチ5に制御信号p1を出力する差動回路の出力端子となる。PMOSトランジスタ7-8、7-9のソースは電源線7-6に接続される。これにより、PMOSトランジスタ7-8、7-9は差動回路における能動負荷として機能する。

20

#### 【0053】

NMOSトランジスタ7-10は、NMOSトランジスタ7-12のゲートとドレインとの間を短絡することができるよう設けられる。NMOSトランジスタ7-11は、NMOSトランジスタ7-13のゲートとドレインとの間を短絡することができるよう設けられる。NMOSトランジスタ7-17のドレインとソースは、NMOSトランジスタ7-13のドレインとソースにそれぞれ接続される。NMOSトランジスタ7-17は、図7のNMOSトランジスタ7-7に対応するしきい値電圧シフト部として機能する。

30

#### 【0054】

図9の回路の動作タイミングは図8と同様である。時刻t3において制御信号resがローレベルからハイレベルに移行すると、NMOSトランジスタ7-10、7-11がともにオンとなる。これにより、クランプ期間において、差動増幅器3のオフセット電圧と、差動回路のオフセット電圧との電圧差をキャンセルするような電圧がクランプ容量7-14、7-15に保持される。その後、時刻t5において、制御信号p2がローレベルからハイレベルになり、NMOSトランジスタ7-17がオンになる。これにより、前記比較器のオフセット電圧がシフトする。より具体的には、NMOSトランジスタ7-17がオフの場合に比べて、制御信号p1のレベルが反転するときの差動増幅器3の反転入力端子1の電圧がより低くなる。このようにして、図9に示す本実施形態の回路構成においても第2実施形態と同様の動作が可能であるとともに、しきい値電圧を任意に調整することができる。

40

#### 【0055】

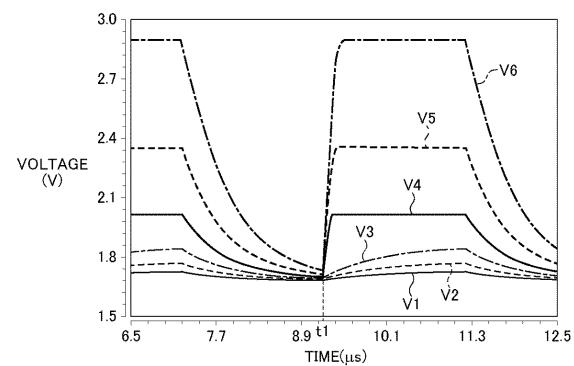

図10、図11(a)、図11(b)、図11(c)及び図12は、本実施形態による図7又は図9の回路の動作をシミュレーションした結果を示すグラフである。図10は出力端子8における電圧波形を示すグラフである。V1~V6が付された電圧波形は、入力電圧の振幅を6段階に変化させたときの出力電圧波形である。V1~V6の添字(1~6

50

)の数字が大きいものほど入力電圧の振幅が大きいものとする。電圧波形V1、V2、V3は、差動増幅器3の反転入力端子1の電圧振幅がしきい値電圧を超えない範囲である小さな入力電圧振幅の場合のシミュレーションである。電圧波形V4、V5、V6は、差動増幅器3の反転入力端子1の電圧振幅がしきい値電圧を超える大きな入力電圧振幅の場合のシミュレーションである。電圧波形V4、V5、V6のケースでは、スイッチ5がオンになり、ブースト用電流源4が、一時的に差動増幅器3にバイアス電流を供給する。

#### 【0056】

電圧波形V1、V2、V3のケースでは、時刻t1において入力電圧源11からの入力電圧が変化すると、出力電圧はなだらかに上昇する。すなわち、電圧波形V1、V2、V3においては、出力スルーレートが小さく、セトリング時間が長い。これに対し、電圧波形V4、V5、V6のケースでは、時刻t1以降出力電圧が短時間に上昇し、一定値となる。すなわち、電圧波形V4、V5、V6においては、ブースト用電流源4が供給するバイアス電流により出力スルーレートが大きくなり、セトリング時間が短縮される。

#### 【0057】

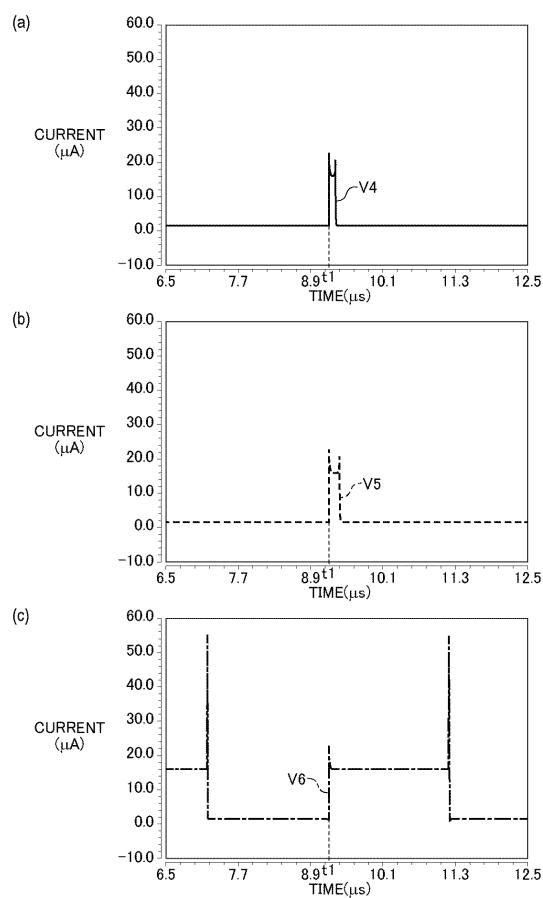

図11(a)、図11(b)、図11(c)は、それぞれ、図10の電圧波形V4、V5、V6のケースにおいて差動増幅器3に供給されるバイアス電流の変化を示すグラフである。時刻t1において、電圧波形V4、V5、V6のいずれのケースにおいても、ブースト用電流源4が差動増幅器3に接続され、バイアス電流は増加する。その後、一定時間が経過し、差動増幅器3の反転入力端子1の電圧が安定すると差動増幅器3に供給されるバイアス電流は元の値に戻る。入力電圧の振幅が大きいほどバイアス電流を増加させるブースト時間が長くなることが図11(a)、図11(b)、図11(c)より理解できる。

#### 【0058】

入力電圧の振幅とブースト時間との関係について、シミュレーション結果と動作タイミングを対比した図12を参照して説明する。電圧V<sub>in</sub>の変化が大きいほど、差動増幅器3の反転入力端子1の電圧V<sub>a</sub>の変化量も大きくなる。そのため、電圧V<sub>in</sub>の振幅が大きいほど、しきい値電圧V<sub>th2</sub>を下回る時間が長くなる。したがって、制御信号p1のパルス幅が電圧V<sub>in</sub>のレベルに応じて決まるので、ブースト時間は電圧V<sub>in</sub>のレベルに応じて調節され、消費電力の増大は最小限に抑えられる。そのため、撮像装置の高速動作と低消費電力の両立が可能となる。

#### 【0059】

##### [第4実施形態]

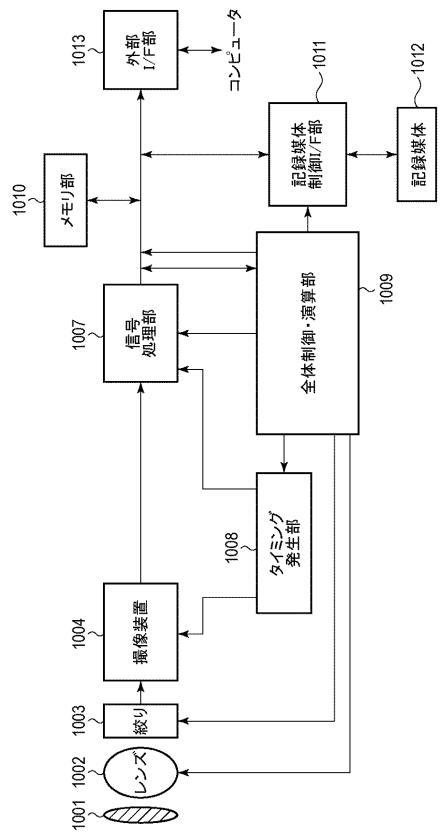

第4実施形態に係る撮像システムを説明する。撮像システムとして、デジタルスチルカメラ、デジタルカムコーダ、複写機、ファクシミリ、携帯電話、車載カメラ、観測衛星などがあげられる。図13に、第4実施形態に係る撮像システムの例としてデジタルスチルカメラのプロック図を示す。

#### 【0060】

図13において、撮像システムは、レンズの保護のためのバリア1001、被写体の光学像を撮像装置1004に結像させるレンズ1002、レンズ1002を通った光量を可変するための絞り1003を備える。撮像システムは上述の第1乃至第3実施形態で説明した撮像装置1004をさらに備え、撮像装置1004はレンズ1002により結像された光学像を画像データとして出力する。

#### 【0061】

撮像システムは、さらに信号処理部1007、タイミング発生部1008、全体制御・演算部1009、メモリ部1010、記録媒体制御I/F(インターフェース)部1011、記録媒体1012、外部I/F部1013を備える。信号処理部1007は、撮像装置1004より出力された画像データに対し各種の補正、データ圧縮等の信号処理を行う。タイミング発生部1008は、撮像装置1004及び信号処理部1007に各種タイミング信号を出力する。全体制御・演算部1009は、撮像システム全体を制御する。メモリ部1010は画像データを一時的に記憶するためのフレームメモリとして機能する。記

10

20

30

40

50

録媒体制御 I / F 部 1011 は記録媒体への記録又は読み出しを行う。記録媒体 1012 は、着脱可能な半導体メモリ、撮像システムに内蔵された半導体メモリ等から構成され、画像データの記録又は読み出しを行う。外部 I / F 部 1013 は、外部コンピュータ等との通信のためのインターフェースである。

#### 【0062】

ここで、タイミング信号等の制御のための信号は撮像システムの外部から入力されてもよく、撮像システムは少なくとも撮像装置 1004 と、撮像装置 1004 から出力された撮像信号を処理する信号処理部 1007 を有すればよい。

#### 【0063】

本実施形態に係る撮像システムは、撮像装置 1004 として第 1 乃至第 3 実施形態に係る撮像装置を備えている。そのため、本実施形態に係る撮像システムは、高速な撮像と低消費電力を両立することができる。 10

#### 【符号の説明】

#### 【0064】

- 1 差動増幅器の反転入力端子

- 2 差動増幅器の非反転入力端子

- 3 差動増幅器

- 4 ブースト用電流源

- 5 スイッチ

- 6 バイアス電流源

- 7 比較器

10

20

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

審査官 鈴木 明

(56)参考文献 特開2012-044549 (JP, A)

特開2012-124835 (JP, A)

特開2005-175517 (JP, A)

特開昭64-073906 (JP, A)

特開平06-069799 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378