(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

29 March 2012 (29.03.2012)

(10) International Publication Number

WO 2012/039120 A2

(51) International Patent Classification:

H05K 1/02 (2006.01) H01L 25/065 (2006.01)

H05K 1/16 (2006.01) H01L 23/66 (2006.01)

(21) International Application Number:

PCT/JP2011/005246

KABUSHIKI KAISHA, 30-2, Shimomaruko 3-chome, Ohta-ku, Tokyo, 1468501 (JP).

(22) International Filing Date:

16 September 2011 (16.09.2011)

(74) Agents: ABE, Takuma et al.; C/O CANON KABUSHIKI KAISHA, 30-2, Shimomaruko 3-chome, Ohta-ku, Tokyo, 1468501 (JP).

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

2010-214397 24 September 2010 (24.09.2010) JP

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(71) Applicant (for all designated States except US): CANON KABUSHIKI KAISHA [JP/JP]; 30-2, Shimomaruko 3-chome, Ohta-ku, Tokyo, 1468501 (JP).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ,

[Continued on next page]

(54) Title: PRINTED CIRCUIT BOARD

[Fig. 1]

(57) Abstract: A multi-layer printed circuit board includes an embedded capacitor substrate composed of a power source conductor layer and a ground conductor layer, the layers being disposed close to each other. The power source conductor layer has a first power source plane to supply power to a circuit element, and a second power source plane that is separated from the first power source plane by a gap and functions as a main power source. The first power source plane is partially connected to the second power source plane by a connecting line. The ground conductor layer has an opening at a position overlapping with a projected image when the connecting line is projected on the ground conductor layer. This structure suppresses propagation of the noise caused at the circuit element and reduces radiation noise in the printed circuit board.

WO 2012/039120 A2

TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

— *without international search report and to be republished upon receipt of that report (Rule 48.2(g))*

## Description

### Title of Invention: PRINTED CIRCUIT BOARD

#### Technical Field

[0001] The present invention relates to a printed circuit board having a circuit element thereon.

#### Background Art

[0002] Printed circuit boards with a circuit element mounted thereon such as integrated circuit (IC) and large-scale integration (LSI) are known to have a problem: the circuit element in a printed circuit board causes electromagnetic wave noise when turned on/off, and the noise adversely affects the other circuits of the electronic device that incorporates the printed circuit board and the other electronic devices, leading to malfunction. The noise is caused mainly by the parasitic capacitance component and the inductance component of the wiring structure electrically connecting circuit elements, and by the high-frequency current flowing through the electromagnetic coupling of these components.

[0003] In recent years, ICs and LSIs have extensively increased in processing speed to have operating frequencies from hundreds of MHz to several GHz. In the operating frequency range exceeding hundreds of MHz, the parasitic components of a noise suppression element itself or the wiring structure in the printed circuit board more and more adversely affect the circuits, so that the noise suppression components cannot achieve their original function, providing only insufficient suppression effect.

[0004] U.S. Patent No. 5,079,069 discusses use of an embedded capacitor substrate to suppress radiation noise at a frequency band exceeding hundreds of MHz. In the embedded capacitor substrate, a printed circuit board is configured to have a structure of a capacitor having a small parasitic inductance component. The embedded capacitor substrate includes a power source conductor layer and a ground conductor layer, and uses these entire layers as electrodes, and further has a thin dielectric layer with a thickness of 100 micrometer or less disposed between the power source conductor layer and the ground conductor layer to form a capacitor.

[0005] However, in the embedded capacitor substrate using the entire power source conductor layer and ground conductor layer as electrodes, noise caused locally by operation of circuit element is propagated over the substrate, increasing radiation noise.

#### Citation List

#### Patent Literature

[0006] PTL 1: U.S. Patent No. 5,079,069

## Summary of Invention

[0007] The present invention provides a printed circuit board having a circuit element thereon, in which radiation noise is reduced by suppressing propagation of noise caused by a circuit element.

[0008] The present invention provides a printed circuit board including a power source conductor layer, a ground conductor layer, and a signal wiring layer having a circuit element thereon, the power source conductor layer, the ground conductor layer, and the signal wiring layer being multilayered with a dielectric layer interposed therebetween. The printed circuit board further includes a first power source plane provided in the power source conductor layer, a second power source plane provided in the power source conductor layer at a position separated from the first power source plane by a gap, a connecting line connecting the first power source plane to the second power source plane, and a ground plane provided in the ground conductor layer, wherein the ground plane has an opening at a portion overlapping with the image of the connecting line when projected onto the ground conductor layer.

[0009] Further features of the present invention will become apparent from the following description of exemplary embodiments with reference to the attached drawings.

## Brief Description of Drawings

[0010] The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate exemplary embodiments, features, and aspects of the invention and, together with the description, serve to explain the principles of the invention.

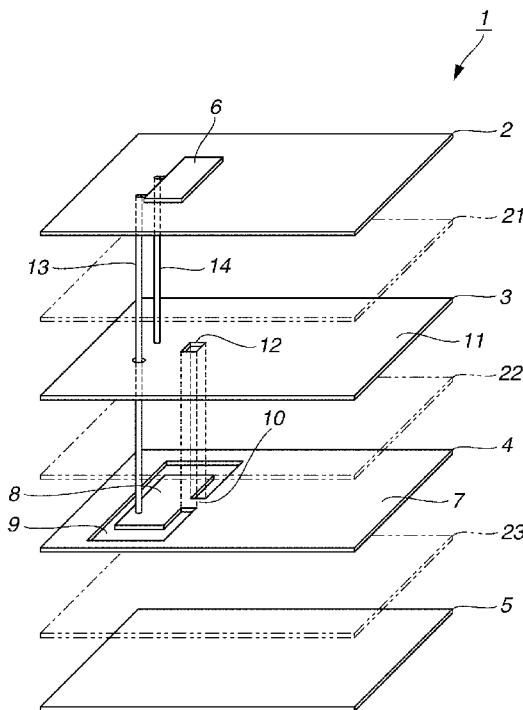

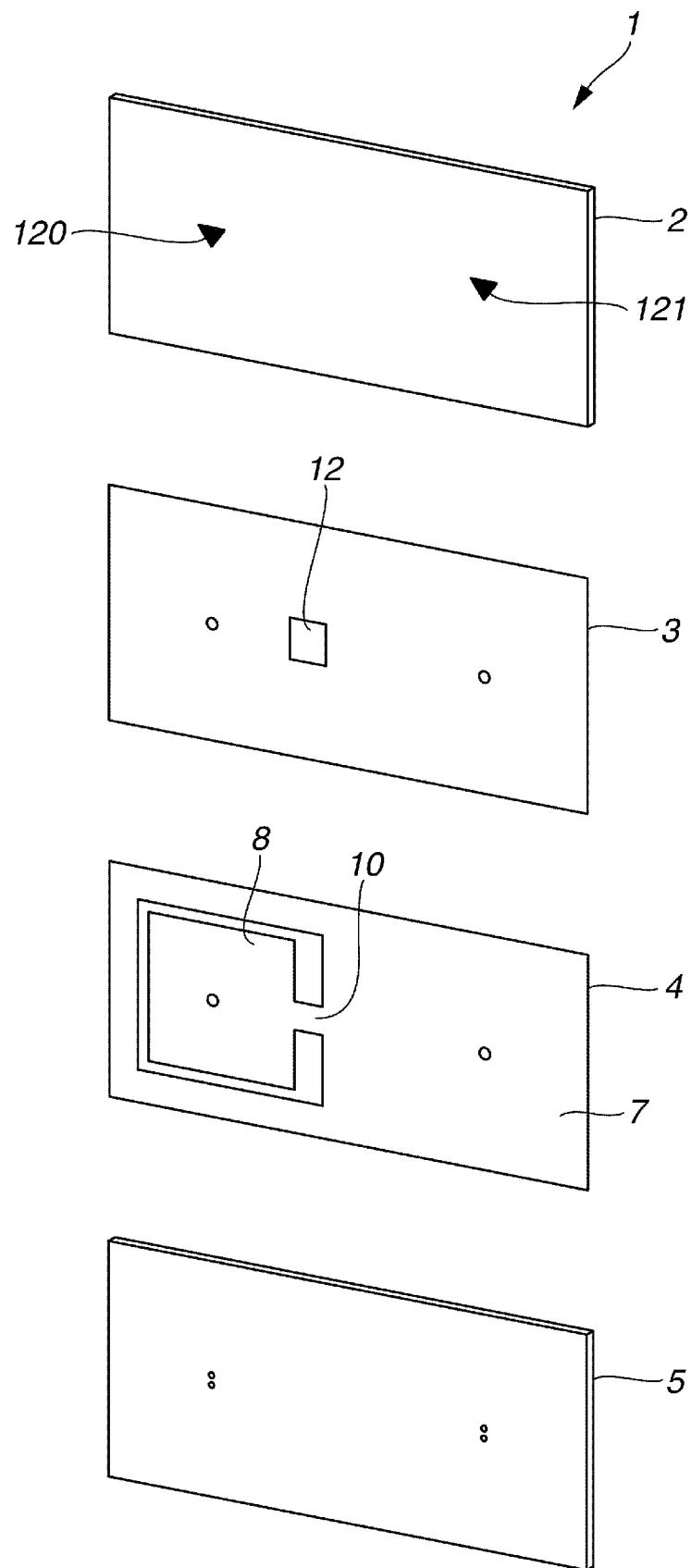

[fig.1]Fig. 1 schematically illustrates a printed circuit board according to an exemplary embodiment.

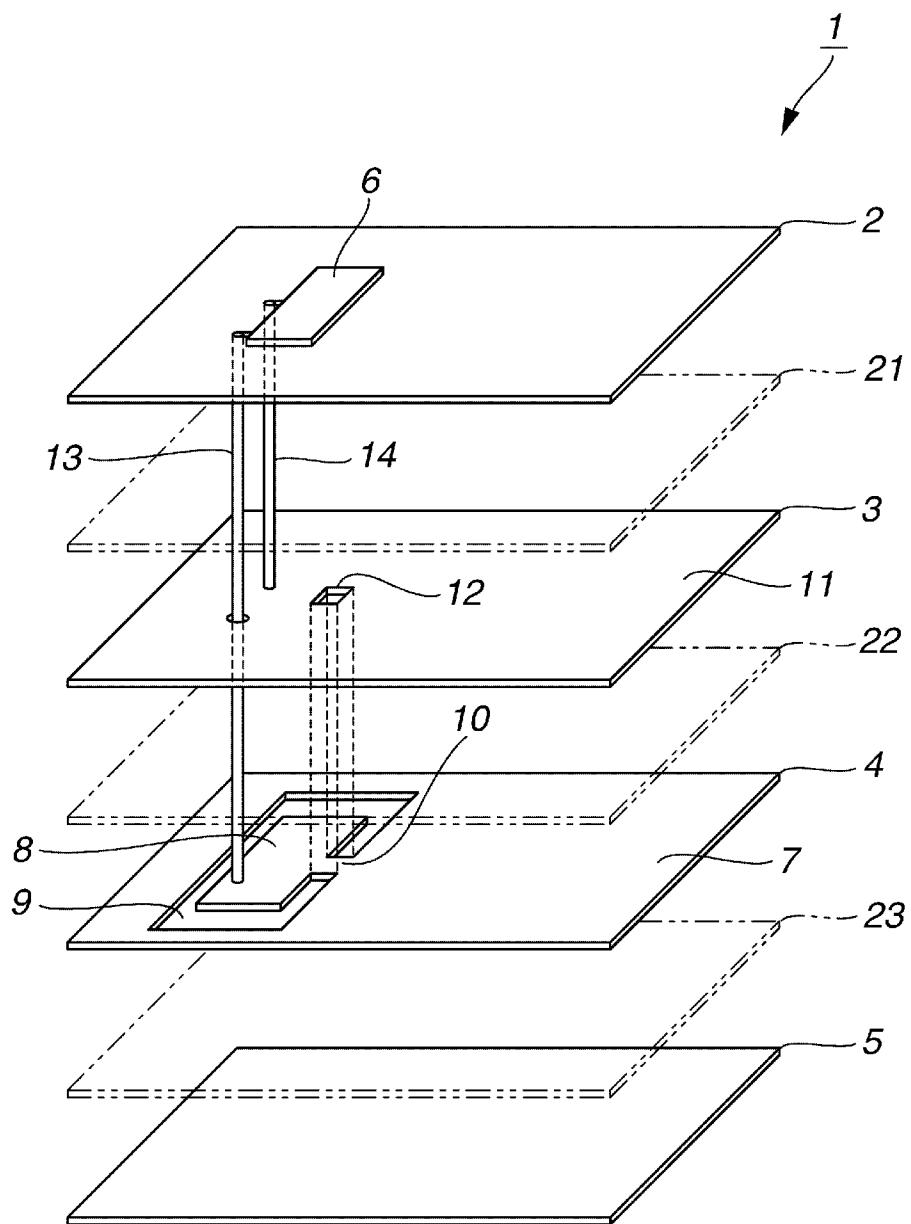

[fig.2]Fig. 2 is a circuit diagram illustrating a printed circuit board according to an exemplary embodiment.

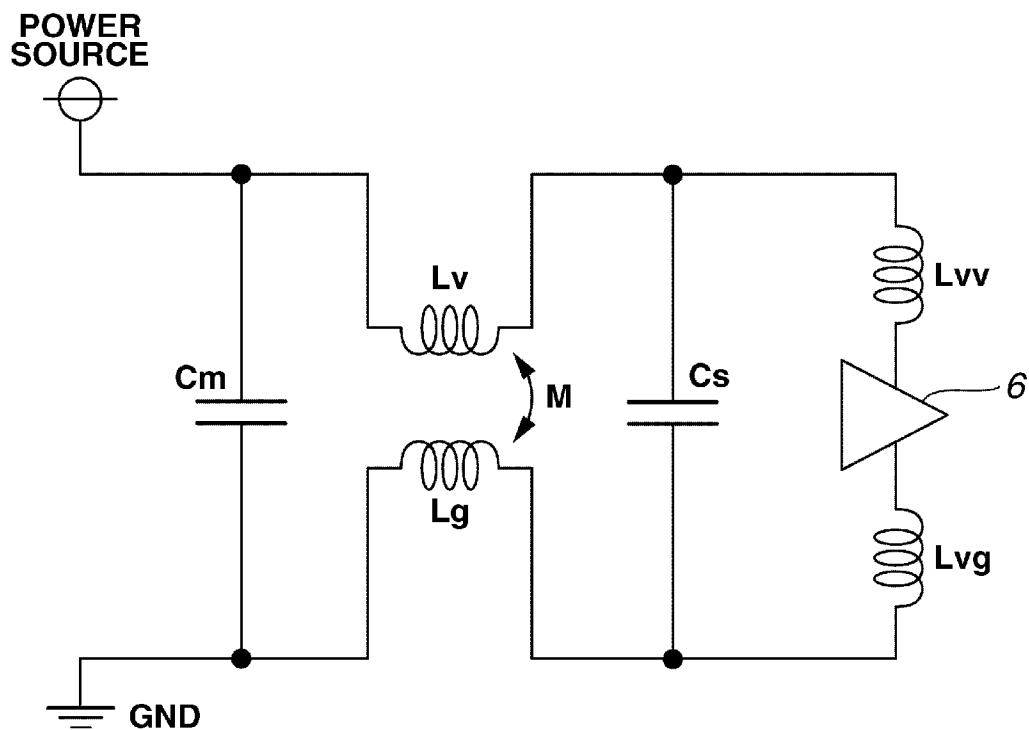

[fig.3]Fig. 3 is an exploded perspective diagram of a simulation model of a printed circuit board according to an exemplary embodiment.

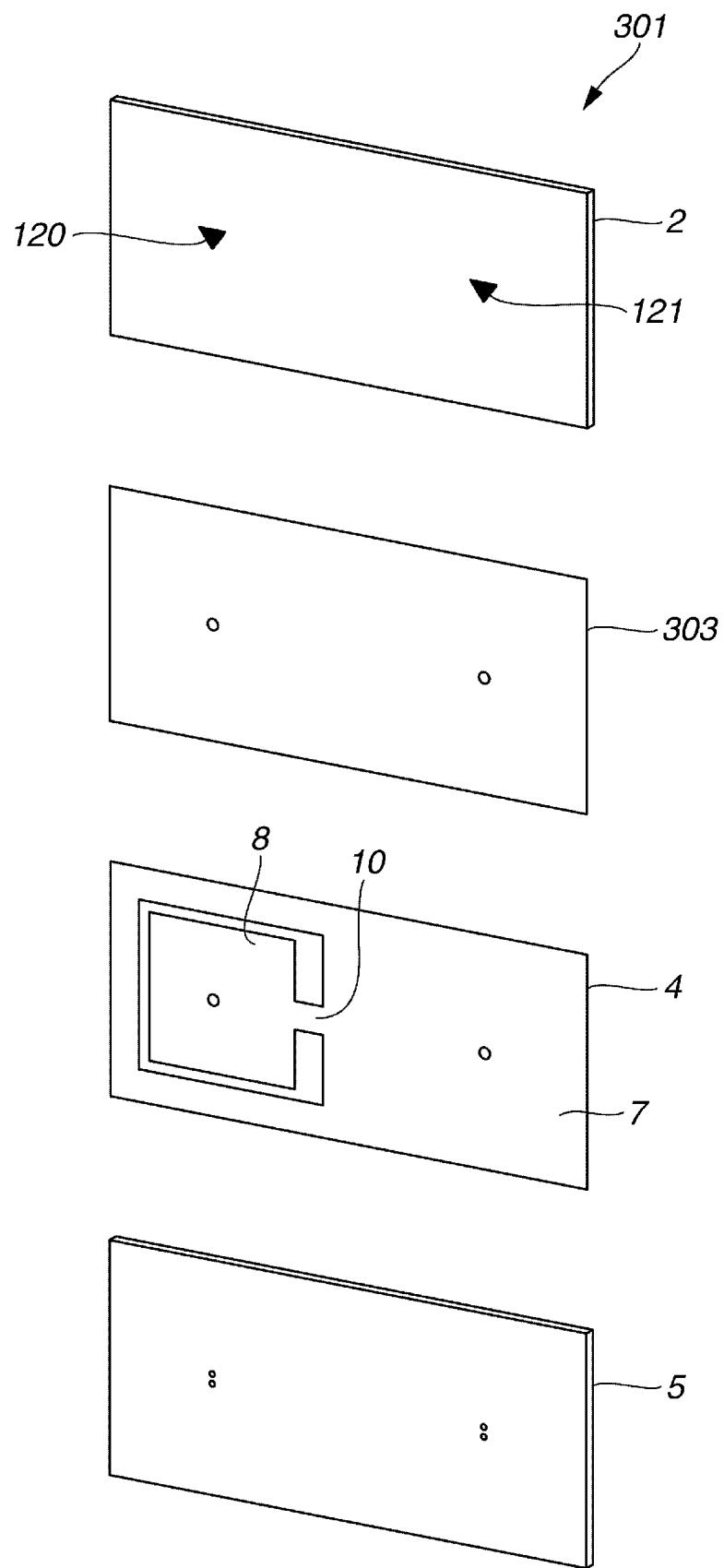

[fig.4]Fig. 4 is an exploded perspective diagram of a simulation model of a printed circuit board in a comparative example.

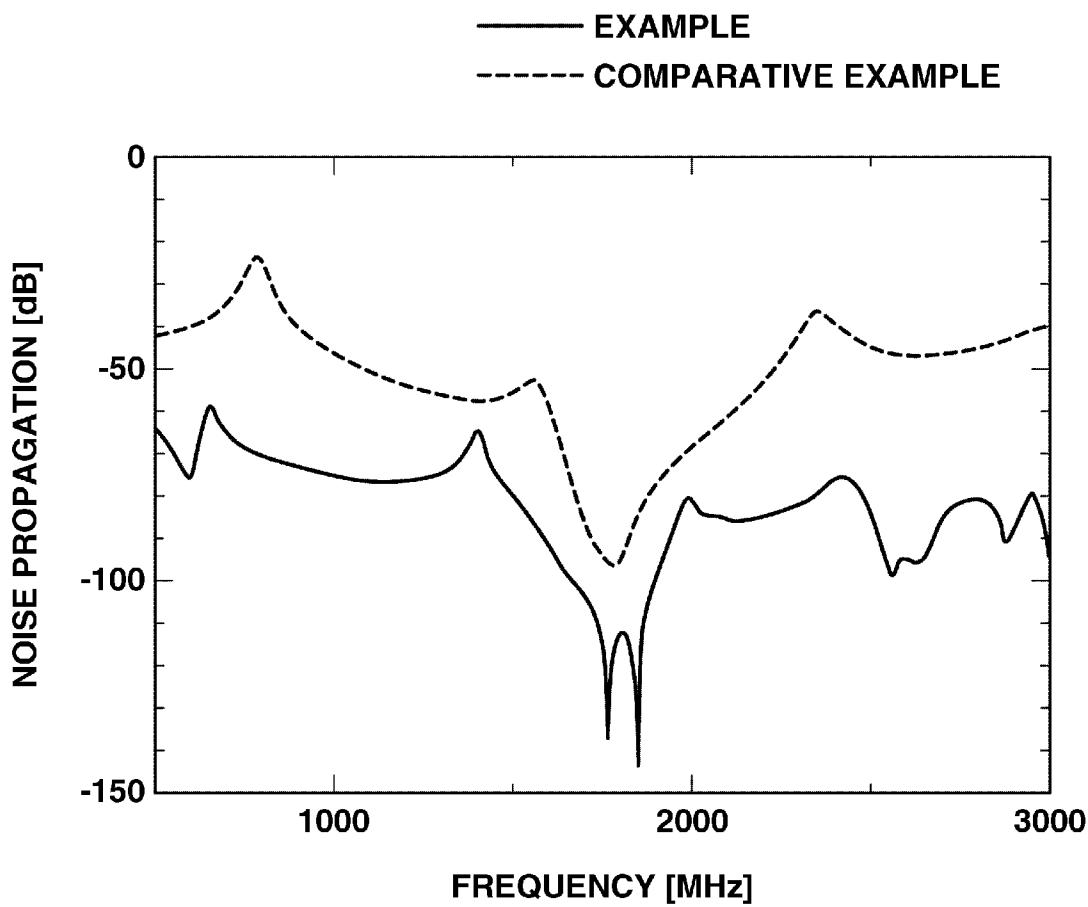

[fig.5]Fig. 5 is a graph illustrating simulation results of the printed circuit boards according to an exemplary embodiment and a comparative example respectively.

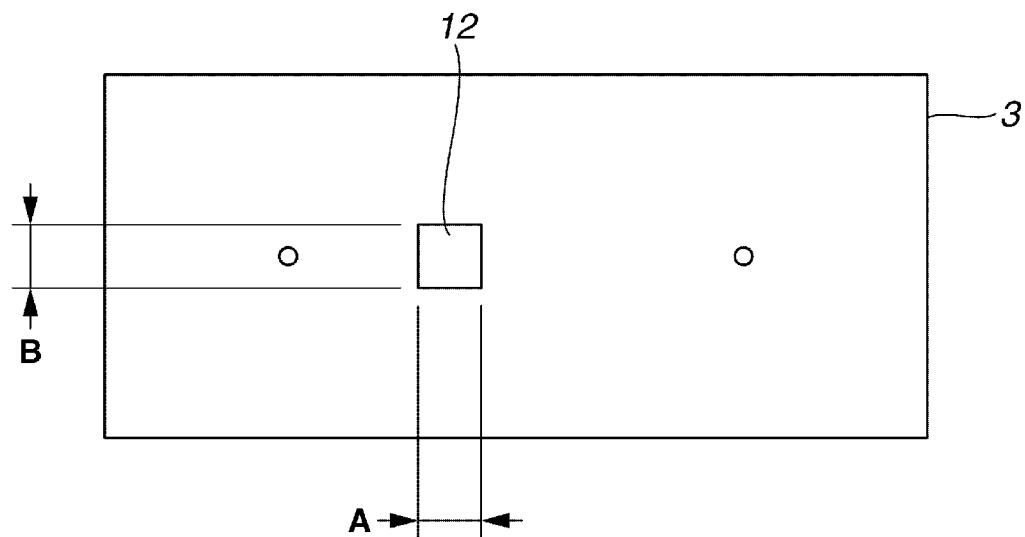

[fig.6A]Fig. 6A is a plan view illustrating a ground conductor layer of a printed circuit board according to an exemplary embodiment.

[fig.6B]Fig. 6B is a plan view illustrating a power source conductor layer of a printed circuit board according to an exemplary embodiment.

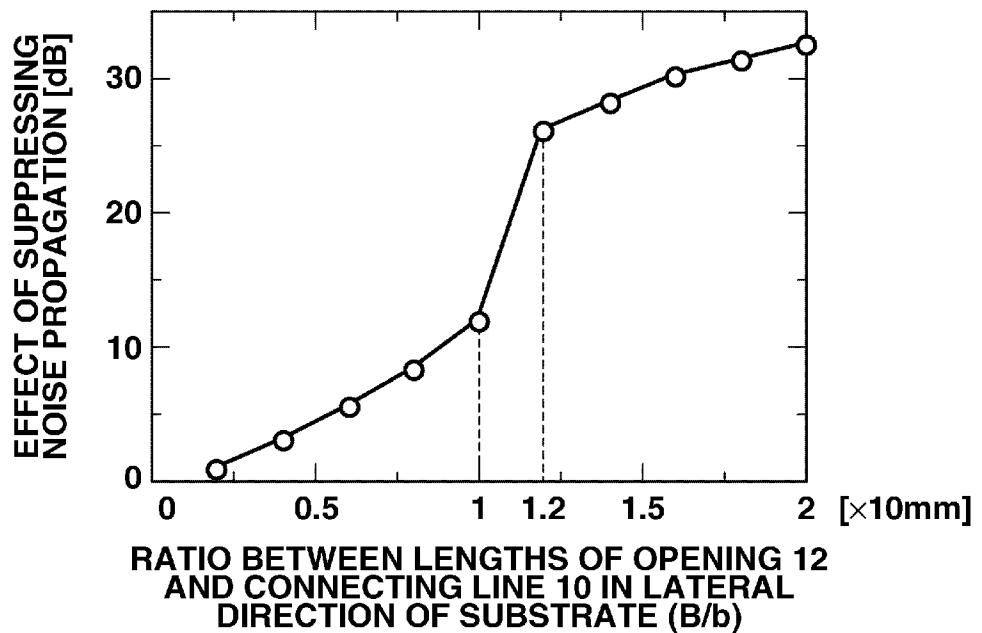

[fig.7A]Fig. 7A is a graph illustrating the effect of suppressing noise propagation in a simulation model of a printed circuit board according to an exemplary embodiment.

[fig.7B]Fig. 7B is a graph illustrating the effect of suppressing noise propagation in a simulation model of a printed circuit board according to an exemplary embodiment.

## Description of Embodiments

- [0011] Various exemplary embodiments, features, and aspects of the invention will be described in detail below with reference to the drawings.

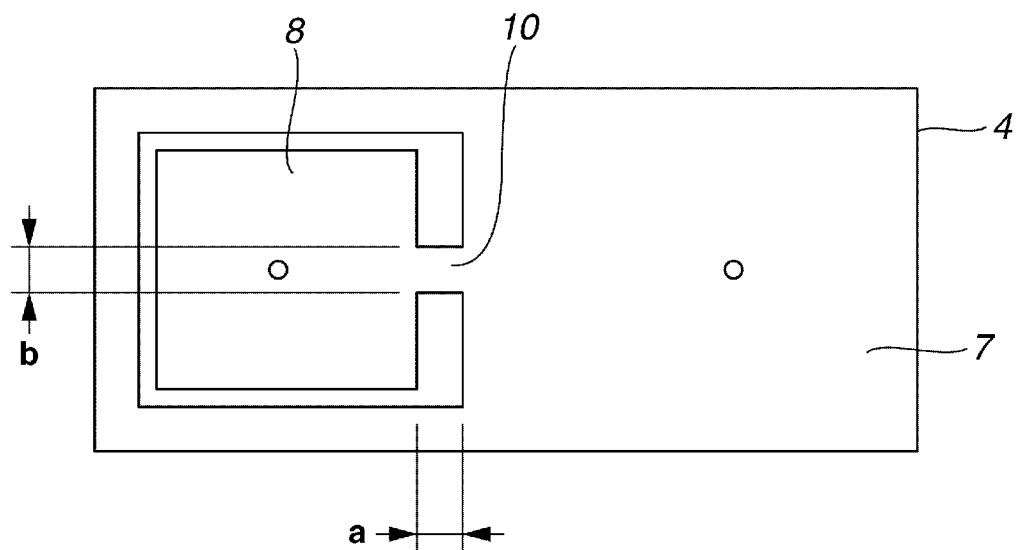

- [0012] Fig. 1 schematically illustrates a printed circuit board according to an exemplary embodiment. A printed circuit board 1 according to the present exemplary embodiment is a multi-layer printed circuit board having a first signal wiring layer 2, a ground conductor layer 3, a power source conductor layer 4, and a second signal wiring layer 5, the layers being multilayered in sequence with insulator layers (conductor layers) 21, 22, and 23 respectively interposed therebetween.

- [0013] The insulator layers 21, 22, and 23 are provided with an isolator (dielectric) that is composed of resin or glass fiber for example. The power source conductor layer 4 is located opposite the ground conductor layer 3 with the insulator layer 22 interposed therebetween to form an embedded capacitor. The insulator layer 22 in the embedded capacitor satisfies the following condition either (1) or (2), or both of (1) and (2): (1) having a thickness of 100 micrometer or less; and (2) being composed of a high dielectric material having a relative permittivity of 5 or more. The first wiring layer 2 has a semiconductor apparatus 6 as a circuit element such as IC and LSI provided with signal lines, power source lines, and ground lines (not illustrated). Furthermore, while the first signal wiring layer 2 and the second signal wiring layer 5 are signal wiring layers mainly for supplying a signal to the semiconductor apparatus 6, other than wiring layers for signals, a conductor for ground and a conductor for the power source can also be provided there.

- [0014] The power source conductor layer 4 includes a main power supply plane 7 and an IC power supply plane 8 separated from each other by a gap. The main power supply plane 7 is connected to the IC power supply plane 8 by a connecting line 10.

- [0015] The IC power supply plane 8 is a first power source plane to supply a power source potential (power) supplied from the main power supply plane 7 to the semiconductor apparatus 6. The IC power supply plane (first power source plane) 8 preferably has a size to accommodate the area of an image of the semiconductor apparatus 6 when projected onto the power source conductor layer 4. In the present exemplary embodiment, the IC power supply plane 8 has a size to fit (the same size as that of) an image of the semiconductor apparatus 6 when projected onto the power source conductor layer 4. The semiconductor apparatus 6 has a power source terminal connected to the IC power supply plane 8 through a via 13.

- [0016] The main power supply plane 7 is a second power source plane provided in the

power source conductor layer 4, and separated from the IC power supply plane 8 by a gap. More specifically, the main power supply plane 7 has an approximately C-shaped opening 9 which separates the IC power supply plane 8 as an island from the main power supply plane 7. The connecting line 10 connects the IC power supply plane 8 to the main power supply plane 7.

- [0017] The connecting line 10 is a linear strip connecting a side of the main power supply plane 7 to a side of the IC power supply plane 8 which are opposing each other. In the above structure, power can be supplied to the power source terminal of the semiconductor apparatus 6. In Fig. 1, only one connecting line 10 is provided, but more than two connecting lines 10 may be provided as needed. Furthermore, while the power source conductor layer 4 is a conductor layer mainly for supplying power source potential to the semiconductor apparatus 6, other than the conductor for the power source, a conductor for ground and a wiring layer for signal can also be provided there.

- [0018] The ground conductor layer 3 has a ground plane 11 covering almost all over the ground conductor layer 3. The semiconductor apparatus 6 has a ground terminal connected to the ground plane 11 through a via 14. The ground plane 11 has an opening 12 at a position overlapping with an image of the connecting line 10 when projected on the ground conductor layer 3. In the present exemplary embodiment, the opening 12 has a shape approximately the same as that of the image of the connecting line 10 when projected.

- [0019] The second signal wiring layer 5 is provided with wiring patterns and electronic parts (not illustrated). In the present exemplary embodiment, the ground conductor layer 3 is disposed closer to the first signal wiring layer 2 having the semiconductor apparatus 6 thereon than the power source conductor layer 4, but the power source conductor layer 4 may be disposed closer to the first wiring layer 2.

- [0020] When the semiconductor apparatus 6 starts to operate, noise current caused by the operation will flow from the IC power supply plane 8 to the main power supply plane 7 through the connecting line 10. At this point, feedback current of the noise will start to flow over the ground plane 11 on the ground conductor layer 3. In other words, the current flowing through the connecting line 10 has reverse phase components to those of the current flowing over the ground plane 11.

- [0021] Fig. 2 illustrates an equivalent circuit of the power source conductor layer 4 and the ground conductor layer 3 which constitute an embedded capacitor substrate. In Fig. 2, the circuit has a self inductance component  $L_v$  in the connecting line 10, a self inductance component  $L_g$  near the opening 12 in the ground plane 11, and a mutual inductance component  $M$  between the connecting line 10 and the opening 12 in the ground plane 11, a capacitance component  $C_m$  between the main power supply plane 7 and the ground conductor layer 3, and a capacitance component  $C_s$  between the IC

power supply plane 8 and the ground conductor layer 3.

[0022] The circuit further has an inductance component  $L_{vv}$  mainly caused by the via 13 connecting the IC power supply plane 8 to the power source terminal of the semiconductor apparatus 6, and an inductance component  $L_{vg}$  mainly caused by the via 14 connecting the ground conductor layer 3 to the ground terminal of the semiconductor apparatus 6. To suppress propagation of a noise current, an effective inductance  $L_x$  of the connecting line 10 is increased. The effective inductance  $L_x$  can be expressed as follows.

[0023]

$$L_x = L_v + L_g - 2M \quad (1)$$

[0024] In this case, directions of the high-frequency current for supplying power to the semiconductor device 6 through the connecting line 10 and that through the ground plane 11 are opposite. Thereby, the mutual inductance component is subtracted from the sum of the inductance components  $L_v$  and  $L_g$ .

[0025] More specifically, if the opening 12 is arranged at a position of an image of the connecting line 10 when projected on the ground conductor layer 3, the mutual inductance component  $M$  is extremely reduced, as compared with the case without the opening 12. Accordingly, despite of the size of the opening 12, the opening 12 at a position overlapping with the projected image area reduces the mutual inductance component  $M$ , increasing the effective inductance  $L_x$ , and enhancing the connect impedance.

[0026] In other words, the noise that is otherwise propagated to the entire substrate can be confined within the IC power supply plane 8 by the high impedance connection. As a result, not only the noise radiated from the substrate acting as an antenna, but also the noise propagated to cables through connectors disposed at the ends of the substrate and radiated by the cables and a housing that can act as antennas can be suppressed. In this way, since the impedance at the connecting line 10 becomes high, the noise caused by the operation of the semiconductor device 6 at the IC power supply plane 8 can be suppressed and cannot be propagated to the main power supply plane 7, thus reducing radiation noise.

[0027] The opening 12 preferably has a size equal to or more than the projected image when the connecting line 10 is projected onto the ground conductor layer 3. A value of the mutual inductance component  $M$  varies inversely proportional to the distance between conductors. Accordingly, in the multi-layer printed circuit board having a thin space between layers, the mutual inductance component  $M$  sharply decreases when the conductors are separated from each other out of their opposed positions on the projection plane as seen in the vertical direction. Especially in the embedded capacitor substrate, the decrease is prominent. Thus, a larger opening 12 results in a smaller mutual inductance component  $M$ .

[0028] Accordingly, the opening 12 having a size equal to or larger than the connecting line 10 can more effectively increase the effective inductance  $L_x$ , more effectively suppress the propagation of a noise current, and more effectively reduce radiation noise.

[0029] Especially, the opening 12 preferably has a shape approximately the same as that of an image of the connecting line 10 when projected on the ground conductor layer 3. This structure effectively increases the effective inductance  $L_x$  while keeping an area of the opening 12 small, so that a sufficient area of the ground plane 11 can be maintained to ensure a returning path of a signal current. Accordingly, the propagation of a noise current can be more effectively suppressed, and radiation noise can be more effectively reduced.

[0030] The present invention has been described by way of the above exemplary embodiment, but the present invention is not limited to the exemplary embodiment. The above exemplary embodiment has been described using a multi-layer printed circuit board having four layers, but the same effect can be obtained by a multi-layer printed circuit board having a different number of layers, provided that the printed circuit board is configured to include an embedded capacitor to have the above described structure.

[0031] In the above exemplary embodiment, the ground plane 11 is provided with the opening 12 having the same size (rectangular shape) of the connecting line 10, but the opening 12 may be of a different shape.

[0032] For example, the ground plane 11 may be divided into a first ground plane containing an image area of the semiconductor apparatus 6 when projected onto the ground conductor layer 3, and a second ground plane provided in the ground conductor layer 3 and separated from the first ground plane by a gap. In this case, an opening needs to be provided so that the ground plane 11 is divided into the first ground plane and the second ground plane. The first ground plane can be connected to the second ground plane by a connecting line, which only needs to be located at a position that does not overlap with an image of the connecting line 10 when projected onto the ground conductor layer 3.

[0033] When the IC needs a plurality of different power sources, the first power source plane at an IC power supply unit and the second power source plane at a main power supply unit are configured with a plurality of lines.

### Examples

[0034] To verify the effect described in the above exemplary embodiment, a simulation was performed using an electromagnetic field simulation software, MW-Studio (manufactured by Computer Simulation Technology Inc.(CST)). Fig. 3 is an exploded perspective diagram illustrating wiring structures of conductor layers of a simulation

model in the present Example. Fig. 3 illustrates the first signal wiring layer 2, the ground conductor layer 3, the power source conductor layer 4, and the second signal wiring layer 5. The printed circuit board 1 illustrated in Fig. 3 has a rectangular shape of 40 mm x 90 mm. Each of the first signal wiring layer 2, the ground conductor layer 3, the power source conductor layer 4, and the second signal wiring layer 5 is made of a 50micrometer thick copper.

- [0035] Between the conductor layers, the insulator layers 21, 22, and 23 (see Fig. 1) each having a relative permittivity of 4.3 are interposed. The insulator layer 21 has a thickness of 100 micrometer, the insulator layer 22 has a thickness of 50 micrometer, and the insulator layer 23 has a thickness of 1.3 mm.

- [0036] The IC power supply plane 8 is a square of 26 mm x 26 mm, and is separated from the main power supply plane 7 by a 4-mm width gap. The IC power supply plane 8 is connected to the main power supply plane 7 by the connecting line 10, which is a strip conductor having a 4-mm length in the direction parallel to the longitudinal direction of the printed circuit board 1, and a 5-mm length in the direction parallel to the lateral direction of the printed circuit board 1. In other words, the connecting line 10 is 4 mm long in its extending direction, and 5 mm long in the direction orthogonal to the extending direction.

- [0037] The ground plane 11 is provided with the opening 12 of a size to fit (the same size as that of) an image of the connecting line 10 when projected onto the ground conductor layer 3, the opening 12 being 4 mm long in the direction parallel to the longitudinal direction of the printed circuit board 1, and 5 mm long in the direction parallel to the lateral direction of the printed circuit board 1.

- [0038] An input port 120 is connected, at one end thereof, to the IC power supply plane 8, and to the ground conductor layer 3 at the other end thereof. An output port 121 is connected to the main power supply plane 7 at one end, and to the ground conductor layer 3 at the other end. Each port has a 50 ohm impedance. Using the above described model, noise propagation to the output port 121 when Gaussian pulses with 1-V amplitude were input to the input port 120 was simulated and calculated.

- [0039] To check the effect of suppressing noise propagation in the present Example, a simulation model for a conventional printed circuit board was made in a Comparative Example, and the resultant calculation in the Comparative Example was compared with that in the Example. Fig. 4 is an exploded perspective diagram illustrating line structures of conductor layers of a simulation model for a printed circuit board 301 in the present Comparative Example. The simulation model for a printed circuit board 301 in the present Comparative Example in Fig. 4 differs from that for the printed circuit board 1 in the Example in Fig. 3 in that the simulation model in the present Comparative Example does not have an opening in a ground conductor layer 302

thereof.

[0040] Fig. 5 illustrates simulation results for the printed circuit board 1 in the Example that is depicted by the solid line, and simulation results for the printed circuit board 301 in the present Comparative Example that is depicted by the dashed line. In Fig. 5, the horizontal axis represents frequency, and the vertical axis represents noise propagation. As is obvious from Fig. 5, the propagation of a noise current from the input port 120 to the output port 121 in the printed circuit board 1 in the Example is much less than that in printed circuit board 301 in the Comparative Example. The difference proves that the structure of the printed circuit board 1 in the Example suppresses the propagation of noise current to the entire printed circuit board.

[0041] Next, the relationship between the size of the rectangular opening 12 in the ground plane 11 and the effect of suppressing noise propagation was examined: the opening 12 having a side length (the length parallel to the longitudinal direction of the connecting line 10) and another side length (the length parallel to the lateral direction of the connecting line 10). Figs. 6A and 6B each illustrate a conductor layer as a part of the simulation model for the printed circuit board 1 in the Example as a plan view: Fig. 6A illustrates the ground conductor layer 3; and Fig. 6B illustrates the power source conductor layer 4.

[0042] In Fig. 6A, the opening 12 has a side length A parallel to the longitudinal direction of the connecting line 10, and a side length B parallel to the lateral direction of the connecting line 10. In Fig. 6B, the connecting line 10 has a length a in its extending direction, and another length b in its lateral direction.

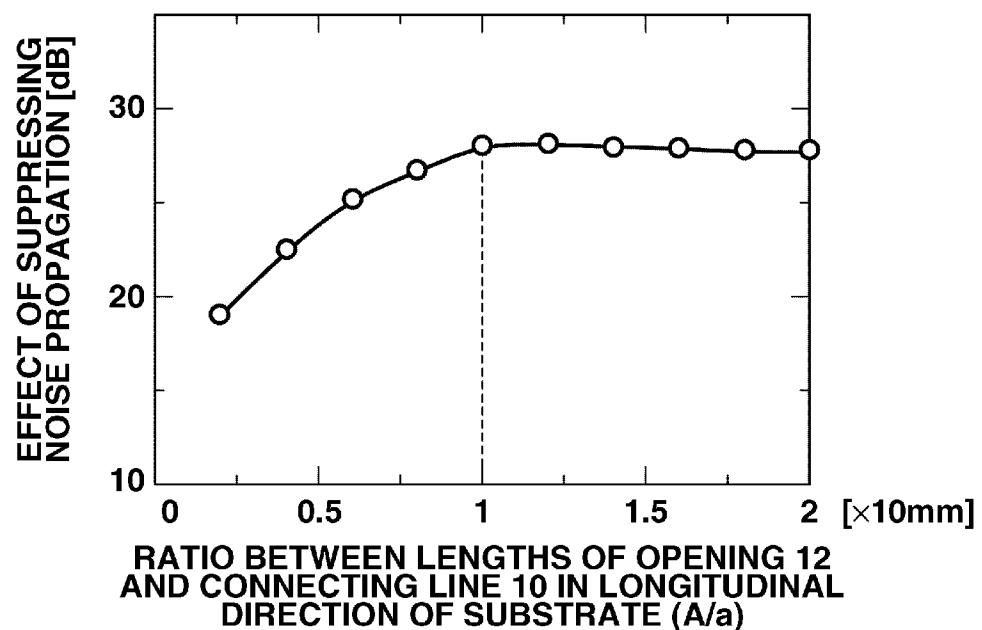

[0043] First, the length A of the opening 12 in Fig. 6A was changed in a range from 1 mm to 20 mm to obtain a noise propagation amount by a simulation. The simulated result was compared with a noise propagation amount in the Comparative Example, and the difference is shown in Fig. 7A as the effect of suppressing noise propagation. In Fig. 7A, the horizontal axis represents a ratio (A/a) between the side length A (the length along the longitudinal length of the substrate) of the opening 12 and the length a (the length along the longitudinal length of the substrate) of the connecting line 10, and the vertical axis represents the effect of suppressing noise propagation at frequency of 1.5 GHz.

[0044] The effect of suppressing noise propagation shows certain inclination within a wide range from hundreds of MHz to several GHz, and the result in the present Example at the frequency of 1.5 GHz is a typical example.

[0045] As illustrated in Fig. 7A, the effect of suppressing noise propagation remains at the almost same level after the ratio (A/a) reaches one. Therefore, the opening 12 having a side length A that is equal to or more than the length a of the connecting line 10 in its extending direction seems to maximize the effect of suppressing noise propagation.

[0046] Next, the another length B of the opening 12 in Fig. 6A was changed within a range from 1 mm to 20 mm to obtain a noise propagation amount by simulation. The simulated result was compared with a noise propagation amount in the Comparative Example, and the difference is shown in Fig. 7B as the effect of suppressing noise propagation. In Fig. 7B, the horizontal axis represents a ratio (B/b) between the side length B (the length along the lateral length of the substrate) of the opening 12 and the length b (the length along the lateral length of the substrate) of the connecting line 10, and the vertical axis represents the effect of suppressing noise propagation at frequency of 1.5 GHz.

[0047] As illustrated in Fig. 7B, the effect of suppressing noise propagation is increased after the ratio (B/b) reaches one. Especially, the effect is sharply increased between the ratio (B/b) of 1 and the ratio (B/b) of 1.2. Thus, further enhanced effect of suppressing noise propagation is obtained when the ratio (B/b) is equal to or more than 1.2. Therefore, the opening 12 having a side length B that is equal to or more than the length b of the connecting line 10 in its lateral direction maximizes the effect of suppressing noise propagation.

[0048] While the present invention has been described with reference to exemplary embodiments, it is to be understood that the invention is not limited to the disclosed exemplary embodiments. The scope of the following claims is to be accorded the broadest interpretation so as to encompass all modifications, equivalent structures, and functions.

[0049] This application claims priority from Japanese Patent Application No. 2010-214397 filed September 24 2010, which is hereby incorporated by reference herein in its entirety.

## Claims

[Claim 1] A printed circuit board, wherein

a power source conductor layer;

a ground conductor layer; and

a signal wiring layer having a circuit element thereon;

are multilayered with dielectric layers interposed therebetween, the

printed circuit board, comprising;

a first power source plane provided in the power source conductor layer

to supply a power source potential to the circuit element;

a second power source plane provided in the power source conductor

layer separated from the first power source plane by a gap;

a connecting line connecting the first power source plane to the second

power source plane; and

a ground plane provided in the ground conductor layer,

wherein the ground plane has an opening at a portion overlapping with

a projected image when the connecting line is projected onto the

ground conductor layer.

[Claim 2] The printed circuit board according to claim 1, wherein the opening has

a size equal to or larger than the projected image when the connecting

line is projected onto the ground conductor layer.

[Claim 3] The printed circuit board according to claim 1, wherein the dielectric

layer interposed between the power source conductor layer and the

ground conductor layer has a thickness equal to or less than 100 mi-

crometer.

[Fig. 1]

[Fig. 2]

[Fig. 3]

[Fig. 4]

[Fig. 5]

[Fig. 6A]

[Fig. 6B]

[Fig. 7A]

[Fig. 7B]