(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

29 November 2007 (29.11.2007)

PCT

(10) International Publication Number

WO 2007/136412 A2(51) International Patent Classification:

*B21C 1/00* (2006.01)(74) Agents: **DONALD, J., Featherstone et al.**; Sterne, Kessler, Goldstein & Fox P.L.L.C., 1100 New York Avenue, N.W., Washington, DC 20005-3934 (US).

(21) International Application Number:

PCT/US2006/048456

(22) International Filing Date:

20 December 2006 (20.12.2006)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

60/754,519 29 December 2005 (29.12.2005) US

(71) Applicant (for all designated States except US):

**NANOSYS, INC.** [US/US]; 2625 Hanover Street, Palo Alto, CA 94304 (US).

(71) Applicants and

(72) Inventors: **PAN, Yaoling** [US/US]; 34964 Eastin Drive, Union City, CA 94587 (US). **DUAN, Xiangfeng** [CN/US]; 1200 Dale Avenue, Apt. 131, Mountain View, CA 94040 (US). **DUBROW, Robert, S.** [US/US]; 766 Orange Avenue, San Carlos, CA 94070 (US). **GOLDMAN, Jay, L.** [US/US]; 1200 Dale Avenue, Apt. 131, Mountain View, CA 94040 (US). **MOSTARSHED, Shahriar** [US/US]; 1951 O'Farrell Street#405, San Mateo, CA 94403 (US). **NIU, Chunming** [US/US]; 450 Loma Verde Avenue, Palo Alto, CA 94306 (US). **ROMANO, Linda, T.** [US/US]; 1055 Westchester Drive, Sunnyvale, CA 94087 (US). **STUMBO, David, P.** [US/US]; 1561 6th Avenue, Belmont, CA 94002 (US). **FISCHER-COLBRIE, Alice** [US/US]; 615 Handley Trail, Redwood City, CA 94062 (US). **SAHI, Vijendra** [CA/US]; 3637 Fair Oaks Avenue, Menlo Park, CA 94025 (US). **ROBBINS, Virginia** [US/US]; 20311 Beatty Ridge Road, Los Gatos, CA 95033 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Declaration under Rule 4.17:**

— as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

**Published:**

— without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: METHODS FOR ORIENTED GROWTH OF NANOWIRES ON PATTERNED SUBSTRATES

(57) Abstract: The present invention is directed to systems and methods for nanowire growth and harvesting. In an embodiment, methods for nanowire growth and doping are provided, including methods for epitaxial oriented nanowire growth using a combination of silicon precursors, as well as use of patterned substrates to grow oriented nanowires. In a further aspect of the invention, methods to improve nanowire quality through the use of sacrificial growth layers are provided. In another aspect of the invention, methods for transferring nanowires from one substrate to another substrate are provided.

## METHODS FOR ORIENTED GROWTH OF NANOWIRES ON PATTERNEDE SUBSTRATES

### BACKGROUND OF THE INVENTION

#### Field of the Invention

[0001] The present invention relates to nanowires, and more particularly, to nanowire growth and harvesting.

#### Background of the Invention

[0002] Nanostructures, and in particular, nanowires have the potential to facilitate a whole new generation of electronic devices. A major impediment to the emergence of this new generation of electronic devices based on nanostructures is the ability to effectively grow and harvest nanowires and other nanostructures that have consistent characteristics. Current approaches to grow and harvest nanowires do not facilitate mass production and do not yield consistent nanowire performance characteristics.

[0003] What are needed are systems and methods to grow and harvest nanowires that have consistent performance characteristics.

## SUMMARY OF THE INVENTION

**[0004]** The present invention provides methods for producing nanowires that include depositing one or more nucleating particles on a substrate material; heating the nucleating particles to a first temperature, contacting the nucleating particles with a first precursor gas mixture to create a liquid alloy droplet and initiate nanowire growth, heating the alloy droplet to a second temperature, and contacting the alloy droplet with a second precursor gas mixture, whereby nanowires are grown at the site of the alloy droplet. The substrate material utilized in the processes of the present invention may be crystallographic or amorphous. Suitably, the substrate material comprises crystallographic silicon, either polycrystalline or single crystalline. In other embodiments, the substrate may be amorphous SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, or alumina.

**[0005]** In another embodiment, the present invention provides methods for producing nanowires (e.g., Si nanowires) which include depositing one or more nucleating particles (e.g., a metal catalyst such as gold nanoparticles) on a substrate material (or nucleating nanoparticles on a substrate surface (e.g., by heating a gold film coating layer on the surface)), heating the nucleating particles to a first temperature at which a first precursor gas decomposes to form a eutectic phase with the nucleating particles, contacting the nucleating particles with the first precursor gas mixture, wherein the first precursor gas mixture comprises a first precursor gas comprising at least one atomic species (e.g., Cl) that assists in orienting the growing nanowires (e.g., by etching as described in more detail below), contacting nucleating particles with a second precursor gas mixture after initiation of nanowire growth, wherein the second precursor gas mixture includes a precursor gas that decomposes to form a eutectic phase with the nucleating particles at a second temperature which is lower than the first temperature, and heating the nucleating particles to the second temperature.

**[0006]** The above method can be reversed such that the process of nanowire growth is initiated with a precursor gas at the lower temperature, and then

nanowire growth is continued at a higher temperature using a second precursor gas (e.g., a gas having a reactive etchant species to aid in nanowire orientation such as chlorine). The first precursor gas utilized is preferably SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub> which contains Si and Cl atoms upon disassociation at the first temperature. The Si atoms provide for nanowire growth and the Cl atoms allow for growth of the wires in a <111> orientation when grown on a crystallographic substrate as a result of etching of the native oxide layer on the silicon substrate. Once nanowire growth has been initiated, a second precursor gas mixture including a precursor gas such as SiH<sub>4</sub> or Si<sub>2</sub>H<sub>6</sub> can be introduced which decomposes to form a eutectic phase with the nucleating particles at a lower temperature than the first precursor gas. The disassociated Si atoms from SiH<sub>4</sub> or Si<sub>2</sub>H<sub>6</sub> at the second temperature continue the growth of the Si nanowires. Thus, nanowire growth can continue with the free Si atoms at a lower temperature than that at which nanowire growth is initiated, e.g., allowing growth of the oriented wires to a desired length while minimizing diffusion of the metal catalyst into the growing nanowires.

[0007] The substrate material utilized in these methods may be crystallographic or amorphous. Suitably, the substrate material comprises crystallographic silicon, either polycrystalline or single crystalline. In other embodiments, the substrate may be amorphous SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, or alumina

[0008] In embodiments where crystalline substrates are utilized, the wires growing on the substrate material can preferably grow in an epitaxial orientation. Nanowires produced according to the processes of the present invention grow out of the plane of the substrate material, and are capable of transporting electrical charge.

[0009] In certain suitable embodiments of the methods of the present invention, the first temperature to which the nucleating particles is heated is higher than the second temperature to which the alloy droplet is heated. Suitably, the first temperature is at least about 50°C higher than the second temperature. The nucleating particles used in the practice of the present invention will suitably be a metal catalyst and will comprise a metal that reacts

with both the first precursor gas mixture and the second precursor gas mixture (i.e., decomposed first and second precursor gas mixtures) to form a eutectic from which Si may precipitate. Suitable metal catalysts comprise Au, Al, Pt, Fe, Ti, Ga, Ni, Sn or In and in certain such embodiments, may be a Au or Al colloid or Au or Al film.

**[00010]** The first precursor gas mixture and the second precursor gas mixture utilized in the processes of the present invention will suitably comprise SiH<sub>4</sub>, Si<sub>2</sub>H<sub>6</sub>, SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>, and may further comprise B<sub>2</sub>H<sub>6</sub>, trimethyl boron (TMB) POCl<sub>3</sub> or PH<sub>3</sub> (e.g., as dopant materials). Additional embodiments of the processes of the present invention may further comprise contacting the growing nanowires with one or more additional precursor gas mixtures comprising SiH<sub>4</sub>, Si<sub>2</sub>H<sub>6</sub>, SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub> and further comprising B<sub>2</sub>H<sub>6</sub>, TMB, POCl<sub>3</sub> or PH<sub>3</sub> to grow the nanowires to a desired length. The precursor gases used in the processes of the present invention may also suitably be introduced via plasma enhanced sputter deposition.

**[00011]** In another embodiment of the present invention, the need for growing nanowires at different temperatures can be avoided by growing the nanowires at lower temperatures (e.g., lower than about 800°C) using Plasma Enhanced Sputter Deposition (or Plasma Enhanced Chemical Vapor Deposition (PECVD)). In this embodiment, the nucleating particles are contacted with a precursor gas mixture that preferably includes a precursor gas comprising a reactive species (e.g., Cl) that aids in orienting the growing nanowires, such as SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>. Alternatively, the precursor gas mixture may include chlorine gas (or plasma) from a separate, independent source that can be provided in combination with one or more of the precursor gases discussed above (e.g., SiH<sub>4</sub>, Si<sub>2</sub>H<sub>6</sub>, SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>). Where the precursor gas mixture includes SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>, decomposition of SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub> into Si and Cl in the presence of a carrier gas (e.g., H<sub>2</sub>, H<sub>2</sub>Ar) forms HCl. As discussed in more detail below, this creates a competition between etching with HCl and growth from the Si vapor. Chlorine aids in removal of interfacial oxide on Si substrates leading to the oriented nanowire growth. The addition of an

independent source of chlorine gas has the advantage of allowing the reactive species of Si and Cl to be independently controlled in the plasma to enhance or suppress etching as needed to promote nanowire growth. Sputter deposition can be accomplished via any method known to the ordinarily skilled artisan, for example, diode, radio frequency and direct current deposition.

[00012] The present invention also provides methods for producing nanowires which do not involve metal catalysts, including, for example, hydroxylating a substrate material, contacting the substrate material with a first precursor gas mixture, forming one or more nuclei (e.g., nanoparticles) on a surface of the substrate material, contacting the nuclei with a second precursor gas mixture, and growing nanowires at the site of the one or more nuclei.

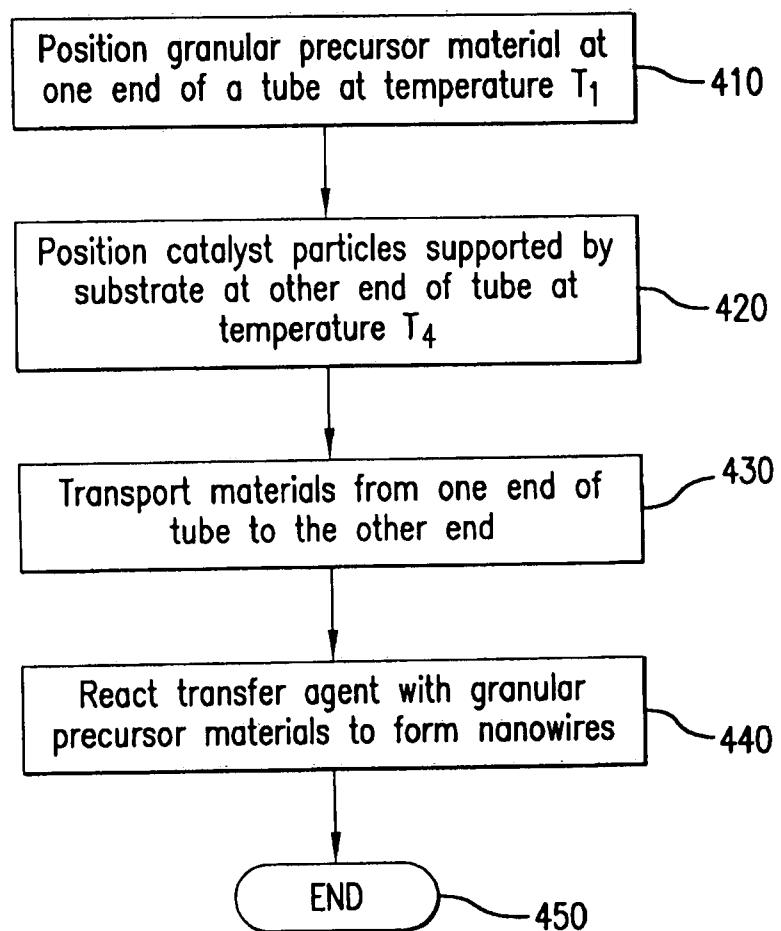

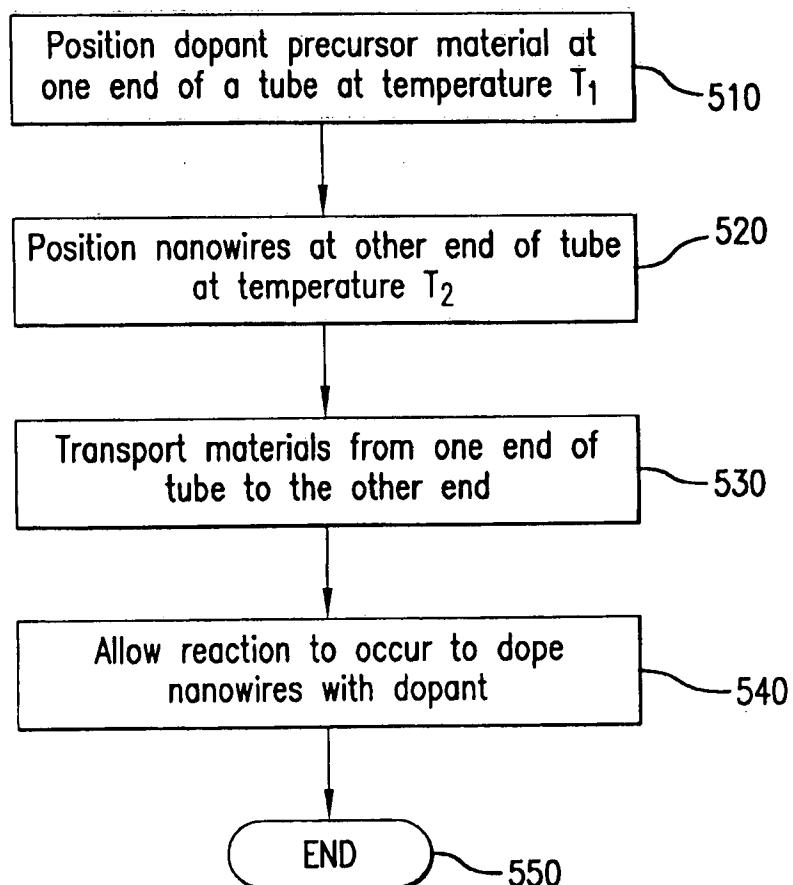

[00013] In another aspect of the invention, additional methods for nanowire synthesis are provided. In an embodiment, a method for nanowire synthesis includes positioning a granular precursor material at one end of a vessel at one temperature and positioning catalyst particles at an opposite end of the vessel at another temperature. Materials are then transferred from one end of the vessel to another. A transport agent is reacted with the granular nanowire precursor material to form nanowires. In an alternative embodiment, a similar method is provided to dope nanowires.

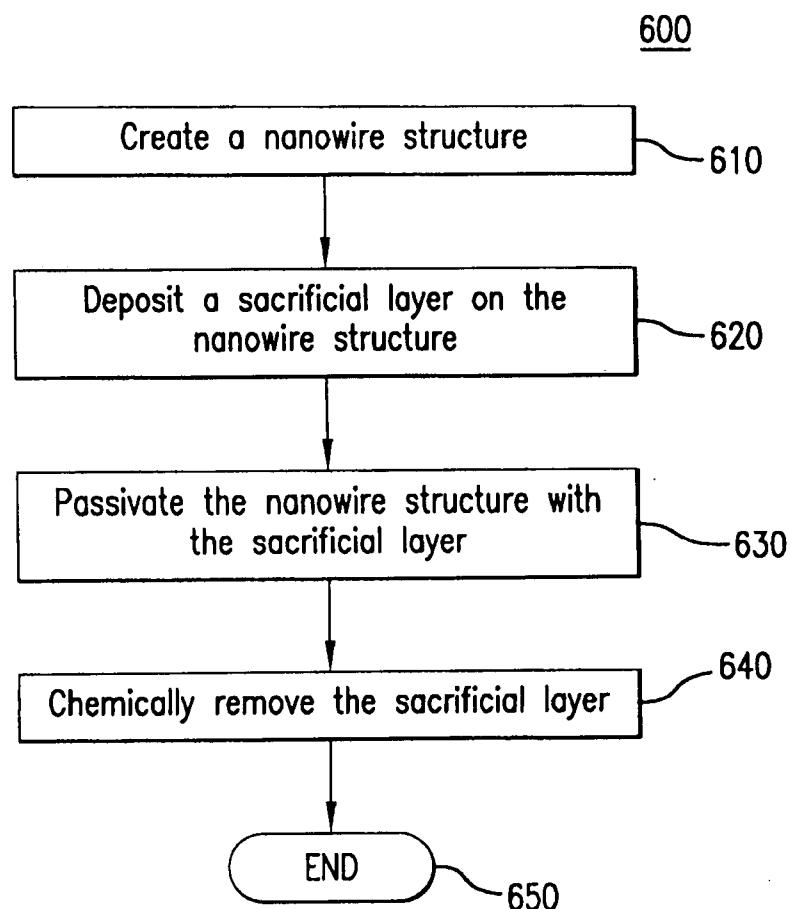

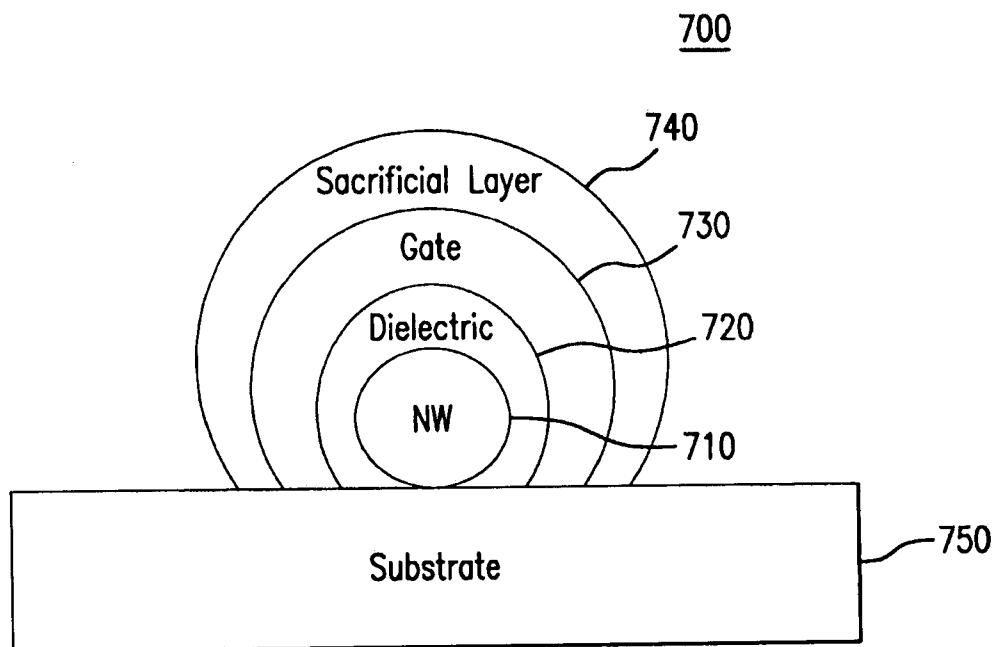

[00014] In a further aspect of the invention, methods to improve nanowire quality during manufacturing are provided. In particular, a method to reduce surface states from dangling bonds on a nanowire structure is provided. In an embodiment, the method includes creating a nanowire structure, depositing a sacrificial layer on the nanowire structure, passivating the nanowire structure with the sacrificial layer, and chemically removing the sacrificial layer to free the nanowires.

[00015] In another embodiment, a method for producing a nanowire device is disclosed that includes providing a substrate having nanowires attached to a surface in a vertical orientation, depositing a dielectric layer on the surface of the nanowires, depositing one or more nanowire contacts on the nanowires,

depositing a material over the nanowires to form a nanowire composite, and separating the nanowire composite from the substrate.

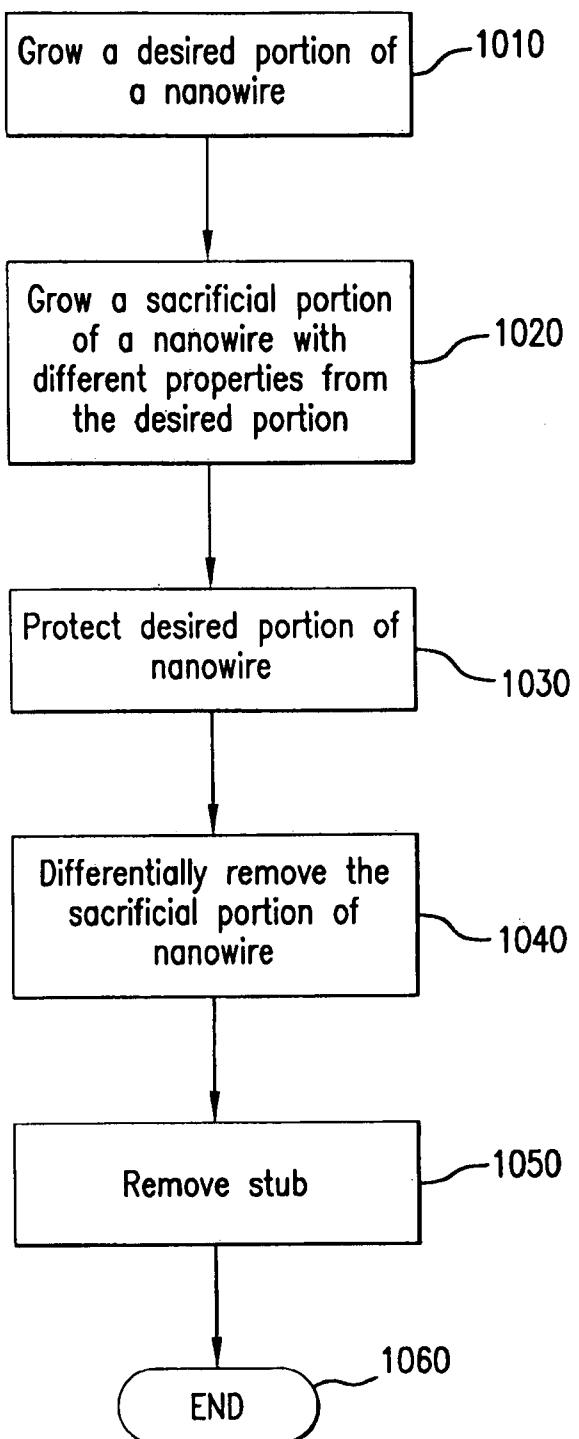

**[00016]** A series of methods are also provided for harvesting nanowires. In an embodiment, a method includes growing a nanowire with a desired portion and a sacrificial portion. The desired portion has different properties than those of the sacrificial portion. In one example, the sacrificial portion is an alloy and the desired portion is not. In another example, the sacrificial portion is doped differently than the desired portion. Wet etchants are used to differentially remove the sacrificial portion of the nanowires. The example wet etchants etch away the sacrificial portion of the nanowire at a far greater rate than the desired portion. As a result, nanowires can be produced with consistent lengths.

**[00017]** In another embodiment, silicon nanowires are grown on a silicon substrate in which the orientation of the silicon in the nanowires is different from the orientation of the silicon in the substrate. For example, the atoms in the silicon nanowires can have Miller indices of 111, while the silicon atoms in the substrate can have Miller indices of 100. As in the previous case, wet etchants can be used to differentially remove portions of the silicon substrate to free the nanowires.

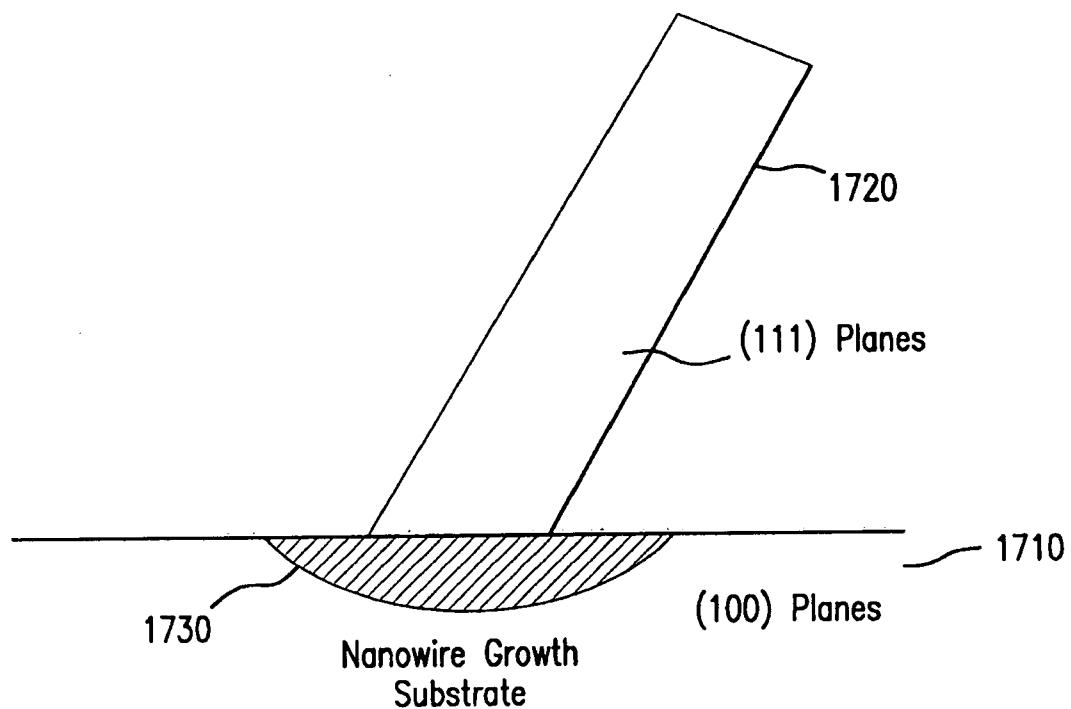

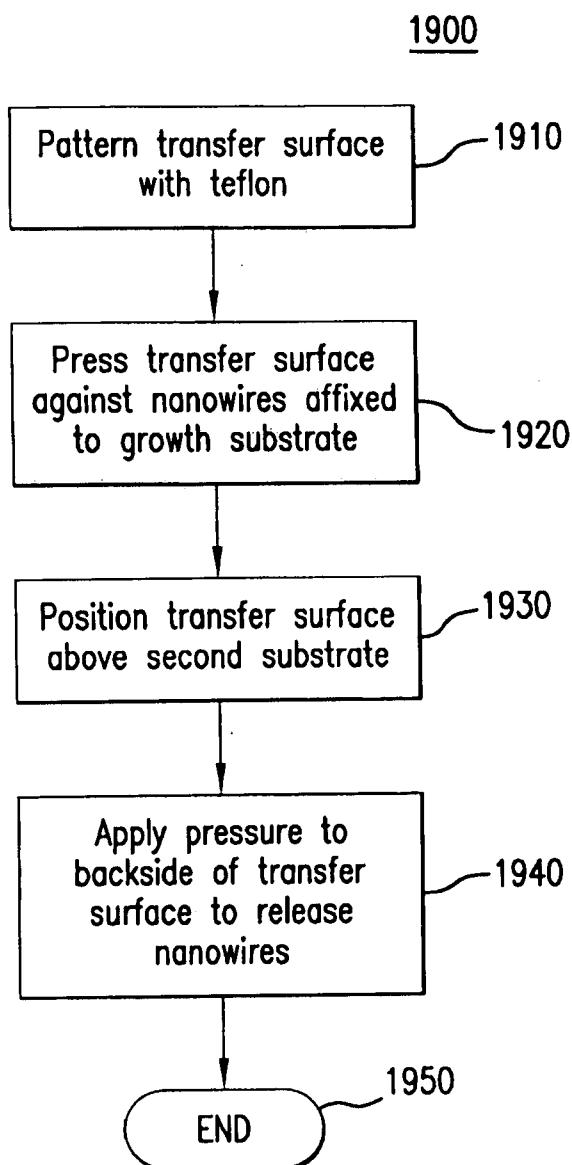

**[00018]** In another aspect of the invention, methods for transferring nanowires from one substrate to another substrate are provided. The methods can be used, for example, to transfer nanowires from a nanowire growth substrate to a device substrate. In an embodiment, the method includes coating a transfer surface with a non-stick coating, such as TEFLON. The transfer surface can then be pressed against nanowires that are affixed to a nanowire growth substrate. The nanowires become stuck to the transfer surface with the non-stick coating. The transfer surface is then positioned over a device substrate, and pressure is applied to the back of the transfer surface to release the nanowires onto the device substrate. In alternative embodiments, the transfer surface can be patterned with a non-stick coating to match areas on a device substrate where nanowires are to be placed. In a similar alternative

embodiment, the non-stick coating can be distributed all over the transfer surface, and pressure can be placed on the backside of the transfer surface in a patterned fashion to release nanowires onto particular areas of a device substrate.

**[00019]** In an additional embodiment, methods for harvesting and transferring nanowires are disclosed that include providing a substrate material having one or more nanowires attached to a top surface, providing a transfer substrate oriented above the top surface of the substrate, applying pressure to the transfer substrate, such that the transfer substrate is brought in contact with the one or more nanowires, transferring one or more of the nanowires from the substrate to the transfer substrate, and removing the transfer substrate. In this embodiment, the transfer substrate can be a flexible polymer and a probe can be used to apply pressure. In embodiments the probe may be heated or the substrate may be heated.

**[00020]** In a further embodiment, the present invention provides methods for producing nanowires, comprising: layering a catalyst-repelling material on a substrate material to at least partially cover the substrate material; depositing one or more nucleating particles on the substrate material; heating the nucleating particles to a first temperature; contacting the nucleating particles with a first precursor gas mixture to create a liquid alloy droplet to initiate nanowire growth; heating the alloy droplet to a second temperature; and contacting the alloy droplet with a second precursor gas mixture, whereby nanowires are grown at the site of the alloy droplet. Suitably, the substrate material will comprise a crystallographic material, such as Si, and the nucleating particles will comprise metallic films or colloids, such as films or colloids comprising Au, Al, Pt, Fe, Ti, Ga, Ni, Sn or In. Examples of catalyst-repelling material include, but are not limited to, SiO<sub>2</sub>, and anodic alumina. As noted throughout, the temperature and precursor gases can be varied throughout the growth process, suitably starting at a higher temperature initially, and then using a lower temperature for continued nanowire growth. Examples of precursor gas mixtures for use in the methods of the present

invention include, but are not limited to, SiH<sub>4</sub>, SiCl<sub>4</sub> and SiH<sub>2</sub>Cl<sub>2</sub>. The present invention also provides nanowires produced by the methods of the present invention and electronic devices comprising such nanowires.

[00021] Further embodiments, features, and advantages of the invention, as well as the structure and operation of the various embodiments of the invention are described in detail below with reference to accompanying drawings.

#### BRIEF DESCRIPTION OF THE FIGURES

[00022] The invention is described with reference to the accompanying drawings. In the drawings, like reference numbers indicate identical or functionally similar elements. The drawing in which an element first appears is indicated by the left-most digit in the corresponding reference number.

[00023] FIG. 1A is a diagram of a single crystal semiconductor nanowire.

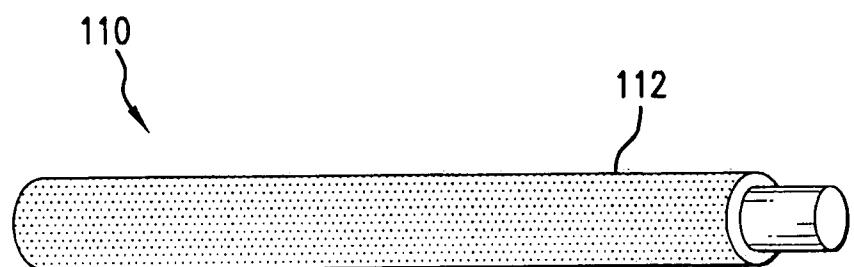

[00024] FIG. 1B is a diagram of a nanowire doped according to a core-shell structure.

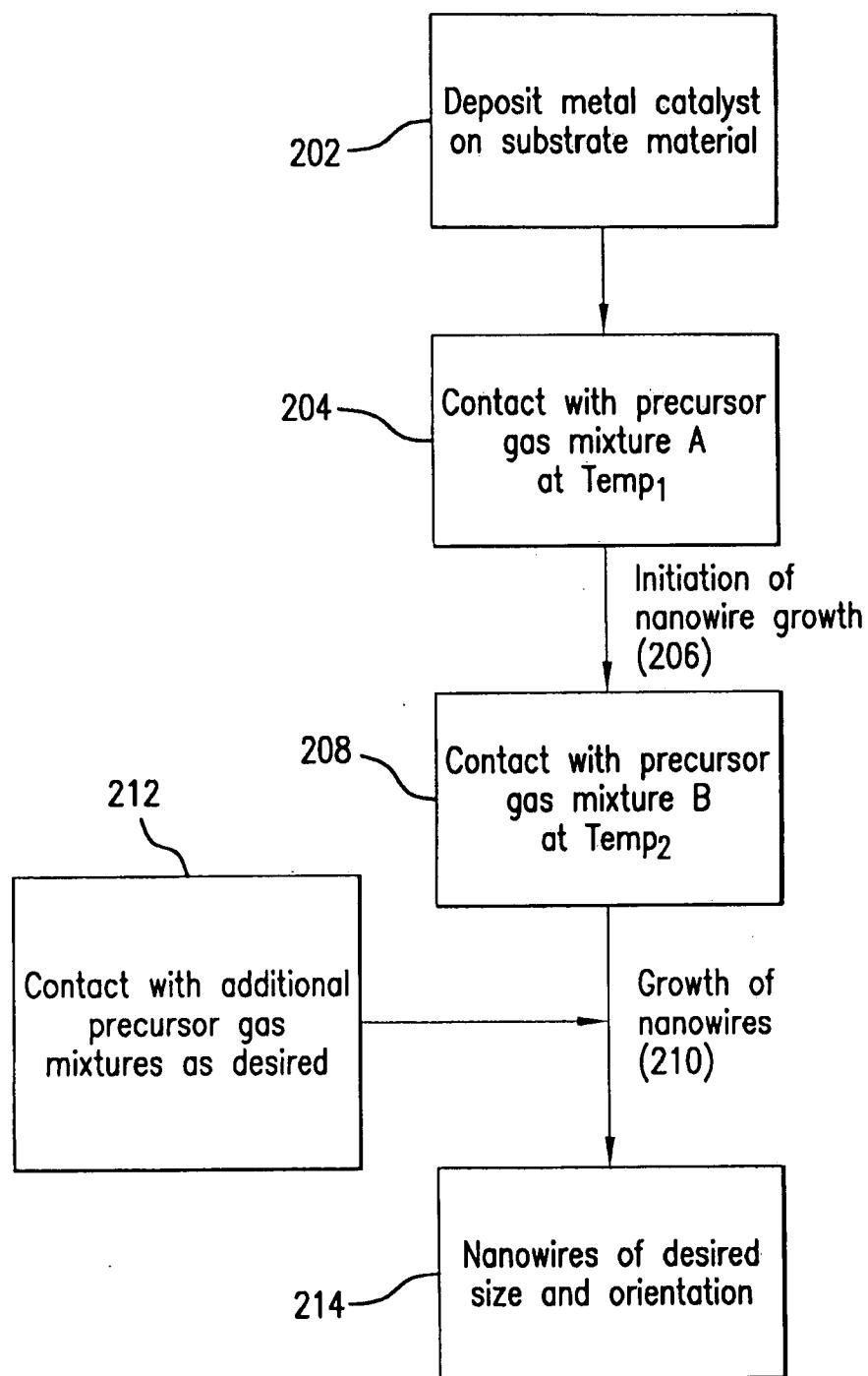

[00025] FIG. 2 is a flowchart of a method for preparing nanowires using a combination of Si precursors, according to an embodiment of the invention.

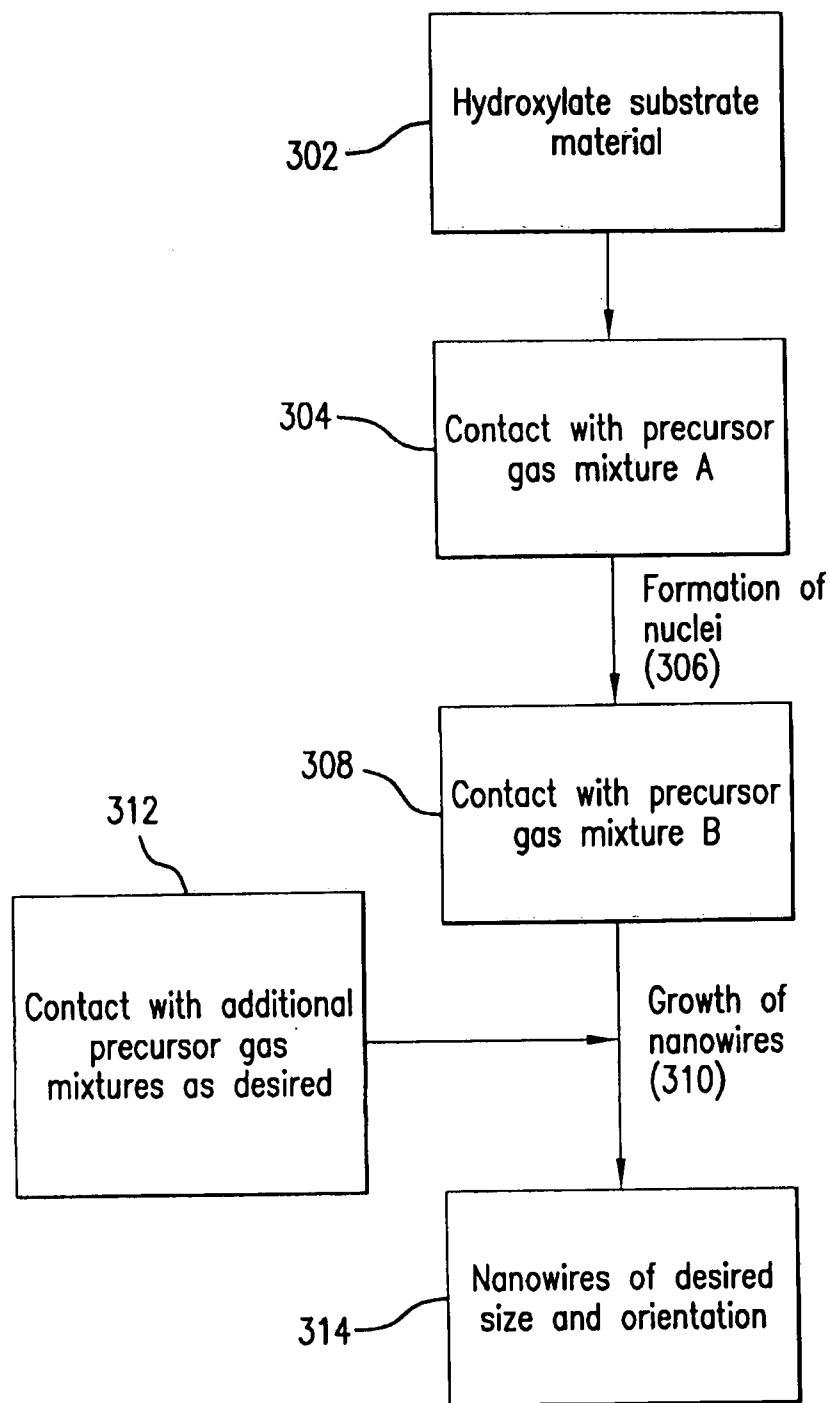

[00026] FIG. 3 is a flowchart of a method for preparing nanowires using a combination of Si precursors, according to an embodiment of the invention.

[00027] FIG. 4 is a flowchart of a method for nanowire synthesis, according to an embodiment of the invention.

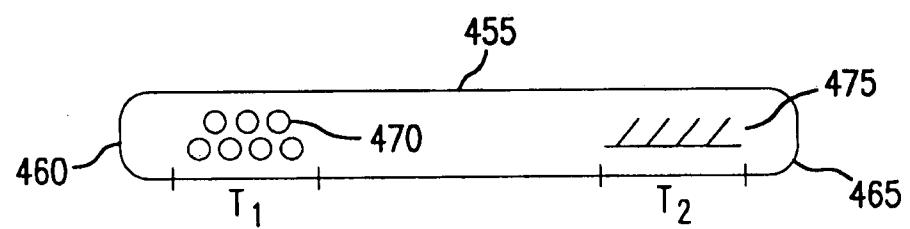

[00028] FIG. 4A is a diagram of a nanowire synthesis vessel, according to an embodiment of the invention.

[00029] FIG. 5 is a flowchart of a method for doping nanowires, according to an embodiment of the invention.

[00030] FIG. 6 is a flowchart of a method for reducing surface states from dangling bonds on a nanowire structure, according to an embodiment of the invention.

[00031] FIG. 7 is a diagram of a nanowire coated with a sacrificial layer, according to an embodiment of the invention.

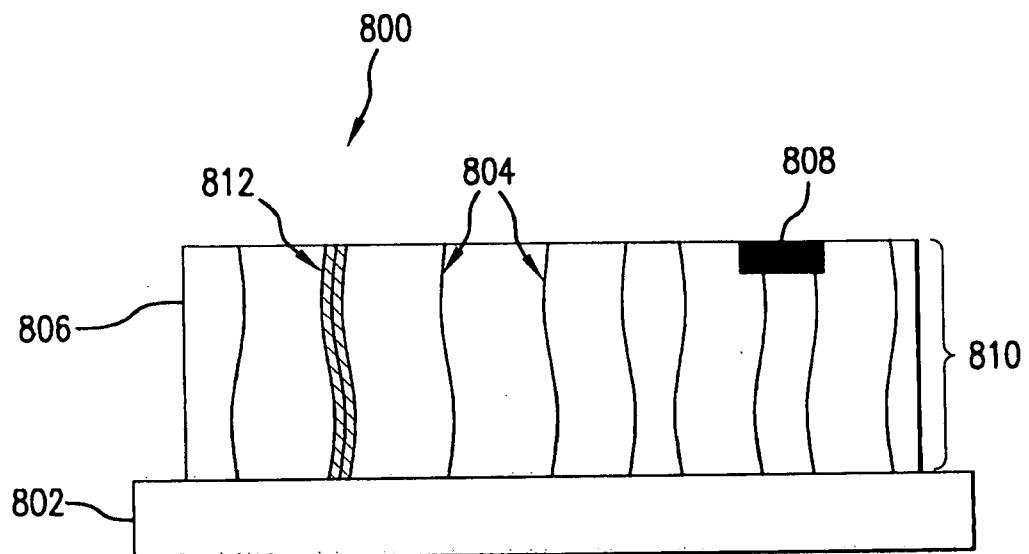

[00032] FIG. 8 is a diagram showing nanowire processing in accordance with one embodiment of the present invention.

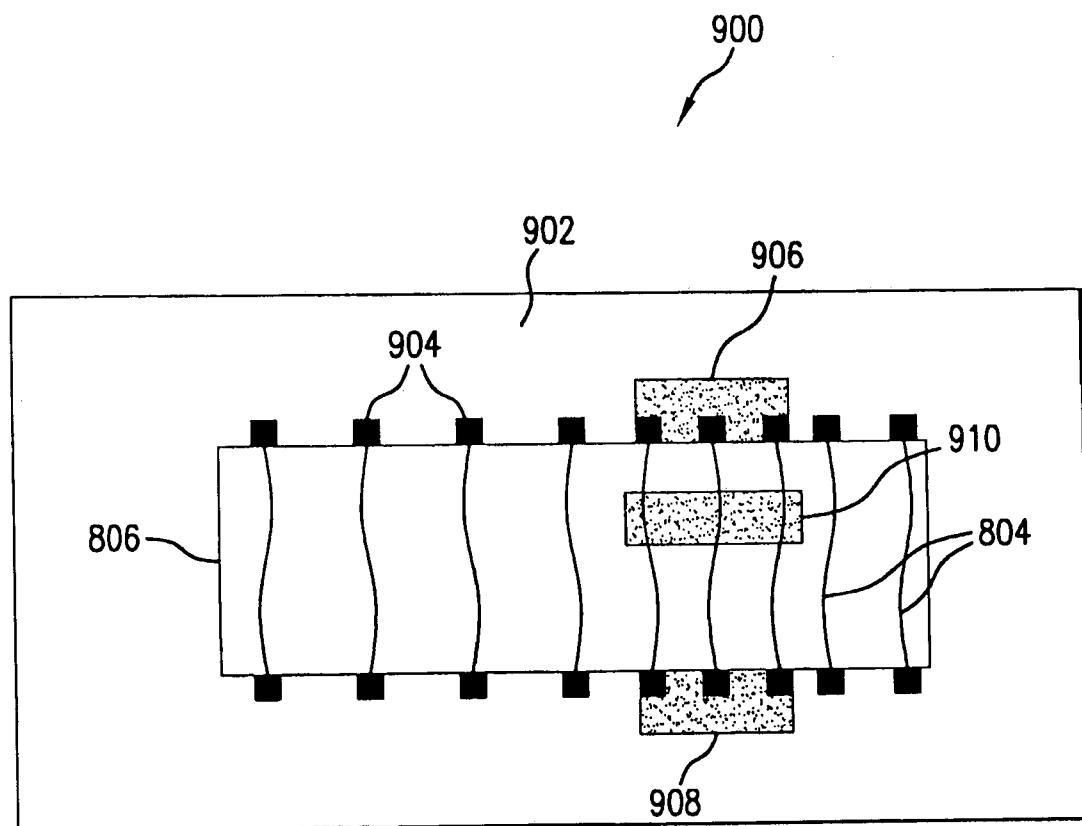

[00033] FIG. 9 is a diagram showing nanowire processing following transfer in accordance with one embodiment of the present invention.

[00034] FIG. 10 is a flowchart of a method of harvesting a nanowire using a sacrificial portion, according to an embodiment of the invention.

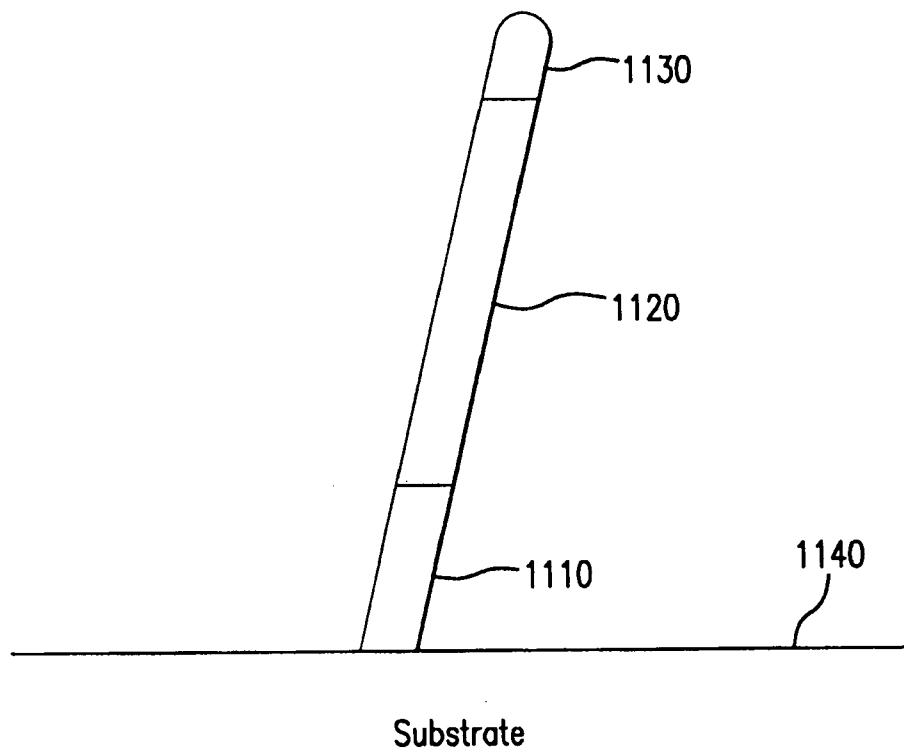

[00035] FIG. 11 is a diagram of a nanowire with a sacrificial portion, according to an embodiment of the invention.

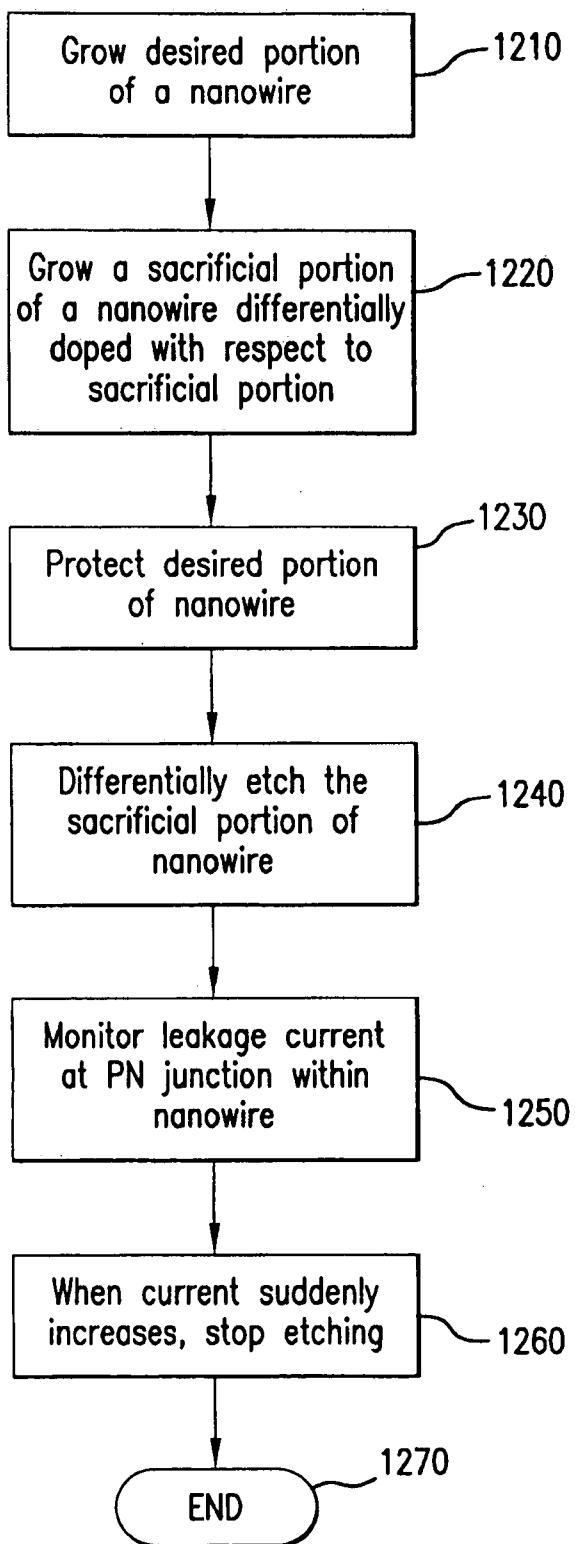

[00036] FIG. 12 is a flowchart of a method of harvesting a nanowire by monitoring of a PN junction, according to an embodiment of the invention.

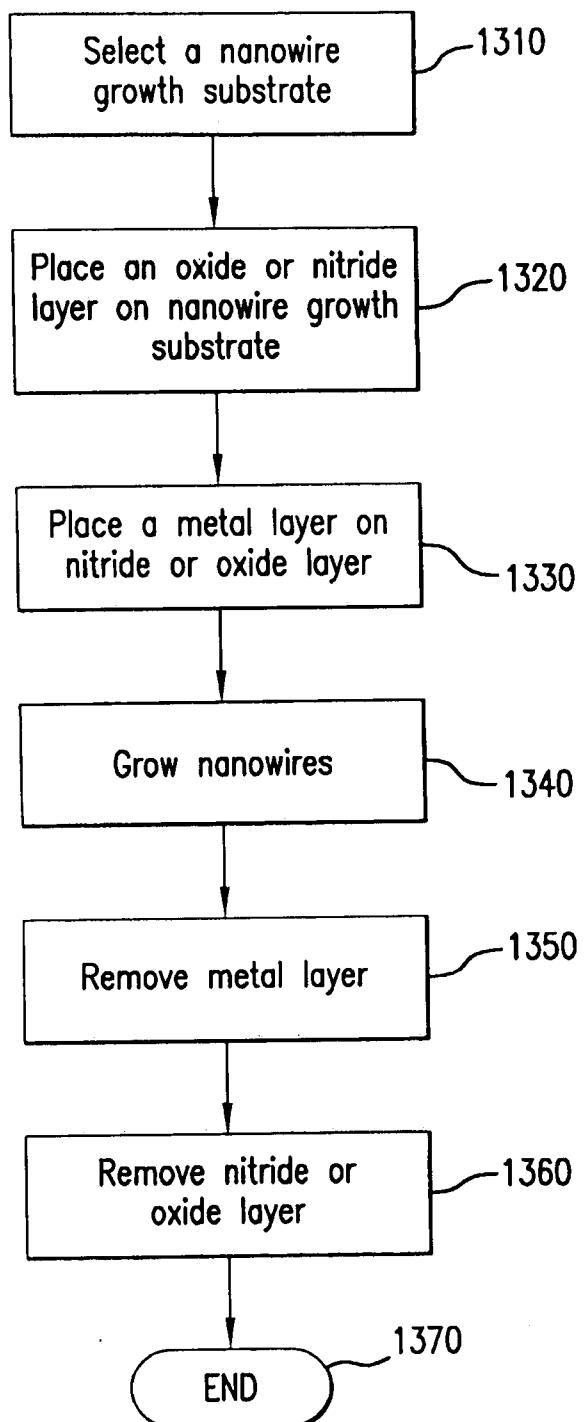

[00037] FIG. 13 is a flowchart of a method of harvesting a nanowire using a sacrificial metal layer on a nanowire growth substrate, according to an embodiment of the invention.

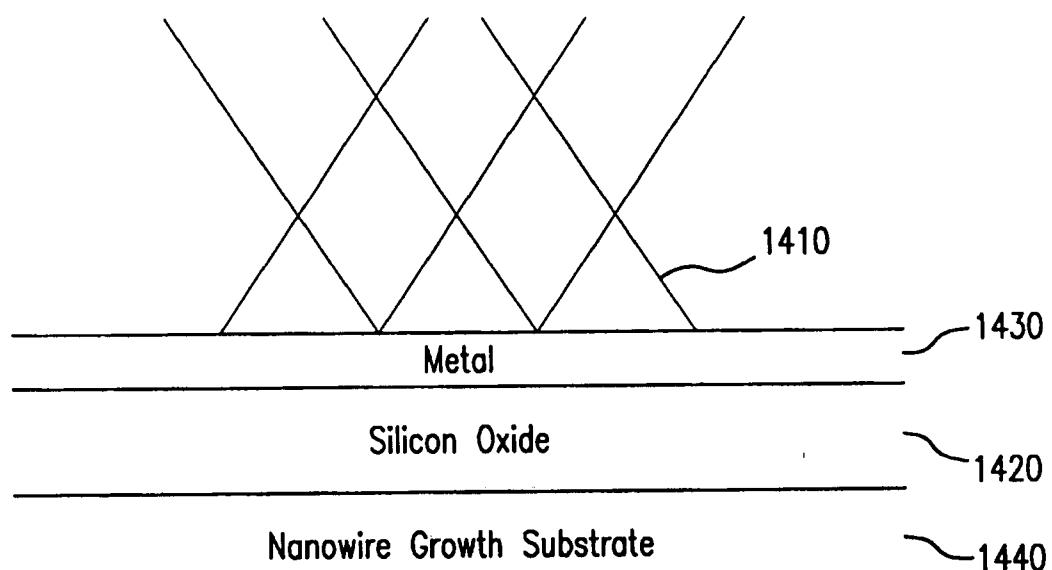

[00038] FIG. 14 is a diagram of a nanowire grown on a sacrificial metal layer on a nanowire growth substrate, according to an embodiment of the invention.

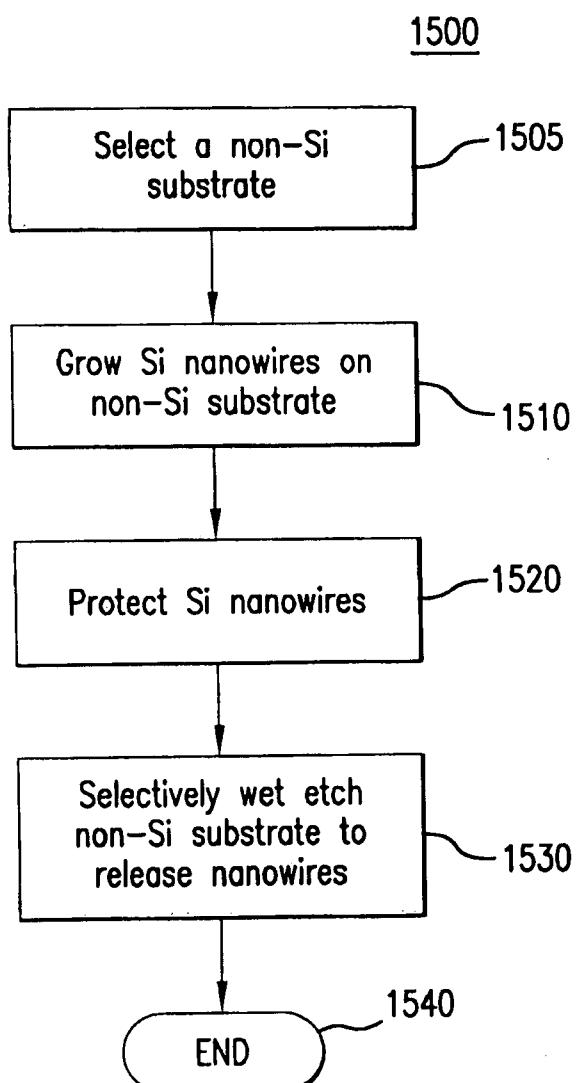

[00039] FIG. 15 is a flowchart of a method of harvesting an Si nanowire when using a non-Si substrate, according to an embodiment of the invention.

[00040] FIG. 16 is a flowchart of a method of harvesting a nanowire with one orientation when a nanowire growth substrate with a different orientation is used, according to an embodiment of the invention.

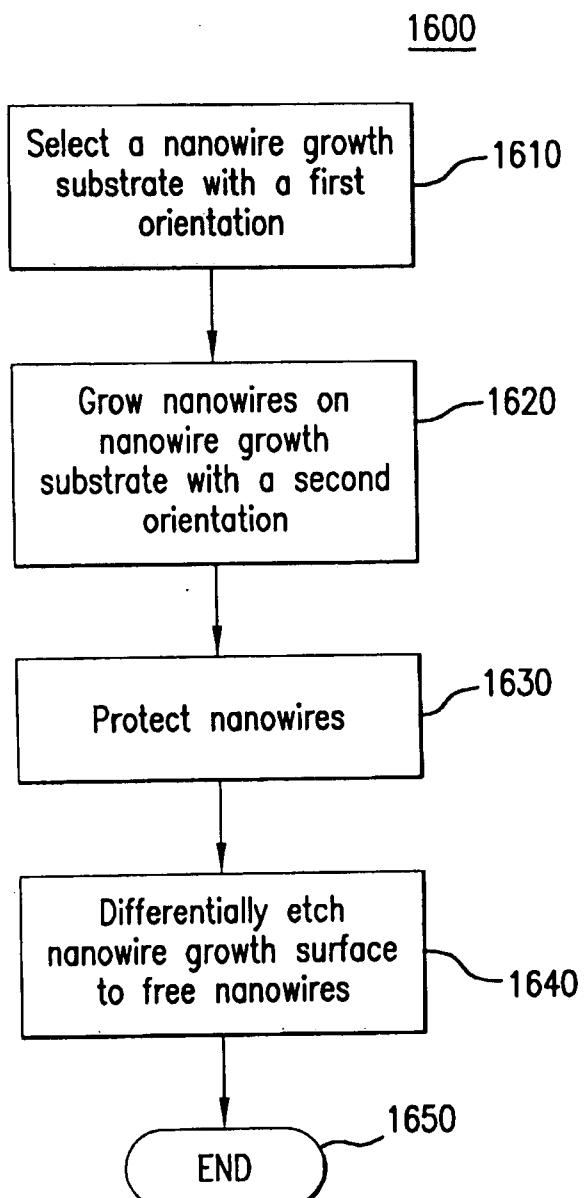

[00041] FIG. 17 is a diagram of a nanowire with one orientation growing on a nanowire growth substrate with a different orientation, according to an embodiment of the invention.

[00042] FIG. 18 is a flowchart of a method for transferring nanowires from a first substrate to a second substrate, according to an embodiment of the invention.

[00043] FIG. 19 is a flowchart of a method for transferring nanowires from a first substrate with a patterned coating to a second substrate, according to an embodiment of the invention.

- 10 -

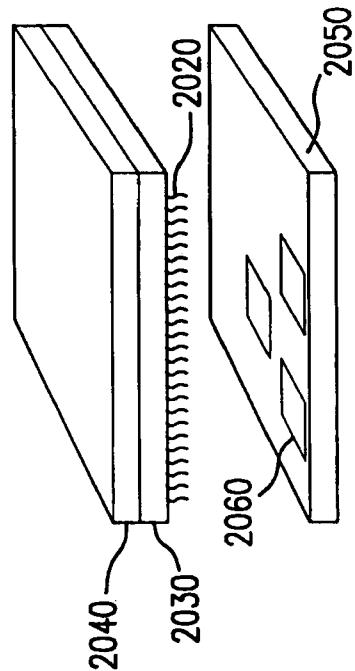

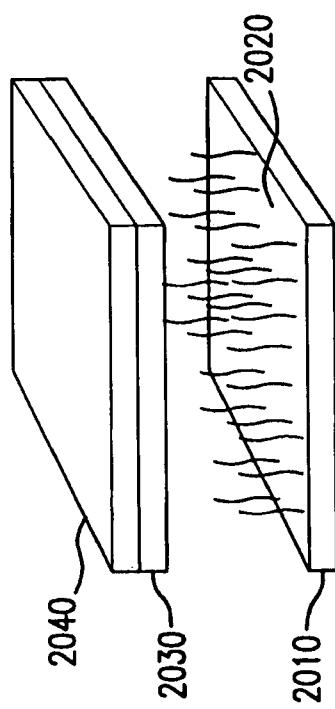

[00044] FIG. 20A is a diagram of a first substrate with nanowires and a transfer substrate, according to an embodiment of the invention.

[00045] FIG. 20B is a diagram of a device substrate and a transfer substrate transferring nanowires, according to an embodiment of the invention.

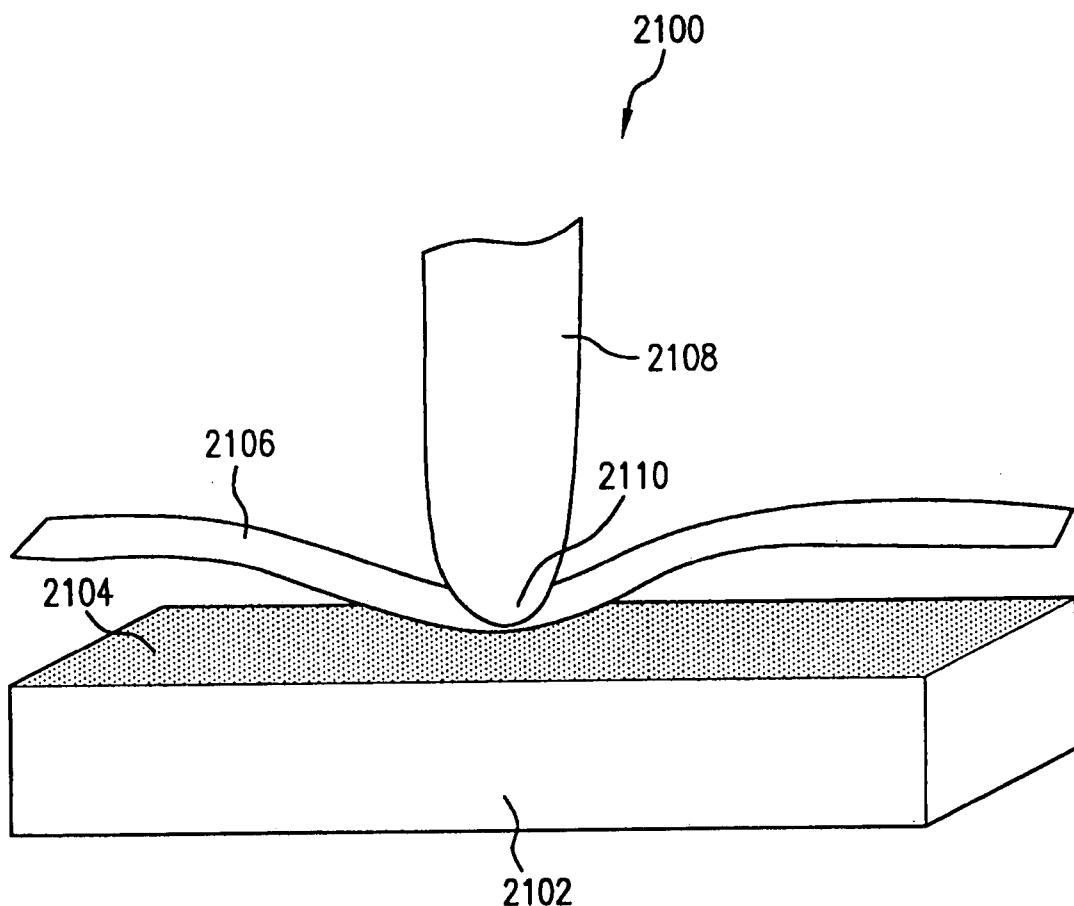

[00046] FIG. 21 is a representation of probe nanowire transfer scheme in accordance with one embodiment of the present invention.

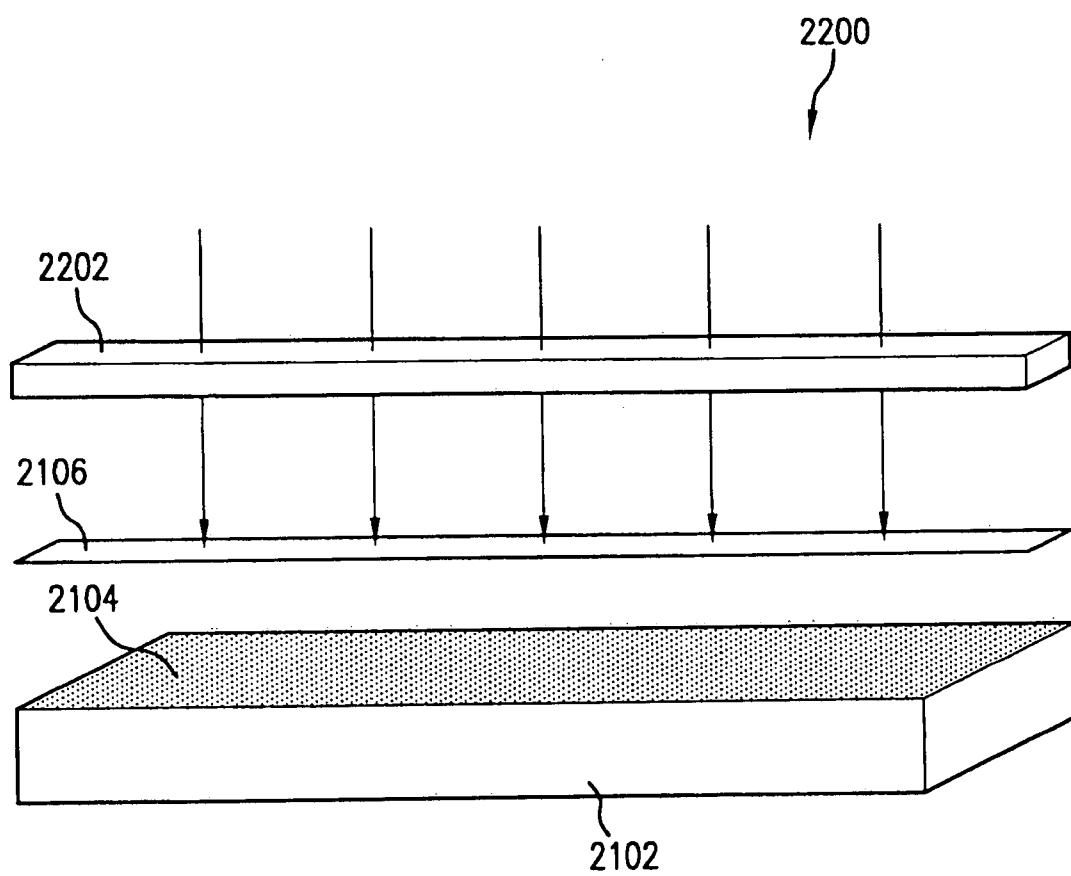

[00047] FIG. 22 is a representation of global nanowire transfer in accordance with one embodiment of the present invention.

[00048] FIGs. 23A is a transmission electron micrograph that shows a substrate with e-field oriented nanowires prior to transfer, according to an embodiment of the invention.

[00049] FIG. 23B is a transmission electron micrograph that shows nanowires remaining on substrate following transfer, according to an embodiment of the invention.

[00050] FIG. 23C is a transmission electron micrograph that shows nanowires on transfer substrate following transfer, according to an embodiment of the invention.

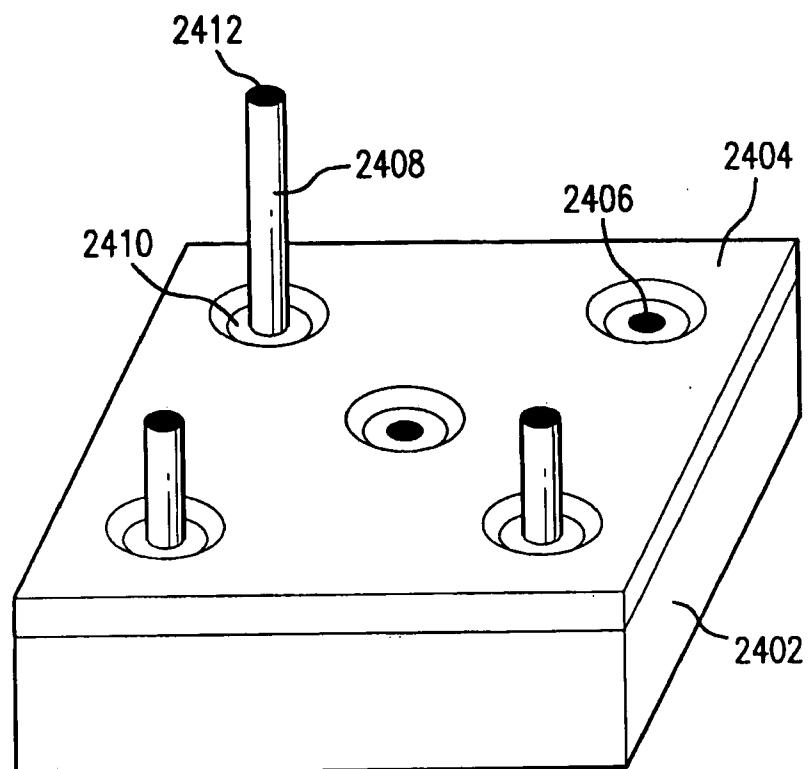

[00051] FIG. 24 is a diagram showing oriented nanowire growth using a patterned substrate in accordance with one embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

[00052] It should be appreciated that the particular implementations shown and described herein are examples of the invention and are not intended to otherwise limit the scope of the present invention in any way. Indeed, for the sake of brevity, conventional electronics, manufacturing, semiconductor devices, and nanowire (NW), nanorod, nanotube, and nanoribbon technologies and other functional aspects of the systems (and components of the individual operating components of the systems) may not be described in detail herein.

Furthermore, for purposes of brevity, the invention is frequently described herein as pertaining to nanowires.

[00053] It should be appreciated that although nanowires are frequently referred to, the techniques described herein are also applicable to other nanostructures, such as nanorods, nanotubes, nanotetrapods, nanoribbons and/or combinations thereof. It should further be appreciated that the manufacturing techniques described herein could be used to create any semiconductor device type, and other electronic component types. Further, the techniques would be suitable for application in electrical systems, optical systems, consumer electronics, industrial electronics, wireless systems, space applications, or any other application.

[00054] As used herein, an "aspect ratio" is the length of a first axis of a nanostructure divided by the average of the lengths of the second and third axes of the nanostructure, where the second and third axes are the two axes whose lengths are most nearly equal to each other. For example, the aspect ratio for a perfect rod would be the length of its long axis divided by the diameter of a cross-section perpendicular to (normal to) the long axis.

[00055] The term "heterostructure" when used with reference to nanostructures refers to nanostructures characterized by at least two different and/or distinguishable material types. Typically, one region of the nanostructure comprises a first material type, while a second region of the nanostructure comprises a second material type. In certain embodiments, the nanostructure comprises a core of a first material and at least one shell of a second (or third etc.) material, where the different material types are distributed radially about the long axis of a nanowire, a long axis of an arm of a branched nanocrystal, or the center of a nanocrystal, for example. A shell need not completely cover the adjacent materials to be considered a shell or for the nanostructure to be considered a heterostructure. For example, a nanocrystal characterized by a core of one material covered with small islands of a second material is a heterostructure. In other embodiments, the different material types are distributed at different locations within the nanostructure. For example,

material types can be distributed along the major (long) axis of a nanowire or along a long axis of arm of a branched nanocrystal. Different regions within a heterostructure can comprise entirely different materials, or the different regions can comprise a base material.

[00056] As used herein, a "nanostructure" is a structure having at least one region or characteristic dimension with a dimension of less than about 500 nm, e.g., less than about 200 nm, less than about 100 nm, less than about 50 nm, or even less than about 20 nm. Typically, the region or characteristic dimension will be along the smallest axis of the structure. Examples of such structures include nanowires, nanorods, nanotubes, branched nanocrystals, nanotetrapods, tripods, bipods, nanocrystals, nanodots, quantum dots, nanoparticles, branched tetrapods (e.g., inorganic dendrimers), and the like. Nanostructures can be substantially homogeneous in material properties, or in certain embodiments can be heterogeneous (e.g., heterostructures). Nanostructures can be, for example, substantially crystalline, substantially monocrystalline, polycrystalline, amorphous, or a combination thereof. In one aspect, each of the three dimensions of the nanostructure has a dimension of less than about 500 nm, for example, less than about 200 nm, less than about 100 nm, less than about 50 nm, or even less than about 20 nm.

[00057] As used herein, the term "nanowire" generally refers to any elongated conductive or semiconductive material (or other material described herein) that includes at least one cross sectional dimension that is less than 500 nm, and preferably, less than 100 nm, and has an aspect ratio (length:width) of greater than 10, preferably greater than 50, and more preferably, greater than 100.

[00058] The nanowires of this invention can be substantially homogeneous in material properties, or in certain embodiments can be heterogeneous (e.g. nanowire heterostructures). The nanowires can be fabricated from essentially any convenient material or materials, and can be, e.g., substantially crystalline, substantially monocrystalline, polycrystalline, or amorphous. Nanowires can have a variable diameter or can have a substantially uniform diameter, that is,

a diameter that shows a variance less than about 20% (e.g., less than about 10%, less than about 5%, or less than about 1%) over the region of greatest variability and over a linear dimension of at least 5 nm (e.g., at least 10 nm, at least 20 nm, or at least 50 nm). Typically the diameter is evaluated away from the ends of the nanowire (e.g. over the central 20%, 40%, 50%, or 80% of the nanowire). A nanowire can be straight or can be e.g. curved or bent, over the entire length of its long axis or a portion thereof. In certain embodiments, a nanowire or a portion thereof can exhibit two- or three-dimensional quantum confinement. Nanowires according to this invention can expressly exclude carbon nanotubes, and, in certain embodiments, exclude "whiskers" or "nanowhiskers", particularly whiskers having a diameter greater than 100 nm, or greater than about 200 nm.

**[00059]** Examples of such nanowires include semiconductor nanowires as described in Published International Patent Application Nos. WO 02/17362, WO 02/48701, and WO 01/03208, carbon nanotubes, and other elongated conductive or semiconductive structures of like dimensions, which are incorporated herein by reference.

**[00060]** As used herein, the term "nanorod" generally refers to any elongated conductive or semiconductive material (or other material described herein) similar to a nanowire, but having an aspect ratio (length:width) less than that of a nanowire. Note that two or more nanorods can be coupled together along their longitudinal axis so that the coupled nanorods span all the way between electrodes. Alternatively, two or more nanorods can be substantially aligned along their longitudinal axis, but not coupled together, such that a small gap exists between the ends of the two or more nanorods. In this case, electrons can flow from one nanorod to another by hopping from one nanorod to another to traverse the small gap. The two or more nanorods can be substantially aligned, such that they form a path by which electrons can travel between electrodes.

**[00061]** A wide range of types of materials for nanowires, nanorods, nanotubes and nanoribbons can be used, including semiconductor material selected from,

e.g., Si, Ge, Sn, Se, Te, B, C (including diamond), P, B-C, B-P(BP<sub>6</sub>), B-Si, Si-C, Si-Ge, Si-Sn and Ge-Sn, SiC, BN/BP/BAs, AlN, AlP, AlAs, AlSb, GaN, GaP, GaAs, GaSb, InN, InP, InAs, InSb, ZnO, ZnS, ZnSe, ZnTe, CdS, CdSe, CdTe, HgS, HgSe, HgTe, BeS, BeSe, BeTe, MgS, MgSe, GeS, GeSe, GeTe, SnS, SnSe, SnTe, PbO, PbS, PbSe, PbTe, CuF, CuCl, CuBr, CuI, AgF, AgCl, AgBr, AgI, BeSiN<sub>2</sub>, CaCN<sub>2</sub>, ZnGeP<sub>2</sub>, CdSnAs<sub>2</sub>, ZnSnSb<sub>2</sub>, CuGeP<sub>3</sub>, CuSi<sub>2</sub>P<sub>3</sub>, (Cu, Ag)(Al, Ga, In, Tl, Fe)(S, Se, Te)<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Ge<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, (Al, Ga, In)<sub>2</sub>(S, Se, Te)<sub>3</sub>, Al<sub>2</sub>CO, and an appropriate combination of two or more such semiconductors.

[00062] The nanowires can also be formed from other materials such as metals such as gold, nickel, palladium, iridium, cobalt, chromium, aluminum, titanium, tin and the like, metal alloys, polymers, conductive polymers, ceramics, and/or combinations thereof. Other now known or later developed conducting or semiconductor materials can be employed.

[00063] In certain aspects, the semiconductor may comprise a dopant from a group consisting of: a p-type dopant from Group III of the periodic table; an n-type dopant from Group V of the periodic table; a p-type dopant selected from a group consisting of: B, Al and In; an n-type dopant selected from a group consisting of: P, As and Sb; a p-type dopant from Group II of the periodic table; a p-type dopant selected from a group consisting of: Mg, Zn, Cd and Hg; a p-type dopant from Group IV of the periodic table; a p-type dopant selected from a group consisting of: C and Si.; or an n-type dopant selected from a group consisting of: Si, Ge, Sn, S, Se and Te. Other now known or later developed dopant materials can be employed.

[00064] Additionally, the nanowires or nanoribbons can include carbon nanotubes, or nanotubes formed of conductive or semiconductive organic polymer materials, (e.g., pentacene, and transition metal oxides).

[00065] Hence, although the term "nanowire" is referred to throughout the description herein for illustrative purposes, it is intended that the description herein also encompass the use of nanotubes (e.g., nanowire-like structures having a hollow tube formed axially therethrough). Nanotubes can be formed

in combinations/thin films of nanotubes as is described herein for nanowires, alone or in combination with nanowires, to provide the properties and advantages described herein.

**[00066]** It should be understood that the spatial descriptions (e.g., "above", "below", "up", "down", "top", "bottom," etc.) made herein are for purposes of illustration only, and that devices of the present invention can be spatially arranged in any orientation or manner. In addition, there may also be intervening layers for materials present in such devices to facilitate processing.

*Types of Nanowires and Their Synthesis*

**[00067]** FIG. 1A illustrates a single crystal semiconductor nanowire core (hereafter "nanowire") 100. FIG. 1A shows a nanowire 100 that is a uniformly doped single crystal nanowire. Such single crystal nanowires can be doped into either p- or n-type semiconductors in a fairly controlled way. Doped nanowires such as nanowire 100 exhibit improved electronic properties. For instance, such nanowires can be doped to have carrier mobility levels comparable to bulk single crystal materials.

**[00068]** FIG. 1B shows a nanowire 110 doped according to a core-shell structure. As shown in FIG. 1B, nanowire 110 has a doped surface layer 112, which can have varying thickness levels, including being only a molecular monolayer on the surface of nanowire 110.

**[00069]** The valence band of the insulating shell can be lower than the valence band of the core for p-type doped wires, or the conduction band of the shell can be higher than the core for n-type doped wires. Generally, the core nanostructure can be made from any metallic or semiconductor material, and the shell can be made from the same or a different material. For example, the first core material can comprise a first semiconductor selected from the group consisting of: a Group II-VI semiconductor, a Group III-V semiconductor, a Group IV semiconductor, and an alloy thereof. Similarly, the second material of the shell can comprise a second semiconductor, the same as or different

- 16 -

from the first semiconductor, e.g., selected from the group consisting of: a Group II-VI semiconductor, a Group III-V semiconductor, a Group IV semiconductor, and an alloy thereof. Example semiconductors include, but are not limited to, CdSe, CdTe, InP, InAs, CdS, ZnS, ZnSe, ZnTe, HgTe, GaN, GaP, GaAs, GaSb, InSb, Si, Ge, AlAs, AlSb, PbSe, PbS, and PbTe. As noted above, metallic materials such as gold, chromium, tin, nickel, aluminum etc. and alloys thereof can be used as the core material, and the metallic core can be overcoated with an appropriate shell material such as silicon dioxide or other insulating materials

**[00070]** Nanostructures can be fabricated and their size can be controlled by any of a number of convenient methods that can be adapted to different materials. For example, synthesis of nanocrystals of various composition is described in, e.g., Peng et al. (2000) "Shape Control of CdSe Nanocrystals" Nature 404, 59-61; Puntes et al. (2001) "Colloidal nanocrystal shape and size control: The case of cobalt" Science 291, 2115-2117; USPN 6,306,736 to Alivisatos et al. (October 23, 2001) entitled "Process for forming shaped group III-V semiconductor nanocrystals, and product formed using process"; USPN 6,225,198 to Alivisatos et al. (May 1, 2001) entitled "Process for forming shaped group II-VI semiconductor nanocrystals, and product formed using process"; USPN 5,505,928 to Alivisatos et al. (April 9, 1996) entitled "Preparation of III-V semiconductor nanocrystals"; USPN 5,751,018 to Alivisatos et al. (May 12, 1998) entitled "Semiconductor nanocrystals covalently bound to solid inorganic surfaces using self-assembled monolayers"; USPN 6,048,616 to Gallagher et al. (April 11, 2000) entitled "Encapsulated quantum sized doped semiconductor particles and method of manufacturing same"; and USPN 5,990,479 to Weiss et al. (November 23, 1999) entitled "Organo luminescent semiconductor nanocrystal probes for biological applications and process for making and using such probes."

**[00071]** Growth of nanowires having various aspect ratios, including nanowires with controlled diameters, is described in, e.g., Gudiksen et al (2000) "Diameter-selective synthesis of semiconductor nanowires" J. Am. Chem.

- 17 -

Soc. 122, 8801-8802; Cui et al. (2001) "Diameter-controlled synthesis of single-crystal silicon nanowires" Appl. Phys. Lett. 78, 2214-2216; Gudiksen et al. (2001) "Synthetic control of the diameter and length of single crystal semiconductor nanowires" J. Phys. Chem. B 105, 4062-4064; Morales et al. (1998) "A laser ablation method for the synthesis of crystalline semiconductor nanowires" Science 279, 208-211; Duan et al. (2000) "General synthesis of compound semiconductor nanowires" Adv. Mater. 12, 298-302; Cui et al. (2000) "Doping and electrical transport in silicon nanowires" J. Phys. Chem. B 104, 5213-5216; Peng et al. (2000) "Shape control of CdSe nanocrystals" Nature 404, 59-61; Puntes et al. (2001) "Colloidal nanocrystal shape and size control: The case of cobalt" Science 291, 2115-2117; USPN 6,306,736 to Alivisatos et al. (October 23, 2001) entitled "Process for forming shaped group III-V semiconductor nanocrystals, and product formed using process"; USPN 6,225,198 to Alivisatos et al. (May 1, 2001) entitled "Process for forming shaped group II-VI semiconductor nanocrystals, and product formed using process"; USPN 6,036,774 to Lieber et al. (March 14, 2000) entitled "Method of producing metal oxide nanorods"; USPN 5,897,945 to Lieber et al. (April 27, 1999) entitled "Metal oxide nanorods"; USPN 5,997,832 to Lieber et al. (December 7, 1999) "Preparation of carbide nanorods"; Urbau et al. (2002) "Synthesis of single-crystalline perovskite nanowires composed of barium titanate and strontium titanate" J. Am. Chem. Soc., 124, 1186; and Yun et al. (2002) "Ferroelectric Properties of Individual Barium Titanate Nanowires Investigated by Scanned Probe Microscopy" Nanoletters 2, 447.

[00072] Growth of branched nanowires (e.g., nanotetrapods, tripods, bipods, and branched tetrapods) is described in, e.g., Jun et al. (2001) "Controlled synthesis of multi-armed CdS nanorod architectures using monosurfactant system" J. Am. Chem. Soc. 123, 5150-5151; and Manna et al. (2000) "Synthesis of Soluble and Processable Rod-, Arrow-, Teardrop-, and Tetrapod-Shaped CdSe Nanocrystals" J. Am. Chem. Soc. 122, 12700-12706.

[00073] Synthesis of nanoparticles is described in, e.g., USPN 5,690,807 to Clark Jr. et al. (November 25, 1997) entitled "Method for producing

semiconductor particles”; USPN 6,136,156 to El-Shall, et al. (October 24, 2000) entitled “Nanoparticles of silicon oxide alloys”; USPN 6,413,489 to Ying et al. (July 2, 2002) entitled “Synthesis of nanometer-sized particles by reverse micelle mediated techniques”; and Liu et al. (2001) “Sol-Gel Synthesis of Free-Standing Ferroelectric Lead Zirconate Titanate Nanoparticles” J. Am. Chem. Soc. 123, 4344. Synthesis of nanoparticles is also described in the above citations for growth of nanocrystals, nanowires, and branched nanowires, where the resulting nanostructures have an aspect ratio less than about 1.5.

[00074] Synthesis of core-shell nanostructure heterostructures, namely nanocrystal and nanowire (e.g., nanorod) core-shell heterostructures, are described in, e.g., Peng et al. (1997) “Epitaxial growth of highly luminescent CdSe/CdS core/shell nanocrystals with photostability and electronic accessibility” J. Am. Chem. Soc. 119, 7019-7029; Dabbousi et al. (1997) “(CdSe)ZnS core-shell quantum dots: Synthesis and characterization of a size series of highly luminescent nanocrystals” J. Phys. Chem. B 101, 9463-9475; Manna et al. (2002) “Epitaxial growth and photochemical annealing of graded CdS/ZnS shells on colloidal CdSe nanorods” J. Am. Chem. Soc. 124, 7136-7145; and Cao et al. (2000) “Growth and properties of semiconductor core/shell nanocrystals with InAs cores” J. Am. Chem. Soc. 122, 9692-9702. Similar approaches can be applied to growth of other core-shell nanostructures.

[00075] Growth of nanowire heterostructures in which the different materials are distributed at different locations along the long axis of the nanowire is described in, e.g., Gudiksen et al. (2002) “Growth of nanowire superlattice structures for nanoscale photonics and electronics” Nature 415, 617-620; Bjork et al. (2002) “One-dimensional steeplechase for electrons realized” Nano Letters 2, 86-90; Wu et al. (2002) “Block-by-block growth of single-crystalline Si/SiGe superlattice nanowires” Nano Letters 2, 83-86; and US patent application 60/370,095 (April 2, 2002) to Empedocles entitled “

Nanowire heterostructures for encoding information.” Similar approaches can be applied to growth of other heterostructures.

*Epitaxial-Oriented Nanowire Growth Using a Combination of Silicon Precursors*

**[00076]** FIG. 2 is a flowchart of method 200 for preparing nanowires using a combination of Si precursors, according to an embodiment of the invention. Method 200 begins in step 202. In step 202, one or more nucleating particles, suitably metal catalysts, are deposited on a substrate material to create a nucleation site for nanowire growth. As shown in step 204, heating of the nucleating particles to a first temperature and contacting the nucleating particles with a first precursor gas mixture, creates a liquid alloy droplet and initiates nanowire growth, which is indicated by label 206. In step 208 heating the alloy droplet to a second temperature and contacting the alloy droplet with a second precursor gas mixture, allows nanowires to grow at the site of the alloy droplet, which is indicated by label 210, until they reach the desired size and orientation, as shown in step 214.

**[00077]** In suitable embodiments, the substrate material on which the nanowires are grown is a crystallographic substrate. The term "crystallographic substrate" includes any substrate material which comprises atoms situated in a repeating or periodic array over large atomic distances, typically on the order of 10 or more angstroms (Å). Such crystallographic substrates may be polycrystalline or may comprise single crystals. Suitably, the crystallographic substrate utilized in the processes of the present invention is silicon (Si). Other suitable crystallographic materials included, but are not limited to, germanium (Ge), gallium arsenide (GaAs), gallium nitride (GaN), sapphire, quartz, and silicon germanium (SiGe). In other embodiments of the present invention, the substrate material may comprise an amorphous material. Suitable amorphous substrate materials which may be used in the practice of

- 20 -

the present invention include, but are not limited to  $\text{SiO}_2$ ,  $\text{Si}_3\text{N}_4$  and alumina. In additional embodiments, substrate materials are composed of multiple layers, such as a silicon on insulator (SOI) surface.

[00078] As outlined in FIG. 2, in certain embodiments, the methods of the present invention comprise first depositing nucleating particles on a substrate material. Nucleating particles that may be used in the practice of the present invention include metal catalysts and can be any metal that reacts with both the first precursor gas mixture and the second precursor gas mixture (i.e., decomposed forms of the first and second precursor gas mixtures) to form a eutectic phase. Such a mixture has a minimum melting point at which all components are in solution. Upon addition and decomposition of precursor gas molecules (e.g., silicon) a saturation point on the eutectic phase diagram is reached such that semiconductor particles (e.g., Si) begin to precipitate out of the metal solution, thereby creating a growing nanowire. Continuous addition of precursor gas, as it decomposes, will continue to saturate the eutectic, thereby generating additional material for nanowire growth.

[00079] In suitable embodiments, the nucleating particles will be metal catalysts and can comprise any of the transition metals from the Periodic Table, including, but not limited to, copper, silver, gold, nickel, palladium, platinum, cobalt, rhodium, iridium, iron, ruthenium, tin, osmium, manganese, chromium, molybdenum, tungsten, vanadium, niobium, tantalum, titanium, zirconium and gallium, including mixtures of one or more of these metals. In preferred embodiments of the present invention, the metal catalyst can comprise a gold (Au) or aluminum (Al) colloid (i.e., a Au or Al nanoparticle) or Au or Al film. In certain such embodiments, 60 nanometer (nm) diameter gold colloids can be used. The target is to achieve a uniform deposition of gold nanoparticles with density between 2-4 particles per square micrometer ( $\mu\text{m}$ ). A key is minimized gold particle cluster formation. The clusters can result in undesired larger diameter nanowire growth. Spin coating and self assembly methods can be explored for the deposition (see e.g., U.S. Patent

Application No. 10/674,060, filed September 30, 2003, which incorporated by reference herein in its entirety).

**[00080]** Spin coating is a fairly straightforward process. A deposition density can be controlled through variation of the gold particle concentration in the precursor colloids, manipulation of surface chemistry of the silicon wafer, and changing the spin speed. A drawback of spin coating can be low utilization efficiency of gold colloid solution. A recycling process in the production stage can be used if warranted.

**[00081]** Self assembly involves some use of well established chemistry. The surface of 4 inch silicon oxide coated wafer is functionalized with either (3-aminopropyl)-trimethoxysilane (APTMS) or (3-mercaptopropyl)-trimethoxysilane (MPTMS), then contacted with 60 nm gold colloid solution. The gold particles are assembled on the surface. The difference between two different chemistries are compared, and the possibility of controlling the density of gold particles by control of the contact time and gold particle concentration in the contact solution can be used.

**[00082]** The nucleating particles used to practice the present invention can also be formed on a substrate surface by heating a gold film coating layer on the surface.

**[00083]** In one embodiment, the present invention comprises heating the first precursor gas mixture to a temperature at which 1) the gas dissociates into its free component atoms, and 2) the nucleating particles (e.g. metal catalyst) melts to a liquid. The free gas molecules can then diffuse into the metal catalyst to form a liquid alloy droplet. This process is commonly known to those of ordinary skill in the art as chemical vapor deposition (CVD).

**[00084]** In suitable embodiments of the present invention, the first precursor gas may comprise a gas which includes at least one atomic species that promotes the growth of nanowires (e.g., Si) as well as an atomic species that aids in orienting the nanowires during their growth (e.g., Cl atoms). For example, the first precursor gas may be selected from, but not limited to, Si<sub>2</sub>H<sub>6</sub>, SiH<sub>4</sub>, SiCl<sub>4</sub> and SiH<sub>2</sub>Cl<sub>2</sub> gas, preferably SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>.

[00085] Heating these Si precursor gases above the temperature at which the thermal energy is sufficient to break the bond energies between the gaseous molecules generates free Si atoms. (e.g., Si-H bond: 93kcal/mole, Si-Cl bond: 110kcal/mole, Si-Si bond; 77kcal/mole, *see* M.T. Swihart and R.W. Carr, *J. Phys Chem A* 102:1542-1549 (1998).) Provided that this temperature is also high enough to liquefy the metal catalyst, the free Si atoms will diffuse into the metal and generate a eutectic phase. Dissociation temperatures for SiH<sub>4</sub> and Si<sub>2</sub>H<sub>6</sub>, and SiCl<sub>4</sub> and SiH<sub>2</sub>Cl<sub>2</sub> gases are between about 300°C to 500°C (for Si<sub>2</sub>H<sub>6</sub> and SiH<sub>4</sub>), and above about 800°C (for SiCl<sub>4</sub> and SiH<sub>2</sub>Cl<sub>2</sub>) respectively. In the instances of SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>, Cl atoms are also generated. Decomposition of SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub> into Si and Cl in the presence of a carrier gas (e.g., H<sub>2</sub>, H<sub>2</sub>Ar) forms HCl.

[00086] As discussed in more detail below, this creates a competition between etching with HCl and growth from the Si vapor. Chlorine aids in removal of interfacial oxide on Si substrates leading to oriented NW growth. However, because the decomposition of SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub> into Si and Cl occurs at a relatively high temperature (e.g., above about 800°C), metal diffusion of the metal catalysts into the growing nanowires is more likely to occur if the temperature is maintained above about 800°C for an extended time period.

[00087] Furthermore, at higher temperatures, the loss of metal catalyst is more likely to occur due to increased melting of the catalyst leaving less catalyst (or none) available to promote growth of the nanowires, thus limiting the length to which the nanowires can be grown. Accordingly, following the initiation of nanowire growth and orientation with SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>, it is preferable to introduce another precursor gas mixture (including, e.g., Si<sub>2</sub>H<sub>6</sub> or SiH<sub>4</sub>) to contact the metal catalyst, which gas mixture includes a precursor gas which decomposes into Si atoms at lower temperatures than the first precursor gas (but at a high enough temperature to form a eutectic phase with the metal catalyst).

[00088] In all embodiments of the present invention, the precursor gas mixtures used during any of the nanowire growth processes may further comprise one

or more doping gases. Examples of suitable doping gases that may be used in the practice of the present invention include, but are not limited to, B<sub>2</sub>H<sub>6</sub>, trimethyl boron (TMB) POCl<sub>3</sub> and PH<sub>3</sub>.

[00089] In one embodiment of the present invention, the first precursor gas can comprise SiCl<sub>4</sub> and suitably a carrier gas, such as He, Ar, or other inert gas. Heating this gas mixture to a sufficiently high temperature, e.g., above about 800°C, generates free Si and Cl atoms. In suitable such embodiments, the first precursor gas may comprise one or more dopant gases selected from those described throughout the application. The first precursor gas mixture is passed over the nucleating particles, suitably metal-catalyst particles (e.g., gold nanoparticles) deposited on the substrate material at a total pressure between about 20 to about 50 Torr, while the nucleating particles are heated up to a temperature of about 800°C. In other embodiments of the present invention, the gas pressure may be increased or decreased, thereby requiring a modification in the temperature required to dissociate the precursor gas mixture.

[00090] For example, SiCl<sub>4</sub> when heated to the appropriate temperature will decompose into free Si and Cl atoms. When B<sub>2</sub>H<sub>6</sub> is present in the precursor gas mixture, B atoms will also be generated. Si and B will diffuse into the metal catalyst and generate a liquid alloy droplet. This eutectic phase of metal catalyst and precursor gases will continue to exist as precursor gas is solvated in the metal catalyst. Once an over-saturation is reached, Si/B atoms will precipitate out and initiate nanowire growth. In order to continue nanowire growth, a continuous supply of Si precursor gas and doping gas are required. However, maintaining a temperature above about 800°C for extended periods can lead to the metal catalyst diffusing into the growing nanowire creating trap states and reducing the diameter and length of the overall nanowire that can be obtained.

[00091] In certain embodiments of the present invention, once nanowire growth is initiated (e.g., using SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>), a second precursor gas can be substituted (e.g., SiH<sub>4</sub>) and nanowire growth continued. The point at which

the second precursor gas is introduced into the system can be determined experimentally by the skilled artisan. In other embodiments of the present invention, nanowire growth can be initiated using SiH<sub>4</sub> and then followed with SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub> as a second precursor gas thereby allowing for Cl etching. In certain such embodiments, the first temperature at which the first precursor gas mixture is added to initiate nanowire growth and the second temperature at which nanowire growth is continued using a second precursor gas mixture can be the same, so long as the temperature used is high enough to allow for dissociation of the gases and diffusion of Si and dopant into the liquid metal catalyst. In other embodiments, the first temperature used to initiate nanowire growth will be higher than the second temperature used to continue nanowire growth. These temperatures can differ by any amount (e.g., about a few degrees C to 10's of degrees C to 100's of degrees C), so long as the temperatures used are high enough to allow for dissociation of the gases and diffusion of Si and dopant into the liquid metal catalyst.

**[00092]** In certain embodiments of the present invention, once nanowire growth is initiated, suitably using a temperature of about 800°C and SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub> as a first precursor gas, a second precursor gas can be substituted and the temperature changed to continue nanowire growth. The point at which the second precursor gas is introduced into the system can be determined experimentally by the skilled artisan. In certain such embodiments, the first temperature at which nanowire growth is initiated will be higher than the second temperature, where nanowire growth continues. In suitable embodiments, the second precursor gas will comprise SiH<sub>4</sub> and growth will continue at a temperature of about 300°C to about 500°C. In certain embodiments, the first temperature will be at least about 50°C above the second temperature. Continuing to grow the nanowire at a lower temperature reduces the possibility that the metal catalyst can diffuse into the growing nanowire.

**[00093]** The present invention encompasses the use of any number of precursor gases in the process of growing nanowires. For example, nanowire growth

can be initiated with a first precursor gas comprising  $\text{SiCl}_4$ , suitably at a temperature of about  $800^\circ\text{C}$ , and then continued with a second precursor gas comprising  $\text{SiH}_2\text{Cl}_2$ , suitably at a temperature of about  $750^\circ\text{C}$ . In other embodiments,  $\text{SiH}_2\text{Cl}_2$  can be used as the first precursor gas. The wires then can be contacted with a third precursor gas, comprising, for example  $\text{SiH}_4$  or  $\text{Si}_2\text{H}_6$ , suitably at a temperature of about  $300\text{--}500^\circ\text{C}$ . As shown in FIG 2 in step 212, in other embodiments of the invention, any number of precursor gases can be introduced to the nanowires during the initiation and growth processes, until the nanowires reach the desired size and orientation, which is indicated in step 214. Provided that as long as the temperature at which the precursor gases contact the metal catalyst is above the dissociation temperature of the gas mixture and above the temperature required to liquefy the metal catalyst, the wires will continue to grow, as Si (or other suitable semiconductor materials as discussed throughout) and the dopant will continue to precipitate out of the metal catalyst allow droplet.

**[00094]** In certain embodiments, nanowire growth can be initiated using  $\text{SiH}_4$  or  $\text{Si}_2\text{H}_6$  and then continued using  $\text{SiCl}_4$  or  $\text{SiH}_2\text{Cl}_2$  to allow for Cl etching of Si growing in undesired locations and orientations on the substrate surface. The precursor gas mixture may then be switched back to  $\text{SiH}_4$  or  $\text{Si}_2\text{H}_6$  if desired. In certain such embodiments, the temperature at which the three gases can be kept the same, or can be modified as needed, so long as free Si atoms are allowed to mix with the liquefied metal catalyst. In other embodiments of the present invention, free Si, Cl or H atoms may be supplied to the growing nanowires to aid in growth (e.g., Si), etching (e.g., Cl) or gas dissociation (e.g., H) as needed.

**[00095]** As discussed throughout, the precursor gas mixtures used in the processes of the present invention may further comprise a dopant. In suitable embodiments of the present invention, wires can be grown using the same doping gas in each of the precursor gas mixtures. In such embodiments, the entire resulting wire will be either p-type or n-type, depending on the choice of dopant. In other embodiments of the present invention, different doping gases

can be introduced throughout the process as components of the different precursor gases. For example, wire growth can be initiated using a precursor gas comprising a n-type dopant (e.g., P, As or Sb) and then continued using a precursor gas using a p-type dopant (e.g., B, Al or In). In other embodiments, a p-type doing gas will be used during initiation and then an n-type doping gas during growth.

[00096] In other embodiments, the type of doping gas can be switched multiple times throughout the growth process as the precursor gases are switched. The resulting nanowires therefore can comprise several different dopant portions throughout their length. For example, a nanowire produced via the present invention may comprise an n-type base, a p-type middle section, and an n-type top, or any suitable combination as envisioned by the ordinarily skilled artisan. Such embodiments of the present invention would allow for an n-type wire to be grown on a p-type substrate, and vice versa.

[00097] Continuously supplying the second precursor gas mixture (and third, fourth, fifth, etc.) will allow the nanowire to continue growing until termination by desire or death caused by local condition change. The quality of the nanowires is dependent on the quality of gold nanoparticles, control of gold nanoparticle distribution on the substrate and growth condition including temperature, ratio of dopant to precursor gas, partial pressure of the precursor gas, and resident time of precursor gases in the reactor. In suitable embodiments of the present invention, the processes of the present invention can be accomplished using a computer controlled 8" semiconductor furnace.

[00098] In suitable embodiments, the various precursor gas mixtures that are introduced in any of the processes of the present invention may be introduced via Plasma Enhanced Sputter Deposition (or Plasma Enhanced Chemical Vapor Deposition (PECVD)) and the processes performed at lower temperatures. (See Hofmann *et al.*, "Gold Catalyzed Growth of Silicon Nanowires by Plasma Enhanced Chemical Vapor Deposition," *J. Appl. Phys.* 94:6005-6012 (2003).) Decomposition of SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub> into Si and Cl in the presence of a carrier gas (e.g., H<sub>2</sub>, H<sub>2</sub>Ar) forms HCl. This creates a

competition between etching with HCl and growth from the Si vapor. Chlorine aids in removal of interfacial oxide on Si substrates leading to the oriented NW growth. Loss of metal catalyst (e.g., Au or Al) can occur either by etching or thermal evaporation of AuCl that can form. Use of PECVD to grow NWs at temperatures below about 800°C, with the addition of chlorine gas from SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>, and/or the addition of chlorine gas from a source separate from the source of SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>, the reactive species of Si and Cl can be independently controlled in the plasma to enhance or suppress etching as needed to promote nanowire growth. Sputter deposition can be accomplished via any method known to the ordinarily skilled artisan, for example, diode, radio frequency and direct current deposition.

[00099] The diameter distribution of silicon nanowires of these certain embodiments of the present invention is determined by that of the nucleating particles, e.g., metal (suitably gold) nanoparticles. Commercially available 60 nanometer gold colloids can have a diameter distribution of  $\pm$  10%. The same distribution can be attained in the nanowires. Gold nanoparticles can be split into smaller ones resulting in smaller diameter nanowires, depending on the growth condition. Growth conditions can be optimized to minimize this event. Given a growth condition, the length of nanowires can be controlled by varying duration of the growth. Crystallinity of silicon nanowires and dopant concentration are also growth condition dependent. They can be optimized and controlled together with other important nanowire characteristics.

[000100] The nanowires produced according to any of the processes of the present invention will suitably grow out of the plane of the substrate material. Such growth includes nanowires that project out of the plane of the substrate material at any angle with respect to the substrate. For example, nanowires can grow at an angle of about 1° to about 90°, and any angle in between these values, relative to the plane of the substrate material. It is a requirement of the present invention that the nanowires produced by the processes described herein must project out of the plane of the substrate. That is, the nanowires produced by the processes of the present invention must extend off of the

plane of the substrate material a distance greater than the dimension of a single molecule. As such, the nanowires produced according to the present invention are distinct from structures such as thin films and quantum dots, which spread on the surface of a substrate material, rather than growing in a manner such that they project out of the plane of the substrate a distance that exceeds the atomic diameter of a single Si molecule for instance.

**[000101]** Suitably, the nanowires produced according to any of the processes of the present invention will project out of the plane of the substrate material so as to attain a final length of about 100 nm to less than about 1  $\mu\text{m}$ . In suitable such embodiments, the nanowires produced according the present invention can attain a final length of a few 100 nms. The nanowires of the present invention will suitably be at least about 1 nm to less than about 1  $\mu\text{m}$  in diameter. For use in electronic devices, the nanowires of the present invention will have a diameter of about a few nms to 100's of nms, so as to allow them to be harvested and utilized in an electronic device, suitably by placing the wires in plastic substrates so as to act as conductive media. (See U.S. Application No. 60/491,979, filed August 4, 2003, for a description of nanowire harvesting which is incorporated herein by reference.)

**[000102]** In suitable embodiments of the present invention, the nanowires, when growing on a crystalline substrate (whether polycrystalline or single crystal) will preferably grow in an epitaxial orientation. However, the present invention also embodies growth on crystalline substrates wherein the nanowires do not grow in an epitaxial orientation. As used herein, the term epitaxial as it refers to the growth of nanowires means that the nanowires have the same crystallographic characteristic(s) as the substrate material on which they are growing. For example, the orientation of the substrate material can be any crystallographic orientation known to the ordinarily skilled artisan, including, but not limited to,  $<111>$ ,  $<110>$ ,  $<100>$  and  $<211>$ . In suitable embodiments then, the nanowires produced by the processes of the present invention can be grown in any crystallographic orientation, and suitably in the

same orientation as the substrate material, including those orientations discussed throughout and as known to the ordinarily skilled artisan.

[000103] As discussed throughout, suitable precursor gases that can be used in the processes of the present invention comprise  $\text{SiCl}_4$  and  $\text{SiH}_2\text{Cl}_2$ . Dissociation of these gasses generates free chloride ions (Cl) in the gas phase. These Cl ions, and/or additional chlorine ions introduced from a separate source of chlorine gas, act to etch the growing Si nanowires in an orientation that is preferentially a <111> orientation.

[000104] In other suitable embodiments of the present invention, the crystallographic plane of the substrate material can be off axis of the 0° horizontal plane. The nanowires growing on the surface of such a substrate material can project out of the substrate material at an angle such that the wires can be normal to the crystallographic plane (i.e., 90° with respect to the crystallographic plane) or can be off axis relative to the crystallographic plane such that they can be normal to a 0° horizontal plane.

[000105] In embodiments of the present invention where amorphous substrates are utilized, the nanowires produced according to the processes of the present invention will not grow epitaxially, as the amorphous material does not comprise a crystallographic orientation. However, as noted above, the nanowires grown on such substrates may project out of the plane of the substrate at any angle relative to the horizontal plane.

[000106] The processes of the present invention produce nanowires that may carry electrons between two points in space and thus act to transfer charge. In this way, the nanowires of the present invention are further distinct from nanodots and in their size and orientation, are distinct from semiconductor films.

[000107] In another embodiment, the present invention provides for processes for producing nanowires which does not require a starting metal catalyst, as outlined in FIG 3. FIG. 3 is a flowchart of a method for preparing nanowires using a combination of Si precursors which does not require a starting metal catalyst, according to an embodiment of the invention.

- 30 -

[000108] Method 300 begins in step 302. In step 302 a substrate material is hydroxylated to produce nucleation sites. In step 304 contacting the substrate material with a first precursor gas mixture generates one or more nuclei on a surface of the substrate material, which is indicated by label 306. In step 308 contacting the nuclei with a second precursor gas mixture, allows nanowires to grow at the site of the one or more nuclei, as indicated by label 310, until they reach the desired size and orientation, which is shown as step 314.

[000109] This process of the present invention does not require the use of a metal catalyst to provide a nucleation site for the nanowire, and therefore eliminates the problems and concerns that arise due to metals diffusing into the growing nanowires. A similar process has been described by De Salvo *et al.* for the production of nanocrystals in the form of nanodots ("How far will Silicon nanocrystals push the scaling limits of NVMs technologies?", *IEEE Proceeding, Session 26*, p.1 (2003)), but has not been extended to the production of nanowires as in the present invention.

[000110] As discussed throughout, any suitable substrate material may be used for the processes of the present invention. Suitably, the substrate material will be crystallographic, including both polycrystalline and single crystal substrates. In certain embodiments, the substrate material utilized in this embodiment of the present invention will comprise silicon. In other suitable embodiments of the present invention, the substrate material will be an amorphous material, including but not limited to, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, or alumina.

[000111] Hydroxylation of the substrate material in these embodiments of the present invention can be generated by any suitable process known to the ordinarily skilled artisan. For example, hydroxylation of a substrate material of the present invention can be generated by chemical treatment of the substrate material with diluted HF solution. Generation of hydroxyl groups on the surface of the substrate material create nucleation points for Si or other semiconductor materials to deposit and initiate nanowire growth.

[000112] Following hydroxylation, the substrate material is then contacted with one or more precursor gas mixtures to allow nucleation and initiation of

nanowire growth. Any precursor gas mixture known to the ordinarily skilled artisan can be used in the processes of the present invention, and suitably can comprise dopants. Examples of precursor gases useful in the practice of the present invention comprise, but are not limited to, SiH<sub>4</sub>, Si<sub>2</sub>H<sub>6</sub>, SiCl<sub>4</sub> and SiH<sub>2</sub>Cl<sub>2</sub>, preferably SiH<sub>4</sub> or Si<sub>2</sub>H<sub>6</sub>, which nucleates particles on the surface of the substrate, and in suitable embodiments may further comprise dopants such as, but not limited to, B<sub>2</sub>H<sub>6</sub>, TMB, POCl<sub>3</sub> and PH<sub>3</sub>. The temperature for dissociation and nucleation of the nanowires is dependent upon the dissociation temperature of the precursor gas mixture as discussed throughout. In suitable embodiments, this temperature is at least about 300°C, but is optimized based on the dissociation temperature of the precursor gas mixture as discussed throughout. In certain such embodiments, the first precursor gas mixture will comprise SiH<sub>4</sub>.

[000113] Following nucleation and initiation of growth, the substrate material is then contacted with one or more second precursor gas mixtures as described throughout, and suitably can comprise SiH<sub>4</sub>, Si<sub>2</sub>H<sub>6</sub>, SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>, preferably SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>, and may further comprise B<sub>2</sub>H<sub>6</sub>, POCl<sub>3</sub> or PH<sub>3</sub>. In certain embodiments, the second precursor gas mixture will comprise SiCl<sub>4</sub> or SiH<sub>2</sub>Cl<sub>2</sub>. Use of such precursor gases will allow for growth in a <111> orientation when grown on a crystallographic substrate as a result of etching from the dissociated Cl as discussed above. In other embodiments of the invention, as shown in step 312 of FIG. 3, any number of precursor gases may be introduced to the nanowires during the initiation and growth processes, as long as one or more of the precursor gases is capable of nucleating particles on the surface of the substrate, and one or more precursor gas(es) aids in orienting the nanowires during the growth process (e.g., via etching). Provided further that as long as the temperature at which the wires contact the metal catalyst is above the dissociation temperature of the gas mixture, the wires will continue to grow. In other embodiments free H, Cl or Si atoms can be added to the growing nanowires as discussed throughout. As discussed throughout, the processes of the present invention can be used to produce nanowires that

comprise various dopants and different regions of these dopants throughout the length of the nanowire.

[000114] In embodiments of the present invention where crystallographic substrates are utilized, the nanowires produced will preferably grow in an epitaxial orientation, though the present invention also encompasses embodiments where growth on crystallographic substrates is not epitaxial. The processes of the present invention, as discussed throughout, produce nanowires that grow and project out of the plane of the substrate material. As such, the nanowires of the present invention are distinct from nanodots that do not grow in such an orientation, but rather remain in the plane of the substrate material. The present invention, by providing Si structures that project out of the plane of the substrate material, allow for the production of nanowires that can be used to transport electrical charge as discussed throughout.

[000115] In an embodiment, a method for producing nanowires, includes hydroxylating a substrate material; contacting the substrate material with a first precursor gas mixture comprising a first precursor gas that is capable of forming one or more nucleated particles on a surface of the substrate material; contacting the one or more nucleated particles with a second precursor gas mixture, comprising at least one atomic species that aids in orienting the growing nanowires; and growing nanowires at the site of the one or more nucleated particles. In an aspect of this embodiment the first precursor gas mixture comprises  $\text{SiH}_4$  or  $\text{Si}_2\text{H}_6$ . In another aspect of this embodiment the second precursor gas mixture comprises  $\text{SiCl}_4$  or  $\text{SiH}_2\text{Cl}_2$ . In another aspect of this embodiment the second precursor gas mixture comprises chlorine gas from an independent chlorine gas source which is separate from the source of  $\text{SiCl}_4$  or  $\text{SiH}_2\text{Cl}_2$  gas. Nanowires can be produced by this method. Electronic circuits including nanowires produced by this method can also be produced.

[000116] The present invention also provides for nanowires produced by any of the processes of the present invention. As discussed throughout, nanowires produced by the processes of the present invention will suitably be of a length of at least about 100nm and at least about 1 nm to less than about 1  $\mu\text{m}$  in

diameter, and may comprise various dopants (i.e., p- and n- type regions) throughout their length.

[000117] The present invention also provides for electronic circuits comprising the nanowires produced by any of the processes of the present invention. Suitably collections of nanowires produced according to the processes of the present invention are useful building blocks for high performance electronics. A collection of nanowires orientated in substantially the same direction will have a high mobility value. Furthermore, nanowires can be flexibly processed in solution to allow for inexpensive manufacture. Collections of nanowires can be easily assembled onto any type of substrate from solution to achieve a thin film of nanowires. For example a thin film of nanowires used in a semiconductor device can be formed to include 2, 5, 10, 100, and any other number of nanowires between or greater than these amounts, for use in high performance electronics.

[000118] The nanowires of the present invention can also be used to make high performance composite materials when combined with polymers/materials such as organic semiconductor materials, which can be flexibly spin-cast on any type of substrate. Nanowire/polymer composites can provide properties superior to a pure polymer materials. Further detail on nanowire/polymer composites is provided below.

[000119] Collections or thin films of nanowires of the present invention can be aligned into being substantially parallel to each other, or can be left non-aligned or random. Non-aligned collections or thin films of nanowires provide electronic properties comparable or superior to polysilicon materials, which typically have mobility values in the range of 1-10 cm<sup>2</sup>/V·s.

[000120] Aligned thin films of nanowires of the present invention can be obtained in a variety of ways. For example, aligned thin films of nanowires can be produced by using the following techniques: (a) Langmuir-Blodgett film alignment; (b) fluidic flow approaches, such as described in U.S. Serial No. 10/239,000, filed September 10, 2002 (Attorney Docket No. 01-000540), and incorporated herein by reference in its entirety; and (c) application of

mechanical shear force. For example, mechanical shear force can be used by placing the nanowires between first and second surfaces, and then moving the first and second surfaces in opposite directions to align the nanowires. Aligned thin films of nanowires/polymer composites can be obtained using these techniques, followed by a spin-casting of the desired polymer onto the created thin film of nanowires. For example, nanowires can be deposited in a liquid polymer solution, alignment can then be performed according to one of these or other alignment processes, and the aligned nanowires can then be cured (e.g., UV cured, crosslinked, etc.). An aligned thin film of nanowires/polymer composite can also be obtained by mechanically stretching a randomly oriented thin film of nanowires/polymer composite.

**[000121]** P-doped nanowires and n-doped nanowires produced by the processes of the present invention can be separately fabricated, and deposited in a homogeneous mixture onto a surface, such as a macroelectronic substrate. On a macroscopic level, the resulting material appears to contain a high concentration of both n- and p-dopants. By creating such a mixture of p- and n-doped nanowires, macroelectronic devices can be fabricated that respond as if they are both n- and p-doped. For example, a resulting thin film of nanowires that includes both n-doped and p-doped nanowires can exhibit characteristics of both n-doped and p-doped nanowires. For example, diode, transistor, and other known electrical devices can be fabricated to include a combination of p-doped nanowires and n-doped nanowires.