(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6306063号

(P6306063)

(45) 発行日 平成30年4月4日(2018.4.4)

(24) 登録日 平成30年3月16日(2018.3.16)

(51) Int.Cl.

F 1

|             |           |      |        |      |

|-------------|-----------|------|--------|------|

| HO1L 27/00  | (2006.01) | HO1L | 27/00  | 301D |

| HO1L 29/786 | (2006.01) | HO1L | 29/78  | 613Z |

| HO1L 21/822 | (2006.01) | HO1L | 27/04  | A    |

| HO1L 27/04  | (2006.01) | HO1L | 27/088 | 331E |

| HO1L 27/088 | (2006.01) | HO1L | 27/092 | G    |

請求項の数 5 (全 14 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-561629 (P2015-561629)  |

| (86) (22) 出願日 | 平成26年3月5日(2014.3.5)           |

| (65) 公表番号     | 特表2016-517625 (P2016-517625A) |

| (43) 公表日      | 平成28年6月16日(2016.6.16)         |

| (86) 國際出願番号   | PCT/US2014/020941             |

| (87) 國際公開番号   | W02014/138317                 |

| (87) 國際公開日    | 平成26年9月12日(2014.9.12)         |

| 審査請求日         | 平成29年2月6日(2017.2.6)           |

| (31) 優先権主張番号  | 13/788,224                    |

| (32) 優先日      | 平成25年3月7日(2013.3.7)           |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                         |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                         |

| (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                         |

| (74) 代理人  | 100194814<br>弁理士 奥村 元宏                                                                                         |

最終頁に続く

(54) 【発明の名称】半導体集積回路のモノリシック3次元集積化

## (57) 【特許請求の範囲】

## 【請求項1】

方法であって、

第2の半導体ウエハに酸化接合されることとなる第1の半導体ウエハの少なくとも一部においてn型およびp型のドープ領域を形成するためにイオンを前記第1の半導体ウエハに注入すること、ここにおいて、前記n型およびp型のドープ領域は、複数のナノワイヤトランジスタのためのチャネルを備える、と、

熱開裂を容易にするためにイオンを前記第1の半導体ウエハに注入することと、

前記第1の半導体ウエハを前記第2の半導体ウエハに酸化接合することと、

前記第1の半導体ウエハの前記一部が前記第2の半導体ウエハに酸化接合されたままとなるように熱開裂させるために前記第1の半導体ウエハを450度以下の温度に加熱することと、

前記第2の半導体ウエハに酸化接合された前記第1の半導体ウエハの前記一部において前記n型およびp型のドープ領域を分離させるために酸化物分離トレンチを形成することと、

前記第2の半導体ウエハに酸化接合された前記第1の半導体ウエハの前記一部において前記複数のナノワイヤトランジスタのための前記n型およびp型のドープ領域内の前記チャネルと接触しているソースおよびドレインを選択的に形成するために、450度以下の温度で、エピタキシャル成長中にその場でドープすること、ここにおいて、エピタキシャル成長中にその場でドープするステップは、酸化物分離トレンチを形成するステップの後

10

20

に実行される、と、

を備える方法。

【請求項 2】

前記第2の半導体ウエハは最下階層を備え、前記最下階層は複数のトランジスタを備え、熱開裂させるために前記第1の半導体ウエハを450度以下の温度に加熱することは、前記第1の半導体ウエハの前記一部を、前記最下階層に酸化接合させたままにする、請求項1に記載の方法。

【請求項 3】

前記複数のナノワイヤトランジスタは、pチャネル電界ピンチナノワイヤトランジスタ、nチャネル電界ピンチナノワイヤトランジスタ、p型反転チャネルナノワイヤトランジ

10 スター、および／またはn型反転チャネルナノワイヤトランジスタを備える、請求項2に記載の方法。

【請求項 4】

前記チャネルを備える前記n型およびp型のドープ領域は、前記ソースおよびドレインのものよりも低い濃度にドープされる、請求項1に記載の方法。

【請求項 5】

前記複数のナノワイヤトランジスタは蓄積モードで動作する、請求項4に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

[0001] 本発明は、超小型電子加工技術に関し、具体的には、半導体デバイスのモノリシック3次元集積化に関する。

20

【背景技術】

【0002】

[0002] 主にスケーリングによって、過去40年にわたり集積回路（IC）の機能性および性能は劇的に増加してきており、このスケーリングでは、歴代の各技術でIC内の部品サイズが小型化（スケーリング）されてきた。スケーリングにより、多くの場合トランジスタ性能および密度は改善するが、これらトランジスタを互いに接続する配線（インターフェクト（interconnect））は性能を低下させる。配線は、ICの性能、機能性、および電力消費を左右することが多い。

30

【0003】

[0003] 半導体チップ（ダイ）の一連の3D（3次元）集積化は、配線性能に取り組む際の1つの手段である。2次元ではなく3次元でトランジスタを配列することで、ICトランジスタを互いのより近くに配置することができる。これは、配線長を短縮し、信号遅延を減らす。しかしながら、3D集積化チップの実用的な実装には多くの障害が存在する。1つのそのような障害は、配線レベルが低い温度（450度よりも低い）で形成されることに対し、ICにおけるトランジスタ形成が通常高い温度（約700度よりも高い）を必要とすることである。銅およびアルミニウムの配線レベルは、約500度よりも高い温度に曝されるとダメージを受けうる。そのため、3D集積化ICの製造は、いくつかの挑戦をもたらす。

40

【発明の概要】

【0004】

[0004] 本発明の実施形態は、半導体集積回路の3次元集積化のためのシステムおよび方法に向けられる。

【0005】

[0005] ある実施形態では、方法は、熱開裂（thermal cleavage）を容易にするためにイオンを第1の半導体ウエハに注入することと、第1の半導体ウエハを第2の半導体ウエハに酸化接合することとを含む。第1の半導体ウエハは、第1の半導体ウエハの一部が第2の半導体ウエハに酸化接合されたままとなるように熱開裂を引き起こすために450度以下の温度に加熱される。第2の半導体ウエハに酸化接合された第1の半導体ウエハの一

50

部における複数のナノワイヤトランジスタのためのソースおよびドレインは、450度以下の温度でエピタキシャル成長中にその場(*in-situ*)でドープすることで形成される。

#### 【0006】

[0006] 別の実施形態では、装置は、シリコン基板と、このシリコン基板に酸化接合された最上階層(*top tier*)とを含み、最上階層は複数のナノワイヤトランジスタを備え、複数のナノワイヤトランジスタの各ナノワイヤトランジスタは、ソースと、ドレインと、ソースおよびドレインのものよりも低いドーピング濃度(*doping concentration*)を有するチャネルとを備える。

#### 【0007】

[0007] 別の実施形態では、装置は、シリコン基板と、このシリコン基板上に形成された最下階層(*bottom tier*)、前記最下階層は複数のトランジスタを含む、と、最下階層に酸化接合された最上階層、前記最上階層は複数のナノワイヤトランジスタを備え、ここにおいて、複数のナノワイヤトランジスタの各ナノワイヤトランジスタは、ソースと、ドレインと、ソースおよびドレインのものよりも低いドーピング濃度を有するチャネルとを備える、と、および、接続するための手段、前記接続するための手段は、最下階層における複数のトランジスタのうちの少なくとも1つのトランジスタを、最上階層における複数のナノワイヤトランジスタの少なくとも1つのナノワイヤトランジスタに接続するためのものである、と、を含む。

#### 【0008】

[0008] 別の実施形態では、方法は、イオンを注入するための手段、前記イオンを注入するための手段は、第1の半導体ウエハにおいて熱開裂を容易にするためのものである、と、接合するための手段、前記接合するための手段は、第1の半導体ウエハを第2の半導体ウエハに酸化接合するためのものであり、第2の半導体ウエハは、トランジスタの最下階層を備える、と、加熱するための手段、前記加熱するための手段は、第1の半導体ウエハの一部が最下階層に酸化接合されたままになるように熱開裂を引き起こすために450度以下の温度に第1の半導体ウエハを加熱するためのものである、と、ドープするための手段、前記ドープするための手段は、最下階層に酸化接合された第1の半導体ウエハの一部における複数のナノワイヤトランジスタのためのソースおよびドレインを形成するために450度以下の温度でエピタキシャル成長中にその場でドープするためのものである、と、を含む。

#### 【0009】

[0009] 添付の図面は、本発明の実施形態の説明を助けるために提示され、これら実施形態の限定としてではなくその例示のためだけに提供される。

#### 【図面の簡単な説明】

#### 【0010】

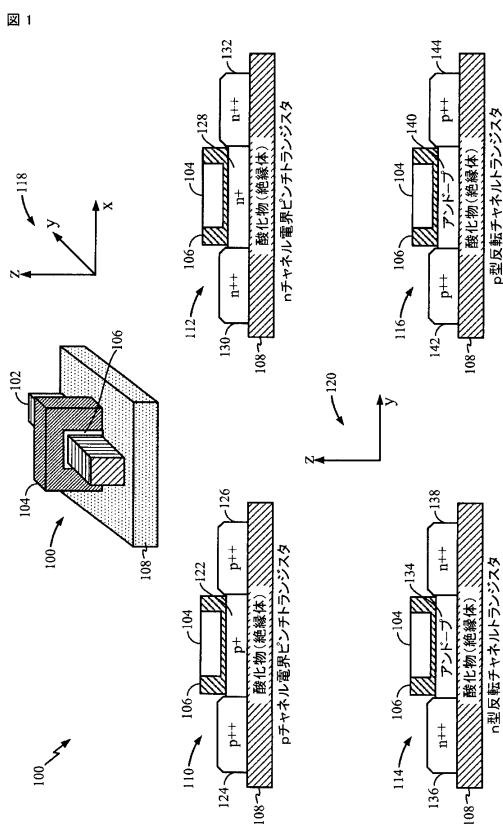

【図1】図1は、ある実施形態に係る様々なタイプのナノワイヤトランジスタを例示する。

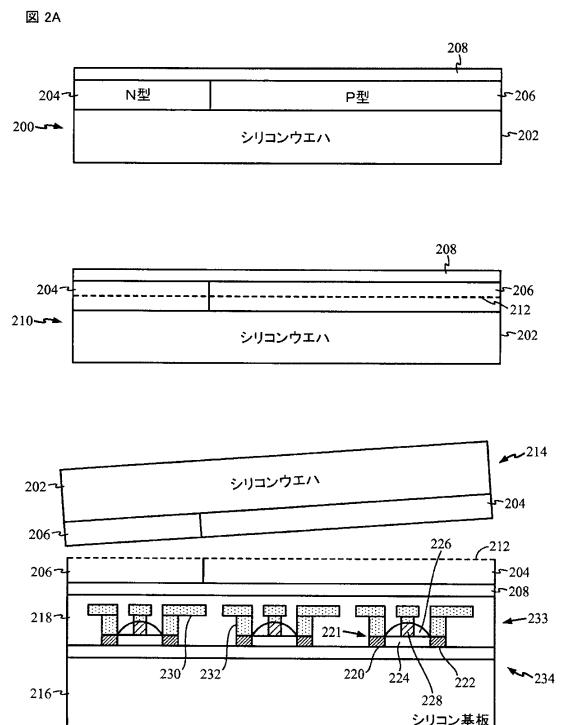

【図2A】図2Aは、ある実施形態に係る、プロセスフローにおける様々な構造およびステップを例示する。

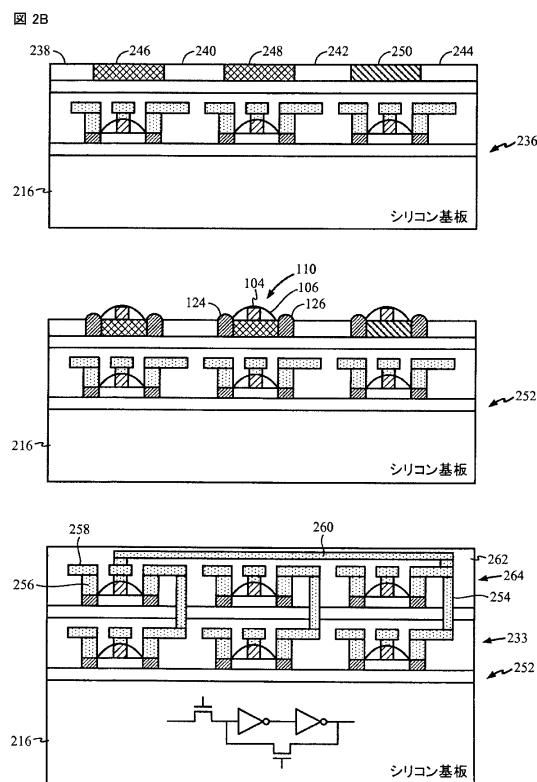

【図2B】図2Bは、ある実施形態に係る、プロセスフローにおける様々な構造およびステップを例示する。

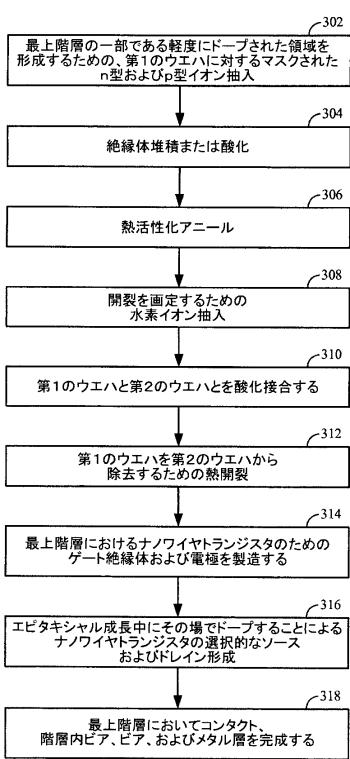

【図3】図3は、ある実施形態に係る、プロセスフローにおける様々なステップを例示する。

【図4】図4は、実施形態が応用されるワイヤレス通信システムを例示する。

#### 【発明を実施するための形態】

#### 【0011】

[0014] 本発明の態様は、本発明の特定の実施形態に向けられた以下の説明および関連の図面で開示される。代替的な実施形態が、本発明の適用範囲(*scope*)から逸脱することなく考案されうる。追加的に、本発明の周知の要素は、本発明に関連性のある詳細を曖昧にしないために、詳細には説明されないかまたは省略されるだろう。

10

20

30

40

50

## 【0012】

[0015] 「例示的（な）」という単語は、本明細書では、「実例、事例、または例示としての役割を果たす」という意味で使用される。「例示的（な）」として本明細書で説明される任意の実施形態は、必ずしも、他の実施形態よりも好ましいまたはそれよりも有利であると解釈されるべきではない。同様に、「本発明の実施形態」という用語は、本発明のすべての実施形態が、説明される特徴、利点、または動作モードを含むことを必要とするわけではない。

## 【0013】

[0016] 本明細書で使用される専門用語は、特定の実施形態を説明するためのものにすぎず、本発明の実施形態を制限することは意図されていない。本明細書で使用される場合、単数形「a」、「an」、および「the」は、別途内容から明らかに示されていない限り、複数形もまた包含することが意図される。「備える」、「備えている」、「含む」、および／または「含んでいる」という用語は、本明細書で使用される場合、示される特徴、整数、ステップ、動作、要素、および／または構成要素の存在を特定するが、1つまたは複数の他の特徴、整数、ステップ、動作、要素、構成要素、および／またはそれらのグループの存在または追加を妨げないことはさらに理解されるだろう。

10

## 【0014】

[0017] さらに、多くの実施形態は、例えば、コンピューティングデバイスの要素によって行われるべき一連の動作（sequences of actions）の観点から説明される。特定の回路（例えば、特定用途集積回路（A S I C））、プログラム命令を実行する1つまたは複数のプロセッサ、または両者の組み合わせが、本明細書で説明される様々な動作を行いうることは認識されるだろう。追加的に、本明細書で説明されるこれら一連の動作は、実行に応じて関連プロセッサに本明細書で説明される機能を行わせるだろう対応するセットのコンピュータ命令を格納しているあらゆる形式のコンピュータ可読記憶媒体内で完全に具現化されるものと考えられる。ゆえに、本発明の様々な態様は、多数の異なる形式で具現化できること、それらはすべて、請求される主題の適用範囲内にあるものと予想されている。加えて、本明細書で説明される実施形態の各々について、そのようなあらゆる実施形態の対応する形式が、例えば、説明される動作を行う「ように構成された論理」として本明細書で説明されうる。

20

## 【0015】

30

[0018] 実施形態は、能動C M O S (Complimentary Metal Oxide Semiconductor) デバイスの最下層に相接して形成された、ナノワイヤトランジスタの1つまたは複数の最上能動層を備える。最上層は最上階層とも呼ばれ得、最下層は最下階層とも呼ばれうる。組み立て最終段階において、最下層または階層は、それが上に形成されるウエハ基板に相接しており、最上層または階層との関係でウエハ基板に最も近い。

## 【0016】

[0019] ナノワイヤトランジスタはジャンクションレストランジスタである。図1を参照すると、ソース - チャネル - ドレイン領域102、ゲート104、および、ゲート104とソース - チャネル - ドレイン領域102との間に配設された絶縁体106を備える簡略化された透視図100が例示されている。絶縁体106はH i g h - K 誘電体でありうる。この構造は、絶縁体膜108上に集積化されて示される。ソース - チャネル - ドレイン領域102がどのようにドープされるかに依存して、様々なタイプのナノワイヤトランジスタが実現されうる：pチャネル電界ピンチナノワイヤトランジスタ（p-channel field pinched nanowire transistor）110、nチャネル電界ピンチナノワイヤトランジスタ（n-channel field pinched nanowire transistor）112、n型反転チャネルナノワイヤトランジスタ（n-type inversion channel nanowire transistor）114、およびp型反転チャネルナノワイヤトランジスタ（p-type inversion channel nanowire transistor）116。これらナノワイヤトランジスタの各々のための半導体材料はシリコン（S i）であり得、ゲートは金属またはポリシリコンでありうる。

40

## 【0017】

50

[0020] ナノワイヤトランジスタ 110、112、114、および 116 によって示される図 (view) は、ナノワイヤトランジスタ 110 の簡略化された断面図である。これらの図同士の関係は、座標系 118 がナノワイヤトランジスタ 100 の向きを指し、座標系 120 がナノワイヤトランジスタ 110、112、114、および 116 の向きを指し、それによって、後者のナノワイヤトランジスタの図が、ナノワイヤトランジスタ 100 の y - z 平面のスライスを表していることに注意することによって示されている。

#### 【0018】

[0021] ナノワイヤトランジスタ 110 および 112 は蓄積モードで動作し、ナノワイヤトランジスタ 114 および 116 は反転モードで動作する。ナノワイヤトランジスタ 110 のチャネル 122 は、軽度にドープされた ( $p^+$ )  $p$  型半導体であり、ここでは、典型的なドーピング濃度は約  $10^{18} \text{ cm}^{-3}$  でありうる。他の実施形態は、例えば、 $10^{18} \text{ cm}^{-3}$  未満のドーピング濃度のような、異なるドーピング濃度を有しうる。ソースおよびドレイン領域 124 および 126 は、高度にドープされた ( $p^{++}$ )  $P$  型であり、ここでは、典型的なドーピング濃度は約  $10^{20} \text{ cm}^{-3}$  でありうる。他の実施形態は、例えば、 $10^{20} \text{ cm}^{-3}$  を超えるドーピング濃度のような、異なるドーピング濃度を有しうる。ナノワイヤトランジスタ 112 のチャネル 128 は、軽度にドープされた ( $n^+$ )  $n$  型であり、ここでは、典型的なドーピング濃度は約  $10^{18} \text{ cm}^{-3}$  でありうる。他の実施形態は、例えば、 $10^{18} \text{ cm}^{-3}$  未満のドーピング濃度のような、異なるドーピング濃度を有しうる。ソースおよびドレイン領域 130 および 132 は、高度にドープされた ( $n^{++}$ )  $n$  型であり、ここでは、典型的なドーピング濃度は約  $10^{20} \text{ cm}^{-3}$  でありうる。他の実施形態は、例えば、 $10^{20} \text{ cm}^{-3}$  を超えるドーピング濃度のような、異なるドーピング濃度を有しうる。10 20

#### 【0019】

[0022] ナノワイヤトランジスタ 114 のチャネル 134 はドープされておらず (ニュートラル、または、ゼロのドナー濃度であり)、ソースおよびドレイン領域 136 および 138 は、高度にドープされた ( $n^{++}$ )  $n$  型であり、ここでは、典型的なドーピング濃度は約  $10^{20} \text{ cm}^{-3}$  でありうる。他の実施形態は、例えば、 $10^{20} \text{ cm}^{-3}$  を超えるドーピング濃度のような、異なるドーピング濃度を有しうる。ナノワイヤトランジスタ 116 のチャネル 140 は、ドープされておらず、ソースおよびドレイン領域 142 および 144 は、高度にドープされた ( $p^{++}$ )  $p$  型であり、ここでは、典型的ドーピング濃度は約  $10^{20} \text{ cm}^{-3}$  でありうる。他の実施形態は、例えば、 $10^{20} \text{ cm}^{-3}$  を超えるドーピング濃度のような、異なるドーピング濃度を有しうる。30

#### 【0020】

[0023] ナノワイヤトランジスタの基礎となっている物理学の分野は研究が盛んに行われており、それらの動作は、開示される実施形態を理解および実施するために本明細書で詳細に説明される必要はない。

#### 【0021】

[0024] 図 2A および 2B は、ある実施形態に係るプロセスフローを表す。ステップ 200において、シリコンウェハ 202 は、様々な  $n$  型および  $P$  型領域を備える能動層 (最上階層) を形成するために、マスクされたイオン注入の方法によってドープされる。例示を容易にするために、 $n$  型領域 204 および  $p$  型領域 206 という 2 つのそのような領域だけが図 2A に例示される。絶縁体堆積または酸化は、能動層より上に薄い酸化物層 208 を形成する。高温度の熱活性化アニールは約 1000 度で行われる。40

#### 【0022】

[0025]  $n$  型領域 204 および  $P$  型領域 206 を備える能動層は、最終的な 3D 集積回路において、最上階層 264 (図 2B 参照) の一部を形成するだろう。より正確には、領域 204 および 206 を備える能動層の一部が、後述されるように、最上階層 264 の一部を形成するだろう。 $n$  型領域 204 および  $p$  型領域 206 は、例えば、約  $10^{18} \text{ cm}^{-3}$  のドナー濃度で、軽度にドープされる。これらの領域は、最上階層 264 におけるナノワイヤトランジスタのためのチャネル、ならびにこれらのナノワイヤトランジスタのソ50

ースおよびドレインの一部を形成するだろう。

**【0023】**

[0026] ステップ210では、開裂界面(cleavage interface)212を定めるためにイオン注入が行われる。界面212は、領域204および208を備える能動領域内にある。いくつかの実施形態では、イオンは水素イオンでありうる。

**【0024】**

[0027] ステップ214では、ウエハ202が裏返され、ウエハ216に酸化接合される。この酸化接合することは、例えば、400度以下の温度のような、比較的低い温度で行われる。例示を容易にするために、ステップ214は、実際には、ウエハ216に接合されたウエハ202を示していないが、接合手順では、ウエハ202における酸化物層208は、ウエハ216における酸化物層218に接合される。ウエハ216は、最終的な3D集積回路の基板として機能し、したがって、基板216と呼ばれるだろう。

10

**【0025】**

[0028] ウエハ216において形成されるものは、pMOSFET(金属酸化膜半導体電界効果トランジスタ)およびnMOSFETデバイスを備えるCMOS能動層であり、メタル層およびビアが、これらCMOSデバイスのソース、ドレイン、およびゲートへの様々な電気的接続を行う。例えば、3つのCMOSデバイスが基板216上に形成されて示されており、ここで、例えば、これらCMOSデバイスのうちの1つ221は、ソースおよびドレイン領域220および222、チャネル224、ゲート228、ならびにゲート228とチャネル224との間に配設された絶縁体226を備える。基板216上に形成されるCMOS集積回路の他の特徴は、例えばメタル層230のような1つまたはメタル層、および、例えばビア232のような、デバイス端子を1つまたはメタル層に接続するビアである。基板216上のCMOS能動層は、最終的な3D集積回路における最下階層233である。

20

**【0026】**

[0029] ステップ234に至ったとき、接合されたウエハは、このウエハが開裂界面212で分離されうるように、例えば300度以下の比較的低い温度に加熱される。開裂界面212よりも上のウエハ202の一部が除去されると、ウエハ202上に形成された領域204および206を備える能動層の薄膜(例えば、前に参照された「一部」)は、この時点で、基板216上の酸化物208に接合されたままとなる。

30

**【0027】**

[0030] 図2Bのステップ236において、酸化物分離トレント(en oxide isolation trench)が、最上階層能動層において形成される。例えば、4つの酸化物分離トレント238、240、242、および244が、ステップ236に例示される。結果として、熱開裂の後も基板216上に残っているP型領域206の一部は、p型領域246およびp型領域248へと分離されており、残りのn型領域204の一部は、n型領域205へと分離されている。

**【0028】**

[0031] 元々ウエハ202上に形成され、かつ、酸化物層208に接合された活性領域の一部は極めて薄いため、これは実質的に透明であり、したがって、ステップ236で例示された酸化物トレントを形成するために使用される様々なマスク、および、最上階層の製造における残りのステップで形成された特徴を位置合わせするときに光学的位置合わせを使用するのに実用的である。

40

**【0029】**

[0032] CMP(化学的機械研磨)平坦化の後、ステップ252において、ゲート絶縁体および電極堆積が行われ、ゲート画定(gate definition)およびスペーサ形成が続く。エピタキシャル成長中にその場(in-situ)でドープすることは、450度以下の温度で、選択的なソースおよびドレイン形成のために行われる。例えば、ステップ252において、ソースおよびドレイン領域124および126、ゲート104、およびゲート絶縁体106を有するpチャネル電界ピンチナノワイヤトランジスタ110が示される。

50

## 【0030】

[0033] ステップ252は、例えば、階層間ビア254のような階層間ビアを形成すること、例えば、ビア256のような、ナノワイヤトランジスタのソース、ドレイン、およびゲートへのビアを形成すること、および、例えば、メタル層258および260といったインターフェクトを形成するための1つまたは複数のメタル層といった、3D集積化を完了するために様々な製造段階を含む。メタル層およびナノワイヤトランジスタを保護する酸化物層262もまた形成される。酸化物層262はまた、追加の最上階層層のための付着面として機能し、ここでは、上述されたステップが繰り返される。

## 【0031】

[0034] いくつかの実施形態について、最後的な集積回路において最上階層の一部となるウエハ202における能動層がドープされていないか、または様々なアンドープ領域(undoped regions)を備えるステップ200が修正される。これは、図1に関連して説明されたナノワイヤトランジスタ114および116のような、反転モードで動作するナノワイヤトランジスタに導く。

10

## 【0032】

[0035] 図3は、上述されたプロセスフローを概説する。マスクされたn型およびp型イオン注入が、最上階層における能動層の一部としてn型またはp型領域を形成するために、第1のウエハに対して行われる(302)。n型およびp型領域は軽度にドープされており、ナノワイヤトランジスタのためのソース、ドレイン、チャネルを形成するために使用されるだろう。いくつかの実施形態では、ステップ302が行われないためにドーピングが存在しないか、または、いくつかの実施形態では、いくつかの領域はドープされておらず、他の領域は軽度にドープされる。

20

## 【0033】

[0036] 絶縁体または酸化物層が活性領域の上に形成され(304)、熱活性化およびアニール(306)が、イオン注入による結晶損傷を修復するために高い温度で行われる。水素イオン注入が、開裂界面を定めるために行われ(308)、第1のウエハは、低い温度で第2のウエハに酸化接合される。

## 【0034】

[0037] 前述されたように、第2のウエハは、すでに集積CMOS回路をその上に形成しており、ここでは、CMOS能動層が、3D集積回路の最下階層233となるであろう。第2のウエハは、3D集積回路のための基板として機能する。開裂界面は、最上階層におけるナノワイヤトランジスタのソース、ドレイン、およびチャネルを形成することとなる、以前に形成されたn型およびp型領域の一部を備える薄い能動層を最下階層233上に残して、第1のウエハ材料の大半が第2のウエハから除去されうるように熱活性化される(312)。

30

## 【0035】

[0038] 最上階層ナノワイヤトランジスタのためのゲート絶縁体および電極が製造される(314)。エピタキシャル成長中に低い温度でその場(in-situ)でドープすること(316)は、最上階層ナノワイヤトランジスタのためのソースおよびドレインを形成するために使用される。最上階層におけるコンタクト、階層内ビア、階層間ビア、および様々なメタル層が完成され、それらは、酸化物層によって保護される(318)。

40

## 【0036】

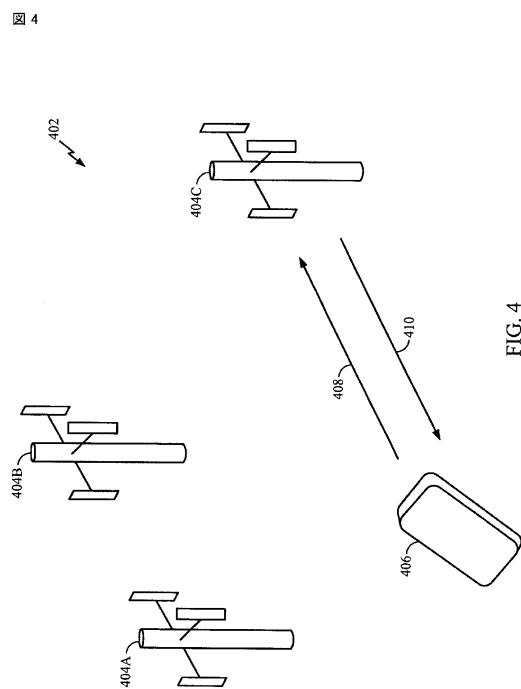

[0039] 図4は、実施形態が応用されうるワイヤレス通信システムを例示する。図4は、基地局404A, 404B、および404Cを備えるワイヤレス通信ネットワーク402を例示する。図4は、いわゆるスマートフォン、タブレット、またはセルラ電話ネットワークに適した何らかの他の種類の通信デバイスのようなモバイルセルラ通信デバイスでありうる406とラベル付された通信デバイスを示す。通信デバイス406は、モバイルである必要はない。図4の特定の例では、通信デバイス406は、基地局404Cに関連付けられたセル内に位置する。矢印408および410はそれぞれ、通信デバイス406が基地局404Cと通信するアップリンクチャネルおよびダウンリンクチャネルを図示す

50

る。

#### 【0037】

[0040] 実施形態は、例えば、通信デバイス406に、または基地局404Cに、あるいはその両方に関連付けられたデータ処理システムで使用されうる。図4は、本明細書で説明された実施形態が採用されうる多くの中の1つにすぎない応用例を例示する。

#### 【0038】

[0041] 説明された実施形態にしたがって作られた構造は、(1) TSV(シリコン貫通ビア)エリアペナルティおよびインターフェクト信号遅延の増加なしに3次元回路にトランジスタを詰め込みおよび接続すること、(2)トランジスタ階層ごとの平均的な金属層インターフェクト層を減らし、それによって、総合的なインターフェクトRC遅延を減らすこと(これは、従来のTSV方法では達成することが困難である)、(3)ウエハ(ダイ)接合位置合わせによる問題を緩和し、それによって、様々な階層(半導体層)を通して極めて正確かつ高い密度のビア接続を可能にすること、(4)数千の、さらには数万のビアを利用する多くのコア分散メモリーアーキテクチャを可能にすること(これは、従来のTSVワイヤドエンドアプローチでは容易に達成されることができない)、(5)各層に高性能基本デバイスを有する3次元ICおよびアーキテクチャ、ならびに(6)金属層使用量を削減し、欠陥密度を下げ、生産性を増やし、検査コストを減らすことでトランジスタ集積化コストを低減させること、を提供することが期待される。10

#### 【0039】

[0042] 最下階層層がCMOSデバイスを備える実施形態が説明されている。しかしながら、実施形態は、CMOSデバイスの最下階層の上に形成された、ナノワイヤトランジスタの最上階層に限られるわけではない。最下階層は、例えば、バイポーラデバイスのような、他のタイプのトランジスタを備えうる。さらに、いくつかの実施形態について、デバイスの最下階層である必要はなく、むしろ、ナノワイヤトランジスタは、基板に酸化接合され得、ここでは、接合のために使用される酸化物は絶縁体として機能する。20

#### 【0040】

[0043] 当業者は、情報および信号が様々な異なる技術および技法のいずれかを使用して表されうることを認識するだろう。例えば、上記説明の全体にわたって参照されうるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場または磁性粒子、光場または光粒子、あるいはこれらの任意の組み合わせによって表されうる。30

#### 【0041】

[0044] さらに、当業者は、本明細書に開示された実施形態に関連して説明された様々な実例となる論理ブロック、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、コンピュータソフトウェア、または両者の組み合わせとして実現されうることを認識するだろう。このハードウェアおよびソフトウェアの互換性を明確に例示するために、様々な実例となる構成要素、ブロック、モジュール、回路、およびステップが、概ねそれらの機能性の観点から上で説明されている。このような機能性がハードウェアとして実現されるかソフトウェアとして実現されるかは、特定の用途およびシステム全体に課せられる設計制約に依存する。当業者は、特定の用途ごとに様々な方法で、上で説明された機能性を実現しうるが、このような実現の決定は本発明の適用範囲からの逸脱の原因になるとして解釈されるべきではない。40

#### 【0042】

[0045] 本明細書に開示された実施形態に関連して説明された方法、シーケンス、および/またはアルゴリズムは、直接ハードウェアにおいて、プロセッサによって実行されるソフトウェアモジュールにおいて、またはこれら2つの組み合わせにおいて具現化されうる。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROM(登録商標)メモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られているその他の形式の記憶媒体に存在しうる。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み出し、記憶媒50

体に情報を書き込むことができるようにプロセッサに結合される。代替的に、記憶媒体はプロセッサに一体化されうる。

#### 【0043】

[0046] したがって、本発明の実施形態は、最新鋭のマイクロ加工環境内の単一の基板の上で層ごとにトランジスタおよびIC構成要素の連続的な集積化のための方法を具現化するコンピュータ可読媒体を含むことができる。したがって、本発明は、例示された例に限られるわけではなく、本明細書で説明された機能性を行うためのあらゆる手段が本発明の実施形態に含まれる。

#### 【0044】

[0047] 上の開示は、本発明の実例となる実施形態を示しているが、本発明の特許請求の範囲によって規定されるような発明の適用範囲から逸脱することなく、様々な変更および修正が本明細書で行われうることに留意されたい。本明細書で説明された発明の実施形態にしたがった方法請求項の機能、ステップ、および／または動作は、任意の特定の順序で行われる必要はない。さらに、本発明の要素は、単数形で説明または請求されうるが、単数形に限定することが明記されていない限り、複数形が予想される。

以下に本願発明の当初の特許請求の範囲に記載された発明を付記する。

#### [C 1]

方法であつて、

熱開裂を容易にするためにイオンを第1の半導体ウエハに注入することと、

前記第1の半導体ウエハを第2の半導体ウエハに酸化接合することと、

前記第1の半導体ウエハの一部が前記第2の半導体ウエハに酸化接合されたままとなるように熱開裂させるために前記第1の半導体ウエハを450度以下の温度に加熱することと、

前記第2の半導体ウエハに酸化接合された前記第1の半導体ウエハの前記一部において複数のナノワイヤトランジスタのためのソースおよびドレインを形成するために、450度以下の温度で、エピタキシャル成長中にその場でドープすることと、

を備える方法。

#### [C 2]

前記第2の半導体ウエハは最下階層を備え、前記最下階層は複数のトランジスタを備え、熱開裂させるために前記第1の半導体ウエハを450度以下の温度に加熱することは、前記第1の半導体ウエハの前記一部を、前記最下階層に酸化接合させたままにする、C 1に記載の方法。

#### [C 3]

前記複数のトランジスタは、pMOSFET (p型金属酸化膜半導体電界効果トランジスタ) およびnMOSFETを備える、C 2に記載の方法。

#### [C 4]

前記複数のナノワイヤトランジスタにおける各ナノワイヤトランジスタは、ドープされていないチャネルを有し、反転モードで動作する、C 3に記載の方法。

#### [C 5]

前記複数のナノワイヤトランジスタにおける各ナノワイヤトランジスタは、ドープされていないチャネルを有し、反転モードで動作する、C 1に記載の方法。

#### [C 6]

その場で前記ドープすることは、 $10^{20} \text{ cm}^{-3}$ 以上のドーピング濃度に前記ソースおよびドレインをドープすることをさらに備える、C 5に記載の方法。

#### [C 7]

その場で前記ドープすることは、 $10^{20} \text{ cm}^{-3}$ 以上のドーピング濃度に前記ソースおよびドレインをドープすることをさらに備える、C 1に記載の方法。

#### [C 8]

ドープ領域を形成するためにイオンを前記第1の半導体ウエハに注入することをさらに備え、前記ドープ領域は、前記第2の半導体ウエハに酸化接合された前記第1の半導体ウ

10

20

30

40

50

エハの前記一部を含む、C 1 に記載の方法。

[ C 9 ]

前記第2の半導体ウエハは最下階層を備え、前記最下階層は複数のトランジスタを備え、熱開裂を引き起こすために前記第1の半導体ウエハを450度以下の温度に加熱することは、前記第1の半導体ウエハの前記一部を、前記最下階層に酸化接合されたままにする、C 8 に記載の方法。

[ C 10 ]

前記複数のトランジスタは、pMOSFET (p型金属酸化膜半導体電界効果トランジスタ) およびnMOSFETを備える、C 9 に記載の方法。

[ C 11 ]

前記ドープ領域は、p型領域およびn型領域を含む、C 10 に記載の方法。

10

[ C 12 ]

前記ドープ領域は、 $10^{18} \text{ cm}^{-3}$ 以下の濃度にドープされる、C 10 に記載の方法。

[ C 13 ]

その場で前記ドープすることは、 $10^{20} \text{ cm}^{-3}$ 以上のドーピング濃度に前記ソースおよびドレインをドープすることをさらに備える、C 12 に記載の方法。

[ C 14 ]

前記ドープ領域は、前記ソースおよびドレインのものよりも低い濃度にドープされる、C 10 に記載の方法。

20

[ C 15 ]

前記ドープ領域は、p型領域およびn型領域を含む、C 8 に記載の方法。

[ C 16 ]

前記ドープ領域は、前記複数のナノワイヤトランジスタのためのチャネルを備える、C 8 に記載の方法。

[ C 17 ]

前記ドープ領域は、 $10^{18} \text{ cm}^{-3}$ 以下の濃度にドープされる、C 8 に記載の方法。

[ C 18 ]

その場で前記ドープすることは、 $10^{20} \text{ cm}^{-3}$ 以上のドーピング濃度に前記ソースおよびドレインをドープすることをさらに備える、C 17 に記載の方法。

30

[ C 19 ]

前記ドープ領域は、前記ソースおよびドレインのものよりも低い濃度にドープされる、C 8 に記載の方法。

[ C 20 ]

前記複数のナノワイヤトランジスタは蓄積モードで動作する、C 19 に記載の方法。

[ C 21 ]

装置であって、

シリコン基板と、

前記シリコン基板に酸化接合された最上階層と

を含み、前記最上階層は、複数のナノワイヤトランジスタを備え、前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタは、ソースと、ドレインと、前記ソースおよび前記ドレインのものよりも低いドーピング濃度を有するチャネルとを備える、装置。

40

[ C 22 ]

前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタのための前記ソースおよびドレインは、450度以下の温度で、その場のエピタキシャル成長によって形成される、C 21 に記載の装置。

[ C 23 ]

前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタのための前記ソースおよびドレインは、 $10^{20} \text{ cm}^{-3}$ 以上のドーピング濃度を有する、C 22 に記載の装置

。

50

## [ C 2 4 ]

前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタのための前記チャネルは、ゼロのドーピング濃度を有する、C 2 1 に記載の装置。

## [ C 2 5 ]

前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタのための前記ソースおよびドレインは、 $10^{20} \text{ C m}^{-3}$  以上のドーピング濃度を有する、C 2 1 に記載の装置

。

## [ C 2 6 ]

前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタの前記チャネルは、 $10^{18} \text{ C m}^{-3}$  以下のドーピング濃度を有する、C 2 5 に記載の装置。

10

## [ C 2 7 ]

前記複数のナノワイヤトランジスタの各チャネルは、ゼロのドーピング濃度を有する、C 2 6 に記載の装置。

## [ C 2 8 ]

前記シリコン基板上に形成された最下階層、ここで、前記最上階層は前記最下階層に酸化接合されており、前記最下階層は、複数のトランジスタを備える、と、

前記最下階層における前記複数のトランジスタのうちの少なくとも 1 つのトランジスタを、前記最上階層における前記複数のナノワイヤトランジスタの少なくとも 1 つのナノワイヤトランジスタに接続する複数のインターフェクトと、

をさらに備える、C 2 1 に記載の装置。

20

## [ C 2 9 ]

前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタのための前記ソースおよびドレインは、450 度以下の温度で、その場のエピタキシャル成長によって形成される、C 2 8 に記載の装置。

## [ C 3 0 ]

前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタのための前記ソースおよびドレインは、 $10^{20} \text{ C m}^{-3}$  以上のドーピング濃度を有する、C 2 9 に記載の装置

。

## [ C 3 1 ]

前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタのための前記チャネルは、ゼロのドーピング濃度を有する、C 3 0 に記載の装置。

30

## [ C 3 2 ]

前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタのための前記チャネルは、 $10^{18} \text{ C m}^{-3}$  以下のドーピング濃度を有する、C 3 0 に記載の装置。

## [ C 3 3 ]

前記複数のトランジスタは、p MOSFET ( p 型金属酸化膜半導体電界効果トランジスタ ) および n MOSFET を備える、C 2 8 に記載の装置。

## [ C 3 4 ]

前記シリコン基板と前記最上階層とを備える集積回路と、

前記集積回路を備えるセルラ電話と、

をさらに備える、C 2 1 に記載の装置。

40

## [ C 3 5 ]

前記シリコン基板と前記最上階層とを備える集積回路と、

前記集積回路を備える基地局と、

をさらに備える、C 2 1 に記載の装置。

## [ C 3 6 ]

装置であって、

シリコン基板と、

前記シリコン基板上に形成された最下階層、ここで、前記最下階層は複数のトランジスタを備える、と、

50

前記最下階層に酸化接合された最上階層、ここで、前記最上階層は複数のナノワイヤトランジスタを備え、前記複数のナノワイヤトランジスタの各ナノワイヤトランジスタは、ソースと、ドレインと、前記ソースおよび前記ドレインのものよりも低いドーピング濃度を有するチャネルとを備える、と、

接続するための手段、ここで、前記接続するための手段は、前記最下階層における前記複数のトランジスタの少なくとも1つのトランジスタを、前記最上階層における前記複数のナノワイヤトランジスタの少なくとも1つのナノワイヤトランジスタに接続するためのものである、と、

を備える装置。

【C 37】

10

方法であって、

イオンを注入するための手段、前記イオンを注入するための手段は、第1の半導体ウエハにおける熱開裂を容易にするためのものである、と、

結合するための手段、ここで、前記結合するための手段は、前記第1の半導体ウエハを第2の半導体ウエハに酸化接合するためのものであり、前記第2の半導体ウエハは、トランジスタの最下階層を備える、と、

加熱するための手段、ここで、前記加熱するための手段は、前記第1の半導体ウエハの一部が前記最下階層に酸化接合されたままとなるように熱開裂を引き起こすために前記第1の半導体ウエハを450度以下の温度に加熱するためのものである、と、

ドープするための手段、ここで、前記ドープするための手段は、前記最下階層に酸化接合された前記第1の半導体ウエハの前記一部における複数のナノワイヤトランジスタのためのソースおよびドレインを形成するために、450度以下の温度で、エピタキシャル成長中にその場でドープするためのものである、と、

を備える方法。

【図1】

【図2A】

FIG. 2A

【図2B】

FIG. 2B

【図3】

FIG. 3

【図4】

FIG. 4

## フロントページの続き

| (51)Int.Cl. |                   | F I    |                |

|-------------|-------------------|--------|----------------|

| H 01 L      | 21/8238 (2006.01) | H 01 L | 29/78 6 1 6 L  |

| H 01 L      | 27/092 (2006.01)  | H 01 L | 21/02 B        |

| H 01 L      | 21/336 (2006.01)  | H 01 L | 21/205         |

| H 01 L      | 21/02 (2006.01)   | H 01 L | 21/20          |

| H 01 L      | 21/205 (2006.01)  | H 01 L | 27/092 C       |

| H 01 L      | 21/20 (2006.01)   | H 01 L | 27/088 3 3 1 A |

| H 01 L      | 29/06 (2006.01)   | H 01 L | 29/78 6 1 3 A  |

|             |                   | H 01 L | 29/78 6 2 7 D  |

|             |                   | H 01 L | 29/78 6 2 1    |

|             |                   | H 01 L | 29/78 6 1 8 F  |

|             |                   | H 01 L | 29/06 6 0 1 N  |

(72)発明者 ドゥ、ヤン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 市川 武宜

(56)参考文献 米国特許出願公開第2010/0259296(US, A1)

国際公開第2010/098151(WO, A1)

特表2012-513118(JP, A)

米国特許出願公開第2004/0036126(US, A1)

米国特許出願公開第2013/0026539(US, A1)

米国特許出願公開第2010/0193770(US, A1)

米国特許出願公開第2012/0305893(US, A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 27 / 0 0

H 01 L 21 / 0 2

H 01 L 21 / 2 0

H 01 L 21 / 2 0 5

H 01 L 21 / 3 3 6

H 01 L 21 / 8 2 2

H 01 L 21 / 8 2 3 8

H 01 L 27 / 0 4

H 01 L 27 / 0 8 8

H 01 L 27 / 0 9 2

H 01 L 29 / 0 6

H 01 L 29 / 7 8 6