(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-148746

(P2005-148746A)

(43) 公開日 平成17年6月9日(2005.6.9)

(51) Int.CI.<sup>7</sup>

F 1

テーマコード(参考)

**G09G 3/28**

G09G 3/28

H

5C058

**G09G 3/20**

G09G 3/20

612U

5C080

**HO4N 5/66**

G09G 3/20

622C

G09G 3/20

641E

G09G 3/20

642E

審査請求 未請求 請求項の数 22 O L (全 24 頁) 最終頁に続く

(21) 出願番号

特願2004-329451 (P2004-329451)

(22) 出願日

平成16年11月12日 (2004.11.12)

(31) 優先権主張番号

2003-079783

(32) 優先日

平成15年11月12日 (2003.11.12)

(33) 優先権主張国

韓国 (KR)

(71) 出願人

590001669

エルジー電子株式会社

大韓民国、ソウル特別市永登浦区汝矣島洞

20

(74) 代理人

110000165

グローバル・アイピー東京特許業務法人

(72) 発明者

カン ソンホ

大韓民国、ダエグ、ブクーク、タエジョン

ードン 442 ベオンジ、ウバン 3チ

ヤ 105-903

(72) 発明者

ユン サンジン

大韓民国、ギョンサンブクード、チルゴク

ーク、セオクジエオクミョン、ナムユ

ルーリ 710、ウバン シンチョンジ

タウン 103-1802

最終頁に続く

(54) 【発明の名称】プラズマディスプレイパネルの初期化を制御するための方法および装置

## (57) 【要約】

【課題】コントラストを改善し、リセット期間を減らすようにしたPDPの初期化制御方法及び装置を提供する。

【解決手段】本発明に係るプラズマディスプレイパネルの初期化制御方法及び装置は、1フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割し、前記入力映像の平均明るさが以前映像の平均明るさより低い時、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号の電圧が低いサブフィールドの数を増加させる。本発明に係るPDPの初期化制御方法及び装置は、APLが基準値より低い時及び/または高い時、上昇ランプ信号を省略するか、そのセットアップ電圧を低下させる。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

1フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割する段階と、

前記入力映像の平均明るさが以前映像の平均明るさより低い時、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号の電圧が低いサブフィールドの数を増加させる段階と、を含むことを特徴とするプラズマディスプレイパネルの初期化制御方法。

**【請求項 2】**

1フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割する段階と、

前記入力映像の平均明るさが所定の基準値であれば、前記サブフィールドのそれぞれで前記初期化信号として第1信号を用いてセルの初期化を行う段階と、

前記入力映像の平均明るさが前記基準値より低ければ、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号として前記第1信号の電圧より低い第2信号を用いるサブフィールドの数を増加させる段階と、

前記入力映像の平均明るさが前記基準値より高ければ、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号として前記第1信号の電圧より低い第2信号を用いるサブフィールドの数を増加させる段階と、を含むことを特徴とするプラズマディスプレイパネルの初期化制御方法。

**【請求項 3】**

前記初期化信号は、電圧が徐々に上昇して弱放電で書き込み放電を起こすためのランプ信号であることを特徴とする請求項1または2記載のプラズマディスプレイパネルの初期化制御方法。

**【請求項 4】**

入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割駆動されるプラズマディスプレイパネルを初期化する初期化制御装置であって、

前記入力映像の平均明るさを算出するA P L算出部と、

前記A P L算出部によって算出された前記入力映像の平均明るさが以前映像の平均明るさより低い時、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号の電圧が低いサブフィールドの数を増加させる初期化制御部と、を備えることを特徴とするプラズマディスプレイパネルの初期化制御装置。

**【請求項 5】**

入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割駆動されるプラズマディスプレイパネルを初期化する初期化制御装置であって、

前記入力映像の平均明るさを算出するA P L算出部と、

前記A P L算出部によって算出された前記入力映像の平均明るさが所定の基準値であれば、前記サブフィールドのそれぞれで前記初期化信号として第1信号を前記プラズマディスプレイパネルに供給する第1初期化制御部と、

前記入力映像の平均明るさが前記基準値より低ければ、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号として前記第1信号の電圧より低い第2信号を用いるサブフィールドの数を増加させる第2初期化制御部と、

前記入力映像の平均明るさが前記基準値より高ければ、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号として前記第1信号の電圧より低い第2信号を用いるサブフィールドの数を増加させる第3初期化制御部と、を備えることを特徴とするプラズマディスプレイパネルの初期化制御装置。

10

20

30

40

50

**【請求項 6】**

前記初期化信号は、電圧が徐々に上昇して弱放電で書き込み放電を起こすためのランプ信号であることを特徴とする請求項 4 または 5 記載のプラズマディスプレイパネルの初期化制御装置。

**【請求項 7】**

前記初期化制御部は、

前記初期化信号を発生させる初期化信号発生部と、

前記 APL によって算出された平均明るさ信号に応答して前記初期化信号発生部を制御するための制御部と、を備えることを特徴とする請求項 4 または 5 記載のプラズマディスプレイパネルの初期化制御装置。

10

**【請求項 8】**

(表 1 )

1 フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能である複数のサブフィールドに時分割する段階と、

前記入力映像の平均明るさが低下するほど、前記初期化信号を省略するサブフレーム数を増加する段階と、

を含むことを特徴とするプラズマディスプレイパネルの初期化制御方法。

**【請求項 9】**

前記初期化信号を省略するサブフレーム数は、最上位ビット側から増加することを特徴とする、請求項 8 に記載のプラズマディスプレイパネルの初期化制御方法。

20

**【請求項 10】**

(表 2 )

1 フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能である複数のサブフィールドに時分割する段階と、

前記入力映像の平均明るさが所定の基準値範囲であれば 1 フレームの全サブフィールドで初期化信号を印加する段階と、

前記入力映像の平均明るさが所定の基準値範囲から低くなるほど、初期化信号を省略するサブフレーム数を増加させる段階と、

前記入力信号の平均の明るさが所定の基準値範囲から高くなるほど、初期化信号を省略するサブフレーム数を増加させる段階と、

を含むことを特徴とするプラズマディスプレイパネルの初期化制御方法。

30

**【請求項 11】**

前記入力映像の平均明るさが所定の基準値範囲から低くなるほど、初期化信号を省略するサブフレーム数を最上位ビット側から増加させ、前記入力映像の平均明るさが所定の基準値範囲から高くなるほど、初期化信号を省略するサブフレーム数を最下位ビット側から増加させることを特徴とする、請求項 10 に記載のプラズマディスプレイパネルの初期化制御方法。

**【請求項 12】**

(表 3 )

1 フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号の電圧が調節可能である複数のサブフィールドに時分割する段階と、

前記入力映像の平均明るさが低下するほど前記初期化信号を低下させる段階と、

を含むことを特徴とするプラズマディスプレイパネルの初期化制御方法。

40

**【請求項 13】**

1 フレームの最初のサブフィールドで第 1 信号の初期化信号を印加する段階をさらに含み、

前記初期化信号を低下させる段階では、前記最初のサブフィールド以外のサブフィールドにおいて、前記第 1 信号の電圧よりも低い電圧の第 2 信号の初期化信号が印加され、前記入力映像の平均明るさが低下するほど前記第 2 信号が低下されることを特徴とする、請求項 12 に記載のプラズマディスプレイパネルの初期化制御方法。

50

**【請求項 14】****(表4)**

1フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号の電圧が調節可能である複数のサブフィールドに時分割する段階と、

前記入力映像の平均明るさが所定値より低下するほど前記初期化信号を低下させ、前記入力映像の平均明るさが所定値より増加するほど前記初期化信号を低下させる段階と、を含むことを特徴とするプラズマディスプレイパネルの初期化制御方法。

**【請求項 15】**

1フレームの最初のサブフィールドで第1信号の初期化信号を印加する段階をさらに含み、

前記初期化信号を低下させる段階では、前記最初のサブフィールド以外のサブフィールドにおいて、前記第1信号の電圧よりも低い電圧の第2信号の初期化信号が印加され、前記入力映像の平均明るさが所定値より低下するほど前記第2信号の電圧を低下させ前記入力映像の平均明るさが所定値より増加するほど前記第2信号の電圧を低下させることを特徴とする、請求項14に記載のプラズマディスプレイパネルの初期化制御方法。

**【請求項 16】****(表5、表6)**

1フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割する段階と、

前記入力信号の平均の明るさが低くなるほど、前記初期化信号を省略又は低下するサブフィールド数を増加させるか、或いは、前記初期化信号を低下させる段階と、を含むことを特徴とするプラズマディスプレイパネルの初期化制御方法。

**【請求項 17】****(表5)**

前記初期化信号を省略又は低下するサブフィールド数を増加させるか、或いは、前記初期化信号を低下させる段階は、

前記入力映像の平均明るさが所定値未満である場合には、前記入力信号の平均の明るさが低下するほど、前記初期化信号を低下させ、前記入力映像の平均明るさが所定値以上である場合には、前記入力信号の平均の明るさが増加するほど、前記初期化信号を省略又は低下するサブフィールド数を減少させることを特徴とする、請求項16に記載のプラズマディスプレイパネルの初期化制御方法。

**【請求項 18】****(表6)**

前記初期化信号を省略するサブフィールド数を増加させるか、又は、前記初期化信号を低下させる段階は、

前記入力映像の平均明るさが所定値未満である場合には、前記入力信号の平均の明るさが低下するほど、前記初期化信号を省略又は低下するサブフィールド数を増加させる段階と、

前記入力映像の平均明るさが所定値以上である場合には、前記入力信号の平均の明るさが増加するほど、前記初期化信号を高くする段階と、

を含むことを特徴とするプラズマディスプレイパネルの初期化制御方法。

**【請求項 19】**

1フレームの最初のフレームにおいて第1信号の初期化信号を印加する段階をさらに含み、

前記初期化信号を省略又は低下するサブフィールド数を増加させるか、或いは、前記初期化信号を低下させる段階は、前記最初のフレーム以外のフレームで実行され、前記第1信号の電圧よりも低い第2信号が初期化信号として印加されることを特徴とする、請求項16乃至18の何れかに記載のプラズマディスプレイパネルの初期化制御方法。

**【請求項 20】**

10

20

30

40

50

(表7)

1フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割する段階と、

前記入力映像の平均明るさが前記第1所定値から前記第1所定値未満の第2所定値まで低くなるほど、前記初期化信号を省略又は低下するサブフィールド数を増加する段階と、

前記入力映像の平均明るさが前記第2所定値より低くなるほど、前記初期化信号を低下させる段階と、

前記入力映像の平均明るさが前記第1所定値から前記第1所定値より大きい第3所定値まで高くなるほど、前記初期化信号を省略又は低下するサブフィールド数を増加する段階と、

前記入力映像の平均明るさが前記第3所定値より高くなるほど、前記初期化信号を低下させる段階と、

を含むことを特徴とするプラズマディスプレイパネルの初期化制御方法。

#### 【請求項21】

前記入力映像の平均明るさが前記第1所定値から前記第1所定値未満の第2所定値まで低くなるほど、前記初期化信号を省略又は低下するサブフィールド数を増加する段階、及び、前記入力映像の平均明るさが前記第1所定値から前記第1所定値より大きい第3所定値まで高くなるほど、前記初期化信号を省略又は低下するサブフィールド数を増加する段階は、最上位ビット側から前記初期化信号を省略又は低下するサブフィールド数を増加することを特徴とする、請求項20に記載のプラズマディスプレイパネルの初期化制御方法。

#### 【請求項22】

1フレームの最初のフレームにおいて第1信号の初期化信号を印加する段階をさらに含み、

前記各段階は、前記最初のフレーム以外のフレームで実行されることを特徴とする、請求項20に記載のプラズマディスプレイパネルの初期化制御方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、プラズマディスプレイパネルに係り、特に、プラズマディスプレイパネルの初期化を制御するための方法及び装置に関する。

#### 【背景技術】

#### 【0002】

プラズマディスプレイパネル(Plasma Display Panel:以下、「PDP」という)は、ガス放電によって発生する紫外線が蛍光体を励起させると同時に蛍光体から発生する可視光線を用いて画像を表示する。かかるPDPは、今まで表示手段の主軸を成してきた陰極線管(Cathode Ray Tube: CRT)に比べて厚さが薄くて軽く、かつ高鮮明/大画面の具現が可能であるという長所がある。

#### 【0003】

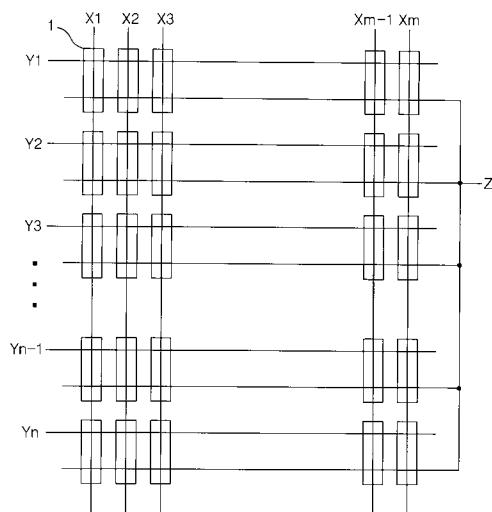

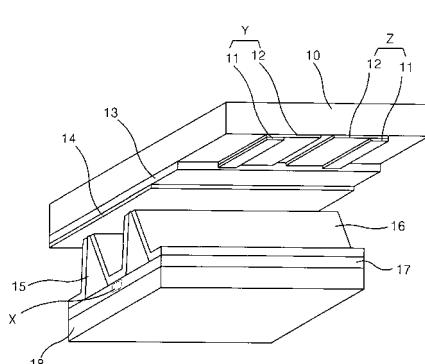

図1は、従来のプラズマディスプレイパネルを概略的に示す平面図であり、図2は、図1に示したセルの構造を詳しく示す斜視図である。図1及び図2を参照すれば、3電極交流面放電型PDPは、上部基板10上に形成されたスキャン電極Y1~Ynおよびサステイン電極Zと、下部基板18上に形成されたアドレス電極X1~Xmと、を備える。

#### 【0004】

このPDPの放電セル1は、スキャン電極Y1~Yn、サステイン電極Zおよびアドレス電極X1~Xmの交差部に形成される。スキャン電極Y1~Ynとサステイン電極Zのそれぞれは、透明電極12と、透明電極12の線幅より小さい線幅を有し、透明電極の一側端に形成される金属バス電極11と、を含む。

#### 【0005】

10

20

30

40

50

透明電極 12 は、通常インジウムスズ酸化物 (Indium-Tin-Oxide: ITO) で上部基板 10 上に形成される。金属バス電極 11 は、通常金属で透明電極 12 上に形成され、高抵抗の透明電極 12 による電圧降下を減らす役割を果たす。スキャン電極 Y1 ~ Yn とサステイン電極 Z が形成された上部基板 10 には、上部誘電体層 13 と保護膜 14 が積層される。上部誘電体層 13 上にはプラズマ放電時に発生した壁電荷が蓄積される。保護膜 14 は、プラズマ放電時に発生したスペッタリングによる電極 Y1 ~ Yn、Z と上部誘電体層 13 の損傷を防止すると共に 2 次電子の放出効率を高める。この保護膜 14 としては通常酸化マグネシウム MgO が利用される。

## 【0006】

アドレス電極 X1 ~ Xm は、スキャン電極 Y1 ~ Yn 及びサステイン電極 Z と交差する方向に下部基板 18 上に形成される。下部基板 18 上には下部誘電体層 17 と隔壁 15 が形成される。下部誘電体層 17 と隔壁 15 の表面には蛍光体層 16 が形成される。隔壁 15 は、アドレス電極 X1 ~ Xm に並んで形成され、放電セルを物理的に区分し、隣接した放電セル 1 間の電気的、光学的干渉を遮断する。蛍光体層 16 は、プラズマ放電時に発生した紫外線によって励起・発光して赤色、緑色または青色のいずれか一つの可視光線を発生させる。

## 【0007】

上 / 下部基板 10、18 と隔壁 15 との間に設けられた放電セル 1 の放電空間には、放電のための He + Xe、Ne + Xe、He + Ne + Xe などの不活性混合ガスが注入される。

## 【0008】

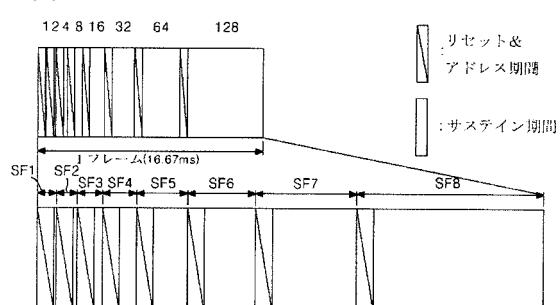

このような PDP は、画像の階調 (Gray Level) を具現するために、一つのフレームを発光回数の異なる複数のサブフィールドに分けて時分割駆動している。各サブフィールドは、放電を一様に起こすためのリセット期間と、放電セルを選択するためのアドレス期間と、放電回数によって階調を具現するサステイン期間と、に分けられる。

## 【0009】

図 3 は、1 フレーム期間を複数のサブフィールドに時分割したサブフィールドパターンを示す図である。256 階調で画像を表示しようとする場合、1/60 秒に該当するフレーム期間 (16.67 ms) は、図 3 のように 8 個のサブフィールド SF1 ~ SF8 に分けられる。また、8 個のサブフィールド SF1 ~ SF8 のそれぞれは、リセット期間、アドレス期間及びサステイン期間にさらに分けられる。

## 【0010】

ここで、各サブフィールド SF1 ~ SF8 のリセット期間及びアドレス期間は各サブフィールド毎に同一である反面、サステイン期間及びその放電回数はサステインパルスの数に比例して各サブフィールド SF1 ~ SF8 において  $2^n$  (但し、 $n = 0, 1, 2, 3, 4, 5, 6, 7$ ) の割合で増加する。このように各サブフィールド SF1 ~ SF8 におけるサステイン期間が変わることにより、画像の階調を具現できるようになる。

## 【0011】

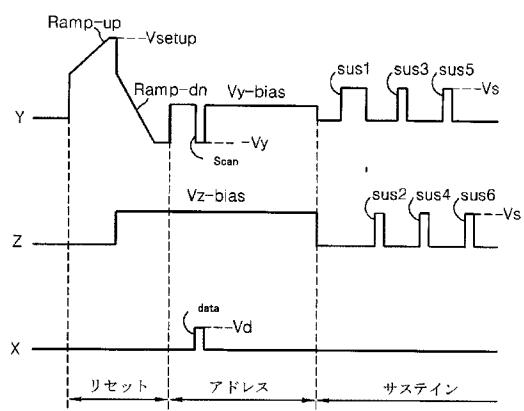

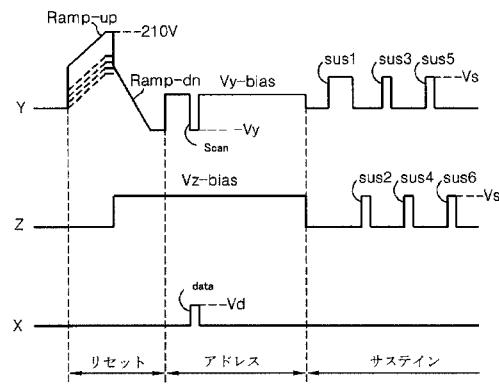

図 4 は、図 1 のようなプラズマディスプレイパネルを駆動するための従来の駆動信号を示す波形図であり、各サブフィールド SF1 ~ SF8 で PDP の電極に供給される駆動信号を示す。

## 【0012】

図 4 を参照すれば、リセット期間の初期にはすべてのスキャン電極 Y に上昇ランプ信号 Ramp-up が同時に供給される。これと同時に、サステイン電極 Z とアドレス電極 X には 0 [V] が供給される。上昇ランプ信号 Ramp-up によって全画面のセル内において、スキャン電極 Y とアドレス電極 X との間と、スキャン電極 Y とサステイン電極 Z との間とには、弱放電で書き込み放電が起こる。この書き込み放電によってアドレス電極 X およびサステイン電極 Z 上には正極性 (+) の壁電荷が蓄積され、スキャン電極 Y 上には負極性 (-) の壁電荷が蓄積される。

## 【0013】

10

20

30

40

50

このような上昇ランプ信号 R a m p - u p が供給された後、その上昇ランプ信号 R a m p - u p のピーク電圧より低いサステイン電圧 V s から落ち始めて負極性のスキャンバイアス電圧 - V y まで落ちる降下ランプ信号 R a m p - d n が、スキャン電極 Y に同時に供給される。これと同時に、サステイン電極 Z にはサステイン電圧 V s のバイアス電圧 V z - b i a s が供給され、アドレス電極 X には 0 [ V ] が供給される。このように降下ランプ信号 R a m p - d n が供給されるとき、スキャン電極 Y とサステイン電極 Z との間と、スキャン電極 Y とアドレス電極 Z との間とに、弱放電で消去放電が起こる。このような消去放電により、書き込み放電によって形成された壁電荷の中から、アドレス放電に不要な過剰壁電荷が消去される。

## 【0014】

10

アドレス期間では、負極性スキャンパルス s c a n がスキャン電極 Y に順次供給されると同時に、スキャンパルス s c a n に同期される正極性のデータパルス d a t a がアドレス電極 X に供給される。スキャンパルス s c a n とデータパルス d a t a との電圧差とりセット期間に生成された壁電圧とが加えられることにより、データパルス d a t a が供給されるセル内ではアドレス放電が発生する。アドレス放電によって選択されたセル内には、サステイン電圧 V s が供給されるときに放電が起りうるようにする程度の壁電荷が形成される。このアドレス期間中にサステイン電極 Z には正極性直流電圧 Z d c が供給される。

## 【0015】

20

サステイン期間では、スキャン電極 Y とサステイン電極 Z に交互にサステインパルス s u s が供給される。そうすると、アドレス放電によって選択された放電セル 1 は放電セル 1 内の壁電圧とサステインパルス s u s とが加えられることにより、各サステインパルス s u s 1 ~ s u s 6 が供給される度にスキャン電極 Y とサステイン電極 Z との間でサステイン放電、すなわち表示放電が発生する。サステインパルス s u s 1 ~ s u s 6 の個数は、各サブフィールド S F 1 ~ S F 8 に付与された輝度加重値によってサブフィールド毎に異なるように設定される。

## 【0016】

30

サステイン放電が終了した後には、図示しない消去ランプ信号がスキャン電極 Y やサステイン電極 Z に供給される。消去ランプ信号はセル内で弱放電で消去放電を起こすことにより、サステイン放電によって生成された壁電荷を消去させる。

## 【0017】

30

ところが、従来の P D P は、非表示期間に発生する光のためにコントラスト比 ( contrast ratio ) が低いという短所がある。例えば、各サブフィールド毎に割り当てられるリセット期間中に全放電セル 1 内で数回発生する放電、特に上昇ランプ信号 R a m p - u p によって発生する書き込み放電またはセットアップ放電に伴って光が発生し、その光によってブラック輝度が高くなる。

## 【0018】

40

また、従来の P D P は、リセット期間が各サブフィールド毎に割り当てられるので、リセット期間の分だけのアドレス期間やサステイン期間が限定されるという問題点がある。例えば、各サブフィールド毎に割り当てられるリセット期間が原因で発生する擬似輪郭ノイズ ( Contour noise ) などの画質不良要因を減らすために、サブフィールドの追加や輝度の増加を必要とするが、このためのサステインパルスの追加が困難である。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0019】

本発明は、かかる従来の問題点を解決するためのもので、その目的は、コントラストを改善し、リセット期間を減らすようにした P D P の初期化制御方法及び装置を提供する。

## 【課題を解決するための手段】

## 【0020】

50

本発明の実施形態に係る P D P の初期化制御方法は、1 フレーム期間を、入力映像の平

均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割する段階と、前記入力映像の平均明るさが以前映像の平均明るさより低い時、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号の電圧が低いサブフィールドの数を増加させる段階と、を含む。

【0021】

本発明の他の実施形態に係るPDPの初期化制御方法は、1フレーム期間を、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割する段階と、前記入力映像の平均明るさが所定の基準値であれば、前記サブフィールドのそれぞれで前記初期化信号を用いてセルの初期化を行う段階と、前記入力映像の平均明るさが前記基準値より低ければ、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号の電圧が低いサブフィールドの数を増加させる段階と、前記入力映像の平均明るさが前記基準値より高ければ、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号の電圧が低いサブフィールドの数を増加させる段階と、を含む。

【0022】

前記初期化信号は、電圧が徐々に上昇して弱放電で書き込み放電を起こすためのランプ信号であることを特徴とする。

【0023】

本発明の実施形態に係るPDPの初期化制御装置は、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割駆動されるPDPと、前記入力映像の平均明るさを算出するAPL算出部と、前記APL算出部によって算出された前記入力映像の平均明るさが以前映像の平均明るさより低い時、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号の電圧が低いサブフィールドの数を増加させる初期化制御部と、を備える。

【0024】

本発明の他の実施形態に係るPDPの初期化制御装置は、入力映像の平均明るさによって初期化放電を起こすための初期化信号が省略可能であるか、前記初期化信号の電圧が調節可能である複数のサブフィールドに時分割駆動されるPDPと、前記入力映像の平均明るさを算出するAPL算出部と、前記APL算出部によって算出された前記入力映像の平均明るさが所定の基準値であれば、前記サブフィールドのそれぞれで前記初期化信号を前記PDPに供給する第1初期化制御部と、前記入力映像の平均明るさが前記基準値より低ければ、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号の電圧が低いサブフィールドの数を増加させる第2初期化制御部と、前記入力映像の平均明るさが前記基準値より高ければ、前記初期化信号が省略されるサブフィールドの数を増加させるか、前記初期化信号の電圧が低いサブフィールドの数を増加させる第3初期化制御部と、を備える。

【0025】

前記初期化信号は、電圧が徐々に上昇して弱放電で書き込み放電を起こすためのランプ信号である。

【0026】

前記初期化制御部は、前記初期化信号を発生させる初期化信号発生部と、前記APLによって算出された平均明るさ信号に応答して前記初期化信号発生部を制御するための制御部と、を備える。

【発明の効果】

【0027】

本発明に係るPDPの初期化制御方法及び装置は、APLが基準値より低い時及び/または高い時、上昇ランプ信号を省略するか、そのセットアップ電圧を低下させる。その結果、本発明は、初期化放電数を減らすか初期化放電を弱くして、放電時に伴う光放出量を

10

20

30

40

50

減らすことにより、ブラック輝度を低めてコントラスト比を向上させ且つリセット期間を減らすことができる。

【発明を実施するための最良の形態】

【0028】

以下、本発明の実施形態を添付図を参照して詳しく説明する。

【0029】

(1) 第1実施形態

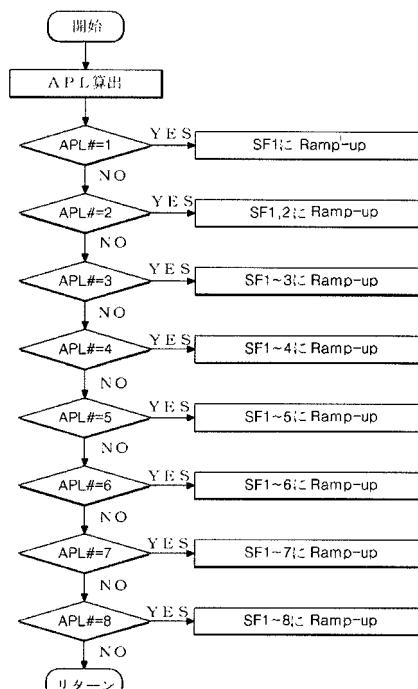

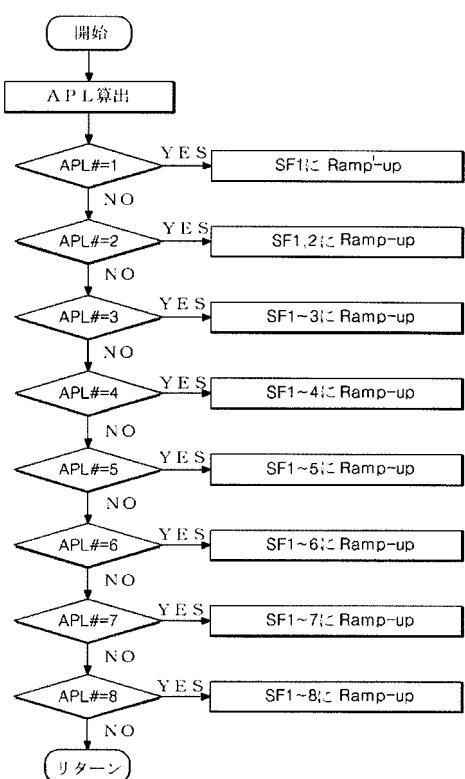

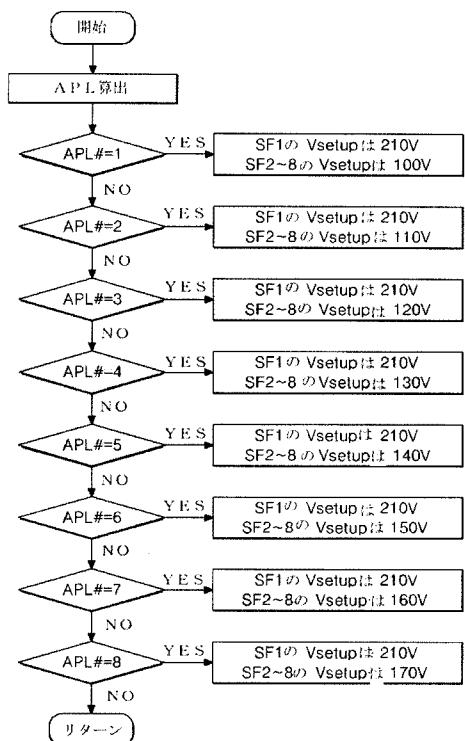

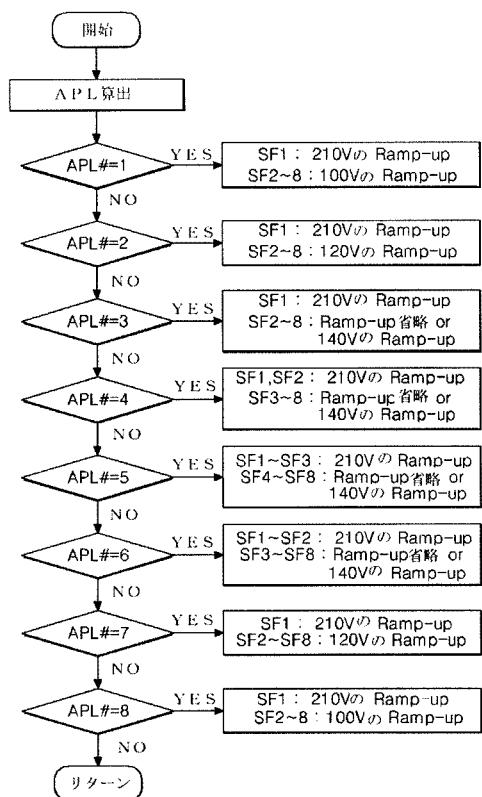

図5は、本発明の第1実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。

【0030】

本発明の第1実施形態に係るPDPの初期化制御方法は、1画面の平均輝度レベル(Average Picture Level:以下、「APL」という)を算出し、そのAPLが低いほど高い加重値のサブフィールドにおいて上昇ランプ信号Ramp-upをより多く省略する。

【0031】

次の表1と図5は、サブフィールド8個で最大1024階調まで表現できるサブフィールドパターンを仮定し、本発明の第1実施形態に係るPDPの初期化制御方法において上昇ランプ信号Ramp-upの省略可否を示す。

【0032】

【表1】

10

20

30

|      | SF1<br>(1 k) | SF2<br>(2 k) | SF3<br>(4 k) | SF4<br>(8 k) | SF5<br>(16 k) | SF6<br>(32 k) | SF7<br>(64 k) | SF8<br>(128 k) |

|------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|----------------|

| APL1 | あり           | なし           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL2 | あり           | あり           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL3 | あり           | あり           | あり           | なし           | なし            | なし            | なし            | なし             |

| APL4 | あり           | あり           | あり           | あり           | なし            | なし            | なし            | なし             |

| APL5 | あり           | あり           | あり           | あり           | あり            | なし            | なし            | なし             |

| APL6 | あり           | あり           | あり           | あり           | あり            | あり            | なし            | なし             |

| APL7 | あり           | あり           | あり           | あり           | あり            | あり            | あり            | なし             |

| APL8 | あり           | あり           | あり           | あり           | あり            | あり            | あり            | あり             |

【0033】

表1において、かっこの中の数字は各サブフィールドに付与される輝度加重値であり、「k」はAPLによって輝度加重値を最大4倍に乗算させる値である。例えば、APLが低いほど第8サブフィールドSF8の加重値「128」は「256」、「384」、「512」に調整される。

【0034】

APLは最大1024の階調に対応して0~1023まで総1024段階に細分化され、総1024段階のAPLは表1のようにさらに8個のAPL群に分けられる。第1APL群APL1は最も低い範囲のAPLであって0~100段階のAPLを含み、第2APL群APL2は101~200段階のAPLを含む。第3APL群APL3は201~300段階のAPL、第4APL群APL4は301~400段階のAPL、第5APL群APL5は401~500段階のAPL、第6APL群APL6は501~600段階のAPL、第7APL群APL7は601~700段階のAPLをそれぞれ含む。また、第8APL群APL8は最も高い範囲のAPLであって701~1023段階のAPLを含む。

【0035】

表1及び図5に示すように、APLが第1APL群APL1に算出されると、輝度加重値が最も低い第1サブフィールドSF1にのみ上昇ランプ信号Ramp-upが割り当てられ、その以外のサブフィールドSF2~SF8には上昇ランプ信号Ramp-upが割

40

50

り当てられない。

【0036】

また、A P Lが101～200間の値、すなわち第2 A P L群A P L2に算出されると、第1及び第2サブフィールドS F1、S F2にのみ上昇ランプ信号R a m p - u pが印加される。

【0037】

画面が明るくなるとともにA P Lが601～700間の値、すなわち第7 A P L群A P L7に算出されると、第8サブフィールドS F8を除いた第1～第7サブフィールドS F1～S F7に上昇ランプ信号R a m p - u pが印加され、画面がピークホワイトに近づく明るさにさらに明るくなるとともにA P Lが701～1023間の値、すなわち第8 A P L群A P L8に算出されると、すべてのサブフィールドS F1～S F8に上昇ランプ信号R a m p - u pが印加される。10

【0038】

A P L値が低ければ、すなわち画面が比較的暗い場合にはデータが最下位ビット(Least Significant Bits: L S B)に対応する低輝度加重値のサブフィールド、例えば第1～第3サブフィールドS F1～S F3に主に存在する一方、最上位ビット(Most Significant Bits: M S B)に対応する高輝度加重値のサブフィールドにはほとんど存在しない。

【0039】

よって、本発明の第1実施形態に係るP D Pの初期化制御方法は、暗い画面でデータが存在するサブフィールドの初期化を安定化させる一方、データのない、すなわち点灯するセルがほとんどない高輝度加重値のサブフィールドでリセット期間を減らすか省略することにより、暗い画面でブラック輝度を低めてコントラスト比を高める。また、本発明の第1実施形態に係るP D Pの初期化制御方法は、明るい画面でリセット期間が含まれるサブフィールドの個数を増加させ、データが存在可能なほぼすべてのサブフィールドの初期化を安定化させることで、各サブフィールド毎の駆動マージンを充分に確保することができる。20

【0040】

一方、降下ランプ信号R a m p - d nは各サブフィールド毎に割り当てることもでき、A P Lによって上昇ランプ信号R a m p - u pと同様に省略することもできる。

【0041】

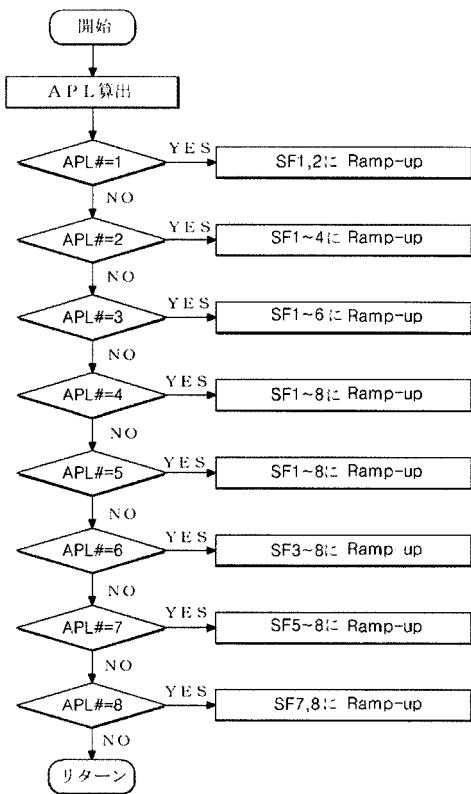

本発明の第2実施形態に係るP D Pの初期化制御方法は、1画面のA P Lを算出し、そのA P Lが低いほど高い加重値のサブフィールドにおいて上昇ランプ信号R a m p - u pをより多く省略するとともに、A P Lが高いほど低い加重値のサブフィールドにおいて上昇ランプ信号R a m p - u pをより多く省略する。30

【0042】

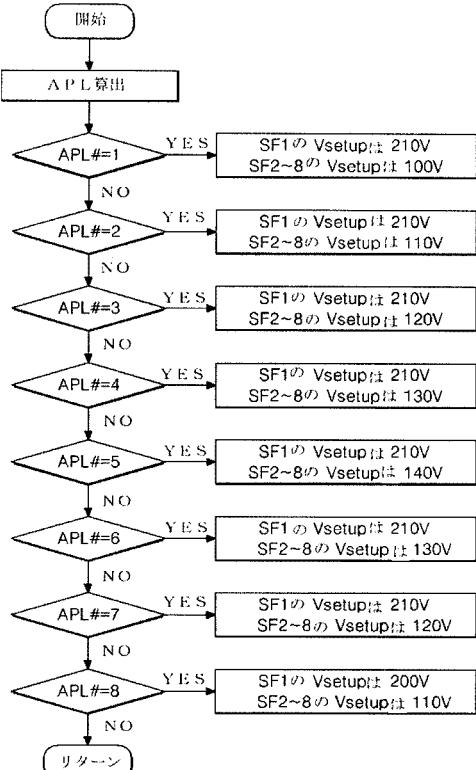

(2) 第2実施形態

図6は、本発明の第2実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。次の表2と図6は、サブフィールド8個で最大1024階調まで表現できるサブフィールドパターンを仮定し、本発明の第2実施形態に係るP D Pの初期化制御方法において上昇ランプ信号R a m p - u pの省略可否を示す。40

【0043】

【表2】

|      | SF1<br>(1 k) | SF2<br>(2 k) | SF3<br>(4 k) | SF4<br>(8 k) | SF5<br>(16 k) | SF6<br>(32 k) | SF7<br>(64 k) | SF8<br>(128 k) |

|------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|----------------|

| APL1 | あり           | あり           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL2 | あり           | あり           | あり           | あり           | なし            | なし            | なし            | なし             |

| APL3 | あり           | あり           | あり           | あり           | あり            | あり            | なし            | なし             |

| APL4 | あり           | あり           | あり           | あり           | あり            | あり            | あり            | あり             |

| APL5 | あり           | あり           | あり           | あり           | あり            | あり            | あり            | あり             |

| APL6 | なし           | なし           | あり           | あり           | あり            | あり            | あり            | あり             |

| APL7 | なし           | なし           | なし           | なし           | あり            | あり            | あり            | あり             |

| APL8 | なし           | なし           | なし           | なし           | なし            | なし            | あり            | あり             |

10

## 【0044】

表2及び図6に示すように、APLが第1APL群APL1に算出されると、輝度加重値が最も低い第1及び第2サブフィールドSF1、SF2にのみ上昇ランプ信号Ramp-upが割り当てられ、その以外のサブフィールドSF3～SF8には上昇ランプ信号Ramp-upが割り当てられない。また、APLが101～200間の値、すなわち第2APL群APL2に算出されると、第1～第4サブフィールドSF1～SF4に上昇ランプ信号Ramp-upが印加され、APLが第3APL群APL3に算出されると、第1～第6サブフィールドSF1～SF6に上昇ランプ信号Ramp-upが印加される。

20

## 【0045】

画面が中間の明るさになるとともにAPLが第4及び第5APL群APL4、APL5中に算出されると、上昇ランプ信号Ramp-upはすべてのサブフィールドSF1～SF8に印加される。

## 【0046】

画面がさらに明るくなるとともにAPLが第6APL群APL6に算出されると、第3～第8サブフィールドSF3～SF8に上昇ランプ信号Ramp-upが印加され、第7APL群APL7に算出されると、第5～第8サブフィールドSF5～SF8に上昇ランプ信号Ramp-upが印加される。画面がピークホワイトに近づきさらに明るくなるとともにAPLが第8APL群APL8に算出されると、第7及び第8サブフィールドSF7、SF8にのみ上昇ランプ信号Ramp-upが印加される。

30

## 【0047】

APL値が低ければ、すなわち画面が比較的暗い場合には最下位ビット(Least Significant Bits: LSB)側に対応する低輝度加重値のサブフィールド、例えば第1～第3サブフィールドSF1～SF3にデータが主に存在する一方、最上位ビット(Most Significant Bits: MSB)側に対応する高輝度加重値のサブフィールドにデータがほとんど存在しない。そして、放電回数が多いほど放電セル内に荷電粒子が多くなり、安定化したプライミング効果が強まり、放電セルの放電特性が安定化される。

## 【0048】

よって、本発明の第2実施形態に係るPDPの初期化制御方法は、暗い画面でデータが存在するサブフィールドの初期化を安定化させる一方、データがない、すなわち点灯するセルがほとんどない高輝度加重値のサブフィールドでリセット期間を省略することにより、暗い画面でブラック輝度を低めてコントラスト比を高める。

40

## 【0049】

本発明の第2実施形態に係るPDPの初期化制御方法は、放電回数が多くなるため、比較的各サブフィールドで駆動マージンが高くなる明るい画面において、明るさが明るくなるほど上昇ランプ信号Ramp-upが省略されるサブフィールドの個数を増加させる。明るい画面で上昇ランプ信号Ramp-upが省略されるサブフィールドは、明るい画面で最上位ビットMSB側にデータの存在する確率が高いため、最下位ビットMSBに側に対応する低輝度加重値のサブフィールドでリセット期間が省略される。

50

## 【0050】

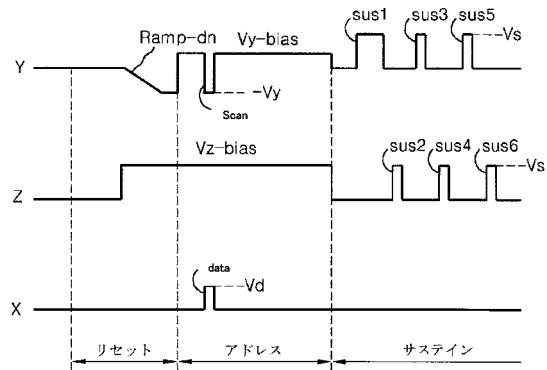

図7は、本発明の第1及び第2実施形態に係るPDPの初期化制御方法において上昇ランプ信号Ramp-upが省略されるサブフィールドの駆動信号を示す。図7に示すように、本発明の第1及び第2実施形態に係るPDPの初期化制御方法は、確率的にデータがほとんどないサブフィールドで上昇ランプ信号Ramp-upが省略されるので、その分リセット期間が短くなり、リセット期間で書き込み放電が発生しないので、ブラック輝度が低くなる。

## 【0051】

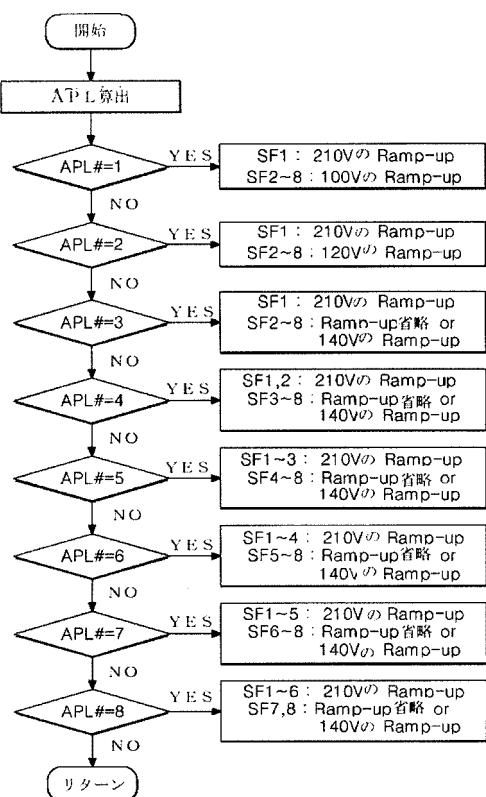

## (3) 第3実施形態

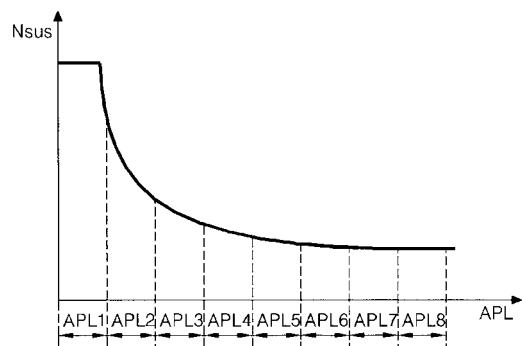

本発明の第3実施形態に係るPDPの初期化制御方法は、APLが低いほど、第1サブフィールドSF1を除いた残りのサブフィールドSF2～SF8で上昇ランプ信号Ramp-upのセットアップ電圧Vsetupを低下させる。

## 【0052】

図8は、本発明の第3実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。次の表3と図8は、サブフィールド8個で最大1024階調まで表現できるサブフィールドパターンを仮定し、本発明の第3実施形態に係るPDPの初期化制御方法において上昇ランプ信号Ramp-upのセットアップ電圧Vsetupを示す。

## 【0053】

## 【表3】

10

20

30

|      | SF1<br>(1 k) | SF2<br>(2 k) | SF3<br>(4 k) | SF4<br>(8 k) | SF5<br>(16 k) | SF6<br>(32 k) | SF7<br>(64 k) | SF8<br>(128 k) |

|------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|----------------|

| APL1 | 210V         | 100V         | 100V         | 100V         | 100V          | 100V          | 100V          | 100V           |

| APL2 | 210V         | 110V         | 110V         | 110V         | 110V          | 110V          | 110V          | 110V           |

| APL3 | 210V         | 120V         | 120V         | 120V         | 120V          | 120V          | 120V          | 120V           |

| APL4 | 210V         | 130V         | 130V         | 130V         | 130V          | 130V          | 130V          | 130V           |

| APL5 | 210V         | 140V         | 140V         | 140V         | 140V          | 140V          | 140V          | 140V           |

| APL6 | 210V         | 150V         | 150V         | 150V         | 150V          | 150V          | 150V          | 150V           |

| APL7 | 210V         | 160V         | 160V         | 160V         | 160V          | 160V          | 160V          | 160V           |

| APL8 | 210V         | 170V         | 170V         | 170V         | 170V          | 170V          | 170V          | 170V           |

## 【0054】

第1サブフィールドSF1はフレームがスタートするサブフィールドであって初期化を最も安定化させる必要がある。このために第1サブフィールドSF1では、APLにかかわらず180V～240V間の電圧、好ましくは210Vセットアップ電圧の上昇ランプ信号Ramp-upで初期化のための書き込み放電を発生させる。この第1サブフィールドSF1を除いた他のサブフィールドSF2～SF8では、APLによって上昇ランプ信号Ramp-upのセットアップ電圧Vsetupが変わる。APLが低い時、すなわち暗い画面でブラック輝度が低くなるほどAPLが低い値に算出され、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧Vsetupは低くなる。

## 【0055】

表3と図8に示すように、APLが第1APL群APL1に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧Vsetupは、100Vというふうに最も低く設定される。APLが第2APL群APL2に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧Vsetupは110Vに設定される。

## 【0056】

このようにAPLが高いほどセットアップ電圧Vsetupは高く設定され、画面が明るくなるとともにAPLが第7APL群APL7に算出されると、第2～第8サブフィー

40

50

ルドSF2～SF8におけるセットアップ電圧V<sub>set up</sub>は160Vに設定され、第8APL群APL8に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧V<sub>set up</sub>は170Vに設定される。

#### 【0057】

##### (4) 第4実施形態

本発明の第4実施形態に係るPDPの初期化制御方法は、APLが低いほど又はAPLが高いほど、第1サブフィールドSF1を除いた残りのサブフィールドSF2～SF8における上昇ランプ信号Ramp-upのセットアップ電圧V<sub>set up</sub>が低くなる。

#### 【0058】

図9は、本発明の第4実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。次の表4と図9は、サブフィールド8個で最大1024階調まで表現できるサブフィールドパターンを仮定し、本発明の第4実施形態に係るPDPの初期化制御方法において上昇ランプ信号Ramp-upのセットアップ電圧V<sub>set up</sub>を示す。

#### 【0059】

##### 【表4】

|      | SF1<br>(1 k) | SF2<br>(2 k) | SF3<br>(4 k) | SF4<br>(8 k) | SF5<br>(16 k) | SF6<br>(32 k) | SF7<br>(64 k) | SF8<br>(128 k) |

|------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|----------------|

| APL1 | 210V         | 100V         | 100V         | 100V         | 100V          | 100V          | 100V          | 100V           |

| APL2 | 210V         | 110V         | 110V         | 110V         | 110V          | 110V          | 110V          | 110V           |

| APL3 | 210V         | 120V         | 120V         | 120V         | 120V          | 120V          | 120V          | 120V           |

| APL4 | 210V         | 130V         | 130V         | 130V         | 130V          | 130V          | 130V          | 130V           |

| APL5 | 210V         | 140V         | 140V         | 140V         | 140V          | 140V          | 140V          | 140V           |

| APL6 | 210V         | 130V         | 130V         | 130V         | 130V          | 130V          | 130V          | 130V           |

| APL7 | 210V         | 120V         | 120V         | 120V         | 120V          | 120V          | 120V          | 120V           |

| APL8 | 210V         | 110V         | 110V         | 110V         | 110V          | 110V          | 110V          | 110V           |

#### 【0060】

第1サブフィールドSF1はフレームがスタートするサブフィールドであって初期化を最も安定化させる必要がある。このために第1サブフィールドSF1では、APLにかかわらず180V～240V間の電圧、好ましくは210Vセットアップ電圧の上昇ランプ信号Ramp-upで初期化のための書き込み放電を発生させる。この第1サブフィールドSF1を除いた他のサブフィールドSF2～SF8では、APLによって上昇ランプ信号Ramp-upのセットアップ電圧V<sub>set up</sub>が変わる。

#### 【0061】

APLが低い時、すなわち暗い画面でブラック輝度の低くなるほどAPLが低い値に算出され、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧V<sub>set up</sub>は低くなる。APLが高い時、すなわち明るい画面では放電回数が多いためプライミング効果が強い。このために、明るい画面ではセットアップ電圧V<sub>set up</sub>が低い場合にも初期化のための書き込み放電を全放電セルで安定して起こすことができる、APLが高い値に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧V<sub>set up</sub>は低くなる。

#### 【0062】

表4と図9に示すように、APLが第1APL群APL1に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧V<sub>set up</sub>は、100Vに最も低く設定される。APLが第2APL群APL2に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧V<sub>set up</sub>は110Vに設定される。このようにAPLが高いほどセットアップ電圧V<sub>set up</sub>は高く設定されるが、画面が明るくなるとともにAPLが第6APL群APL6に算出されると、第2～第8サブフィ

10

20

30

40

50

ールドSF2～SF8におけるセットアップ電圧V<sub>setup</sub>は130Vとまた低く設定される。また、さらに画面が明るくなるほどセットアップ電圧V<sub>setup</sub>は徐々に低く設定される。すなわち、APLが第7APL群APL7に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧V<sub>setup</sub>は120Vに設定され、第8APL群APL8に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧V<sub>setup</sub>は110Vに設定される。

#### 【0063】

図10は、本発明の第3及び第4実施形態に係るプラズマディスプレイパネルの初期化制御方法において上昇ランプ波形Ramp-upのセットアップ電圧V<sub>setup</sub>が平均明るさによって変わることを示す波形図である。図10は、本発明の第3及び第4実施形態に係るPDPの初期化制御方法において上昇ランプ信号Ramp-upのセットアップ電圧V<sub>setup</sub>を示す。

#### 【0064】

図10に示すように、本発明の第3及び第4実施形態に係るPDPの初期化制御方法は、APLによって少なくとも一部サブフィールドで上昇ランプ信号Ramp-upのセットアップ電圧V<sub>setup</sub>が点線で示すように100V～200V間で可変的に設定される。セットアップ電圧V<sub>setup</sub>が点線のように低く設定されると、その分上昇ランプ信号Ramp-upによる書き込み放電が弱く発生してブラック輝度を低めることができる。

#### 【0065】

##### (5) 第5実施形態

本発明の第5実施形態に係るPDPの初期化制御方法は、APLが低いほど、上昇ランプ信号Ramp-upが省略されるサブフィールドの個数を多くするか、少なくとも一部サブフィールドで上昇ランプ信号Ramp-upのセットアップ電圧V<sub>setup</sub>を低く設定する。また、本発明の第5実施形態に係るPDPの初期化制御方法は、APLが高いほど、上昇ランプ信号Ramp-upが省略されるサブフィールドの個数を少なくするか、少なくとも一部サブフィールドで上昇ランプ信号Ramp-upのセットアップ電圧V<sub>setup</sub>を高く設定する。

#### 【0066】

次の表5と図11は、サブフィールド8個で最大1024階調まで表現できるサブフィールドパターンを仮定し、本発明の第5実施形態に係るPDPの初期化制御方法において上昇ランプ信号Ramp-upの省略可否とセットアップ電圧V<sub>setup</sub>を示す。

#### 【0067】

##### 【表5】

|      | SF1<br>(1 k) | SF2<br>(2 k) | SF3<br>(4 k) | SF4<br>(8 k) | SF5<br>(16 k) | SF6<br>(32 k) | SF7<br>(64 k) | SF8<br>(128 k) |

|------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|----------------|

| APL1 | あり           | 100V         | 100V         | 100V         | 100V          | 100V          | 100V          | 100V           |

| APL2 | あり           | 120V         | 120V         | 120V         | 120V          | 120V          | 120V          | 120V           |

| APL3 | あり           | なし           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL4 | あり           | あり           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL5 | あり           | あり           | あり           | なし           | なし            | なし            | なし            | なし             |

| APL6 | あり           | あり           | あり           | あり           | なし            | なし            | なし            | なし             |

| APL7 | あり           | あり           | あり           | あり           | あり            | なし            | なし            | なし             |

| APL8 | あり           | あり           | あり           | あり           | あり            | あり            | なし            | なし             |

#### 【0068】

表5において、「あり」は上昇ランプ信号Ramp-upが省略されないサブフィールド、即ち上昇ランプ信号Ramp-upありを意味する。このサブフィールドでは正常な210Vセットアップ電圧V<sub>setup</sub>の上昇ランプ信号Ramp-upが印加される。

10

20

30

40

50

'なし'は上昇ランプ信号Ramp-upが省略されるか、セットアップ電圧Vsetupが140Vに低く設定される上昇ランプ信号Ramp-upが印加されるサブフィールドを意味する。

#### 【0069】

第1サブフィールドSF1では210Vセットアップ電圧の上昇ランプ信号Ramp-upで初期化のための書き込み放電が発生する。この第1サブフィールドSF1を除いた他のサブフィールドSF2～SF8では、APLによって上昇ランプ信号Ramp-upが省略されるか、上昇ランプ信号Ramp-upのセットアップ電圧Vsetupが変わる。APLが低い時、すなわち暗い画面でブラック輝度の低くなるようにAPLが低い値に算出されると、第2～第8サブフィールドSF2～SF8の少なくとも一部には上昇ランプ信号Ramp-upが省略されるか、低いセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。

#### 【0070】

表5と図11に示すように、APLが第1APL群APL1に算出されると、第2～第8サブフィールドSF2～SF8には100Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。APLが第2APL群APL2に算出されると、第2～第8サブフィールドSF2～SF8には120Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。APLが第3APL群APL3に算出されると、第2～第8サブフィールドSF2～SF8には上昇ランプ信号Ramp-upが省略されるか、140Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。APLが第4APL群APL4に算出されると、第1及び第2サブフィールドSF1、SF2には210Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加され、第3～第8サブフィールドSF3～SF8には上昇ランプ信号Ramp-upが省略されるか、140Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。APLが第5APL群APL5に算出されると、第1～第3サブフィールドSF1～SF3には210Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加され、第4～第8サブフィールドSF4～SF8には上昇ランプ信号Ramp-upが省略されるか、140Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。

#### 【0071】

このように、APLが高いほど、上昇ランプ信号Ramp-upが省略されるサブフィールドの個数が減るか、低いセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加されるサブフィールドの個数が減る。すなわち、画面が明るくなるとともにAPLが第7APL群APL7に算出されると、第1～第5サブフィールドSF1～SF5には210Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加され、第6～第8サブフィールドSF6～SF8には上昇ランプ信号Ramp-upが省略されるか、140Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。また、APLが第8APL群APL8に算出されると、第1～第6サブフィールドSF1～SF6には210Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加され、第7及び第8サブフィールドSF7、SF8には上昇ランプ信号Ramp-upが省略されるか、140Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。

#### 【0072】

本発明の第5実施形態に係るPDPの初期化制御方法の他の例は、表6のようにAPLが低いほど、上昇ランプ信号Ramp-upが省略されるサブフィールドの個数を多くし、APLが高い時、少なくとも一部サブフィールドで上昇ランプ信号Ramp-upのセットアップ電圧Vsetupが低く設定される。

#### 【0073】

【表6】

|      | SF1<br>(1 k) | SF2<br>(2 k) | SF3<br>(4 k) | SF4<br>(8 k) | SF5<br>(16 k) | SF6<br>(32 k) | SF7<br>(64 k) | SF8<br>(128 k) |

|------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|----------------|

| APL1 | あり           | なし           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL2 | あり           | あり           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL3 | あり           | あり           | あり           | なし           | なし            | なし            | なし            | なし             |

| APL4 | あり           | あり           | あり           | あり           | なし            | なし            | なし            | なし             |

| APL5 | あり           | 140V         | 140V         | 140V         | 140V          | 140V          | 140V          | 140V           |

| APL6 | あり           | 150V         | 150V         | 150V         | 150V          | 150V          | 150V          | 150V           |

| APL7 | あり           | 160V         | 160V         | 160V         | 160V          | 160V          | 160V          | 160V           |

| APL8 | あり           | 170V         | 170V         | 170V         | 170V          | 170V          | 170V          | 170V           |

10

20

30

## 【0074】

## (6) 第6実施形態

本発明の第6実施形態に係るPDPの初期化制御方法は、APLが低いほど又はAPLが高いほど、上昇ランプ信号Ramp-upが省略されるか、上昇ランプ信号Ramp-upのセットアップ電圧Vsetupが低く設定される。

## 【0075】

次の表7と図12は、サブフィールド8個で最大1024階調まで表現できるサブフィールドパターンを仮定し、本発明の第6実施形態に係るPDPの初期化制御方法において上昇ランプ信号Ramp-upの省略可否とセットアップ電圧Vsetupを示す。

## 【0076】

## 【表7】

|      | SF1<br>(1 k) | SF2<br>(2 k) | SF3<br>(4 k) | SF4<br>(8 k) | SF5<br>(16 k) | SF6<br>(32 k) | SF7<br>(64 k) | SF8<br>(128 k) |

|------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|----------------|

| APL1 | あり           | 100V         | 100V         | 100V         | 100V          | 100V          | 100V          | 100V           |

| APL2 | あり           | 120V         | 120V         | 120V         | 120V          | 120V          | 120V          | 120V           |

| APL3 | あり           | なし           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL4 | あり           | あり           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL5 | あり           | あり           | あり           | なし           | なし            | なし            | なし            | なし             |

| APL6 | あり           | あり           | なし           | なし           | なし            | なし            | なし            | なし             |

| APL7 | あり           | 120V         | 120V         | 120V         | 120V          | 120V          | 120V          | 120V           |

| APL8 | あり           | 100V         | 100V         | 100V         | 100V          | 100V          | 100V          | 100V           |

## 【0077】

第1サブフィールドSF1はフレームがスタートするサブフィールドであって初期化を最も安定化させる必要がある。このために第1サブフィールドSF1では、APLにかかる180V～240V間の電圧、好ましくは210Vセットアップ電圧の上昇ランプ信号Ramp-upで初期化のための書き込み放電を発生させる。この第1サブフィールドSF1を除いた他のサブフィールドSF2～SF8では、APLが低い時とAPLが高い時、上昇ランプ信号Ramp-upが省略されるサブフィールドの個数が増加するか、セットアップ電圧Vsetupが低く設定される。

40

## 【0078】

表7と図12に示すように、APLが第1APL群APL1に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧Vsetupは100Vに低く設定される。APLが第2APL群APL2に算出されると、第2～第8サブフィールドSF2～SF8におけるセットアップ電圧Vsetupは120Vに設定される。AP

50

Lが第3 APL群APL3に算出されると、第2～第8サブフィールドSF2～SF8には上昇ランプ信号Ramp-upが省略されるか、140Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。

#### 【0079】

APLが第4 APL群APL4に算出されると、第1及び第2サブフィールドSF1、SF2には210Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加され、第3～第8サブフィールドSF3～SF8には上昇ランプ信号Ramp-upが省略されるか、140Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。APLが第5 APL群APL5に算出されると、第1～第3サブフィールドSF1～SF3には210Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加され、第4～第8サブフィールドSF4～SF8には上昇ランプ信号Ramp-upが省略されるか、140Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。

#### 【0080】

APLが第6 APL群APL6以上に高くなると、上昇ランプ信号Ramp-upが省略されるサブフィールドの個数が増えるか、セットアップ電圧が低くなる。すなわち、画面が明るくなるとともにAPLが第6 APL群APL6に算出されると、第1及び第2サブフィールドSF1、SF2には210Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加され、第3～第8サブフィールドSF3～SF8には上昇ランプ信号Ramp-upが省略されるか、140Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。

#### 【0081】

APLが第7 APL群APL7に算出されると、第1サブフィールドSF1には210Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加され、第2～第8サブフィールドSF2～SF8には120Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。また、APLが第8 APL群APL8に算出されると、第1サブフィールドSF1には210Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加され、第2～第8サブフィールドSF2～SF8には100Vのセットアップ電圧Vsetupの上昇ランプ信号Ramp-upが印加される。

#### 【0082】

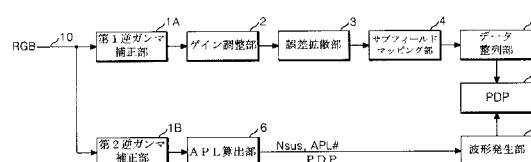

図13及び図14は、本発明のPDPの初期化制御装置を示す図である。

#### 【0083】

図13及び図14を参照すれば、本発明の実施形態に係るPDPの初期化制御装置は、第1逆ガンマ補正部1Aとデータ整列部5との間に接続されたゲイン調整部2、誤差拡散部3及びサブフィールドマッピング部4と、第2逆ガンマ補正部1Bと波形発生部7との間に接続されたAPL算出部6と、を備える。

#### 【0084】

第1及び第2逆ガンマ補正部1A、1Bは、入力ライン10からのデジタルビデオデータRGBを逆ガンマ補正して映像信号の階調値に対する輝度を線形的に変換させる。

#### 【0085】

ゲイン調整部2は、赤色、緑色及び青色の各データ別に有効利得を調整して色温度を補償する。

#### 【0086】

誤差拡散部3は、ゲイン調整部2から入力されるデジタルビデオデータの量子化誤差を隣接したセルに拡散させることにより、輝度値を微細に調整する。このために、誤差拡散部3はデータを整数部と小数部に分けて小数部にフロイド・シュタインベルグ(Floyd-Steinberg)係数をかける。

#### 【0087】

サブフィールドマッピング部4は、誤差拡散部3から入力されたデータを各ビット別に予め保存されたサブフィールドパターンにマッピングし、そのマッピングデータをデータ

10

20

30

40

50

整列部 5 に供給する。

【 0 0 8 8 】

データ整列部 5 は、サブフィールドマッピング部 4 から入力されるデジタルビデオデータを P D P 8 のデータ駆動部 1 0 2 に供給する。データ駆動部 1 0 2 は、P D P 8 のアドレス電極 X 1 ~ X m に接続され、データ整列部 5 から入力されるデータを 1 水平ライン分ずつラッチした後、ラッチされたデータを 1 水平期間単位でアドレス電極 X 1 ~ X m に供給する。

【 0 0 8 9 】

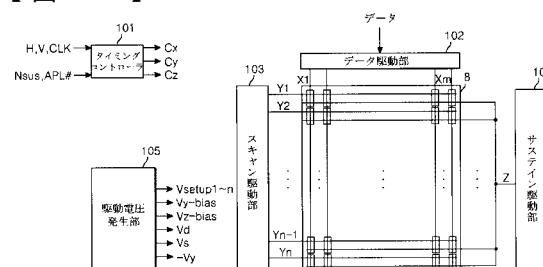

A P L 算出部 6 は、第 2 逆ガンマ補正部 1 B から入力されるデジタルビデオデータに対して 1 画面単位で A P L を算出し、算出された A P L に対応するサステインパルス数データ N s u s を出力する。また、A P L 算出部 6 は、算出された A P L が含まれる A P L 群の識別データ A P L # を出力する。このために、A P L 算出部 6 は、図 1 5 のように A P L に対応するサステインパルス数データ N s u s が搭載されたロックアップテーブルを検索し、サステインパルス数データ N s u s と A P L 群の識別データ A P L # を読み出す。

【 0 0 9 0 】

波形発生部 7 は、図 1 4 のようにタイミングコントローラ 1 0 1 、駆動電圧発生部 1 0 5 、スキャン駆動部 1 0 3 及びサステイン駆動部 1 0 4 を備える。

【 0 0 9 1 】

タイミングコントローラ 1 0 1 は、垂直 / 水平同期信号 H 、 V とクロック信号 C L K を利用して各駆動部 1 0 2 、 1 0 3 、 1 0 4 に必要なタイミング制御信号 C x 、 C y 、 C z を発生させ、そのタイミング制御信号 C x 、 C y 、 C z を当該駆動部 1 0 2 、 1 0 3 、 1 0 4 に供給することにより、各駆動部 1 0 2 、 1 0 3 、 1 0 4 を制御する。

【 0 0 9 2 】

データ制御信号 C x には、データをサンプリングするためのサンプリングクロック、ラッチ制御信号、エネルギー回收回路と駆動スイッチ素子のオン / オフタイムを制御するためのスイッチ制御信号が含まれる。スキャン制御信号 C y には、スキャン駆動部 1 0 3 内のエネルギー回收回路と駆動スイッチ素子のオン / オフタイムを制御するためのスイッチ制御信号が含まれる。サステイン制御信号 C z には、サステイン駆動部 1 0 4 内のエネルギー回收回路と駆動スイッチ素子のオン / オフタイムを制御するためのスイッチ制御信号が含まれる

タイミングコントローラ 1 0 1 は、サステインパルス数データ N s u s によってスキャン制御信号 C y とサステイン制御信号 C z を調整することにより、A P L によってサステインパルス数を制御し、A P L 群識別データ A P L # に応答して、前述した実施形態のように上昇ランプ信号 R a m p - u p を省略するか、そのセットアップ電圧 V s e t u p を調整する。

【 0 0 9 3 】

スキャン駆動部 1 0 3 は、タイミングコントローラ 1 0 1 の制御下でスキャン電極 Y 1 ~ Y m に対し、リセット期間中に上昇ランプ信号 R a m p - u p と降下ランプ信号 R a m p - d n を供給し、アドレス期間中にスキャンパルス s c a n を順次供給する。また、スキャン駆動部 1 0 3 は、タイミングコントローラ 1 0 1 の制御下でスキャン電極 Y 1 ~ Y n にサステイン期間中にサステインパルス s u s 1 、 s u s 3 、 s u s 5 を供給する。特に、スキャン駆動部 1 0 3 は、タイミングコントローラ 1 0 1 の制御下で前述した実施形態のように A P L によって選択的に少なくとも一部サブフィールドで上昇ランプ信号 R a m p - u p を省略するか、上昇ランプ信号 R a m p - u p のセットアップ電圧 V s e t u p 1 ~ V s e t u p n を調整する。

【 0 0 9 4 】

サステイン駆動部 1 0 4 は、タイミングコントローラ 1 0 1 の制御下でアドレス期間中に直流バイアス電圧 V z - b i a s を供給した後、サステイン期間中にスキャン駆動部 1 0 3 と交互に動作してサステインパルス s u s 2 、 s u s 4 、 s u s 6 を供給する。

【 0 0 9 5 】

10

20

30

40

50

駆動電圧発生部 105 は、上昇ランプ信号  $R_{uy}$ 、 $R_{uz}$  のセットアップ電圧  $V_{set\_up}$ 、 $V_{set\_up\_n}$ 、スキャン電圧で設定される負極性のスキャンバイアス電圧 -  $V_y$ 、直流バイアス電圧 ( $V_y$ -bias、 $V_z$ -bias)、サステイン電圧  $V_s$ 、データ電圧  $V_d$ などを発生させる。このような駆動電圧は放電ガスの組成や放電セル構造によって変わることができる。

#### 【0096】

上述したように、本発明に係る PDP の初期化制御方法及び装置は、APL が基準値より低い時及び / または高い時、上昇ランプ信号を省略するか、そのセットアップ電圧を低下させる。その結果、本発明は、初期化放電数を減らすか、初期化放電を弱くして放電時に伴わう光放出量を減らすことにより、ブラック輝度を低めてコントラスト比を向上させ且つリセット時間を減らすことができる。10

#### 【0097】

一方、本発明は、APL によって上昇ランプ波形の数やそのセットアップ電圧を調節することを中心として実施形態を説明したが、上昇ランプ波形の勾配を APL によって制御するか、降下ランプ波形の数や電圧を APL によって制御することもできる。

#### 【図面の簡単な説明】

#### 【0098】

【図 1】従来のプラズマディスプレイパネルを概略的に示す平面図である。

【図 2】図 1 に示したセルの構造を詳しく示す斜視図である。

【図 3】1 フレーム期間を複数のサブフィールドに時分割したサブフィールドパターンを示す図である。20

【図 4】図 1 のようなプラズマディスプレイパネルを駆動するための従来の駆動信号を示す波形図である。

【図 5】本発明の第 1 実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。

【図 6】本発明の第 2 実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。

【図 7】本発明の第 1 及び第 2 実施形態に係るプラズマディスプレイパネルの初期化制御方法において上昇ランプ波形が省略されるサブフィールドの駆動信号を示す波形図である。30

【図 8】本発明の第 3 実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。

【図 9】本発明の第 4 実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。

【図 10】本発明の第 3 及び第 4 実施形態に係るプラズマディスプレイパネルの初期化制御方法において上昇ランプ波形のセットアップ電圧が平均明るさによって変わることを示す波形図である。

【図 11】本発明の第 5 実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。

【図 12】本発明の第 6 実施形態に係るプラズマディスプレイパネルの初期化制御方法の制御手順を段階的に示す流れ図である。40

【図 13】本発明の実施形態に係るプラズマディスプレイパネルの初期化制御装置を示すプロック図である。

【図 14】図 13 の波形発生部を詳しく示すプロック図である。

【図 15】図 13 に示した APL 算出部で算出される APL とそれによるサステインバルス数とを示すグラフである。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き(51)Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 04 N 5/66 101B

G 09 G 3/28 KF ターム(参考) 5C058 AA11 AB02 BA04 BA07 BA08 BA13

5C080 AA05 BB05 DD03 EE29 FF12 HH02 HH04 JJ02 JJ04 JJ05

JJ06 JJ07