(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-541077

(P2016-541077A)

(43) 公表日 平成28年12月28日(2016.12.28)

(51) Int.Cl.

G06F 1/26 (2006.01)

G05F 1/56 (2006.01)

F 1

G06F 1/26

G05F 1/56A

310F

テーマコード(参考)

5B011

5H430

審査請求 有 予備審査請求 未請求 (全 24 頁)

(21) 出願番号 特願2016-550452 (P2016-550452)

(86) (22) 出願日 平成25年12月18日 (2013.12.18)

(85) 翻訳文提出日 平成28年4月26日 (2016.4.26)

(86) 國際出願番号 PCT/US2013/076298

(87) 國際公開番号 WO2015/094252

(87) 國際公開日 平成27年6月25日 (2015.6.25)

(71) 出願人 593096712

インテル コーポレイション

アメリカ合衆国 95054 カリフォルニア州 サンタ クララ ミッション カレッジ ブールバード 2200

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

最終頁に続く

(54) 【発明の名称】適応ゲインを持ったデジタル合成可能な低ドロップアウトレギュレータ

## (57) 【要約】

適応ゲインを持った電圧レギュレータであって、デジタルバスによって制御可能であり、第1電力供給を負荷へ供給し且つ第2電力供給を入力として受けるよう動作する複数のパワーゲートトランジスタと、第1電力供給を受け、第1電力供給を表すデジタル出力を生成するアナログ - デジタルコンバータ(ADC)と、第1電力供給を表すデジタル出力を受け、複数のパワーゲートトランジスタを制御するためにデジタルバスを生成して、複数のパワーゲートトランジスタの伝達関数が動作範囲にわたって略線形であるようにするコントローラとを有する電圧レギュレータが記載される。

## 【特許請求の範囲】

## 【請求項 1】

デジタルバスによって制御される複数のパワーゲートトランジスタであって、第1電力供給を負荷へ供給し、第2電力供給を入力として受けよう動作する前記複数のパワーゲートトランジスタと、

前記第1電力供給を受け、該第1電力供給を表すデジタル出力を生成するアナログ-デジタルコンバータ(ADC)と、

前記第1電力供給を表す前記デジタル出力を受け、前記複数のパワーゲートトランジスタを制御するための前記デジタルバスを生成して、前記複数のパワーゲートトランジスタの伝達関数が動作範囲にわたって略線形であるようにするコントローラと

を有する装置。

## 【請求項 2】

前記コントローラは、前記複数のパワーゲートトランジスタ、前記ADC、及び前記コントローラによって形成されるループのゲインを変更するよう動作し、

前記コントローラは、動作点の関数として前記ループのゲインを変更するよう動作する、

請求項1に記載の装置。

## 【請求項 3】

前記コントローラは、

直列につなぎ合わされた第1の複数の遅延ユニットであって、該第1の複数の遅延ユニットの中の1つの遅延ユニットが前記第1電力供給を表す前記デジタル出力を受ける、前記第1の複数の遅延ユニットと、

前記第1の複数の遅延ユニットの夫々の出力のゲインを増幅する第1の複数のゲイン段と、

加算された出力を生成するよう前記増幅された出力を加算する加算器と

を有する、

請求項2に記載の装置。

## 【請求項 4】

前記コントローラは、

前記ループのゲインを変更するよう前記加算された出力に係数を乗じて、前記複数のパワーゲートトランジスタの伝達関数が動作範囲にわたって略線形であるようにする乗算器と

を有する、

請求項3に記載の装置。

## 【請求項 5】

前記コントローラは、

前記加算された出力の符号を検出し、該検出された符号が前記係数を決定する符号検出器

を有する、

請求項4に記載の装置。

## 【請求項 6】

前記コントローラは、

直列につなぎ合わされた第2の複数の遅延ユニットであって、該第2の複数の遅延ユニットの中の1つの遅延ユニットが前記コントローラの出力を受ける、前記第2の複数の遅延ユニットと、

前記第2の複数の遅延ユニットの夫々の出力のゲインを増幅する第2の複数のゲイン段と、

を有する、

請求項4に記載の装置。

## 【請求項 7】

前記コントローラは、

10

20

30

40

50

前記第2の複数の遅延ユニットの夫々の増幅された出力及び前記乗算器の出力を積分して、前記コントローラの出力を生成する積分器

を有する、

請求項6に記載の装置。

## 【請求項8】

前記複数のパワーゲートトランジスタはp形トランジスタである、

請求項1に記載の装置。

## 【請求項9】

電圧識別信号(VID)を前記ADCのための複数のアナログ信号に変換するデジタル

-アナログコンバータ(DAC)を更に有する

請求項1に記載の装置。

10

## 【請求項10】

前記VIDは電力制御ユニット(PCU)によって生成される、

請求項9に記載の装置。

## 【請求項11】

前記コントローラの出力を復号して、前記複数のパワーゲートトランジスタを制御する

ための前記デジタルバスを生成するデコーダを更に有する

請求項1に記載の装置。

## 【請求項12】

前記デコーダは、前記複数のパワーゲートトランジスタの略全てをオンすることによっ

て、当該装置をバイパスモードにおいて作動させるよう動作する、

請求項11に記載の装置。

20

## 【請求項13】

前記デコーダは、全ての前記複数のパワーゲートトランジスタをオフさせる前記デジタ

ルバスを生成するよう動作する、

請求項11に記載の装置。

## 【請求項14】

第1電力供給を表すデジタル出力を受け、複数のパワーゲートトランジスタを制御する

ためのデジタルバスを生成して、前記複数のパワーゲートトランジスタの伝達関数が動作

範囲にわたって略線形であるようにするコントローラと、

30

前記コントローラの出力を復号して、前記複数のパワーゲートトランジスタを制御する

ための前記デジタルバスを生成するデコーダと

を有する装置。

## 【請求項15】

前記コントローラは、前記複数のパワーゲートトランジスタ、アナログ-デジタルコン

バータ(ADC)、及び前記コントローラによって形成されるループのゲインを変更する

よう動作し、

前記コントローラは、動作点の関数として前記ループのゲインを変更するよう動作する

、

請求項14に記載の装置。

40

## 【請求項16】

前記コントローラは、

直列につなぎ合わされた第1の複数の遅延ユニットであって、該第1の複数の遅延ユニ

ットの中の1つの遅延ユニットが前記第1電力供給を表す前記デジタル出力を受ける、前

記第1の複数の遅延ユニットと、

前記第1の複数の遅延ユニットの夫々の出力のゲインを増幅する第1の複数のゲイン段

と、

加算された出力を生成するよう前記増幅された出力を積分する加算器と

を有する、

請求項15に記載の装置。

50

## 【請求項 17】

前記コントローラは、

前記ループのゲインを変更するよう前記加算された出力に係数を乗じて、前記複数のパワーゲートトランジスタの伝達関数が動作範囲にわたって略線形であるようにする乗算器を有する、

請求項 16 に記載の装置。

## 【請求項 18】

前記コントローラは、

前記加算された出力の符号を検出し、該検出された符号が前記係数を決定する符号検出器

10

を有する、

請求項 17 に記載の装置。

## 【請求項 19】

前記コントローラは、

直列につなぎ合わされた第 2 の複数の遅延ユニットであって、該第 2 の複数の遅延ユニットの中の 1 つの遅延ユニットが前記コントローラの出力を受ける、前記第 2 の複数の遅延ユニットと、

前記第 2 の複数の遅延ユニットの夫々の出力のゲインを増幅する第 2 の複数のゲイン段と

を有する、

請求項 17 に記載の装置。

20

## 【請求項 20】

前記コントローラは、

前記第 2 の複数の遅延ユニットの夫々の増幅された出力及び前記乗算器の出力を積分して、前記コントローラの出力を生成する積分器

を有する、

請求項 19 に記載の装置。

## 【請求項 21】

メモリユニットと、

前記メモリユニットへ結合され、請求項 1 乃至 13 のうちいずれか一項に記載の装置に従う電圧レギュレータを備えるプロセッサと、

前記プロセッサがアンテナを通じて他のデバイスと通信することを可能にする無線インターフェイスと

を有するシステム。

30

## 【請求項 22】

表示ユニットを更に有する請求項 21 に記載のシステム。

## 【請求項 23】

前記表示ユニットはタッチスクリーンである、

請求項 22 に記載のシステム。

40

## 【請求項 24】

メモリユニットと、

前記メモリユニットへ結合され、請求項 14 乃至 20 のうちいずれか一項に記載の装置に従う電圧レギュレータを備えるプロセッサと、

前記プロセッサがアンテナを通じて他のデバイスと通信することを可能にする無線インターフェイスと

を有するシステム。

## 【請求項 25】

表示ユニットを更に有する請求項 24 に記載のシステム。

## 【請求項 26】

前記表示ユニットはタッチスクリーンである、

50

請求項 2 5 に記載のシステム。

【発明の詳細な説明】

【背景技術】

【0 0 0 1】

既存の低ドロップアウト ( L D O ; low dropout ) レギュレーターアーキテクチャは、 L D O レギュレータに対するゲート駆動を制御するためにアナログ電圧を使用する。アナログ電圧を生成することは、アナログ回路を生成する回路の注意深い設計を必要とし得る。一般に、そのような回路は、プロセステクノロジを用いて適切に拡張又は縮小しない。 L D O の出力電圧をレギュレートするよう、ヘッドルーム ( 約 5 0 m V から 1 2 0 m V ) が L D O レギュレータの入力電源電圧と出力電圧との間に必要とされ得る。アナログ L D O レギュレータアプローチに関して、多くの課題がある。

10

【0 0 0 2】

例えば、アナログ L D O レギュレータのフィードバックループの安定性は、パッケージ寄生及び出力極に極めて依存し得る。結果として、フィードバックループの安定性を得るよう、バンド幅における不利益が起こり得る。アナログ L D O レギュレータはまた、 L D O レギュレータの通常の動作について、その出力ノードで最小のドロップアウトを示し得る ( 例えば、 5 0 m V から 1 2 0 m V ) 。入力電源が小さくなる場合に、そのような最小ドロップアウトは課題になる。アナログ L D O レギュレータはまた、 D C セットポイントの精度に影響を及ぼすゲイン制限に起因して、有限な直流 ( D C ; direct-current ) オフセットエラーを示し得る。アナログ設計、特に、デュアルループアーキテクチャを使用するものにおいては更に複数の集積及び設計の課題がある。

20

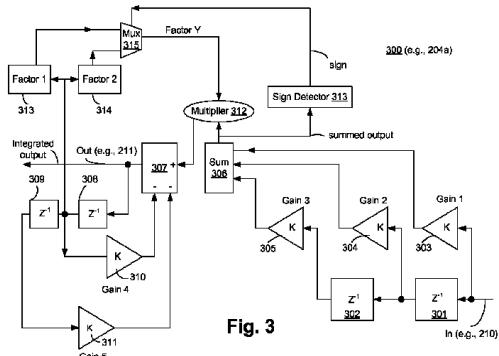

【0 0 0 3】

パワー F E T ( Field Effect Transistor ) アレイは、 L D O レギュレータが電力を出力ノードへ供給するために使用されてよく、それによりアレイは並列バンクとして接続される。この F E T アレイの伝達関数は非線形である。図 1 A は、 F E T アレイの並列バンクの非線形伝達関数を示すプロット 1 0 0 を表す。ここで、 x 軸はコードである。コードが高くなればなるほど、オンされる並列バンク内のトランジスタはますます多くなる。 y 軸は、トランジスタの並列バンクの抵抗である。より多くのトランジスタがオンされる ( すなわち、コード数が増える ) につれて、並列バンクの抵抗は非線形に下がる。伝達関数は非線形なゲインを有するので、コード ' N ' の値が高い L D O 電圧レギュレータ ( V R ; voltage regulator ) の動作点に関して、システムのゲインは低く、コード ' N ' が低い場合に、システムのゲインは高い。これは、過渡応答を ' N ' が低い場合に鋭くし、 ' N ' が高い場合に鈍くする。 L D O V R のそのような非線形応答は、 L D O V R の出力が、例えば、負荷需要の突然の変化に起因して、電圧ドロップに見舞われる場合に、課題である。

30

【図面の簡単な説明】

【0 0 0 4】

本開示の実施形態は、以下で与えられる詳細な説明から、及び本開示の様々な実施形態の添付の図面から、より完全に理解されるであろう。なお、実施形態は、本開示を具体的な実施形態に制限するものと解されるべきではなく、単に説明及び理解のためである。

40

【0 0 0 5】

【図 1 A 】 F E T の並列バンクの非線形伝達関数を示すプロットを表す。

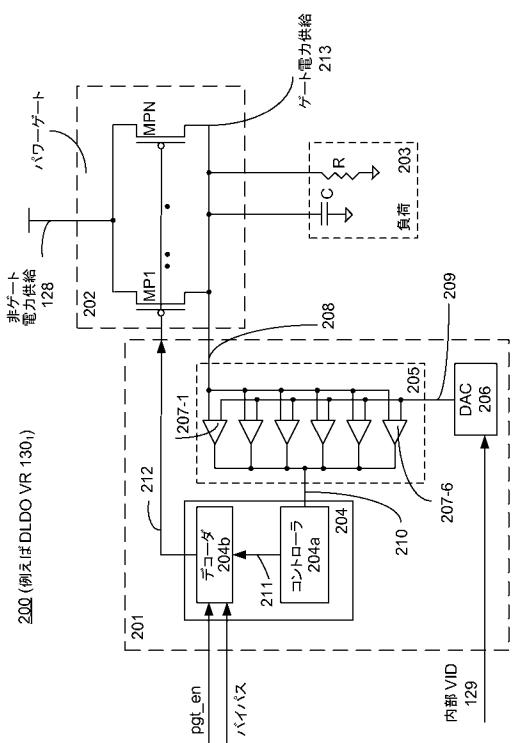

【0 0 0 6】

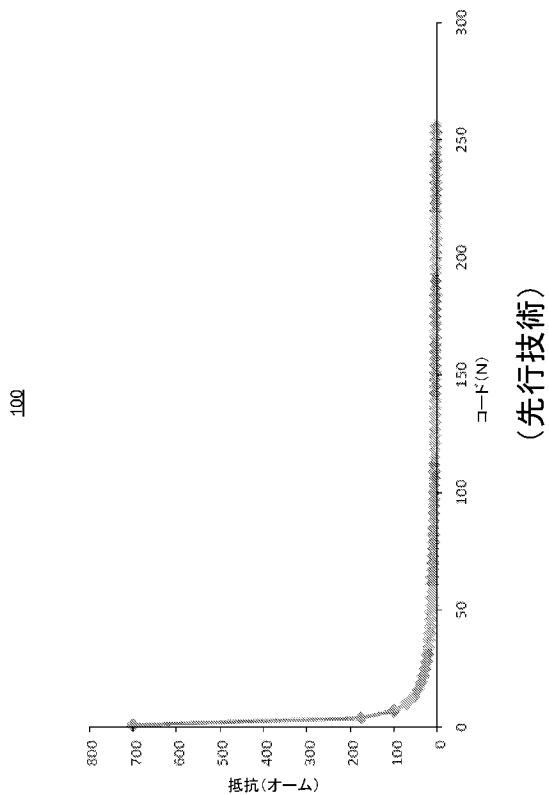

【図 1 B 】 本開示の一実施形態に従って、 1 つ以上のデジタル低ドロップアウト ( D L D O ) 電圧レギュレータ ( V R ) を備えた電力アーキテクチャを表す。

【0 0 0 7】

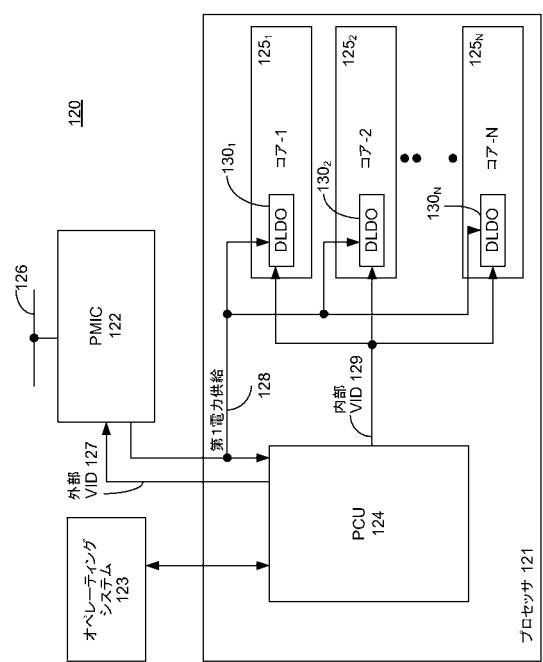

【図 2 】 本開示の一実施形態に従う D L D O V R を表す。

【0 0 0 8】

【図 3 】 本開示の一実施形態に従って、 D L D O V R のコントローラを実装する数学モデルを表す。

50

## 【0009】

【図4】本開示の一実施形態に従って、コントローラの技術的効果を示すプロットを表す。

## 【0010】

【図5】本開示の一実施形態に従って、D L D O V R を備えたスマートデバイス又はコンピュータシステム又はS o C (System-on-Chip) を表す。

## 【発明を実施するための形態】

## 【0011】

実施形態は、装置、例えば、デジタル低ドロップアウト (D L D O) V R (電圧レギュレータ) であって、デジタルバスによって制御可能であり、第1電力供給をプロセッシングコアへ供給し且つ第2電力供給を入力として受ける複数のパワーゲートトランジスタと、前記第1電力供給を受け、該第1電力供給を表すデジタル出力を生成するアナログ - デジタルコンバータ (A D C ; analog to digital converter) と、前記第1電力供給を表す前記デジタル出力を受け、前記複数のパワーゲートトランジスタを制御するための前記デジタルバスを生成するコントローラとを有する装置について説明する。

10

## 【0012】

D L D O V R の幾つかの技術的効果がある。幾つかの制限されない技術的効果は、全ての動作点について応答を速くするようD L D O V R の動作範囲にわたって一様なゲインを有する。一実施形態において、動作範囲にわたって一様なゲインは、動作点の関数である余得係数をフィルタ伝達関数に加えることによって達成される。

20

## 【0013】

他の例となる技術的効果は、D L D O V R のコントローラがスタンバイモードにおいて自己消費電流が低い合成ロジックであることから、D L D O V R のコントローラにおけるD C (直流) 電流経路のおおよその削除を含む。一実施形態において、D L D O V R コントローラの係数は再プログラム可能であり、これは、S o C (System-on-Chip ; システムオンチップ) が製造された後でさえ、D L D O V R におけるループが調整されることを可能にする。一実施形態において、D L D O V R のコントローラは、D L D O V R の出力ノードでの極を補償し、故に、D L D O V R ループに存在するD C ゲインエンサーは略零である。実施形態のD L D O V R は、デジタル制御によりパワーゲートのソフトスタートを可能にする。D L D O V R のアーキテクチャは、設計者が、(D L D O

30

V R によって駆動される) 負荷の全ての部分への一様な電力供給を確かにすることによる同様の重みを持ったパワーゲートの分布にわたる制御を有することを可能にする。

## 【0014】

D L D O V R の実施形態は、D L D O V R のドループ応答を改善するために非対称 / 非線形なゲイン関数のような非線形制御機能を用いることを可能にする。D L D O V R の実施形態は、デジタルV I D (電圧識別 ; voltage identification) コードによって定義される入力電圧を可能にする。これは、デジタル領域において実施することが(アナログ回路と比較して)より簡単である。D L D O V R の実施形態は、(通常のL D Oと比較して) D L D O V R のより多くの回路がデジタルであるので、より簡単なテスト容易化設計 (D F T ; Design-for-Test) を集積することを可能にする。そのようなD F Tは、大量製造 (H V M ; High Volume Manufacturing) 試験を可能にすることができる。

40

## 【0015】

以下の記載において、多数の詳細は、本開示の実施形態のより完全な説明を与えるために論じられる。なお、当業者に当然ながら、本開示の実施形態は、それらの具体的な詳細によらずに実施されてよい。他の事例では、よく知られている構造及びデバイスは、本開示の実施形態を不明りょうにしないように、詳細にではなく、ブロック図形式において示される。

## 【0016】

実施形態の対応する図面において、信号は線を用いて表される点に留意されたい。幾つ

50

かの線は、より多くの構成信号経路を示すようより太く、且つ／あるいは、主要な情報フロー方向を示すよう1つ以上の端部で矢印を有してよい。むしろ、線は、回路又は論理ユニットのより容易な理解を促すよう1つ以上の例となる実施形態に関連して使用される。如何なる表されている信号も、設計ニーズ又は好みによって影響されるように、どちらか一方の方向において進むことができる1つ以上の信号を実際には有してよく、如何なる適切なタイプの信号スキームによっても実施されてよい。

#### 【0017】

明細書を通して、更には特許請求の範囲において、語「接続される (connected)」は、如何なる中間デバイスもなしで接続される物の間の直接的な電気接続を意味する。語「結合される (coupled)」は、接続される物の間の直接的な電気接続、又は1つ以上の受動的若しくは能動的な中間デバイスを通じた間接的な接続のいずれかを意味する。語「回路 (circuit)」は、所望の機能を提供するよう互いに協働するよう構成されている1つ以上の受動的な及び／又は能動的なコンポーネントを意味する。語「信号 (signal)」は、少なくとも1つの電流信号、電圧信号又はデータ／クロック信号を意味する。「1つの (a又はan)」及び「前記 (the)」の意味は、複数参照を含む。“～において (in)”の意味は、「～の中に (in)」及び「～の上に (on)」を含む。

10

#### 【0018】

語「スケーリング (scaling)」は、一般に、1つのプロセステクノロジから他のプロセステクノロジへ設計（回路図及びレイアウト）を変換することを言う。語「スケーリング」は、一般に、同じテクノロジノード内でレイアウト及びデバイスをダウンサイジングすることも言う。語「略 (substantially)」、「近くに (close)」、「近似的に (approximately)」、「おおよそ (near)」、「約 (about)」は、一般に、目標値の±20%内にあることを言う。

20

#### 【0019】

特段示されない限り、共通のオブジェクトを示すための序数形容詞「第1 (first)」、「第2 (second)」及び「第3 (third)」などの使用は、同じオブジェクトの異なるインスタンスが言及されていることを単に示すのであって、そのように記載されているオブジェクトが時間的に、空間的に、順位付けにおいて、又は何らかの他の方法において所与の順序になければならないことを示すよう意図されない。

30

#### 【0020】

実施形態のために、トランジスタは、ドレイン、ソース、ゲート、及びバルク端子を有する金属酸化膜半導体 (MOS ; metal oxide semiconductor) トランジスタである。トランジスタには、更に、トライゲート及びFinFETトランジスタが含まれる。ソース及びドレイン端子は、同じ端子であってよく、ここでは同義的に使用される。当業者に明らかなように、他のトランジスタ、例えば、バイポーラ接合トランジスタ、すなわち、BJT PNP/NPN、BiCMOS、CMOS、eFET、などは、本開示の適用範囲から逸脱することなしに使用されてよい。語「MN」は、n形トランジスタ（例えば、NMOS、NPN BJT、など）を示し、語「MP」は、p形トランジスタ（例えば、PMOS、PNP BJT、など）を示す。

40

#### 【0021】

語「電力状態」又は「電力モード」は、一般に、プロセッサ又はSoC (System-on-Chip) の性能レベルを言う。電力状態は、2011年11月23日付で公開されたアドバンスド・コンフィグレーション・アンド・パワー・インターフェイス (ACPI ; Advanced Configuration and Power Interface) 規格の改訂5.0によって定義されてよい。なお、実施形態は、ACPI電力状態に制限されない。電力状態を定義する他の標準又は非標準も使用されてよい。

#### 【0022】

図1Bは、本開示の一実施形態に従って、1つ以上のDLDO VRを備えた電力アーキテクチャ120を表す。一実施形態において、電力アーキテクチャ120は、プロセッサ121、電力モジュール集積回路 (PMIC ; power module integrated circuit)

50

122、及びオペレーティングシステム123を有する。

【0023】

一実施形態において、プロセッサ121は、Nが1よりも大きい整数であるとして、1つ以上のプロセッシングコア125<sub>1~N</sub>を有する。一実施形態において、制御ユニット124（例えば、電力制御ユニット（PCU；power control unit））は、プロセッサ121の様々なコンポーネントへ電源を供給するように少なくとも2つのVID（電圧識別）コードを生成するよう動作する。

【0024】

一実施形態において、PCU124は、VID127（外部VID又は第1VIDとも呼ばれる。）をPMIC122へ送出する。一実施形態において、PMIC122はオフダイVRであり、すなわち、プロセッサ121と同じダイに集積されていない。一実施形態において、PMIC122は、プロセッサ121のためのパッケージと同じパッケージに位置してよい。一実施形態において、PMIC122は、プロセッサ121と完全に一体化される（すなわち、PMIC122はプロセッサ121と同じダイにある。）。

10

【0025】

一実施形態において、VID127は、7ビットのVIDコードである。他の実施形態では、より少ない又はより多いビットのコードが、VIDを表すために使用されてよい。一実施形態において、VID127は、VID127に対応する電力供給を提供するようPMIC122に要求するためのリクエストコードである。一実施形態において、PMIC122は、外部電源126を（例えば、電源出力、コンピュータバッテリ、などから）受け、VID127に対応するレギュレートされた第1電力供給128を生成する。例えば、VID127は、1.15Vが電力プロセッサ121に必要とされることをPMIC122に示す。次いで、PMIC122は、レギュレートされた1.15V電源を第1電力供給として生成する。一実施形態において、幾つか又は全てのプロセッシングコア125<sub>1~N</sub>は、第1電力供給128を受ける。

20

【0026】

一実施形態において、PCU124は、第2VID129（内部VIDとも呼ばれる。）を幾つか又は全てのプロセッサコア125<sub>1~N</sub>へ送出する。一実施形態において、夫々のプロセッサコアは、独立したVID（簡単のために単一の信号バス129として示される。）を受ける。そのような実施形態において、夫々の独立したVID129は、個々のプロセッサコアのための電力供給設定を提供する。一実施形態において、夫々のプロセッシングコアは、DLDO VR、例えば、「N」が整数であるとして、130<sub>1~N</sub>を有する。DLDO VRは図2を参照して説明される。

30

【0027】

図1Bを参照し直すと、一実施形態において、夫々のDLDO VRは、第1電力供給128を入力電源として受け、そのVID129を更に受ける。VID129は、そのコアのための特定のレベルの出力電源を生成するようDLDO VRに指示するために使用される。例えば、DLDO VR130<sub>1</sub>は、VID129を受け、コア-1 125<sub>1</sub>のために1.15Vの第1電力供給128を用いて0.9Vのレギュレートされた電力供給を生成する。他の例では、DLDO VR130<sub>2</sub>は、その対応するVID129を受け、コア-2 125<sub>2</sub>のために1.15Vの第1電力供給128を用いて0.9Vのレギュレートされた電力供給を生成する。上記の例を用いると、一実施形態において、DLDO VR130<sub>1</sub>は、第1電力供給128が外部VIDによって1.0Vに下げられる場合でさえ、前の1.15Vから、0.9Vのレギュレートされた電力供給をシームレス（すなわち、その負荷に対してシームレス）に提供することができる。

40

【0028】

一実施形態において、個々のプロセッサコア125<sub>1~N</sub>は、集積VR（例えば、DLDO VR130<sub>1~N</sub>）を介して第1電力供給128へ結合され、それらの集積VRの出力電圧は、内部VID129によって定義される。一実施形態において、内部VID129も、外部VID127のように7ビットのコードである。他の実施形態において、内

50

部 V I D 1 2 9 及び外部 V I D 1 2 7 は、異なるビット数を有する。

【 0 0 2 9 】

一実施形態において、外部 V I D 1 2 7 の設定は、最高の性能（例えば、高出力及び高周波数のターボモード）により動作したいと望むプロセッサコア（プロセッサコア 1 2 5<sub>1 ~ N</sub> の中のプロセッサコア）によって必要とされる電圧によって定義される。一実施形態において、そのプロセッサコアの D L D O V R は、バイパスモードにおいて動作し、内部 V I D 1 2 9 を受けて、D L D O V R のコントローラに、D L D O V R の全てのパワーゲートをオンさせる。そのような実施形態において、より低い性能要件を有する全ての他のプロセッサコアに関して、それらのプロセッシングコアのための内部 V I D 1 2 9 は、対応する D L D O V R（又は集積 V R）が、必要とされる性能のための要件に適合するようより低い出力電圧を有するように、設定される。

10

【 0 0 3 0 】

一実施形態において、最高の性能で動作するプロセッシングコアにおいて、その集積 V R（すなわち、D L D O V R）はバイパスモードにおいて動作する（すなわち、全て又はほとんどのパワーゲートはオンされるので、2つ以上の V R のカスケーディング効果により電力損失はない（又は略零である）。そのような実施形態において、より低い性能モードで動作する全ての他のプロセッシングコアについて、対応する V R（すなわち、より低い性能モードで動作するそれらのプロセッサの D L D O V R）のための入力供給電圧はスケールダウンされるので、電力はセーブされる。一実施形態において、全てのプロセッシングコア 1 2 5<sub>1 ~ N</sub> が同じ性能モードにおいて動作している場合には、全ての集積 V R はバイパスモードにあり、プロセッシングコア 1 2 5<sub>1 ~ N</sub> の電圧は、外部 V I D 1 2 7 によって設定される。一実施形態において、異なるプロセッシングコアは、異なる電力状態へとシームレスに遷移することができ、内部及び外部 V I D ( 1 2 9 及び 1 2 7 ) は、様々なシナリオに必要とされるように変更され得る。

20

【 0 0 3 1 】

一実施形態において、夫々の D L D O V R は、全ての動作点について応答を高速化するよう D L D O V R の動作範囲にわたって一様なゲインを提供するコントローラを有する。一実施形態において、動作範囲にわたる一様なゲインは、動作範囲の関数である余得係数をフィルタ伝達関数に加えることによって達成される。

30

【 0 0 3 2 】

図 2 は、本開示の一実施形態に従って、D L D O V R 2 0 0（例えば、D L D O V R 1 3 0<sub>1</sub>）を表す。いずれかの他の図の要素と同じ参照符号（又は名称）を有する図 2 の要素は、記載されているのと同様の何らかの方法において動作又は機能することができるが、そのように制限されないことが指摘される。

【 0 0 3 3 】

一実施形態において、D L D O V R 2 0 0 は、ロジック 2 0 1 及びパワーゲート 2 0 2 を有して、ゲート電力供給 2 1 3 を負荷 2 0 3 へ供給する。一実施形態において、ロジック 2 0 1 は、制御ユニット 2 0 4 、アナログ - デジタルコンバータ（A D C）2 0 5 、及びデジタル - アナログコンバータ（D A C）2 0 6 を有する。一実施形態において、制御ユニット 2 0 4 は、コントローラ 2 0 4 a 及びデコーダ 2 0 4 b を有する。一実施形態において、コントローラ 2 0 4 a は、A D C 2 0 5 の出力 2 1 0 を受けて、パワーゲート 2 0 2 の強さを表す信号 2 1 1 を生成する。

40

【 0 0 3 4 】

一実施形態において、コントローラ 2 0 4 a は、D L D O V R 2 0 0 の動作範囲にわたって一様なゲインを引き起こして、全ての動作点について応答を高速化する。一実施形態において、動作範囲にわたる一様なゲインは、動作点の関数である余得係数をフィルタ伝達関数に加えることによって達成される。

【 0 0 3 5 】

一実施形態において、デコーダ 2 0 4 b は、信号 2 1 1 を受信し、それをデジタルコード 2 1 2 へと復号して、パワーゲート 2 0 2 をオン / オフする。一実施形態において、デ

50

コーダ 204b は、バイナリ符号化されたデジタルコード 212 を生成する。一実施形態において、デコーダ 204b は、サーモメータ符号化されたデジタルコード 212 を生成する。他の実施形態では、デコーダ 204b は、デジタルコード 212 を生成するために他の形式の符号化スキームを用いる。

【0036】

一実施形態において、デコーダ 204b は、D L D O V R 200 にバイパスモードにおいて動作するよう指示する P C U 124 からのバイパス信号を受信する。一実施形態において、デコーダ 204b は、バイパス信号がバイパスモードを示す場合に全ての（又は略全ての）パワーゲートをオンさせるデジタルコード 212 を生成する。そのような実施形態において、A D C 205 の出力及びコントローラ 204a はバイパスされる。一実施形態において、全ての（又は略全ての）パワーゲート 202 がオンされる場合に、ゲート電力供給 213 は、非ゲート電力供給 128（第 1 電力供給 128 と同じ。）と（電圧レベル及び電流ドライブにおいて）略同じである。一実施形態において、D L D O V R 200 が通常モード（すなわち、L D O モード）において動作すべきことをバイパス信号が示す場合に、デコーダ 204b は、コントローラ 204a からの信号 211 を復号する。そのような実施形態において、A D C 205 はバイパスされず、208 から 212 のフィードバックループが機能する。

10

【0037】

一実施形態において、デコーダ 204b は、パワーゲート 202 を有効又は無効にする p g t \_ e n 信号（パワーゲート・イネーブル）を受信する。例えば、プロセッサモジュールがより低い又は最低の電力状態において動作する場合に、パワーゲート 202 はオフされて、ゲート電力供給 213 は浮いている。この例では、p g t \_ e n 信号は、デコーダ 204b に、パワーゲート 202 における全てのパワーゲートデバイスをオフするデジタルコード 212 を生成するよう指示する。一実施形態において、p g t \_ e n 信号が有効にされる場合に、デコーダ 204b は、通常（すなわち、L D O モード）又はバイパスモードにおいて動作する。

20

【0038】

一実施形態において、コントローラ 204a は、ゲート電力供給 213 のデジタル表現を受け、ゲート電力供給 213 を上げるべきか、それとも下げるべきかを決定する。一実施形態において、L D O モードの間、制御ユニット 204 は、パワーゲート 202 のデバイスをオン又はオフさせて、（負荷 203 の）所与の負荷電流のためのゲート電力供給 213 を達成するようパワーゲート 202 の実効抵抗を調節する。そのような実施形態において、パワーゲート 202 は、広い動作範囲を持った線形電圧レギュレータのように動作する。一実施形態において、コントローラ 204a は、D L D O V R 200 における如何なる支配極（dominant pole）も補償する。

30

【0039】

一実施形態において、コントローラ 204a は、全ての動作範囲について応答を高速化するよう D L D O V R 200 の動作範囲にわたって一様なゲインを提供する。一実施形態において、動作範囲にわたる一様なゲインは、動作点の関数である余得係数をフィルタ伝達関数に加えることによって達成される。

40

【0040】

実施形態において、パワーゲート 202 は、非ゲート電力供給 128 とゲート電力供給 213 との間に結合されているソース及びドレイン端子を有する p 形デバイス（‘N’ が 1 よりも大きい整数であるとして、M P 1 ~ M P N）を有する。そのような実施形態において、p 形デバイスのゲート端子は、デジタルコード 212 によって駆動される。一実施形態において、パワーゲート 202 は、非ゲート電力供給 128 とゲート電力供給 213 との間に結合されているソース及びドレイン端子を有する n 形デバイス（図示せず。）を有する。そのような実施形態において、n 形デバイスのゲート端子は、デジタルコード 212 の逆数によって駆動される。一実施形態において、パワーゲート 202 は、非ゲート電力供給 128 とゲート電力供給 213 との間に結合されている n 形及び p 形デバイスの

50

組み合わせを有する。そのような実施形態において、p形デバイスのゲート端子は、デジタルコード212によって駆動され、一方、n形デバイスのゲート端子は、デジタルコード212の逆数によって駆動される。

【0041】

一実施形態において、抵抗は、n形及び/又はp形デバイスに直列に結合される。このとき、抵抗の一方の端部は、n形及び/又はp形デバイスのソース/ドレイン端子へ結合され、一方で、抵抗の他方の端部は、ゲート電力供給213へ結合される。他の実施形態において、トランジスタと能動/受動デバイスとの他の組み合わせは、デジタルコード212(及び/又はデジタルコード212の逆数)によって制御されるパワーゲート202を実装するために使用されてよい。一実施形態において、パワーゲート202のデバイスは、トライオード領域(又は線形領域)において動作し、ゲート電力供給213は、パワーゲート202のデバイスをオン及び/又はオフすることによって(制御ユニット204によって)変調される。

10

【0042】

一実施形態において、DLD0 VR200は2極システムである。第1の極は、ゲート電力供給213と関連した極であって、負荷203のインピーダンス及びパワーゲート202の出力インピーダンスによって定義される。第2の極は、定常状態エラーを零に減らすよう原点においてコントローラ204によって導入される積分極である。一実施形態において、制御ユニット204は、負荷203のインピーダンス及び(負荷203から見た)パワーゲート202の出力インピーダンスによって定義される、ゲート電力供給213と関連した極を補償する。そのような実施形態において、ゲート電力供給213と関連した極は、零を導入することによって、ループゲイン及びバンド幅を下げるこなしに補償される。制御ユニット204によって実行されるリード補償は、DLD0 VR200のバンド幅及びゲインを改善する。リード補償を実行するコントローラ204aの数学モデルは、図3を参照して説明される。

20

【0043】

図2を参照し直すと、一実施形態において、ADC205はフラッシュ型ADCである。一実施形態において、ADC205は窓化フラッシュ型ADCである。一実施形態において、ADC205はシグマ・デルタ型ADCである。他の実施形態において、ADC205はフルフラッシュ型ADCである。一実施形態において、ADC205は、「N」が1よりも大きい整数であるとして、複数の補償器207-1~207-Nを有する。この例では、N=6であり、故に、ADC205は、6つの補償器207-1~207-6を有する6ビットADCである。一実施形態において、補償器207-1は、DAC206からの入力及びゲート電力供給213からの他の入力を受ける差動補償器である。補償器207-1の出力は、ゲート電力供給213が、基準電圧バス209の基準電圧の1つであるDAC206からの入力よりも高いか又は低いかを示すデジタル信号である。

30

【0044】

一実施形態において、DAC206は、内部VID129を受け、それを、内部VID129のアナログ表現である基準信号209のバスへ変換する。一実施形態において、DAC206は、基準信号209のバスを生成し、基準信号の夫々は電圧(例えば、12mV)で分けられる。他の実施形態では、他の細かさのレベルが基準信号209のために使用されてよい。一実施形態において、DAC206は、直列につなぎ合わされた抵抗の列により実装されてよい。一実施形態において、DAC206はカレントステアリング型DACである。他の実施形態において、DAC206は、バイナリ重み付け入力型DACの代わりであるR/2R DACである。

40

【0045】

一実施形態において、補償器207-6は、基準信号209のバスから第1基準電圧を受ける。一実施形態において、補償器207-6は、基準信号のバスから第2基準電圧を受ける。第2基準電圧は、「X」が数字であるとして、第1基準電圧よりも大きい「X」mVである。一実施形態において、補償器207-1は、基準信号209のバスから第6

50

基準電圧を受ける。第6基準電圧は、第1基準電圧よりも6倍大きい‘X’mVである。他の実施形態において、ADC205の補償器への基準信号209の割り当ての順序は、逆であってよい。

#### 【0046】

一実施形態において、ADC205の出力210は、ゲート電力供給213のデジタル表現を示す。一実施形態において、出力210は、サーモメータ符号化されたコードであって、サーモメータ-バイナリコンバータ(図示せず。)によってバイナリコードに変換される。バイナリコードは、制御ユニット204へ与えられる。他の実施形態において、ADC205の出力210は、サーモメータコードからバイナリコードへ変換する必要なしに直接に制御ユニット204によって受け取られる。

10

#### 【0047】

一実施形態において、制御ユニット204は、制御ユニット204のコンポーネントがデジタルであることから、RTL(レジスタハードウェア言語; register hardware language)を用いて合成され得る。DLDO VR200においてデジタル制御ユニット204を用いる幾つかの技術的効果がある。特に制御ユニット204及び一般にDLDO VR200の幾つかの制限されない技術的効果には、DLDO VR200の制御ユニット204がスタンバイモードにおいて自己消費電流が低い合成ロジックであることから、制御ユニット204におけるDC(直流)電流経路のおおよその削除がある。

#### 【0048】

一実施形態において、コントローラ204aの係数はプログラム可能であって、DLDO VR200におけるループが、SOCが製造された後でさえ、後に調整されることを可能にする。一実施形態において、コントローラ204aは、DLDO VR200の出力ノードにおいて極を補償し、故に、DLDO VRループにおいて存在するDCゲインエラーは略零である。一実施形態において、DLDO VR200は、デジタルコード212を用いてパワーゲート202のソフトスタートを可能にする。DLDO VR200は、設計者が、負荷203の全ての部分への一様な電力供給を確かにするよう同様の重みを持ったパワーゲートデバイス(例えば、MP1~MON)の分布にわたって制御を有することを可能にする。これは、例えば、負荷ラインが非一様な電圧降下を引き起こさないことを確かにする。なお、そのような非一様な電圧降下に基づき、負荷の部分は電流を引き込む。

20

#### 【0049】

一実施形態において、DLDO VR200は、VRのドループ応答を改善するよう非対称/非線形なゲイン関数のような非線形制御機能を用いることを可能にする。例えば、ADC205へのエラー電圧が窓化ADCの範囲を超えるほど十分に高い場合に、エラーは、DLDO VR200を線形ゲイン制御から脱せさせるほど十分に高い(すなわち、区域外である)と考えられる。この条件において、パワーゲート202における多数(プログラム可能な数)のFETは、追加の電荷を負荷203へ供給するよう1クロック周期において即座にオンされる。そのような非線形制御機能は、一実施形態に従って、供給電圧208におけるドループを補償するために使用される。

30

#### 【0050】

一実施形態において、DLDO VR200は、デジタル内部VIDコード129によって定義される入力電圧(例えば、基準信号209)を可能にする。これは、デジタル領域において実施するのが(アナログ回路と比較して)より容易である。一実施形態において、DLDO VR200は、(通常のLDOと比較して)DLDO VR200のより多くの回路がデジタルであるので、より簡単なDFT(Design-for-Test)を集積することを可能にする。そのようなDFTは、HVM(High Volume Manufacturing)試験を可能にすることができる。

40

#### 【0051】

DLDO VR200を使用する1つの動機は、プロセッサ又はSOCのプロセッサコア(又はモジュール)が小さいステップ(例えば、12mV)においてバイパスからレギ

50

ュレーションモード（すなわち、LDOモード）へ滑らかに遷移することができる。これは、電力状態の動的变化を伴ったプロセッサ又はSoC性能に基づきゲート電力供給213の変調を可能にする。一実施形態において、DLDO VR200はまた、同程度の性能である夫々のプロセッサコア（又はモジュール）へのゲート電力供給213の微調整を可能にする（例えば、ターボモード202、HFM203、など）。

#### 【0052】

プロセス変動に起因して、同じ性能レベルで機能することに関してさえ、異なるプロセッサコア（例えば、125<sub>1-N</sub>）は異なる電圧を必要としてよい。例えば、より遅いプロセッサコアは、同じ性能を生み出すために、より高い供給電圧を必要としてよく、より速いプロセッサコアは、より遅いプロセッサと同じ性能を生み出すために、より低い供給電圧を必要としてよい。一実施形態において、内部VID129は、入出力ロジックにおいて電圧レベルシフタを必要とすることなしに所定の（又はプログラム可能な）量だけ夫々のプロセッサコアへの供給電圧を調整する能力を提供する。一実施形態において、所定の（又はプログラム可能な）量は±50mVである。他の実施形態では、他の電圧レベルが所定の（又はプログラム可能な）量のために使用されてよい。（内部VID129を介した）この機能は、個々のプロセッサコアが適切な電圧へと調整され得るので、更なる電力節約をシステムに与える。

10

#### 【0053】

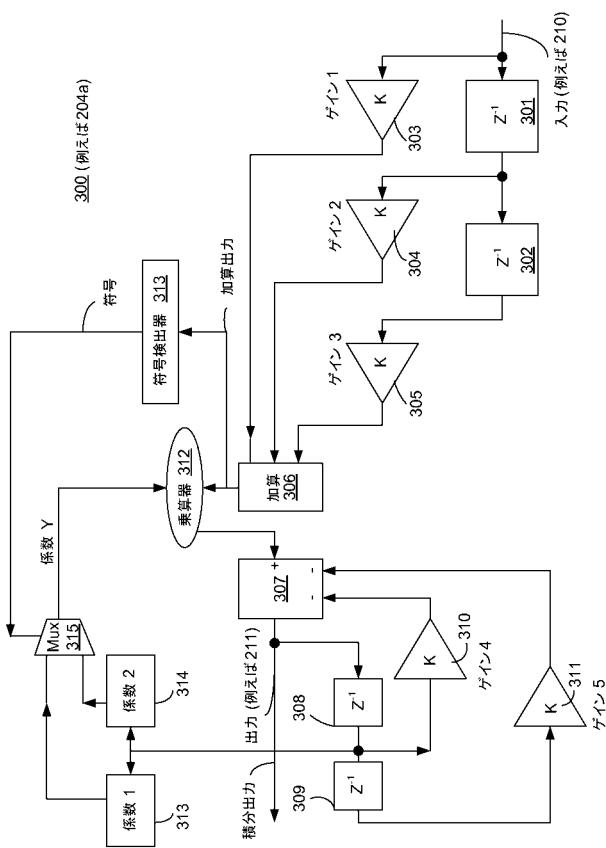

図3は、本開示の一実施形態に従って、DLDO VR200のコントローラ（例えば、204a）を実装する論理モデル300を表す。いずれかの他の図の要素と同じ参照符号（又は名称）を有する図3の要素は、記載されているのと同様の何らかの方法において動作又は機能することができるが、そのように制限されないことが指摘される。

20

#### 【0054】

一実施形態において、論理モデル300は、ADC205から入力210を受ける第1遅延段301（Z<sup>-1</sup>）を有する。一実施形態において、遅延段301の出力は、第2遅延段302（Z<sup>-1</sup>）によって受け取られる。一実施形態において、入力210並びに遅延段301及び302からのその遅延されたバージョンは、ゲイン段303（ゲイン1）、304（ゲイン2）及び305（ゲイン3）によって夫々増幅される。ここで、'K'はゲイン量を示す。一実施形態において、ゲイン段303、304及び305の出力は、加算ユニット306によって加算される。

30

#### 【0055】

一実施形態において、加算ユニット306の出力は、乗算器312によって受け取られる。一実施形態において、加算ユニット306の出力は、符号検出器313によって受け取られる“加算出力”である。一実施形態において、符号検出器313は、前の段からのバイナリコードが正又は負であるかどうかを判定するロジックとして実装される。符号検出器313は、加算出力の符号を決定する。一実施形態において、加算出力の正の符号は、ループゲインを低減する方向を示し、一方、負の符号は、ループゲインを増大させる方向を示す。一実施形態において、符号の方向に依存して、係数がマルチプレクサ315によって選択される。一実施形態において、この係数（すなわち、マルチプレクサ315の出力）は、乗算器312によって、加算ユニット306からの加算出力に乗じられる。一実施形態において、マルチプレクサ315の出力は、論理ユニット307（積分器ともここでは称される。）へ供給される。

40

#### 【0056】

一実施形態において、論理ユニット307は、出力を出力の前の値と加算し、（ゲインユニット310及び311からの）2つの信号を減じる。一実施形態において、コントローラ204aの出力211（積分出力とも呼ばれる。）は、第3遅延段308（Z<sup>-1</sup>）によって遅延される。一実施形態において、第3遅延段308の出力は、第4遅延段309（Z<sup>-1</sup>）によって更に遅延される。一実施形態において、第3及び第4遅延段（夫々308及び309）の出力は、ゲインユニット310（ゲイン4）及び311（ゲイン5）によって夫々増幅される。一実施形態において、ゲインユニット310及び311の出

50

力は、論理ユニット 307 によって受け取られる。一実施形態において、論理ユニット 307 は、ゲインユニット 310 及び 311 の出力を加算ユニット 306 の出力から減じて出力 211 を生成する。一実施形態において、出力 211 は、パワーゲート 202 を制御するデジタルコード 212 を生成するようデコーダ 204b によって復号される。

#### 【0057】

一実施形態において、第 3 遅延段 308 の出力は、それをスカラー係数へと変換する論理ユニット 313 及び 314 へ供給される。一実施形態において、係数 1 は、加算出力がゲインの正方向を有する場合に（符号を介して）マルチプレクサ 315 によって選択される大きい正の係数である。一実施形態において、係数 2 は、加算出力がゲインの負方向を有する場合に（符号を介して）マルチプレクサ 315 によって選択される、より低い係数又は 1 である。

10

#### 【0058】

実施形態において、ループのゲインは、動作点の関数として変更される。一実施形態において、ゲインは、係数 Y（すなわち、マルチプレクサ 315 の出力）を伝達関数の分子、すなわち、加算ユニット 306 からの加算出力に乗じることによって、変更される。分子 'N' は、 $N = N_1 \times V_{in}(n-2) + N_2 \times V_{in}(n-1) + N_3 \times V_{in}(n)$  によって定義される。ここで、“N1”は段 305 のゲイン 3 であり、“N2”は段 304 のゲイン 2 であり、“N3”は段 303 のゲイン 1 であり、 $V_{in}(n)$  は入力 210 であり、 $V_{in}(n-1)$  は遅延段 301 の出力であり、 $V_{in}(n-2)$  は遅延段 302 の出力である。

20

#### 【0059】

一実施形態において、分子値 'N' は、伝達関数の出力状態によって決定されるゲイン係数 'Y' を乗じられる。一実施形態において、パワー FET への  $V_{out}$  コードが高い場合に、システムのゲインは低い。この低ゲインは、より高い値を分子 'N' に乗じることによって補償される。そのような実施形態において、伝達関数のゲインは、全ての動作点について平らにされる。

#### 【0060】

ゲインは、コードが大きくなる場合（ゲインを低減する方向）及びコードが小さくなる場合（ゲインを増大させる方向）において異なるので、一実施形態に従って、分子値（すなわち、加算出力の符号）が正である場合及び負である場合において異なる乗率が分子に適用される。一実施形態において、「N」が正味正の値を有する場合に、マルチプレクサ（すなわち、 $M_{ux}$ ）315 は、ループゲインを増大させるよう係数 1 を選択する。一実施形態において、「N」が正味負の値を有する場合に、マルチプレクサ 315 は、ループゲインを下げるよう係数 2 を選択する。

30

#### 【0061】

一実施形態において、理想的に、「N」に乗じられるべきゲイン係数（313 及び 314 の出力のうちの一方）は、その出力自体の値である。上述されたように、分子 'N' は、 $N = N_1 \times V_{in}(n-2) + N_2 \times V_{in}(n-1) + N_3 \times V_{in}(n)$  によって定義される。例えば、積分器の出力が 1 のバイナリコードである場合に、「N」はそのままで使用され、積分器の出力が 2 のバイナリコードである場合に、システムのゲインは、出力値の係数だけ減り、出力に比例するゲインによって補償される。一実施形態において、より高い負荷電流に関して、様々な実施形態によって記載される適応ゲインによれば、ADC 205 の分解能はパワー FET 202 の細かさよりも高いことが可能である。この場合に、リップルが電圧出力 208 において引き起こされ得る。このリップルを回避するよう、1 に満たない値を持ったゲイン係数が使用される。

40

#### 【0062】

一実施形態において、論理ユニット 307 は、ゲインをエラー信号に加え、積分関数を加えて DC エラーを零（又は零近く）に減らし、更には、極及び零を加えて負荷極を補償する。エラー信号は、レギュレータ（例えば、200）の出力ノード（例えば、208）及び基準ノード（例えば、209）の間の電圧差である。一実施形態において、加えられ

50

た零は、負荷極の影響を補償し、加えられた極は、ゲインがある周波数を超えて 0 dB より低く減衰されることを確かにする。

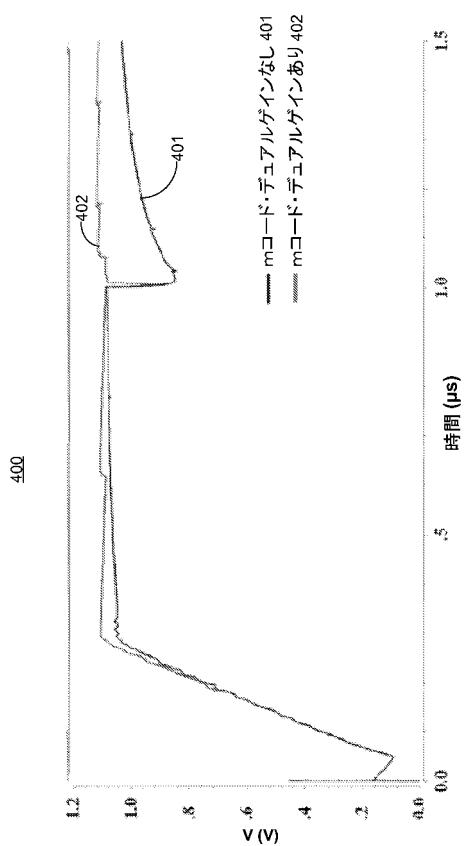

【0063】

図 4 は、本開示の一実施形態に従って、コントローラ 204a の技術的効果を示すプロット 400 を表す。ここで、x 軸はマイクロ秒 (μs) における時間であり、y 軸は電圧 (V) である。プロット 400 は 2 つの波形を示す。上側の波形 401 は、乗算効果を備えたコントローラ 204a を使用する過渡応答時間を示す。波形 401 の下側にある波形 402 は、乗算効果がコントローラにおいて使用されない場合の過渡応答である。

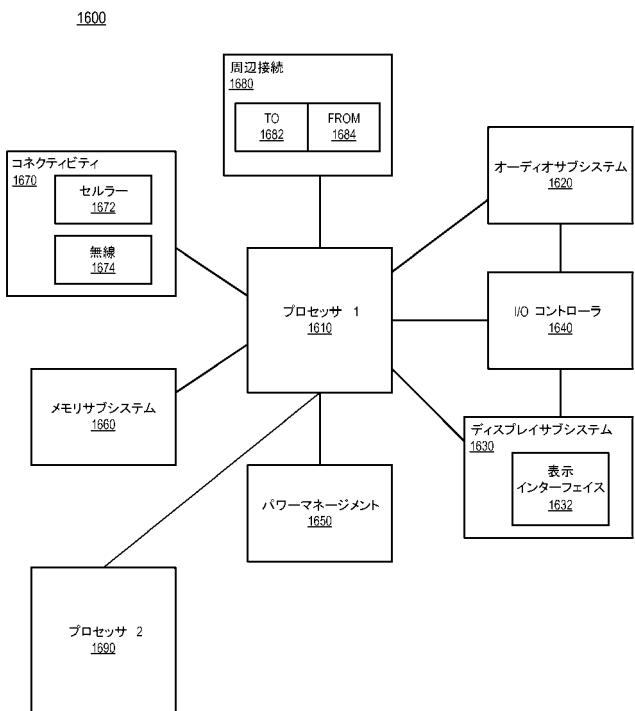

【0064】

図 5 は、本開示の一実施形態に従って、D L D O V R を備えたスマートデバイス又はコンピュータシステム又は S o C を表す。図 5 は、フラット・サーフェス・インターフェイス・コネクタが使用され得るモバイルデバイスの実施形態のブロック図を表す。一実施形態において、コンピュータデバイス 1600 は、例えば、コンピュータタブレット、携帯電話機若しくはスマートフォン、無線対応電子リーダー、又は他の無線モバイルデバイスのような、モバイルコンピュータデバイスを表す。特定のコンポーネントが一般的に示されており、そのようなデバイスの全てのコンポーネントがコンピュータデバイス 1600 において示されているわけでないことが理解されるであろう。

10

【0065】

一実施形態において、コンピュータデバイス 1600 は、実施形態に従う D L D O V R を備えた第 1 プロセッサ 1610 を有する。一実施形態において、コンピュータデバイス 1600 は、ここで論じられている実施形態に従う D L D O V R を備えた第 2 プロセッサ 1690 を有する。一実施形態において、第 2 プロセッサ 1690 は任意である。I / O デバイスを備えたコンピュータデバイス 1600 の他のブロックも、実施形態の D L D O V R を有してよい。本開示の様々な実施形態は、例えば、無線インターフェイスのような、1670 内のネットワークインターフェイスを更に有してよく、それにより、システム実施形態は、無線デバイス、例えば、携帯電話機又はパーソナルデジタルアシスタントに組み込まれてよい。

20

【0066】

一実施形態において、プロセッサ 1610 は、例えば、マイクロプロセッサ、アプリケーションプロセッサ、マイクロコントローラ、プログラム可能論理デバイス、又は他のプロセッシング手段のような、1 つ以上の物理デバイスを有することができる。プロセッサ 1610 によって実行されるプロセッシング動作には、アプリケーション及び / 又はデバイス機能が実行されるオペレーティングプラットフォーム又はオペレーティングシステムの実行が含まれる。プロセッシング動作には、人間のユーザによる若しくは他のデバイスによる I / O (入出力 : input/output) に関する動作、電力管理に関する動作、及び / 又はコンピュータデバイス 1600 を他のデバイスへ接続することに関する動作が含まれる。プロセッシング動作には、オーディオ I / O 及び / 又はディスプレイ I / O に関する動作も含まれてよい。

30

【0067】

一実施形態において、コンピュータデバイス 1600 は、オーディオサブシステム 1620 を有する。オーディオサブシステム 1620 は、オーディオ機能をコンピュータデバイスに提供することに関連したハードウェア (例えば、オーディオハードウェア及びオーディオ回路) 及びソフトウェア (例えば、ドライバ、コーデック) コンポーネントを表す。オーディオ機能には、スピーカ及び / 又はヘッドホン出力並びにマイクロホン入力が含まれ得る。そのような機能のためのデバイスは、コンピュータデバイス 1600 と一体化されるか、あるいは、コンピュータデバイス 1600 へ接続され得る。一実施形態において、ユーザは、プロセッサ 1610 によって受け取られて処理されるオーディオコマンドを与えることによって、コンピュータデバイス 1600 と対話する。

40

【0068】

ディスプレイサブシステム 1630 は、ユーザがコンピュータデバイス 1600 と対話

50

するための視覚的及び／又は触覚的な表示を提供するハードウェア（例えば、表示デバイス）及びソフトウェア（例えば、ドライバ）を表す。ディスプレイサブシステム 1630 は、表示をユーザに提供するために使用される特定のスクリーン又はハードウェアデバイスを含む表示インターフェイス 1632 を有する。一実施形態において、表示インターフェイス 1632 は、表示に関する少なくとも何らかの処理を実行する、プロセッサ 1610 とは別個のロジックを有する。一実施形態において、ディスプレイサブシステム 1630 は、ユーザへ出力及び入力の両方を提供するタッチスクリーン（又はタッチパッド）デバイスを有する。

#### 【0069】

I/Oコントローラ 1640 は、ユーザとのインタラクションに関するハードウェアデバイス及びソフトウェアコンポーネントを表す。I/Oコントローラ 1640 は、オーディオサブシステム 1620 及び／又はディスプレイサブシステム 1630 の部分であるハードウェアを管理するよう動作する。加えて、I/Oコントローラ 1640 は、コンピュータデバイス 1600 へ接続する追加のデバイスのための接続点を表し、それを通じてユーザはシステムと対話し得る。例えば、コンピュータデバイス 1600 に取り付けられ得るデバイスには、マイクロホンデバイス、スピーカ若しくはステレオシステム、ビデオシステム若しくは他の表示デバイス、キーボード若しくはキーパッドデバイス、又はカードリーダ若しくは他のデバイスのような特定の用途により使用される他の I/O デバイスが含まれ得る。

#### 【0070】

上述されたように、I/Oコントローラ 1640 は、オーディオサブシステム 1620 及び／又はディスプレイサブシステム 1630 と相互作用することができる。例えば、マイクロホン又は他のオーディオデバイスを通じた入力は、コンピュータデバイス 1600 の1つ以上のアプリケーション又は機能のための入力又はコマンドを与えることができる。加えて、オーディオ出力は、ディスプレイ出力の代わりに、又はそれに加えて供給され得る。他の例では、ディスプレイサブシステム 1630 がタッチスクリーンを有する場合には、表示デバイスは入力デバイスとしても働き、I/Oコントローラ 1640 によって少なくとも部分的に管理され得る。I/Oコントローラ 1640 によって管理される I/O 機能を提供するようコンピュータデバイス 1600 には更なるボタン又はスイッチも存在することができる。

#### 【0071】

一実施形態において、I/Oコントローラ 1640 は、例えば、加速度計、カメラ、光センサ若しくは他の環境センサ、又はコンピュータデバイス 1600 に含まれ得る他のハードウェアのような、デバイスを管理する。入力は、直接的なユーザインタラクションの部分であることができるとともに、環境入力をシステムに与えてその動作（例えば、ノイズのフィルタリング、輝度検出のためのディスプレイの調整、カメラのフラッシュの適用、又は他の機能）に影響を及ぼすことができる。

#### 【0072】

一実施形態において、コンピュータデバイス 1600 は、バッテリ電力使用量、バッテリの充電、及び電力節約動作に関する機能を管理するパワーマネジメント 1650 を有する。メモリサブシステム 1660 は、情報をコンピュータデバイス 1600 において記憶するためのメモリデバイスを有する。メモリは、不揮発性（メモリデバイスへの電力が中断される場合に状態が変化しない。）及び／又は揮発性（メモリデバイスへの電力が中断される場合に状態が不定である。）メモリデバイスを有することができる。メモリサブシステム 1660 は、アプリケーションデータ、ユーザデータ、音楽、写真、ドキュメント、又は他のデータとともに、コンピュータデバイス 1600 のアプリケーション及び機能の実行に関するシステムデータ（長期又は一時に関わらず。）を記憶することができる。

#### 【0073】

実施形態の要素は、コンピュータ実行可能命令（例えば、ここで論じられている如何な

10

20

30

40

50

る他のプロセスも実施する命令)を記憶するための機械可読媒体(例えば、メモリ1660)としても提供される。機械可読媒体(例えば、メモリ1660)には、制限なしに、フラッシュメモリ、光ディスク、CD-ROM、DVD-ROM、RAM、EPROM、EEPROM、磁気若しくは光学式カード、相変化メモリ(PCM; phase change memory)、又は電子若しくはコンピュータ実行可能命令を記憶するのに適した他のタイプの機械可読媒体が含まれてよい。例えば、本開示の実施形態は、遠隔のコンピュータ(例えば、サーバ)から要求元のコンピュータ(例えば、クライアント)へデータ信号によって通信リンク(例えば、モデム又はネットワーク接続)を介して転送され得るコンピュータプログラム(例えば、BIOS)としてダウンロードされてよい。

【0074】

10

コネクティビティ1670は、コンピュータデバイス1600が外部のデバイスと通信することを可能にするハードウェアデバイス(例えば、無線及び/又は有線コネクタ並びに通信ハードウェア)及びソフトウェアコンポーネント(例えば、ドライバ、プロトコルスタック)を有する。コンピュータデバイス1600は、他のコンピュータデバイス、無線アクセスポイント又は基地局のような別個デバイス、並びにヘッドセット、プリンタ又は他のデバイスのような周辺機器であってよい。

【0075】

20

コネクティビティ1670は、多種多様なタイプのコネクティビティを有することができる。一般的に言えば、コンピュータデバイス1600は、セルラーコネクティビティ1672及び無線コネクティビティ1674により表されている。セルラーコネクティビティ1672は、例えば、GSM(global system for mobile communications)又は変形若しくは派生、CDMA(code division multiple access)又は変形若しくは派生、TDM(time division multiplexing)又は変形若しくは派生、あるいは他のセルラーサービス標準を介して提供されるような、無線キャリアによって提供されるセルラーネットワークコネクティビティを言う。無線コネクティビティ(又は無線インターフェイス)1674は、セルラーではない無線コネクティビティを言い、パーソナルエリアネットワーク(例えば、Bluetooth(登録商標)、近距離通信、など)、ローカルエリアネットワーク(例えば、Wi-Fi(登録商標))、及び/又はワイドエリアネットワーク(例えば、WiMAX(登録商標))、あるいは、他の無線通信を有することができる。

30

【0076】

周辺接続1680は、終戦接続を行うハードウェアインターフェイス及びコネクタ並びにソフトウェアコンポーネント(例えば、ドライバ、プロトコルスタック)を有する。コンピュータデバイス1600は、他のコンピュータデバイスへの周辺機器であってよく(“to”1682)、更には、周辺機器を自身に接続されることも可能である(“from”1684)。コンピュータデバイス1600は、例えば、コンピュータデバイス1600においてコンテンツを管理すること(例えば、ダウンロード及び/又はアップロード、変更、同期化)のような目的のために、他のコンピュータデバイスへ接続するための“ドッキング”コネクタを一般的に備える。加えて、ドッキングコネクタは、コンピュータデバイス1600が、例えば、オーディオビジュアル又は他のシステムへ出力されるコンテンツを制御することを可能にする特定の周辺機器へ、コンピュータデバイス1600が接続することを可能にすることができる。

40

【0077】

独自仕様のドッキングコネクタ又は他の独自仕様の接続ハードウェアに加えて、コンピュータデバイス1600は、一般的な又は標準規格に基づいたコネクタを介して周辺機器接続1680を行うことができる。一般的なタイプには、ユニバーサル・シリアル・バス(USB; Universal Serial Bus)コネクタ(多種多様なハードウェアインターフェイスのいずれかを含むことができる。)、ミニディスプレイポート(MDP; Mini DisplayPort)を含むディスプレイポート、高精細マルチメディアインターフェイス(HDMI; High Definition Multimedia Interface)、ファイアワイヤ、又は他

50

のタイプが含まれ得る。

【0078】

「実施形態」、「一実施形態」、「幾つかの実施形態」又は「他の実施形態」との明細書中の言及は、実施形態に関連して記載される特定の機能、構造、又は特性が、必ずしも全ての実施形態ではなく、少なくとも幾つかの実施形態に含まれることを意味する。「実施形態」、「一実施形態」又は「幾つかの実施形態」の様々な出現は、必ずしも全てが同じ実施形態に言及しているわけではない。コンポーネント、機能、構造、又は特性が“含まれ得る”、“含まれてよい”、又は“含まれることがある”と明細書において述べられる場合に、その特定のコンポーネント、機能、構造、又は特性は含まれる必要はない。明細書又は特許請求の範囲において要素を単称形で呼ぶ場合に、それは、その要素がただ1つしか存在しないことを意味するわけではない。明細書及び特許請求の範囲において“更なる”要素と言及する場合に、それは、更なる要素が1つよりも多く存在していることを除外しない。

10

【0079】

更に、特定の特徴、構造、機能、又は特性は、1つ以上の実施形態において如何なる適切な方法においても組み合わされてよい。例えば、第1及び第2の実施形態に関連する特定の特徴、構造、機能、又は特性が相互排他的でない場合には、第1の実施形態は第2の実施形態と組み合わされてよい。

20

【0080】

本開示は、その具体的な実施形態と関連して記載されてきたが、そのような実施形態の多くの代替、改良及び変形は、上記の記載を鑑みて当業者に明らかであろう。例えば、他のメモリアーキテクチャ、例えば、動的RAM(DRAM)は、論じられている実施形態を使用してよい。本開示の実施形態は、添付の特許請求の範囲の広範な適用範囲内に入るように全てのそのような代替、改良及び変形を包含するよう意図される。

20

【0081】

加えて、集積回路( I C ; integrated circuit )チップ及び他のコンポーネントへのよく知られている電力 / 接地接続は、本開示を不明りょうにしないように、例示及び議論の簡単のために、提示されている図において図示されてもされなくてもよい。更に、配置は、本開示を不明りょうにしないように、更には、そのようなブロック図配置の実施に関する仕様が、本開示が実装されるプラットフォームに大いに依存するという事実を鑑みて(すなわち、そのような仕様は、当業者の範囲内に十分あるべきである。)、ブロック図形式において示されてよい。具体的な詳細(例えば、回路)が本開示の例となる実施形態を記載するために示される場合に、当業者に当然に、本開示は、そのような具体的な詳細によらずに、又はその変形により実施され得る。よって、記載は、制限ではない例示と見なされるべきである。

30

【0082】

以下の例は、更なる実施形態に関連する。例における細部は、1つ以上の実施形態においてどこでも使用されてよい。ここで記載される装置の全ての任意の特徴は、方法又はプロセスに関しても実装されてよい。

40

【0083】

例えば、デジタルバスによって制御される複数のパワーゲートトランジスタであって、第1電力供給を負荷へ供給し、第2電力供給を入力として受けるよう動作する前記複数のパワーゲートトランジスタと、前記第1電力供給を受け、該第1電力供給を表すデジタル出力を生成するアナログ - デジタルコンバータ(ADC)と、前記第1電力供給を表す前記デジタル出力を受け、前記複数のパワーゲートトランジスタを制御するための前記デジタルバスを生成して、前記複数のパワーゲートトランジスタの伝達関数が動作範囲にわたって略線形であるようにするコントローラとを有する装置が提供される。

【0084】

一実施形態において、前記コントローラは、前記複数のパワーゲートトランジスタ、前記ADC、及び前記コントローラによって形成されるループのゲインを変更するよう動作

50

し、前記コントローラは、動作点の関数として前記ループのゲインを変更するよう動作する。一実施形態において、前記コントローラは、直列につなぎ合わされた第1の複数の遅延ユニットであって、該第1の複数の遅延ユニットの中の1つの遅延ユニットが前記第1電力供給を表す前記デジタル出力を受ける、前記第1の複数の遅延ユニットと、前記第1の複数の遅延ユニットの夫々の出力のゲインを増幅する第1の複数のゲイン段と、加算された出力を生成するよう前記増幅された出力を加算する加算器とを有する。

#### 【0085】

一実施形態において、前記コントローラは、前記ループのゲインを変更するよう前記加算された出力に係数を乗じて、前記複数のパワーゲートトランジスタの伝達関数が動作範囲にわたって略線形であるようとする乗算器を有する。一実施形態において、前記コントローラは、前記加算された出力の符号を検出し、該検出された符号が前記係数を決定する符号検出器を有する。一実施形態において、前記コントローラは、直列につなぎ合わされた第2の複数の遅延ユニットであって、該第2の複数の遅延ユニットの中の1つの遅延ユニットが前記コントローラの出力を受ける、前記第2の複数の遅延ユニットと、前記第2の複数の遅延ユニットの夫々の出力のゲインを増幅する第2の複数のゲイン段とを有する。

10

#### 【0086】

一実施形態において、前記コントローラは、前記第2の複数の遅延ユニットの夫々の増幅された出力及び前記乗算器の出力を積分して、前記コントローラの出力を生成する積分器を有する。一実施形態において、前記複数のパワーゲートトランジスタはp形トランジスタである。一実施形態において、当該装置は、電圧識別信号(VID)を前記ADCのための複数のアナログ信号に変換するデジタル-アナログコンバータ(DAC)を更に有する。一実施形態において、前記VIDは電力制御ユニット(PCI)によって生成される。

20

#### 【0087】

一実施形態において、当該装置は、前記コントローラの出力を復号して、前記複数のパワーゲートトランジスタを制御するための前記デジタルバスを生成するデコーダを更に有する。一実施形態において、前記デコーダは、前記複数のパワーゲートトランジスタの略全てをオンすることによって、当該装置をバイパスモードにおいて作動させるよう動作する。一実施形態において、前記デコーダは、全ての前記複数のパワーゲートトランジスタをオフさせる前記デジタルバスを生成するよう動作する。

30

#### 【0088】

他の例では、メモリユニットと、該メモリユニットへ結合され、上記の装置に従う電圧レギュレータを備えるプロセッサとを有するシステムが提供される。一実施形態において、当該システムは、前記プロセッサがアンテナを通じて他のデバイスと通信することを可能にする無線インターフェイスを更に有する。一実施形態において、当該システムは表示ユニットを更に有する。一実施形態において、前記表示ユニットはタッチスクリーンである。

#### 【0089】

他の例では、第1電力供給を表すデジタル出力を受け、複数のパワーゲートトランジスタを制御するためのデジタルバスを生成して、前記複数のパワーゲートトランジスタの伝達関数が動作範囲にわたって略線形であるようとするコントローラと、前記コントローラの出力を復号して、前記複数のパワーゲートトランジスタを制御するための前記デジタルバスを生成するデコーダとを有する装置が提供される。

40

#### 【0090】

一実施形態において、前記コントローラは、前記複数のパワーゲートトランジスタ、アナログ-デジタルコンバータ(ADC)、及び前記コントローラによって形成されるループのゲインを変更するよう動作し、前記コントローラは、動作点の関数として前記ループのゲインを変更するよう動作する。一実施形態において、前記コントローラは、直列につなぎ合わされた第1の複数の遅延ユニットであって、該第1の複数の遅延ユニットの中の

50

1つの遅延ユニットが前記第1電力供給を表す前記デジタル出力を受ける、前記第1の複数の遅延ユニットと、前記第1の複数の遅延ユニットの夫々の出力のゲインを増幅する第1の複数のゲイン段と、加算された出力を生成するよう前記増幅された出力を積分する加算器とを有する。

【0091】

一実施形態において、前記コントローラは、前記ループのゲインを変更するよう前記加算された出力に係数を乗じて、前記複数のパワーゲートトランジスタの伝達関数が動作範囲にわたって略線形であるようにする乗算器を有する。一実施形態において、前記コントローラは、前記加算された出力の符号を検出し、該検出された符号が前記係数を決定する符号検出器を有する。一実施形態において、前記コントローラは、直列につなぎ合わされた第2の複数の遅延ユニットであって、該第2の複数の遅延ユニットの中の1つの遅延ユニットが前記コントローラの出力を受ける、前記第2の複数の遅延ユニットと、前記第2の複数の遅延ユニットの夫々の出力のゲインを増幅する第2の複数のゲイン段とを有する。一実施形態において、前記コントローラは、前記第2の複数の遅延ユニットの夫々の増幅された出力及び前記乗算器の出力を積分して、前記コントローラの出力を生成する積分器を有する。

【0092】

他の例では、メモリユニットと、該メモリユニットへ結合され、上記の装置に従う電圧レギュレータを備えるプロセッサとを有するシステムが提供される。一実施形態において、当該システムは、前記プロセッサがアンテナを通じて他のデバイスと通信することを可能にする無線インターフェイスを更に有する。一実施形態において、当該システムは表示ユニットを更に有する。一実施形態において、前記表示ユニットはタッチスクリーンである。

【0093】

要約は、読者が技術的開示の本質及び要点を確かめることを可能にするよう与えられている。要約は、それが特許請求の範囲の適用範囲及び意義を制限するために使用されないとの理解の下で提出される。特許請求の範囲は、これをもって詳細な説明に組み込まれる。夫々の請求項は、別個の実施形態として自立している。

【 図 1 A 】

【 図 1 B 】

【 図 2 】

〔 図 3 〕

【図4】

【図5】

## 【国際調査報告】

| <b>INTERNATIONAL SEARCH REPORT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                          | International application No.<br>PCT/US 2013/076298                                    |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------|-----------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|--------------------------------------------------------------------------------------------------------|------|---|--------------------------------------------------------------------------------------------------------|-----------|---|-------------------------------------------------------------------------------------------------------------------|------------|---|----------------------------------------------------------------------------------------------------|-------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br><i>G06F 1/26 (2006.01)</i><br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                          |                                                                                        |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br><b>G06F 1/00-1/30, 9/00-9/52, 11/00-11/30, 15/00-15/78, G05F 1/00-1/70, 5/00-5/08, G05B 11/00-11/38, 19/00-19/414, G01R 19/00, H03L 5/00</b><br>Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                          |                                                                                        |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br><b>PatSearch (RUPTO internal), USPTO, PAJ, Esp@cenet, Information Retrieval System of FIPS</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                          |                                                                                        |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category*</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="text-align: center; padding: 2px;">Y</td> <td style="padding: 2px;">US 2013/0305065 A1 (RENESAS ELECTRONICS CORPORATION) 14.11.2013, abstract, par. [0037], [0040]-[0042], [0044], [0048]-[0049], [0059], [0062]-[0063], [0067]-[0069], [0076]-[0079], fig.1</td> <td style="text-align: center; padding: 2px;">1-26</td> </tr> <tr> <td style="text-align: center; padding: 2px;">Y</td> <td style="padding: 2px;">US 5740420 A (ADVANCED MICRO DEVICES, INC.) 14.04.1998, col.5, line 44-col.6, line 24, claim 18, fig.3</td> <td style="text-align: center; padding: 2px;">1-26</td> </tr> <tr> <td style="text-align: center; padding: 2px;">Y</td> <td style="padding: 2px;">US 2012/0159219 A1 (LILLY HUANG et al.) 21.06.2012, paragraphs [0013]-[0017], [0023]-[0025], fig. 1, 4</td> <td style="text-align: center; padding: 2px;">10, 21-26</td> </tr> <tr> <td style="text-align: center; padding: 2px;">Y</td> <td style="padding: 2px;">US 5548192 A (HEWLETT-PACKARD COMPANY) 20.08.1996, col.1, lines 34-37, col. 4, line 46 -col. 5, line 43, fig.1, 4</td> <td style="text-align: center; padding: 2px;">3-7, 16-20</td> </tr> <tr> <td style="text-align: center; padding: 2px;">Y</td> <td style="padding: 2px;">US 2010/0176794 A1 (TING-CHIN TSEN) 15.07.2010, abstract, paragraphs [0007], [0009]-[0011], [0015]</td> <td style="text-align: center; padding: 2px;">5, 18</td> </tr> </tbody> </table> |                                                                                                                                                                                          |                                                                                        | Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | Y | US 2013/0305065 A1 (RENESAS ELECTRONICS CORPORATION) 14.11.2013, abstract, par. [0037], [0040]-[0042], [0044], [0048]-[0049], [0059], [0062]-[0063], [0067]-[0069], [0076]-[0079], fig.1 | 1-26 | Y | US 5740420 A (ADVANCED MICRO DEVICES, INC.) 14.04.1998, col.5, line 44-col.6, line 24, claim 18, fig.3 | 1-26 | Y | US 2012/0159219 A1 (LILLY HUANG et al.) 21.06.2012, paragraphs [0013]-[0017], [0023]-[0025], fig. 1, 4 | 10, 21-26 | Y | US 5548192 A (HEWLETT-PACKARD COMPANY) 20.08.1996, col.1, lines 34-37, col. 4, line 46 -col. 5, line 43, fig.1, 4 | 3-7, 16-20 | Y | US 2010/0176794 A1 (TING-CHIN TSEN) 15.07.2010, abstract, paragraphs [0007], [0009]-[0011], [0015] | 5, 18 |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                       | Relevant to claim No.                                                                  |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | US 2013/0305065 A1 (RENESAS ELECTRONICS CORPORATION) 14.11.2013, abstract, par. [0037], [0040]-[0042], [0044], [0048]-[0049], [0059], [0062]-[0063], [0067]-[0069], [0076]-[0079], fig.1 | 1-26                                                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | US 5740420 A (ADVANCED MICRO DEVICES, INC.) 14.04.1998, col.5, line 44-col.6, line 24, claim 18, fig.3                                                                                   | 1-26                                                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | US 2012/0159219 A1 (LILLY HUANG et al.) 21.06.2012, paragraphs [0013]-[0017], [0023]-[0025], fig. 1, 4                                                                                   | 10, 21-26                                                                              |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | US 5548192 A (HEWLETT-PACKARD COMPANY) 20.08.1996, col.1, lines 34-37, col. 4, line 46 -col. 5, line 43, fig.1, 4                                                                        | 3-7, 16-20                                                                             |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | US 2010/0176794 A1 (TING-CHIN TSEN) 15.07.2010, abstract, paragraphs [0007], [0009]-[0011], [0015]                                                                                       | 5, 18                                                                                  |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                          |                                                                                        |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier document but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                          |                                                                                        |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |

| Date of the actual completion of the international search<br><br>13 October 2014 (13.10.2014)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                          | Date of mailing of the international search report<br><br>30 October 2014 (30.10.2014) |           |                                                                                    |                       |   |                                                                                                                                                                                          |      |   |                                                                                                        |      |   |                                                                                                        |           |   |                                                                                                                   |            |   |                                                                                                    |       |