(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6399486号

(P6399486)

(45) 発行日 平成30年10月3日(2018.10.3)

(24) 登録日 平成30年9月14日(2018.9.14)

(51) Int.Cl.

F 1

H03F 3/34 (2006.01)

H03F 3/45 (2006.01)H03F 3/34

H03F 3/453/34

3/45A

Z

請求項の数 14 (全 22 頁)

(21) 出願番号 特願2014-144598 (P2014-144598)

(22) 出願日 平成26年7月14日 (2014.7.14)

(65) 公開番号 特開2016-21668 (P2016-21668A)

(43) 公開日 平成28年2月4日 (2016.2.4)

審査請求日 平成29年6月30日 (2017.6.30)

(73) 特許権者 305018292

株式会社エイアールテック

広島県東広島市西条町御園宇4781-4

(72) 発明者 村坂 佳隆

広島県東広島市西条大坪町10番29-1

205号 株式会社エイアールテック内

(72) 発明者 岩田 穆

広島県東広島市西条大坪町10番29-1

205号 株式会社エイアールテック内

審査官 緒方 寿彦

最終頁に続く

(54) 【発明の名称】演算增幅回路

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の入力端子と第2の入力端子の差動の信号を変調し前記の変調された差動の信号を増幅し復調して第1の出力端子と第2の出力端子に出力する差動增幅回路を有し、前記差動增幅回路は第1、第2の入力端子に入力された信号を第1のセレクタで選択して増幅して出力電流を生成し第2のセレクタで前記の出力電流の出力先として第1、第2の出力端子を選択する信号増幅ユニットをN個 (Nは4以上の偶数)と前記N個の信号増幅ユニットが出力できる電流の合計値を制限する回路と

10

前記第1の出力端子に電流を供給する第1の電流源と前記第2の出力端子に電流を供給する第2の電流源とを有し、前記N個の信号増幅ユニットにおいて第1のセレクタは第1の入力端子を選択し第2のセレクタは第1の出力端子を選択した状態1と第1のセレクタは第2の入力端子を選択し第2のセレクタは第2の出力端子を選択した状態2の2つの状態を切り替えるための信号増幅ユニット用制御信号をN個有し、前記N個の信号増幅ユニット用制御信号は第1の周期で周期的に変化し、前記N個の信号増幅ユニットの状態1と状態2のくみあわせの数が4パターン以上である

20

事を特徴とする演算増幅回路

【請求項 2】

第1の入力端子と第2の入力端子の差動の信号を変調し

前記の変調された差動の信号を増幅し復調して第1の出力端子と第2の出力端子に出力する差動増幅回路を有し、

前記差動増幅回路は第1、第2の入力端子に入力された信号を第1のセレクタで選択して増幅して出力電流を生成し

第2のセレクタで前記の出力電流を信号増幅手段1または信号増幅手段2を介して第1または第2の出力端子に出力するよう選択する信号増幅ユニットをN個と

10

前記N個の信号増幅ユニットが出力できる電流の合計値を制限する回路と

前記第1の出力端子に電流を供給する第1の電流源と

前記第2の出力端子に電流を供給する第2の電流源とを有し、

前記N個の信号増幅ユニットにおいて

第1のセレクタは第1の入力端子を選択し第2のセレクタは第1の出力端子を選択した状態1と

第1のセレクタは第2の入力端子を選択し第2のセレクタは第2の出力端子を選択した状態2の

2つの状態を切り替えるための信号増幅ユニット用制御信号をN個有し、

前記N個の信号増幅ユニット用制御信号は第1の周期で周期的に変化し、

20

前記N個の信号増幅ユニットの状態1と状態2のくみあわせの数が4パターン以上である事を特徴とする演算増幅回路

【請求項 3】

前記第1、第2の電流源として、電流を第3のセレクタで第1、第2の出力端子に選択して出力する機能を有する電流源ユニットをM個（Mは4以上の偶数）有し、

前記電流源ユニットにおいて第3のセレクタは第1の出力端子を選択した状態3と、第2の出力端子を選択した状態4の

2つの状態を切り替えるための電流源ユニット用制御信号をM個有し、

前記M個の電流源ユニット用制御信号は第2の周期で周期的に変化し、

30

前記M個の電流源ユニットの状態3と状態4のくみあわせの数が2パターン以上である

事を特徴とする請求項1、2のいずれかに記載の演算増幅回路

【請求項 4】

前記第1、第2の電流源として、電流を第3のセレクタで第1、第2の出力端子に選択して出力する機能を有する電流源ユニットをM個有し、

前記電流源ユニットの第3のセレクタと第1の出力端子の間には信号増幅手段3を有し、

前記電流源ユニットの第3のセレクタと第2の出力端子の間には信号増幅手段4を有し、

前記電流源ユニットにおいて第3のセレクタは第1の出力端子を選択した状態3と、第2の出力端子を選択した状態4の

2つの状態を切り替えるための電流源ユニット用制御信号をM個有し、

40

前記M個の電流源ユニット用制御信号は第2の周期で周期的に変化し、

前記M個の電流源ユニットの状態3と状態4のくみあわせの数が2パターン以上である

事を特徴とする請求項1、2のいずれかに記載の演算増幅回路

【請求項 5】

前記第1、第2の電流源として、電流を第3のセレクタで第1、第2の出力端子に選択して出力する機能を有する電流源ユニットをM個有し、

前記電流源ユニットにおいて第3のセレクタは第1の出力端子を選択した状態3と、第2の出力端子を選択した状態4の

2つの状態を切り替えるための電流源ユニット用制御信号をM個有し、

前記M個の電流源ユニット用制御信号は第2の周期で周期的に変化し、

50

前記M個の電流源ユニットの状態3と状態4のくみあわせの数が4パターン以上である

事を特徴とする請求項1、2のいずれかに記載の演算増幅回路

【請求項6】

前記第1、第2の電流源として、電流を第3のセレクタで第1、第2の出力端子に選択して出力する機能を有する電流源ユニットをM個有し、

前記電流源ユニットの第3のセレクタと第1の出力端子の間には信号増幅手段3を有し、前記電流源ユニットの第3のセレクタと第2の出力端子の間には信号増幅手段4を有し、前記電流源ユニットにおいて第3のセレクタは第1の出力端子を選択した状態3と、第2の出力端子を選択した状態4の2つの状態を切り替えるための電流源ユニット用制御信号をM個有し、

10

前記M個の電流源ユニット用制御信号は第2の周期で周期的に変化し、

前記M個の電流源ユニットの状態3と状態4のくみあわせの数が4パターン以上である

事を特徴とする請求項1、2のいずれかに記載の演算増幅回路

【請求項7】

第1の入力端子と第2の入力端子の差動の信号を変調し

前記の変調された差動の信号を増幅し復調して第1の出力端子と第2の出力端子に出力する差動増幅回路を有し、

前記差動増幅回路は第1、第2の入力端子に入力された信号を第1のセレクタで選択して増幅して出力電流を生成し

20

第2のセレクタで前記の出力電流の出力先として第1、第2の出力端子を選択する信号増幅ユニットをN個と

前記N個の信号増幅ユニットが出力できる電流の合計値を制限する回路と

前記第1の出力端子に電流を供給する第1の電流源と

前記第2の出力端子に電流を供給する第2の電流源とを有し、

前記N個の信号増幅ユニットにおいて

第1のセレクタは第1の入力端子を選択し第2のセレクタは第1の出力端子を選択した状態1と

第1のセレクタは第2の入力端子を選択し第2のセレクタは第2の出力端子を選択した状態2の

2つの状態を切り替えるための信号増幅ユニット用制御信号をN個有し、

30

前記N個の信号増幅ユニット用制御信号は第1の周期で周期的に変化し、

前記N個の信号増幅ユニットの状態1と状態2のくみあわせの数が2パターン以上あり、

前記第1、第2の電流源として、電流を第3のセレクタで第1、第2の出力端子に選択して出力する機能を有する電流源ユニットをM個有し、

前記電流源ユニットにおいて第3のセレクタは第1の出力端子を選択した状態3と、第2の出力端子を選択した状態4の

2つの状態を切り替えるための電流源ユニット用制御信号をM個有し、

前記M個の電流源ユニット用制御信号は第2の周期で周期的に変化し、

40

前記M個の電流源ユニットの状態3と状態4のくみあわせの数が4パターン以上である

事を特徴とする演算増幅回路

【請求項8】

第1の入力端子と第2の入力端子の差動の信号を変調し

前記の変調された差動の信号を増幅し復調して第1の出力端子と第2の出力端子に出力する差動増幅回路を有し、

前記差動増幅回路は第1、第2の入力端子に入力された信号を第1のセレクタで選択して増幅して出力電流を生成し

第2のセレクタで前記の出力電流の出力先として第1、第2の出力端子を選択する信号増

50

幅ユニットをN個と

前記N個の信号增幅ユニットが出力できる電流の合計値を制限する回路と

前記第1の出力端子に電流を供給する第1の電流源と

前記第2の出力端子に電流を供給する第2の電流源とを有し、

前記N個の信号增幅ユニットにおいて

第1のセレクタは第1の入力端子を選択し第2のセレクタは第1の出力端子を選択した状態1と

第1のセレクタは第2の入力端子を選択し第2のセレクタは第2の出力端子を選択した状態2の

2つの状態を切り替えるための信号增幅ユニット用制御信号をN個有し、

10

前記N個の信号增幅ユニット用制御信号は第1の周期で周期的に変化し、

前記N個の信号增幅ユニットの状態1と状態2のくみあわせの数が2パターン以上あり、

前記第1、第2の電流源として、電流を第3のセレクタで第1、第2の出力端子に選択して出力する機能を有する電流源ユニットをM個有し、

前記電流源ユニットの第3のセレクタと第1の出力端子の間には信号增幅手段3を有し、

前記電流源ユニットの第3のセレクタと第2の出力端子の間には信号增幅手段4を有し、

前記電流源ユニットにおいて第3のセレクタは第1の出力端子を選択した状態3と、第2の出力端子を選択した状態4の2つの状態を切り替えるための電流源ユニット用制御信号をM個有し、

20

前記M個の電流源ユニット用制御信号は第2の周期で周期的に変化し、

前記M個の電流源ユニットの状態3と状態4のくみあわせの数が4パターン以上ある事を特徴とする演算增幅回路

### 【請求項9】

第1の入力端子と第2の入力端子の差動の信号を変調し

前記の変調された差動の信号を増幅し復調して第1の出力端子と第2の出力端子に出力する差動增幅回路を有し、

30

前記差動增幅回路は第1、第2の入力端子に入力された信号を第1のセレクタで選択して増幅して出力電流を生成し

第2のセレクタで前記の出力電流を信号増幅手段1または信号増幅手段2を介して第1または第2の出力端子に出力するよう選択する信号増幅ユニットをN個と

前記N個の信号増幅ユニットが出力できる電流の合計値を制限する回路と

前記第1の出力端子に電流を供給する第1の電流源と

前記第2の出力端子に電流を供給する第2の電流源とを有し、

前記N個の信号増幅ユニットにおいて

第1のセレクタは第1の入力端子を選択し第2のセレクタは第1の出力端子を選択した状態1と

40

第1のセレクタは第2の入力端子を選択し第2のセレクタは第2の出力端子を選択した状態2の

2つの状態を切り替えるための信号増幅ユニット用制御信号をN個有し、

前記N個の信号増幅ユニット用制御信号は第1の周期で周期的に変化し、

前記N個の信号増幅ユニットの状態1と状態2のくみあわせの数が2パターン以上あり、

前記第1、第2の電流源として、電流を第3のセレクタで第1、第2の出力端子に選択して出力する機能を有する電流源ユニットをM個有し、

前記電流源ユニットにおいて第3のセレクタは第1の出力端子を選択した状態3と、第2

50

の出力端子を選択した状態 4 の

2つの状態を切り替えるための電流源ユニット用制御信号をM個有し、

前記M個の電流源ユニット用制御信号は第2の周期で周期的に変化し、

前記M個の電流源ユニットの状態3と状態4のくみあわせの数が4パターン以上である

事を特徴とする演算増幅回路

**【請求項10】**

第1の入力端子と第2の入力端子の差動の信号を変調し

前記の変調された差動の信号を増幅し復調して第1の出力端子と第2の出力端子に出力する差動増幅回路を有し、

10

前記差動増幅回路は第1、第2の入力端子に入力された信号を第1のセレクタで選択して増幅して出力電流を生成し

第2のセレクタで前記の出力電流を信号増幅手段1または信号増幅手段2を介して第1または第2の出力端子に出力するよう選択する信号増幅ユニットをN個と

前記N個の信号増幅ユニットが出力できる電流の合計値を制限する回路と

前記第1の出力端子に電流を供給する第1の電流源と

前記第2の出力端子に電流を供給する第2の電流源とを有し、

前記N個の信号増幅ユニットにおいて

第1のセレクタは第1の入力端子を選択し第2のセレクタは第1の出力端子を選択した状態1と

20

第1のセレクタは第2の入力端子を選択し第2のセレクタは第2の出力端子を選択した状態2の

2つの状態を切り替えるための信号増幅ユニット用制御信号をN個有し、

前記N個の信号増幅ユニット用制御信号は第1の周期で周期的に変化し、

前記N個の信号増幅ユニットの状態1と状態2のくみあわせの数が2パターン以上であり、

、

前記第1、第2の電流源として、電流を第3のセレクタで第1、第2の出力端子に選択して出力する機能を有する電流源ユニットをM個有し、

前記電流源ユニットの第3のセレクタと第1の出力端子の間には信号増幅手段3を有し、

30

前記電流源ユニットの第3のセレクタと第2の出力端子の間には信号増幅手段4を有し、

前記電流源ユニットにおいて第3のセレクタは第1の出力端子を選択した状態3と、第2の出力端子を選択した状態4の2つの状態を切り替えるための電流源ユニット用制御信号をM個有し、

前記M個の電流源ユニット用制御信号は第2の周期で周期的に変化し、

前記M個の電流源ユニットの状態3と状態4のくみあわせの数が4パターン以上である事を特徴とする演算増幅回路

40

**【請求項11】**

前記第1の周期と第2の周期が等しい事を特徴とする請求項3から10のいずれかに記載の演算増幅回路

**【請求項12】**

前記第1の周期と第2の周期が異なる事を特徴とする請求項3から10のいずれかに記載の演算増幅回路

**【請求項13】**

前記第1の周期と第2の周期が異なり、前記第1の周期と第2の周期の比率が自然数対自然数で表せる事を特徴とする請求項3から10のいずれかに記載の演算増幅回路

**【請求項14】**

50

前記N個の信号増幅ユニットの状態1から状態2、状態2から状態1に遷移するタイミングと前記M個の電流源ユニットの状態3から状態4、状態4から状態3に遷移するタイミングが異なり同じタイミングで状態遷移が発生しない事を特徴とする請求項3から13のいずれかに記載の演算増幅回路

【発明の詳細な説明】

【技術分野】

【0001】

本発明は演算増幅回路に関し、特に演算増幅回路のオフセット電圧及び $1/f$ 雑音の低減のための回路技術に関するものである。

10

【背景技術】

【0002】

演算増幅回路は半導体集積回路において幅広い用途で用いられる。特に、現在は高速、低電力、コストの面から、CMOSプロセスで製造される半導体集積回路が主流であるので演算増幅回路もMOSトランジスタで構成される。

【0003】

MOSトランジスタの比精度に起因するオフセットや $1/f$ 雑音は、バイポーラトランジスタに比べて一般に1桁程度悪いので、低オフセット電圧で且つ低雑音の演算増幅回路の実現が難しい。

【0004】

この問題を解決するためにあるのが、(非特許文献1、2)や(特許文献1から5)に示すチョッパ変調技術である。

20

【0005】

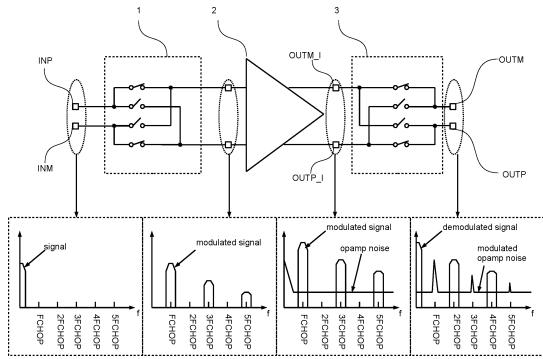

図1にチョッパ変調技術を用いた演算増幅回路を示す。演算増幅回路2の入力と出力にそれぞれチョッパ回路1と3を設けて、変調周波数FCCHOPで変調動作を行う。

【0006】

入力信号は入力のチョッパ回路で変調されて、その変調された信号は演算増幅回路で増幅され、出力のチョッパ回路で復調される。信号の増幅は、変調された高い周波数でなされるため、演算増幅回路のオフセット電圧や $1/f$ 雑音の影響を除去できる。

【0007】

一方、演算増幅回路のオフセット電圧や $1/f$ 雑音は出力のチョッパ回路で変調周波数FCCHOPとその奇数次の高調波に変調されるので、出力の低周波にはオフセット電圧や $1/f$ 雑音が現れない。

30

【0008】

チョッパ変調技術を用いた演算増幅回路は、低オフセット電圧や、 $1/f$ 雑音の特性を生かして様々な用途に用いられる。例えば(特許文献2から4)や(非特許文献1、2)に挙げたデルタシグマAD変換器やバンドギャップリファレンス回路などがある。

【0009】

変調された演算増幅回路のオフセット電圧や $1/f$ 雑音成分が特性上問題になる場合は、ローパスフィルタを設けて除去する必要がある。

40

【先行技術文献】

【特許文献】

【0010】

【特許文献1】米国特許4947135

【特許文献2】米国特許4939516

【特許文献3】米国特許4994805

【特許文献4】米国特許6462612

【特許文献5】米国特許7224216

【非特許文献】

【0011】

50

【非特許文献 1】 K C Hsieh, P R Gray, D. Senderowicz, and D G Messerschmidt, "A low-noise copper-stabilized differential switched-capacitor filtering technique," IEEE J. Solid-State Circuits, vol. SC-16, pp. 708-715, Dec. 1981.

【非特許文献 2】 Sanduleanu, M.A.T., et al., "Accurate low power bandgap voltage reference in 0.5 μm CMOS technology," Electronic Letters, May 14, 1998, vol. 34 No. 10, p 10. 1025.

#### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0012】

チョッパ変調技術を用いた演算增幅回路では、演算增幅回路 2 への正相と逆相の入力および出力電圧がチョッパ回路 1 と 3 により交互に入れ替わるため、演算增幅回路 2 の周波数特性とスルーレートともに高い性能が要求される。

##### 【0013】

例えば入力信号が変調周波数 F C H O P よりも低い周波数の正弦波である場合、演算增幅回路 2 の端子 OUTP\_I と OUTM\_I は、時間 0.5 / F C H O P で正弦波の最大値から最小値まで変化する必要がある。すなわち、周波数特性とスルーレートについて、増幅すべき信号に要するよりも高い値が必要になる。また、この周波数特性とスルーレートの不足は歪の原因となる。

20

##### 【0014】

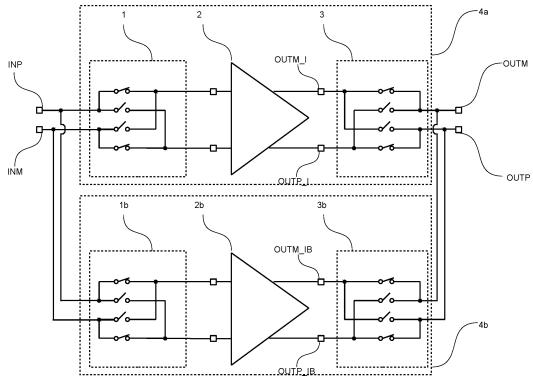

(特許文献 5) では、チョッパ変調技術を用いた演算增幅回路を、図 2 の 4 a、4 b で示すように 2 つ以上のセグメントに分割して、一度に状態が変化する演算增幅回路の数を減らす事で前記の周波数特性とスルーレートの影響を低減している。

30

##### 【0015】

例えば、4 a、4 b の各セグメントの比率を等しくした場合は、一度に状態が変化するの 30 は 4 a または 4 b のいずれかのセグメントなので、前記の周波数特性とスルーレートの影響を半分にできる。

##### 【0016】

しかし、チョッパ変調技術を用いた演算增幅回路をセグメントに分割すると、分割後の各セグメントについて統計的なばらつきが増加する。これによりセグメント間にスルーレートのミスマッチが発生して、歪を悪化させる可能性がある。また、有限の周波数特性とスルーレートに起因するグリッジ形状のノイズの低減方法についてはまだ改善の余地があった。

#### 【課題を解決するための手段】

##### 【0017】

本発明の演算增幅回路は、入力信号に応じて電流を出力する N 個 (N は 4 以上の偶数) の信号増幅ユニットと、電流を出力する M 個 (M は 4 以上の偶数) の電流源ユニットと、信号増幅ユニットの出力電流の合計値を制限するための回路を有する。信号増幅ユニットは差動の入力信号を変調し差動の出力電流を復調するためのスイッチからなるセレクタを有し、電流源ユニットは差動の出力電流を変調するためのスイッチからなるセレクタを有し、信号増幅ユニットと電流源ユニットのオフセット及び 1/f 雑音を変調する。

40

##### 【0018】

信号増幅ユニットと電流源ユニットの変調動作に伴う状態の組み合わせの数のうち、いずれか一方を 4 パターン以上、もう一方を 2 パターン以上となるよう制御を行い、且つ 1 度の状態遷移で発生する信号増幅ユニットと電流源ユニットの遷移数を減らすように制御を行う。また信号増幅ユニットと電流源ユニットの状態遷移が同時に発生しないように状態

50

遷移のタイミングをずらす、信号増幅ユニットと電流源ユニットの状態遷移の周期を異なる値とするなどの制御を行う。

【発明の効果】

【0019】

チョッパ変調技術と同様に低オフセット電圧で  $1/f$  雑音を低減した演算増幅回路を実現できる。チョッパ変調技術に比べ、1回の状態遷移あたりに変化する信号の変化量が減少するので、演算増幅回路に必要な周波数特性やスルーレートが低下し、有限の周波数特性とスルーレートに起因するグリッジ形状のノイズや歪を低減できる。

【0020】

回路のスルーレートは信号増幅ユニットの出力電流の合計値で決まるので、演算増幅回路をセグメント化する場合よりもスルーレートのミスマッチの問題を低減できる。N個の信号増幅ユニットの出力電流について、これらの加算はN個の出力端子同士を短絡することで容易に行える。M個の電流源ユニットの出力電流についても、これらの加算はM個の各出力端子同士を短絡することで容易に行える。また、出力電流を加算した後に電流入力型のゲート接地アンプなどの信号増幅手段で信号を増幅できるので、出力端子での電圧変動が小さくなり、回路に必要な周波数特性とスルーレートが低下し、周波数特性とスルーレートに起因する出力の歪を低減できる。

10

【0021】

信号増幅ユニットと電流源ユニットの状態遷移のタイミングを別々に制御できるので、状態遷移のタイミングを分散させられる。これにより1回の状態遷移あたりに変化する信号の変化量をさらに低減できるので、有限の周波数特性とスルーレートに起因するグリッジ形状のノイズや歪をさらに低減できる。そして、信号増幅ユニットと電流源ユニットの状態遷移の周期を異なる値に設定できる。つまり信号増幅および電流源ユニットそれぞれに適切な状態遷移の周期を設定できる。

20

【発明を実施するための形態】

【実施例1】

【0022】

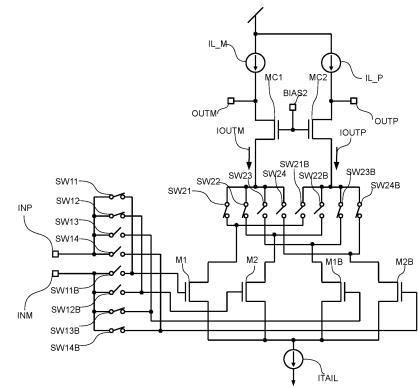

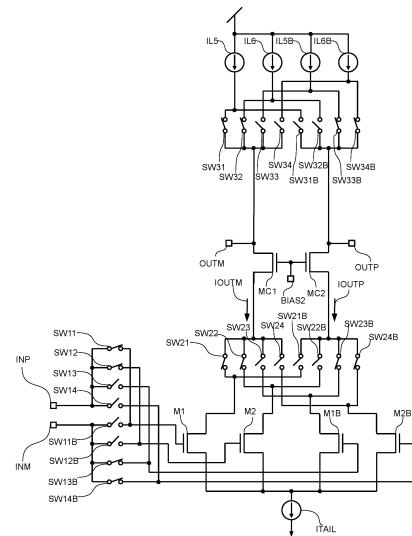

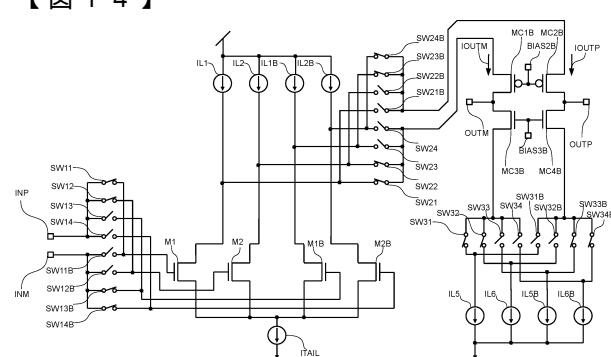

実施例1を図3に示す。

【0023】

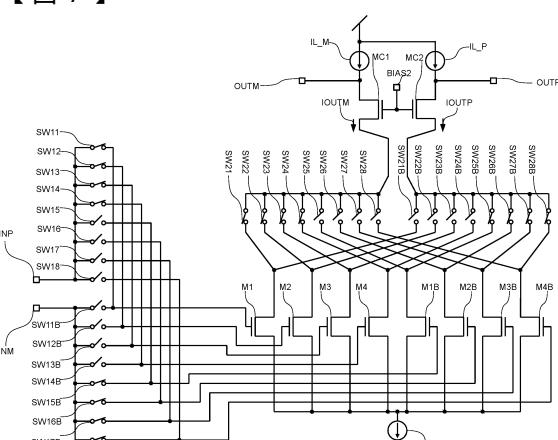

演算増幅回路はスイッチ SW11 ~ 14、スイッチ SW11B ~ 14B、スイッチ SW21 ~ 24、スイッチ SW21B ~ 24B と、トランジスタ M1、M2、M1B、M2B を有する信号増幅ユニット4つと、信号増幅ユニットから出力される電流を増幅する信号増幅手段のトランジスタ MC1、MC2 と、電流源 IL\_M、IL\_P とテイル電流源 ITA IL で構成されている。

30

【0024】

信号増幅ユニットはそれぞれ、

スイッチ SW11、SW11B、SW21、SW21B と、トランジスタ M1 で1回路、

スイッチ SW12、SW12B、SW22、SW22B と、トランジスタ M2 で1回路、

スイッチ SW13、SW13B、SW23、SW23B と、トランジスタ M1B で1回路、

スイッチ SW14、SW14B、SW24、SW24B と、トランジスタ M2B で1回路で構成されている。便宜的に、これらの信号増幅ユニットをそれぞれ1 ~ 4番の信号増幅ユニットと名前を付ける。

40

【0025】

スイッチ SW11 と SW11B は同時に導通する事はない。

すなわち、スイッチ SW11 が導通しているときは、SW11B は遮断状態で、スイッチ SW11B が導通しているときは、SW11 は遮断状態である。

【0026】

スイッチ SW12 ~ 14 と SW12B ~ 14B、スイッチ SW21 ~ 24 と SW21B ~ 24B についても同様で、一方のスイッチが導通しているときは、もう一方のスイッチは

50

遮断状態である。

【0027】

ここで1番目の信号増幅ユニットの動作について説明する。1番目の信号増幅ユニットは、

正相の入力端子INPに入力された信号をスイッチSW11がトランジスタM1のゲート端子に伝達してSW21を介してトランジスタM1のドレイン端子とトランジスタMC1のソース端子を接続する状態1と、

逆相の入力端子INMに入力された信号をスイッチSW11BがトランジスタM1のゲート端子に伝達してSW21Bを介してトランジスタM1のドレイン端子をトランジスタMC2のソース端子に接続する状態2の2つの状態をもつ。

10

【0028】

残りの2から4番目の信号増幅ユニットについても同様の動作を行う。

すなわち、正相の入力端子INPに入力された信号を増幅して、出力電流をトランジスタMC1のソース端子に出力する状態1と逆相の入力端子INMに入力された信号を増幅して、出力電流をトランジスタMC2のソース端子に出力する状態2の2つの状態をもつ。

【0029】

つまり、スイッチSW11～14とイッチSW11B～14Bは入力信号を変調する動作を行い、スイッチSW21～24とスイッチSW21B～24Bは入力信号を復調する動作を行う。

【0030】

信号増幅ユニットの出力は電流なので、各信号増幅ユニットの出力の加算は信号増幅ユニットの出力端子同士を短絡することで容易に行える。

20

【0031】

さらに、出力電流をトランジスタMC1とMC2のソース端子に入力し、MC1とMC2をゲート接地アンプとして動作させるとMC1とMC2のソース端子のインピーダンスは低くなるため、本発明の変調動作に伴う電流源ユニットの出力端子の電圧変動を小さくできる効果があり回路動作に要求される周波数特性とスルーレートを低減できる。

【0032】

信号増幅ユニットを構成するトランジスタM1、M2、M1B、M2Bのソース端子は短絡してテイル電流源ITA1Lから電流を供給する。これによって、信号増幅ユニットの出力電流の合計がテイル電流源の電流量により制限される。

30

【0033】

段落(0032)より、本発明では動作中の任意の時間において1つの差動対に信号を入力しているとみなす事ができ、スルーレートは各信号増幅ユニットの状態によらずほぼ一定になるので、段落(0016)に示した演算増幅回路をセグメント化する場合のセグメント間のスルーレートのミスマッチに起因する歪の問題を軽減できる。

【0034】

それぞれの信号増幅ユニットが状態1と状態2である時間の割合は、オフセットと1/f雑音の変調動作の観点から、50%対50%であるのが望ましい。比率がこの値からずれるとオフセットと1/f雑音の変調の効果が低下する。

40

【0035】

トランジスタMC1とMC2のドレイン端子は、それぞれ逆相、正相の出力端子のOUTM、OUTPに接続する。

【0036】

出力端子OUTM、OUTPには、負荷として電流源IL\_M、IL\_Pを接続する。

【0037】

正相の出力端子OUTPと逆相の出力端子OUTMの同相電圧を制御するために、コモンモードフィードバック回路を設けて電流源IL\_M、IL\_Pまたはテイル電流ITA1Lの電流量を調整してもよい。

【0038】

50

本実施例では、トランジスタM1、M2、M1B、M2Bは等しいデバイスサイズで作り、同じバイアス状態では等しいドレン電流が流れるように設計する場合を説明する。

【0039】

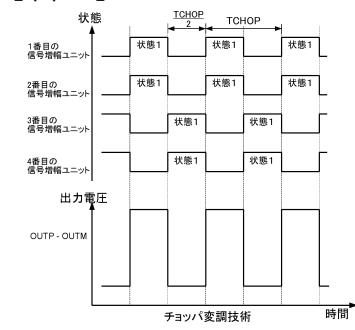

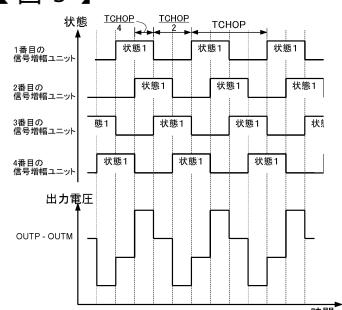

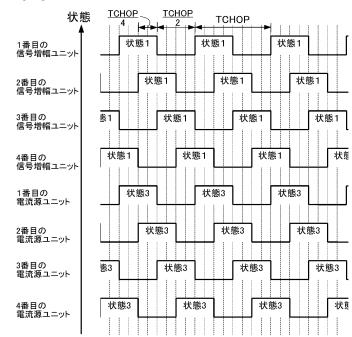

図4に従来のチョッパ安定技術と同等の効果を得られるように図3の回路を制御した場合の、信号増幅ユニットの状態と出力電圧を示したタイミングチャートを示す。このタイミングチャートについて明示的に状態1と示していない部分は状態2である。

【0040】

変調信号周期TCHOP内の1～4番目の信号増幅ユニットの状態の組み合わせは、TCHOP/2ごとに変化する。具体的な信号増幅ユニットの状態の組み合わせは、それぞれ状態1、1、2、2と

状態2、2、1、1の2パターンである。

【0041】

正相と逆相の入力端子INPとINMに等しい直流信号を印加している場合、出力端子OUTMとOUTPにはオフセットと $1/f$ 雑音が変調信号周期TCHOPの信号で変調されたものが現れる。すなわち、正相と逆相の出力端子OUTPとOUTMには時間TCHOP/2ごとに2つの状態を交互に遷移する矩形波になる。

【0042】

加えて状態遷移のタイミングにおいては、信号増幅ユニットの有限の周波数特性とスルーレートに起因するグリッジ形状のノイズがOUTPとOUTMに現れる。

【0043】

図5に本発明を用いて、2番目と4番目の信号増幅ユニットの状態遷移のタイミングをTCHOP/4の時間遅らせた場合の、信号増幅ユニットの状態と出力電圧を示したタイミングチャートを示す。このタイミングチャートについて明示的に状態1と示していない部分は状態2である。

【0044】

変調信号周期TCHOP内の1～4番目の信号増幅ユニットの状態の組み合わせは、TCHOP/4の時間ごとに変化する。具体的な信号増幅ユニットの状態の組み合わせは、それぞれ

状態1、2、2、1と

状態1、1、2、2と

状態2、1、1、2と

状態2、2、1、1の4パターンである。

【0045】

オフセットと $1/f$ 雑音は、TCHOP/4の時間ごとに4つの状態を順番に遷移する波形に変調されるので、チョッパ変調技術と同様の効果が得られる。

【0046】

一度の状態遷移あたりの信号増幅ユニット数が従来のチョッパ変調技術に比べ半分に減少するため、状態遷移のタイミングで発生する信号増幅ユニットの有限の周波数特性とスルーレートに起因するグリッジ形状のノイズは減少する。

【0047】

2番目と4番目の信号増幅ユニットの状態遷移のタイミングをTCHOP/4の時間遅せる例を示したが、これはこの時間を厳密にTCHOP/4にする必要があると限定するものではない。

【0048】

また、信号増幅ユニットの状態の組み合わせのパターンについて、これは組み合せの数を4に限定するものではない。4個の信号増幅ユニットのうち重複のない2個を選ぶ組み合せは最大で $C(4, 2) = 6$ 通りとなりうる。

【0049】

本実施例で示したトランジスタM1、M2、M1B、M2Bは、入力信号に応じて電流を出力する回路であれば良い。例えばトランジスタM1の前段に増幅回路を設けても良く、

10

20

30

40

50

トランジスタM1のドレイン端子とSW21、SW21Bの間にさらにゲート接地アンプを設けても良い。回路を構成するデバイスはMOSトランジスタに限定するものではない。

【0050】

なお、前記のスイッチを制御する信号は、原理的には周期信号である必要はなく、ランダム信号であっても良い。前記ランダム信号は周期性の有無を問わない。

【0051】

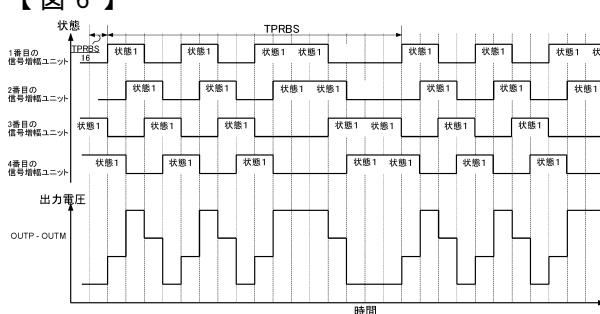

図6にスイッチを制御する信号として擬似ランダム信号を用いた場合のスイッチの状態と出力電流を示したタイミングチャートを示す。このタイミングチャートについて明示的に状態1と示していない部分は状態2である。

10

【0052】

1番目の信号増幅ユニットは周期TPRBSの擬似ランダム信号がHIGHの場合は状態1になるとして制御し、3番目の信号増幅ユニットは前記擬似ランダム信号がLOWの場合は状態1になるとして制御する。2と4番目の信号増幅ユニットはそれぞれ1と3番目の信号増幅ユニットの状態をTPRBS/16の時間だけ遅延させて制御している。

【実施例2】

【0053】

実施例1で示した信号増幅ユニットの数は4個に限定されるものではなく、4個以上の偶数であればよい。図7に実施例2の回路図を示す。

【0054】

20

実施例1の回路にスイッチSW15～18、スイッチSW15B～18B、スイッチSW25～28、スイッチSW25B～28Bと、トランジスタM3、M4、M3B、M4Bを有する信号増幅ユニット4つを加えている。

【0055】

追加した信号増幅ユニットは、それぞれ

スイッチSW15、SW15B、SW25、SW25Bと、トランジスタM3で1回路、スイッチSW16、SW16B、SW26、SW26Bと、トランジスタM4で1回路、スイッチSW17、SW17B、SW27、SW27Bと、トランジスタM3Bで1回路、

スイッチSW18、SW18B、SW28、SW28Bと、トランジスタM4Bで1回路である。便宜的に、これらの信号増幅ユニットをそれぞれ5～8番の信号増幅ユニットと名前を付ける。

30

【0056】

これらの5から8番目の信号増幅ユニットについても段落(0027)と同様の動作を行う。

すなわち、正相の入力端子INPに入力された信号を増幅して出力電流をトランジスタMC1のソース端子に出力する状態1と、逆相の入力端子INMに入力された信号を増幅して出力電流をトランジスタMC2のソース端子に出力する状態2の2つの状態をもつ。

【0057】

本実施例では、トランジスタM1からM4、およびM1BからM4Bは等しいデバイスサインで作り、同じバイアス状態では等しいドレイン電流が流れるように設計する場合を説明する。

40

【0058】

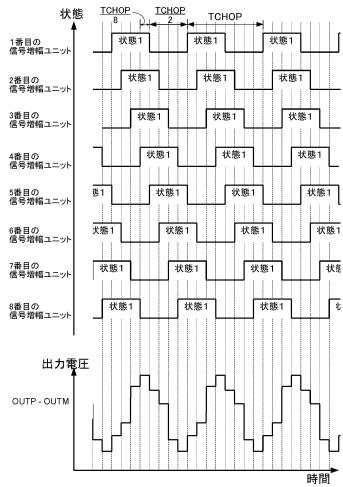

図8に実施例2の信号増幅ユニットの状態と出力電圧を示したタイミングチャートを示す。このタイミングチャートについて明示的に状態1と示していない部分は状態2である。

【0059】

1番目の信号増幅ユニットの動作状態に対して、2から8番目の信号増幅ユニットの動作タイミングを順番にTCPCHOP/8ずつ遅らせる。

【0060】

これにより変調信号周期TCPCHOP内の1～8番目の信号増幅ユニットの状態の組み合わ

50

せは、T C H O P / 8 の時間ごとに変化する。具体的な信号増幅ユニットの状態の組み合

わせは、それぞれ

状態 1、2、2、2、 2、1、1、1 と、

状態 1、1、2、2、 2、2、1、1 と、

状態 1、1、1、2、 2、2、2、1 と、

状態 1、1、1、1、 2、2、2、2 と、

状態 2、1、1、1、 1、2、2、2 と、

状態 2、2、1、1、 1、1、2、2 と、

状態 2、2、2、1、 1、1、1、2 と、

状態 2、2、2、2、 1、1、1、1 との 8 パターンである。 10

#### 【 0 0 6 1 】

オフセットと  $1/f$  雑音は、T C H O P / 8 の時間ごとに 8 つの状態を順番に遷移する波

形に変調されるので、チョッパ変調技術と同様の効果が得られる。

#### 【 0 0 6 2 】

一度の状態遷移あたりの信号増幅ユニット数が従来のチョッパ変調技術に比べ  $1/4$  に減

少するため、状態遷移のタイミングで発生する信号増幅ユニットの有限の周波数特性とス

ルーレートに起因するグリッジ形状のノイズも減少する。

#### 【 0 0 6 3 】

1 番目の信号増幅ユニットの動作状態に対して、2 から 8 番目の信号増幅ユニットの動作

タイミングを順番に T C H O P / 8 ずつ遅らせる例を示したが、これはこの時間を厳密に 20

T C H O P / 8 にする必要があると限定するものではない。

#### 【 0 0 6 4 】

また、電流 I O U T M、電流 I O U T P を構成する信号増幅ユニットの状態の組み合

わせが 8 パターンの例を示したが、これは組み合わせの数を 8 に限定するものではない。8 個

の信号増幅ユニットのうち重複のない 4 個を選ぶ組み合わせは最大で  $C(8, 4) = 70$

通りとなりうる。信号増幅ユニットの数を N 個とした場合の組み合わせの最大値は  $C(N,

N/2)$  で決まる。

#### 【 実施例 3 】

#### 【 0 0 6 5 】

実施例 1 と 2 で示した電流源 I L \_ M、I L \_ P に起因するオフセット、 $1/f$  雑音を除

去するための実施例 3 を図 9 に示す。 30

#### 【 0 0 6 6 】

実施例 1 の電流源 I L \_ M、I L \_ P にかえて、スイッチ SW 3 1 ~ 3 4、スイッチ SW

3 1 B ~ 3 4 B と、電流源 I L 5、I L 6、I L 5 B、I L 6 B を有する電流源ユニット

を 4 つ有する。

#### 【 0 0 6 7 】

電流源ユニットはそれぞれ、

スイッチ SW 3 1、SW 3 1 B と、電流源 I L 5 で 1 回路、

スイッチ SW 3 2、SW 3 2 B と、電流源 I L 6 で 1 回路、

スイッチ SW 3 3、SW 3 3 B と、電流源 I L 5 B で 1 回路、 40

スイッチ SW 3 4、SW 3 4 B と、電流源 I L 6 B で 1 回路

で構成されている。便宜的に、これらの電流増幅ユニットをそれぞれ 1 ~ 4 番の電流源ユ

ニットと名前を付ける。

#### 【 0 0 6 8 】

ここで 1 つの電流源ユニットの動作について説明する。1 番目の電流源ユニットは、電流

源 I L 5 の電流をスイッチ SW 3 1 を介して出力端子 O U T M に接続する状態 3 と、スイ

ッチ SW 3 1 B を介して出力端子 O U T P に接続する状態 4 の 2 つの状態をもつ。

#### 【 0 0 6 9 】

残りの 2 から 4 番目の電流源ユニットについても同様の動作を行う。すなわち、電流源 I

L 6、I L 5 B、I L 6 B の電流を出力端子 O U T M に接続する状態 3 と、電流源 I L 6 50

、 I L 5 B 、 I L 6 B の電流を出力端子 O U T P に接続する状態 4 の 2 つの状態をもつ。

【 0 0 7 0 】

電流源ユニットの出力は電流なので、各電流源ユニットの出力の加算は電流源ユニットの出力端子同士を短絡することで容易に行える。

【 0 0 7 1 】

それぞれの電流源ユニットが状態 3 と状態 4 である時間の割合は、オフセットと  $1/f$  雑音の変調動作の観点から、 50% 対 50% であるのが望ましい。比率がこの値からずるとオフセットと  $1/f$  雑音の変調の効果が低下する。

【 0 0 7 2 】

正相の出力端子 O U T P と逆相の出力端子 O U T M の同相電圧を制御するために、コモンモードフィードバック回路を設けて電流源 I L 5 、 I L 6 、 I L 5 B 、 I L 6 B またはテイル電流 T A I L の電流量を調整してもよい。

10

【 0 0 7 3 】

本実施例では、電流源 I L 5 、 I L 6 、 I L 5 B 、 I L 6 B を等しいデバイスサイズで作り、同じバイアス状態では等しいドレイン電流が流れるように設計する場合を説明する。

【 0 0 7 4 】

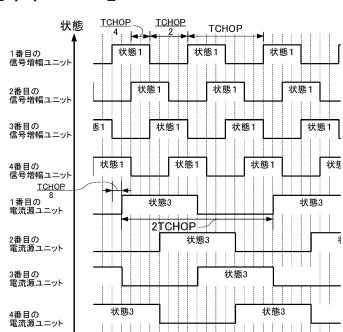

図 10 に信号增幅ユニット、電流源ユニットの状態のタイミングチャートを示す。

信号增幅ユニットの状態のタイミングチャートについて明示的に状態 1 と示していない部分は状態 2 であり、電流源ユニットの状態のタイミングチャートについて明示的に状態 3 と示していない部分は状態 4 である。

20

【 0 0 7 5 】

1 から 4 番目の信号增幅ユニットが状態 1 と状態 2 であるタイミングが 1 から 4 番目の電流源ユニットが状態 3 と状態 4 であるタイミングと等しい状態である。

変調信号周期 T C H O P 内の 1 ~ 4 番目の信号增幅ユニットの状態の組み合わせは段落 ( 0 0 4 4 ) に示す通り 4 パターンであり、同様に 1 ~ 4 番目の電流源ユニットの状態の具体的な組み合わせはそれぞれ

状態 3 、 4 、 4 、 3 と

状態 3 、 3 、 4 、 4 と

状態 4 、 3 、 3 、 4 と

状態 4 、 4 、 3 、 3 の 4 パターンである。

30

【 0 0 7 6 】

段落 ( 0 0 4 5 ) と同様に、電流源 I L 5 、 I L 6 、 I L 5 B 、 I L 6 B のオフセットと  $1/f$  雑音は、 T C H O P / 4 の時間ごとに 4 つの状態を順番に遷移する波形に変調されるので、チョッパ変調技術と同様の効果が得られる。

【 0 0 7 7 】

段落 ( 0 0 4 6 ) と同様に、一度の状態遷移あたりの電流源ユニット数が従来のチョッパ変調技術に比べ半分に減少するため、状態遷移のタイミングで発生する信号增幅ユニットの有限の周波数特性とスルーレートに起因するグリッジ形状のノイズは減少する。

【 0 0 7 8 】

信号增幅ユニットの状態遷移と電流源ユニットの状態遷移が同時に発生しないよう制御する方法の例を図 11 に示す。信号增幅ユニットの状態のタイミングチャートについて明示的に状態 1 と示していない部分は状態 2 であり、電流源ユニットの状態のタイミングチャートについて明示的に状態 3 と示していない部分は状態 4 である。

40

【 0 0 7 9 】

図 11 は、図 10 の 1 から 4 番目の電流源ユニットの動作タイミングを T C H O P / 8 だけ遅らせたものである。

【 0 0 8 0 】

これにより、信号增幅ユニットと電流源ユニットの状態遷移が同時に発生しないようにできるので、従来のセグメント化された演算增幅回路を用いたチョッパ変調技術に比べて、状態遷移のタイミングで発生する信号增幅ユニットの有限の周波数特性とスルーレートに

50

起因するグリッジ形状のノイズを低減できる。

【0081】

段落(0079)でTCHOP/8だけ動作タイミングを遅らせると記載したが、これは段落(0080)の記載のように信号増幅ユニットと電流源ユニットの状態遷移を同時に発生させないのが目的なので、動作タイミングを遅せる量はTCHOP/8に限定されない。

【0082】

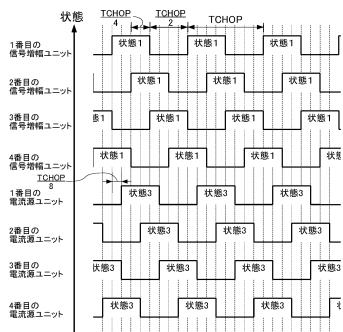

図11に加えて、信号増幅ユニットの状態遷移と電流源ユニットの状態遷移の周期が異なる場合の例を図12に示す。信号増幅ユニットの状態のタイミングチャートについて明示的に状態1と示していない部分は状態2であり、電流源ユニットの状態のタイミングチャートについて明示的に状態3と示していない部分は状態4である。

10

【0083】

図12は、図10の1から4番目の電流源ユニットの動作タイミングをTCHOP/8だけ遅らせて、さらに状態遷移の周期をTCHOPの2倍の2TCHOPとしたものであり、信号増幅ユニットと電流源ユニットの状態遷移が同時に発生しないように制御している。

【0084】

信号増幅ユニットと電流源ユニットの状態遷移の周期、つまり変調の周波数は、従来のチヨッパ変調技術と同様に $1/f$ 雑音を除去する観点から各ユニットを構成するデバイスが発する $1/f$ 雑音のコーナ周波数よりも高い周波数とするのが望ましい。

20

一方変調の周波数が高いと、信号増幅ユニットと電流源ユニットに要求される動作速度が高まり大面積化や消費電流増加を招くため、変調の周波数はなるべく低い方が望ましい。

【0085】

ここで、デバイスの種類や大きさ等により、信号増幅ユニットと電流源ユニットの $1/f$ 雑音のコーナ周波数が異なる場合、図12に示すように両者の変調の周波数を異なる値に設定できるので、段落(0080)と(0081)の考えに基づいて、信号増幅ユニットと電流源ユニットの状態遷移を同時に発生させないように両者の変調の周波数を設定できる。

【0086】

図12では信号増幅ユニットの状態遷移の周期が電流源ユニットの周期よりも短い例を示したが、これらの周期の大小関係は図12の例に限定するものではない。信号増幅ユニットの状態遷移の周期が電流源ユニットの周期よりも長くてもよい。

30

【0087】

信号増幅ユニットと電流源ユニットの状態遷移が同時に発生しないように制御するのが望ましく、これを実現するためには信号増幅ユニットと電流源ユニットの状態遷移の動作は同期していることが望ましい。

つまり、言い換えると信号増幅ユニットと電流源ユニットの状態遷移の周期の比が自然数対自然数で表せられる事が望ましい。

【0088】

電流源ユニットの数は4個に限定されず、M個(Mは4以上の偶数)であればよい。信号増幅ユニットの個数のN個と電流源ユニットの数のM個は同じである必要はなく、異なる値であってもよい。

40

【0089】

信号増幅ユニットの状態の組み合わせの数と、電流源ユニットの状態の組み合わせの数は同じ数である必要はなく、異なる数であってもよい。

【0090】

デバイスの種類や大きさ等で決まる回路特性によっては、信号増幅ユニットと電流源ユニットの状態の組み合わせの数を両方とも4パターン以上にする必要はなく、信号増幅ユニットと電流源ユニットの状態の組み合わせの数のうちいずれか一方を2パターンとしてもよい。

50

また、信号増幅ユニットと電流源ユニットの状態の組み合わせの数がそれぞれ 2 パターンの場合は、段落 (0046) と (0077) で示した状態遷移あたりの信号増幅ユニット数を減少させる効果は得られないが、段落 (0080) と (0081) で示した信号増幅ユニットと電流源ユニットの状態遷移が同時に発生しないように動作タイミングをずらす効果と、段落 (0085) で示した信号増幅ユニットと電流源ユニットの変調の周波数を異なる値に設定する効果は得られる。

【0091】

段落 (0038) (0057) (0073) で、信号増幅ユニットと電流源ユニットを構成するトランジスタまたは電流源について、等しいデバイスサイズで作り、同じバイアス状態では等しいドレイン電流が流れるように設計する場合を説明したが、これは本発明の信号増幅ユニットと電流源ユニットそれぞれについて流れる電流を等しく設計する事に限定するものではない。信号増幅ユニットが取りうるすべての状態の組み合わせにおいて、正相と逆相の出力端子に電流を出力するデバイスサイズの合計値が等しく、同じバイアス状態では等しい電流が流れるように設計すればよい。電流源ユニットに関しても同様である。

例えば図 5 のタイミングチャートにおいて、1 番目と 3 番目の信号増幅ユニットは状態 1 である状態が重複せず、2 番目と 4 番目の信号増幅ユニットは状態 1 である状態が重複していない。この場合、1 番目から 4 番目の信号増幅ユニットのデバイスサイズの比率を 1 対 2 対 1 対 2 とする事で、状態 1 と状態 2 である信号増幅ユニットのデバイスサイズの比率は常に 3 対 3 となり、同じバイアス状態では正相と逆相の出力端子に等しい電流が流れ 20 設計にできる。電流源ユニットに関しても同様である。

【実施例 4】

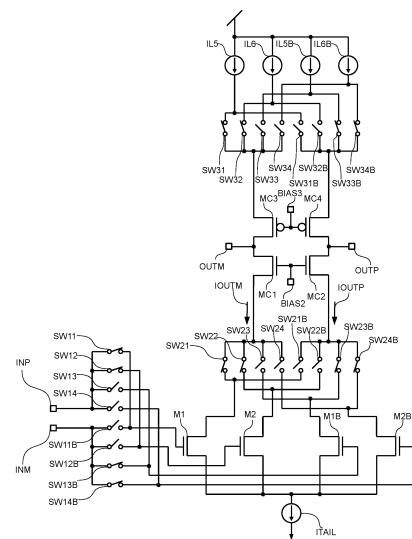

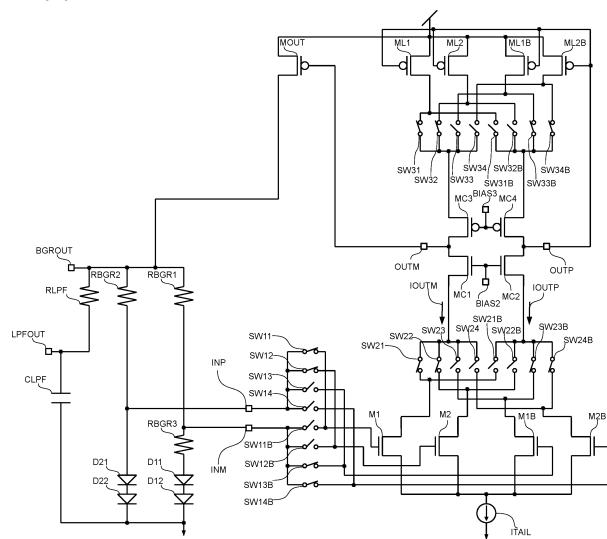

【0092】

実施例 3 で示した回路に信号増幅手段としてトランジスタ M C 3、M C 4 を追加し、電流源ユニットと組み合わせてカスコード電流源を構成する例を図 13 に示す。

【0093】

4 個の電流源ユニットと、出力端子 O U T M、O U T P の間にトランジスタ M C 3、M C 4 を設け、そのゲートバイアスとして B I A S 2 を印加する。

【0094】

信号増幅ユニット、電流源ユニットの動作は実施例 3 と同様である。

【0095】

図 13 で示した実施例 4 の変更は、電流源ユニットの出力端子について段落 (0030)、(0031) と同様な効果がある。すなわち変調動作に伴う電圧変動を小さくできる効果があり回路動作に要求される周波数特性とスルーレートを低減できる。

【0096】

なお、信号増幅手段として用いているトランジスタ M C 1、M C 2 および M C 3、M C 4 について、これらは演算増幅回路の負荷によっては信号増幅の効果が小さくなるため、必ずしも必要ではない。

【実施例 5】

【0097】

実施例 4 の回路を変形する事でフォールデットカスコード構成とできる。実施例を図 14 に示す。

【0098】

実施例 4 の回路について、4 個の信号増幅ユニットにそれぞれ電流源 I L 1、I L 2、I L 1 B、I L 2 B を追加し、トランジスタ M C 1、M C 2、M C 3、M C 4 をトランジスタ M C 1 B、M C 2 B、M C 3 B、M C 4 B に置き換えている。

【0099】

信号増幅ユニットはそれぞれ、

スイッチ S W 1 1、S W 1 1 B、S W 2 1、S W 2 1 B と、トランジスタ M 1 と電流源 I L 1 で 1 回路、

10

20

30

40

50

スイッチ SW12、SW12B、SW22、SW22B と、トランジスタ M2 と電流源 IL2 で 1 回路、

スイッチ SW13、SW13B、SW23、SW23B と、トランジスタ M1B と電流源 IL1B で 1 回路、

スイッチ SW14、SW14B、SW24、SW24B と、トランジスタ M2B と電流源 IL2B で 1 回路

で構成されている。

【0100】

これらの信号增幅ユニットの動作は、トランジスタ MC1、MC2 が MC1B、MC2B に置き換わっているだけで実施例 1 と同様である。

10

【0101】

電流源ユニットは、電流源の出力電流の向きが電源方向かグランド方向か異なるだけで実施例 4 のものと同様である。これらの電流源ユニットの動作はトランジスタ MC3、MC4 が MC3B、MC4B に置き換わっているだけで実施例 4 と同様である。

【実施例 6】

【0102】

本発明の演算增幅回路は、従来技術の演算增幅回路が使用される用途全般において、置き換えて用いる事ができる。実施例 4 の演算增幅回路を用いてバンドギャップリファレンス回路を構成した実施例を図 15 に示す。

【0103】

この実施例では、図 13 の回路の電流源 IL5、IL6、IL5B、IL6B にかえて、トランジスタ ML1、ML2、ML1B、ML2B とした。これらトランジスタのゲート端子は OUTP 端子に接続して出力を差動から単相に変換する。

20

【0104】

トランジスタ MOUT のゲートは出力端子 OUTM と接続し、ドレインは端子 BGROUT と接続する。

【0105】

端子 BGROUT には抵抗 RBGR1、RBGR2 と RLPF の一方の端子を接続する。

【0106】

抵抗 RBGR1 と RBGR2 のもう一方の端子は、それぞれ入力端子 INM と INP と接続する。入力端子 INM、INP にはそれぞれ D21 のアノード、抵抗 RBGR3 の一方の端子を接続する。

30

【0107】

ダイオード D11 のカソードと D12 のアノードを接続、抵抗 RBGR3 のもう一方の端子はダイオード D11 のアノードと接続する。

ダイオード D21 のカソードと D22 のアノードを接続してダイオード D12 と D22 のカソードはグランド端子に接続する。

【0108】

抵抗 RLDF のもう一方の端子は容量 CLPF と接続、容量 CLPF のもう一方の端子はグランド端子と接続することでローパスフィルタを構成し、その出力は端子 LPFOUT である。

40

【0109】

回路動作により入力端子 INP と INM が等しくなるようにフィードバックがかかる。抵抗 RBGR1 と RBGR2 の値が等しく、ダイオード D11 と D12 のサイズが等しく、D21、D22 のサイズが等しくて、D11 のサイズが D21 の A 倍だとして、D21 の順方向電圧を VF、ダイオードの熱電圧を Vt とすると、端子 BGROUT の電圧は  $2 * (V_F + (RBGR1 / RBGR3) * V_t * \ln(A))$  で表せる。

【0110】

トランジスタ M11、M12、M11B、M12B と、トランジスタ ML1、ML2、ML1B、ML2B のオフセット及び  $1/f$  雑音は変調されたため、端子 BGROUT に現

50

れる演算增幅回路のオフセット電圧や $1/f$ 雑音は低減される。

【0111】

変調された前記のオフセット電圧及び $1/f$ 雑音は前記のローパスフィルタで低減できる。

【図面の簡単な説明】

【0112】

【図1】従来のチョッパ変調技術の説明図

【図2】チョッパ変調技術を用いた演算增幅回路をセグメント化した従来技術の説明図

【図3】実施例1の回路図

10

【図4】従来のチョッパ変調技術を用いた場合の、信号増幅ユニットの状態と出力電圧を示したタイミングチャート

【図5】実施例1の、信号増幅ユニットの状態と出力電圧を示したタイミングチャート

【図6】スイッチを制御する信号として擬似ランダム信号を用いた場合の信号増幅ユニットの状態と出力電圧を示したタイミングチャート

【図7】実施例2の回路図

【図8】実施例2の、信号増幅ユニットの状態と出力電圧を示したタイミングチャート

【図9】実施例3の回路図

【図10】実施例3の、信号増幅ユニットと電流源ユニットの状態を示したタイミングチャート

20

【図11】図10に対して信号増幅ユニットと電流源ユニットの状態遷移タイミングをTCP/8ずらした場合を示したタイミングチャート

【図12】図10に対して信号増幅ユニットと電流源ユニットの状態遷移タイミングをTCP/8ずらして、且つ両者の状態遷移周期が異なる場合を示したタイミングチャート

【図13】実施例4の回路図

【図14】実施例5の回路図

【図15】実施例6の回路図、実施例4の回路を用いたバンドギャップリファレンスの回路図

【符号の説明】

30

【0113】

1、1b 入力のチョッパ回路

2、2b 演算增幅回路

3、3b 出力のチョッパ回路

4a、4b セグメント化されたチョッパ変調の機能を有する演算增幅回路

F C H O P 变調周波数

I N P 正相の入力端子

I N M 逆相の入力端子

S W 1 1 ~ 1 8 正相の入力端子I N Pと、トランジスタM 1 ~ 4、M 1 B ~ 4 Bのゲートを接続するスイッチ

40

S W 1 1 B ~ 1 8 B 逆相の入力端子I N Mと、トランジスタM 1 ~ 4、M 1 B ~ 4 Bのゲートを接続するスイッチ

M 1 ~ 4 トランジスタ

M 1 B ~ 4 B トランジスタ

O U T P 正相の出力端子

O U T M 逆相の出力端子

S W 2 1 ~ 2 8 トランジスタM 1 ~ 4、M 1 B ~ 4 Bのドレインに接続するスイッチ

S W 2 1 B ~ 2 8 B トランジスタM 1 ~ 4、M 1 B ~ 4 Bのドレインに接続するスイッチ

50

I O U T P 正相の出力端子の電流経路に流れる電流

I O U T M 逆相の出力端子の電流経路に流れる電流

T C H O P 变調信号周期

T P R B S 擬似ランダム信号周期

I T A I L テイル電流源

I L \_\_ P 電流源

I L \_\_ M 電流源

I L 5、6 電流源

I L 5 B、6 B 電流源

S W 3 1 ~ 3 4 電流源 I L 5、6、I L 5 B、6 B に接続するスイッチ

S W 3 1 B ~ 3 4 B 電流源 I L 5、6、I L 5 B、6 B に接続するスイッチ

M L 1、2 トランジスタ

M L 1 B、2 B トランジスタ

M C 1 ~ 4 トランジスタ

B I A S 2 トランジスタ M C 1 と M C 2 のバイアス端子

B I A S 3 トランジスタ M C 3 と M C 4 のバイアス端子

M C 1 B ~ 4 B トランジスタ

B I A S 2 B トランジスタ M C 1 B と M C 2 B のバイアス端子

B I A S 3 B トランジスタ M C 3 B と M C 4 B のバイアス端子

B G R O U T バンドギャップリファレンス回路の出力

L P F O U T ローパスフィルタの出力

M O U T ゲート端子が出力端子 O U T M に、ドレイン端子が B G R O U T に接続されたトランジスタ

R B G R 1 バンドギャップリファレンス回路を構成する抵抗

R B G R 2 バンドギャップリファレンス回路を構成する抵抗

R B G R 3 バンドギャップリファレンス回路を構成する抵抗

D 1 1 バンドギャップリファレンス回路を構成するダイオード

D 1 2 バンドギャップリファレンス回路を構成するダイオード

D 2 1 バンドギャップリファレンス回路を構成するダイオード

D 2 2 バンドギャップリファレンス回路を構成するダイオード

R L P F ローパスフィルタを構成する抵抗

C L P F ローパスフィルタを構成する容量

10

20

30

40

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図13】

【図12】

【図14】

【図15】

---

フロントページの続き

(56)参考文献 特開2006-310959 ( J P , A )

米国特許第4947135 ( U S , A )

特開2014-116713 ( J P , A )

特開2009-303121 ( J P , A )

特開昭60-72406 ( J P , A )

I. Akita, M. Ishida, A 0.06mm<sup>2</sup> 14nV/ Hz Chopper Instrumentation Amplifier with Automatic Differential-Pair Matching, Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013, 米国, IEEE, 2013年 2月19日, pp.178-179, Figure 10.4.1

(58)調査した分野(Int.Cl. , DB名)

H 03 F 1 / 00 - 3 / 72

I E E E X p l o r e