(19) 대한민국특허청(KR)

(12) 특허공보(B1)

(51) Int. Cl.<sup>5</sup>

H01L 21/30

(45) 공고일자 1991년 12월 21일

(11) 공고번호 91-010219

---

|           |                |           |                |

|-----------|----------------|-----------|----------------|

| (21) 출원번호 | 특 1988-0011034 | (65) 공개번호 | 특 1989-0004394 |

| (22) 출원일자 | 1988년 08월 30일  | (43) 공개일자 | 1989년 04월 21일  |

---

|            |                                |

|------------|--------------------------------|

| (30) 우선권주장 | 62-216667 1987년 08월 31일 일본(JP) |

| (71) 출원인   | 가부시키가이샤 도시바 아오이 죠이치            |

일본국 가나가와현 가와사키시 사이와이구 호리가와정 72번지

|          |                                                                       |

|----------|-----------------------------------------------------------------------|

| (72) 발명자 | 히로사와 다츠야<br>일본국 가나가와현 가와사키시 사이와이구 호리가와정 72번지 가부시키<br>가이샤 도시바 호리가와정공장내 |

|----------|-----------------------------------------------------------------------|

(74) 대리인 김윤배

**심사관 : 박형식 (책자공보 제2598호)**

---

**(54) 반도체장치의 제조방법**

---

**요약**

내용 없음.

**대표도**

**영세서**

[발명의 명칭]

반도체장치의 제조방법

[도면의 간단한 설명]

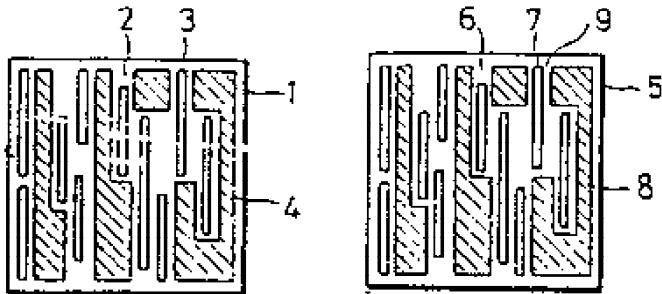

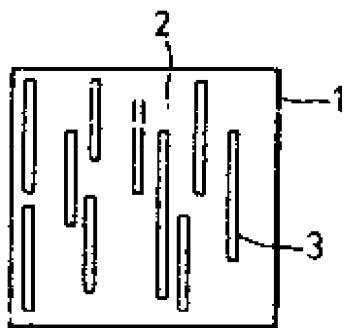

제1a도는 본 발명의 제1실시예에 이용되는 반도체장치제조용 유리마스크의 평면도.

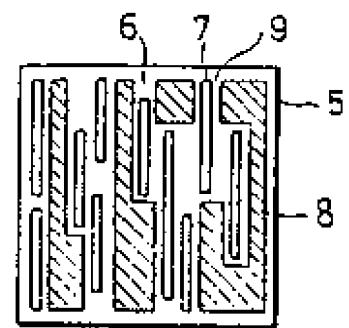

제1b도는 제1a도에 도시한 유리마스크를 이용해서 얻은 반도체 칩의 평면도.

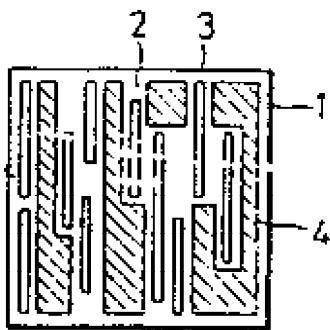

제2a도는 종래의 반도체장치제조용 유리마스크의 평면도.

제2b도는 제2a도에 도시한 유리마스크를 이용해서 얻은 반도체 칩의 평면도이다.

\* 도면의 주요부분에 대한 부호의 설명

1 : 유리마스크

2 : 유리기판

3 : 산화크롬패턴

4 : 더미산화크롬패턴

5 : 반도체 칩

6 : 반도체밀바탕

7 : 배선

8 : 더미배선

9 : 배선의 사이

## [발명의 상세한 설명]

### [적용분야]

본 발명은 반도체장치의 제조방법에 적용되는 반도체장치(칩적회로)의 배선공정에 관한 것으로, 특히 배선영역의 면적이 작은 반도체장치의 배선을 형성시킬 때에 적용되는 반도체장치의 제조방법에 관한 것이다.

### [종래기술 및 그 문제점]

통상, 배선영역의 면적이 작은 반도체장치의 배선을 형성시킬 때 배선밀도가 작으면 배선의 사이드 엣칭(side etching)이 있게 되므로, 종래에는 엣칭시간을 줄이는 등 엣칭조건을 조정하여 이에 대처하고 있었다. 또한 게이트어레이 등에서는 게이트크기를 한 등급 줄임으로써 소자면적(칩면적)에 대한 배선영역면적의 비율이 가능한 한 높아지도록(40% 이상 목표) 설계단계에서 조정하고 있었다.

상기한 바와 같이 배선형성시의 특성으로 배선면적이 작으면, 배선의 엣칭시에 사이드엣칭 현상이 발생하여 배선이 가늘어지게 되고 결국 배선이 소실되어 버리는 경우가 있다. 이것은 RIE(Reactive Ion Etching)장치로 배선을 엣칭할 때의 레지스트층벽 부착효과(RIE의 이온에서 풍겨진 배선패턴상의 레지스트가 배선의 측벽에 부착되어 배선의 사이드엣칭을 방지함)가 배선면적이 작기 때문에(결국 레지스트면적이 작기 때문에) 감소되어 사이드엣칭이 가속적으로 진행되고 말기 때문이다.

제2a도는 종래의 반도체장치제조용 유리마스크의 평면도, 제2b도는 제2a도에 도시된 유리마스크를 이용해서 얻은 반도체 칩의 평면도로서, 각 도면에서 참조부호 1은 유리마스크(이 경우 포지티브 헤프), 2는 유리기판을, 3은 산화크롬패턴을, 5는 반도체 칩을, 6은 반도체밀바탕(게이트어레이라고 하는 확산웨이퍼)을, 7은 배선패턴을 각각 나타낸 것이다. 이 도면을 보아도 알 수 있는 바와 같이 침면적에 대해서 배선면적이 작으면, 마스크(1)에 의해 전사 형성된 배선(7)이 배선의 사이드엣칭에 의해 가늘어진다든지 단절되는 경우가 생기고는 한다.

그래서 종래에는 엣칭조건(엣칭시간, 가스조건, 엣칭파워 등)을 조정하여 상기 사이드엣칭에 대처하고 있었다. 그러나 이렇게 하면, 각 제품마다 다른 엣칭조건을 설정하지 않으면 않되기 때문에 제조 현장에서의 관리가 복잡하게 될 뿐만 아니라, 엣칭의 제어성과 재현성에도 문제가 생긴다. 한편, 소자의 성능을 떨어뜨리지 않도록 배선면적만을 크게 설계한다면, 설계상의 제약이 상당히 커져버리고 만다.

### [발명의 목적]

본 발명은 상기한 실정을 감안해서 발명된 것으로서, 통상의 소자배선(실제로 사용하는 소자배선)외에 이것과 도통되지 않는 더미배선(dummy 배선)을 배치함으로써 실효적인 배선면적을 증가시키면서, 배선형성시(엣칭시)의 제어성 및 재현성, 원료에 대한 제품비율, 신뢰성 등을 향상시킬 수 있는 반도체장치의 제조방법을 제공하고자 함에 그 목적이 있다.

### [발명의 구성]

상기한 목적을 달성하기 위한 본 발명은 반도체장치의 배선형성시에 사용하는 마스크에 더미배선용 마스크영역을 설치하고 이 마스크를 이용해서 실제로 사용하는 소자배선 외에 더미배선을 형성하는 것을 특징으로 한다. 즉, 본 발명은 배선의 설계시에 소자의 기능을 만족시키는데 필요한 배선(소자 배선)이외에 소자의 기능에는 영향을 주지 않는 배선영역, 결국 소자와는 전기적으로 도통하지 않는 배선영역(더미배선영역)을 설치해서 배선면적/소자면적의 비를 향상시켜 상기 사이드엣칭의 폐해를 없애도록 한 것이다.

### [실시예]

이하, 도면을 참조하여 본 발명의 제1실시예를 설명한다.

제1a도는 본 발명의 제1실시예에 이용되는 반도체장치제조용 유리마스크의 평면도이고, 제1b도는 제1a도에 도시한 유리마스크를 이용해서 얻은 반도체 칩의 평면도인 바, 각 도면은 상기 종래예에 대응시킨 경우의 예이므로 대응되는 곳에는 동일부호를 붙여서 그에 대한 설명을 생략하고, 특징점만을 설명한다.

본 실시예의 특징은 마스크(1)상에 더미산화크롬패턴(4: dummy chrome pattern)을 추가로 설치 함으로써 이것에 대응해서 칩(5)상에도 더미배선(8)을 형성한 것에 있다. 여기서는 일례로서 배선/침면적의 비를 2.5%로부터 40% 정도로 증가시키고 있다.

그 결과, 엣칭 때에 배선의 사이드엣칭을 막는 레지스트 측벽부착효과가 현저하게 증대되어, 엣칭 후의 배선(7,8)에는 제1b도에 도시한 것처럼 종래예와 같은 배선의 가늘어짐, 배선절단 등이 발생하지 않게 된다.

더구나 더미배선(8)은 소자배선(7)과 도통시킬 필요는 없고, 오히려 배선용량의 증대 등의 악영향을 방지하는 의미로도 도통시키지 않는 쪽이 더 좋다. 또한 침면적 증대를 방지하는 의미로 배선영역의 빈부분을 더미배선(8)으로 매우도록 하면, 침면적은 증대되지 않는다. 또 배선의 사이(9)는 배선규칙에 따른 최소배선간격치(예컨대 3μm)이상으로 하는 것이 좋다.

### [효과]

본 발명은 이상에서 설명한 바와 같이 배선패턴의 설계시에 배선밀도가 작은 제품에 대해서 새로운 더미배선영역을 추가시킴으로써, 종래에 문제로 되고 있던 배선형성시의 배선의 가늘어짐이나 배선의 절단이 발생하지 않게 되어, 원료에 대한 제품의 비율 및 신뢰성을 현저하게 향상시킬 수 있다.

## (57) 청구의 범위

## 청구항 1

반도체장치의 배선형성시에 사용하는 마스크(1)에 더미배선용 마스크영역(4)을 설치하고, 이 마스크(1)를 이용해서 실제로 사용하는 소자배선(7)이외에 더미배선(8)을 형성시키는 것을 특징으로 하는 반도체장치의 제조방법.

## 청구항 2

제1항에 있어서, 상기 마스크(1)가 유리마스크인 것을 특징으로 하는 반도체장치의 제조방법.

## 도면

도면1-a

도면1-b

도면2-a

도면2-b