# **PCT**

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

| (21) International Application Number: PCT/US89/05579 (22) International Filing Date: 8 December 1988 (09.12.89) (30) Priority data: 283,425 9 December 1988 (09.12.88) US 283,534 9 December 1988 (09.12.88) US 283,534 9 December 1988 (09.12.88) US 282,008 9 December 1988 (09.12.88) US 283,406 9 December 1988 (09.12.88) US 283,410 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 283,427 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 283,427 (CIP) Silled on 9 December 1988 (09.12.88) US Silled on 9 December 1988 (09.12.88) US US  (60) Parent Applications or Grants (63) Related by Continuation US  (64) Parent Applications or Grants (65) Related by Continuation US  (65) Related by Continuation US  283,427 (CIP) Silled on 9 December 1988 (09.12.88) US US  (72) International Filing Date: 8 December 1988 (09.12.88) US 9 December 1988 (09.12.88) US 8 December 1988 (09.12.88) US 8 December 1988 (09.12.88) US 9 December 1988 (09.12.88) US 8 December 1988 (09.12 | (51) International Patent Classification <sup>5</sup> : |                         |         | (11) International Publication Number: |                                                    | WO 90/06633                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------|---------|----------------------------------------|----------------------------------------------------|------------------------------|--|

| (22) International Filing Date: 8 December 1989 (08.12.89)  (30) Priority data:  283,425 9 December 1988 (09.12.88) US 283,534 9 December 1988 (09.12.88) US 282,402 9 December 1988 (09.12.88) US 282,008 9 December 1988 (09.12.88) US 283,427 9 December 1988 (09.12.88) US 283,427 9 December 1988 (09.12.88) US 283,440 9 December 1988 (09.12.88) US 283,442 9 December 1988 (09.12.88) US 283,440 9 December 1988 (09 |                                                         | 06F 7/00                | A1      | (43                                    | 3) International Publication Date:                 | 14 June 1990 (14.06.90)      |  |

| (22) International Filing Date: 8 December 1989 (08.12.89)  (30) Priority data:  283,425 9 December 1988 (09.12.88) US 282,819 9 December 1988 (09.12.88) US 282,402 9 December 1988 (09.12.88) US 282,402 9 December 1988 (09.12.88) US 282,406 9 December 1988 (09.12.88) US 283,427 9 December 1988 (09.12.88) US 283,427 9 December 1988 (09.12.88) US 283,428 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 282,402 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 282,492 9 December 1988 (09.12.88) US 282,492 9 December 1988 (09.12.88) US 282,492 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US Filed on 9 December 1988 (09.12.88) US US  100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (21) International Application Number: PCT/US           |                         |         | 579                                    | 1                                                  | 9 December 1988 (09.12.88)   |  |

| (23) Priority data:  283,425 9 December 1988 (09.12.88) US 282,349 9 December 1988 (09.12.88) US 282,402 9 December 1988 (09.12.88) US 282,402 9 December 1988 (09.12.88) US 282,406 9 December 1988 (09.12.88) US 283,447 9 December 1988 (09.12.88) US 283,447 9 December 1988 (09.12.88) US 283,447 9 December 1988 (09.12.88) US 283,446 9 December 1988 (09.12.88) US 283,446 9 December 1988 (09.12.88) US 283,454 9 December 1988 (09.12.88) US 283,455 10 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |                         | (00 12  | ou/                                    |                                                    |                              |  |

| Section   Priority data:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (22) International Filing Date: 8 December 1989         |                         | (00.12. | 07)                                    |                                                    | 283,426 (CIP)                |  |

| 283,425 9 December 1988 (09.12.88) US 282,402 9 December 1988 (09.12.88) US 282,403 9 December 1988 (09.12.88) US 282,406 9 December 1988 (09.12.88) US 283,427 9 December 1988 (09.12.88) US 283,140 9 December 1988 (09.12.88) US 283,140 9 December 1988 (09.12.88) US 283,428 9 December 1988 (09.12.88) US 283,428 9 December 1988 (09.12.88) US 283,428 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 283,544 9 December 1988 (09.12.88) US 283,549 9 December 1988 (09.12.88) US 283,549 9 December 1988 (09.12.88) US 283,549 9 December 1988 (09.12.88) US 283,426 10 9 December 1988 (09.12.88) US 283,426 10 9 December 1988 (09.12.88) US 283,426 10 9 December 1988 (09.12.88) US 283,427 0 10 9 December 1988 (09.12.88) US 283,426 10 9 December 1988 (09.12.88) US 283,427 0 10 9 December 1988 (09.12.88) US 283,426 10 9 December 1988 (09.12.88) US 283,426 10 9 December 1988 (09.12.88) US 283,426 10 9 December 1988 (09.12.88) US 283,427 0 10 9 December 1988 (09.12.88) US 283,429 10 9 December 1988 (09.12.88) US 383,549 10 9 December 1988 (09.12.88) US 383,549 10 9 December 1988 (09.12.88) US 383,426 10 9 December 1988 (09.12.88) US 383,549 10 9 December 100.00 US 383,425 (US). US,                                                                             | (30) Priority data:                                     |                         |         |                                        |                                                    | 9 December 1988 (09.12.88)   |  |

| 282,819   9   December 1988 (09.12.88)   US   283,544   9   December 1988 (09.12.88)   US   282,402   9   December 1988 (09.12.88)   US   283,427   9   December 1988 (09.12.88)   US   283,427   9   December 1988 (09.12.88)   US   283,440   9   December 1988 (09.12.88)   US   283,440   9   December 1988 (09.12.88)   US   283,440   9   December 1988 (09.12.88)   US   283,428   9   December 1988 (09.12.88)   US   283,426   9   December 1988 (09.12.88)   US   283,426   9   December 1988 (09.12.88)   US   283,549   9   December 1988 (09.12.88)   US   282,410   CIP   CI   |                                                         | 9 December 1988 (09.12. | 88)     | US                                     | US                                                 | 282,792 (CIP)                |  |

| 283,534 9 December 1988 (09.12.88) US 282,402 9 December 1988 (09.12.88) US 282,2008 9 December 1988 (09.12.88) US 282,406 9 December 1988 (09.12.88) US 282,406 9 December 1988 (09.12.88) US 283,140 9 December 1988 (09.12.88) US 283,410 9 December 1988 (09.12.88) US 283,428 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 283,426 [US |                                                         |                         |         | US                                     | Filed on                                           | 9 December 1988 (09.12.88)   |  |

| 282,402 9 December 1988 (09.12.88) US 282,406 9 December 1988 (09.12.88) US 283,427 9 December 1988 (09.12.88) US 283,427 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 283,549 9 December 1988 (09.12.88) US 283,470 S December 1988 (09.12.88) US 282,410 S December 1988 (09.12.88) US S 282,410 S December 1988 (09.12.88) US S 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 Decembe | 283,534                                                 | 9 December 1988 (09.12. |         |                                        |                                                    |                              |  |

| 282,008 9 December 1988 (09.12.88) US 283,427 9 December 1988 (09.12.88) US 282,406 9 December 1988 (09.12.88) US 283,140 9 December 1988 (09.12.88) US 283,428 9 December 1988 (09.12.88) US 283,554 9 December 1988 (09.12.88) US 283,554 9 December 1988 (09.12.88) US 282,792 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 282,402 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 D |                                                         | 9 December 1988 (09.12. |         |                                        |                                                    |                              |  |

| 282,406 9 December 1988 (09.12.88) US 283,140 9 December 1988 (09.12.88) US 282,417 9 December 1988 (09.12.88) US 283,428 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 282,792 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (2IP) Filed on 9 December 1988 (09.12.88) US US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 1US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 10 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 10 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.8 |                                                         |                         |         |                                        |                                                    |                              |  |

| 283,440 9 December 1988 (09.12.88) US 282,417 9 December 1988 (09.12.88) US 283,428 9 December 1988 (09.12.88) US 283,554 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 283,429 9 December 1988 (09.12.88) US 283,534 9 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US US 283,426 (CIP) Filed on 9 December 1988 (09.12.88) US US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,534 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,534 (CIP) Filed on 9 December 1988 (09.12.88) US 283,634 (CIP) Filed on 9 December 1988 (09.12.88) US 283,640 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 |                                                         |                         |         |                                        | Filed on                                           | 9 December 1988 (09.12.88)   |  |

| SEMICONDUCTOR CORPORATION [US/US]; 435                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         |                         |         |                                        | (Ma) 1 1 / (C                                      | Charles assemble TICL DALLAS |  |

| Beltwood Parkway South, Dallas, TX 75244 (US).  283,428 9 December 1988 (99.12.88) US 283,544 9 December 1988 (99.12.88) US 282,792 9 December 1988 (99.12.88) US 283,549 9 December 1988 (99.12.88) US 283,549 9 December 1988 (99.12.88) US 282,410 9 December 1988 (99.12.88) US (60) Parent Applications or Grants (63) Related by Continuation US (64) Parent Applications or Grants (65) Related by Continuation US (66) Parent Applications or Grants (66) Parent Applications or Grants (67) Parent Applications or Grants (68) Related by Continuation US (69) Parent Applications or Grants (69) Parent Applications or Grants (61) Related by Continuation US (60) Parent Applications or Grants (61) Related by Continuation US (62) Parent Applications or Grants (63) Related by Continuation US (64) Parent Applications or Grants (65) Related by Continuation US (66) Parent Applications or Grants (65) Related by Continuation US (66) Parent Applications or Grants (67) Inventors; and (75) Inventors |                                                         |                         |         |                                        | (71) Applicant (for all designated                 | DODATION HIS /HISI / 1250    |  |

| 283,554 9 December 1988 (09.12.88) US 283,426 9 December 1988 (09.12.88) US 282,792 9 December 1988 (09.12.88) US 283,549 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US (60) Parent Applications or Grants (63) Related by Continuation US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 283,534 (CIP) Filed on 9 December 1988 (09.12.88) US 283,534 (CIP) Filed on 9 December 1988 (09.12.88) US 282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,421 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,424 (CIP) Filed on 9 December 1988 (09.12.88) US 283,424 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 282,400 (CIP) Filed on 9 December 1988 (09.12.88) US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US 282,400 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 28 |                                                         |                         |         |                                        |                                                    |                              |  |

| 283,426 9 December 1988 (09.12.88) US 282,792 9 December 1988 (09.12.88) US 283,549 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US (60) Parent Applications or Grants (63) Related by Continuation US Filed on US Electropean patent) Filed on US Filed on US Electropean patent), FR (European patent), JP, KR, LU (European patent), JP, KR, LU (European patent), SE (European patent), JP, KR, LU (European patent), SE (European patent), SE (European patent), SE (European patent), JP, KR, LU (European patent), SE (European patent), JP, KR, LU (European patent), SE (European patent), JP, KR, LU (European patent), VS Filed on US US SEQ.417 (CIP) Filed on US SEQ.41 | 283,428                                                 |                         |         |                                        | beliwood raikway South, i                          | Janas, 1A /3244 (05).        |  |

| 282,792 9 December 1988 (09.12.88) US 283,549 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US  (60) Parent Applications or Grants (63) Related by Continuation US Filed on US Filed on US 283,425 (CIP) Filed on 9 December 1988 (09.12.88) US Filed on US 282,402 (CIP) Filed on 9 December 1988 (09.12.88) US Filed on 9 December 1988 (09.12.88) US Filed on 9 December 1988 (09.12.88) US 282,402 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12.88) US 283,447 (CIP) Filed on 9 December 1988 (09.12. |                                                         | 9 December 1986 (09.12. |         |                                        | (72) Inventors and                                 |                              |  |

| 283,349 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US 282,410 9 December 1988 (09.12.88) US (60) Parent Applications or Grants (63) Related by Continuation US Filed on US Say,402 (CIP) Filed on US Say,402 (CIP) Filed on US Say,402 (CIP) Filed on US Filed on US Say,402 (CIP) Filed on US Say,402 (CIP) Filed on US Say,402 (CIP) Filed on US Say,403 (CIP) Filed on US Say,404 (CIP) Filed on US Say,406 (CIP) Filed on US Say,407 (CIP) Filed on US Say,417 (CIP) Filed on US Say,410 (CIP) Filed on US Say,410 (CIP) Filed on US Say,417 (CIP) Filed on US Say,410 (CIP) Say,410 (CI |                                                         |                         |         |                                        | (75) Inventors/Applicants (for IIS of              | nh) · LEE, Robert, D. IUS/   |  |

| 282,410 9 December 1988 (09.12.88) US  (60) Parent Applications or Grants (63) Related by Continuation US Filed on US Eas, 406 (CIP) Filed on US Eas, 417 (CIP) Filed on US Eas, 418 (US-US]; 2217 Via del Norte, Carrollton, TS 75006 (US). MOUNGER, Robert, W. [US/US]; 428 Mists Trail, Dal las, TX 75248 (US). HEPTIG, John, Patrick [US/US] 7000 Treehaven, Fort Worth, TX 76116 (US). KUWSKI, Hal [US/US]; 4208 West Creek Drive, Dal las, TX 75252 (US). KLUGHART, Kevin, M. [US/US] 3721 Spring Valley Road, 143131, Dallas, TX 7524 (US).  (US).  (VS).  (V |                                                         |                         |         |                                        | USI: 916 Linwood, Denton.                          | TX 76201 (US), DIAS, Do-     |  |

| (60) Parent Applications or Grants (63) Related by Continuation US Filed on US Exa,402 (CIP) Filed on US Exa,404 (CIP) Filed on US Exa,404 (CIP) Filed on US Exa,405 (CIP) Filed on US Exa,406 (CIP) Filed on US Exa,407 (CIP) Filed on US Exa,408 (CIP) Filed on US |                                                         |                         |         |                                        | nald, R. IUS/USI: 2217 Vi                          | a del Norte, Carrollton, TX  |  |

| (60) Parent Applications or Grants (63) Related by Continuation US Filed on US | 202,410                                                 | ) December 1900 (03:12: | 00)     | -                                      | 75006 (US), MOUNGER,                               | Robert, W. [US/US]; 4280     |  |

| (63) Related by Continuation US Filed on US Examples U | (60) Parent Applications or Grants                      |                         |         |                                        | Trinity Mills Road, 143507, Dallas, TX 75252 (US). |                              |  |

| S   183,425 (CIP)   Filed on   9 December 1988 (09.12.88)   US   283,534 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,402 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,008 (CIP)   Filed on   9 December 1988 (09.12.88)   US   283,427 (CIP)   Filed on   9 December 1988 (09.12.88)   US   283,427 (CIP)   Filed on   9 December 1988 (09.12.88)   US   283,427 (CIP)   Filed on   9 December 1988 (09.12.88)   US   283,440 (CIP)   Filed on   9 December 1988 (09.12.88)   US   283,440 (CIP)   Filed on   9 December 1988 (09.12.88)   US   283,440 (CIP)   Filed on   9 December 1988 (09.12.88)   US   283,440 (CIP)   Filed on   9 December 1988 (09.12.88)   US   283,440 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   US   282,417 (CIP)   Filed on   9 December 1988 (09.12.88)   282,417 (CIP)   European patent), IT (European patent), SE (European patent), US   Published   Published   Pu   | (63) Related by Continu                                 | ation                   |         |                                        | BOLAN, Michael, L. [US/US]; 6214 Misty Trail, Dal- |                              |  |

| Second Prize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                         | 283,                    | 425 (C) | IP)                                    | las, TX 75248 (US). HEPT                           | IG, John, Patrick [US/US];   |  |

| Filed on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Filed on                                                |                         |         |                                        | 7000 Treehaven, Fort Wor                           | th, TX 76116 (US). KUR-      |  |

| Sampels & Wooldridge, 2001 Bryan Tower, Suite 3200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |                         |         |                                        | KOWSKI, Hal [US/US]; 4                             | 208 West Creek Drive, Dal-   |  |

| Filed on 9 December 1988 (09.12.88) US 282,402 (CIP) Filed on 9 December 1988 (09.12.88) US 282,008 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 283,440 (CIP) Filed on 9 December 1988 (09.12.88) US 283,440 (CIP) Filed on 9 December 1988 (09.12.88) US 283,440 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) EXAMPLE: GROOVER, Robert, III; Worsham, Forsythe Sampels & Wooldridge, 2001 Bryan Tower, Suite 3200  (81) Designated States: AT (European patent), DE (European patent), FR (European patent), IT (European patent), IT (European patent), NL (European patent), SE (European patent), US  Published                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Filed on                                                |                         |         |                                        | las, TX 75252 (US). KLUG                           | HART, Kevin, M. [US/US];     |  |

| US                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |                         |         |                                        |                                                    | 143131, Dallas, 1X /5244     |  |

| Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 283,440 (CIP) Filed on 9 December 1988 (09.12.88) US 283,440 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) Published                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |                         |         |                                        | (US).                                              |                              |  |

| US  282,008 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88) US 283,406 (CIP) Filed on 9 December 1988 (09.12.88) EX (European patent), FR (European patent), JP, KR, LU (European patent), IT (European patent |                                                         |                         |         |                                        | CROOKER D.L.                                       | III. Washam Famula           |  |

| Filed on 9 December 1988 (09.12.88) US 283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88)                                                                                                              |                                                         |                         |         |                                        | (74) Agent: GROOVER, Robert,                       | , III; worsnam, rorsythe,    |  |

| US  283,427 (CIP) Filed on 9 December 1988 (09.12.88) US 282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88) Published  (81) Designated States: AT (European patent), BE (European patent), CH (European patent), FR (European patent), JP, KR, LU (European patent), IV (European patent), SE (European patent), US  Published                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |                         |         |                                        | Sampels & Wooldnage, 200                           | of Bryan Tower, Suite 3200,  |  |

| Filed on US 282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88)  Published  (81) Designated States: AT (European patent), BE (European patent), CH (European patent), FR (European patent), FR (European patent), IT (European patent), IT (European patent), IT (European patent), SE (European patent), US  Published                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |                         |         |                                        | Danas, 1A /3201 (OS).                              |                              |  |

| US  282,406 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88) Published  patent), CH (European patent), DE (European patent) ES (European patent), IT (European patent), JP, KR, LU (European patent), NL (European patent), SE (European patent), US.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                         |                         |         |                                        | (21) Designated States AT (Furo                    | hean natent) BF (Furonean    |  |

| Filed on 9 December 1988 (09.12.88) US 283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88) Filed on 9 December 1988 (09.12.88)  Published  ES (European patent), FR (European patent), JP, KR, LU (European patent), NL (European patent), SE (European patent), US.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |                         |         |                                        |                                                    |                              |  |

| US  283,140 (CIP) Filed on 9 December 1988 (09.12.88) US 282,417 (CIP) Filed on 9 December 1988 (09.12.88) Published  ropean patent), IT (European patent), JP, KR, LU (European patent), NL (European patent), SE (European patent), US.  Published                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         |                         |         |                                        | ES (Furonean natent) FR                            | (European patent). GB (Eu-   |  |

| Filed on 9 December 1988 (09.12.88) ropean patent), NL (European patent), SE (European patent), US patent), US. Filed on 9 December 1988 (09.12.88) Published                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |                         |         |                                        | ropean patent), IT (Europe                         | an patent). JP. KR. LU (Eu-  |  |

| US 282,417 (CIP) patent), US. Filed on 9 December 1988 (09.12.88) <b>Published</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |                         |         |                                        | ropean patent), NL (Euror                          | pean patent). SE (European   |  |

| Filed on 9 December 1988 (09.12.88) Published                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         | 282.                    | 417 (CI | ĮΡ                                     |                                                    | ,, Ç                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |                         |         |                                        |                                                    |                              |  |

| US 283,428 (CIP)   With international search report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | US                                                      |                         |         |                                        | With international search repu                     | ort                          |  |

#### (54) Title: MICROPOWERED RF DATA MODULES

#### (57) Abstract

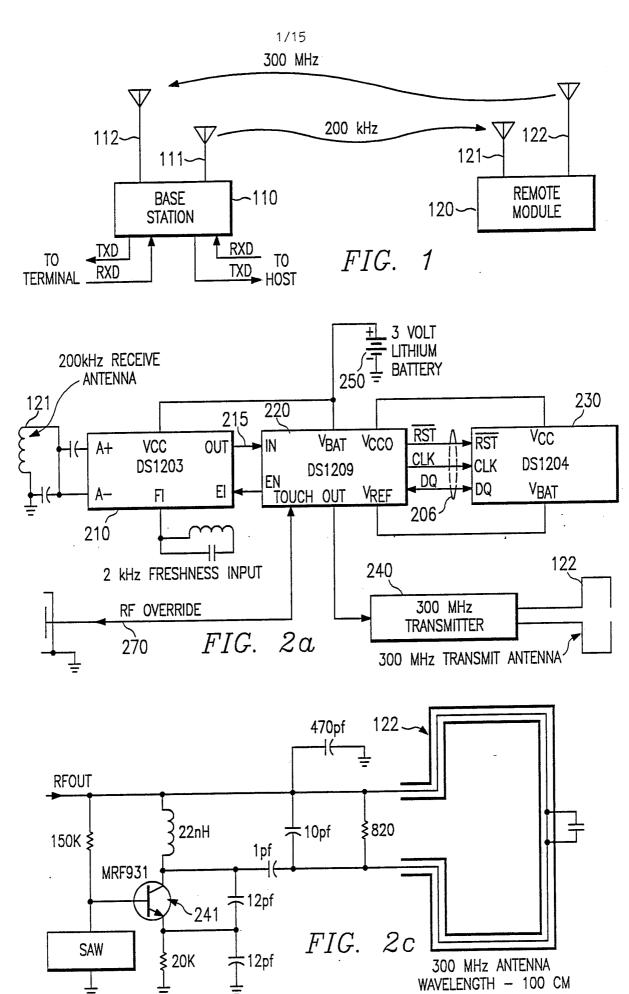

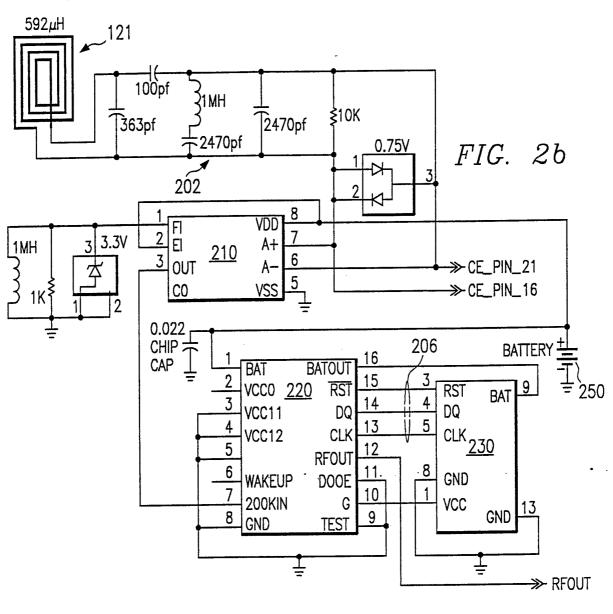

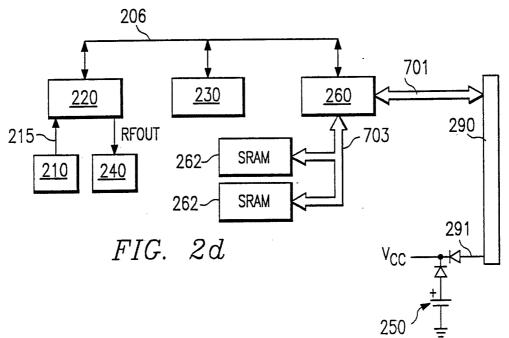

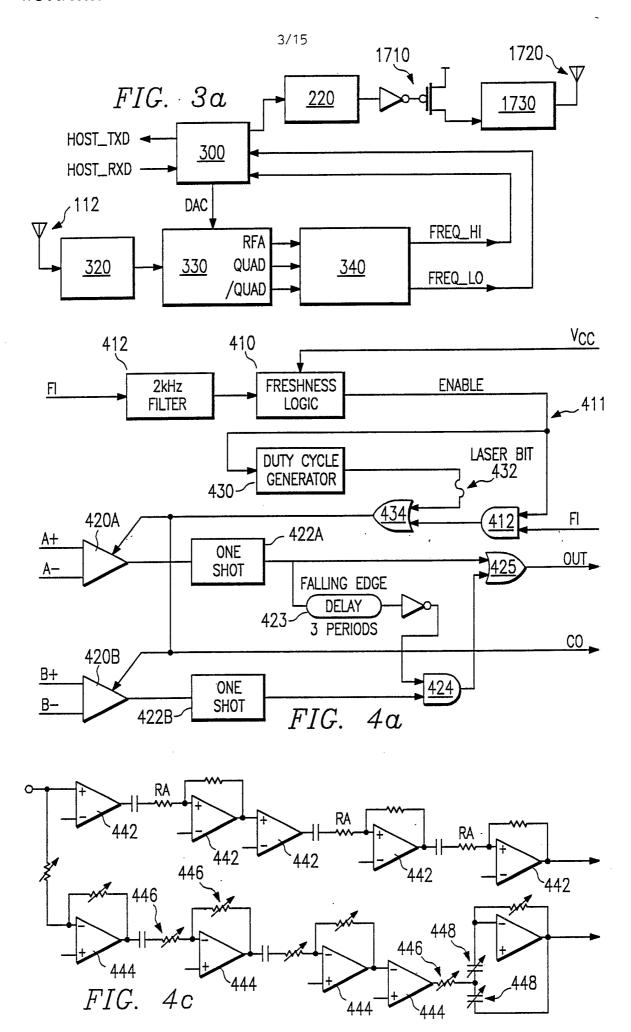

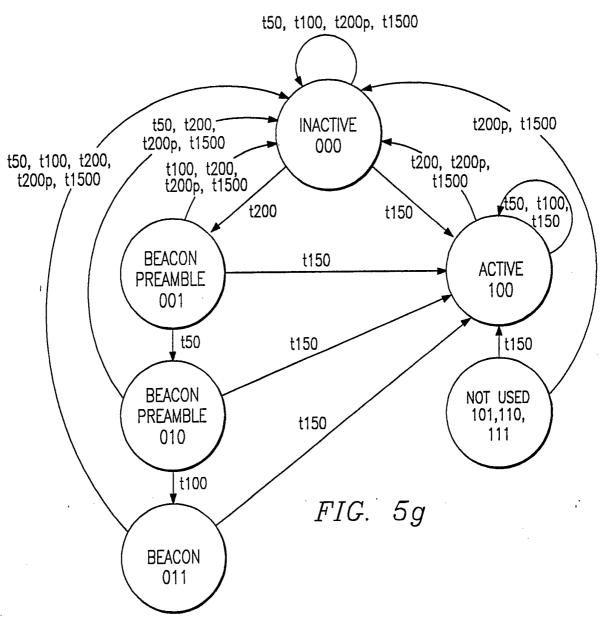

A low-power wireless data communication system, in which base stations (110) can automatically interface to batter-powered portable data modules (210) as they are brought within range. In the data modules (210), each receive antenna (121) is directly connected to a gain-controlled comparator (420A, 420B). Bandpass filtering (448) is accomplished economically by use of simple digital circuits. The two-level digital output from the comparator (420A, 420B) is fed (through an intersymbol detector, a counter, and a ripple-through magnitude comparator) to a state

3 VOLT LITHIUM 200kHz RECEIVE BATTERY antènna 230 VCC **Vcco** VCC OUT **VBAT** A+ DS1203 DS1204 DS1209 El FI VREF VBAT TOUCH OUT 210 2 kHz FRESHNESS INPUT 240 RF OVERRIDE 300 MHz TRANSMITTER 270 300 MHz TRANSMIT ANTENNA?

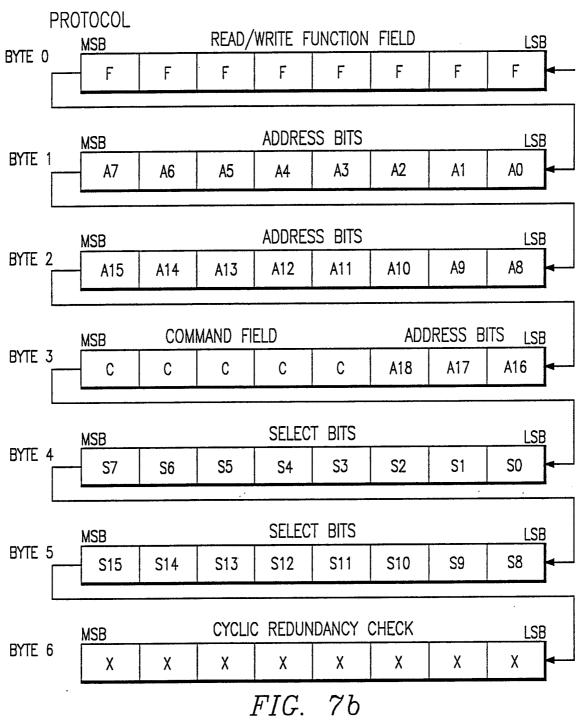

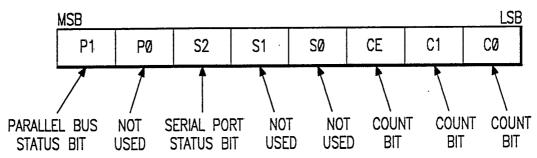

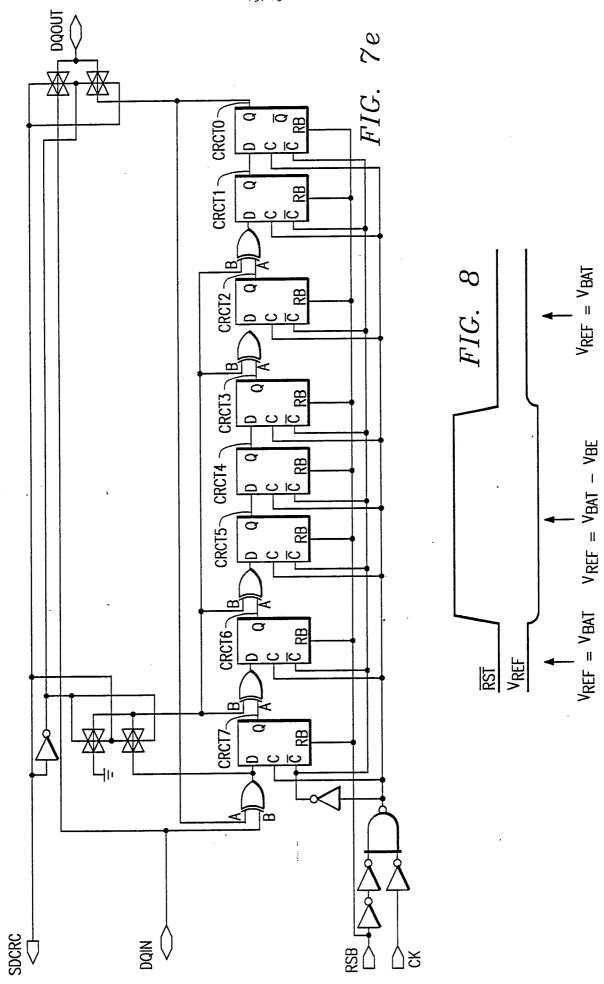

magnitude comparator) to a state machine (552), which decodes the resulting digital waveform to a conventional serial-bus format. The internal data bus (701D) provides an interface to memory chips (262) and (optionally) to other chips, such as an electronic key. The decoder chip (220) also provides a secondary power supply to the other chips (230), and modulates the power supply (250) to assist detection of transitions on the reset-bar line of the serial bus (206). The modules (230) use widely different frequencies for read and write operations. (Transmissions by the base station (110) use a pulse-width modulation scheme where the most commonly used signals correspond to the shortest pulse. A "read" command is encoded as the same pulse width as one of the two write commands). In addition, a pair of touch contacts (270) can be used to override the RF link. Error-checking (Fig. 7E) is performed on incoming commands before memory access (260) is permitted. "Freshness seal" logic (510) prevents any battery drain until the module is initially turned on (by placing it in a strong field).

1

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT | Austria                      | ES  | Spain                        | MG | Madagascar               |

|----|------------------------------|-----|------------------------------|----|--------------------------|

| AU | Australia                    | FI  | Finland                      | ML | Mali                     |

| BB | Barbados                     | FR  | France                       | MR | Mauritania               |

| BE | Belgium                      | GA  | Gabon                        | MW | Malawi -                 |

| BF | Burkina Fasso                | GB  | United Kingdom               | NL | Netherlands              |

| BG | Bulgaria                     | HU  | Hungary                      | NO | Norway                   |

| BJ | Benin                        | π   | Italy                        | RO | Romania                  |

| BR | Brazil                       | JР  | Japan                        | SD | Sudan                    |

| CA | Canada                       | KP  | Democratic People's Republic | SE | Sweden                   |

| CF | Central African Republic     |     | of Korea                     | SN | Senegal                  |

| CG | Congo                        | KR  | Republic of Korea            | SU | Soviet Union             |

| CH | Switzerland                  | Ц   | Liechtenstein                | TD | Chad                     |

| CM | Cameroon                     | LK. | Sri Lanka                    | TG | Togo                     |

| DE | Germany, Federal Republic of | m   | Luxembourg                   | US | United States of America |

| מע | Danmark                      | MC  | Manag                        | -  |                          |

# MICROPOWERED RF DATA MODULES

5

10

15

25

### BACKGROUND AND SUMMARY OF THE INVENTION

The present invention relates to wireless data interface systems, and to portable data modules for use within such a system, and to powerefficient integrated circuits.

Systems which can provide short-range wireless data communication between a base station and a portable low-power module have recently been the subject of development efforts by a number of groups. Such systems can be extremely useful in many contexts, such as control of personnel access to secure facilities, medical monitoring of inpatients, automated livestock management, automated manufacturing generally, inventory control, theft control, and others described below.

There are many uses for low-powered RF receivers, in such systems and elsewhere. Due to the legal constraints of spectrum allocation, many short-range data links must use extremely small RF signal levels. Moreover, in many cases the transceivers used for such communication must operate with minimal power drain, including minimal standby power.

10

15

25

30

It is very difficult to satisfy the objectives of low power consumption while also providing adequate sensitivity and noise rejection.

However, such a system is subject to many constraints. If the portability of the portable stations is to be maximized, the battery weight must be small. This means that the power consumption of the portable module - in active or in standby mode - must be exceedingly low. Moreover, many possible applications are highly cost-sensitive.

In most applications, rechargeable batteries are not suitable for a power supply. Rechargeable batteries not only impose a user burden (to perform recharging), but also tend to have electrical characteristics which may be dependent on the discharge/recharge history of the particular battery. Many possible applications cannot tolerate such uncertainty, and require a degree of reliability which demands a very conservative approach to power supply design and rating.