(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4617546号

(P4617546)

(45) 発行日 平成23年1月26日(2011.1.26)

(24) 登録日 平成22年11月5日(2010.11.5)

(51) Int.Cl.

H01S 5/22 (2006.01)

F 1

H01S 5/22 610

請求項の数 5 (全 8 頁)

(21) 出願番号 特願2000-235342 (P2000-235342)

(22) 出願日 平成12年8月3日 (2000.8.3)

(65) 公開番号 特開2002-50829 (P2002-50829A)

(43) 公開日 平成14年2月15日 (2002.2.15)

審査請求日 平成18年12月26日 (2006.12.26)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100098785

弁理士 藤島 洋一郎

(74) 代理人 100109656

弁理士 三反崎 泰司

(74) 代理人 100130915

弁理士 長谷部 政男

(74) 代理人 100155376

弁理士 田名網 孝昭

(72) 発明者 平田 照二

東京都品川区北品川6丁目7番35号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】アレイ型プロードストライプ半導体レーザおよびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

凸領域と凹領域とが隣接して形成されると共に前記凸領域が一定のピッチで複数設けられ、前記凸領域の幅が  $10 \mu m \sim 100 \mu m$  である第1導電型の基板と、

前記基板の凸領域に、第1導電型のクラッド層、活性層、第2導電型のクラッド層の順に形成される機能層と、

前記基板の凹領域に、前記機能層と同じ構成で、その凹領域を埋めるよう形成される埋め込み層と、

前記機能層および前記埋め込み層の上に形成される第2導電型の第1コンタクト層と、

前記埋め込み層上に形成された第1コンタクト層の上で少なくとも前記活性層の端部全域にわたり接するよう形成される第1導電型の電流ブロック層と

を備えるアレイ型プロードストライプ半導体レーザ。

## 【請求項 2】

前記電流ブロック層上には、前記機能層上の第1コンタクト層とほぼ同じ位置に、第2導電型の第2コンタクト層が形成されている

請求項1記載のアレイ型プロードストライプ半導体レーザ。

## 【請求項 3】

前記電流ブロック層と前記第2コンタクト層との間に高さ調整層が設けられている

請求項2記載のアレイ型プロードストライプ半導体レーザ。

## 【請求項 4】

10

20

前記基板は G a A s 系基板である

請求項 1 記載のアレイ型プロードストライプ半導体レーザ。

【請求項 5】

第 1 導電型の基板に凸領域と凹領域とを隣接して形成すると共に前記凸領域を一定のピッチで複数設け、前記凸領域の幅を  $10 \mu m \sim 100 \mu m$  とする工程と、

前記基板に第 1 導電型のクラッド層、活性層、第 2 導電型のクラッド層を順に積層し、前記凸領域上に機能層、前記凹領域内に埋め込み層を同時に構成する工程と、

前記機能層および前記埋め込み層の上に第 2 導電型の第 1 コンタクト層を形成する工程と、

前記第 1 コンタクト層の上に第 1 導電型の電流ブロック層を形成し、前記埋め込み層上に形成された第 1 コンタクト層の上において、前記電流ブロック層が少なくとも前記活性層の端部全域にわたり接する状態にする工程と、

前記電流ブロック層の上に第 2 導電型の第 2 コンタクト層を形成する工程と、

前記凸領域上で前記第 1 コンタクト層より上に形成された層を除去する工程と

を備えるアレイ型プロードストライプ半導体レーザの製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、予め基板に形成した凹凸を利用して各層を形成したアレイ型プロードストライプ半導体レーザおよびその製造方法に関する。

【0002】

【従来の技術】

出力が数十W以上の半導体レーザは、レーザディスプレイ、レーザ加工、高調波発生等に用いる光源として近年開発が進んでいる。特に、複数の発光部を並べた構成となるアレイ型のプロードストライプレーザは、高出力光を出射できる光源として期待がもたれている。

【0003】

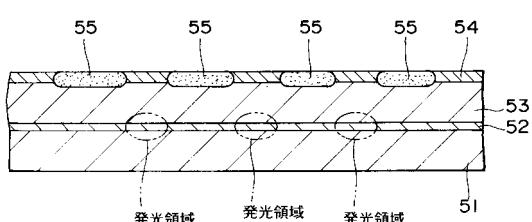

図 10 は従来のアレイ型半導体レーザを説明する模式図である。このアレイ型半導体レーザは、複数の発光領域の全体にわたり、n 型クラッド層 51、活性層 52、p 型クラッド層 53 および p 型コンタクト層 54 を順に形成し、発光領域以外の p 型コンタクト層 54 にイオン注入を行って電流抑制層 55 を形成する。これにより、電流抑制層 55 以外の部分に電流が注入され、それに対応する複数の発光領域からレーザ光が出射されることになる。

【0004】

【発明が解決しようとする課題】

しかしながら、このようなアレイ型半導体レーザでは、各発光領域を構成する活性層がつながっていることから、いずれかの発光領域で発生した欠陥（劣化による欠陥等）が <100 > 方向に沿って活性層面内で成長し、隣の発光領域まで転移してしまう。これは、電流非注入であるはずの活性層内非活性領域を欠陥が簡単に通過してしまうのが原因であり、活性層内での電流拡散や隣接の活性層光出力による光励起が増殖エネルギー源となっているものと推測される。これにより、各発光領域の劣化を早め、信頼性の低下を招くという問題が生じる。

【0005】

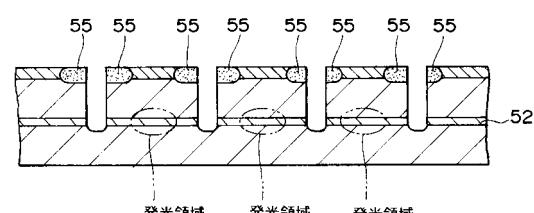

そこで、図 11 に示すように、電流抑制層の位置から活性層に達するエッティングを形成し、各発光領域の活性層 52 を分離したアレイ型半導体レーザが考えられている。これにより、いずれかの発光領域で発生した欠陥が活性層 52 を通して隣の発光領域に至ることがなくなる。

【0006】

しかし、このような構造では、欠陥の転移は抑制できるものの、エッティングによって活性層 52 界面（端部が露出する部分）が発生し、ここを新たな起点として欠陥の転移が起こ

10

20

30

40

50

るという問題がある。

【0007】

【課題を解決するための手段】

本発明は、このような課題を解決するために成されたものである。すなわち、本発明のアレイ型プロードストライプ半導体レーザは、凸領域と凹領域とが隣接して形成されると共に凸領域が一定のピッチで複数設けられ、凸領域の幅が $10\text{ }\mu\text{m} \sim 100\text{ }\mu\text{m}$ である第1導電型の基板と、基板の凸領域に、第1導電型のクラッド層、活性層、第2導電型のクラッド層の順に形成される機能層と、基板の凹領域に、機能層と同じ構成で、その凹領域を埋めるよう形成される埋め込み層と、機能層および埋め込み層の上に形成される第2導電型の第1コンタクト層と、埋め込み層上に形成された第1コンタクト層の上で少なくとも活性層の端部全域にわたり接するよう形成される第1導電型の電流ブロック層とを備えている。10

【0008】

このような本発明では、凸領域上に機能層が形成され、その機能層における活性層の端部に電流ブロック層が接するように形成されているため、欠陥の発生や転移を抑制することができるようになる。

【0009】

また、本発明のアレイ型プロードストライプ半導体レーザの製造方法は、第1導電型の基板に凸領域と凹領域とを隣接して形成すると共に凸領域を一定のピッチで複数設け、凸領域の幅を $10\text{ }\mu\text{m} \sim 100\text{ }\mu\text{m}$ とする工程と、基板に第1導電型のクラッド層、活性層、第2導電型のクラッド層を順に積層し、凸領域上に機能層、凹領域内に埋め込み層を同時に構成する工程と、機能層および埋め込み層の上に第2導電型の第1コンタクト層を形成する工程と、第1コンタクト層の上に第1導電型の電流ブロック層を形成し、埋め込み層上に形成された第1コンタクト層の上において、その電流ブロック層が少なくとも活性層の端部全域にわたり接する状態にする工程と、電流ブロック層の上に第2導電型の第2コンタクト層を形成する工程と、凸領域上で第1コンタクト層より上に形成された層を除去する工程とを備えている。20

【0010】

このような本発明では、凸領域に機能層を形成し、これと同時に凹領域内に埋め込み層を形成し、その後に形成する電流ブロック層で機能層の活性層端部を囲むことができる。これにより、結晶成長炉で連続して各層を形成して活性層端部を囲むように構成でき、欠陥の発生や転移を抑制することができるようになる。30

【0011】

【発明の実施の形態】

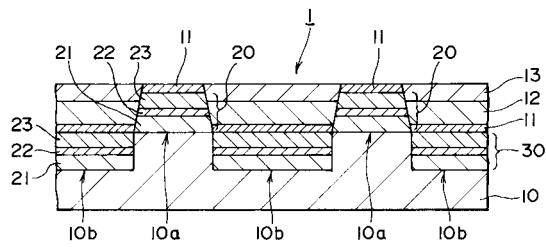

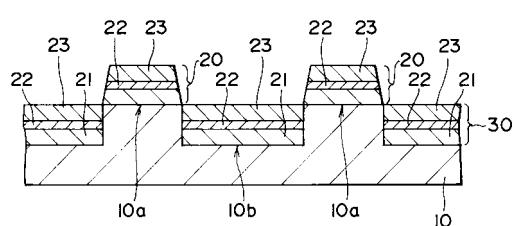

以下、本発明の実施の形態を図に基づいて説明する。図1は、本実施形態に係る半導体レーザを説明する模式断面図である。すなわち、この半導体レーザ1は、凸領域10aと凹領域10bとが隣接して形成されたn型の基板10と、この基板10の凸領域10aに、n型クラッド層21、活性層22、p型クラッド層23の順に形成される機能層20と、基板1の凹領域10bに機能層20と同じ構成で凹領域10bを埋めるよう形成される埋め込み層30と、埋め込み層30上および機能層20上に形成されるn型の第1コンタクト層11と、埋め込み層30上の第1コンタクト層11上で、少なくとも活性層22の端部全域にわたり接するよう形成されるn型の電流ブロック層12と、電流ブロック層12上に形成されるp型の第2コンタクト層13とを備えている。40

【0012】

基板10は、例えばn型のGaAs系、AlGaInP系、GaN系、InGaAs系、InP系が用いられる。なお、本実施形態では、(100)面を持つGaAs系の基板1を用いるものとする。この基板10の表面には、例えばウェットエッティングによって<011>方向の凸領域10aと凹領域10bとのストライプが形成されている。凸領域10aの高さ(凹領域10bの深さ)は約 $3\text{ }\mu\text{m} \sim 4\text{ }\mu\text{m}$ 、凸領域10aの図中横方向に沿った幅は約 $10\text{ }\mu\text{m} \sim 100\text{ }\mu\text{m}$ となる。50

## 【0013】

$n$ 型クラッド層21は、 $A1_{0.4}Ga_{0.2}As$ から構成され、 $2\mu m$ 厚で形成される。また、活性層22は、ノンドープの $A1_{0.12}Ga_{0.88}As$ から構成され、 $0.05\mu m$ 厚で形成される。さらに、 $p$ 型クラッド層23は、 $A1_{0.4}Ga_{0.6}As$ から構成され、 $2\mu m$ 厚で形成される。この $n$ 型クラッド層21、活性層22、 $p$ 型クラッド層23の3層によって凸領域10a上に発光のための機能層20が構成される。また、この3層の厚さと凹領域10bの深さとがほぼ等しく設定されており、3層を形成することで凹領域10bは埋め込み層30によって埋まる状態となる。

## 【0014】

埋め込み層30の上に形成される $p$ 型の第1コンタクト層11は、 $GaAs$ から構成され、 $0.3\mu m$ 以上の厚さで形成される。 $n$ 型の電流ブロック層12は、 $A1_{0.5}Ga_{0.5}As$ から構成され、 $0.5\mu m$ 厚で形成される。なお、図示する電流ブロック層12は、第1コンタクト層11上に形成される高さ調整用のダミー層を含むものとする。これにより、凸領域10a上に形成された機能層20の活性層22における端部が $n$ 型の電流ブロック層12で囲まれる状態となる。

10

## 【0015】

また、 $n$ 型の電流ブロック層12の上には必要に応じて $p$ 型の高さ調整層（図示せず）を設け、その上に $p$ 型の第2コンタクト層13が形成される。 $p$ 型の第2コンタクト層13は、 $GaAs$ から構成され、 $0.5\mu m$ 厚で形成される。

20

## 【0016】

このような構成から成る本実施形態の半導体レーザ1では、機能層20上の第1コンタクト層11と基板10の裏面とに電極を形成し、機能層20へ電流を注入する。この際、凹領域10bについては $n$ 型クラッド層21、 $p$ 型クラッド層23、 $n$ 型の電流ブロック層12および $p$ 型の第2コンタクト層13によって $n-p-n-p$ 型のサイリスタが構成され、電流は流れない状態となる。これにより、機能層20の活性層22のバンドギャップに対応する波長のレーザ光が出射される。

## 【0017】

特に、本実施形態では、凸領域10aの幅を $10\mu m \sim 100\mu m$ 程度にすることで、プロードストライプの機能層20を構成でき、幅広のレーザ光を出射できるようになる。しかも、複数の機能層20を設けて各々からレーザ光を出射することにより、高出力レーザ光を出射できることになる。

30

## 【0018】

また、このような半導体レーザ1では、機能層20および埋め込み層30を同一工程で製造でき、しかも、これら機能層20および埋め込み層30の成膜から連続して第1コンタクト層11、電流ブロック層12等の上層を形成できるため、活性層22の端部が製造途中で露出することがなくなり、活性層22の端部での欠陥発生を抑制できるようになる。

## 【0019】

また、本実施形態の半導体レーザ1は、基板10に凸領域10aと凹領域10bとが隣接するストライプを複数形成することにより、複数の凸領域10a上に各々機能層20を形成でき、アレイ型の半導体レーザ1を容易に構成できる。この際、先に説明したように、活性層22の端部が電流ブロック層12で囲まれているため、隣接する活性層22への欠陥の転移を的確に防止できることになる。

40

## 【0020】

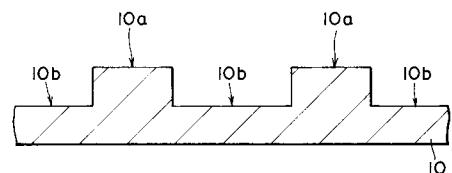

次に、本実施形態に係る半導体レーザ1の製造方法を説明する。先ず、図2に示すように、 $n$ 型 $GaAs$ から成る基板10を用い、その(100)面より成る主面にフォトレジストを塗布し、ストライプ状にパターニングして、<011>方向にウェットエッチングを施し、凸領域10aと凹領域10bとを交互に形成する。

## 【0021】

ここで、ウェットエッチングとしては、硫酸系の $H_2SO_4$ と $H_2O_2$ と $H_2O$ とが3:1:1の割合で混合されたエッチング液による結晶学的エッチングを行う。このエッチングに

50

より、凸領域 10 a の幅を 10 μm ~ 100 μm、凹領域 10 b の幅を 200 μm、深さを 3 μm ~ 4 μm にする。

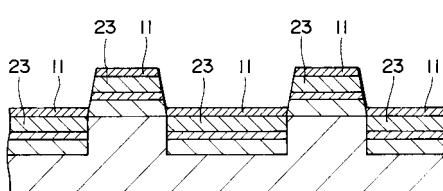

#### 【0022】

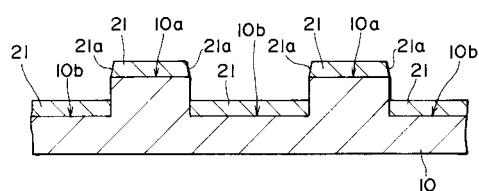

次に、図 3 に示すように、凸領域 10 a および凹領域 10 b が形成された基板 10 の(100)面に有機金属気相成長法(以下、「MOCVD」と言う。)によって第1導電型、例えばn型の  $\text{Al}_{0.4}\text{Ga}_{0.6}\text{As}$  から成るn型クラッド層 21 を厚さ 2 μm 形成する。

#### 【0023】

この際、凸領域 10 a 上に形成されるn型クラッド層 21 の側壁 21 a は、基板 10 の正面に対して約 55° の角度で成す(111)B結晶面が自然発生的に生じる。この(111)B結晶面ではエピタキシャル成長が生じにくいことから、凸領域 10 a 上と凹領域 10 b 内とでn型クラッド層 21 が分断して形成されることになる。

#### 【0024】

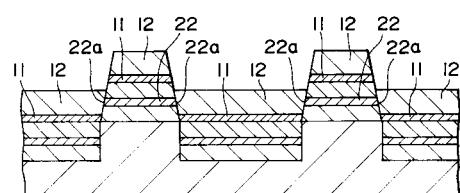

次に、図 4 に示すように、n型クラッド層 21 の上にノンドープの活性層 22 を例えば MOCVD によって形成する。活性層 22 としては、 $\text{Al}_{0.12}\text{Ga}_{0.88}\text{As}$  の組成で、例えば 0.05 μm 厚で形成する。

#### 【0025】

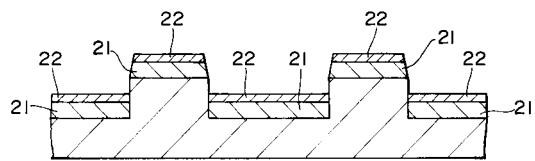

次いで、図 5 に示すように、この活性層 22 上に第2導電型、例えば p型の  $\text{Al}_{0.4}\text{Ga}_{0.6}\text{As}$  から成るn型クラッド層 21 を厚さ 2 μm 形成する。これにより、基板 10 の凸領域 10 a 上にn型クラッド層 21、活性層 22、p型クラッド層 23 から成る機能層 20 が構成され、基板 10 の凹領域 10 b 内に機能層 20 と同じ構成から成る埋め込み層 30 が構成される。なお、この埋め込み層 30 によって、凹領域 10 b 内がほぼ埋まる状態となる。

#### 【0026】

次に、図 6 に示すように、p型クラッド層 23 の上に第2導電型である例えば p型の第1コンタクト層 11 を形成する。第1コンタクト層 11 は、例えば GaAs から成り、0.3 μm 程度形成する。

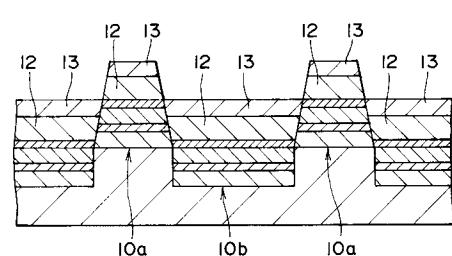

#### 【0027】

その後、図 7 に示すように、第1コンタクト層 11 の上に第1導電型である例えば n型の電流ブロック層 12 を形成する。n型の電流ブロック層 12 は、 $\text{Al}_{0.5}\text{Ga}_{0.5}\text{As}$  から構成され、2.5 μm 厚で形成される。これにより、凸領域 10 a 上に形成された機能層 20 の活性層 22 における端部 22 a が n型の電流ブロック層 12 で囲まれる状態となる。

#### 【0028】

次に、図 8 に示すように、電流ブロック層 12 の上に第2導電型である例えば p型の第2コンタクト層 13 を形成する。ここで、凹領域 10 b 上に形成する第2コンタクト層 13 の高さと、凸領域 10 a 上に形成されている第1コンタクト層 11 の高さとを合わせるために、電流ブロック層 12 と第2コンタクト層 13 との間に図示しない高さ調整層(例えば、第2導電型の  $\text{Al}_{0.4}\text{Ga}_{0.6}\text{As}$ )を設けてもよい。

#### 【0029】

そして、図 9 に示すように、基板 10 の凸領域 10 a 上に突出して形成された電流ブロック層 12 および第2コンタクト層 13 をエッチングし、凸領域 10 a 上の第1コンタクト層 11 が露出するようにする。

#### 【0030】

また、この後、第1コンタクト層 11 上に p 側電極(図示せず)、基板 10 の裏面に n 側電極(図示せず)を形成する。その後、基板 10 を所定の大きさに劈開し、本実施形態の半導体レーザ 1 が完成する。

#### 【0031】

このような半導体レーザ 1 の製造方法では、各層の形成を一連の MOCVD によってその供給ガスを切り替えることで 1 作業すなわち 1 回の結晶成長で製造することができる。つまり、MOCVD のチャンバ内を大気開放することなく、各層を各々形成できるようにな

10

20

30

40

50

る。

**【0032】**

これにより、活性層22の端部22aを大気にさらすことなく電流ブロック層12で囲むことができ、しかも、隣の機能層20における活性層22と電流ブロック層によって分離できるようになるため、欠陥の発生や転移を抑制できるようになる。

**【0033】**

なお、本実施形態では、図面の関係上、2つの凸領域10a上に各々機能層20を形成した例を示したが、本発明はこれに限定されず、3つ以上の凸領域に各々機能層を設けるようにしてもよい。1つの凸領域上に1つの機能層を形成してもよい。

**【0034】**

さらに、本実施形態では、第1導電型をn型、第2導電型をp型として説明したが、反対であってもよい。つまり、n型のGaAsから成る基板10を用いる例を示したが、p型のGaAsから成る基板を用いるようにしてもよい。このp型のGaAsから成る基板を用いるメリットは、電流リーケが少ないこと、Seドーパントを後でドープするため、Se分布の急峻性がよくなり、信頼性が向上する点である。

**【0035】**

また、基板10としては、GaAs以外であっても、例えばAlGaInP系、GaN系、InGaAs系、InP系の半導体レーザに適した材料であれば適用可能である。

**【0036】**

**【発明の効果】**

以上説明したように、本発明によれば次のような効果がある。すなわち、複数の機能層を備えているアレイ型プロードストライプ半導体レーザでも、各機能層の活性層が独立しているため、欠陥の転移が発生せず、信頼性を向上させることが可能となる。しかも、活性層の端部が電流ブロック層で囲まれているため、ここからの欠陥発生を抑制できるようになる。また、一度の結晶成長で製造できることから、製造工程を簡素化することが可能となる。

**【図面の簡単な説明】**

**【図1】**本実施形態に係る半導体レーザを説明する模式断面図である。

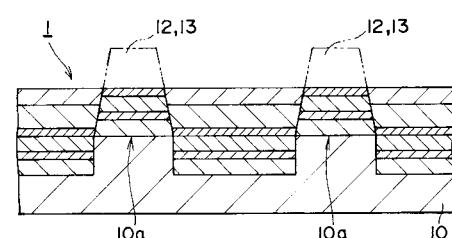

**【図2】**本実施形態に係る半導体レーザの製造方法を説明する模式断面図（その1）である。

**【図3】**本実施形態に係る半導体レーザの製造方法を説明する模式断面図（その2）である。

**【図4】**本実施形態に係る半導体レーザの製造方法を説明する模式断面図（その3）である。

**【図5】**本実施形態に係る半導体レーザの製造方法を説明する模式断面図（その4）である。

**【図6】**本実施形態に係る半導体レーザの製造方法を説明する模式断面図（その5）である。

**【図7】**本実施形態に係る半導体レーザの製造方法を説明する模式断面図（その6）である。

**【図8】**本実施形態に係る半導体レーザの製造方法を説明する模式断面図（その7）である。

**【図9】**本実施形態に係る半導体レーザの製造方法を説明する模式断面図（その8）である。

**【図10】**従来例を説明する模式断面図（その1）である。

**【図11】**従来例を説明する模式断面図（その2）である。

**【符号の説明】**

1...半導体レーザ、10...基板、10a...凸領域、10b...凹領域、11...第1コンタクト層、12...電流ブロック層、13...第2コンタクト層、20...機能層、21...n型クラッド層、22...活性層、23...p型クラッド層、30...埋め込み層

10

20

30

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

審査官 小林 和幸

(56)参考文献 特開平05-063298(JP,A)

特開平04-364084(JP,A)

特開平04-216691(JP,A)

特開平10-200204(JP,A)

特開2000-011417(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00-5/50