(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6242852号

(P6242852)

(45) 発行日 平成29年12月6日(2017.12.6)

(24) 登録日 平成29年11月17日(2017.11.17)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| G 11 C 7/22   | (2006.01) |

| G 11 C 11/419 | (2006.01) |

| H 03 K 3/017  | (2006.01) |

| G 06 F 12/00  | (2006.01) |

| G 06 F 1/06   | (2006.01) |

| G 11 C 7/22   | 100       |

| G 11 C 11/419 | 140       |

| H 03 K 3/017  | 564 C     |

| G 06 F 12/00  | 520       |

請求項の数 14 (全 15 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-503586 (P2015-503586)  |

| (86) (22) 出願日 | 平成25年3月28日 (2013.3.28)        |

| (65) 公表番号     | 特表2015-520434 (P2015-520434A) |

| (43) 公表日      | 平成27年7月16日 (2015.7.16)        |

| (86) 国際出願番号   | PCT/US2013/034414             |

| (87) 国際公開番号   | W02013/149040                 |

| (87) 国際公開日    | 平成25年10月3日 (2013.10.3)        |

| 審査請求日         | 平成28年3月7日 (2016.3.7)          |

| (31) 優先権主張番号  | 13/433,891                    |

| (32) 優先日      | 平成24年3月29日 (2012.3.29)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                        |

|-----------|----------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サン・ディエゴ モアハウス・ド<br>ライブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                 |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                 |

| (72) 発明者  | シャオピン・グ<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ド<br>ライブ・5775                       |

最終頁に続く

(54) 【発明の名称】内蔵型レベルシフタならびにプログラム可能立上りエッジおよびパルス幅を有するパルスクロック生成論理

## (57) 【特許請求の範囲】

## 【請求項1】

パルスクロックを生成するための方法であって、

読み取り動作または書き込み動作を示す信号に基づき、低電圧ドメインでの未加工クロック

から、プログラム可能立上りエッジ遅延だけ立上りエッジを遅延された出力クロックを選

択的に生成するステップと、

パルスクロック生成回路によって、前記遅延された出力クロックに基づいて、高電圧ド

メイン内の前記パルスクロックを出力するステップであって、前記パルスクロック生成回

路内の内蔵型レベルシフタによって、前記低電圧ドメインから前記高電圧ドメインへの電

圧レベルシフトを与えるステップを含む、ステップを含み、

前記パルスクロックのプログラム可能パルス幅が、前記高電圧ドメイン内の前記パルス

クロック生成回路の出力から、前記低電圧ドメイン内の前記パルスクロック生成回路の入

力へのフィードバック経路に基づき、

前記フィードバック経路が、前記読み取り動作または書き込み動作を示す信号に基づき前記

プログラム可能パルス幅を与えるための選択的パルス幅拡張論理部と、予想されるメモリ

アレイ読み取りアクセス遅延と一致するような読み取り遅延を与えるための読み取り遅延模倣論

理部とを備える、方法。

## 【請求項2】

多周期メモリ読み取りまたは書き込み動作の持続期間全体にわたるように、前記パルスクロ

ックの単一パルスを構成するステップをさらに含む、請求項1に記載の方法。

## 【請求項 3】

前記フィードバック経路を通して前記パルスロック生成回路をリセットするステップをさらに含む、請求項1に記載の方法。

## 【請求項 4】

メモリ書き込み動作用の前記プログラム可能立上りエッジ遅延が前記読み取り遅延よりも大きい、請求項1に記載の方法。

## 【請求項 5】

前記フィードバック経路を通して前記パルスロック生成回路に自己リセットおよび自己タイミング機能性を提供するステップをさらに含む、請求項1に記載の方法。

## 【請求項 6】

メモリ書き込み動作用の前記プログラム可能パルス幅が、メモリ読み取り動作用の前記プログラム可能パルス幅よりも大きくなるようにプログラムされる、請求項1に記載の方法。

10

## 【請求項 7】

未加工クロックに結合された、低電圧ドメイン内の入力と、

パルスロックに接続された、高電圧ドメイン内の出力と、

前記低電圧ドメインから前記高電圧ドメインへの電圧レベルシフトを与えるように構成された内蔵型レベルシフタと、

読み取り動作または書き込み動作を示す信号に基づき、前記パルスロックの立上りエッジを、前記未加工クロックの立上りエッジから、プログラム可能立上りエッジ遅延だけ遅延させるための選択的遅延論理部と、

20

前記高電圧ドメイン内のパルスロック生成回路の前記出力から、前記低電圧ドメイン内の前記パルスロック生成回路の前記入力へのフィードバック経路であって、前記読み取り動作または書き込み動作を示す信号に基づき前記パルスロックのプログラム可能パルス幅を与えるための選択的パルス幅拡張論理部、およびメモリアレイ読み取りアクセス遅延と一致するような読み取り遅延を与えるための読み取り遅延模倣論理部を備えるフィードバック経路とを備えるパルスロック生成回路。

## 【請求項 8】

前記フィードバック経路が、前記パルスロック生成回路に自己リセットおよび自己タイミング機能性を与えるようにさらに構成される、請求項7に記載のパルスロック生成回路。

30

## 【請求項 9】

前記パルスロックを低論理レベルに駆動するように構成された、前記フィードバック経路に接続された入力リセット信号をさらに備える、請求項7に記載のパルスロック生成回路。

## 【請求項 10】

前記パルスロックを安定させるためのラッチをさらに備える、請求項7に記載のパルスロック生成回路。

## 【請求項 11】

前記ラッチによって生じる電荷共有を削減するためのブルアップトランジスタをさらに備える、請求項10に記載のパルスロック生成回路。

40

## 【請求項 12】

前記パルスロックのパルス拳動を有効にするための入力イネーブル信号をさらに備える、請求項7に記載のパルスロック生成回路。

## 【請求項 13】

前記入力イネーブル信号が、メモリアクセス動作の完了期間に対応する複数のクロック周期にわたって、前記パルスロックのパルス拳動を有効にするように構成される、請求項12に記載のパルスロック生成回路。

## 【請求項 14】

請求項1から6のいずれか1項に記載の方法をコンピュータまたはプロセッサに実施させるための少なくとも1つの命令を含む、コンピュータプログラム。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

開示する実施形態は概して、パルスクロック生成に関する。より詳細には、例示的な実施形態は、異なるメモリアクセス動作の様々な要件に合わせて構成されたプログラム可能エッジおよびパルス幅を有するパルスクロックの生成を対象とする。

**【背景技術】****【0002】**

ハンドヘルドデバイスおよびモバイル電話業界においてバッテリ寿命が長く、処理速度が高いことへの要求が高まり、それに相応して低電力であり高性能のメモリシステムの必要が生じている。省電力のために、オンチップのメモリは、低電源電圧レベルに制限される。

10

**【0003】**

ただし、6トランジスタスタティックランダムアクセスメモリ(6T-SRAM)など、従来のメモリセルは、非常に低い電圧では動作することができない。一般的な解決策は、複数の電圧ドメインの使用を伴い、その結果メモリセルは、比較的高電圧レベルで操作することができ、他のオンチップ論理は、より低電圧で操作することができる。複数の電圧ドメインを達成するために、レベルシフタが通常、必要に応じて、低電圧を高電圧に、およびその逆に変換するのに使われる。ただし、レベルシフタは待ち時間をもたらし、これは、タイミング依存経路では望ましくない場合がある。

20

**【0004】**

大規模メモリセルアレイを備えるメモリシステムのケースでは、ローカルに生成された自己タイミング型パルスクロックがしばしば、(たとえば、プロセス変形体による)デバイス変形体の影響を克服するのに利用される。これらのパルスクロックは、異なるメモリアクセス動作についての相反する要求を受け得る。たとえば、メモリ読取り動作中、迅速な読取リアクセスを可能にするために、パルスクロックの立上りエッジが、アクセスされているメモリアレイのメモリセルに可能な限り速く達することが望ましい場合がある。さらに、メモリ読取り動作中、ビット線上での全電圧振幅を認めないことによって、電力消費を削減するために、パルスクロックのパルス幅は狭くなることが望ましい場合がある。

30

**【0005】**

一方、メモリ書き込み動作は通常、タイミング依存ではなく、したがって、パルスクロックの立上りエッジにおけるより高い到着遅延を許容し得る。実際、メモリ書き込み動作は、書き込まれるデータ用に十分なセットアップ時間を可能にするように、パルスクロックにおける遅延の恩恵を受け得る。読取り動作とはさらに対照的に、書き込み動作中、パルスクロックのパルス幅は、特により低い電源電圧レベルでの、書き込み動作の完了成功を保証するために、十分な書き込み時間を可能にするように、より広くなることが望ましい場合がある。従来のパルスクロック実装形態は、メモリセル上での読取りおよび書き込み動作についてのこれらの相反する要求を満たすのに好適ではない。

**【発明の概要】****【発明が解決しようとする課題】**

40

**【0006】**

したがって、レベルシフタおよびパルスクロックに関連した、上述の問題を回避する解決策が、当該分野において必要である。

**【課題を解決するための手段】****【0007】**

本発明の例示的な実施形態は、異なるメモリアクセス動作の様々な要件に合わせて構成されたプログラム可能エッジおよびパルス幅を有するパルスクロックを生成するためのシステムおよび方法を対象とする。

**【0008】**

たとえば、例示的な実施形態は、パルスクロックのプログラム可能立上りエッジ遅延を

50

構成するステップと、パルスクロックのプログラム可能パルス幅を構成するステップと、パルスクロックの電圧レベルをシフトするためのレベルシフタを構成するステップと、プログラムされた立上りエッジ遅延、プログラムされたパルス幅、およびシフトされた電圧レベルに従ってパルスクロックを生成するステップとを含む、パルスクロックを生成するための方法を対象とする。

#### 【0009】

別の例示的な実施形態は、パルスクロックのプログラム可能立上りエッジ遅延を与えるための選択的遅延論理と、パルスクロックのプログラム可能パルス幅を与えるための選択的パルス幅拡張論理と、パルスクロックの電圧レベルをシフトするように構成された内蔵型レベルシフタと、プログラムされた立上りエッジ遅延、プログラムされたパルス幅、およびシフトされた電圧レベルに従ってパルスクロックを生成するように構成された論理とを備えるパルスクロック生成回路を対象とする。

10

#### 【0010】

さらに別の例示的な実施形態は、パルスクロックを生成するためのパルスクロック生成システムを対象とし、パルスクロック生成システムは、パルスクロックのプログラム可能立上りエッジ遅延を与えるための選択的遅延手段と、パルスクロックのプログラム可能パルス幅を与えるための選択的パルス幅拡張手段と、パルスクロックの電圧レベルをシフトするための内蔵型レベルシフト手段と、プログラムされた立上りエッジ遅延、プログラムされたパルス幅、およびシフトされた電圧レベルに従ってパルスクロックを生成するための手段とを備える。

20

#### 【0011】

さらに別の例示的な実施形態は、コードを備える非一時的コンピュータ可読記憶媒体を対象とし、コードは、プロセッサによって実行されると、プロセッサに、パルスクロック生成器をプログラムするための動作を実施させ、非一時的コンピュータ可読記憶媒体は、パルスクロックのプログラム可能立上りエッジ遅延を構成するためのコードと、パルスクロックのプログラム可能パルス幅を構成するためのコードと、パルスクロックの電圧レベルをシフトするためのレベルシフタを構成するためのコードと、プログラムされた立上りエッジ遅延、プログラムされたパルス幅、およびシフトされた電圧レベルに従ってパルスクロックを生成するためのコードとを備える。

#### 【0012】

30

添付の図面は、本発明の実施形態に関する説明において助けとなるように提示されており、本発明の限定ではなく、実施形態の例示のみのために提供されている。

#### 【図面の簡単な説明】

#### 【0013】

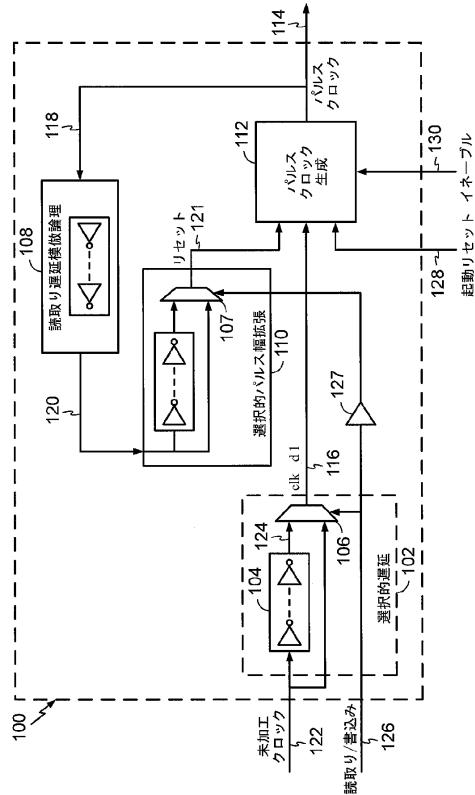

【図1】例示的な実施形態に従って構成された自己タイミング型パルスクロック生成回路100の概略表現を示す図である。

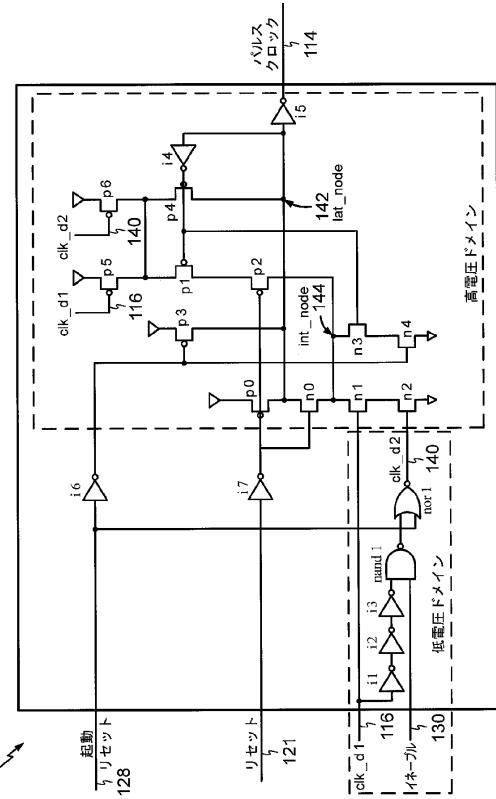

【図2】図1の自己タイミング型パルスクロック生成回路100のパルスクロック生成論理112のトランジスタレベルの概略図である。

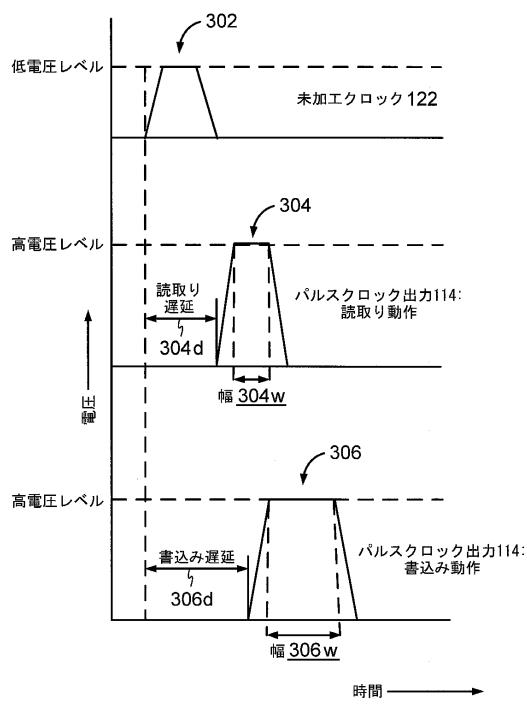

【図3】自己タイミング型パルスクロック生成回路100に関するパルスクロックの表現を含むタイミング図である。

40

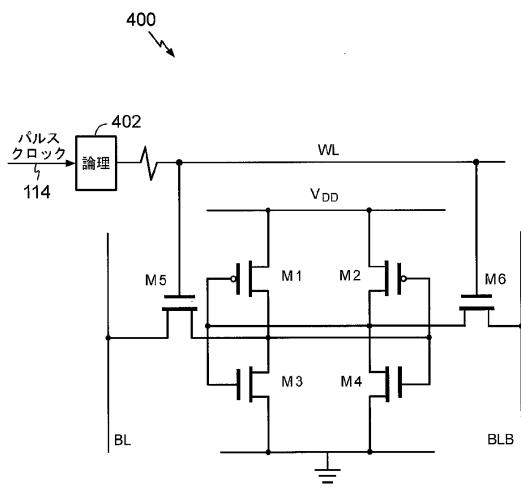

【図4】例示的な実施形態に従って生成されたパルスクロックが適用され得る従来の6T SRAMセル400を示す図である。

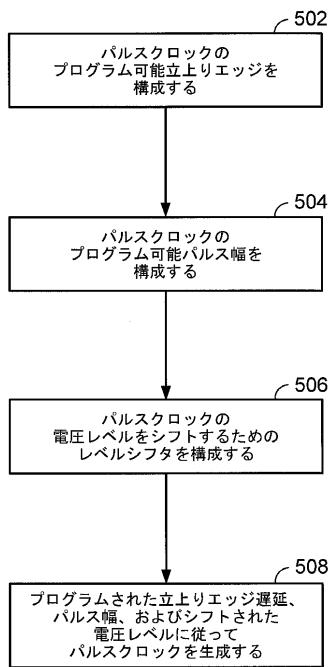

【図5】例示的な実施形態による、パルスクロックを生成する例示的な方法を表すフローチャートである。

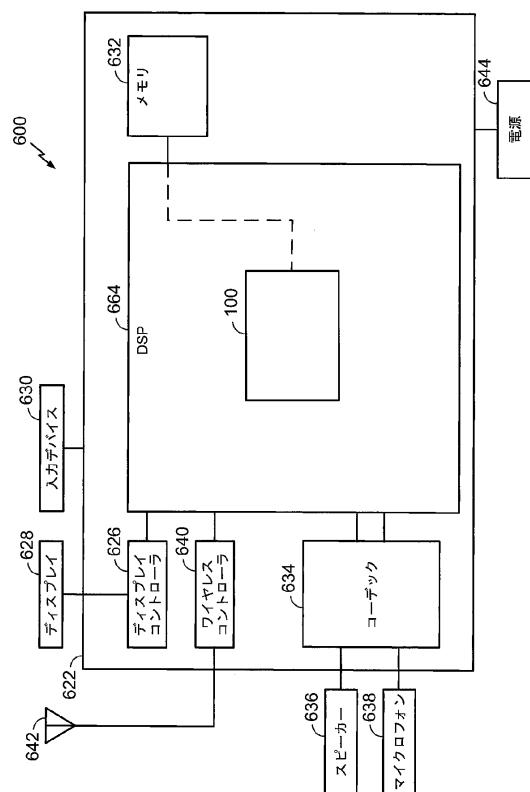

【図6】本開示の一実施形態が有利に採用され得る例示的なワイヤレス通信システム600を示す図である。

#### 【発明を実施するための形態】

#### 【0014】

本発明の特定の実施形態を対象とする以下の説明および関連する図面において、本発明の態様が開示される。本発明の範囲から逸脱することなく、代替の実施形態が考案され得

50

る。加えて、本発明の関連する詳細を不明瞭にしないように、本発明のよく知られている要素は詳細に説明されないか、または省略される。

#### 【 0 0 1 5 】

「例示的」という単語は、本明細書では「例、事例、または例示の働きをすること」を意味するために使用される。「例示的な」として本明細書で説明される任意の実施形態は、必ずしも他の実施形態よりも好ましいか、または有利であると解釈されるべきではない。同様に、「本発明の実施形態」という用語は、本発明のすべての実施形態が、論じられた特徴、利点または動作モードを含むことを必要としない。

#### 【 0 0 1 6 】

本明細書で使用する用語は、特定の実施形態の説明のみを目的とするものであり、本発明の実施形態を限定するものではない。本明細書で使用する単数形「a」、「an」、および「the」は、文脈が別段に明確に示すのでなければ、複数形をも含むものとする。さらに、本明細書で使用されるとき、「備える(comprises)」、「備えている(comprising)」、「含む(includes)」、および/または「含んでいる(including)」という用語は、述べられた特徴、整数、ステップ、動作、要素、および/または構成要素の存在を明示するが、1つまたは複数の他の特徴、整数、ステップ、動作、要素、構成要素、および/またはそれらのグループの存在または追加を排除しないことを理解されよう。

10

#### 【 0 0 1 7 】

さらに、多くの実施形態が、たとえばコンピューティングデバイスの要素によって実施すべき、一連のアクションに関して説明される。本明細書で説明する様々なアクションは、特定の回路(たとえば、特定用途向け集積回路(ASIC))によって、1つまたは複数のプロセッサによって実行されるプログラム命令によって、または両方の組合せによって実施できることを認識されよう。さらに、本明細書で説明するこれらの一連のアクションは、実行時に、関連するプロセッサに本明細書で説明する機能性を実施させるコンピュータ命令の対応するセットを記憶した、任意の形式のコンピュータ可読記憶媒体内で全体として具現化されるものと見なすことができる。したがって、本発明の様々な態様は、特許請求される主題の範囲内にすべて入ることが企図されているいくつかの異なる形式で具現化され得る。加えて、本明細書で説明する実施形態ごとに、そのような任意の実施形態の対応する形式を、たとえば、説明される動作を実施する「ように構成された論理」として本明細書で説明されることがある。

20

#### 【 0 0 1 8 】

例示的な実施形態は、読み取りおよび書き込み動作の相反する要件を満たすためのプログラム可能パルス幅および立上りエッジ遅延のために構成された自己タイミング型パルスクロック生成回路を対象とする。さらに、例示的な実施形態は、別個の電圧レベルシフタからの追加遅延をもたらすことなく、同時に従来の実装形態において起こり得るグリッチおよび電荷共有問題も防止しながら、低電圧ドメイン内の未加工クロックを、高電圧ドメイン内の読み取りおよび書き込み動作用のパルスクロックに変換するように構成された内蔵型レベルシフタを含み得る。

30

#### 【 0 0 1 9 】

ここで図1を参照すると、例示的な実施形態に従って構成された自己タイミング型パルスクロック生成回路100が示されている。未加工クロック122は、自己タイミング型パルスクロック生成回路100に入力することができ、読み取りおよび書き込み動作のための、カスタマイズされたクロックパルスを生成するためのベースクロックとして働き得る。未加工クロック122は、知られている技術によって、圧電性結晶などの使用によって生成することができる。未加工クロック122は、低電圧レベルで使用可能にすることことができ、または低電圧ドメインから導出することができる。

40

#### 【 0 0 2 0 】

未加工クロック122は最初に、選択的遅延論理102に入ればよく、ここで未加工クロック122は、書き込み動作のために選択的に遅延させられ得る。プログラム可能遅延論理104、読み取り/書き込み制御126およびセレクタ106は、未加工クロック122を選択的に遅延させるため

50

に、図に示すように構成することができる。一例では、読み取り/書き込み制御126によって読み取り動作が指示される場合、未加工クロック122は、セレクタ106によって、選択的に遅延された出力クロックclk\_d1 116を形成するように選択され得る。一方、読み取り/書き込み制御126が書き込み動作を指示する場合、プログラム可能遅延論理104は、未加工クロック122を所望の量だけ遅延させ、遅延されたクロック124を生成すればよく、クロック124は次いで、セレクタ106によって、選択的に遅延された出力クロックclk\_d1 116を形成するように選択され得る。プログラム可能遅延論理104は、知られている技術によって、直列に結合されるべきいくつかのインバータまたはバッファ要素を制御することなどによって実装することができる。これらのインバータまたはバッファ要素の有効サイズは、遅延量を調整するように制御されてもよい。当業者は、プログラム可能遅延論理104に対する好適な実装態様を認識するであろう。

10

#### 【0021】

選択的に遅延された出力クロック、したがってこのように生成されたclk\_d1 116は次いで、パルスクロック生成論理112に入ればよい。パルスクロック生成論理112は最終的には、例示的な実施形態における読み取りおよび書き込み動作についての上記要件を満たすパルスクロック114を出力することができる。パルスクロック生成論理112は、個々の電圧レベルシフタからの望まれない待ち時間をもたらすことなく、高電圧レベルにおいて出力パルスクロック114が使用可能にされるような、電圧レベルシフトのための論理を含み得る。さらに、パルスクロック生成論理112は、出力パルスクロック114におけるグリッチをなくすように構成され得る。出力パルスクロック114からリセット121を通してパルスクロック生成論理112に戻るフィードバック経路118は、図に示すように、読み取り遅延模倣論理108および選択的パルス幅拡張論理110を含み得る。フィードバック経路118は、パルスクロック生成論理112に、自己リセットを、およびしたがって自己タイミング機能性を与えることができる。パルスクロック生成論理112、読み取り遅延模倣論理108、および選択的パルス幅拡張論理110について、次にさらに詳しく説明する。

20

#### 【0022】

ここで図2を参照すると、トランジスタレベルの概略を含む、パルスクロック生成論理112の拡大図が与えられている。イネーブル130および起動リセット128が、出力パルスクロック114を有効にし、またはリセットするために、外部ソース(図示せず)からクロック生成論理112に入力される。パルスクロック生成論理112の例示的な動作について、ここで説明する。最初に、起動リセット128がハイに駆動され、したがってインバータi6の出力をローに駆動させ、プルアップトランジスタp3を、lat\_node142をプルアップするようにトリガし、そうすることによって、インバータi5を介して出力パルスクロック114をローに駆動する。図2に示すように、プルアップトランジスタp3は高電圧ドメイン内にあることが観察されよう。したがって、出力パルスクロック114は、高電圧ドメイン内で導出される。

30

#### 【0023】

その後、起動リセット128はローに駆動され、イネーブル130はハイに駆動される。選択的に遅延された出力クロック、すなわちclk\_d1 116は、インバータi1、i2、およびi3を横断し、したがってi3の出力は、clk\_d1に続く、反転および遅延されたパルスを提示する。i3の出力も立ち上がった時点で、nand1への両方の入力、すなわちi3およびイネーブル130の出力はハイであり、したがってnand1の出力をローにさせる。これは、nor1の両方の入力、すなわちnand1および起動リセット128の出力がローであり、したがって、ノードclk\_d2 140がハイに駆動され、そうすることによってプルダウントランジスタn2をオンにすることを意味する。さらに、インバータi6の出力がハイに駆動されることになるので、プルダウントランジスタn4は、ここでオンにされる。

40

#### 【0024】

未加工クロック122の立上りエッジの第1の事例について、ここで検討する。選択的に遅延された出力クロックclk\_d1 116は、未加工クロック122の、選択的に遅延されたバージョンであることが思い起こされよう。未加工クロック122および選択的に遅延された出力

50

クロックclk\_d1\_116は両方とも、低電圧ドメイン内にあり得る。したがって、未加工クロック122の立上りエッジは、遅延の後、選択的に遅延された出力クロックclk\_d1\_116の立上りエッジを引き起こし、次いで、プルダウントランジスタn1をオンにし得る。この時間インスタンスにおいて、プルダウントランジスタn3は、オフにされたままになろう。選択的に遅延された出力クロックclk\_d1\_116は、プルアップトランジスタp5のゲートに結合され、ノードclk\_d2\_140は、トランジスタp6のゲートに結合されることに、図2から気づかれよう。したがって、プルアップトランジスタp5およびp6のソース電圧が高電圧ドメイン内にあり、それらのゲート電圧が低電圧ドメイン内にあるので、プルアップトランジスタp5およびp6は、部分的にオフにされ、すべての4つのプルダウントランジスタn0、n1、n2、およびn4が、この事例においてオンにされる。したがって、両方のノードint\_node144およびlat\_node142がプルダウンされ、インバータi5は、出力パルスクロック114をハイに駆動する。lat\_node142がプルダウンされている時間中、プルダウントランジスタn3がオンにされ、これにより、追加電流源が与えられて、lat\_node142およびint\_node144のプルダウンプロセスの速度が増す。出力パルスクロック114はすでに高電圧ドメイン内にあることが思い起こされよう。したがって、低電圧ドメイン内の未加工クロック122の立上りエッジは、追加電圧レベルシフト論理を必要とすることなく、高電圧ドメイン内の出力パルスクロック114の立上りエッジを生じる。途中でオフにされるプルアップトランジスタp5およびp6が軽度の遅延および電力消費コストを招き得るが、これらのコストは、プルダウントランジスタn3およびn4によって提供される追加プルダウン経路によって相殺することができる。

10

#### 【0025】

ここで、リセット機構がlat\_node142を高状態に戻し、したがって出力パルスクロック114をローに駆動するまで、インバータi4およびプルアップトランジスタp4、p6とプルダウントランジスタn3、n4の組合せによって作成されるラッチにより、lat\_node142は低状態に留まり、パルスクロック114は高状態に留まる。リセット121は、後でさらに詳しく説明するが、出力パルスクロック114の立下りエッジを制御することができる。出力パルスクロック114の立上りエッジと出力パルスクロック114の立下りエッジとの間の期間を制御することにより、出力パルスクロック114において導出されるクロックパルスの幅が決まることが認識されよう。

20

#### 【0026】

ここで図1に戻ると、選択的パルス幅拡張論理110が、出力パルスクロック114の立上りエッジと立下りエッジとの間のパルス幅を選択的に広げるのに採用され得る。選択的遅延論理102と同様、選択的パルス幅拡張論理110は、マルチブレクサ107を採用して、読み取り/書き込み制御126に基づいて、追加遅延のない入力信号と、入力信号の遅延されたバージョンのどちらかを選ぶことができる。読み取り/書き込み制御126のタイミングは、前述した選択的遅延プロック102を通過した後、選択的パルス幅拡張プロック110に達する際の遅延を考慮し、バッファ127によって適切に調整することができる。したがって、動作が読み取りであるか、それとも書き込みであるかに依存して、選択的パルス幅拡張論理を通る遅延経路は、書き込み動作用のパルス幅がより広くされるように制御することができる。言い換えると、読み取り遅延模倣論理108(後でさらに詳しく論じる)の出力120は、選択的パルス幅拡張論理110の出力、リセット121の幅を変化させるように選択的に遅延させることができる。これは、リセット121が、低レベルから高レベルに立ち上がり、次いで、低レベルにフォールバックするのにかかる時間を制御する。

30

#### 【0027】

リセット121が立ち下がると、上記プロセスを繰り返すことによって、出力パルスクロック114の次の立上りエッジが生成され得る。次の立下りエッジは、読み取り遅延模倣論理108によって、読み取り動作のために適切に遅延させることができる。言い換えると、読み取り遅延模倣論理108は、最終的には出力パルスクロック114の立下りエッジを遅延させるように構成され、したがってパルス幅を制御する。思い起こされるように、出力パルスクロック114の立上りエッジは、選択的遅延論理102によって制御される。

40

50

## 【0028】

ここで図1と図2を組み合わせて参照し、出力パルスクロック114からリセット121へのフィードバック経路118について、ここで説明する。図1に示すように、この経路は、読み取り遅延模倣論理108および選択的パルス幅拡張論理110を備える。

## 【0029】

読み取り遅延模倣論理108は、読み取り動作中に遭遇したメモリアレイアクセス遅延を考慮するために、出力パルスクロック114の立上りエッジから、出力パルスクロック114の立下りエッジにおける遅延を制御するために含まれ得る。たとえば、読み取り遅延模倣論理108は、メモリアレイ中のメモリセルにアクセスする際に招かれ得る遅延に対応する遅延を与えるように構成されてよい。読み取り遅延模倣論理は、予想される読み取りアクセス遅延と一致するようなプログラム可能遅延要素を備え得る。したがって、出力パルスクロック114の立上りエッジは、読み取り遅延模倣論理108によって、出力120の立上りエッジを形成するように遅延される。読み取り動作のケースでは、選択的パルス幅拡張論理110は、いかなる遅延も追加されることなく、入力を選択し、出力120の立上りエッジは本質的に、リセット121の立上りエッジとして見え、リセット121は、パルスクロック生成論理112中のインバータi7によって反転される。ここで図2を特に参照すると、プルアップトランジスタp0およびプルダウントランジスタn0によって形成されたインバータは、lat\_node142を高状態にリセットすることになる。言い換えると、図1の読み取り模倣遅延論理108を含むフィードバックループにより、本質的に、出力パルスクロック114の立下りエッジは、読み取り動作の場合、高電圧ドメイン内で、遅延時間に確実に使用可能になる。

## 【0030】

再度、リセットから出た後の未加工クロック122の立上りエッジの第1の事例に移ると、選択的に遅延された出力クロックclk\_d1 116の立上りエッジがインバータi1、i2、i3、ならびにnand1およびnor1を横断した後、ノードclk\_d2 140が立ち下がることになる。これにより、プルダウントランジスタn2がオフにされ、プルアップトランジスタp6もオンにされる。これにより、lat\_node142を立ち上がらせ、したがって出力パルスクロック114の立下りエッジを生じさせる。この時点で、プルダウントランジスタn1は、lat\_node142のラッチ機能に影響することなく、オンまたはオフにされる。選択的に遅延された出力クロックclk\_d1 116の立下りエッジが(未加工クロック122の立下りエッジから選択的に遅延された後)成功すると、プルダウントランジスタn1もオフにされ、プルアップトランジスタp5はオンにされることになる。プルダウントランジスタn1およびn2両方をオフにすると、プルダウントランジスタn1およびn2を備える経路を通る漏れ電力がさらに削減される。書き込み動作のケースでは、選択的パルス幅拡張論理110が、リセット121がアサートされ得る前に、フィードバック経路中の追加遅延を選択的にもたらし、したがって、lat\_node142を立ち上がらせ、出力パルスクロック114の立下りエッジを生じさせる。このように、書き込み動作は、より広いパルス幅を有することになる。前述したように、より広いパルス幅は、書き込み動作(思い起こされるように、通常タイミング依存ではない)の完了のための追加時間を与えることによって、書き込み動作を容易にすることができる。

## 【0031】

プルダウントランジスタn1およびn2両方をオンにすることは、自己タイミング型プロセスであることが理解されよう。プルダウントランジスタn1およびn2がオンにされる期間は、インバータi1、i2、i3、ならびにゲートnand1およびnor1を通る遅延で決まり得る。概して、プルダウントランジスタn1およびn2は、リセット121がアサート解除される前にオフにされることになる。したがって、読み取り/書き込み動作が、動作の完了に複数の周期を必要とする場合、動作全体の間にイネーブル130の単一パルスが与えられればよく、したがって、出力パルスクロック114の単一パルスのみが、動作全体の持続期間だけ、確実に生成されるようになる。

## 【0032】

したがって、出力パルスクロック114の立上りエッジは、未加工クロック122から、読み取り動作および書き込み動作のために制御可能な量だけ、遅延され得ることがわかる。インバ

10

20

30

40

50

ータi4と、プルアップトランジスタp4、p6およびプルダウントランジスタn3、n4の組合せとを含むラッチ機構i4は、信号リセット121をアサートすることによって、読み取りおよび書き込み動作のための制御可能期間の後、立下りエッジが課されるまで、出力パルスクロック114を高状態に保つ。

【0033】

ここで、パルスクロック生成論理112は、グリッチと、たとえば、lat\_node142とint\_node144の間で起こり得る望ましくない電荷共有とを回避するようにも構成されることに留意されたい。リセット121が、高状態と低状態との間で変化するとき、lat\_node142は、ラッチ機構により、高状態に留まり得るが、int\_node144は、低状態に立ち下がり、したがって、プルダウントランジスタn0のドレインノードとソースノードとの間の大きい電圧差を起こし得ることが認識されよう。これは、望まれない電荷共有問題につながり得る。そのような問題が起こるのを防ぐために、int\_node144は、プルアップトランジスタp5、p6、p1およびp2を使って、高状態にプルアップされてよい。したがって、lat\_node142およびint\_node144は両方とも高状態になり、大きい差動電圧は、プルダウントランジスタn0にそれ以上影響しない。

【0034】

ここで図3を参照すると、上述したような読み取りおよび書き込み動作のための未加工クロック122および出力パルスクロック114の例示的な概略表現を含むタイミング図が示されている。図に示すように、水平軸は時間を含み、垂直軸は電圧レベルを含む。タイミング図302は、低電圧レベルでの未加工クロック122を示す。タイミング図304に示すように、読み取り動作に生成された出力パルスクロック114は、高電圧レベルにあり、立上りエッジ遅延304dを含み、タイミング図306に示すように、書き込み動作に生成された出力パルスクロック114は、高電圧レベルにあり、立上りエッジ遅延306dを含む。予想される読み取りアレイ遅延が(たとえば、図1の読み取り遅延模倣論理108を通して)なくされた後、立上りエッジ遅延304dは、高速読み取り動作の必要性を満たすのに必要とされる限り速くされ得る。それと比較して、立上りエッジ遅延306dは、速くなる必要はなくてよく、したがって、必要に応じて減速されてよい。さらに、タイミング図304と比較して、タイミング図306は、書き込み動作が、上述したように、書き込み動作のより広いパルス幅要件を満足するために、読み取り動作のためのパルス幅304wよりも広くなるためのパルス幅306wを示す。

【0035】

ここで図4を参照すると、例示的な実施形態に従って生成された出力パルスクロック114が適用され得る従来の6T SRAMセル400が示されている。図に示すように、出力パルスクロック114は、概して図4における論理402で指定される、ワード線デコーダなど、当該分野においてよく知られている論理構成要素によって使われる。6T SRAMセル400の動作は、よく知られている。トランジスタM1、M2、M3、およびM4は、交差結合インバータ記憶要素を形成し、アクセストランジスタM5およびM6は、記憶要素のための読み取り/書き込み動作を制御する。ワード線WLは、アクセストランジスタM5およびM6のゲートを制御し、補足ビット線BLおよびBLBは、書き込み動作の特定の6T SRAMセル400を選択するのに、および読み取り動作のために記憶された値を読み出すのに使われる。図に示すように、出力パルスクロック114は、たとえば、図3に示すように、読み取りおよび書き込み動作のための特定のパルスクロック要件を満たすために、ワード線WLに適用され得る。

【0036】

例示的な実施形態における書き込み動作に関して、選択的遅延論理102によってもたらされる遅延は、書き込み動作中に出力パルスクロック114の立上りエッジを遅延させることができ、これにより、ビット線BLおよびBLBに対する追加セットアップ時間が再度可能になり、付随するバッファおよびドライバが小型化され得るので、さらに電力を削減し得ることがわかるであろう。さらに、選択的パルス幅拡張論理110によって作成されるより広いパルス幅により、より低電圧レベルであっても書き込み動作を容易にすることことができ、このことが、成果の向上につながり得る。

【0037】

10

20

30

40

50

さらに、パルスクロック生成論理112に電圧レベルシフト機構を統合すると、パルスクロック生成論理から分離されたレベルシフタを有する従来の実装形態と比較して、より低い待ち時間、および機能ブロックの再利用の向上につながり得る。プルダウントランジスタn3およびn4を経由する内蔵型レベルシフタへのフィードバック経路は、未加工クロック122の低電圧レベルと出力パルスクロック114の高電圧レベルとの間の電圧差が大きいときに、出力パルスクロック114の立ち上りエッジの速度を増すことができる。パルスクロック生成論理112中のラッチ機構は、出力パルスクロック114の論理状態を安定させたままにしておくことをさらに容易にすることができます。

#### 【0038】

実施形態は、本明細書で開示されるプロセス、機能および/またはアルゴリズムを実施するための、様々な方法を含むことが諒解されよう。たとえば、図5に示すように、ある実施形態は、パルスクロックのプログラム可能立上りエッジ遅延(たとえば、図3のタイミング図304および306に示したような立上りエッジ遅延304dおよび306d)を構成するステップ、すなわちブロック502と、パルスクロックのプログラム可能パルス幅(たとえば、図3のタイミング図304および306に示したような幅304wおよび306w)を構成するステップ、すなわちブロック504と、パルスクロックの電圧レベルをシフトするためのレベルシフタ(たとえば、図1～図2のパルスクロック生成論理112内の内蔵型レベルシフタ)を構成するステップ、すなわちブロック506と、プログラムされた立上りエッジ遅延、パルス幅、およびシフトされた電圧レベルに従ってパルスクロックを生成するステップ、すなわちブロック508とを含む、パルスクロック(たとえば、図1の出力パルスクロック114)を生成するための方法を含み得る。

#### 【0039】

情報および信号が多種多様な異なる技術および技法のいずれかを使用して表すことができることを、当業者は諒解されよう。たとえば、上記の説明全体にわたって言及され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁界もしくは磁性粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表され得る。

#### 【0040】

さらに、本明細書で開示された実施形態に関連して説明された様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムステップは、電子ハードウェア、コンピュータソフトウェア、または両方の組合せとして実装され得ることを、当業者は諒解されよう。ハードウェアとソフトウェアのこの互換性を明確に示すために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップを、上記では概してそれらの機能性に関して説明した。そのような機能性をハードウェアとして実装するか、ソフトウェアとして実装するかは、特定の適用例および全体的なシステムに課される設計制約に依存する。当業者は、説明した機能性を特定の適用例ごとに様々な方法で実装し得るが、そのような実装の決定は、本発明の範囲からの逸脱を生じるものと解釈すべきではない。

#### 【0041】

本明細書で開示された実施形態に関連して記載された方法、シーケンス、および/またはアルゴリズムは、ハードウェアで、プロセッサによって実行されるソフトウェアモジュールで、またはその2つの組合せで直接具現化することができる。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られている任意の他の形態の記憶媒体中に常駐し得る。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、かつ記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替として、記憶媒体はプロセッサと一体であり得る。

#### 【0042】

図6を参照すると、例示的な実施形態に従って構成されたマルチコアプロセッサを含むワイヤレスデバイスの特定の例示的な実施形態のブロック図が示され、全体的に600と表される。デバイス600は、図1の自己タイミング型パルスクロック生成回路100を含み得る

10

20

30

40

50

デジタル信号プロセッサ(DSP)664を含む。DSP664は、図に示すようにメモリ632に結合されてよく、自己タイミング型パルスクロック生成回路100からの生成されたパルスクロックは、メモリ632におけるメモリアクセスに使うことができる。たとえば、図6は、DSP664とディスプレイ628とに結合されたディスプレイコントローラ626のような外部デバイスも示している。コーダ/デコーダ(コーデック)634(たとえば、オーディオおよび/またはボイスコーデック)のような外部デバイスも、DSP664に結合され得る。(モデムを含み得る)ワイヤレスコントローラ640などの他の構成要素/外部デバイスも示されている。スピーカー636およびマイクロフォン638が、コーデック634に結合され得る。図6は、ワイヤレスコントローラ640が、ワイヤレスアンテナ642に結合され得ることも示している。ある特定の実施形態では、DSP664、ディスプレイコントローラ626、メモリ632、コーデック634、およびワイヤレスコントローラ640は、システムインパッケージデバイスまたはシステムオンチップデバイス622に含まれる。

#### 【0043】

ある特定の実施形態では、入力デバイス630および電源644が、システムオンチップデバイス622に結合される。さらに、ある特定の実施形態では、図6に示すように、ディスプレイ628、入力デバイス630、スピーカー636、マイクロフォン638、ワイヤレスアンテナ642、および電源644は、システムオンチップデバイス622の外部にある。ただし、ディスプレイ628、入力デバイス630、スピーカー636、マイクロフォン638、ワイヤレスアンテナ642、および電源644の各々は、インターフェースまたはコントローラのような、システムオンチップデバイス622の構成要素に結合され得る。

#### 【0044】

図6はワイヤレス通信デバイスを示しているが、DSP664およびメモリ632がセットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、携帯情報端末(PDA)、固定ロケーションデータユニット、またはコンピュータに統合されてもよいことに留意されたい。プロセッサ(たとえば、DSP664)がそのようなデバイスに統合されてもよい。

#### 【0045】

したがって、本発明の実施形態は、内蔵型レベルシフタならびにプログラム可能立上りエッジおよびプログラム可能パルス幅をもつパルスクロックを生成するための方法を具現化するコンピュータ可読媒体を含み得る。したがって、本発明は、示された例に限定されず、本明細書に説明された機能性を実施するための任意の手段は、本発明の実施形態に含まれる。

#### 【0046】

上記の開示は本発明の例示的な実施形態を示すが、添付の特許請求の範囲によって規定される本発明の範囲から逸脱することなく、本明細書において様々な変更および修正が行われ得ることに留意されたい。本明細書で説明した本発明の実施形態による方法クレームの機能、ステップおよび/またはアクションは、特定の順序で実施されなくてもよい。さらに、本発明の要素は、単数形で説明または特許請求されていることがあるが、単数形に限定することが明示的に述べられていない限り、複数形が企図される。

#### 【符号の説明】

#### 【0047】

- 100 自己タイミング型パルスクロック生成回路

- 102 選択的遅延論理

- 104 プログラム可能遅延論理

- 106 セレクタ

- 107 マルチプレクサ

- 108 讀取り遅延模倣論理

- 110 選択的パルス幅拡張論理

- 112 パルスクロック生成論理

- 114 パルスクロック

10

20

30

40

50

|     |                               |    |

|-----|-------------------------------|----|

| 116 | 出力クロック                        |    |

| 118 | フィードバック経路                     |    |

| 120 | 出力                            |    |

| 121 | リセット                          |    |

| 122 | 未加工クロック                       |    |

| 124 | 遅延されたクロック                     |    |

| 126 | 読み取り/書き込み制御                   |    |

| 127 | パッファ                          |    |

| 128 | 起動リセット                        |    |

| 130 | イネーブル                         | 10 |

| 140 | ノード                           |    |

| 142 | ノード                           |    |

| 144 | ノード                           |    |

| 600 | ワイヤレス通信システム、デバイス              |    |

| 622 | システムインパッケージデバイス、システムオンチップデバイス |    |

| 626 | ディスプレイコントローラ                  |    |

| 628 | ディスプレイ                        |    |

| 630 | 入力デバイス                        |    |

| 632 | メモリ                           |    |

| 634 | コーダ/デコーダ(コーデック)               | 20 |

| 636 | スピーカー                         |    |

| 638 | マイクロフォン                       |    |

| 640 | ワイヤレスコントローラ                   |    |

| 642 | ワイヤレスアンテナ                     |    |

| 644 | 電源                            |    |

| 664 | デジタル信号プロセッサ(DSP)              |    |

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6】

---

フロントページの続き

(72)発明者 チアミン・チャイ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 スティーブン・エドワード・ライルズ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 ラム・ヴィ・ヌウェン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 ジェフリー・ハーバート・フィッシャー

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 酒井 恭信

(56)参考文献 国際公開第2005/018091(WO, A1)

米国特許出願公開第2006/0097768(US, A1)

米国特許第06850460(US, B1)

特開2003-030991(JP, A)

特開2000-188528(JP, A)

国際公開第2010/077776(WO, A1)

(58)調査した分野(Int.Cl., DB名)

G11C 11/4076

H03K 3/017

G06F 12/00

G06F 1/06