# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2017/0243901 A1 HU

Aug. 24, 2017 (43) Pub. Date:

### (54) THIN FILM TRANSISTOR ARRAY SUBSTRATE, METHOD FOR MANUFACTURING THE SAME, AND DISPLAY DEVICE

(71) Applicant: BOE TECHNOLOGY GROUP CO.,

LTD., Beijing (CN)

(72) Inventor: **Hehe HU**, Beijing (CN)

Assignee: BOE TECHNOLOGY GROUP CO.,

LTD., Beijing (CN)

(21) Appl. No.: 15/322,460

(22) PCT Filed: Nov. 5, 2015

(86) PCT No.: PCT/CN2015/093818

§ 371 (c)(1),

(2) Date: Dec. 28, 2016

#### (30)Foreign Application Priority Data

Nov. 13, 2014 (CN) ...... 201410641424.6

### **Publication Classification**

(51) Int. Cl. H01L 27/12 (2006.01)H01L 21/3213 (2006.01)H01L 29/423 (2006.01)H01L 21/027 (2006.01)

(52)U.S. Cl.

CPC ...... H01L 27/1288 (2013.01); H01L 21/0274 (2013.01); H01L 21/32133 (2013.01); H01L 21/32139 (2013.01); H01L 29/42356 (2013.01); H01L 27/124 (2013.01)

### (57)ABSTRACT

The present disclosure provides a thin film transistor array substrate, a method for manufacturing the same and a display device. The method includes forming, on a substrate, a gate electrode, a common electrode, a gate insulation layer, an active layer and a source-drain metal layer, and forming, on the resultant substrate, a pixel electrode and a passivation layer by one patterning process.

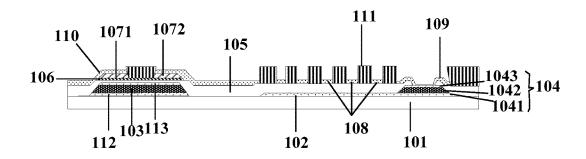

FIG. 1-1

FIG. 1-2

FIG. 1-3

FIG. 1-4

FIG. 1-5

102 103 —— 104 —— 101

FIG. 1-7

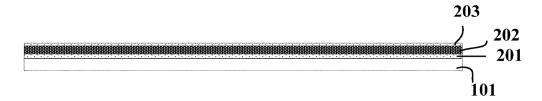

FIG. 2-1

FIG. 2-2

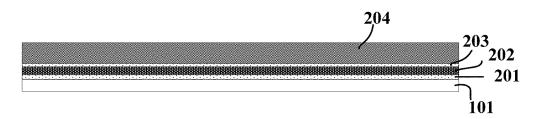

FIG. 2-3

FIG. 2-4

FIG. 2-5

FIG. 2-6

FIG. 2-7

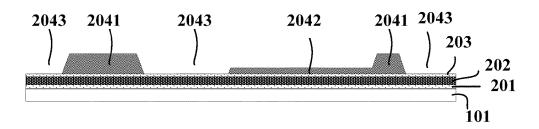

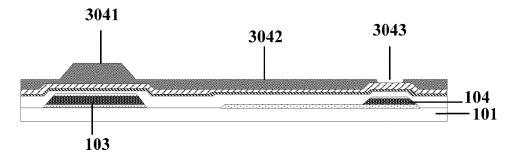

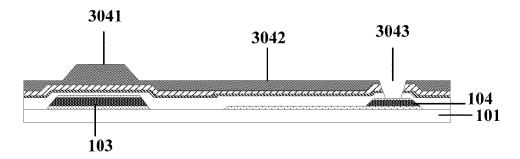

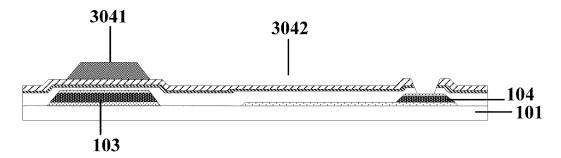

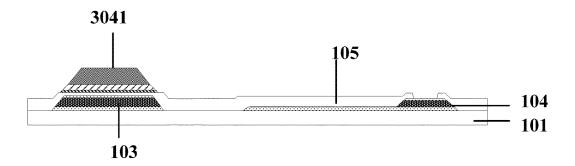

FIG. 3-1

FIG. 3-2

FIG. 3-3

FIG. 3-4

FIG. 3-5

FIG. 3-6

FIG. 3-7

FIG. 4

## THIN FILM TRANSISTOR ARRAY SUBSTRATE, METHOD FOR MANUFACTURING THE SAME, AND DISPLAY DEVICE

# CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application claims a priority to Chinese Patent Application No. 201410641424.6 filed on Nov. 13, 2014, the disclosures of which are incorporated in their entirety by reference herein.

### TECHNICAL FIELD

[0002] The present disclosure relates to the field of displaying technology, and in particular to a thin film transistor (TFT) array substrate and a method for manufacturing the same, and a display device.

### BACKGROUND

[0003] In order to achieve a high pixel per inch (PPI) and a high production capacity, it is necessary to reduce sizes of TFTs and reduce the number of masks used in the process of manufacturing the TFTs. At present, the process of manufacturing a TFT array substrate includes processes of using 7 masks, 6 masks, 5 masks and 4 masks. It may be understood that, the fewer the masks used in the manufacturing process of the TFT array substrate, the lower the cost thereof will be.

### **SUMMARY**

[0004] In view of this, the present disclosure provides a thin film transistor array substrate, a method for manufacturing the same and a display device, so as to reduce the number of the masks used in the process of manufacturing the TFT array substrate.

[0005] To achieve the object hereinabove, a method for manufacturing the TFT array substrate includes: forming, on a substrate, a gate electrode, a common electrode, a gate insulation layer, an active layer and a source and drain metal layer; and forming, on the resultant substrate, a pixel electrode and a passivation layer by one patterning process.

[0006] Optionally, the forming, on the resultant substrate, the pixel electrode and the passivation layer by one patterning process includes:

[0007] forming a third transparent conductive thin film; [0008] coating photoresist onto the third transparent conductive thin film;

[0009] exposing and developing the photoresist by a common mask plate, so as to form a photoresist fully-reserved region and a photoresist fully-unreserved region, where the photoresist fully-reserved region includes a region corresponding to the pixel electrode, a common electrode line and source and drain electrodes, and the photoresist fully-unreserved region includes a region corresponding to a channel between the source and the drain electrodes and the passivation layer;

[0010] etching the third transparent conductive thin film at the photoresist fully-unreserved region, so as to form the pixel electrode, the common electrode line and a source electrode protective portion, where the source electrode protective portion covers the source electrode, and the pixel electrode covers the drain electrode;

[0011] etching the source and drain metal layer at the photoresist fully-unreserved region, so as to form the source and the drain electrodes, where the pixel electrode is overlapped with and jointed to the drain electrode;

[0012] forming a passivation layer thin film; and

[0013] peeling off the photoresist at the photoresist fully-reserved region, so as to form the passivation layer.

[0014] Optionally, the forming on the substrate, the gate electrode, the common electrode, the gate insulation layer, the active layer and the source and drain metal layer includes: forming, on the substrate, the gate electrode, the common electrode, and a common electrode line connection portion by one patterning process.

[0015] Optionally, the forming, on the substrate, the gate electrode, the common electrode, and the common electrode line connection portion by one patterning process includes: [0016] forming, on the substrate, a first transparent conductive thin film, a gate metal thin film and a second transparent conductive thin film in sequence;

[0017] coating photoresist onto the second transparent conductive thin film;

[0018] exposing and developing the photoresist with a grey tone mask plate or a halftone mask plate, so as to form a photoresist fully-reserved region, a photoresist partially-reserved region and a photoresist fully-unreserved region, where the photoresist fully-reserved region includes a region corresponding to the gate electrode and the common electrode line connection portion, the photoresist partially-reserved region includes a region corresponding to the common electrode, and the photoresist fully-unreserved region includes a region other than the photoresist fully-reserved region and the photoresist partially-reserved region;

[0019] removing the first transparent conductive thin film, the gate metal thin film and the second transparent conductive thin film at the photoresist fully-unreserved region by an etching process;

[0020] removing the photoresist at the photoresist partially-reserved region by an ashing process;

[0021] removing the gate metal thin film and the second transparent conductive thin film at the photoresist partially-reserved region by an etching process, so as to form the common electrode; and

[0022] peeling off the photoresist at the photoresist fullyreserved region, so as to expose the gate electrode and the common electrode line connection portion.

[0023] Optionally, the forming on the substrate, the gate electrode, the common electrode, the gate insulation layer, the active layer and the source and drain metal layer further includes: forming the gate insulation layer, the active layer and the source and drain metal layer by one patterning process.

[0024] Optionally, the forming the gate insulation layer, the active layer and the source and drain metal layer by one patterning process includes:

[0025] forming a gate insulation thin film, an active layer thin film and a source and drain metal thin film in sequence; [0026] coating photoresist onto the source and drain metal thin film;

[0027] exposing and developing the photoresist with a grey tone mask plate or a halftone mask plate, so as to form a photoresist fully-reserved region, a photoresist partially-reserved region and a photoresist fully-unreserved region, where the photoresist fully-reserved region includes a region corresponding to the active layer, the photoresist fully-

unreserved region includes a region corresponding to the common electrode line connection portion, and the photoresist partially-reserved region includes a region other than the photoresist fully-reserved region and the photoresist fully-unreserved region;

[0028] removing the gate insulation thin film, the active layer thin film and the source and drain metal thin film at the photoresist fully-unreserved region by an etching process;

[0029] removing the photoresist at the photoresist partially-reserved region by an ashing process;

[0030] removing the source and drain metal thin film and the active layer thin film at the photoresist partially-reserved region by an etching process, so as to form the gate insulation layer; and

[0031] peeling off the photoresist at the photoresist fullyreserved region, so as to expose the source and drain metal layer and the active layer.

[0032] A thin film transistor (TFT) array substrate is further provided, including: a substrate, and a gate electrode, a common electrode, a gate insulation layer, an active layer, a source electrode and a drain electrode arranged on the substrate; a pixel electrode, arranged on the gate insulation layer and overlapped with and jointed to the drain electrode; and a passivation layer, arranged on the gate insulation layer and a channel between the source and the drain electrode.

[0033] Optionally, the TFT array substrate further includes: a common electrode line, arranged at a layer and made of a material identical to the pixel electrode.

[0034] Optionally, the gate electrode and the common electrode are arranged on the substrate, and the TFT array substrate further includes:

[0035] a transparent conductive thin film protective portion, arranged between the gate electrode and the substrate and arranged at a layer and made of a material identical to the common electrode;

[0036] a common electrode line connection portion, arranged on the common electrode and including a first transparent conductive layer and a gate metal layer, where the common electrode is connected to the corresponding common electrode line via the common electrode line connection portion.

[0037] Optionally, the TFT array substrate further includes: a gate electrode protective layer, arranged between the gate electrode and the gate insulation layer, where the common electrode line connection portion further includes a second transparent conductive layer arranged at a layer and made of a material identical to the gate electrode protective layer.

[0038] Optionally, the TFT array substrate further includes: a source electrode protective portion arrange on the source electrode and arranged at a layer and made of a material identical to the pixel electrode.

[0039] According to the present disclosure, the pixel electrode and the passivation layer may be formed by one patterning process, thereby reducing the number of the masks used in the process of manufacturing the TFT array substrate and reducing the production cost.

### BRIEF DESCRIPTION OF THE DRAWINGS

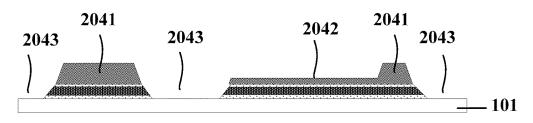

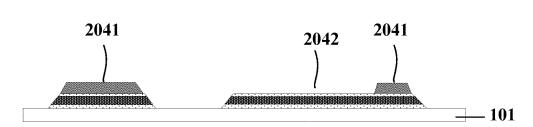

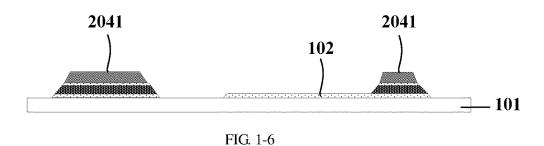

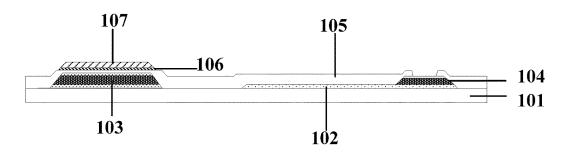

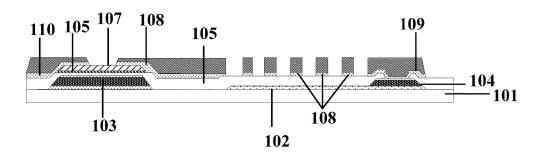

[0040] FIGS. 1-1 to 1-7 show a process of forming a gate electrode, a common electrode and a common electrode line connection portion on a substrate by one patterning process in some embodiments of the present disclosure;

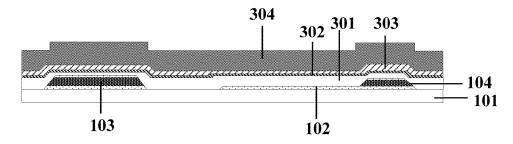

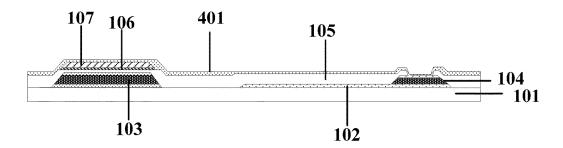

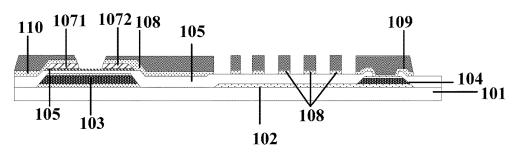

[0041] FIGS. 2-1 to 2-7 show a process of forming a gate insulation layer, an active layer and a source-drain metal layer by one patterning process in some embodiments of the present disclosure;

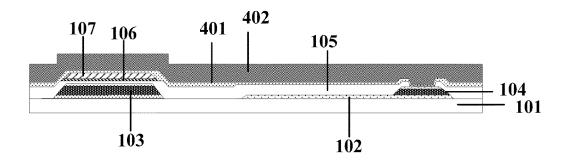

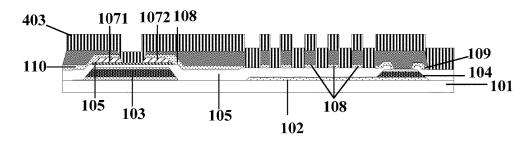

[0042] FIGS. 3-1 to 3-7 show a process of forming a pixel electrode, a common electrode line, source-drain electrodes and a passivation layer by one patterning process in some embodiments of the present disclosure; and

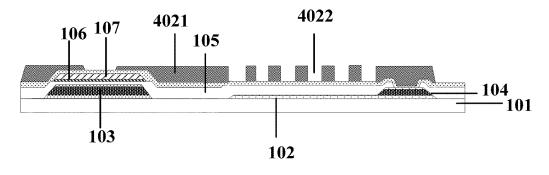

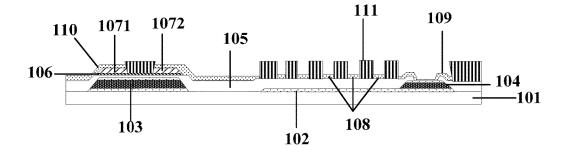

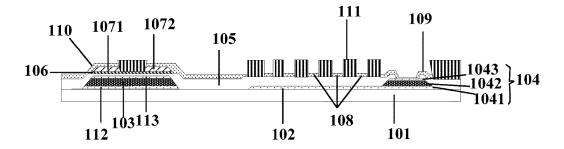

[0043] FIG. 4 is a schematic view of a TFT array substrate in some embodiments of the present disclosure.

### DETAILED DESCRIPTION

[0044] In order to make the technical issues, the technical solutions and the advantages of the present disclosure more apparent, the present disclosure will be described hereinafter in details in conjunction with the drawings and embodiments.

[0045] According to a method for manufacturing a TFT array substrate in the related art, after source-drain electrodes are formed, a passivation (PVX) layer is generally deposited onto the source-drain electrodes, and via-holes are formed in the passivation layer by one patterning process. Then, a transparent conductive thin film is formed on the passivation layer, and a pixel electrode is formed by one patterning process. Each pixel electrode is connected to the corresponding drain electrode through the via-hole. In other words, two masks are required to form the passivation layer and the pixel electrode in the process of manufacturing the TFT array substrate in the related art.

[0046] In order to reduce the number of the masks used in the process of manufacturing the TFT array substrate, a method for manufacturing a TFT array substrate is provided in the present disclosure, including:

[0047] Step S1: forming, on a substrate, a gate electrode, a common electrode, a gate insulation layer, an active layer and a source-drain metal layer; and

[0048] Step S2: forming, on the substrate on which the gate electrode, the common electrode, the gate insulation layer, the active layer and the source-drain metal layer are formed, a pixel electrode and a passivation layer by one patterning process.

**[0049]** According to the method in some embodiments of the present disclosure, the pixel electrode and the passivation layer may be formed by one patterning process, thereby reducing the number of the masks used in the process of manufacturing the TFT array substrate and reducing the production cost.

[0050] The step of forming the pixel electrode and the passivation layer by one patterning process will be described in details hereinafter.

[0051] At Step S1, the source-drain metal layer may cover completely a channel between source-drain electrodes, i.e., the channel between the source-drain electrodes is not formed. Optionally, the source -drain metal layer may not cover the channel between the source and drain electrodes, i.e., the channel between the source-drain electrodes is formed.

[0052] At Step S1, when the source-drain metal layer covers completely the channel between the source and drain electrodes, the step of forming the pixel electrode and the passivation layer by one patterning process includes following steps.

[0053] Step S211 is to form a third transparent conductive thin film. The third transparent conductive thin film may be an indium tin oxide (ITO) or an indium zinc oxide (IZO) conductive thin film.

[0054] Step S212 is to coat photoresist onto the third transparent conductive thin film.

[0055] Step S213 is to expose and develop the photoresist by a common mask plate, so as to form a photoresist fully-reserved region and a photoresist fully-unreserved region. The photoresist fully-reserved region includes a region corresponding to the pixel electrode, a common electrode line and the source-drain electrodes. The photoresist fully-unreserved region includes a region corresponding to the channel between the source and the drain electrodes and the passivation layer.

[0056] Step S214 is to etch the third transparent conductive thin film at the photoresist fully-unreserved region, so as to form the pixel electrode, the common electrode line and a source electrode protective portion. The source electrode protective portion covers the source electrode. The pixel electrode covers the drain electrode.

[0057] Step S215 is to etch the source-drain metal layer at the photoresist fully-unreserved region, so as to form the source and the drain electrodes.

[0058] In Step S215, since the source electrode protective portion covers the source electrode, so the source-drain metal layer at the region of the source electrode may not be etched. Since the pixel electrode covers the drain electrode, so the source-drain metal layer at the region of the drain electrode may not be etched.

[0059] Step S216 is to form a passivation layer thin film. [0060] Step S217 is to peel off the photoresist at the photoresist fully-reserved region, so as to form the passivation layer.

[0061] In some embodiments of the present disclosure, the pixel electrode and the common electrode line are formed simultaneously, i.e., the pixel electrode and the common electrode line are formed on the same plane, and thus it is easy to achieve lap joints of the pixel electrode and the common electrode when bright points occur, so as to turn the bright points into dark points.

[0062] Of course, in some embodiments of the present disclosure, the pixel electrode and the common electrode line may not be formed simultaneously. Then, in Step S213, the photoresist fully-reserved region merely includes a region corresponding to the pixel electrode and the source and drain electrodes, and does not include a region corresponding to the common electrode line.

[0063] In the embodiments of the present disclosure, after the source-drain metal layer is formed, the pixel electrode is formed firstly and then the passivation layer thin film is formed without peeling off the photoresist. Then, the photoresist at the photoresist fully-reserved region is peeled off, such that the passivation layer thin film on this part of the photoresist is removed accordingly. The passivation layer thin film at the photoresist fully-unreserved region forms the passivation layer which covers and protects a region not covered by the transparent conductive thin film. It can be seen that, in the embodiment of the present disclosure, the pixel electrode and the passivation layer may be formed by merely one patterning process, thereby reducing the number of the masks used in the process of manufacturing the TFT array substrate and reducing the production cost.

[0064] In Step S1, when the source-drain metal layer does not cover the channel between the source and drain electrode, i.e., the channel between the source and drain electrode is formed, the step of forming the pixel electrode and the passivation layer by one patterning process includes the following steps.

[0065] Step S221 is to form a third transparent conductive thin film. The third transparent conductive thin film may be an ITO or an IZO conductive thin film.

[0066] Step S222 is to coat photoresist onto the third transparent conductive thin film.

[0067] Step S223 is to expose and develop the photoresist by a common mask plate, so as to form a photoresist fully-reserved region and a photoresist fully-unreserved region. The photoresist fully-reserved region includes a region corresponding to the pixel electrode and a common electrode line. The photoresist fully-unreserved region includes a region corresponding to the passivation layer.

[0068] Step S224 is to etch the third transparent conductive thin film at the photoresist fully-unreserved region, so as to form the pixel electrode and the common electrode line.

[0069] Step S225 is to form a passivation layer thin film. [0070] Step S226 is to peel off the photoresist at the photoresist fully-reserved region, so as to form the passivation layer.

[0071] In some embodiments of the present disclosure, the pixel electrode and the common electrode line are formed simultaneously, i.e., the pixel electrode and the common electrode line are formed on the same plane, and thus it is easy to achieve lap joints of the pixel electrode and the common electrode when the bright points occur, so as to turn the bright points into dark points.

[0072] Of course, in some embodiments of the present disclosure, the pixel electrode and the common electrode line may not be formed simultaneously. Then, in Step S223, the photoresist fully-reserved region merely includes a region corresponding to the pixel electrode and source and drain electrodes, and does not include a region corresponding to the common electrode line.

[0073] In the embodiments of the present disclosure, after the source-drain metal layer is formed, the pixel electrode is formed firstly and then the passivation layer thin film is formed without peeling off the photoresist. Then, the photoresist at the photoresist fully-reserved region is peeled off, such that the passivation layer thin film on this part of the photoresist is removed accordingly. The passivation layer thin film at the photoresist fully-unreserved region forms the passivation layer which covers and protects a region not covered by the transparent conductive thin film. It can be seen that, in the embodiment of the present disclosure, the pixel electrode and the passivation layer may be formed by merely one patterning process, thereby reducing the number of the masks used in the process of manufacturing the TFT array substrate and reducing the production cost.

[0074] In Step S1 hereinabove, the gate electrode, the common electrode, the gate insulation layer, the active layer and the source-drain metal layer may be formed on the substrate by a method in the related art. In order to further reduce the number of the masks, the gate electrode, the common electrode, the gate insulation layer, the active layer and the source-drain metal layer may be formed on the substrate by the method in the embodiments of the present disclosure hereinafter.

[0075] For example, the gate electrode, the common electrode, and a common electrode line connection portion may be formed by one patterning process.

[0076] To be specific, the step of forming, on the substrate, the gate electrode, the common electrode, and the common electrode line connection portion by one patterning process may include the following steps.

[0077] Step S111 is to form, on the substrate, a first transparent conductive thin film, a gate metal thin film and a second transparent conductive thin film in sequence. The first and second transparent conductive thin films may be ITO or IZO conductive thin films.

[0078] Step S112 is to coat photoresist onto the second transparent conductive thin film.

[0079] Step S113 is to expose and develop the photoresist by a grey tone mask plate or a half tone mask plate, so as to form a photoresist fully-reserved region, a photoresist partially-reserved region and a photoresist fully-unreserved region. The photoresist fully-reserved region includes a region corresponding to the gate electrode and the common electrode line connection portion. The photoresist partially-reserved region includes a region corresponding to the common electrode. The photoresist fully-unreserved region includes a region other than the photoresist fully-reserved region and the photoresist partially-reserved region.

[0080] The common electrode line connection portion formed in Step S113 is configured to connect the common electrode to the common electrode line. The common electrode line is formed in a plane identical to the pixel electrode and formed simultaneously with the pixel electrode.

[0081] Step S114 is to remove the first transparent conductive thin film, the gate metal thin film and the second transparent conductive thin film at the photoresist fully-unreserved region by an etching process.

[0082] Step S115 is to remove the photoresist at the photoresist partially-reserved region by an ashing process. [0083] Step S116 is to remove the gate metal thin film and the second transparent conductive thin film at the photoresist

partially-reserved region by an etching process, so as to form the common electrode.

[0084] Step S117 is to peel off the photoresist at the

photoresist fully-reserved region, so as to expose the gate electrode and the common electrode line connection portion. [0085] In the embodiment hereinabove, when the gate electrode is formed, a gate electrode protective layer, which is formed by the reserved second transparent conductive thin film, may be formed on the gate electrode, so as to protect the gate electrode in the subsequent step of etching the source-drain metal layer. Of course, if the etching process of the source-drain metal layer can be controlled well, it is unnecessary to form such gate electrode protective layer. Then, in Step S111, it is merely required to form the first transparent conductive thin film and the gate metal thin film, without forming the second transparent conductive thin film. [0086] Of course, when the common electrode line is arranged at a plane different from the pixel electrode, merely the gate electrode and the common electrode may be formed on the substrate by one patterning process. Then, the photoresist fully-reserved region formed in Step S113 merely

[0087] In order to further reduce the number of the masks, the gate insulation layer, the active layer and the source-drain metal layer may be formed by one patterning process in some embodiments of the present disclosure.

includes a region corresponding to the gate electrode.

[0088] To be specific, the step of forming the gate insulation layer, the active layer and the source-drain metal layer by one patterning process may include the following steps.

[0089] Step S121 is to form a gate insulation thin film, an active layer thin film and a source-drain metal thin film in sequence.

[0090] Step S122 is to coat photoresist onto the source-drain metal thin film.

[0091] Step S123 is to expose and develop the photoresist by a grey tone mask plate or a half tone mask plate, so as to form a photoresist fully-reserved region, a photoresist partially-reserved region and a photoresist fully-unreserved region. The photoresist fully-reserved region includes a region corresponding to the active layer. The photoresist fully-unreserved region includes a region corresponding to the common electrode line connection portion. The photoresist partially-reserved region includes a region other than the photoresist fully-reserved region and the photoresist fully-unreserved region.

[0092] The common electrode line connection portion formed in Step S123 is configured to connect the common electrode to the common electrode line. The common electrode line is formed in a plane identical to the pixel electrode and formed simultaneously with the pixel electrode.

[0093] Step S124 is to remove the gate insulation thin film, the active layer thin film and the source-drain metal thin film at the photoresist fully-unreserved region by an etching process.

[0094] Step S125 is to remove the photoresist at the photoresist partially-reserved region by an ashing process.

[0095] Step S126 is to remove the source-drain metal thin film and the active layer thin film at the photoresist partially-reserved region by an etching process, so as to form the gate insulation layer.

[0096] Step S127 is to peel off the photoresist at the photoresist fully-reserved region, so as to expose the source-drain metal layer and the active layer.

[0097] In the source-drain metal layer formed in some embodiments of the present disclosure, the source-drain metal layer covers completely a channel between the source and the drain electrodes, i.e., the channel between the source and the drain electrodes has not been formed, so that the channel may be protected in the subsequent step of forming the pixel electrode by an etching process.

[0098] In the embodiment hereinabove, a bottom-gate type TFT array substrate is taken as an example to illustrate the method in some embodiments of the present disclosure. Of course, the step of forming the pixel electrode and the passivation layer by one pattering process is also applicable to a top-gate type TFT array substrate.

[0099] From the above, in Step S1, the gate electrode, the common electrode, the gate insulation layer, the active layer and the source-drain metal layer may be formed by merely two patterning processes, i.e., according to the method for manufacturing the TFT array substrate in some embodiments of the present disclosure, the TFT array substrate may be formed by merely three patterning processes, thereby reducing the number of the masks and making the process simple and easy to be controlled.

[0100] The method of forming the TFT array substrate by three patterning processes will be described hereinafter and may include the following steps.

[0101] Step S31 is to form, on a substrate, a gate electrode, a common electrode, and a common electrode line connection portion by one patterning process.

[0102] Step S32 is to form, on the resultant substrate, a gate insulation layer, an active layer and a source-drain metal layer by one patterning process.

[0103] Step S33 is to form, on the resultant substrate, a pixel electrode, a common electrode line, source and drain electrodes and a passivation layer.

[0104] Referring to FIG. 1-1 to FIG. 1-7, the Step S31 further includes the following steps.

[0105] Step S311 is to form, on a substrate 101, a first transparent conductive thin film 201, a gate metal thin film 202 and a second transparent conductive thin film 203 in sequence. The first transparent conductive thin film 201 and the second transparent conductive thin film 203 may be ITO or IZO conductive thin films.

[0106] Step S312 is to coat photoresist 204 onto the second transparent conductive thin film 203.

[0107] Step S313 is to expose and develop the photoresist by a grey tone mask plate or a half tone mask plate, so as to form a photoresist fully-reserved region 2041, a photoresist partially-reserved region 2042 and a photoresist fully-unreserved region 2043. The photoresist fully-reserved region 2041 includes a region corresponding to the gate electrode and the common electrode line connection portion. The photoresist partially-reserved region 2042 includes a region corresponding to the common electrode. The photoresist fully-unreserved region 2043 includes a region other than the photoresist fully-reserved region 2041 and the photoresist partially-reserved region 2042.

[0108] Step S314 is to remove the first transparent conductive thin film 201, the gate metal thin film 202 and the second transparent conductive thin film 203 at the photoresist fully-unreserved region 2043 by an etching process.

[0109] Step S315 is to remove the photoresist at the photoresist partially-reserved region 2042 by an ashing process.

[0110] Step S316 is to remove the gate metal thin film 202 and the second transparent conductive thin film 203 at the photoresist partially-reserved region 2042 by an etching process, so as to form the common electrode 102.

[0111] Step S317 is to peel off the photoresist at the photoresist fully-reserved region 2041, so as to expose the gate electrode 103 and the common electrode line connection portion 104.

[0112] Referring to FIG. 2-1 to FIG. 2-7, the Step S32 further includes the following steps.

[0113] Step S321 is to form a gate insulation thin film 301, an active layer thin film 302 and a source-drain metal thin film 303 in sequence.

[0114] Step S322 is to coat photoresist 304 onto the source-drain metal thin film 303.

[0115] Step S323 is to expose and develop the photoresist by a grey tone mask plate or a half tone mask plate, so as to form a photoresist fully-reserved region 3041, a photoresist partially-reserved region 3042 and a photoresist fully-unreserved region 3043. The photoresist fully-reserved region 3041 includes a region corresponding to the active layer. The photoresist fully-unreserved region 3043 includes a region corresponding to the common electrode line connection portion. The photoresist partially-reserved region 3042

includes a region other than the photoresist fully-reserved region 3041 and the photoresist fully-unreserved region 3043.

[0116] Step S324 is to remove the gate insulation thin film 301, the active layer thin film 302 and the source-drain metal thin film 303 at the photoresist fully-unreserved region 3043 by an etching process.

[0117] Step S325 is to remove the photoresist at the photoresist partially-reserved region 3042 by an ashing process.

[0118] Step S326 is to remove the source-drain metal thin film 303 and the active layer thin film 302 at the photoresist partially-reserved region 3042 by an etching process, so as to form the gate insulation layer 105.

[0119] Step S327 is to peel off the photoresist at the photoresist fully-reserved region 3041, so as to expose the source-drain metal layer 107 and the active layer 106.

[0120] Referring to FIG. 3-1 to FIG. 3-7, the Step S33 further includes the following steps.

[0121] Step S331 is to form a third transparent conductive thin film 104. The third transparent conductive thin film 104 may be an indium tin oxide (ITO) or an indium zinc oxide (IZO) conductive thin film.

[0122] Step S332 is to coat photoresist 402 onto the third transparent conductive thin film 401.

[0123] Step S333 is to expose and develop the photoresist 402 by a common mask plate, so as to form a photoresist fully-reserved region 4021 and a photoresist fully-unreserved region 4022. The photoresist fully-reserved region 4021 includes a region corresponding to the pixel electrode, the common electrode line and the source and drain electrodes. The photoresist fully-unreserved region 4022 includes a region corresponding to a channel between the source and the drain electrode and the passivation layer.

[0124] Step S334 is to etch the third transparent conductive thin film 401 at the photoresist fully-unreserved region 4022, so as to form the pixel electrode 108, the common electrode line 109 and a source electrode protective portion 110.

[0125] Step S335 is to etch the source-drain metal layer 107 at the photoresist fully-unreserved region 4022, so as to form the source electrode 1071 and the drain electrode 1072. [0126] Step S336 is to form a passivation layer thin film

**403**. [0127] Step S337 is to peel off the photoresist at the photoresist fully-reserved region **4021**, so as to form the

photoresist fully-reserved region 4021, so as to form the passivation layer 111.

[0128] As shown in FIG. 4, a TFT array substrate is further

provided in some embodiments of the present disclosure, including:

[0129] a substrate 101, and a gate electrode 103, a common electrode 102, a gate insulation layer 105, an active layer 106, a source electrode 1071 and a drain electrode 1072 arranged on the substrate 101;

[0130] a pixel electrode 108 arranged on the gate insulation layer 105 and overlapped with and jointed to the drain electrode 1072; and

[0131] a passivation layer 111 arranged on the gate insulation layer 105 and a channel between the source electrode 1071 and the drain electrode 1072.

[0132] Optionally, the TFT array substrate further includes: a common electrode line 109, arranged at a layer and made of a material identical to the pixel electrode 108.

[0133] That is, the pixel electrode 108 and the common electrode line 109 are formed on the same plane, and thus it is easy to achieve the lap joints of the pixel electrode 102 and the common electrode 108 when the bright points occur, so as to turn the bright points into dark points.

[0134] Optionally, the TFT array substrate further includes:

[0135] the gate electrode 103, arranged on the substrate 101:

[0136] the common electrode 102, arranged on the substrate 101.

[0137] The thin film transistor array substrate further includes:

[0138] a transparent conductive thin film protective portion 112, arranged between the gate electrode 103 and the substrate 101 and arranged at a layer and made of a material identical to the common electrode 102;

[0139] a common electrode line connection portion 104, arranged on the common electrode 102 and including a first transparent conductive layer 1041 and a gate metal layer 1042, where the common electrode 102 is connected to the corresponding common electrode line 109 via the common electrode line connection portion 104.

[0140] Optionally, the TFT array substrate further includes: a gate electrode protective layer 113, arranged between the gate electrode 103 and the gate insulation layer 105.

[0141] The common electrode line connection portion 104 further includes a second transparent conductive layer 1043 arranged at a layer and made of a material identical to the gate electrode protective layer 113.

[0142] Optionally, the TFT array substrate further includes: a source electrode protective portion 110 arrange on the source electrode 1071 and arranged at a layer and made of a material identical to the pixel electrode 108.

[0143] A display device is further provided in some embodiments of the present disclosure, including the TFT array substrate hereinabove.

[0144] The above are merely the optional embodiments of the present disclosure. A person skilled in the art may make further modifications and improvements without departing from the principle of the present disclosure, and these modifications and improvements shall also fall within the scope of the present disclosure.

1. A method for manufacturing a thin film transistor array substrate, comprising:

forming, on a substrate, a gate electrode, a common electrode, a gate insulation layer, an active layer and a source-drain metal layer; and

forming, on the substrate on which the gate electrode, the common electrode, the gate insulation layer, the active layer and the source-drain metal layer are formed, a pixel electrode and a passivation layer by one patterning process.

2. The method according to claim 1, wherein the forming the pixel electrode and the passivation layer by one patterning process comprises:

forming a transparent conductive thin film;

coating photoresist onto the transparent conductive thin film:

exposing and developing the photoresist with a common mask plate, so as to form a photoresist fully-reserved region and a photoresist fully-unreserved region, wherein the photoresist fully-reserved region comprises a region corresponding to the pixel electrode, a common electrode line and a source electrode and a drain electrode, and the photoresist fully-unreserved region comprises a region corresponding to a channel between the source electrode and the drain electrode and the passivation layer;

etching the transparent conductive thin film at the photoresist fully-unreserved region, so as to form the pixel electrode, the common electrode line and a source electrode protective portion;

etching the source-drain metal layer at the photoresist fully-unreserved region, so as to form the source and drain electrodes; wherein the pixel electrode is overlapped with and jointed to the drain electrode; wherein the source electrode protective portion covers the source electrode, and the pixel electrode covers the drain electrode;

forming a passivation layer thin film; and

peeling off the photoresist at the photoresist fully-reserved region, so as to form the passivation layer.

3. The method according to claim 1, wherein the forming on the substrate, the gate electrode, the common electrode, the gate insulation layer, the active layer and the source-drain metal layer comprises:

forming, on the substrate, the gate electrode, the common electrode, and a common electrode line connection portion by one patterning process.

**4**. The method according to claim **3**, wherein the forming, on the substrate, the gate electrode, the common electrode, and the common electrode line connection portion by one patterning process comprises:

forming, on the substrate, a first transparent conductive thin film, a gate metal thin film and a second transparent conductive thin film in sequence;

coating photoresist onto the second transparent conductive thin film;

exposing and developing the photoresist with a grey tone mask plate or a half tone mask plate, so as to form a photoresist fully-reserved region, a photoresist partially-reserved region and a photoresist fully-unreserved region, wherein the photoresist fully-reserved region comprises a region corresponding to the gate electrode and the common electrode line connection portion, the photoresist partially-reserved region comprises a region corresponding to the common electrode, and the photoresist fully-unreserved region comprises a region other than the photoresist fully-reserved region and the photoresist partially-reserved region;

removing the first transparent conductive thin film, the gate metal thin film and the second transparent conductive thin film at the photoresist fully-unreserved region by an etching process;

removing the photoresist at the photoresist partiallyreserved region by an ashing process;

removing the gate metal thin film and the second transparent conductive thin film at the photoresist partiallyreserved region by an etching process, so as to form the common electrode; and

peeling off the photoresist at the photoresist fully-reserved region, so as to expose the gate electrode and the common electrode line connection portion.

5. The method according to claim 3, wherein the forming on the substrate, the gate electrode, the common electrode,

the gate insulation layer, the active layer and the sourcedrain metal layer further comprises:

- forming the gate insulation layer, the active layer and the source-drain metal layer by one patterning process.

- **6**. The method according to claim **5**, wherein the forming the gate insulation layer, the active layer and the source-drain metal layer by one patterning process comprises:

forming a gate insulation thin film, an active layer thin film and a source-drain metal thin film in sequence;

- coating photoresist onto the source-drain metal thin film; exposing and developing the photoresist with a grey tone mask plate or a half tone mask plate, so as to form a photoresist fully-reserved region, a photoresist partially-reserved region and a photoresist fully-unreserved region, wherein the photoresist fully-urserved region comprises a region corresponding to the active layer, the photoresist fully-unreserved region comprises a region corresponding to the common electrode line connection portion, and the photoresist partially-reserved region comprises a region other than the photoresist fully-unreserved region;

- removing the gate insulation thin film, the active layer thin film and the source-drain metal thin film at the photoresist fully-unreserved region by an etching process;

- removing the photoresist at the photoresist partiallyreserved region by an ashing process;

- removing the source-drain metal thin film and the active layer thin film at the photoresist partially-reserved region by an etching process, so as to form the gate insulation layer; and

- peeling off the photoresist at the photoresist fully-reserved region, so as to expose the source-drain metal layer and the active layer.

- 7. A thin film transistor (TFT) array substrate, comprising: a substrate, and a gate electrode, a common electrode, a gate insulation layer, an active layer, a source electrode and a drain electrode arranged on the substrate, wherein the TFT array substrate further comprises:

- a pixel electrode, arranged on the gate insulation layer, overlapped with and jointed to the drain electrode; and

- a passivation layer, arranged on the gate insulation layer and a channel between the source and drain electrodes.

- **8**. The TFT array substrate according to claim **7**, further comprising:

- a common electrode line, arranged at a same layer and made of a same material as the pixel electrode.

- 9. The TFT array substrate according to claim 8, further comprising:

- a transparent conductive thin film protective portion, arranged between the gate electrode and the substrate, wherein the transparent conductive thin film protective portion is arranged at a same layer and made of a same material as the common electrode;

- a common electrode line connection portion, arranged on the common electrode and comprising a first transparent conductive layer and a gate metal layer, wherein the common electrode is connected to the common electrode line via the common electrode line connection portion.

- 10. The TFT array substrate according to claim 9, further comprising:

- a gate electrode protective layer, arranged between the gate electrode and the gate insulation layer;

- wherein the common electrode line connection portion further comprises a second transparent conductive layer arranged at a same layer and made of a same material as the gate electrode protective layer.

- 11. The TFT array substrate according to claim 8, further comprising:

- a source electrode protective portion covering the source electrode and arranged at a same layer and made of a same material as the pixel electrodes.

- 12. A display device, comprising: a thin film transistor (TFT) array substrate according to any one of claims 7 11 array substrate;

- wherein the thin film transistor array substrate comprises: a substrate, and a gate electrode, a common electrode, a gate insulation layer, an active layer, a source electrode and a drain electrode arranged on the substrate, wherein the TFT array substrate further comprises:

- a pixel electrode, arranged on the gate insulation layer, overlapped with and jointed to the drain electrode; and

- a passivation layer, arranged on the gate insulation layer and a channel between the source and drain electrodes.

- 13. The display device according to claim 12, wherein the TFT array substrate further comprises:

- a common electrode line, arranged at a same layer and made of a same material as the pixel electrode.

- **14**. The display device according to claim **13**, wherein the TFT array substrate further comprises:

- a transparent conductive thin film protective portion, arranged between the gate electrode and the substrate, wherein the transparent conductive thin film protective portion is arranged at a same layer and made of a same material as the common electrode;

- a common electrode line connection portion, arranged on the common electrode and comprising a first transparent conductive layer and a gate metal layer, wherein the common electrode is connected to the common electrode line via the common electrode line connection portion.

- **15**. The display device according to claim **14**, wherein the TFT array substrate further comprises:

- a gate electrode protective layer, arranged between the gate electrode and the gate insulation layer;

- wherein the common electrode line connection portion further comprises a second transparent conductive layer arranged at a same layer and made of a same material as the gate electrode protective layer.

- **16**. The display device according to claim **13**, wherein the TFT array substrate further comprises:

- a source electrode protective portion covering the source electrode and arranged at a same layer and made of a same material as the pixel electrodes.

- 17. The method according to claim 4, wherein the forming the pixel electrode and the passivation layer by one patterning process comprises:

- forming a third transparent conductive thin film;

- coating photoresist onto the third transparent conductive thin film;

- exposing and developing the photoresist with a common mask plate, so as to form a photoresist fully-reserved region and a photoresist fully-unreserved region, wherein the photoresist fully-reserved region comprises a region corresponding to the pixel electrode, a

common electrode line and a source electrode and a drain electrode, and the photoresist fully-unreserved region comprises a region corresponding to a channel between the source electrode and the drain electrode and the passivation layer;

etching the third transparent conductive thin film at the photoresist fully-unreserved region, so as to form the pixel electrode, the common electrode line and a source electrode protective portion;

etching the source-drain metal layer at the photoresist fully-unreserved region, so as to form the source and drain electrodes; wherein the pixel electrode is overlapped with and jointed to the drain electrode; wherein the source electrode protective portion covers the source electrode, and the pixel electrode covers the drain electrode;

forming a passivation layer thin film; and peeling off the photoresist at the photoresist fully-reserved region, so as to form the passivation layer.

\* \* \* \* \*