(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-205101

(P2011-205101A)

(43) 公開日 平成23年10月13日(2011.10.13)

(51) Int.Cl.

H01L 27/11 (2006.01)

H01L 21/8244 (2006.01)

F 1

H01L 27/10

3 8 1

テーマコード(参考)

5 F O 8 3

審査請求 未請求 請求項の数 59 O L (全 51 頁)

(21) 出願番号 特願2011-65756 (P2011-65756)

(22) 出願日 平成23年3月24日 (2011.3.24)

(31) 優先権主張番号 10-2010-0026406

(32) 優先日 平成22年3月24日 (2010.3.24)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2011-0001087

(32) 優先日 平成23年1月5日 (2011.1.5)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do, Republic

of Korea

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】半導体メモリ装置及びその製造方法

## (57) 【要約】

【課題】半導体メモリ装置及びその製造方法を提供する。

【解決手段】第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、第1ウェル領域は、第2ウェル領域と第3ウェル領域との間に配され、第1ウェル領域は、第1タイプ導電体を含み、第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板；第1ウェル領域に一列に形成され、電源端子を共有する第1プルアップ素子及び第2プルアップ素子；第2ウェル領域に第1プルダウン素子と隣接するように配される第1プルダウン素子；第3ウェル領域に第2プルダウン素子と隣接するように配される第2プルダウン素子；第2ウェル領域に第2プルアップ素子と隣接するように配される第1アクセス素子；第3ウェル領域に第1プルアップ素子と隣接するように形成される第2アクセス素子；を含む半導体メモリ装置である。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板と、

前記第1ウェル領域に一列に形成され、電源端子を共有する第1プルアップ素子及び第2プルアップ素子と、

前記第2ウェル領域に、前記第1プルアップ素子と隣接するように配される第1プルダウン素子と、10

前記第3ウェル領域に、前記第2プルアップ素子と隣接するように配される第2プルダウン素子と、

前記第2ウェル領域に、前記第2プルアップ素子と隣接するように配される第1アクセス素子と、

前記第3ウェル領域に、前記第1プルアップ素子と隣接するように配される第2アクセス素子と、を含む半導体メモリ装置。20

**【請求項 2】**

前記第1プルアップ素子及び第2プルアップ素子は、単一活性領域に配され、前記単一活性領域は、前記第1ウェル領域に含まれることを特徴とする請求項1に記載の半導体メモリ装置。

**【請求項 3】**

前記第1プルアップ素子及び前記第1プルダウン素子は、第1インバータを構成し、

前記第2プルアップ素子及び前記第2プルダウン素子は、第2インバータを構成することを特徴とする請求項1に記載の半導体メモリ装置。

**【請求項 4】**

前記第1アクセス素子は、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結され、

前記第2アクセス素子は、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結されることを特徴とする請求項3に記載の半導体メモリ装置。30

**【請求項 5】**

前記第1アクセス素子は、ワードラインに印加される電圧によって制御され、1対のビットラインのうち第1ビットラインを、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結させる第1アクセス・トランジスタを含むことを特徴とする請求項3に記載の半導体メモリ装置。

**【請求項 6】**

前記第2アクセス素子は、前記ワードラインに印加される電圧によって制御され、前記1対のビットラインのうち第2ビットラインを、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結させる第2アクセス・トランジスタを含むことを特徴とする請求項5に記載の半導体メモリ装置。40

**【請求項 7】**

前記第1アクセス素子及び前記第1プルダウン素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第2ウェル領域に含まれることを特徴とする請求項1に記載の半導体メモリ装置。

**【請求項 8】**

前記第2アクセス素子及び前記第2プルダウン素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第3ウェル領域に含まれることを特徴とする請求項1に記載の半導体メモリ装置。

**【請求項 9】**

前記第1タイプ導電体は、N型導電体であって、前記第2タイプ導電体は、P型導電体であることを特徴とする請求項1に記載の半導体メモリ装置。50

**【請求項 10】**

前記第1 プルアップ素子は、前記電源端子に連結されるソースを有するPチャネル・トランジスタを含み、

前記第1 プルダウン素子は、前記Pチャネル・トランジスタのドレインに連結されるドレイン、前記Pチャネル・トランジスタのゲートに連結されるゲート、及び接地端子に連結されるソースを有するNチャネル・トランジスタを含むことを特徴とする請求項9に記載の半導体メモリ装置。

**【請求項 11】**

前記第2 プルアップ素子は、前記電源端子に連結されるソースを有するPチャネル・トランジスタを含み、

前記第2 プルダウン素子は、前記Pチャネル・トランジスタのドレインに連結されるドレイン、前記Pチャネル・トランジスタのゲートに連結されるゲート、及び接地端子に連結されるソースを有するNチャネル・トランジスタを含むことを特徴とする請求項9に記載の半導体メモリ装置。

**【請求項 12】**

前記第1 アクセス素子は、ワードラインに連結されるゲートを有するNチャネル・トランジスタを含み、

前記第2 アクセス素子は、前記ワードラインに連結されるゲートを有するNチャネル・トランジスタを含むことを特徴とする請求項9に記載の半導体メモリ装置。

**【請求項 13】**

前記半導体メモリ装置は、電子システムに含まれ、

前記電子システムは、バスを介して互いに通信するメモリ部、プロセッサ及び入出力装置を含み、

前記プロセッサは、前記半導体メモリ装置を含む記憶装置を含むことを特徴とする請求項1に記載の半導体メモリ装置。

**【請求項 14】**

第1 ウェル領域、第2 ウェル領域及び第3 ウェル領域を含む基板であって、前記第1 ウェル領域は、前記第2 ウェル領域と前記第3 ウェル領域との間に配され、前記第1 ウェル領域は、第1 タイプ導電体を含み、前記第2 ウェル領域及び第3 ウェル領域は、第2 タイプ導電体をそれぞれ含む基板と、

前記第1 ウェル領域に含まれ、第1 プルアップ素子及び第2 プルアップ素子が一列に配される第1 活性領域と、

前記第2 ウェル領域に含まれ、前記第2 プルアップ素子に隣接した第1 アクセス素子、及び前記第1 プルアップ素子に隣接した第1 プルダウン素子が配される第2 活性領域と、

前記第3 ウェル領域に含まれ、前記第1 プルアップ素子に隣接した第2 アクセス素子、及び前記第2 プルアップ素子に隣接した第2 プルダウン素子が配される第3 活性領域と、を含む半導体メモリ装置。

**【請求項 15】**

前記第1 プルアップ素子及び第2 プルアップ素子は、第1 方向に沿って一列に配され、

前記第1 プルアップ素子は、前記第1 方向と垂直である第2 方向に沿って、前記第1 プルダウン素子及び前記第2 アクセス素子と隣接するように配され、

前記第2 プルアップ素子は、前記第2 方向に沿って、前記第2 プルダウン素子及び前記第1 アクセス素子と隣接するように配されることを特徴とする請求項14に記載の半導体メモリ装置。

**【請求項 16】**

前記第1 活性領域及び第2 活性領域の上部を横切る方向に、前記基板の上部に形成される第1 ゲート電極と、

前記第1 活性領域及び第3 活性領域の上部を横切る方向に、前記基板の上部に形成される第2 ゲート電極と、をさらに含み、

前記第1 プルアップ素子と前記第1 プルダウン素子は、前記第1 ゲート電極に共通して

10

20

30

40

50

連結されて第1インバータを構成し、前記第2プルアップ素子と前記第2プルダウン素子は、前記第2ゲート電極に共通して連結されて第2インバータを構成することを特徴とする請求項14に記載の半導体メモリ装置。

**【請求項17】**

前記第1アクセス素子を、前記第2インバータの入力端子、及び前記第1インバータの出力端子に連結させる第1金属配線と、

前記第2アクセス素子を、前記第1インバータの入力端子、及び前記第2インバータの出力端子に連結させる第2金属配線と、をさらに含むことを特徴とする請求項16に記載の半導体メモリ装置。

**【請求項18】**

前記第1金属配線及び前記第2金属配線は、同一層に配されることを特徴とする請求項17に記載の半導体メモリ装置。

**【請求項19】**

前記第1金属配線及び前記第2金属配線は、互いに異なる層に配されることを特徴とする請求項17に記載の半導体メモリ装置。

**【請求項20】**

前記第2活性領域の上部を横切る方向に、前記基板の上部に形成される第3ゲート電極と、

前記第3活性領域の上部を横切る方向に、前記基板の上部に形成される第4ゲート電極と、をさらに含むことを特徴とする請求項16に記載の半導体メモリ装置。

**【請求項21】**

前記第3ゲート電極及び第4ゲート電極と平行な方向に伸張するように、前記基板の上部に形成され、前記第3ゲート電極及び第4ゲート電極に連結されるワードラインをさらに含むことを特徴とする請求項20に記載の半導体メモリ装置。

**【請求項22】**

前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される1対のビットラインをさらに含み、

前記1対のビットラインのうち第1ビットラインは、前記第1アクセス素子に連結され、

前記1対のビットラインのうち第2ビットラインは、前記第2アクセス素子に連結されることを特徴とする請求項14に記載の半導体メモリ装置。

**【請求項23】**

前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される電源電極ラインをさらに含み、

前記電源電極ラインは、前記第1プルアップ素子と第2プルアップ素子との間に形成されたコンタクトプラグを介して、前記第1プルアップ素子及び第2プルアップ素子に連結されることを特徴とする請求項14に記載の半導体メモリ装置。

**【請求項24】**

前記第1タイプ導電体は、N型導電体であって、前記第2タイプ導電体は、P型導電体であることを特徴とする請求項14に記載の半導体メモリ装置。

**【請求項25】**

第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板を提供する段階であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む段階と、

前記第1ウェル領域上に含まれた第1活性領域に、第1プルアップ素子及び第2プルアップ素子を一列に形成する段階と、

前記第2ウェル領域上に含まれた第2活性領域に、前記第1プルアップ素子と隣接した第1プルダウン素子と、前記第2プルアップ素子と隣接した第1アクセス素子と、を形成する段階と、

10

20

30

40

50

前記第3ウェル領域上に含まれた第3活性領域に、前記第2プルアップ素子と隣接した第2プルダウン素子と、前記第1プルアップ素子と隣接した第2アクセス素子と、を形成する段階と、を含む半導体メモリ装置の製造方法。

**【請求項26】**

前記第1プルアップ素子及び第2プルアップ素子は、第1方向に沿って一列に形成され、

前記第1プルアップ素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルダウン素子及び前記第2アクセス素子と隣接するように配され、

前記第2プルアップ素子は、前記第2方向に沿って、前記第2プルダウン素子及び前記第1アクセス素子と隣接するように配されることを特徴とする請求項25に記載の半導体メモリ装置の製造方法。 10

**【請求項27】**

前記第1活性領域、第2活性領域及び第3活性領域のうち少なくとも1つの領域の上部を横切る方向に、前記基板の上部に形成される複数の導電性パターンを形成する段階をさらに含み、

前記第1プルアップ素子と前記第1プルダウン素子は、前記複数の導電性パターンのうち一つに共通して連結されて第1インバータを構成し、

前記第2プルアップ素子と前記第2プルダウン素子は、前記複数の導電性パターンのうち他の一つに共通して連結されて第2インバータを構成することを特徴とする請求項25に記載の半導体メモリ装置の製造方法。 20

**【請求項28】**

前記第1アクセス素子を、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結させる第1金属配線；前記第2アクセス素子を、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結させる第2金属配線；を形成する段階をさらに含むことを特徴とする請求項27に記載の半導体メモリ装置の製造方法。

**【請求項29】**

前記第1金属配線及び第2金属配線を形成する段階は、

前記基板の上部に第1絶縁膜を形成する段階と、

前記第1絶縁膜の一部領域をエッチングして複数の第1コンタクトホールを形成し、前記複数の第1コンタクトホールに金属を充填して複数のコンタクトプラグを形成する段階と、 30

前記複数のコンタクトプラグが形成された前記第1絶縁膜上に、第2絶縁膜を形成する段階と、

前記第2絶縁膜の一部領域をエッチングして複数の第2コンタクトホールを形成し、前記複数の第2コンタクトホールに金属を充填し、前記第1金属配線及び第2金属配線を形成する段階と、を含み、

前記第1金属配線及び第2金属配線は、前記複数のコンタクトプラグを介して、前記第1ウェル領域、第2ウェル領域及び第3ウェル領域のうち少なくとも一つに連結されることを特徴とする請求項28に記載の半導体メモリ装置の製造方法。

**【請求項30】**

前記第1ウェル領域、第2ウェル領域及び第3ウェル領域のうち少なくとも一つにシリサイド層を形成する段階をさらに含み、

前記複数のコンタクトプラグは、前記シリサイド層に連結されることを特徴とする請求項29に記載の半導体メモリ装置の製造方法。 40

**【請求項31】**

第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板と、

前記第1ウェル領域に一列に形成されて接地端子を共有する第1プルダウン素子及び第 50

2 プルダウン素子と、

前記第2ウェル領域に、前記第1プルダウン素子と隣接するように配される第1プルアップ素子と、

前記第3ウェル領域に、前記第2プルダウン素子と隣接するように配される第2プルアップ素子と、

前記第2ウェル領域に、前記第2プルダウン素子と隣接するように配される第1アクセス素子と、

前記第3ウェル領域に、前記第1プルダウン素子と隣接するように配される第2アクセス素子と、を含む半導体メモリ装置。

【請求項32】

前記第1プルダウン素子及び第2プルダウン素子は、単一活性領域に配され、前記単一活性領域は、前記第1ウェル領域に含まれることを特徴とする請求項31に記載の半導体メモリ装置。

【請求項33】

前記第1プルダウン素子及び前記第1プルアップ素子は、第1インバータを構成し、

前記第2プルダウン素子及び前記第2プルアップ素子は、第2インバータを構成することを特徴とする請求項31に記載の半導体メモリ装置。

【請求項34】

前記第1アクセス素子は、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結され、

前記第2アクセス素子は、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結されることを特徴とする請求項33に記載の半導体メモリ装置。

【請求項35】

前記第1アクセス素子は、ワードラインに印加される電圧によって制御され、1対のビットラインのうち第1ビットラインを、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結させる第1アクセス・トランジスタを含むことを特徴とする請求項33に記載の半導体メモリ装置。

【請求項36】

前記第2アクセス素子は、前記ワードラインに印加される電圧によって制御され、前記1対のビットラインのうち第2ビットラインを、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結させる第2アクセス・トランジスタを含むことを特徴とする請求項35に記載の半導体メモリ装置。

【請求項37】

前記第1アクセス素子及び前記第1プルアップ素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第2ウェル領域に含まれることを特徴とする請求項31に記載の半導体メモリ装置。

【請求項38】

前記第2アクセス素子及び前記第2プルアップ素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第2ウェル領域に含まれることを特徴とする請求項31に記載の半導体メモリ装置。

【請求項39】

前記第1タイプ導電体は、P型導電体であって、前記第2タイプ導電体は、N型導電体であることを特徴とする請求項31に記載の半導体メモリ装置。

【請求項40】

前記第1プルダウン素子は、前記接地端子に連結されるソースを有するNチャネル・トランジスタを含み、

前記第1プルアップ素子は、前記Nチャネル・トランジスタのドレインに連結されるドレイン、前記Nチャネル・トランジスタのゲートに連結されるゲート、及び電源端子に連結されるソースを有するPチャネル・トランジスタを含むことを特徴とする請求項39に記載の半導体メモリ装置。

10

20

30

40

50

**【請求項 4 1】**

前記第2プルダウン素子は、前記接地端子に連結されるソースを有するNチャネル・トランジスタを含み、

前記第2プルアップ素子は、前記Nチャネル・トランジスタのドレインに連結されるドレイン、前記Nチャネル・トランジスタのゲートに連結されるゲート、及び電源端子に連結されるソースを有するPチャネル・トランジスタを含むことを特徴とする請求項39に記載の半導体メモリ装置。

**【請求項 4 2】**

前記第1アクセス素子は、ワードラインに連結されるゲートを有するPチャネル・トランジスタを含み、

前記第2アクセス素子は、前記ワードラインに連結されるゲートを有するPチャネル・トランジスタを含むことを特徴とする請求項39に記載の半導体メモリ装置。

10

**【請求項 4 3】**

前記半導体メモリ装置は、電子システムに含まれ、

前記電子システムは、バスを介して互いに通信するメモリ部、プロセッサ及び入出力装置を含み、

前記プロセッサは、前記半導体メモリ装置を含む記憶装置を含むことを特徴とする請求項31に記載の半導体メモリ装置。

20

**【請求項 4 4】**

第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板と、

前記第1ウェル領域に含まれ、第1プルダウン素子及び第2プルダウン素子が一列に配される第1活性領域と、

前記第2ウェル領域に含まれ、前記第2プルダウン素子に隣接した第1アクセス素子、及び前記第1プルダウン素子に隣接した第1プルアップ素子が配される第2活性領域と、

前記第3ウェル領域に含まれ、前記第1プルダウン素子に隣接した第2アクセス素子、及び前記第2プルダウン素子に隣接した第2プルアップ素子が配される第3活性領域と、を含む半導体メモリ装置。

30

**【請求項 4 5】**

前記第1プルダウン素子及び第2プルダウン素子は、第1方向に沿って一列に配され、

前記第1プルダウン素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルアップ素子及び前記第2アクセス素子と隣接するように配され、

前記第2プルダウン素子は、前記第2方向に沿って、前記第2プルアップ素子及び前記第1アクセス素子と隣接するように配されることを特徴とする請求項44に記載の半導体メモリ装置。

40

**【請求項 4 6】**

前記第1活性領域及び第2活性領域の上部を横切る方向に、前記基板の上部に形成される第1ゲート電極と、

前記第1活性領域及び第3活性領域の上部を横切る方向に、前記基板の上部に形成される第2ゲート電極と、をさらに含み、

前記第1プルダウン素子と前記第1プルアップ素子は、前記第1ゲート電極に共通して連結されて第1インバータを構成し、前記第2プルダウン素子と前記第2プルアップ素子は、前記第2ゲート電極に共通して連結されて第2インバータを構成することを特徴とする請求項44に記載の半導体メモリ装置。

**【請求項 4 7】**

前記第1アクセス素子を、前記第2インバータの入力端子、及び前記第1インバータの出力端子に連結させる第1金属配線と、

前記第2アクセス素子を、前記第1インバータの入力端子、及び前記第2インバータの

50

出力端子に連結させる第2金属配線と、をさらに含むことを特徴とする請求項46に記載の半導体メモリ装置。

【請求項48】

前記第1金属配線及び前記第2金属配線は、同一層に配されることを特徴とする請求項47に記載の半導体メモリ装置。

【請求項49】

前記第1金属配線及び前記第2金属配線は、互いに異なる層に配されることを特徴とする請求項47に記載の半導体メモリ装置。

【請求項50】

前記第2活性領域の上部を横切る方向に、前記基板の上部に形成される第3ゲート電極と、

前記第3活性領域の上部を横切る方向に、前記基板の上部に形成される第4ゲート電極と、をさらに含むことを特徴とする請求項46に記載の半導体メモリ装置。

【請求項51】

前記第3ゲート電極及び第4ゲート電極と平行な方向に伸張するように、前記基板の上部に形成され、前記第3ゲート電極及び第4ゲート電極に連結されるワードラインをさらに含むことを特徴とする請求項50に記載の半導体メモリ装置。

【請求項52】

前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される1対のビットラインをさらに含み、

前記1対のビットラインのうち第1ビットラインは、前記第1アクセス素子の一端に連結され、

前記1対のビットラインのうち第2ビットラインは、前記第2アクセス素子の他端に連結されることを特徴とする請求項44に記載の半導体メモリ装置。

【請求項53】

前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される接地電極ラインをさらに含み、

前記接地電極ラインは、前記第1プルダウン素子と第2プルダウン素子との間に形成されたコンタクトプラグを介して、前記第1プルダウン素子及び第2プルダウン素子に連結されることを特徴とする請求項44に記載の半導体メモリ装置。

【請求項54】

前記第1タイプ導電体は、P型導電体であって、前記第2タイプ導電体は、N型導電体であることを特徴とする請求項44に記載の半導体メモリ装置。

【請求項55】

第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板を提供する段階であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む段階と、

前記第1ウェル領域上に含まれた第1活性領域に、第1プルダウン素子及び第2プルダウン素子を一列に形成する段階と、

前記第2ウェル領域上に含まれた第2活性領域に、前記第1プルダウン素子と隣接した第1プルアップ素子及び前記第2プルダウン素子と隣接した第1アクセス素子を形成する段階と、

前記第3ウェル領域上に含まれた第3活性領域に、前記第2プルダウン素子と隣接した第2プルアップ素子と、前記第1プルダウン素子と隣接した第2アクセス素子と、を形成する段階と、を含む半導体メモリ装置の製造方法。

【請求項56】

前記第1プルダウン素子及び第2プルダウン素子は、第1方向に沿って一列に形成され、

前記第1プルダウン素子は、前記第1方向と垂直である第2方向に沿って、前記第1プ

10

20

30

40

50

ルアップ素子及び前記第2アクセス素子と隣接するように配され、

前記第2プルダウン素子は、前記第2方向に沿って、前記第2プルアップ素子及び前記第1アクセス素子と隣接するように配されることを特徴とする請求項55に記載の半導体メモリ装置の製造方法。

#### 【請求項57】

前記第1活性領域、第2活性領域及び第3活性領域のうち少なくとも1つの領域の上部を横切る方向に、前記基板の上部に形成される複数の導電性パターンを形成する段階をさらに含み、

前記第1プルダウン素子と前記第1プルアップ素子は、前記複数の導電性パターンのうち一つに共通して連結されて第1インバータを構成し、

前記第2プルダウン素子と前記第2プルアップ素子は、前記複数の導電性パターンのうち他の一つに共通して連結されて第2インバータを構成することを特徴とする請求項55に記載の半導体メモリ装置の製造方法。

#### 【請求項58】

前記第1アクセス素子を、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結させる第1金属配線；前記第2アクセス素子を、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結させる第2金属配線；を形成する段階をさらに含むことを特徴とする請求項57に記載の半導体メモリ装置の製造方法。

#### 【請求項59】

第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板を含み、

前記第1ウェル領域は、第1積層構造を含み、前記第1積層構造は、第1単一活性層上に連続して積層された第1コントラクトプラグ、第1金属絶縁層、ビアプラグ、及び電源電圧または接地電圧ラインを含み、

前記第2ウェル領域は、第2積層構造を含み、前記第2積層構造は、第2単一活性層上に連続して積層された第2コントラクトプラグ及び第2金属絶縁層を含み、

前記第3ウェル領域は、第3積層構造を含み、前記第3積層構造は、第3単一活性層上に連続して積層された第3コントラクトプラグ及び第3金属絶縁層を含むことを特徴とする半導体メモリ装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置に係り、さらに詳細には、半導体メモリ装置及び該半導体メモリ装置の製造方法に関する。

##### 【背景技術】

##### 【0002】

半導体メモリ素子は、記憶方式によって、DRAM(dynamic random-access memory)、SRAM(static random access memory)のような揮発性メモリと、フラッシュメモリのような不揮発性メモリ(non volatile memory)とに分類される。このうち、SRAMは、高速特性、低電力消耗特性及び単純な動作方式などの長所を有する。また、SRAMは、DRAMと異なり、保存された情報を定期的にリフレッシュ(refresh)する必要がないために、設計が容易である。

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0003】

本発明の技術的的思想が解決しようとする課題は、2つのプルアップ(pull-up)素子を形成するための活性領域を一つに併合することによって、半導体メモリ装置の集積

度を向上させることができる半導体メモリ装置及びその製造方法を提供するところにある。

#### 【0004】

また、本発明の技術的思想が解決しようとする他の課題は、2つのプルダウン（pull-down）素子を形成するための活性領域を一つに併合することによって、半導体メモリ装置の集積度を向上させることができる半導体メモリ装置及びその製造方法を提供するところにある。

#### 【課題を解決するための手段】

#### 【0005】

前記課題を解決するための本発明の技術的思想による半導体メモリ装置は、第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板；前記第1ウェル領域に一列に形成されて、電源端子を共有する第1プルアップ素子及び第2プルアップ素子；前記第2ウェル領域に、前記第1プルアップ素子と隣接するように配される第1プルダウン素子；前記第3ウェル領域に、前記第2プルアップ素子と隣接するように配される第2プルダウン素子；前記第2ウェル領域に、前記第2プルアップ素子と隣接するように配される第1アクセス素子；前記第3ウェル領域に、前記第1プルアップ素子と隣接するように配される第2アクセス素子；を含む。

10

#### 【0006】

一部の実施形態において、前記第1プルアップ素子及び第2プルアップ素子は、単一活性領域に配され、前記単一活性領域は、前記第1ウェル領域に含まれうる。

20

#### 【0007】

一部の実施形態において、前記第1プルアップ素子及び前記第1プルダウン素子は、第1インバータを構成し、前記第2プルアップ素子及び前記第2プルダウン素子は、第2インバータを構成できる。

30

#### 【0008】

一部の実施形態において、前記第1アクセス素子は、前記第2インバータの入力端子と、前記第1インバータの出力端子とに連結され、前記第2アクセス素子は、前記第1インバータの入力端子と、前記第2インバータの出力端子とに連結されうる。

#### 【0009】

一部の実施形態において、前記第1アクセス素子は、ワードラインに印加される電圧によって制御され、1対のビットラインのうち第1ビットラインを、前記第2インバータの入力端子と、前記第1インバータの出力端子とに連結させる第1アクセス・トランジスタを含むことができる。一部の実施形態において、前記第2アクセス素子は、前記ワードラインに印加される電圧によって制御され、前記1対のビットラインのうち第2ビットラインを、前記第1インバータの入力端子と、前記第2インバータの出力端子とに連結させる第2アクセス・トランジスタを含むことができる。

#### 【0010】

一部の実施形態において、前記第1アクセス素子及び前記第1プルダウン素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第2ウェル領域に含まれうる。

40

#### 【0011】

一部の実施形態において、前記第2アクセス素子及び前記第2プルダウン素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第3ウェル領域に含まれうる。

#### 【0012】

一部の実施形態において、前記第1タイプ導電体は、N型導電体であって、前記第2タイプ導電体は、P型導電体でありうる。

#### 【0013】

一部の実施形態において、前記第1プルアップ素子は、前記電源端子に連結されるソースを有するPチャネル・トランジスタを含み、前記第1プルダウン素子は、前記Pチャネ

50

ル・トランジスタのドレインに連結されるドレイン、前記Pチャネル・トランジスタのゲートに連結されるゲート、及び接地端子に連結されるソースを有するNチャネル・トランジスタを含むことができる。

【0014】

一部の実施形態において、前記第2プルアップ素子は、前記電源端子に連結されるソースを有するPチャネル・トランジスタを含み、前記第2プルダウン素子は、前記Pチャネル・トランジスタのドレインに連結されるドレイン、前記Pチャネル・トランジスタのゲートに連結されるゲート、及び接地端子に連結されるソースを有するNチャネル・トランジスタを含むことができる。

【0015】

一部の実施形態において、前記第1アクセス素子は、ワードラインに連結されるゲートを有するNチャネル・トランジスタを含み、前記第2アクセス素子は、前記ワードラインに連結されるゲートを有するNチャネル・トランジスタを含むことができる。

【0016】

一部の実施形態において、前記半導体メモリ装置は、電子システムに含まれ、前記電子システムは、バスを介して互いに通信するメモリ部、プロセッサ及び入出力装置を含み、前記プロセッサは、前記半導体メモリ装置を含む記憶装置を含むことができる。

【0017】

また、前記課題を解決するための本発明の技術的思想による半導体メモリ装置は、第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板；前記第1ウェル領域に含まれ、第1プルアップ素子及び第2プルアップ素子が一列に配される第1活性領域；前記第2ウェル領域に含まれ、前記第2プルアップ素子に隣接した第1アクセス素子と、前記第1プルアップ素子に隣接した第1プルダウン素子とが配される第2活性領域；前記第3ウェル領域に含まれ、前記第1プルアップ素子に隣接した第2アクセス素子と、前記第2プルアップ素子に隣接した第2プルダウン素子とが配される第3活性領域；を含む。

【0018】

一部の実施形態において、前記第1プルアップ素子及び第2プルアップ素子は、第1方向に沿って一列に配され、前記第1プルアップ素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルダウン素子及び前記第2アクセス素子と隣接するように配され、前記第2プルアップ素子は、前記第2方向に沿って、前記第2プルダウン素子及び前記第1アクセス素子と隣接するように配されうる。

【0019】

一部の実施形態において、前記半導体メモリ装置は、前記第1活性領域及び第2活性領域の上部を横切る方向に、前記基板の上部に形成される第1ゲート電極；前記第1活性領域及び第3活性領域の上部を横切る方向に、前記基板の上部に形成される第2ゲート電極をさらに含み、前記第1プルアップ素子と前記第1プルダウン素子は、前記第1ゲート電極に共通して連結されて第1インバータを構成し、前記第2プルアップ素子と前記第2プルダウン素子は、前記第2ゲート電極に共通して連結されて第2インバータを構成できる。

【0020】

一部の実施形態において、前記半導体メモリ装置は、前記第1アクセス素子を、前記第2インバータの入力端子と、前記第1インバータの出力端子とに連結させる第1金属配線；前記第2アクセス素子を、前記第1インバータの入力端子と、前記第2インバータの出力端子とに連結させる第2金属配線；をさらに含むことができる。

【0021】

一部の実施形態において、前記第1金属配線及び前記第2金属配線は、同一層に配されうる。一部の実施形態において、前記第1金属配線及び前記第2金属配線は、互いに異なる

10

20

30

40

50

る層に配されうる。

【0022】

一部の実施形態において、前記半導体メモリ装置は、前記第2活性領域の上部を横切る方向に、前記基板の上部に形成される第3ゲート電極と、前記第3活性領域の上部を横切る方向に、前記基板の上部に形成される第4ゲート電極と、をさらに含むことができる。一部の実施形態において、前記半導体メモリ装置は、前記第3ゲート電極及び第4ゲート電極と平行な方向に伸張するように、前記基板の上部に形成され、前記第3ゲート電極及び第4ゲート電極に連結されるワードラインをさらに含むことができる。

【0023】

一部の実施形態において、前記半導体メモリ装置は、前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される1対のビットラインをさらに含み、前記1対のビットラインのうち第1ビットラインは、前記第1アクセス素子に連結され、前記1対のビットラインのうち第2ビットラインは、前記第2アクセス素子に連結されうる。

10

【0024】

一部の実施形態において、前記半導体メモリ装置は、前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される電源電極ラインをさらに含み、前記電源電極ラインは、前記第1プルアップ素子と第2プルアップ素子との間に形成されたコンタクトプラグを介して、前記第1プルアップ素子及び第2プルアップ素子に連結されうる。

20

【0025】

一部の実施形態において、前記第1タイプ導電体は、N型導電体であって、前記第2タイプ導電体は、P型導電体でありうる。

【0026】

また、前記課題を解決するための本発明の技術的思想による半導体メモリ装置の製造方法は、第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板を提供する段階であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む段階と、前記第1ウェル領域上に含まれた第1活性領域に、第1プルアップ素子及び第2プルアップ素子を一列に形成する段階と、前記第2ウェル領域上に含まれた第2活性領域に、前記第1プルアップ素子と隣接した第1プルダウン素子と、前記第2プルアップ素子と隣接した第1アクセス素子とを形成する段階と、前記第3ウェル領域上に含まれた第3活性領域に、前記第2プルアップ素子と隣接した第2プルダウン素子と、前記第1プルアップ素子と隣接した第2アクセス素子とを形成する段階と、を含む。

30

【0027】

一部の実施形態において、前記第1プルアップ素子及び第2プルアップ素子は、第1方向に沿って一列に形成され、前記第1プルアップ素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルダウン素子及び前記第2アクセス素子と隣接するように配され、前記第2プルアップ素子は、前記第2方向に沿って、前記第2プルダウン素子及び前記第1アクセス素子と隣接するように配されうる。

40

【0028】

一部の実施形態において、前記製造方法は、前記第1活性領域、第2活性領域及び第3活性領域のうち少なくとも1つの領域の上部を横切る方向に、前記基板の上部に形成される複数の導電性パターンを形成する段階をさらに含み、前記第1プルアップ素子と前記第1プルダウン素子は、前記複数の導電性パターンのうち一つに共通して連結されて第1インバータを構成し、前記第2プルアップ素子と前記第2プルダウン素子は、前記複数の導電性パターンのうち他の一つに共通して連結されて第2インバータを構成できる。

【0029】

一部の実施形態において、前記製造方法は、前記第1アクセス素子を、前記第2インバ

50

ータの入力端子と、前記第1インバータの出力端子とに連結させる第1金属配線；前記第2アクセス素子を、前記第1インバータの入力端子と、前記第2インバータの出力端子とに連結させる第2金属配線；を形成する段階をさらに含むことができる。

#### 【0030】

一部の実施形態において、前記第1金属配線及び第2金属配線を形成する段階は、前記基板の上部に第1絶縁膜を形成する段階と、前記第1絶縁膜の一部領域をエッティングして複数の第1コントラクトホールを形成し、前記複数の第1コントラクトホールに金属を充填して複数のコントラクトプラグを形成する段階と、前記複数のコントラクトプラグが形成された前記第1絶縁膜上に第2絶縁膜を形成する段階と、前記第2絶縁膜の一部領域をエッティングして複数の第2コントラクトホールを形成し、前記複数の第2コントラクトホールに金属を充填し、前記第1金属配線及び第2金属配線を形成する段階と、を含み、前記第1金属配線及び第2金属配線は、前記複数のコントラクトプラグを介して、前記第1ウェル領域、第2ウェル領域及び第3ウェル領域のうち少なくとも一つに連結されうる。10

#### 【0031】

一部の実施形態において、前記製造方法は、前記第1ウェル領域、第2ウェル領域及び第3ウェル領域のうち少なくとも一つにシリサイド層を形成する段階をさらに含み、前記複数のコントラクトプラグは、前記シリサイド層に連結されうる。

#### 【0032】

また、前記他の課題を解決するための本技術的思想による半導体メモリ装置は、第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板；前記第1ウェル領域に一列に形成されて接地端子を共有する第1プルダウン素子及び第2プルダウン素子；前記第2ウェル領域に、前記第1プルダウン素子と隣接するように配される第1プルアップ素子；前記第3ウェル領域に、前記第2プルダウン素子と隣接するように配される第2プルアップ素子；前記第2ウェル領域に、前記第2プルダウン素子と隣接するように配される第1アクセス素子；前記第3ウェル領域に、前記第1プルダウン素子と隣接するように配される第2アクセス素子；を含む。20

#### 【0033】

一部の実施形態において、前記第1プルダウン素子及び第2プルダウン素子は、単一活性領域に配され、前記単一活性領域は、前記第1ウェル領域に含まれうる。30

#### 【0034】

一部の実施形態において、前記第1プルダウン素子及び前記第1プルアップ素子は、第1インバータを構成し、前記第2プルダウン素子及び前記第2プルアップ素子は、第2インバータを構成できる。

#### 【0035】

一部の実施形態において、前記第1アクセス素子は、前記第2インバータの入力端子と、前記第1インバータの出力端子とに連結され、前記第2アクセス素子は、前記第1インバータの入力端子と、前記第2インバータの出力端子とに連結されうる。

#### 【0036】

一部の実施形態において、前記第1アクセス素子は、ワードラインに印加される電圧によって制御され、1対のビットラインのうち第1ビットラインを、前記第2インバータの入力端子と、前記第1インバータの出力端子とに連結させる第1アクセス・トランジスタを含むことができる。40

#### 【0037】

一部の実施形態において、前記第2アクセス素子は、前記ワードラインに印加される電圧によって制御され、前記1対のビットラインのうち第2ビットラインを、前記第1インバータの入力端子と、前記第2インバータの出力端子とに連結させる第2アクセス・トランジスタを含むことができる。

#### 【0038】

一部の実施形態において、前記第1アクセス素子及び前記第1プルアップ素子は、单一活性領域内に一列に配され、前記单一活性領域は、前記第2ウェル領域に含まれうる。

**【0039】**

一部の実施形態において、前記第2アクセス素子及び前記第2プルアップ素子は、单一活性領域内に一列に配され、前記单一活性領域は、前記第2ウェル領域に含まれうる。

**【0040】**

一部の実施形態において、前記第1タイプ導電体は、P型導電体であって、前記第2タイプ導電体は、N型導電体でありうる。

**【0041】**

一部の実施形態において、前記第1プルダウン素子は、前記接地端子に連結されるソースを有するNチャネル・トランジスタを含み、前記第1プルアップ素子は、前記Nチャネル・トランジスタのドレインに連結されるドレイン、前記Nチャネル・トランジスタのゲートに連結されるゲート、及び電源端子に連結されるソースを有するPチャネル・トランジスタを含むことができる。10

**【0042】**

一部の実施形態において、前記第2プルダウン素子は、前記接地端子に連結されるソースを有するNチャネル・トランジスタを含み、前記第2プルアップ素子は、前記Nチャネル・トランジスタのドレインに連結されるドレイン、前記Nチャネル・トランジスタのゲートに連結されるゲート、及び電源端子に連結されるソースを有するPチャネル・トランジスタを含むことができる。20

**【0043】**

一部の実施形態において、前記第1アクセス素子は、ワードラインに連結されるゲートを有するPチャネル・トランジスタを含み、前記第2アクセス素子は、前記ワードラインに連結されるゲートを有するPチャネル・トランジスタを含むことができる。

**【0044】**

一部の実施形態において、前記半導体メモリ装置は、電子システムに含まれ、前記電子システムは、バスを介して互いに通信するメモリ部、プロセッサ及び入出力装置を含み、前記プロセッサは、前記半導体メモリ装置を含む記憶装置を含むことができる。

**【0045】**

また、前記他の課題を解決するための本発明の技術的思想による半導体装置の製造方法は、第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板；前記第1ウェル領域に含まれ、第1プルダウン素子及び第2プルダウン素子が一列に配される第1活性領域；前記第2ウェル領域に含まれ、前記第2プルダウン素子に隣接した第1アクセス素子と、前記第1プルダウン素子に隣接した第1プルアップ素子とが配される第2活性領域；前記第3ウェル領域に含まれ、前記第1プルダウン素子に隣接した第2アクセス素子と、前記第2プルダウン素子に隣接した第2プルアップ素子とが配される第3活性領域；を含む。30

**【0046】**

一部の実施形態において、前記第1プルダウン素子及び第2プルダウン素子は、第1方向に沿って一列に配され、前記第1プルダウン素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルアップ素子及び前記第2アクセス素子と隣接するように配され、前記第2プルダウン素子は、前記第2方向に沿って、前記第2プルアップ素子及び前記第1アクセス素子と隣接するように配されうる。40

**【0047】**

一部の実施形態において、前記半導体メモリ装置は、前記第1活性領域及び第2活性領域の上部を横切る方向に、前記基板の上部に形成される第1ゲート電極と、前記第1活性領域及び第3活性領域の上部を横切る方向に、前記基板の上部に形成される第2ゲート電極と、をさらに含み、前記第1プルダウン素子と前記第1プルアップ素子は、前記第1ゲ50

ート電極に共通して連結されて第1インバータを構成し、前記第2プルダウン素子と前記第2プルアップ素子は、前記第2ゲート電極に共通して連結されて第2インバータを構成できる。

#### 【0048】

一部の実施形態において、前記半導体メモリ装置は、前記第1アクセス素子を、前記第2インバータの入力端子と、前記第1インバータの出力端子とに連結させる第1金属配線；前記第2アクセス素子を、前記第1インバータの入力端子と、前記第2インバータの出力端子とに連結させる第2金属配線；をさらに含むことができる。

#### 【0049】

一部の実施形態において、前記第1金属配線及び前記第2金属配線は、同一層に配される。一部の実施形態において、前記第1金属配線及び前記第2金属配線は、互いに異なる層に配される。

#### 【0050】

一部の実施形態において、前記半導体メモリ装置は、前記第2活性領域の上部を横切る方向に、前記基板の上部に形成される第3ゲート電極と、前記第3活性領域の上部を横切る方向に、前記基板の上部に形成される第4ゲート電極と、をさらに含むことができる。一部の実施形態において、前記半導体メモリ装置は、前記第3ゲート電極及び第4ゲート電極と平行な方向に伸張するように、前記基板の上部に形成され、前記第3ゲート電極及び第4ゲート電極に連結されるワードラインをさらに含むことができる。

#### 【0051】

一部の実施形態において、前記半導体メモリ装置は、前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される1対のビットラインをさらに含み、前記1対のビットラインのうち第1ビットラインは、前記第1アクセス素子の一端に連結され、前記1対のビットラインのうち第2ビットラインは、前記第2アクセス素子の他端に連結されうる。

#### 【0052】

一部の実施形態において、前記半導体メモリ装置は、前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される接地電極ラインをさらに含み、前記接地電極ラインは、前記第1プルダウン素子と第2プルダウン素子との間に形成されたコントакトプラグを介して、前記第1プルダウン素子及び第2プルダウン素子に連結されうる。

#### 【0053】

一部の実施形態において、前記第1タイプ導電体は、P型導電体であって、前記第2タイプ導電体は、N型導電体でありうる。

#### 【0054】

また、前記他の課題を解決するための本発明の技術的思想による半導体メモリ装置の製造方法は、第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板を提供する段階であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む段階と、前記第1ウェル領域上に含まれた第1活性領域に、第1プルダウン素子及び第2プルダウン素子を一列に形成する段階と、前記第2ウェル領域上に含まれた第2活性領域に、前記第1プルダウン素子と隣接した第1プルアップ素子と、前記第2プルダウン素子と隣接した第1アクセス素子とを形成する段階と、前記第3ウェル領域上に含まれた第3活性領域に、前記第2プルダウン素子と隣接した第2プルアップ素子と、前記第1プルダウン素子と隣接した第2アクセス素子とを形成する段階を含む。

#### 【0055】

一部の実施形態において、前記第1プルダウン素子及び第2プルダウン素子は、第1方向に沿って一列に形成され、前記第1プルダウン素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルアップ素子及び前記第2アクセス素子と隣接するように配さ

10

20

30

40

50

れ、前記第2プルダウン素子は、前記第2方向に沿って、前記第2プルアップ素子及び前記第1アクセス素子と隣接するように配されうる。

【0056】

一部の実施形態において、前記製造方法は、前記第1活性領域、第2活性領域及び第3活性領域のうち少なくとも1つの領域の上部を横切る方向に、前記基板の上部に形成される複数の導電性パターンを形成する段階をさらに含み、前記第1プルダウン素子と前記第1プルアップ素子は、前記複数の導電性パターンのうち一つに共通して連結されて第1インバータを構成し、前記第2プルダウン素子と前記第2プルアップ素子は、前記複数の導電性パターンのうち他の一つに共通して連結されて第2インバータを構成できる。

【0057】

一部の実施形態において、前記製造方法は、前記第1アクセス素子を、前記第2インバータの入力端子と、前記第1インバータの出力端子とに連結させる第1金属配線；前記第2アクセス素子を、前記第1インバータの入力端子と、前記第2インバータの出力端子とに連結させる第2金属配線；を形成する段階をさらに含むことができる。

【0058】

また、前記課題を解決するための本発明の技術的思想による半導体メモリ装置は、第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板を含み、前記第1ウェル領域は、第1積層構造を含み、前記第1積層構造は、第1単一活性層上に連続して積層された第1コントラクトプラグ、第1金属絶縁層、ビアプラグ、及び電源電圧または接地電圧ラインを含み、前記第2ウェル領域は、第2積層構造を含み、前記第2積層構造は、第2単一活性層上に連続して積層された第2コントラクトプラグ及び第2金属絶縁層を含み、前記第3ウェル領域は、第3積層構造を含み、前記第3積層構造は、第3単一活性層上に連続して積層された第3コントラクトプラグ及び第3金属絶縁層を含む。

10

20

20

【図面の簡単な説明】

【0059】

【図1】本発明の一実施形態による半導体メモリ装置を示すレイアウトである。

30

【図2】図1の半導体メモリ装置の金属配線層を示すレイアウトである。

【図3】図1の半導体メモリ装置のビットライン配線層を示すレイアウトである。

【図4】図1の半導体メモリ装置のワードライン配線層を示すレイアウトである。

【図5】図1の半導体メモリ装置の等価回路を示す回路図である。

【図6】図1の半導体メモリ装置のI-I'線に沿って切り取った断面図である。

【図7】図1の半導体メモリ装置のII-II'線に沿って切り取った断面図である。

40

【図8A】本発明の一実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図8B】本発明の一実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図8C】本発明の一実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図8D】本発明の一実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図8E】本発明の一実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図8F】本発明の一実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図8G】本発明の一実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図9】本発明の他の実施形態による半導体メモリ装置を示すレイアウトである。

【図10】図9の半導体メモリ装置の等価回路を示す回路図である。

【図11】本発明のさらに他の実施形態による半導体メモリ装置を示すレイアウトである。

【図12】図11の半導体メモリ装置の金属配線層を示すレイアウトである。

【図13】図11の半導体メモリ装置のビットライン配線層を示すレイアウトである。

【図14】図11の半導体メモリ装置のワードライン配線層を示すレイアウトである。

【図15】図11の半導体メモリ装置の等価回路を示す回路図である。

50

【図16】図11の半導体メモリ装置のI—I—I'—I—I'I'線に沿って切り取った断面図である。

【図17】図11の半導体メモリ装置のIV—IV'線に沿って切り取った断面図である。

【図18A】本発明の他の実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図18B】本発明の他の実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図18C】本発明の他の実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図18D】本発明の他の実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図18E】本発明の他の実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図18F】本発明の他の実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図18G】本発明の他の実施形態による半導体メモリ装置の製造方法を示す断面図である。

【図19】本発明のさらに他の実施形態による半導体メモリ装置を示すレイアウトである。

【図20】図19の半導体メモリ装置の等価回路を示す回路図である。

【図21】本発明の一実施形態による半導体メモリ装置の製造方法を示すフローチャートである。

【図22】本発明の他の実施形態による半導体メモリ装置の製造方法を示すフローチャートである。

【図23】本発明の一実施形態による電子システムの構成を概略的に示すプロック図である。

#### 【発明を実施するための形態】

##### 【0060】

以下、添付された図面を参照しつつ、本発明の望ましい実施形態について詳細に説明する。

##### 【0061】

本発明の実施形態は、当技術分野における当業者に対して、本発明についてさらに完全に説明するために提供されるものであり、下記実施形態は、さまざまな他の形態に変形され、本発明の範囲が、下記実施形態に限定されるものではない。むしろ、それら実施形態は、本開示をさらに充実させて完全なものにし、当業者に、本発明の思想を完全に伝達するために提供されるものである。

##### 【0062】

以下の説明で、ある層が他の層の上に存在すると記述されるとき、それは、他層のすぐ上に存在することもあり、その間に第3の層が介在することもある。また図面で、各層の厚みや大きさは、説明の便宜性及び明確性のために誇張されており、図面上で同一符号は、同じ要素を指す。本明細書で使われているように、用語「及び／または」は、列挙された当該項目のうちいずれか一つ、あるいは一つ以上のあらゆる組み合わせを含む。

##### 【0063】

本明細書で使われた用語は、特定実施形態を説明するために使われ、本発明を制限するためのものではない。本明細書で使われているように、単数形態は、文脈上他の場合を明確に指すものではないならば、複数の形態を含むことができる。また、本明細書で使われる場合、「含む（comprise）」及び／または「含むところの（comprising）」は、言及した形状、数字、段階、動作、部材、要素及び／またはそれらグループの存在を特定するものであり、一つ以上の他の形状、数字、動作、部材、要素及び／またはグループの存在または付加を排除するものではない。

10

20

30

40

50

**【 0 0 6 4 】**

本明細書で、第1，第2のような用語が多様な部材、部品、領域、層及び／または部分を説明するために使われるが、それら部材、部品、領域、層及び／または部分は、それら用語によって限定されるものではないことは自明である。それら用語は、1つの部材、部品、領域、層または部分を、他の領域、層または部分と区別するためにのみ使われる。従って、以下で説明する第1部材、部品、領域、層または部分は、本発明の開示から外れずに、第2部材、部品、領域、層または部分を指すことができる。

**【 0 0 6 5 】**

以下、本発明の実施形態は、本発明の理想的な実施形態を概略的に図示する図面を参照しつつ説明する。図面において、例えば、製造技術及び／または公差(tolerance)によって、図示された形状の変形が予想されうる。従って、本発明の実施形態は、本明細書に図示された特定形状に制限されるものであると解釈されるものではなく、例えば、製造上予測されうる形状の変化を含んでいるものである。また、添付された図面で、同じ参照符号は、同じ構成部材を指す。

10

**【 0 0 6 6 】**

以下、本発明による半導体メモリ装置は、SRAM(static random access memory)を一例として説明する。しかし、本発明は、これに限定されるものではなく、2つのインバータ素子を含む半導体メモリ装置に適用されうる。

**【 0 0 6 7 】**

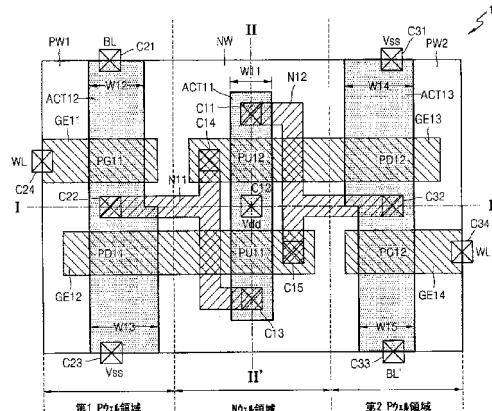

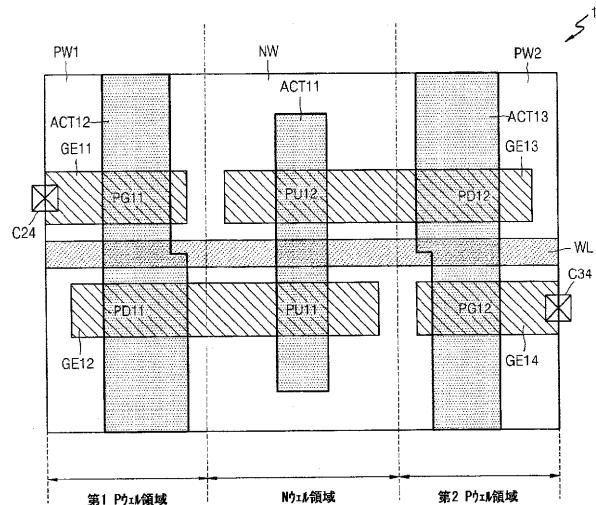

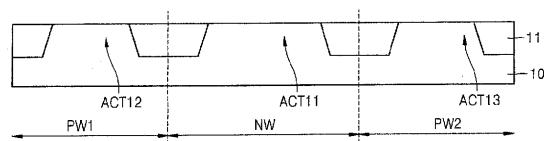

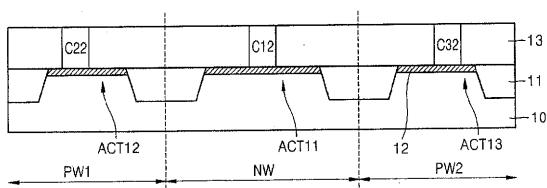

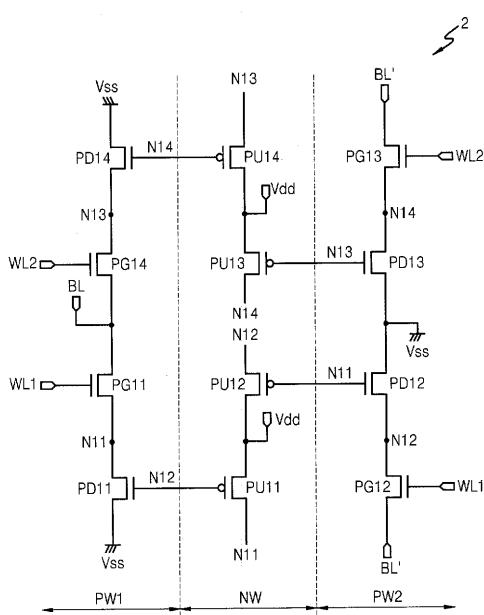

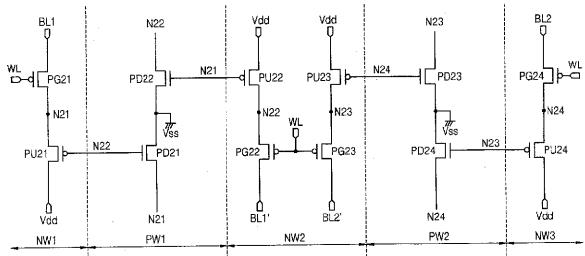

図1は、本発明の一実施形態による半導体メモリ装置を示すレイアウトである。

20

**【 0 0 6 8 】**

図1を参照すれば、半導体メモリ装置1は、第1ウェル領域NW、及び第1ウェル領域NWの両脇に形成される第2ウェル領域PW1及び第3ウェル領域PW2を有する基板上に形成される1つのSRAMセルを含み、1ビットで動作しうる。このとき、第1ウェル領域NWは、第1導電型( conductive type)であり、第2ウェル領域PW1及び第3ウェル領域PW2は、第2導電型を有することができる。本実施形態で、第1導電型はN型であり、第2導電型はP型でありうる。以下、第1ウェル領域は、Nウェル領域NWであり、第2ウェル領域は、第1Pウェル領域PW1であり、第3ウェル領域は、第2Pウェル領域PW2とする。

30

**【 0 0 6 9 】**

Nウェル領域NWは、例えば、イオン注入工程によって基板上に形成されるN型ウェルが配される領域であり、Nウェル領域NWには、素子分離膜によって画定される第1活性(active)領域ACT11が配される。本実施形態で、第1活性領域ACT11は、縦方向に長い形態を有するバー(bar)タイプの単一活性領域でありうる。このとき、第1活性領域ACT11に、P+型不純物をドーピングすることによって、P型拡散領域が形成され、また、第1コンタクトプラグC11、第2コンタクトプラグC12及び第3コンタクトプラグC13が形成されうる。第1活性領域ACT11には、2つのプルアップ(pull-up)素子が一列に形成されうるが、本実施形態で、2つのプルアップ素子は、第1PMOSトランジスタP乌11及び第2PMOSトランジスタP乌12でありうる。

40

**【 0 0 7 0 】**

このように、2つのプルアップ素子、すなわち、第1PMOSトランジスタP乌11及び第2PMOSトランジスタP乌12を、単一活性領域である第1活性領域ACT11に配することによって、第1PMOSトランジスタP乌11と、第2PMOSトランジスタP乌12とのミスマッチ(mismatch)を低減させることができる。具体的には、第1PMOSトランジスタP乌11に係わるスレショルド電圧と、第2PMOSトランジスタP乌12に係わるスレショルド電圧との差を減らすことができる。

**【 0 0 7 1 】**

第1Pウェル領域PW1は、例えば、イオン注入工程によって基板上に形成されるP型ウェルが配される領域であり、第1Pウェル領域PW1には、素子分離膜によって画定さ

50

れる第2活性領域ACT12が配される。本実施形態で、第2活性領域ACT12は、第1活性領域ACT11に平行した方向に伸張する形態を有する単一活性領域でありうる。このとき、第2活性領域ACT12に、N+型不純物をドーピングすることによって、N型拡散領域が形成され、また、第4コンタクトプラグC21，第5コンタクトプラグC22及び第6コンタクトプラグC23が形成されうる。第2活性領域ACT12には、1つのプルダウン(pull-down)素子と1つのアクセス素子とが形成されうるが、本実施形態でプルダウン素子は、第1NMOSトランジスタPD11であり、アクセス素子は、第3NMOSトランジスタPG11でありうる。

#### 【0072】

第2Pウェル領域PW2は、例えは、イオン注入工程によって基板上に形成されるP型ウェルが配される領域であり、第2Pウェル領域PW2には、素子分離膜によって画定される第3活性領域ACT13が配される。本実施形態で、第3活性領域ACT13は、第1活性領域ACT11に平行した方向に伸張する形態を有する単一活性領域でありうる。このとき、第3活性領域ACT13に、N+型不純物をドーピングすることによって、N型拡散領域が形成され、また、第7コンタクトプラグC31，第8コンタクトプラグC32及び第9コンタクトプラグC33が形成されうる。第3活性領域ACT13には、1つのプルダウン素子と1つのアクセス素子とが形成されうるが、本実施形態でプルダウン素子は、第2NMOSトランジスタPD12であり、アクセス素子は、第4NMOSトランジスタPG12でありうる。

#### 【0073】

第1活性領域ACT11，第2活性領域ACT12及び第3活性領域ACT13の幅を比較すれば、次の通りである。第1活性領域ACT11の第1幅W11は、その位置に関係せずに一定の値を有することができる。第2活性領域ACT12の幅は、その位置によって互いに異なりうるが、具体的には、第1NMOSトランジスタPD11が配される領域の第3幅W13は、第3NMOSトランジスタPG11が配される領域の第2幅W12より広く、第2幅W12及び第3幅W13は、第1幅W11より広い。第3活性領域ACT13の幅は、その位置によって互いに異なりうるが、具体的には、第2NMOSトランジスタPD12が配される領域の第4幅W14は、第4NMOSトランジスタPG12が配される領域の第5幅W15より広く、第4幅W14及び第5幅W15は、第1幅W11より広い。また、第4幅W14は、第3幅W13と実質的に同一であり、第5幅W15は、第2幅W12と実質的に同一でありうる。

#### 【0074】

このように、第1NMOSトランジスタPD11及び第2NMOSトランジスタPD12が形成される第2活性領域ACT12及び第3活性領域ACT13の幅W13，W14を最も大きく具現することによって、第1NMOSトランジスタPD11及び第2NMOSトランジスタPD12で、プルダウン動作を行う場合、プルダウン動作の速度を向上させることができる。また、第3NMOSトランジスタPG11及び第4NMOSトランジスタPG12が形成される第2活性領域ACT12及び第3活性領域ACT13の幅W12，W15を、第1PMOSトランジスタPU11及び第2PMOSトランジスタPU12が形成される第1活性領域ACT11の幅W11より広く具現することによって、半導体メモリ装置1に対する書き込み動作を行う場合、書き込み動作の速度を向上させることができる。

#### 【0075】

第1活性領域ACT11，第2活性領域ACT12及び第3活性領域ACT13が配された基板の上部には、第1ゲート電極ないし第4ゲート電極GE11，GE12，GE13，GE14が形成される。具体的には、第1ゲート電極GE11は、第2活性領域ACT12を横切る方向に形成され、第2ゲート電極GE12は、第1活性領域ACT11及び第2活性領域ACT12を横切る方向に形成され、第3ゲート電極GE13は、第1活性領域ACT11及び第3活性領域ACT13を横切る方向に形成され、第4ゲート電極GE14は、第3活性領域ACT13を横切る方向に形成される。このとき、第1ゲート

10

20

30

40

50

電極 G E 1 1 及び第 4 ゲート電極 G E 1 4 の上部には、それぞれワードライン・コンタクトプラグ C 2 4 , C 3 4 が形成され、第 2 ゲート電極 G E 1 2 及び第 3 ゲート電極 G E 1 3 の上部には、それぞれ配線コンタクトプラグ C 1 5 , C 1 4 が形成される。例えば、第 1 ゲート電極ないし第 4 ゲート電極 G E 1 1 , G E 1 2 , G E 1 3 , G E 1 4 は、ポリシリコン層でありうる。

#### 【 0 0 7 6 】

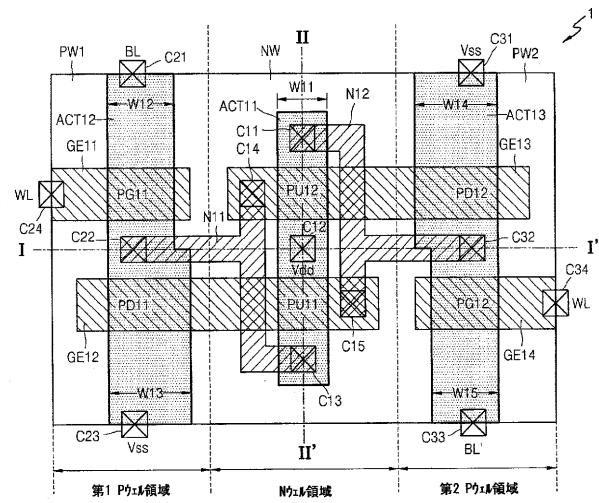

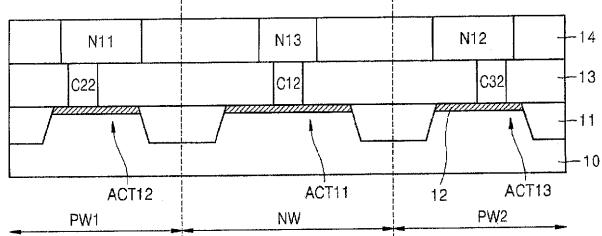

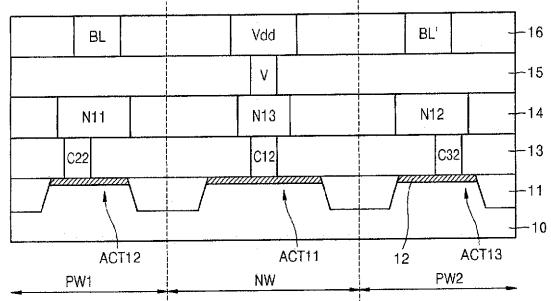

図 2 は、図 1 の半導体メモリ装置の金属配線層を示すレイアウトである。

#### 【 0 0 7 7 】

図 2 を参照すれば、第 1 ゲート電極ないし第 4 ゲート電極 G E 1 1 , G E 1 2 , G E 1 3 , G E 1 4 が形成された基板の上部には、第 1 金属配線 N 1 1 及び第 2 金属配線 N 1 2 が形成される。このとき、第 1 金属配線 N 1 1 は、第 1 活性領域 A C T 1 1 に形成された第 3 コンタクトプラグ C 1 3 、第 2 活性領域 A C T 1 2 に形成された第 5 コンタクトプラグ C 2 2 、及び第 3 ゲート電極 G E 1 3 に形成された配線コンタクトプラグ C 1 4 を連結させる。また、第 2 金属配線 N 1 2 は、第 1 活性領域 A C T 1 1 に形成された第 1 コンタクトプラグ C 1 1 、第 3 活性領域 A C T 1 3 に形成された第 8 コンタクトプラグ C 3 2 、及び第 2 ゲート電極 G E 1 2 に形成された配線コンタクトプラグ C 1 5 を連結させる。例えば、第 1 金属配線 N 1 1 及び第 2 金属配線 N 1 2 は、タンゲステン (W) 、アルミニウム (A l ) 、銅 (C u ) 、モリブデン (M o ) 、チタン (T i ) 、タンタル (T a ) 、ルテニウム (R u ) 、またはそれらの合金を含む金属層、またはポリシリコン層でありうる。

10

#### 【 0 0 7 8 】

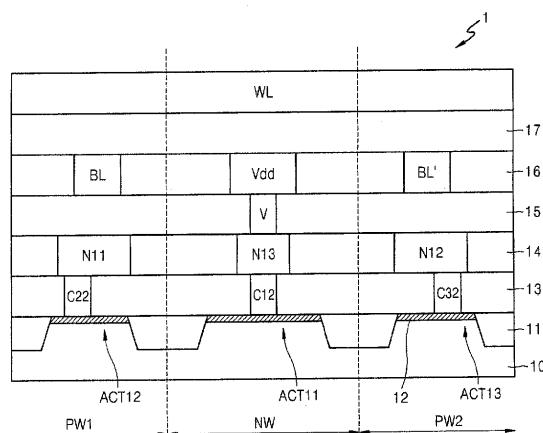

図 3 は、図 1 の半導体メモリ装置のビットライン配線層を示すレイアウトである。

#### 【 0 0 7 9 】

図 3 を参照すれば、第 1 金属配線 N 1 1 及び第 2 金属配線 N 1 2 が形成された基板の上部には、1 対のビットライン、すなわち、ビットライン B L 及びビットラインバー B L ' が形成される。ビットライン B L 及びビットラインバー B L ' は、第 1 活性領域 A C T 1 1 , 第 2 活性領域 A C T 1 2 及び第 3 活性領域 A C T 1 3 と平行な方向に伸張しうる。このとき、ビットライン B L は、第 2 活性領域 A C T 1 2 に形成された第 4 コンタクトプラグ C 2 1 を介して、第 2 活性領域 A C T 1 2 に連結され、ビットラインバー B L ' は、第 3 活性領域 A C T 1 3 に形成された第 9 コンタクトプラグ C 3 3 を介して、第 3 活性領域 A C T 1 3 に連結される。

20

30

#### 【 0 0 8 0 】

また、第 1 金属配線 N 1 1 及び第 2 金属配線 N 1 2 が形成された基板の上部には、電源電極ライン V d d が形成される。電源電極ライン V d d は、1 対のビットライン B L , B L ' 間に形成され、1 対のビットライン B L , B L ' と平行な方向に伸張しうる。このとき、電源電極ライン V d d は、第 1 活性領域 A C T 1 1 に形成された第 2 コンタクトプラグ C 1 2 を介して、第 1 活性領域 A C T 1 1 に連結される。

40

#### 【 0 0 8 1 】

図 4 は、図 1 の半導体メモリ装置のワードライン配線を示すレイアウトである。

#### 【 0 0 8 2 】

図 4 を参照すれば、1 対のビットライン B L , B L ' が形成された基板の上部には、ワードライン W L が形成される。ワードライン W L は、第 1 ゲート電極ないし第 4 ゲート電極 G E 1 1 , G E 1 2 , G E 1 3 , G E 1 4 と平行な方向に伸張しうる。このとき、ワードライン W L は、ワードライン・コンタクトプラグ C 2 4 , C 3 4 を介して、第 1 ゲート電極 G E 1 1 及び第 4 ゲート電極 G E 1 4 にそれぞれ連結される。図示されていないが、ワードライン W L とワードライン・コンタクトプラグ C 2 4 , C 3 4 とを連結させる金属配線がさらに形成されうる。

#### 【 0 0 8 3 】

本実施形態では、1 対のビットライン B L , B L ' の上層に、ワードライン W L が形成されるが、他の実施形態では、ワードライン W L の上層に、1 対のビットライン B L , B

50

$L'$  が形成される場合もある。

【0084】

再び図1を参照すれば、第1PMOSトランジスタPU11は、第1活性領域ACT11の上部に形成される第2ゲート電極GE12、及び第1活性領域ACT11で、第2ゲート電極GE12の両脇に形成された第2コンタクトプラグC12及び第3コンタクトプラグC13によって定義される。ここで、第2コンタクトプラグC12は、第1PMOSトランジスタPU11のソースに対応し、第2ゲート電極GE12は、第1PMOSトランジスタPU11のゲートに対応し、第3コンタクトプラグC13は、第1PMOSトランジスタPU11のドレインに対応する。

【0085】

第1NMOSトランジスタPD11は、第2活性領域ACT12の上部に形成される第2ゲート電極GE12、及び第2活性領域ACT12で、第2ゲート電極GE12の両脇に形成された第5コンタクトプラグC22及び第6コンタクトプラグC23によって定義される。ここで、第5コンタクトプラグC22は、第1NMOSトランジスタPD11のドレインに対応し、第2ゲート電極GE12は、第1NMOSトランジスタPD11のゲートに対応し、第6コンタクトプラグC23は、第1NMOSトランジスタPD11のソースに対応する。

10

【0086】

第2PMOSトランジスタPU12は、第1活性領域ACT11の上部に形成される第3ゲート電極GE13、及び第1活性領域ACT11で、第3ゲート電極GE13の両脇に形成された第1コンタクトプラグC11及び第2コンタクトプラグC12によって定義される。ここで、第1コンタクトプラグC11は、第2PMOSトランジスタPU12のドレインに対応し、第3ゲート電極GE13は、第2PMOSトランジスタPU12のゲートに対応し、第2コンタクトプラグC12は、第2PMOSトランジスタPU12のソースに対応する。

20

【0087】

第2NMOSトランジスタPD12は、第3活性領域ACT13の上部に形成される第3ゲート電極GE13、及び第3活性領域ACT13で、第3ゲート電極GE13の両脇に形成された第7コンタクトプラグC31及び第8コンタクトプラグC32によって定義される。ここで、第7コンタクトプラグC31は、第2NMOSトランジスタPD12のソースに対応し、第3ゲート電極GE13は、第2NMOSトランジスタPD12のゲートに対応し、第8コンタクトプラグC32は、第2NMOSトランジスタPD12のドレインに対応する。

30

【0088】

このとき、第1PMOSトランジスタPU11と、第1NMOSトランジスタPD11は、第2ゲート電極GE12に共通して連結され、第1金属配線N11によって連結されることによって、第1インバータを構成する。また、第2PMOSトランジスタPU12と、第2NMOSトランジスタPD12は、第3ゲート電極GE13に共通して連結され、第2配線N12によって連結されることによって、第2インバータを構成する。半導体メモリ装置1において、第1インバータ及び第2インバータが、ラッチを構成することによって、データを保存することができる。

40

【0089】

第3NMOSトランジスタPG11は、第2活性領域ACT12の上部に形成される第1ゲート電極GE11、及び第2活性領域ACT12で、第1ゲート電極GE11の両脇に形成された第4コンタクトプラグC21及び第5コンタクトプラグC22によって定義される。ここで、第4コンタクトプラグC21及び第5コンタクトプラグC22は、第3NMOSトランジスタPG11のドレイン及びソースに対応し、第1ゲート電極GE11は、第3NMOSトランジスタPG11のゲートに対応する。このとき、第4コンタクトプラグC21は、ピットラインBLと連結され、第1ゲート電極GE11上のワードライン・コンタクトプラグC24は、ワードラインWLと連結される。ここで、第3NMOS

50

トランジスタ P G 1 1 は、第 1 パスゲートまたは第 1 伝達ゲートとして動作しうる。

【 0 0 9 0 】

第 4 NMOS トランジスタ P G 1 2 は、第 3 活性領域 A C T 1 3 の上部に形成される第 4 ゲート電極 G E 1 4 、及び第 3 活性領域 A C T 1 3 で、第 4 ゲート電極 G E 1 4 の両脇に形成された第 8 コンタクトプラグ C 3 2 及び第 9 コンタクトプラグ C 3 3 によって定義される。ここで、第 8 コンタクトプラグ C 3 2 及び第 9 コンタクトプラグ C 3 3 は、第 4 NMOS トランジスタ P G 1 2 のドレイン及びソースに対応し、第 4 ゲート電極 G E 1 4 は、第 4 NMOS トランジスタ P G 1 2 のゲートに対応する。このとき、第 9 コンタクトプラグ C 3 3 は、ビットラインバー B L ' と連結され、第 4 ゲート電極 G E 1 4 上のワードライン・コンタクトプラグ C 3 4 は、ワードライン W L と連結される。ここで、第 4 NMOS トランジスタ P G 1 2 は、第 2 パスゲートまたは第 2 伝達ゲートとして動作しうる。

【 0 0 9 1 】

本実施形態による半導体メモリ装置 1 は、单一活性領域である第 1 活性領域 A C T 1 1 に、第 1 PMOS トランジスタ P U 1 1 及び第 2 PMOS トランジスタ P U 1 2 を一列に形成する。これにより、第 1 PMOS トランジスタ P U 1 1 及び第 2 PMOS トランジスタ P U 1 2 それに係わる 2 つの活性領域を別途に形成するために、複雑なパターニング工程を行う代わりに、単一パターニング工程で、第 1 活性領域 A C T 1 1 を形成できるので、パターニング工程が簡単になる。また、第 1 PMOS トランジスタ P U 1 1 及び第 2 PMOS トランジスタ P U 1 2 それに係わる 2 つの活性領域の代わりに、单一活性領域を形成することによって、2 つの活性領域間に、素子分離膜を形成する必要がないので、半導体メモリ装置 1 の単位セルで、横方向の長さが縮小されることによって、全体的に素子の集積度を向上させることができる。

【 0 0 9 2 】

また、本実施形態による半導体メモリ装置 1 は、第 1 活性領域 A C T 1 1 に形成された第 1 PMOS トランジスタ P U 1 1 及び第 2 PMOS トランジスタ P U 1 2 は、電源電極ライン V d d に連結される第 2 コンタクトプラグ C 1 2 を共有する。これにより、第 1 PMOS トランジスタ P U 1 1 及び第 2 PMOS トランジスタ P U 1 2 それぞれに対して、電源電極 V d d を印加するための 2 つのコンタクトプラグを別途に形成する必要がないので、半導体メモリ装置 1 の単位セルで、縦方向の長さが縮小されることによって、全体的に素子の集積度を向上させることができる。

【 0 0 9 3 】

さらに、本実施形態による半導体メモリ装置 1 は、第 1 活性領域 A C T 1 1 、第 2 活性領域 A C T 1 2 及び第 3 活性領域 A C T 1 3 が互いに平行するように形成され、第 2 活性領域 A C T 1 2 では、第 1 PMOS トランジスタ P U 1 1 に対応する位置に、第 1 NMOS トランジスタ P D 1 1 が配され、第 2 PMOS トランジスタ P U 1 2 に対応する位置に、第 3 NMOS トランジスタ P G 1 1 が配され、第 3 活性領域 A C T 1 3 では、第 1 PMOS トランジスタ P U 1 1 に対応する位置に、第 4 NMOS トランジスタ P G 1 2 が配され、第 2 PMOS トランジスタ P U 1 2 に対応する位置に、第 2 NMOS トランジスタ P D 1 2 が配される。このように、半導体メモリ装置 1 の単位セルにおいて、第 1 PMOS トランジスタ P U 1 1 及び第 2 PMOS トランジスタ P U 1 2 を中心に対称な形態に他のトランジスタが配されることによって、半導体メモリ装置 1 の集積度をさらに向上させることができる。また、半導体メモリ装置 1 に、複数の単位セルが配されるときにも、境界領域に追加領域が要求されない。

【 0 0 9 4 】

前述のように、本実施形態によれば、半導体メモリ素子 1 において、单一活性領域に P チャネル・トランジスタを形成し、N チャネル・トランジスタまたは他の素子は、P チャネル・トランジスタに対して対称的に配されうる。本実施形態では、半導体メモリ装置 1 は、6 個のトランジスタを含んでいるが、他の実施形態では、半導体メモリ装置 1 は、4 個のトランジスタ及び 2 個の抵抗素子を含むことができ、さらに他の実施形態では、半導

10

20

30

40

50

体メモリ装置 1 は、さらに多数のトランジスタを含むことができ、さらに他の実施形態では、半導体メモリ装置 1 は、さらに少数のトランジスタを含むこともできる。

【 0 0 9 5 】

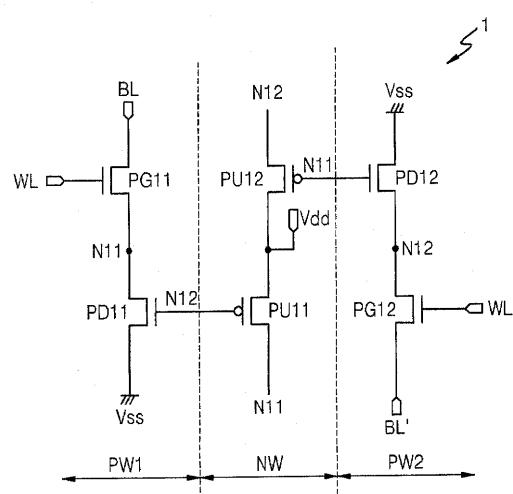

図 5 は、図 1 の半導体メモリ装置の等価回路を示す回路図である。

【 0 0 9 6 】

図 5 を参照すれば、半導体メモリ装置 1 は、第 1 P ウェル領域 PW1 に配される第 1 N MOS トランジスタ PD11 及び第 3 NMOS トランジスタ PG11；N ウェル領域 NW に配される第 1 PMOS トランジスタ PU11 及び第 2 PMOS トランジスタ PU12；第 2 P ウェル領域 PW2 に配される第 2 NMOS トランジスタ PD12 及び第 4 NMOS トランジスタ PG12；を含む。このとき、第 1 PMOS トランジスタ PU11 及び第 1 NMOS トランジスタ PD11 は、第 1 インバータを構成し、第 2 PMOS トランジスタ PU12 及び第 2 NMOS トランジスタ PD12 は、第 2 インバータを構成する。

10

【 0 0 9 7 】

第 3 NMOS トランジスタ PG11 は、ワードライン WL に印加される電圧によってオン／オフになり、ビットライン BL を第 1 ノード N11 に連結させることができる。ここで、第 1 ノード N11 は、図 1 に図示された第 1 金属配線 N11 に対応する。具体的には、ワードライン WL に印加される電圧が、論理「1」であるとき、第 3 NMOS トランジスタ PG11 はターンオンされ、ビットライン BL を第 1 ノード N11 に連結させることができる。第 1 ノード N11 は、第 2 インバータの入力端子、すなわち、第 2 PMOS トランジスタ PU12 のゲートと、第 2 NMOS トランジスタ PD12 のゲートとに連結され、また、第 1 インバータの出力端子、すなわち、第 1 PMOS トランジスタ PU11 のドレインと、第 1 NMOS トランジスタ PD11 のドレインとに連結される。

20

【 0 0 9 8 】

第 4 NMOS トランジスタ PG12 は、ワードライン WL に印加される電圧によって、オン／オフになり、ビットラインバー BL' を第 2 ノード N12 に連結させることができる。ここで、第 2 ノード N12 は、図 1 に図示された第 2 金属配線 N12 に対応する。具体的には、ワードライン WL に印加される電圧が、論理「1」であるとき、第 4 NMOS トランジスタ PG12 はターンオンされ、ビットラインバー BL' を第 2 ノード N12 に連結させることができる。第 2 ノード N12 は、第 1 インバータの入力端子、すなわち、第 1 PMOS トランジスタ PU11 のゲートと、第 1 NMOS トランジスタ PD11 のゲートとに連結され、また、第 2 インバータの出力端子、すなわち、第 2 PMOS トランジスタ PU12 のドレインと、第 2 NMOS トランジスタ PD12 のドレインとに連結される。

30

【 0 0 9 9 】

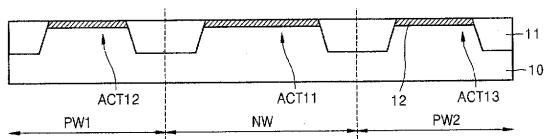

図 6 は、図 1 の半導体メモリ装置の I - I' 線に沿って切り取った断面図を示している。

。

【 0 1 0 0 】

図 6 を参照すれば、半導体メモリ装置 1 は、N ウェル領域 NW、第 1 P ウェル領域 PW1 及び第 2 P ウェル領域 PW2 を有する基板 10 上に形成される。ここで、基板 10 は、半導体基板であるが、例えば、半導体基板は、シリコン、シリコン - オン - 絶縁体 (silicon-on-insulator)、シリコン - オン - サファイア (silicon-on-sapphire)、ゲルマニウム、シリコン - ゲルマニウム及びガリウム - ヒ素のうちいずれか一つを含むことができる。本実施形態で、基板 10 は、P 型半導体基板でありうる。

40

【 0 1 0 1 】

N ウェル領域 NW は、基板 10 に N 型イオンを注入することによって形成され、第 1 P ウェル領域 PW1 及び第 2 P ウェル領域 PW2 は、基板 10 に P 型イオンを注入することによって形成されうる。N ウェル領域 NW、第 1 P ウェル領域 PW1 及び第 2 P ウェル領域 PW2 には、素子分離膜 11 によって画定される第 1 活性領域 ACT11、第 2 活性領域 ACT12 及び第 3 活性領域 ACT13 がそれぞれ配されうる。ここで、素子分離膜 1

50

1は、S T I ( shallow trench isolation ) でありうる。第1活性領域A C T 1 1 , 第2活性領域A C T 1 2 及び第3活性領域A C T 1 3 上には、シリサイド層1 2 が形成されうる。

#### 【 0 1 0 2 】

基板1 0 の上部には、第1絶縁層1 3 が配され、第1絶縁層1 3 には、第5コンタクトプラグC 2 2 , 第2コンタクトプラグC 1 2 及び第8コンタクトプラグC 3 2 が配される。このとき、第5コンタクトプラグC 2 2 は、第2活性領域A C T 1 2 に連結され、第2コンタクトプラグC 1 2 は、第1活性領域A C T 1 1 に連結され、第8コンタクトプラグC 3 2 は、第3活性領域A C T 1 3 にそれぞれ連結される。第1絶縁層1 3 の上部には、第2絶縁層1 4 が配され、第2絶縁層1 4 には、第1金属配線N 1 1 , 第2金属配線N 1 2 及び第3金属配線N 1 3 が配される。ここで、第3金属配線N 1 3 は、電源電極ラインV d d を第1活性領域A C T 1 1 に連結させるための配線である。10

#### 【 0 1 0 3 】

第2絶縁層1 4 の上部には、第3絶縁層1 5 が配され、第3絶縁層1 5 には、ビアプラグVが配される。第3絶縁層1 5 の上部には、第4絶縁層1 6 が配され、第4絶縁層1 6 には、1対のビットラインB L , B L ' と、電源電極ラインV d d とが配される。第4絶縁層1 6 の上部には、第5絶縁層1 7 が配され、第5絶縁層1 7 の上部には、ワードラインW L が配される。

#### 【 0 1 0 4 】

ここで、第1絶縁層ないし第5絶縁層1 3 , 1 4 , 1 5 , 1 6 , 1 7 は、シリコン酸化膜、P S G ( phosphosilicate glass ) またはB P S G ( borophosphosilicate glass ) でありうる。または、第1絶縁層ないし第5絶縁層1 3 , 1 4 , 1 5 , 1 6 , 1 7 は、低誘電率材料であるドーピングされたC V D ( chemical vapor deposition ) ガラス層でありうる。しかし、それらは例示的なものであり、本発明がそれらに限定されるものではない。ここで、コンタクトプラグC 2 2 , C 1 2 , C 3 2 及びビアプラグVは、タンゲステン(W)、アルミニウム(A l)、銅(C u)、モリブデン(M o)、チタン(T i)、タンタル(T a)、ルテニウム(R u)、またはそれらの合金で形成されうる。しかし、これは例示的なものであり、本発明がこれに限定されるものではない。例えば、コンタクトプラグC 2 2 , C 1 2 , C 3 2 及びビアプラグVは、前記例示された金属の導電性窒化物でもありうる。2030

#### 【 0 1 0 5 】

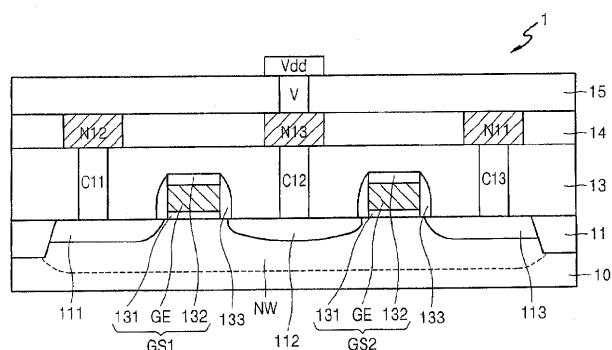

図7は、図1の半導体メモリ装置のI I - I I ' 線に沿って切り取った断面図を示している。

#### 【 0 1 0 6 】

図7を参照すれば、半導体メモリ装置1は、Nウェル領域N Wを有する基板1 0 上に形成される。このとき、Nウェル領域N Wは、基板1 0 に形成される素子分離膜1 1 によって画定される。

#### 【 0 1 0 7 】

Nウェル領域N W上には、第1ゲートスタックG S 1 及び第2ゲートスタックG S 2 が配される。第1ゲートスタックG S 1 及び第2ゲートスタックG S 2 は、ゲート絶縁膜1 3 1 、ゲート電極層G E 及びキャッピング膜1 3 2 を含むことができる。具体的には、第1ゲートスタックG S 1 及び第2ゲートスタックG S 2 は、Nウェル領域N W上に、順次にゲート絶縁膜1 3 1 、ゲート電極層G E 及びキャッピング膜1 3 2 を形成した後、これをパターニングすることによって形成されうる。40

#### 【 0 1 0 8 】

ここで、ゲート絶縁膜1 3 1 はシリコン、酸化膜でありうるが、本発明は、これに制限されるものではない。例えば、ゲート絶縁膜1 3 1 は、シリコン酸化膜よりさらに大きな誘電率を有するシリコン窒化膜(S i N<sub>x</sub>)、タンタル酸化膜(T a O<sub>x</sub>)、ハフニウム酸化膜(H f O<sub>x</sub>)、アルミニウム酸化膜(A l O<sub>x</sub>)及び亜鉛酸化膜(Z n O<sub>x</sub>)のよ50

うな高誘電率薄膜を含むことができる。ゲート電極層 G E は、例えば、高濃度ドーピングされた、ポリシリコン膜；タンゲステン、ニッケル、モリブデン及びコバルトなどの金属膜；金属シリサイド膜、またはそれらの組み合わせ、例えば、高濃度ドーピングされたポリシリコン膜とニッケルコバルトシリサイド膜との積層膜でありうる。キャッピング膜 132 は、シリコン窒化物またはシリコン酸化物でありうる。

#### 【 0109 】

第 1 ゲートスタック GS 1 及び第 2 ゲートスタック GS 2 の側壁には、スペーサ 133 が配される。ここで、スペーサ 133 は、シリコン窒化物から形成されうる。ソース領域及びドレイン領域 111, 112, 113 は、N ウェル領域 NW であり、第 1 ゲートスタック GS 1 及び第 2 ゲートスタック GS 2 の両脇に配される。例えば、ソース領域及びドレイン領域 111, 112, 113 は、スペーサ 133 を、イオン注入マスクとして利用して、N ウェル領域 NW に高濃度のイオン注入工程を行って形成されうる。

10

#### 【 0110 】

第 1 ゲートスタック GS 1 及び第 2 ゲートスタック GS 2 の上部には、第 1 絶縁層 13 が配され、第 1 絶縁層 13 には、第 1 コンタクトプラグ C11, 第 2 コンタクトプラグ C12 及び第 3 コンタクトプラグ C13 が配される。このとき、複数のコンタクトプラグ C11, C12, C13 ) は、ソース領域及びドレイン領域 111, 112, 113 にそれぞれ連結される。図示されていないが、ソース領域及びドレイン領域 111, 112, 113 の上部には、シリサイド層が形成されうる。

20

#### 【 0111 】

第 1 絶縁層 13 の上部には、第 2 絶縁層 14 が配され、第 2 絶縁層 14 には、第 1 金属配線 N11, 第 2 金属配線 N12 及び第 3 金属配線 N13 が配される。第 2 絶縁層 14 の上部には、第 3 絶縁層 15 が配され、第 3 絶縁層 15 には、ビアプラグ V が配される。ビアプラグ V の上部には、電源電極ライン Vdd が配される。

20

#### 【 0112 】

図 8A ないし図 8G は、本発明の一実施形態による半導体メモリ装置の製造方法を示す断面図である。

#### 【 0113 】

図 8A を参照すれば、基板 10 は、PMOS トランジスタが形成される N ウェル領域 NW, NMOS トランジスタが形成される第 1 P ウェル領域 PW1 及び第 2 P ウェル領域 PW2 を含む。N ウェル領域 NW には、第 1 活性領域 ACT11 が形成され、第 1 P ウェル領域 PW1 及び第 2 P ウェル領域 PW2 には、第 2 活性領域 ACT12 及び第 3 活性領域 ACT13 が形成されるが、第 1 活性領域 ACT11, 第 2 活性領域 ACT12 及び第 3 活性領域 ACT13 は、STI のような素子分離膜 11 によって画定されうる。

30

#### 【 0114 】

図 8B を参照すれば、第 1 活性領域 ACT11, 第 2 活性領域 ACT12 及び第 3 活性領域 ACT13 上には、シリサイド膜 12 が形成される。具体的には、基板 10 上に金属層(図示せず)を形成し、金属層が形成された基板 10 に対して熱処理を行うことによって、第 1 活性領域 ACT11, 第 2 活性領域 ACT12 及び第 3 活性領域 ACT13 上にシリサイド膜 12 を形成できる。このように、シリサイド膜 12 を形成することによって、第 1 活性領域 ACT11, 第 2 活性領域 ACT12 及び第 3 活性領域 ACT13 と、以後に形成されるコンタクトプラグとのコンタクト抵抗を低くすることができる。

40

#### 【 0115 】

図 8C を参照すれば、基板 10 の上部に、第 1 絶縁層 13 を形成する。次に、第 1 絶縁層 13 上に、フォトリソグラフィ工程によって、複数の第 1 コンタクトホール(図示せず)が形成される領域を露出させるマスク膜を形成する。次に、乾式エッチング工程を利用して、第 1 絶縁層 13 上に第 1 コンタクトホールを形成し、第 1 コンタクトホールを金属物質で埋め込むことによって、第 5 コンタクトプラグ C22, 第 2 コンタクトプラグ C12 及び第 8 コンタクトプラグ C32 を形成する。ここで、第 5 コンタクトプラグ C22, 第 2 コンタクトプラグ C12 及び第 8 コンタクトプラグ C32 は、タンゲステン(W)、

50

アルミニウム(Al)、銅(Cu)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ルテニウム(Ru)またはそれらの合金によって形成されうる。しかし、これは例示的なものであり、本発明がこれに限定されるものではない。例えば、コンタクトプラグC22, C12, C32は、前記例示された金属の導電性窒化物でもありうる。

## 【0116】

図8Dを参照すれば、第1絶縁層13の上部に、第2絶縁層14を形成する。次に、第2絶縁層14内に、複数の第2コンタクトホールを形成し、複数の第2コンタクトホールを金属物質で埋め込むことによって、第1金属配線N11, 第2金属配線N12及び第3金属配線N13を形成できる。

## 【0117】

図8Eを参照すれば、第2絶縁層14の上部に、第3絶縁層15を形成する。次に、第3絶縁層15内に、第3コンタクトホールを形成し、第3コンタクトホールを金属物質で埋め込むことによって、ビアプラグVを形成できる。ここで、ビアプラグVは、タンゲステン(W)、アルミニウム(Al)、銅(Cu)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ルテニウム(Ru)またはそれらの合金によって形成されうる。しかし、これは例示的なものであり、本発明がこれに限定されるものではない。例えば、ビアプラグVは、前記例示された金属の導電性窒化物でもありうる。

## 【0118】

図8Fを参照すれば、第3絶縁層15の上部に、第4絶縁層16を形成する。次に、第4絶縁層16内に、複数の第4コンタクトホールを形成し、複数の第4コンタクトホールを金属物質で埋め込むことによって、ビットラインBL、電源電極ラインVdd及びビットラインバーBL'を形成できる。他の実施形態では、ビットラインBL及びビットラインバーBL'を、電源電極ラインVddと異なる層に形成できる。さらに他の実施形態では、ビットラインBL、ビットラインバーBL'及び電源電極ラインVddを、第1金属配線N11, 第2金属配線N12及び第3金属配線N13の下層に形成することもできる。

## 【0119】

図8Gを参照すれば、第4絶縁層16の上部に、第5絶縁層17及びワードラインWLを順次に形成する。他の実施形態では、ワードラインWLは、ビットラインBL、ビットラインバーBL'の下層に形成できる。さらに他の実施形態では、ワードラインWLは、第1金属配線N11, 第2金属配線N12及び第3金属配線N13の下層に形成することもできる。

## 【0120】

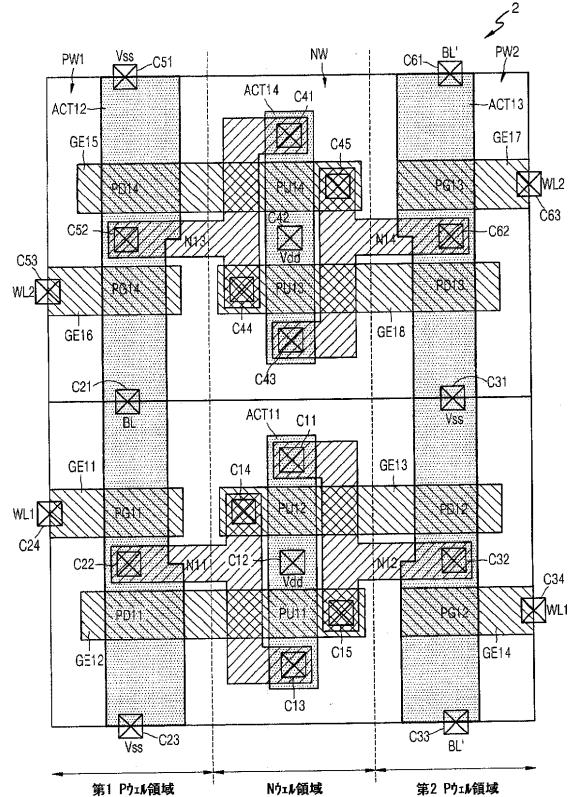

図9は、本発明の他の実施形態による半導体メモリ装置を示すレイアウトである。

## 【0121】

図9を参照すれば、半導体メモリ装置2は、第1ウェル領域NWと、第1ウェル領域NWの両脇に形成される第2ウェル領域PW1及び第3ウェル領域PW2と、を有する基板上に形成される2つのSRAMセルを含み、2ビットで動作しうる。このとき、第1ウェル領域NWは、第1導電型を有し、第2ウェル領域PW1及び第3ウェル領域PW2は、第2導電型を有することができる。本実施形態で、第1導電型はN型であり、第2導電型は、P型でありうる。以下、第1ウェル領域は、Nウェル領域NWであり、第2ウェル領域は、第1Pウェル領域PW1であり、第3ウェル領域は、第2Pウェル領域PW2とする。本実施形態による半導体メモリ装置2は、図1ないし図8を参照しつつ説明した半導体メモリ装置1の変形実施形態であるから、重複する説明は省略する。

## 【0122】

Nウェル領域NWは、例えば、イオン注入工程によって基板上に形成されるN型ウェルが配される領域であり、Nウェル領域NWには、素子分離膜によって画定される第1活性領域ACT11及び第4活性領域ACT14が配される。本実施形態で、第1活性領域ACT11及び第4活性領域ACT14のそれぞれは、縦方向に長い形態を有するバータイプの単一活性領域でありうる。

10

20

30

40

50

## 【0123】

このとき、第1活性領域ACT11に、P+型不純物をドーピングすることによって、P型拡散領域が形成され、また、コンタクトプラグC11, C12, C13が形成されうる。第1活性領域ACT11には、2つのプルアップ素子が一列に形成されうるが、本実施形態で、2つのプルアップ素子は、第1PMOSトランジスタPU11及び第2PMOSトランジスタPU12でありうる。また、第4活性領域ACT14に、P+不純物をドーピングすることによって、P型拡散領域が形成され、また、コンタクトプラグC41, C42, C43が形成されうる。第4活性領域ACT14には、2つのプルアップ素子が一列に形成されうるが、本実施形態で、2つのプルアップ素子は、第3PMOSトランジスタPU13及び第4PMOSトランジスタPU14でありうる。

10

## 【0124】

第1Pウェル領域PW1は、例えば、イオン注入工程によって基板上に形成されるP型ウェルが配される領域であり、第1Pウェル領域PW1には、素子分離膜によって画定される第2活性領域ACT12が配される。本実施形態で、第2活性領域ACT12は、第1活性領域ACT11及び第4活性領域ACT14に平行した方向に伸張する形態を有する単一活性領域でありうる。

20

## 【0125】

このとき、第2活性領域ACT12に、N+型不純物をドーピングすることによって、N型拡散領域が形成され、また、コンタクトプラグC21, C22, C23, C51, C52, C53が形成されうる。第2活性領域ACT12には、2つのプルダウン素子と、2つのアクセス素子が形成されうるが、本実施形態でプルダウン素子は、第1NMOSトランジスタPD11及び第6NMOSトランジスタPD14であり、アクセス素子は、第3NMOSトランジスタPG11及び第8NMOSトランジスタPG14でありうる。

20

## 【0126】

第2Pウェル領域PW2は、例えば、イオン注入工程によって基板上に形成されるP型ウェルが配される領域であり、第2Pウェル領域PW2には、素子分離膜によって画定される第3活性領域ACT13が配される。本実施形態で、第3活性領域ACT13は、第1活性領域ACT11及び第4活性領域ACT14に平行した方向に伸張する形態を有する単一活性領域でありうる。このとき、第3活性領域ACT13に、N+型不純物をドーピングすることによって、N型拡散領域が形成され、また、複数のコンタクトプラグC31, C32, C33, C61, C62が形成されうる。第3活性領域ACT13には、2つのプルダウン素子と、2つのアクセス素子とが形成されうるが、本実施形態でプルダウン素子は、第2NMOSトランジスタPD12及び第5NMOSトランジスタPD13であり、アクセス素子は、第4NMOSトランジスタPG12及び第7NMOSトランジスタPG13でありうる。

30

## 【0127】

第1活性領域ないし第4活性領域ACT11, ACT12, ACT13, ACT14が配された基板の上部には、第1ゲート電極ないし第8ゲート電極GE11, GE12, GE13, GE14, GE15, GE16, GE17, GE18が形成される。具体的には、第1ゲート電極GE11は、第2活性領域ACT12を横切る方向に形成され、第2ゲート電極GE12は、第1活性領域ACT11及び第2活性領域ACT12を横切る方向に形成され、第3ゲート電極GE13は、第1活性領域ACT11及び第3活性領域ACT13を横切る方向に形成され、第4ゲート電極GE14は、第3活性領域ACT13を横切る方向に形成される。また、第5ゲート電極GE15は、第2活性領域ACT12及び第4活性領域ACT14を横切る方向に形成され、第6ゲート電極GE16は、第2活性領域ACT12を横切る方向に形成され、第7ゲート電極GE17は、第3活性領域ACT13を横切る方向に形成され、第8ゲート電極GE18は、第4活性領域ACT14及び第3活性領域ACT13を横切る方向に形成される。このとき、第1ゲート電極GE11, 第4ゲート電極GE14, 第6ゲート電極GE16及び第7ゲート電極GE17の上部には、それぞれワードライン・コンタクトプラグC24, C34, C53, C63が

40

50

形成され、第2ゲート電極G E 1 2 , 第3ゲート電極G E 1 3 , 第5ゲート電極G E 1 5 及び第8ゲート電極G E 1 8の上部には、それぞれ配線コンタクトプラグC 1 5 , C 1 4 , C 4 5 , C 4 4が形成される。

#### 【0128】

第1ゲート電極ないし第8ゲート電極G E 1 1 , G E 1 2 , G E 1 3 , G E 1 4 , G E 1 5 , G E 1 6 , G E 1 7 , G E 1 8が形成された基板の上部には、第1金属配線ないし第4金属配線N 1 1 , N 1 2 , N 1 3 , N 1 4が形成される。このとき、第1金属配線N 1 1は、第1活性領域A C T 1 1に形成されたコンタクトプラグC 1 3 、第2活性領域A C T 1 2に形成されたコンタクトプラグC 2 2 、及び第3ゲート電極G E 1 3に形成された配線コンタクトプラグC 1 4を連結させる。また、第2金属配線N 1 2は、第1活性領域A C T 1 1に形成されたコンタクトプラグC 1 1 、第3活性領域A C T 1 3に形成されたコンタクトプラグC 3 2 、及び第2ゲート電極G E 1 2に形成された配線コンタクトプラグC 1 5を連結させる。また、第3金属配線N 1 3は、第4活性領域A C T 1 4に形成されたコンタクトプラグC 4 1 、第2活性領域A C T 1 2に形成されたコンタクトプラグC 5 2 、及び第8ゲート電極G E 1 8に形成された配線コンタクトプラグC 4 4を連結させる。また、第4金属配線N 1 4は、第4活性領域A C T 1 4に形成されたコンタクトプラグC 4 3 、第3活性領域A C T 1 3に形成されたコンタクトプラグC 6 2 、及び第5ゲート電極G E 1 5に形成された配線コンタクトプラグC 4 5を連結させる。

10

#### 【0129】

本実施形態によれば、半導体メモリ装置2で、第1NMOSトランジスタP D 1 1 , 第1PMOSトランジスタP U 1 1及び第4NMOSトランジスタP G 1 2を横方向に一列に配し、第3NMOSトランジスタP G 1 1 , 第2PMOSトランジスタP U 1 2及び第2NMOSトランジスタP D 1 2を横方向に一列に配し、第8NMOSトランジスタP G 1 4 , 第3PMOSトランジスタP U 1 3及び第5NMOSトランジスタP D 1 3を横方向に一列に配し、第6NMOSトランジスタP D 1 4 , 第4PMOSトランジスタP U 1 4及び第7NMOSトランジスタP G 1 3を横方向に一列に配しうる。

20

#### 【0130】

また、半導体メモリ装置2で、第1NMOSトランジスタP D 1 1 , 第3NMOSトランジスタP G 1 1 , 第8NMOSトランジスタP G 1 4及び第6NMOSトランジスタP D 1 4を、第1Pウェル領域P W 1に縦方向に一列に配し、第1PMOSトランジスタないし第4PMOSトランジスタP U 1 1 , P U 1 2 , P U 1 3 , P U 1 4を、Nウェル領域N Wに縦方向に一列に配し、第4NMOSトランジスタP G 1 2 , 第2NMOSトランジスタP D 1 2 , 第5NMOSトランジスタP D 1 3及び第7NMOSトランジスタP G 1 3を第2Pウェル領域P W 2に縦方向に一列に配しうる。

30

#### 【0131】

このように、半導体メモリ装置2において、第1NMOSトランジスタないし第4NMOSトランジスタP D 1 1 , P D 1 2 , P G 1 1 , P G 1 2は、第1PMOSトランジスタP U 1 1及び第2PMOSトランジスタP U 1 2を基準に、横方向に対称になり、第5NMOSないし第8NMOSトランジスタP D 1 3 , P D 1 4 , P G 1 3 , P G 1 4は、第3PMOSトランジスタ及び第4PMOSトランジスタP U 1 3 , P U 1 4を基準に、横方向に対称になった形態に配されることによって、半導体メモリ装置2で、単位セルの横方向の長さ及び縦方向の長さが縮小されるので、半導体メモリ装置2の集積度が向上しうる。また、半導体メモリ装置2で、複数の単位セルが配される場合にも、境界領域に追加領域が要求されない。

40

#### 【0132】

図10は、図9の半導体メモリ装置の等価回路を示す回路図である。

#### 【0133】

図10を参照すれば、半導体メモリ装置2は、第1Pウェル領域P W 1に配される第1NMOSトランジスタP D 1 1 , 第3NMOSトランジスタP G 1 1 , 第6NMOSトランジスタP D 1 4及び第8NMOSトランジスタP G 1 4、Nウェル領域N Wに配される

50

第1PMOSトランジスタないし第4PMOSトランジスタPU11, PU12, PU13, PU14、及び第2Pウェル領域PW2に配される第2NMOSトランジスタPD12, 第4NMOSトランジスタPG12, 第5NMOSトランジスタPD13及び第7NMOSトランジスタPG13を含む。このとき、第1PMOSトランジスタPU11及び第1NMOSトランジスタPD11は、第1インバータを構成し、第2PMOSトランジスタPU12及び第2NMOSトランジスタPD12は、第2インバータを構成し、第3PMOSトランジスタPU13及び第5NMOSトランジスタPD13は、第3インバータを構成し、第4PMOSトランジスタPU14及び第6NMOSトランジスタPD14は、第4インバータを構成する。

【0134】

10

第3NMOSトランジスタPG11は、ワードラインWL1に印加される電圧によってオン／オフになり、ビットラインBLを第1ノードN11に連結させることができる。ここで、第1ノードN11は、図9に図示された第1金属配線N11に対応する。具体的には、ワードラインWL1に印加される電圧が、論理「1」であるとき、第3NMOSトランジスタPG11はターンオンされ、ビットラインBLを第1ノードN11に連結させることができる。第1ノードN11は、第2インバータの入力端子、すなわち、第2PMOSトランジスタPU12のゲートと、第2NMOSトランジスタPD12のゲートとに連結され、また、第1インバータの出力端子、すなわち、第1PMOSトランジスタPU11のドレインと、第1NMOSトランジスタPD11のドレインとに連結される。

【0135】

20

第4NMOSトランジスタPG12は、ワードラインWL1に印加される電圧によってオン／オフになり、ビットラインバーBL'を第2ノードN12に連結させることができる。ここで、第2ノードN12は、図9に図示された第2金属配線N12に対応する。具体的には、ワードラインWL1に印加される電圧が、論理「1」であるとき、第4NMOSトランジスタPG12はターンオンされ、ビットラインバーBL'を、第2ノードN12に連結させることができる。第2ノードN12は、第1インバータの入力端子、すなわち、第1PMOSトランジスタPU11のゲートと、第1NMOSトランジスタPD11のゲートとに連結され、また、第2インバータの出力端子、すなわち、第2PMOSトランジスタPU12のドレインと、第2NMOSトランジスタPD12のドレインとに連結される。

30

【0136】

第7NMOSトランジスタPG13は、ワードラインWL2に印加される電圧によってオン／オフになり、ビットラインバーBL'を第4ノードN14に連結させることができる。ここで、第4ノードN14は、図9に図示された第4金属配線N14に対応する。具体的には、ワードラインWL2に印加される電圧が論理「1」であるとき、第7NMOSトランジスタPG13はターンオンされ、ビットラインバーBL'を第4ノードN14に連結させることができる。第4ノードN14は、第4インバータの入力端子、すなわち、第4PMOSトランジスタPU14のゲートと、第6NMOSトランジスタPD14のゲートとに連結され、また、第3インバータの出力端子、すなわち、第3PMOSトランジスタPM13のドレインと、第5NMOSトランジスタPD13のドレインに連結される。

40

【0137】

第8NMOSトランジスタPG14は、ワードラインWL2に印加される電圧によってオン／オフになり、ビットラインBLを第3ノードN13に連結させることができる。ここで、第3ノードN13は、図9に図示された第3金属配線N13に対応する。具体的には、ワードラインWL2に印加される電圧が論理「1」であるとき、第8NMOSトランジスタPG14はターンオンされ、ビットラインBLを第3ノードN13に連結させることができる。第3ノードN13は、第3インバータの入力端子、すなわち、第3PMOSトランジスタPU13のゲートと、第5NMOSトランジスタPD13のゲートとに連結され、また、第4インバータの出力端子、すなわち、第4PMOSトランジスタPU14

50

のドレインと、第6N MOSトランジスタPD14のドレインとに連結される。

【0138】

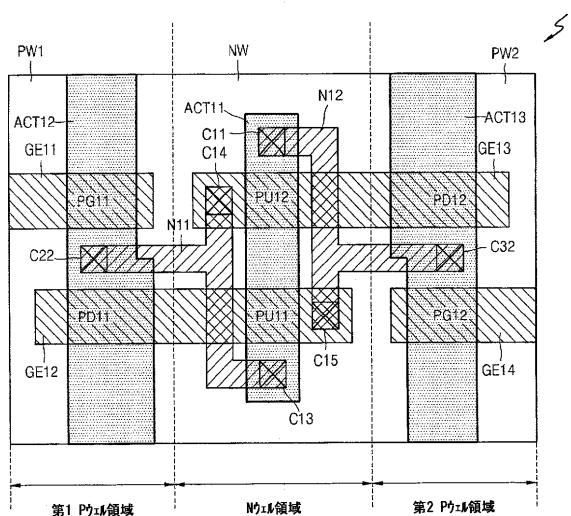

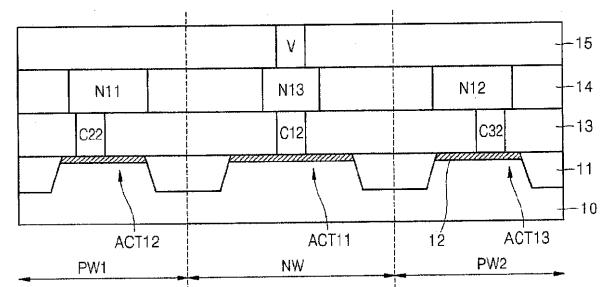

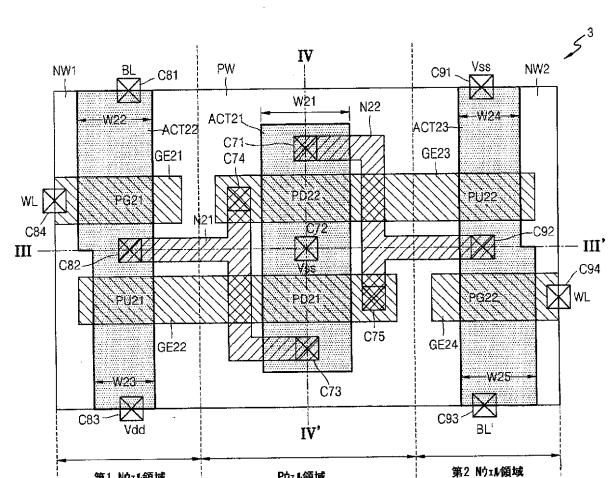

図11は、本発明のさらに他の実施形態による半導体メモリ装置を示すレイアウトである。

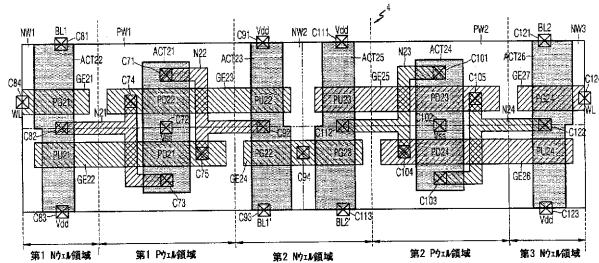

【0139】

図11を参照すれば、半導体メモリ装置3は、第1ウェル領域PWと、第1ウェル領域PWの両脇に形成される第2NW1ウェル領域及び第3ウェル領域NW2を有する基板上に形成される1つのSRAMセルを含み、1ビットで動作しうる。このとき、第1ウェル領域PWは、第1導電型を有し、第2NW1ウェル領域及び第3ウェル領域NW2は、第2導電型を有することができる。本実施形態で、第1導電型はP型であり、第2導電型はN型でありうる。以下、第1ウェル領域は、Pウェル領域PWであり、第2ウェル領域は、第1Nウェル領域NW1であり、第3ウェル領域は、第2Nウェル領域NW2とする。

10

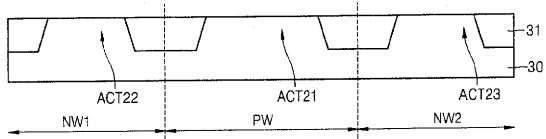

【0140】

Pウェル領域PWは、例えば、イオン注入工程によって基板上に形成されるP型ウェルが配される領域であり、Pウェル領域PWには、素子分離膜によって画定される第1活性領域ACT21が配される。本実施形態で、第1活性領域ACT21は、縦方向に長い形態を有するバータイプの単一活性領域でありうる。このとき、第1活性領域ACT21に、N+型不純物をドーピングすることによって、N型拡散領域が形成され、また、第1コンタクトプラグC71、第2コンタクトプラグ72及び第3コンタクトプラグC73が形成されうる。第1活性領域ACT21には、2つのプルダウン素子が一列に形成されうるが、本実施形態で、2つのプルダウン素子は、第1N MOSトランジスタPD21及び第2N MOSトランジスタPD22でありうる。

20

【0141】

このように、2つのプルダウン素子、すなわち、第1N MOSトランジスタPD21及び第2N MOSトランジスタPD22を、単一活性領域である第1活性領域ACT21に配することによって、第1N MOSトランジスタPD21及び第2N MOSトランジスタPD22間のミスマッチを低減させることができる。具体的には、第1N MOSトランジスタPD21に係わるスレショルド電圧と、第2N MOSトランジスタPD22に係わるスレショルド電圧との差を減らすことができる。

30

【0142】

第1Nウェル領域NW1は、例えば、イオン注入工程によって基板上に形成されるN型ウェルが配される領域であり、第1Nウェル領域NW1には、素子分離膜によって画定される第2活性領域ACT22が配される。本実施形態で、第2活性領域ACT22は、第1活性領域ACT21に平行した方向に伸張する形態を有する単一活性領域でありうる。このとき、第2活性領域ACT22に、P+型不純物をドーピングすることによって、P型拡散領域が形成され、また、第4コンタクトプラグC81、第5コンタクトプラグC82及び第6コンタクトプラグC83が形成されうる。第2活性領域ACT22には、1つのプルアップ素子と、1つのアクセス素子とが形成されうるが、本実施形態で、プルアップ素子は、第1PMOSトランジスタP乌21であり、アクセス素子は、第3PMOSトランジスタPG21でありうる。

40

【0143】

第2Nウェル領域NW2は、例えば、イオン注入工程によって基板上に形成されるN型ウェルが配される領域であり、第2Nウェル領域NW2には、素子分離膜によって画定される第3活性領域ACT23が配される。本実施形態で、第3活性領域ACT23は、第1活性領域ACT21に平行した方向に伸張する形態を有する単一活性領域でありうる。このとき、第3活性領域ACT23に、P+型不純物をドーピングすることによって、P型拡散領域が形成され、また、第7コンタクトプラグC91、第8コンタクトプラグC92及び第9コンタクトプラグC93が形成されうる。第3活性領域ACT23には、1つのプルアップ素子と、1つのアクセス素子とが形成されうるが、本実施形態で、プルアップ素子は、第2PMOSトランジスタP乌22であり、アクセス素子は、第4PMOSト

50

ランジスタ P G 2 2 である。

【 0 1 4 4 】

前述のように、本実施形態によれば、半導体メモリ装置 3 は、第 3 PMOS トランジスタ P G 2 1 及び第 4 PMOS トランジスタ P G 2 2 によって具現されるアクセス素子を含むことができる。半導体メモリ装置 3 を製造する工程で、PMOS トランジスタに係わる性能が向上することによって、NMOS トランジスタを代替して、PMOS トランジスタを利用してアクセス素子を具現できる。

【 0 1 4 5 】

第 1 活性領域 A C T 2 1 , 第 2 活性領域 A C T 2 2 及び第 3 活性領域 A C T 2 3 の幅を比較すれば、次の通りである。第 1 活性領域 A C T 2 1 の第 1 幅 W 2 1 は、その位置に関係せずに一定の値を有することができる。第 2 活性領域 A C T 2 2 の幅は、その位置によって互いに異なりうるが、具体的には、第 3 PMOS トランジスタ P G 2 1 が配される領域の第 2 幅 W 2 2 は、第 1 PMOS トランジスタ P U 2 1 が配される領域の第 3 幅 W 2 3 より広く、第 2 W 2 2 及び第 3 幅 W 2 3 は、第 1 幅 W 2 1 より狭い。第 3 活性領域 A C T 2 3 の幅は、その位置によって互いに異なりうるが、具体的には、第 2 PMOS トランジスタ P U 2 2 が配される領域の第 4 幅 W 2 4 は、第 4 PMOS トランジスタ P G 2 2 が配される領域の第 5 幅 W 2 5 より狭く、第 4 幅 W 2 4 及び第 5 幅 W 2 5 は、第 1 幅 W 2 1 より狭い。また、第 4 幅 W 2 4 は、第 3 幅 W 2 3 と実質的に同一であり、第 5 幅 W 2 5 は、第 2 幅 W 2 2 と実質的に同一である。

10

【 0 1 4 6 】

このように、第 1 NMOS トランジスタ P D 2 1 及び第 2 NMOS トランジスタ P D 2 2 が形成される第 1 活性領域 A C T 2 1 の幅 W 2 1 を最も広く具現することによって、第 1 NMOS トランジスタ P D 2 1 及び第 2 NMOS トランジスタ P D 2 2 でプルダウン動作を行う場合、プルダウン動作の速度を向上させることができる。また、第 3 PMOS トランジスタ P G 2 1 及び第 4 PMOS トランジスタ P G 2 2 が形成される第 2 活性領域 A C T 2 2 及び第 3 活性領域 A C T 2 3 の幅 W 2 2 , W 2 5 を、第 1 PMOS トランジスタ P U 2 1 及び第 2 PMOS トランジスタ P U 2 2 が形成される第 2 活性領域 A C T 2 2 及び第 3 活性領域 A C T 2 3 の幅 W 2 3 , W 2 4 より広く具現することによって、半導体メモリ装置 3 に対する書き込み動作を行う場合、書き込み動作の速度を向上させることができる。

20

【 0 1 4 7 】

第 1 活性領域 A C T 2 1 , 第 2 活性領域 A C T 2 2 及び第 3 活性領域 A C T 2 3 が配された基板の上部には、第 1 ゲート電極ないし第 4 ゲート電極 G E 2 1 , G E 2 2 , G E 2 3 , G E 2 4 が形成される。具体的には、第 1 ゲート電極 G E 2 1 は、第 2 活性領域 A C T 2 2 を横切る方向に形成され、第 2 ゲート電極 G E 2 2 は、第 1 活性領域 A C T 2 1 及び第 2 活性領域 A C T 2 2 を横切る方向に形成され、第 3 ゲート電極 G E 2 3 は、第 1 活性領域 A C T 2 1 及び第 3 活性領域 A C T 2 3 を横切る方向に形成され、第 4 ゲート電極 G E 2 4 は、第 3 活性領域 A C T 2 3 を横切る方向に形成される。このとき、第 1 ゲート電極 G E 2 1 及び第 4 ゲート電極 G E 2 4 の上部には、それぞれワードライン・コンタクトプラグ C 8 4 , C 9 4 が形成され、第 2 ゲート電極 G E 2 2 及び第 3 ゲート電極 G E 2 3 の上部には、それぞれ配線コンタクトプラグ C 7 5 , C 7 4 が形成される。

30

【 0 1 4 8 】

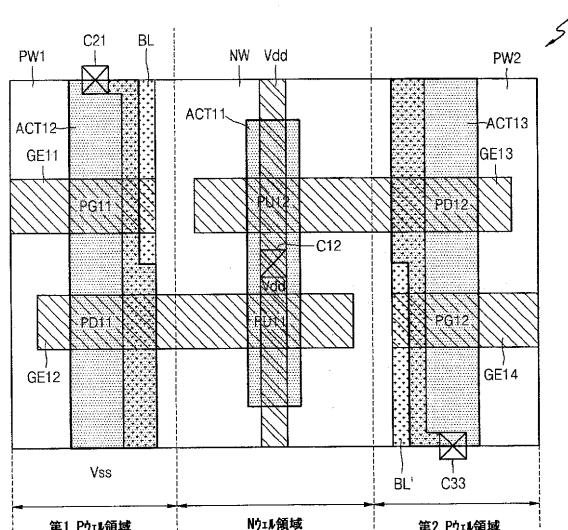

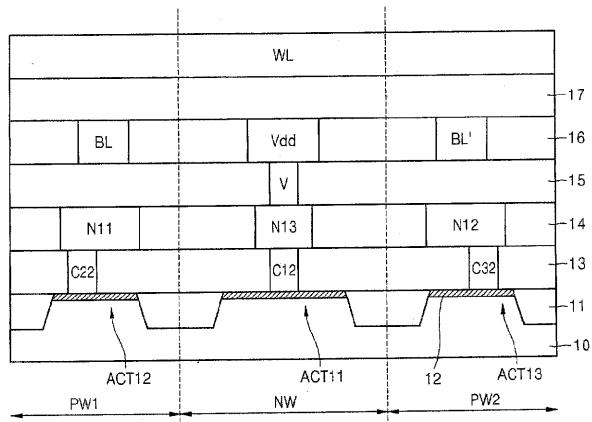

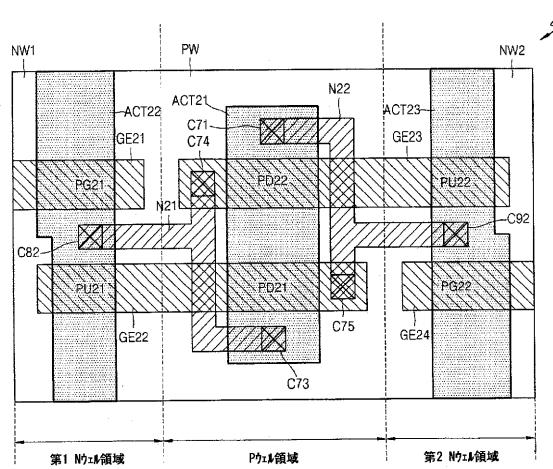

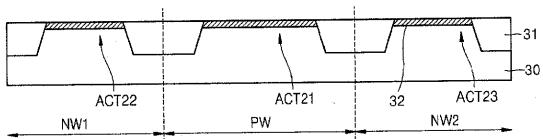

図 1 2 は、図 1 1 の半導体メモリ装置の金属配線層を示すレイアウトである。

【 0 1 4 9 】

図 1 2 を参照すれば、第 1 ゲート電極ないし第 4 ゲート電極 G E 2 1 , G E 2 2 , G E 2 3 , G E 2 4 が形成された基板の上部には、第 1 金属配線 N 2 1 及び第 2 金属配線 N 2 2 が形成される。このとき、第 1 金属配線 N 2 1 は、第 1 活性領域 A C T 2 1 に形成された第 3 コンタクトプラグ C 7 3 、第 2 活性領域 A C T 2 2 に形成された第 5 コンタクトプラグ C 8 2 、及び第 3 ゲート電極 G E 2 3 に形成された配線コンタクトプラグ C 7 4 を連結させる。また、第 2 金属配線 N 2 2 は、第 1 活性領域 A C T 2 1 に形成された第 1 コン

40

50

タクトプラグC71、第3活性領域ACT23に形成された第8コンタクトプラグC92及び第2ゲート電極GE22に形成された配線コンタクトプラグC75を連結させる。

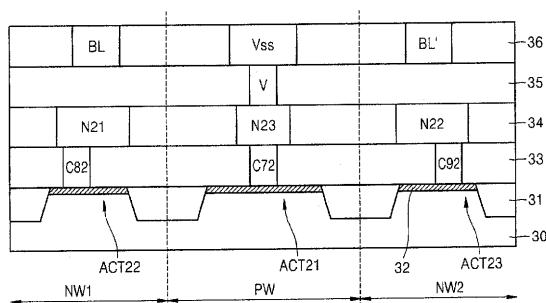

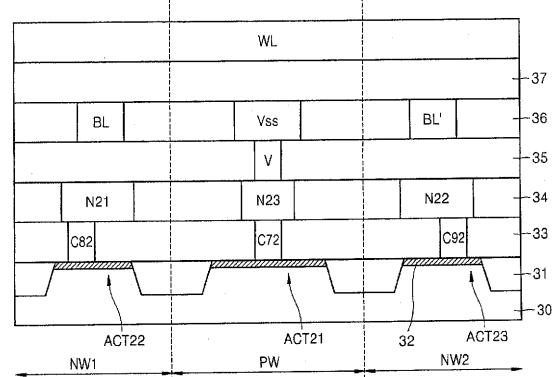

【0150】

図13は、図11の半導体メモリ装置のビットライン配線層を示すレイアウトである。

【0151】

図13を参照すれば、第1金属配線N21及び第2金属配線N22が形成された基板の上部には、1対のビットライン、すなわち、ビットラインBL及びビットラインバーBL'が形成される。ビットラインBL及びビットラインバーBL'は、第1活性領域ACT21、第2活性領域ACT22及び第3活性領域ACT23と平行な方向に伸張しうる。このとき、ビットラインBLは、第2活性領域ACT22に形成された第4コンタクトプラグC81を介して、第2活性領域ACT22に連結され、ビットラインバーBL'は、第3活性領域ACT23に形成された第9コンタクトプラグC93を介して、第3活性領域ACT23に連結される。

10

【0152】

また、第1金属配線N21及び第2金属配線N22が形成された基板の上部には、接地電極ラインVssが形成される。接地電極ラインVssは、1対のビットラインBL、BL'間に形成され、1対のビットラインBL、BL'と平行な方向に伸張しうる。このとき、接地電極ラインVssは、第1活性領域ACT21に形成された第2コンタクトプラグC72を介して、第1活性領域ACT21に連結される。

20

【0153】

図14は、図11の半導体メモリ装置のワードライン配線層を示すレイアウトである。

【0154】

図14を参照すれば、1対のビットラインBL、BL'が形成された基板の上部には、ワードラインWLが形成される。ワードラインWLは、第1ゲート電極ないし第4ゲート電極GE21、GE22、GE23、GE24と平行な方向に伸張しうる。このとき、ワードラインWLは、ワードライン・コンタクトプラグC84、C94を介して、第1ゲート電極GE21及び第4ゲート電極GE24にそれぞれ連結される。図示されていないが、ワードラインWLと、ワードライン・コンタクトプラグC84、C94とを連結させる金属配線がさらに形成されうる。

30

【0155】

本実施形態では、1対のビットラインBL、BL'の上層に、ワードラインWLが形成されるが、他の実施形態では、ワードラインWLの上層に、1対のビットラインBL、BL'が形成される場合もある。

【0156】

再び図11を参照すれば、第1NMOSトランジスタPD21は、第1活性領域ACT21の上部に形成される第2ゲート電極GE22と、第1活性領域ACT21で、第2ゲート電極GE22の両脇に形成された第2コンタクトプラグC72及び第3コンタクトプラグC73と、によって定義される。ここで、第2コンタクトプラグC72は、第1NMOSトランジスタPD21のソースに対応し、第2ゲート電極GE22は、第1NMOSトランジスタPD21のゲートに対応し、第3コンタクトプラグC73は、第1NMOSトランジスタPD21のドレインに対応する。

40

【0157】

第1PMOSトランジスタPU21は、第2活性領域ACT22の上部に形成される第2ゲート電極GE22と、第2活性領域ACT22で、第2ゲート電極GE22の両脇に形成された第5コンタクトプラグC82及び第6コンタクトプラグC83と、によって定義される。ここで、第5コンタクトプラグC82は、第1PMOSトランジスタPU21のドレインに対応し、第2ゲート電極GE22は、第1PMOSトランジスタPU21のゲートに対応し、第6コンタクトプラグC83は、第1PMOSトランジスタPU21のソースに対応する。

【0158】

10

20

30

40

50

第2N MOSトランジスタPD22は、第1活性領域ACT21の上部に形成される第3ゲート電極GE23と、第1活性領域ACT21で、第3ゲート電極GE23の両脇に形成された第1コンタクトプラグC71及び第2コンタクトプラグC72と、によって定義される。ここで、第1コンタクトプラグC71は、第2N MOSトランジスタPD22のドレインに対応し、第3ゲート電極GE23は、第2N MOSトランジスタPD22のゲートに対応し、第2コンタクトプラグC72は、第2N MOSトランジスタPD22のソースに対応する。

## 【0159】

第2PMOSトランジスタPU22は、第3活性領域ACT23の上部に形成される第3ゲート電極GE23と、第3活性領域ACT23で、第3ゲート電極GE23の両脇に形成された第7コンタクトプラグC91及び第8コンタクトプラグC92と、によって定義される。ここで、第7コンタクトプラグC91は、第2PMOSトランジスタPU22のソースに対応し、第3ゲート電極GE23は、第2PMOSトランジスタPU22のゲートに対応し、第8コンタクトプラグC92は、第2PMOSトランジスタPU22のドレインに対応する。

10

## 【0160】

このとき、第1N MOSトランジスタPD21と第1PMOSトランジスタPU21は、第2ゲート電極GE22に共通して連結され、第2金属配線N22によって連結されることによって、第1インバータを構成する。また、第2N MOSトランジスタPD22と第2PMOSトランジスタPU22は、第3ゲート電極GE23に共通して連結され、第1金属配線N21によって連結されることによって、第2インバータを構成する。半導体メモリ装置3で、第1インバータ及び第2インバータは、ラッチを構成することによって、データを保存することができる。

20

## 【0161】

第3PMOSトランジスタPG21は、第2活性領域ACT22の上部に形成される第1ゲート電極GE21と、第2活性領域ACT22で、第1ゲート電極GE21の両脇に形成された第4コンタクトプラグC81及び第5コンタクトプラグC82と、によって定義される。ここで、第4コンタクトプラグC81及び第5コンタクトプラグC82は、第3PMOSトランジスタPG21のドレイン及びソースに対応し、第1ゲート電極GE21は、第3PMOSトランジスタPG21のゲートに対応する。このとき、第4コンタクトプラグC81は、ビットラインBLと連結され、第1ゲート電極GE21上のワードライン・コンタクトプラグC84は、ワードラインWLと連結される。ここで、第3PMOSトランジスタPG21は、第1パスゲートまたは第1伝達ゲートとして動作しうる。

30

## 【0162】

第4PMOSトランジスタPG22は、第3活性領域ACT23の上部に形成される第4ゲート電極GE24と、第3活性領域ACT23で、第4ゲート電極GE24の両脇に形成された第8コンタクトプラグC92及び第9コンタクトプラグC93によって定義される。ここで、第8コンタクトプラグC92及び第9コンタクトプラグC93は、第4PMOSトランジスタPG22のソース及びドレインに対応し、第4ゲート電極GE24は、第4PMOSトランジスタPG22のゲートに対応する。このとき、第9コンタクトプラグC93は、ビットラインバーBL'に連結され、第4ゲート電極GE24上のワードライン・コンタクトプラグC94は、ワードラインWLと連結される。ここで、第4PMOSトランジスタPG22は、第2パスゲートまたは第2伝達ゲートとして動作しうる。

40

## 【0163】

本実施形態による半導体メモリ装置3では、单一活性領域である第1活性領域ACT21に、第1N MOSトランジスタPD21及び第2N MOSトランジスタPD22を一列に形成する。これにより、第1N MOSトランジスタPD21及び第2N MOSトランジスタPD22それぞれに係わる2つの活性領域を別途に形成するために、複雑なパターニング工程を行う代わりに、単一パターニング工程で第1活性領域ACT21を形成できるので、パターニング工程が簡単になる。また、第1N MOSトランジスタPD21及び第

50

2 NMOSトランジスタPD22それぞれに係わる2つの活性領域の代わりに、単一活性領域を形成することによって、2つの活性領域間に素子分離膜を形成する必要がないので、半導体メモリ装置3の単位セルで、横方向の長さが縮小されることによって、全体的に素子の集積度を向上させることができる。

【0164】

また、本実施形態による半導体メモリ装置3は、第1活性領域ACT21に形成された第1NMOSトランジスタPD21及び第2NMOSトランジスタPD22は、接地電極ラインVssに連結される第2コントラクトプラグC72を共有する。これにより、第1NMOSトランジスタPD21及び第2NMOSトランジスタPD22それぞれに対して接地電極Vssを印加するための2つのコントラクトプラグを別途に形成する必要がないので、半導体メモリ装置3の単位セルで、縦方向の長さが縮小されることによって、全体的に素子の集積度を向上させることができる。

10

【0165】

さらに、本実施形態による半導体メモリ装置3は、第1活性領域ACT21、第2活性領域ACT22及び第3活性領域ACT23が互いに平行するように形成され、第2活性領域ACT22では、第1NMOSトランジスタPD21に対応する位置に、第1PMOSトランジスタPDU21が配され、第2NMOSトランジスタPD22に対応する位置に、第3PMOSトランジスタPG21が配され、第3活性領域ACT23では、第1NMOSトランジスタPD21に対応する位置に、第4PMOSトランジスタPG22が配され、第2NMOSトランジスタPD22に対応する位置に、第2PMOSトランジスタPDU22が配される。このように、半導体メモリ装置3の単位セルで、第1NMOSトランジスタPD21及び第2NMOSトランジスタPD22を中心に対称になる形態に他のトランジスタが配されることによって、半導体メモリ装置3の集積度をさらに向上させることができる。また、半導体メモリ装置3で、複数の単位セルが配されるときにも、境界領域に追加領域が要求されない。

20

【0166】

前述のように、本実施形態によれば、半導体メモリ素子3で、単一活性領域にNチャネル・トランジスタを形成し、Pチャネル・トランジスタまたは他の素子は、Nチャネル・トランジスタに対して対称的に配されうる。本実施形態で、半導体メモリ装置3は、6個のトランジスタを含んでいるが、他の実施形態では、半導体メモリ装置3は、4個のトランジスタ及び2個の抵抗素子を含むことができ、さらに他の実施形態では、半導体メモリ装置3は、さらに多数のトランジスタを含むことができ、さらに他の実施形態では、半導体メモリ装置3は、さらに少數のトランジスタを含むこともできる。

30

【0167】

図15は、図11の半導体メモリ装置の等価回路を示す回路図である。

【0168】

図15を参照すれば、半導体メモリ装置3は、第1Nウェル領域NW1に配される第1PMOSトランジスタPDU21及び第3PMOSトランジスタPG21、Pウェル領域PWに配される第1NMOSトランジスタPD21及び第2NMOSトランジスタPD22、及び第2Nウェル領域NW2に配される第2PMOSトランジスタPDU22及び第4PMOSトランジスタPG22を含む。このとき、第1NMOSトランジスタPD21及び第1PMOSトランジスタPDU21は、第1インバータを構成し、第2NMOSトランジスタPD22及び第2PMOSトランジスタPDU22は、第2インバータを構成する。

40

【0169】

第3PMOSトランジスタPG21は、ワードラインWLに印加される電圧によってオン／オフになり、ビットラインBLを第1ノードN21に連結させることができる。ここで、第1ノードN21は、図11に図示された第1金属配線N21に対応する。具体的には、ワードラインWLに印加される電圧が論理「0」であるとき、第3NMOSトランジスタPG21は、ターンオンされ、ビットラインBLを第1ノードN21に連結させることができる。第1ノードN21は、第2インバータの入力端子、すなわち、第2NMOS

50

トランジスタ P D 2 2 のゲートと、第 2 PMOS トランジスタ P U 2 2 のゲートとに連結され、また、第 1 インバータの出力端子、すなわち、第 1 NMOS トランジスタ P D 2 1 のドレインと、第 1 PMOS トランジスタ P U 2 1 のドレインとに連結される。

#### 【 0 1 7 0 】

第 4 PMOS トランジスタ P G 2 2 は、ワードライン W L に印加される電圧によってオン／オフになり、ビットラインバー B L ' を第 2 ノード N 2 2 に連結させることができる。ここで、第 2 ノード N 2 2 は、図 1 1 に図示された第 2 金属配線 N 2 2 に対応する。具体的には、ワードライン W L に印加される電圧が論理「1」であるとき、第 4 PMOS トランジスタ P G 2 2 はターンオンされ、ビットラインバー B L ' を第 2 ノード N 2 2 に連結させることができる。第 2 ノード N 2 2 は、第 1 インバータの入力端子、すなわち、第 1 NMOS トランジスタ P D 2 1 のゲートと、第 1 PMOS トランジスタ P U 2 1 のゲートとに連結され、また、第 2 インバータの出力端子、すなわち、第 2 NMOS トランジスタ P D 2 2 のドレインと、第 2 PMOS トランジスタ P U 2 2 のドレインとに連結される。

10

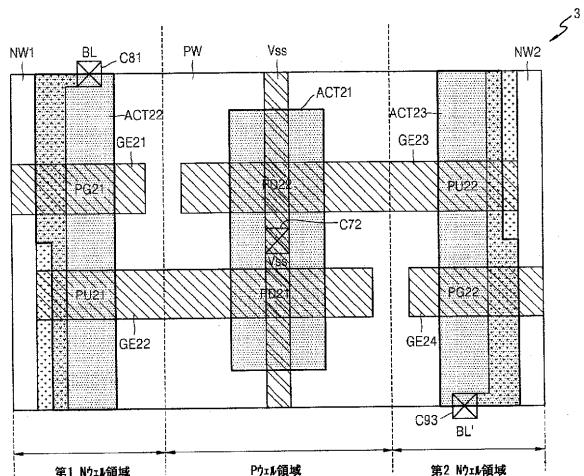

#### 【 0 1 7 1 】

図 1 6 は、図 1 1 の半導体メモリ装置の I I I - I I I ' 線に沿って切り取った断面図を示している。

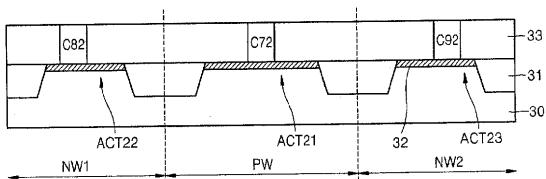

#### 【 0 1 7 2 】

図 1 6 を参照すれば、半導体メモリ装置 3 は、P ウェル領域 P W 、並びに第 1 N ウェル領域 N W 1 及び第 2 N ウェル領域 N W 2 を有する基板 3 0 上に形成される。ここで、基板 3 0 は、図 6 を参照して説明した基板 1 0 と実質的に同一に具現されるので、これに係わる詳細な説明は省略する。

20

#### 【 0 1 7 3 】

P ウェル領域 P W は、基板 3 0 に P 型イオンを注入することによって形成され、第 1 N ウェル領域 N W 1 及び第 2 N ウェル領域 N W 2 は、基板 3 0 に N 型イオンを注入することによって形成されうる。P ウェル領域 P W 、並びに第 1 N ウェル領域 N W 1 及び第 2 N ウェル領域 N W 2 には、素子分離膜 3 1 によって画定される第 1 活性領域 A C T 2 1 、第 2 活性領域 A C T 2 2 及び第 3 活性領域 A C T 2 3 がそれぞれ配されうる。ここで、素子分離膜 3 1 は、S T I であります。第 1 活性領域 A C T 2 1 、第 2 活性領域 A C T 2 2 及び第 3 活性領域 A C T 2 3 上には、シリサイド層 3 2 が形成されうる。

30

#### 【 0 1 7 4 】

基板 3 0 の上部には、第 1 絶縁層 3 3 が配され、第 1 絶縁層 3 3 には、第 5 コンタクトプラグ C 8 2 、第 2 コンタクトプラグ C 7 2 及び第 8 コンタクトプラグ C 9 2 が配される。このとき、第 5 コンタクトプラグ C 8 2 は、第 2 活性領域 A C T 2 2 に連結され、第 2 コンタクトプラグ C 7 2 は、第 1 活性領域 A C T 2 1 に連結され、第 8 コンタクトプラグ C 9 2 は、第 3 活性領域 A C T 2 3 にそれぞれ連結される。第 1 絶縁層 3 3 の上部には、第 2 絶縁層 3 4 が配され、第 2 絶縁層 3 4 には、第 1 金属配線 N 2 1 、第 2 金属配線 N 2 2 及び第 3 金属配線 N 2 3 が配される。ここで、第 3 金属配線 N 2 3 は、接地電極ライン V s s を第 1 活性領域 A C T 2 1 に連結させるための配線である。

40

#### 【 0 1 7 5 】

第 2 絶縁層 3 4 の上部には、第 3 絶縁層 3 5 が配され、第 3 絶縁層 3 5 には、ビアプラグ V が配される。第 3 絶縁層 3 5 の上部には、第 4 絶縁層 3 6 が配され、第 4 絶縁層 3 6 には、1 対のビットライン B L 、B L ' と接地電極ライン V s s とが配される。第 4 絶縁層 3 6 の上部には、第 5 絶縁層 3 7 が配され、第 5 絶縁層 3 7 の上部には、ワードライン W L が配される。ここで、第 1 絶縁層ないし第 5 絶縁層 3 3 、3 4 、3 5 、3 6 、3 7 は、図 6 を参照して説明した第 1 絶縁層ないし第 5 絶縁層 1 3 、1 4 、1 5 、1 6 、1 7 と実質的に同一に具現されるので、これに係わる詳細な説明は省略する。

#### 【 0 1 7 6 】

図 1 7 は、図 1 1 の半導体メモリ装置の I V - I V ' 線に沿って切り取った断面図を示している。

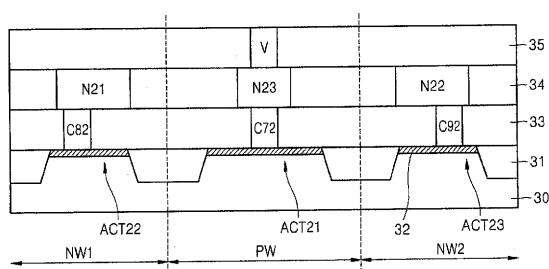

#### 【 0 1 7 7 】

図17を参照すれば、半導体メモリ装置3は、Pウェル領域PWを有する基板30上に形成される。このとき、Pウェル領域PWは、基板30に形成される素子分離膜31によって画定される。

#### 【0178】

Pウェル領域PW上には、第1ゲートスタックGS1及び第2ゲートスタックGS2が配される。第1ゲートスタックGS1及び第2ゲートスタックGS2は、ゲート絶縁膜331、ゲート電極層GE及びキャッピング膜332を含むことができる。具体的には、第1ゲートスタックGS1及び第2ゲートスタックGS2は、Pウェル領域PW上に、順次にゲート絶縁膜331、ゲート電極層GE及びキャッピング膜332を形成した後、これをパターニングすることによって形成されうる。第1ゲートスタックGS1及び第2ゲートスタックGS2の側壁には、スペーサ333が配される。ここで、ゲート絶縁膜331、キャッピング膜332及びスペーサ333は、図7を参照して説明したゲート絶縁膜131、キャッピング膜132及びスペーサ133と実質的に同一に具現されるので、これに係わる詳細な説明は省略する。

10

#### 【0179】

第1ゲートスタックGS1及び第2ゲートスタックGS2の上部には、第1絶縁層33が配され、第1絶縁層33には、第1コンタクトプラグC71、第2コンタクトプラグ72及び第3コンタクトプラグC73が配される。このとき、複数のコンタクトプラグC71、C72、C73は、ソース領域及びドレイン領域311、312、313にそれぞれ連結される。図示されていないが、ソース領域及びドレイン領域311、312、313の上部には、シリサイド層が形成されうる。

20

#### 【0180】

第1絶縁層33の上部には、第2絶縁層34が配され、第2絶縁層34には、第1金属配線N21、第2金属配線N22及び第3金属配線N23が配される。第2絶縁層34の上部には、第3絶縁層35が配され、第3絶縁層35には、ビアプラグVが配される。ビアプラグVの上部には、接地電極ラインVssが配される。

#### 【0181】

図18Aないし18Gは、本発明の他の実施形態による半導体メモリ装置の製造方法を示す断面図である。

#### 【0182】

図18Aを参照すれば、基板30は、NMOSトランジスタが形成されるPウェル領域PW、PMOSトランジスタが形成される第1Nウェル領域NW1、及び第2Nウェル領域NW2を含む。Pウェル領域PWには、第1活性領域ACT21が形成され、第1Nウェル領域NW1及び第2Nウェル領域NW2には、第2活性領域ACT22及び第3活性領域ACT23が形成されるが、第1活性領域ACT21、第2活性領域ACT22及び第3活性領域ACT23は、STIのような素子分離膜31によって画定されうる。

30

#### 【0183】

図18Bを参照すれば、第1活性領域ACT21、第2活性領域ACT22及び第3活性領域ACT23上には、シリサイド膜32が形成される。具体的には、基板30上に金属層(図示せず)を形成し、金属層が形成された基板30に対して熱処理を行うことによって、第1活性領域ACT21、第2活性領域ACT22及び第3活性領域ACT23上にシリサイド膜32を形成できる。このように、シリサイド膜32を形成することによって、第1活性領域ACT21、第2活性領域ACT22及び第3活性領域ACT23と、以後に形成されるコンタクトプラグとのコンタクト抵抗を低くすることができる。

40

#### 【0184】

図18Cを参照すれば、基板30の上部に、第1絶縁層33を形成する。次に、第1絶縁層33上に、フォトリソグラフィ工程によって、複数の第1コンタクトホール(図示せず)が形成される領域を露出させるマスク膜を形成する。次に、乾式エッチング工程を利用し、第1絶縁層33上に、第1コンタクトホールを形成し、第1コンタクトホールを金属物質で埋め込むことによって、第5コンタクトプラグC82、第2コンタクトプラグC

50

7 2 及び第 8 コンタクトプラグ C 9 2 を形成する。ここで、第 5 コンタクトプラグ C 8 2 , 第 2 コンタクトプラグ C 7 2 及び第 8 コンタクトプラグ C 9 2 は、図 8 C を参照して説明した第 5 コンタクトプラグ C 2 2 , 第 2 コンタクトプラグ C 1 2 及び第 8 コンタクトプラグ C 3 2 と実質的に同一に具現されるので、これに係わる詳細な説明は省略する。

#### 【 0 1 8 5 】

図 18 D を参照すれば、第 1 絶縁層 3 3 の上部に、第 2 絶縁層 3 4 を形成する。次に、第 2 絶縁層 3 4 内に複数の第 2 コンタクトホールを形成し、複数の第 2 コンタクトホールを金属物質で埋め込むことによって、第 1 金属配線 N 2 1 , 第 2 金属配線 N 2 2 及び第 3 金属配線 N 2 3 を形成できる。

#### 【 0 1 8 6 】

図 18 E を参照すれば、第 2 絶縁層 3 4 の上部に、第 3 絶縁層 3 5 を形成する。次に、第 3 絶縁層 3 5 内に第 3 コンタクトホールを形成し、第 3 コンタクトホールを金属物質で埋め込むことによって、ビアプラグ V を形成できる。ここで、ビアプラグ V は、図 8 E を参照して説明したビアプラグ V と実質的に同一に具現されるので、これに係わる詳細な説明は省略する。

#### 【 0 1 8 7 】

図 18 F を参照すれば、第 3 絶縁層 3 5 の上部に、第 4 絶縁層 3 6 を形成する。次に、第 4 絶縁層 3 6 内に複数の第 4 コンタクトホールを形成し、複数の第 4 コンタクトホールを金属物質で埋め込むことによって、ビットライン BL 、接地電極ライン V ss 及びビットラインバー BL ' を形成できる。他の実施形態では、ビットライン BL 及びビットラインバー BL ' を接地電極ライン V ss と異なる層に形成できる。さらに他の実施形態では、ビットライン BL 、ビットラインバー BL ' 及び接地電極ライン V ss を、第 1 金属配線 N 2 1 , 第 2 金属配線 N 2 2 及び第 3 金属配線 N 2 3 の下層に形成することもできる。

#### 【 0 1 8 8 】

図 18 G を参照すれば、第 4 絶縁層 3 6 の上部に、第 5 絶縁層 3 7 及びワードライン WL を順次に形成する。他の実施形態では、ワードライン WL は、ビットライン BL , ビットラインバー BL ' の下層に形成できる。さらに他の実施形態では、ワードライン WL は、第 1 金属配線 N 2 1 , 第 2 金属配線 N 2 2 及び第 3 金属配線 N 2 3 の下層に形成することもできる。

#### 【 0 1 8 9 】

図 19 は、本発明のさらに他の実施形態による半導体メモリ装置を示すレイアウトである。

#### 【 0 1 9 0 】

図 19 を参照すれば、半導体メモリ装置 4 は、第 1 P ウェル領域 PW 1 、並びに第 1 P ウェル領域 PW 1 の両脇に形成される第 1 N ウェル領域 NW 1 及び第 2 N ウェル領域 NW 2 ; 第 2 P ウェル領域 PW 2 、並びに第 2 P ウェル領域 PW 2 の両脇に形成される第 2 及び第 3 N ウェル領域 NW 2 , NW 3 ; を有する基板上に形成される 2 つの S R A M セルを含み、 2 ピットで動作しうる。

#### 【 0 1 9 1 】

第 1 P ウェル領域 PW 1 及び第 2 P ウェル領域 PW 2 は、例えば、イオン注入工程によって基板上に形成される P 型ウェルが配される領域であり、第 1 P ウェル領域 PW 1 及び第 2 P ウェル領域 PW 2 には、素子分離膜によって画定される第 1 活性領域 S C T 2 1 及び第 4 活性領域 A C T 2 4 がそれぞれ配される。本実施形態で、第 1 活性領域 S C T 2 1 及び第 4 活性領域 A C T 2 4 は、縦方向に長い形態を有するバータイプの単一活性領域であります。

#### 【 0 1 9 2 】

このとき、第 1 活性領域 A C T 2 1 に、 N + 型不純物をドーピングすることによって、 N 型拡散領域が形成され、また、コンタクトプラグ C 7 1 , C 7 2 , C 7 3 が形成されうる。第 1 活性領域 A C T 2 1 には、 2 つのプルダウン素子が一列に形成されうるが、本実施形態で、 2 つのプルダウン素子は、第 1 N M O S ドランジスタ P D 2 1 及び第 2 N M O

10

20

30

40

50

SトランジスタPD22でありうる。また、第4活性領域ACT24に、N+不純物をドーピングすることによって、N型拡散領域が形成され、また、コンタクトプラグC101,C102,C103が形成されうる。第4活性領域ACT24には、2つのプルダウン素子が一列に形成されうるが、本実施形態で、2つのプルダウン素子は、第3NMOSトランジスタPD23及び第4NMOSトランジスタPD24でありうる。

#### 【0193】

第1Nウェル領域NW1は、例えば、イオン注入工程によって基板上に形成されるN型ウェルが配される領域であり、第1Nウェル領域NW1には、素子分離膜によって画定される第2活性領域ACT22が配される。本実施形態で、第2活性領域ACT22は、第1活性領域SCT21及び第4活性領域ACT24に平行した方向に伸張する形態を有する单一活性領域でありうる。10

#### 【0194】

このとき、第2活性領域ACT22に、P+型不純物をドーピングすることによって、P型拡散領域が形成され、また、コンタクトプラグC81,C82,C83が形成されうる。第2活性領域ACT22には、1つのプルアップ素子と、1つのアクセス素子とが形成されうるが、本実施形態で、プルアップ素子は、第1PMOSトランジスタPU21であり、アクセス素子は、第3PMOSトランジスタPG21でありうる。

#### 【0195】

第2Nウェル領域NW2は、例えば、イオン注入工程によって基板上に形成されるN型ウェルが配される領域であり、第2Nウェル領域NW2には、素子分離膜によって画定される第3活性領域ACT23及び第5活性領域ACT25が配される。本実施形態で、第3活性領域ACT23及び第5活性領域ACT25は、第1活性領域SCT21及び第4活性領域ACT24に平行した方向に伸張する形態を有する单一活性領域でありうる。20

#### 【0196】

このとき、第3活性領域ACT23に、P+型不純物をドーピングすることによって、P型拡散領域が形成され、また、複数のコンタクトプラグC91,C92,C93が形成されうる。第3活性領域ACT23には、1つのプルアップ素子と、1つのアクセス素子とが形成されうるが、本実施形態で、プルアップ素子は、第2PMOSトランジスタPU22であり、アクセス素子は、第4PMOSトランジスタPG22でありうる。

#### 【0197】

また、第5活性領域ACT25に、P+型不純物をドーピングすることによって、P型拡散領域が形成され、また、複数のコンタクトプラグC111,C112,C113が形成されうる。第5活性領域ACT25には、1つのプルアップ素子と、1つのアクセス素子とが形成されうるが、本実施形態で、プルアップ素子は、第5PMOSトランジスタPU23であり、アクセス素子は、第7PMOSトランジスタPG23でありうる。30

#### 【0198】

第3Nウェル領域NM3は、例えば、イオン注入工程によって基板上に形成されるN型ウェルが配される領域であり、第3Nウェル領域NW3には、素子分離膜によって画定される第6活性領域ACT26が配される。本実施形態で、第6活性領域ACT26は、第1活性領域SCT21及び第4活性領域ACT24に平行した方向に伸張する形態を有する单一活性領域でありうる。40

#### 【0199】

このとき、第6活性領域ACT26に、P+型不純物をドーピングすることによって、P型拡散領域が形成され、また、複数のコンタクトプラグC121,C122,C123が形成されうる。第6活性領域ACT26には、1つのプルアップ素子と、1つのアクセス素子とが形成されうるが、本実施形態で、プルアップ素子は、第6PMOSトランジスタPU24であり、アクセス素子は、第8PMOSトランジスタPG24でありうる。

#### 【0200】

本実施形態によれば、隣接したPウェル領域とNウェル領域との幅が実質的にほぼ同じであり、具体的には、第1Pウェル領域PW1,第2Nウェル領域NW2及び第2Pウェ

50

ル領域 P W 2 の幅は実質的にほぼ同じである。これにより、半導体メモリ装置 3 の製造工程において、ウェル領域を形成するためのパターニング工程がさらに容易に遂行されうる。

#### 【 0 2 0 1 】

また、本実施形態によれば、第 1 活性領域 A C T 2 1 及び第 3 活性領域 A C T 2 3 、並びに第 5 活性層 A C T 2 5 及び第 4 活性領域 A C T 2 4 は、互いに対称的な構造を有することができる。これにより、半導体メモリ装置 3 の製造工程において、活性領域を形成するためのフォト工程がさらに容易に遂行されうる。

#### 【 0 2 0 2 】

第 1 活性領域ないし第 6 活性領域 A C T 2 1 , A C T 2 2 , A C T 2 3 , A C T 2 4 , A C T 2 5 , A C T 2 6 が配された基板の上部には、第 1 ゲート電極ないし第 7 ゲート電極 G E 2 1 , G E 2 2 , G E 2 3 , G E 2 4 , G E 2 5 , G E 2 6 , G E 2 7 が形成される。具体的には、第 1 ゲート電極 G E 2 1 は、第 2 活性領域 A C T 2 2 を横切る方向に形成され、第 2 ゲート電極 G E 2 2 は、第 1 活性領域 A C T 2 1 及び第 2 活性領域 A C T 2 2 を横切る方向に形成され、第 3 ゲート電極 G E 2 3 は、第 1 活性領域 A C T 2 1 及び第 3 活性領域 A C T 2 3 を横切る方向に形成され、第 4 ゲート電極 G E 2 4 は、第 3 活性領域 A C T 2 3 及び第 5 活性領域 A C T 2 5 を横切る方向に形成される。また、第 5 ゲート電極 G E 2 5 は、第 4 活性領域 A C T 2 4 及び第 5 活性領域 A C T 2 5 を横切る方向に形成され、第 6 ゲート電極 G E 2 6 は、第 4 活性領域 A C T 2 4 及び第 6 活性領域 A C T 2 6 を横切る方向に形成され、第 7 ゲート電極 G E 2 7 は、第 6 活性領域 A C T 2 6 を横切る方向に形成される。このとき、第 1 ゲート電極 G E 2 1 , 第 4 ゲート電極 G E 2 4 及び第 7 ゲート電極 G E 2 7 の上部には、それぞれワードライン・コンタクトプラグ C 8 4 , C 9 4 , C 1 2 4 が形成され、第 2 ゲート電極 G E 2 2 , 第 3 ゲート電極 G E 2 3 , 第 5 ゲート電極 G E 2 5 及び第 6 ゲート電極 G E 2 6 の上部には、それぞれ配線コンタクトプラグ C 7 5 , C 7 4 , C 1 0 5 , C 1 0 4 が形成される。10 20

#### 【 0 2 0 3 】

第 1 ゲート電極ないし第 7 ゲート電極 G E 2 1 , G E 2 2 , G E 2 3 , G E 2 4 , G E 2 5 , G E 2 6 , G E 2 7 が形成された基板の上部には、第 1 金属配線ないし第 4 金属配線 N 2 1 , N 2 2 , N 2 3 , N 2 4 が形成される。このとき、第 1 金属配線 N 2 1 は、第 1 活性領域 A C T 2 1 に形成されたコンタクトプラグ C 7 3 , 第 2 活性領域 A C T 2 2 に形成されたコンタクトプラグ C 8 2 及び第 3 ゲート電極 G E 2 3 に形成された配線コンタクトプラグ C 7 4 を連結させる。また、第 2 金属配線 N 2 2 は、第 1 活性領域 A C T 2 1 に形成されたコンタクトプラグ C 7 1 , 第 3 活性領域 A C T 2 3 に形成されたコンタクトプラグ C 9 2 及び第 2 ゲート電極 G E 2 2 に形成された配線コンタクトプラグ C 7 5 を連結させる。また、第 3 金属配線 N 2 3 は、第 4 活性領域 A C T 2 4 に形成されたコンタクトプラグ C 1 0 1 、第 5 活性領域 A C T 2 5 に形成されたコンタクトプラグ C 1 1 2 、及び第 6 ゲート電極 G E 2 6 に形成された配線コンタクトプラグ C 1 0 4 を連結させる。また、第 4 金属配線 N 2 4 は、第 4 活性領域 A C T 2 4 に形成されたコンタクトプラグ C 1 0 3 , 第 6 活性領域 A C T 2 6 に形成されたコンタクトプラグ C 1 2 2 及び第 5 ゲート電極 G E 2 5 に形成された配線コンタクトプラグ C 1 0 5 を連結させる。30 40

#### 【 0 2 0 4 】

本実施形態によれば、半導体メモリ装置 4 で、第 1 PMOS トランジスタ P U 2 1 , 第 1 NMOS トランジスタ P D 2 1 , 第 4 PMOS トランジスタ P G 2 2 , 第 7 PMOS トランジスタ P G 2 3 , 第 4 NMOS トランジスタ P D 2 4 及び第 6 PMOS トランジスタ P U 2 4 を横方向に一列に配し、第 3 PMOS トランジスタ P G 2 1 , 第 2 NMOS トランジスタ P D 2 2 , 第 2 PMOS トランジスタ P U 2 2 , 第 5 PMOS トランジスタ P U 2 3 , 第 3 NMOS トランジスタ P D 2 3 及び第 8 PMOS トランジスタ P G 2 4 を横方向に一列に配しうる。

#### 【 0 2 0 5 】

また、半導体メモリ装置 4 で、第 1 PMOS トランジスタ P U 2 1 及び第 3 PMOS T50

ランジスタ PG21を、第1Nウェル領域NW1に縦方向に一列に配し、第1NMOSトランジスタPD21及び第2NMOSトランジスタPD22を、第1Pウェル領域PW1に縦方向に一列に配し、第4PMOSトランジスタPG22及び第2PMOSトランジスタPU22を、第2Nウェル領域NW2に縦方向に一列に配し、第7PMOSPG23及び第5PMOSトランジスタPU23を、第2Nウェル領域NW2に縦方向に一列に配し、第4NMOSトランジスタPD24及び第3NMOSトランジスタPD23を、第2Pウェル領域PW2に縦方向に一列に配し、第6PMOSトランジスタPU24及び第8PMOSトランジスタPG24を第3Nウェル領域NM3に縦方向に一列に配しうる。

## 【0206】

図20は、図19の半導体メモリ装置の等価回路を示す回路図である。 10

## 【0207】

図20を参照すれば、半導体メモリ装置4は、第1Nウェル領域NW1に配される第1PMOSトランジスタPU21、第3PMOSトランジスタPG21；第1Pウェル領域PW1に配される第1NMOSトランジスタPD21、第2NMOSトランジスタPD22；第2Nウェル領域NW2に配される第2PMOSトランジスタPU22、第4PMOSトランジスタPG22、第5PMOSトランジスタPU23及び第7PMOSトランジスタPG23；第2Pウェル領域PW2に配される第3NMOSトランジスタPD23、第4NMOSトランジスタPD24；第3Nウェル領域NW3に配される第6PMOSトランジスタPU24、第8PMOSトランジスタPG24；を含む。

## 【0208】

このとき、第1NMOSトランジスタPD21及び第1PMOSトランジスタPU21は、第1インバータを構成し、第2NMOSトランジスタPD22及び第2PMOSトランジスタPU22は、第2インバータを構成し、第3NMOSトランジスタPD23及び第5PMOSトランジスタPU23は、第3インバータを構成し、第4NMOSトランジスタPD24及び第6PMOSトランジスタPU24は、第4インバータを構成する。 20

## 【0209】

第3PMOSトランジスタPG21は、ワードラインWLに印加される電圧によってオン／オフになり、ビットラインBL1を第1ノードN21に連結させることができる。ここで、第1ノードN21は、図19に図示された第1金属配線N21に対応する。具体的には、ワードラインWLに印加される電圧が、論理「0」であるとき、第3PMOSトランジスタPG21はターンオンされ、ビットラインBL1を、第1ノードN21に連結させることができる。第1ノードN21は、第2インバータの入力端子、すなわち、第2NMOSトランジスタPD22のゲートと、第2PMOSトランジスタPU22のゲートとに連結され、また、第1インバータの出力端子、すなわち、第1NMOSトランジスタPD21のドレインと、第1PMOSトランジスタPU21のドレインとに連結される。 30

## 【0210】

第4PMOSトランジスタPG22は、ワードラインWLに印加される電圧によって、オン／オフになり、ビットラインバーBL1'を第2ノードN22に連結させることができる。ここで、第2ノードN22は、図19に図示された第2金属配線N22に対応する。具体的には、ワードラインWLに印加される電圧が、論理「0」であるとき、第4PMOSトランジスタPG22はターンオンされ、ビットラインバーBL1'を第2ノードN22に連結させることができる。第2ノードN22は、第1インバータの入力端子、すなわち、第1NMOSトランジスタPD21のゲートと、第1PMOSトランジスタPU21のゲートとに連結され、また、第2インバータの出力端子、すなわち、第2NMOSトランジスタPD22のドレインと、第2PMOSトランジスタPU22のドレインとに連結される。 40

## 【0211】

第7PMOSトランジスタPG23は、ワードラインWLに印加される電圧によってオン／オフになり、ビットラインバーBL2'を第3ノードN23に連結させることができる。ここで、第3ノードN23は、図19に図示された第3金属配線N23に対応する。 50

具体的には、ワードラインWLに印加される電圧が、論理「0」であるとき、第7PMOSトランジスタPG23はターンオンされ、ビットラインバーBL2'を第3ノードN23に連結させることができる。第3ノードN23は、第4インバータの入力端子、すなわち、第4NMOSトランジスタPD24のゲートと、第6PMOSトランジスタPU24のゲートとに連結され、また、第3インバータの出力端子、すなわち、第3NMOSトランジスタPM23のドレインと、第5PMOSトランジスタPU23のドレインとに連結される。

#### 【0212】

第8PMOSトランジスタPG24は、ワードラインWLに印加される電圧によってオン／オフになり、ビットラインBL2を第4ノードN24に連結させることができる。ここで、第4ノードN24は、図19に図示された第4金属配線N24に対応する。具体的には、ワードラインWLに印加される電圧が、論理「0」であるとき、第8PMOSトランジスタPG24はターンオンされ、ビットラインBL2を第4ノードN24に連結させることができる。第4ノードN24は、第3インバータの入力端子、すなわち、第3NMOSトランジスタPD23のゲートと、第5PMOSトランジスタPU23のゲートとに連結され、また、第4インバータの出力端子、すなわち、第4NMOSトランジスタPD24のドレインと、第6PMOSトランジスタPU24のドレインとに連結される。

#### 【0213】

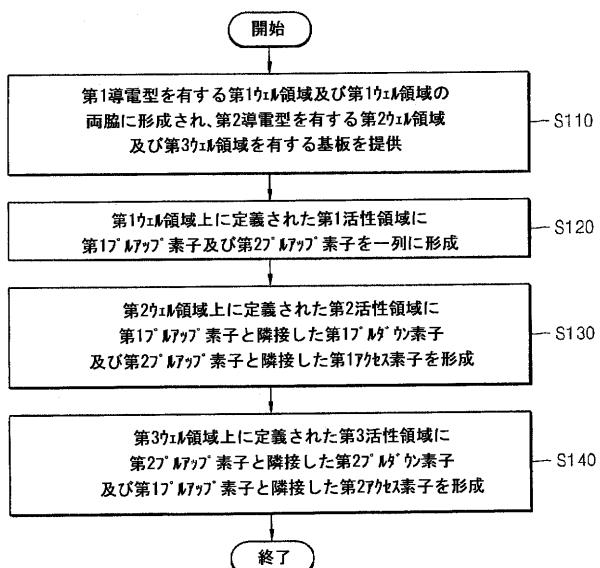

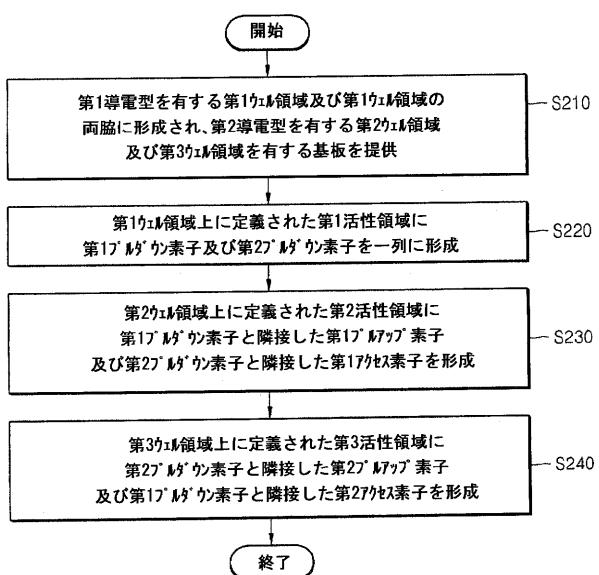

図21は、本発明の一実施形態による半導体メモリ装置の製造方法を示すフローチャートである。

#### 【0214】

図21の半導体メモリ装置の製造方法は、図1ないし図10に図示された半導体メモリ装置を製造する過程を示している。従って、図1ないし図10で説明した内容は、本実施形態にも適用されうる。

#### 【0215】

図22は、本発明の他の実施形態による半導体メモリ装置の製造方法を示すフローチャートである。

#### 【0216】

S110段階で、第1導電型を有する第1ウェル領域と、第1ウェル領域の両脇に形成されて第2導電型を有する第2ウェル領域及び第3ウェル領域と、を有する基板を提供する。

#### 【0217】

S120段階で、第1ウェル領域上に定義された第1活性領域に、第1プルアップ素子及び第2プルアップ素子を一列に形成する。

#### 【0218】

S130段階で、第2ウェル領域上に定義された第2活性領域に、第1プルアップ素子と隣接した第1プルダウン素子と、第2プルアップ素子と隣接した第1アクセス素子と、を形成する。

#### 【0219】

S140段階で、第3ウェル領域上に定義された第3活性領域に、第2プルアップ素子と隣接した第2プルダウン素子と、第1プルアップ素子と隣接した第2アクセス素子と、を形成する。

#### 【0220】

本実施形態で、第1プルアップ素子及び第2プルアップ素子は、第1方向に沿って一列に形成され、第1プルアップ素子は、第1方向と垂直である第2方向に沿って、第1プルダウン素子及び第2アクセス素子と隣接するように配され、第2プルアップ素子は、第2方向に沿って、第2プルダウン素子及び第1アクセス素子と隣接するように配されうる。

#### 【0221】

また、前記製造方法は、第1活性領域、第2活性領域及び第3活性領域のうち少なくとも1つの領域の上部を横切る方向に基板の上部に形成される複数の導電性パターンを形成

する段階をさらに含むことができる。このとき、第1プルアップ素子と第1プルダウン素子は、複数の導電性パターンのうち一つに共通して連結されて第1インバータを構成し、第2プルアップ素子と第2プルダウン素子は、複数の導電性パターンのうち他の一つに共通して連結されて第2インバータを構成できる。

#### 【0222】

また、前記製造方法は、第1アクセス素子の一端を、第2インバータの入力端子及び第1インバータの出力端子に連結させる第1金属配線；第2アクセス素子の一端を第1インバータの入力端子及び第2インバータの出力端子に連結させる第2金属配線；を形成する段階をさらに含むことができる。一実施形態で、第1金属配線及び第2金属配線は、同一層に形成されうる。他の実施形態で、第1金属配線及び第2金属配線は、互いに異なる層に形成される場合もある。

10

#### 【0223】

ここで、第1金属配線及び第2金属配線を形成する段階は、基板の上部に第1絶縁膜を形成する段階、第1絶縁膜の一部領域をエッチングして複数の第1コンタクトホールを形成し、複数の第1コンタクトホールに金属物質を充填して複数のコンタクトプラグを形成する段階、複数のコンタクトプラグが形成された第1絶縁膜上に第2絶縁膜を形成する段階、及び第2絶縁膜の一部領域をエッチングして複数の第2コンタクトホールを形成し、複数の第2コンタクトホールに金属物質を充填し、前記第1金属配線及び第2金属配線を形成する段階を含むことができる。第1金属配線及び第2金属配線は、複数のコンタクトプラグを介して、第1ウェル領域、第2ウェル領域及び第3ウェル領域のうち少なくとも一つに連結されうる。

20

#### 【0224】

また、前記製造方法は、第1ウェル領域、第2ウェル領域及び第3ウェル領域のうち少なくとも一つに、シリサイド層を形成する段階をさらに含むことができ、複数のコンタクトプラグは、シリサイド層に連結されうる。

#### 【0225】

また、前記製造方法は、第1方向に伸張するように、基板の上部に1対のビットラインを形成する段階をさらに含むことができ、1対のビットラインのうち第1ビットラインは、第1アクセス素子の一端に連結され、1対のビットラインのうち第2ビットラインは、第2アクセス素子の他端に連結されうる。

30

#### 【0226】

また、前記製造方法は、第1方向に伸張するように、基板の上部に電源電極ラインを形成する段階をさらに含むことができ、電源電極ラインは、第1プルアップ素子と第2プルアップ素子との間に形成されたコンタクトプラグを介して、第1プルアップ素子及び第2プルアップ素子に連結されうる。

#### 【0227】

また、前記製造方法は、第2方向に伸張するように、基板の上部にワードラインを形成する段階をさらに含むことができる。

#### 【0228】

図22の半導体メモリ装置の製造方法は、図11ないし図20に図示された半導体メモリ装置を製造する過程を示している。従って、図11ないし図20で説明した内容は、本実施形態にも適用されうる。

40

#### 【0229】

S210段階で、第1導電型を有する第1ウェル領域と、第1ウェル領域の両脇に形成されて第2導電型を有する第2ウェル領域及び第3ウェル領域と、を有する基板を提供する。

#### 【0230】

S220段階で、第1ウェル領域上に定義された第1活性領域に、第1プルダウン素子及び第2プルダウン素子を一列に形成する。

#### 【0231】

50

S 2 3 0 段階で、第 2 ウェル領域上に定義された第 2 活性領域に、第 1 プルダウン素子と隣接した第 1 プルアップ素子と、第 2 プルダウン素子と隣接した第 1 アクセス素子と、を形成する。

【 0 2 3 2 】

S 2 4 0 段階で、第 3 ウェル領域上に定義された第 3 活性領域に、第 2 プルダウン素子と隣接した第 2 プルアップ素子と、第 1 プルダウン素子と隣接した第 2 アクセス素子と、を形成する。

【 0 2 3 3 】

本実施形態で、第 1 プルダウン素子及び第 2 プルダウン素子は、第 1 方向に沿って一列に形成され、第 1 プルダウン素子は、第 1 方向と垂直である第 2 方向に沿って、第 1 プルアップ素子及び第 2 アクセス素子と隣接するように配され、第 2 プルダウン素子は、第 2 方向に沿って、第 2 プルアップ素子及び第 1 アクセス素子と隣接するように配されうる。

10

【 0 2 3 4 】

また、前記製造方法は、第 1 活性領域、第 2 活性領域及び第 3 活性領域のうち少なくとも 1 つの領域の上部を横切る方向に基板の上部に形成される複数の導電性パターンを形成する段階をさらに含み、第 1 プルダウン素子と第 1 プルアップ素子は、複数の導電性パターンのうち一つに共通して連結されて第 1 インバータを構成し、第 2 プルダウン素子と第 2 プルアップ素子は、複数の導電性パターンのうち他の一つに共通して連結されて第 2 インバータを構成できる。

【 0 2 3 5 】

また、前記製造方法は、第 1 アクセス素子の一端を、第 2 インバータの入力端子及び第 1 インバータの出力端子に連結させる第 1 金属配線と、第 2 アクセス素子の一端を第 1 インバータの入力端子及び第 2 インバータの出力端子に連結させる第 2 金属配線と、を形成する段階をさらに含むことができる。一実施形態で、第 1 金属配線及び第 2 金属配線は、同一層に形成されうる。他の実施形態で、第 1 金属配線及び第 2 金属配線は、互いに異なる層に形成される場合もある。

20

【 0 2 3 6 】

ここで、第 1 金属配線及び第 2 金属配線を形成する段階は、基板の上部に第 1 絶縁膜を形成する段階、第 1 絶縁膜の一部領域をエッチングして複数の第 1 コンタクトホールを形成し、複数の第 1 コンタクトホールに金属物質を充填して複数のコンタクトプラグを形成する段階、複数のコンタクトプラグが形成された第 1 絶縁膜上に第 2 絶縁膜を形成する段階、及び第 2 絶縁膜の一部領域をエッチングして複数の第 2 コンタクトホールを形成し、複数の第 2 コンタクトホールに金属物質を充填し、前記第 1 金属配線及び第 2 金属配線を形成する段階を含むことができる。第 1 金属配線及び第 2 金属配線は、複数のコンタクトプラグを介して、第 1 ウェル領域、第 2 ウェル領域及び第 3 ウェル領域のうち少なくとも一つに連結されうる。

30

【 0 2 3 7 】

また、前記製造方法は、第 1 ウェル領域、第 2 ウェル領域及び第 3 ウェル領域のうち少なくとも一つにシリサイド層を形成する段階をさらに含むことができ、複数のコンタクトプラグは、シリサイド層に連結されうる。

40

【 0 2 3 8 】

また、前記製造方法は、第 1 方向に伸張するように、基板の上部に 1 対のビットラインを形成する段階をさらに含むことができ、1 対のビットラインのうち第 1 ビットラインは、第 1 アクセス素子の一端に連結され、1 対のビットラインのうち第 2 ビットラインは、第 2 アクセス素子の他端に連結されうる。

【 0 2 3 9 】

また、前記製造方法は、第 1 方向に伸張するように、基板の上部に接地電極ラインを形成する段階をさらに含むことができ、接地電極ラインは、第 1 プルダウン素子と第 2 プルダウン素子との間に形成されたコンタクトプラグを介して、第 1 プルダウン素子及び第 2 プルダウン素子に連結されうる。

50

## 【0240】

また、前記製造方法は、第2方向に伸張するように、基板の上部にワードラインを形成する段階をさらに含むことができる。

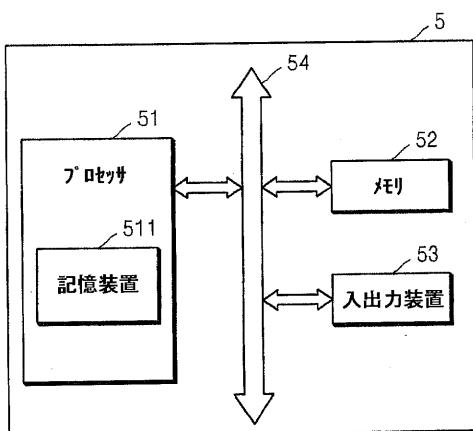

## 【0241】

図23は、本発明の一実施形態による電子システムの構成を概略的に示すブロック図である。

## 【0242】

図23を参照すれば、電子システム5は、プロセッサ51、メモリ部52及び入出力装置53を含むことができ、それらはバス(bus)54を利用して互いにデータ通信を行うことができる。プロセッサ51は、プログラムを実行してシステム5を制御する役割を行うことができる。入出力装置53は、システム5のデータを入力または出力するのに利用されうる。システム5は、入出力装置53を利用して、外部装置、例えば、パソコンまたはネットワークに連結され、外部装置と互いにデータを交換できる。メモリ部52は、プロセッサ51の動作のためのコード及びデータを保存することができる。ここで、プロセッサ51は、キャッシュメモリ、レジスター(register)、ラッチのような記憶装置511を含むことができるが、記憶装置511は、図1ないし図20の半導体メモリ装置を含むことができる。

10

## 【0243】