(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5274475号

(P5274475)

(45) 発行日 平成25年8月28日(2013.8.28)

(24) 登録日 平成25年5月24日(2013.5.24)

(51) Int.Cl.

F 1

H01L 23/532 (2006.01)

H01L 21/88

R

H01L 21/768 (2006.01)

H01L 21/90

A

H01L 21/3205 (2006.01)

請求項の数 7 (全 12 頁)

(21) 出願番号 特願2009-537248 (P2009-537248)

(86) (22) 出願日 平成19年9月10日 (2007.9.10)

(65) 公表番号 特表2010-519723 (P2010-519723A)

(43) 公表日 平成22年6月3日 (2010.6.3)

(86) 國際出願番号 PCT/US2007/077975

(87) 國際公開番号 WO2008/060745

(87) 國際公開日 平成20年5月22日 (2008.5.22)

審査請求日 平成22年5月21日 (2010.5.21)

(31) 優先権主張番号 11/560,044

(32) 優先日 平成18年11月15日 (2006.11.15)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】エレクトロマイグレーションに対する向上した信頼度を有する相互接続構造体及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

相互接続構造体であって、

内部に配置された少なくとも1つの導電性充填構造部を有する誘電体材料と、

前記少なくとも1つの導電性充填構造部を前記誘電体材料から分離する拡散障壁と、

前記少なくとも1つの導電性充填構造部内に配置され、前記少なくとも1つの導電性充填構造部の第1の導電性領域を前記少なくとも1つの導電性充填構造部の第2の導電性領域から少なくとも部分的に分離するエレクトロマイグレーション(EM)防止ライナと、

を備え、

前記少なくとも1つの導電性充填構造部および前記EM防止ライナは、前記誘電体材料に設けられた開口内に配置され、 10

前記第1の導電性領域と前記第2の導電性領域は同じ導電性材料からなり、

前記EM防止ライナは、TaN、Ru、RuN、RuTa、RuTaN、Ir、IrCu、又はCo(W、B、Mo、Re)からなり、U字形の断面形状を有し、前記拡散障壁の垂直壁の上部にのみ当接し、かつ前記誘電体材料には接していない、相互接続構造体。

## 【請求項2】

前記相互接続構造体は、平坦な表面を有し、当該平坦な表面上に設けられた誘電体キャップ層をさらに備える、請求項1に記載の相互接続構造体。

## 【請求項3】

前記誘電体材料は、 $\text{SiO}_2$ 、シリセスキオキサン、 $\text{Si}$ 、 $\text{C}$ 、 $\text{O}$ 及び $\text{H}$ 原子を含むCドープ酸化物、熱硬化性ポリアリーレンエーテル、又はこれらの多層から構成される、請求項1に記載の相互接続構造体。

【請求項4】

前記誘電体材料は、下部相互接続レベルの上に位置する上部相互接続レベルであり、前記下部相互接続レベルは、内部に埋め込まれた別の導電性構造部を有する別の誘電体材料を含む、請求項1に記載の相互接続構造体。

【請求項5】

前記上部相互接続レベル及び前記下部相互接続レベルは、誘電体キャップ層によって部分的に分離される、請求項4に記載の相互接続構造体。

10

【請求項6】

相互接続構造体を製造する方法であって、

誘電体材料内に少なくとも1つの開口部を設けるステップであって、前記少なくとも1つの開口部の内壁が拡散障壁で覆われる、ステップと、

前記少なくとも1つの開口部内に第1の導電性領域を形成するステップと、

少なくとも前記第1の導電性領域の表面上にエレクトロマイグレーション(EM)防止ライナを形成するステップと、

前記EM防止ライナ上に、前記少なくとも1つの開口部内の前記第1の導電性領域が形成されていない部分を充填するように、第2の導電性領域を形成するステップであって、前記第1及び第2の導電性領域が、前記誘電体材料内に導電性構造部を形成するステップと、を含み、

20

前記第1の導電性領域と前記第2の導電性領域は同じ導電性材料からなり、

前記EM防止ライナは、 $\text{TaN}$ 、 $\text{Ru}$ 、 $\text{RuN}$ 、 $\text{RuTa}$ 、 $\text{RuTaN}$ 、 $\text{Ir}$ 、 $\text{IrCu}$ 、又は $\text{Co(W, B, Mo, Re)}$ からなり、U字形の断面形状を有し、前記拡散障壁の垂直壁の上部にのみ当接し、かつ前記誘電体材料には接していない、方法。

【請求項7】

前記第2の導電性領域の形成後の前記相互接続構造体の表面を平坦化するステップと、平坦化された前記相互接続構造体の表面上に誘電体キャップ層を形成するステップと、をさらに含む、請求項6に記載の方法。

【発明の詳細な説明】

30

【技術分野】

【0001】

本発明は、半導体相互接続構造体及びその製造方法に関する。より具体的には、本発明は、エレクトロマイグレーション(EM)防止ライナが誘電体材料の導電性構造部内に存在する、エレクトロマイグレーション(EM)に対する向上した信頼度を有する半導体相互接続構造体に関する。

【背景技術】

【0002】

一般に、半導体デバイスは、半導体基板上に形成された、集積回路(IC)を形成する複数の回路を含む。基板の表面上に分布する回路素子を接続するために、信号経路の複雑なネットワークが通常、経路設定される。デバイス全体にわたるこれらの信号の効率的な経路設定は、例えば、シングル又はデュアル・ダマシン配線構造のようなマルチレベル又は多層方式の構成を必要とする。 $\text{Cu}$ ベースの相互接続部の方が、アルミニウム、すなわち $\text{Al}$ ベースの相互接続部と比べて、複雑な半導体チップ上の多数のトランジスタ間により高速の信号伝送をもたらすので、配線構造体は、典型的には銅、すなわち $\text{Cu}$ を含む。

40

【0003】

典型的な相互接続構造体内において、金属ビアは、半導体基板に対して垂直に延び、金属ラインは、半導体基板に対して平行に延びる。現在のIC製品のチップにおいては、誘電率が4.0より低い誘電体材料内に金属ライン及び金属ビア(例えば、導電性構造体)を埋め込むことによって、さらなる信号速度の向上及び隣接した金属ラインにおける(「ク

50

ロストーク」として知られる)信号の低減が達成されている。

【0004】

半導体相互接続構造体において、エレクトロマイグレーション(EM)が、1つの金属故障(metal failure)の機構として特定されている。EMは、超大規模集積(VLSI)回路についての信頼度に関する最も大きな懸念のうちの1つである。この問題は、プロセスを適格なものとするためにプロセス開発期間中に克服される必要があるのみならず、チップの寿命を通して、持続する。高い電流密度によって生じる金属イオンの移動が原因で、相互接続構造体の金属導体内部にボイドが生成される。

【0005】

金属相互接続部内の高速拡散経路は、チップ形成のために用いられる全体的な組み込み方式及び材料に応じて変化するが、金属/平坦化後の誘電体キャップの界面に沿って移動するCu原子のような金属原子がEM寿命予測において重要な役割を果たすことが観察された。EMの初期ボイドは、最初に金属/誘電体キャップの界面において核形成され、その後、相互接続部の底部方向に成長し、これが、最終的には回路不良(circuit dead)開口(opening)をもたらす。

【0006】

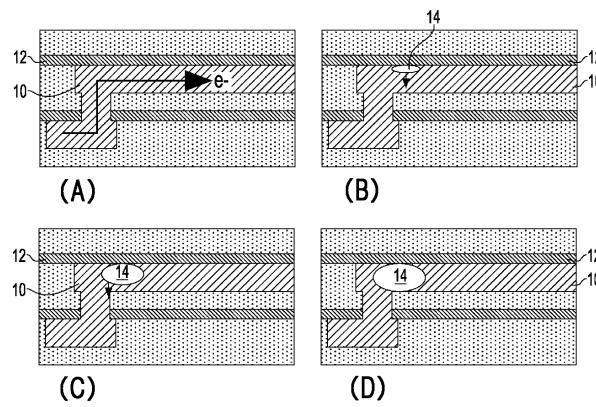

図1(A)乃至図1(D)は、EM故障の種々の段階における従来技術の相互接続構造体を表す図である。これらの図面において、参照符号12は誘電体キャップを示し、参照符号10は金属相互接続構造部を示しており、EMの問題を不明瞭にするのを避けるために、従来技術の相互接続構造体のその他の全ての構成要素は符号を付けていない。図1(A)は、初期応力段階である。図1(B)は、ボイド14の核形成が金属相互接続構造部10/誘電体キャップ12の界面において開始する時点のものである。図1(C)は、ボイド14が導電性構造部10の底部方向に成長している時点のものであり、図1(D)は、ボイド14の成長が金属相互接続構造部10を横断し、回路不良開口をもたらす時点のものである。

【0007】

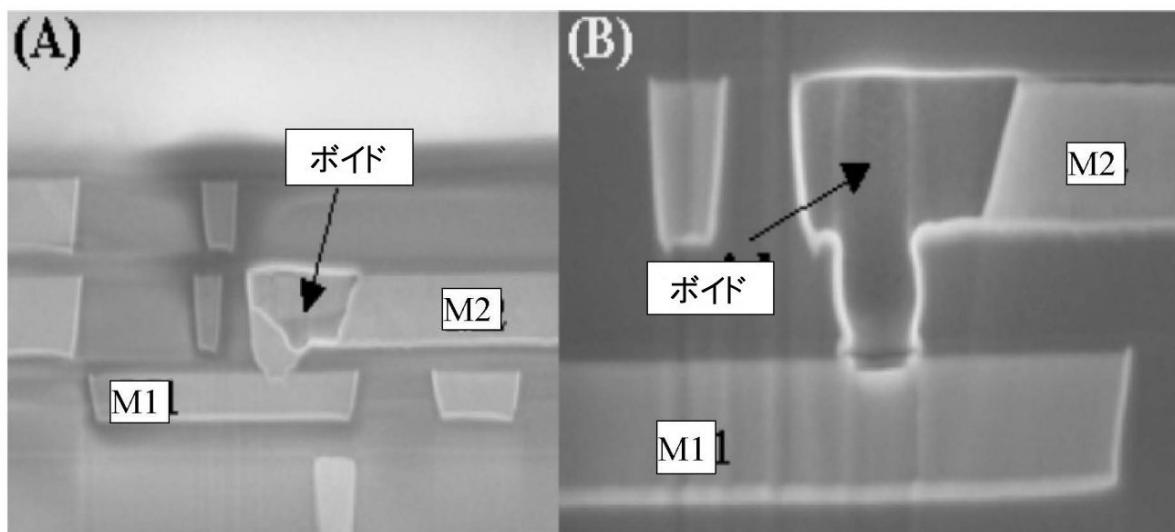

図2(A)乃至図2(B)は、応力がかかった相互接続構造体のSEM画像であり、金属ライン(M2)内で発生するボイドを示しており、これは、金属ライン内における物質移動が金属ラインとその上を覆う誘電体キャップとの界面に沿って生じることを暗示している。

【発明の概要】

【発明が解決しようとする課題】

【0008】

以上のことを鑑みて、EM故障によって引き起こされる回路不良開口(オープン)を回避する相互接続構造体を提供することが必要とされる。

【課題を解決するための手段】

【0009】

1つの態様において、本発明は、向上したEM信頼度を有する相互接続構造体に関する。本発明の相互接続構造体は、EM防止ライナを金属相互接続部内に組み込むことによって、EM故障により引き起こされる回路不良開口を回避する。本発明の構造体の他の利点には、突発的なデータ損失の防止及び半導体装置の寿命の向上が含まれる。

【0010】

総括的に言えば、本発明の半導体相互接続構造体は、内部に配置された少なくとも1つの導電性充填構造部(conductively filled feature)を有する誘電体材料を含み、少なくとも1つの導電性充填構造部は、少なくとも1つの導電性充填構造部の第1の導電性領域を少なくとも1つの導電性充填構造部の第2の導電性領域から少なくとも部分的に分離するエレクトロマイグレーション(EM)防止ライナを含む。

【0011】

1つの実施形態において、少なくとも1つの導電性充填構造部を誘電体材料から分離する拡散障壁に当接する「U字形」のEM防止ライナが設けられる。別の実施形態において

10

20

30

40

50

、「U字形」EM防止ライナと拡散障壁との間には空間（スペース）が配置される。さらに別の実施形態においては、拡散障壁に当接する水平のEMライナが設けられる。さらに別の実施形態において、水平EMライナと拡散障壁との間に空間が存在する。

【0012】

本発明の別の態様は、本発明の相互接続構造体を製造する方法に関する。本発明の方法は、少なくとも1つの開口部を誘電体材料内に設けるステップであって、この少なくとも1つの開口部が拡散障壁で内部を覆われる（ライニングされる）ステップと、少なくとも1つの開口部内に第1の導電性領域を形成するステップと、少なくとも第1の導電性領域の表面上にエレクトロマイグレーション（EM）防止ライナを形成するステップと、EM防止ライナ上に第2の導電性領域を形成するステップであって、第1及び第2の導電性領域が、誘電体材料内に導電性構造部を形成するステップと、を含む。

10

【0013】

1つの実施形態において、導電性構造部を誘電体材料から分離する拡散障壁に当接する「U字形」EM防止ライナが設けられる。別の実施形態において、「U字形」EM防止ライナと拡散障壁との間に空間が配置される。さらに別の実施形態において、拡散障壁に当接する水平のEMライナが設けられる。さらに別の実施形態において、水平EMライナと拡散障壁との間に空間が存在する。

【図面の簡単な説明】

【0014】

【図1】EM故障によって引き起こされる、従来技術の相互接続構造体における回路不良開口の形成を示す（断面）図である。

20

【図2】EM故障によって引き起こされる、従来技術の相互接続構造体における回路不良開口の形成を示すSEM画像である。

【図3】EM防止ライナを金属構造部内に形成することによって、回路不良開口が回避される本発明の種々の相互接続構造体の（断面）図である。

【図4】EM防止ライナを金属構造部内に形成することによって、回路不良開口が回避される本発明の種々の相互接続構造体の（断面）図である。

【図5】EM防止ライナを金属構造部内に形成することによって、回路不良開口が回避される本発明の種々の相互接続構造体の（断面）図である。

【図6】EM防止ライナを金属構造部内に形成することによって、回路不良開口が回避される本発明の種々の相互接続構造体の（断面）図である。

30

【図7】図3に示される構造体を形成するのに用いられる基本的な処理ステップを示す（断面）図である。

【図8】図3に示される構造体を形成するのに用いられる基本的な処理ステップを示す（断面）図である。

【図9】図3に示される構造体を形成するのに用いられる基本的な処理ステップを示す（断面）図である。

【図10】図3に示される構造体を形成するのに用いられる基本的な処理ステップを示す（断面）図である。

【図11】図3に示される構造体を形成するのに用いられる基本的な処理ステップを示す（断面）図である。

40

【図12】図5に示される構造体を形成するのに用いられる中間構造体の（断面）図である。

【図13】誘電体材料の少なくとも1つの開口部を部分的に充填するのに用いられる非理想的なボトムアップ堆積プロセスを示す（断面）図である。

【発明を実施するための形態】

【0015】

本発明は、向上したエレクトロマイグレーション（EM）に対する向上した信頼度を有する相互接続構造体及びその形成方法を提供するものであり、これを、以下の考察及び本出願に添付される図面を参照してより詳細に説明する。本出願の図面は例示の目的のみで

50

提供されるものであり、従って、これらの図面は一定の縮尺で描かれているものではないことに留意されたい。

【0016】

以下の説明において、本発明を完全に理解できるようにするために、詳細な構造、構成要素、材料、寸法、処理ステップ及び技術といった、多数の具体的な詳細が示されている。しかしながら、これらの具体的な詳細なしに本発明を実施することができるが当業者には認識されるであろう。他の例では、本発明を不明瞭にすることを避けるために、周知の構造又は処理ステップは、詳細には記載されていない。

【0017】

層、領域又は基板としての要素が別の要素「の上に(on)」又は「を覆って(over)」あると言われる場合には、それは他の要素の上に直接あるものとすることもできるし、或いは介在要素が存在してもよいことが理解される。それとは対照的に、要素が別の要素「の上に直接」又は「直接覆って」あると言われる場合には、介在要素は存在しない。要素が別の要素に「接続する」又は「結合する」と言われる場合には、それは他の要素に直接接続され又は結合されてもよく、或いは介在要素が存在してもよいことも理解される。それとは対照的に、要素が別の要素に「直接接続する」又は「直接結合する」と言われる場合には、介在要素は存在しない。

【0018】

上述のように、本発明は、向上したEM信頼度を有する相互接続構造体を提供する。本発明の相互接続構造体は、EM防止ライナを金属相互接続部に組み込むことによって、EM故障により引き起こされる回路不良開口を回避する。

【0019】

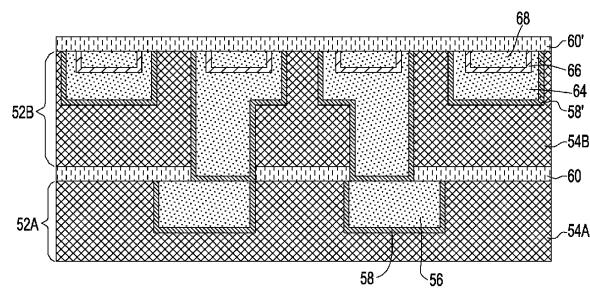

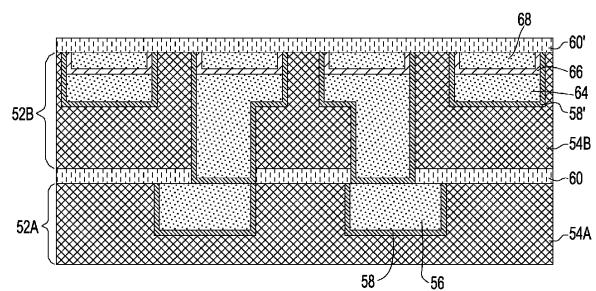

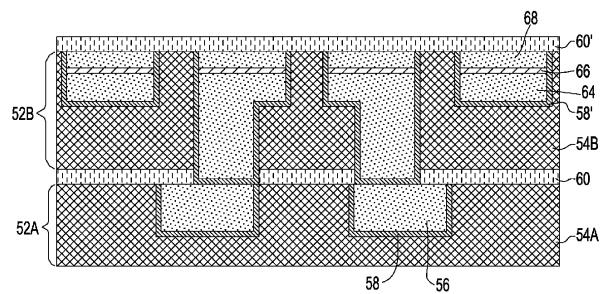

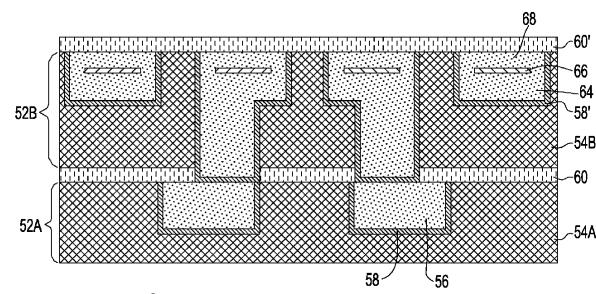

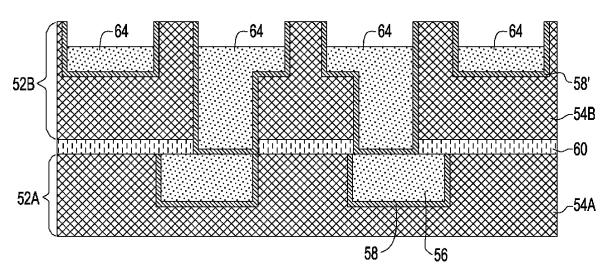

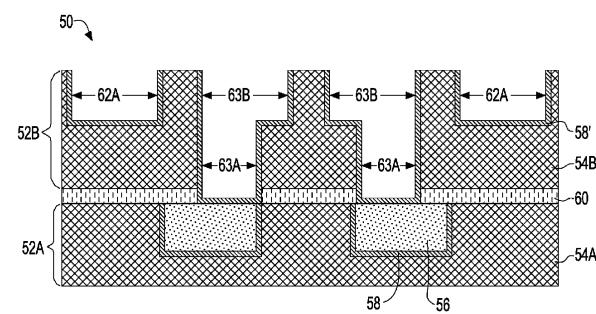

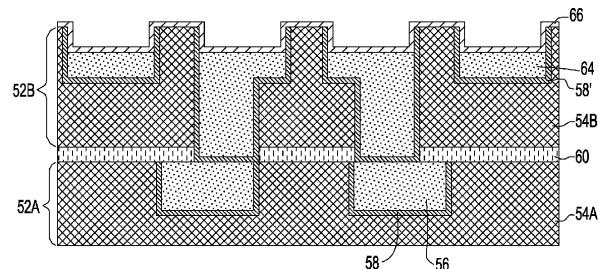

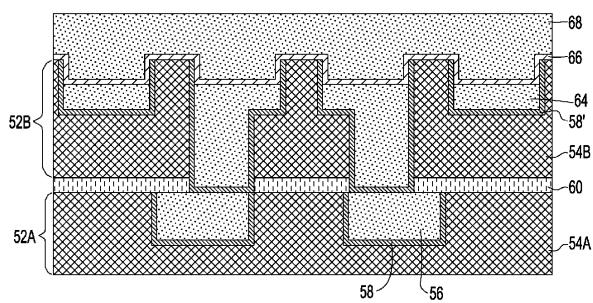

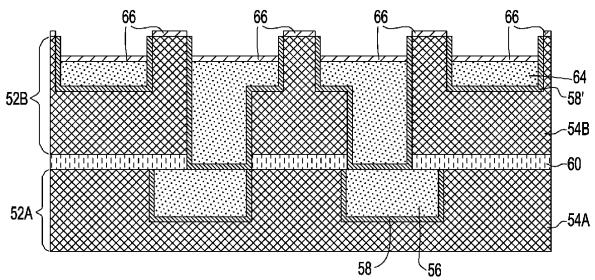

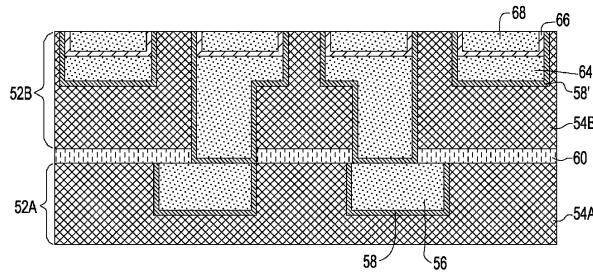

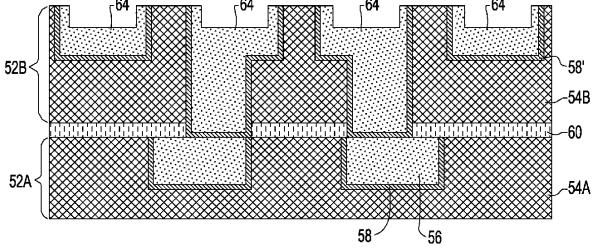

図3乃至図6は、本発明の種々の実施形態を示す。具体的には、図3乃至図6は、導電性材料64及び68で充填された誘電体材料54Bの開口部内にEM防止ライナ66が配置された、本発明の相互接続構造体を示す。本発明によれば、第2の誘電体材料54B内に、導電性材料64が第1の導電性領域を形成し、一方、導電性材料68が第2の導電性領域を形成する。この第1及び第2の導電性領域が、第2の誘電体材料54B内に導電性構造部を形成する。

【0020】

図3は、導電性材料64及び68を誘電体材料54Bから分離する拡散障壁58'に「U字形」のEM防止ライナ66が当接する、本発明の第1の実施形態を示す。図4は、「U字形」EM防止ライナ66と拡散障壁58'との間に空間が配置される、第2の実施形態を示す。図5は、水平のEMライナ66が拡散障壁に当接する第3の実施形態を示し、一方、図6は、水平EMライナ66と拡散障壁58'との間に空間が存在する、本発明の第4の実施形態を示す。

【0021】

ここで、図3に示される半導体相互接続構造体を形成するのに用いられる基本的な処理ステップを示す、図7乃至図11を参照する。この実施形態において、「U字形」のEM防止ライナ66は、第2の誘電体材料54Bの少なくとも1つの開口部をライニングする(内部を覆う)拡散障壁58'に当接する。具体的には、本発明の方法は、図7に示されるパターン形成された相互接続構造体50を準備することから開始する。図7に示されるパターン形成された相互接続構造体50は、誘電体キャップ層60によって部分的に分離された、第1の相互接続レベル52Aと第2の相互接続レベル52Bとを含む。

【0022】

第1の相互接続レベル52Aは、1つ又は複数の半導体デバイスを含む半導体基板の上方に位置することができ、第1の誘電体材料54Aを含む。この第1の誘電体材料54Aは拡散障壁58によって第1の誘電体材料54Aから分離される少なくとも1つの導電性構造部56を有する。第2の相互接続レベル52Bは、内部に位置する少なくとも1つの開口部を有する第2の誘電体材料54Bを含む。

【0023】

10

20

30

40

50

図7において、シングル・ダマシン構造のためのライン開口部62Aと、デュアル・ダマシン構造のためのビア開口部63A及びライン開口部63Bが第2の誘電体材料54B内に示されている。これらの種々の開口部が示されてはいるが、本発明は、シングル・ダマシンのライン開口部のみが形成される場合にも、又はダマシンのライン及びビア開口部が形成される場合にも機能する。デュアル・ダマシンのライン及びビア開口部が形成される場合には、少なくとも1つの導電性構造部56の上方に位置する誘電体キャップ層60の一部が除去される。

【0024】

パターン形成された相互接続構造体50は、第2の誘電体材料54B内に形成された少なくとも1つの開口部内にも拡散障壁58'を含む。

10

【0025】

図7に示されるパターン形成された相互接続構造体50は、シングル・ダマシン又はデュアル・ダマシン・プロセスを含む、当該技術分野において周知の標準的な後工程(BEOL)プロセスを用いて形成される。先にビア開口部を作り、次いでライン開口部を作るプロセスを用いることもできるし、又は先にライン開口部を作り、次いでビア開口部を作るプロセスを用いることもできる。

【0026】

プロセスは、典型的には、堆積、リソグラフィ、開口部のエッチングと拡散障壁及びその後の導電性材料の充填、及びその後の平坦化を含む。このような相互接続構造体を形成するための処理の詳細は当業者には周知であるので、本発明を不明瞭にすることを避けるために、本明細書において詳細は省略されている。

20

【0027】

パターン形成された相互接続構造体50の第1の相互接続レベル52Aは、基板(本出願の図面には示されていない)の上に形成することができることに留意されたい。基板は、図示されていないが、半導体材料、絶縁材料、導電性材料又はこれらのいずれかの組み合わせを含むことができる。基板が半導体材料からなる場合には、Si、SiGe、SiGeC、SiC、Ge合金、GaAs、InAs、InP及び他のIII/V族又はII/VI族化合物半導体のような、いずれの半導体を用いることもできる。列挙されたこれらのタイプの半導体材料に加えて、本発明は、半導体基板が、例えばSi/SiGe、Si/SiC、シリコン・オン・インシュレータ(SOI)、又はシリコンゲルマニウム・オン・インシュレータ(SGOI)のような層状半導体である場合も意図している。

30

【0028】

基板が絶縁材料である場合、絶縁材料は、有機絶縁体、無機絶縁体又は多層を含むこれらの組み合わせとすることができます。基板が導電性材料である場合、基板は、例えば、ポリSi、元素金属、元素金属の合金、金属シリサイド、金属窒化物又は多層を含むこれらの組み合わせを含むことができる。基板が半導体材料を含む場合には、例えば相補型金属酸化膜半導体(CMOS)デバイスのような1つ又は複数の半導体デバイスをその上に形成することができる。基板が絶縁材料と導電性材料との組み合わせを含む場合には、基板は、多層相互接続構造体の第1の相互接続レベルを表すことができる。

【0029】

第1の誘電体材料54A及び第2の誘電体材料54Bは、同じ又は異なる材料とすることができ、無機誘電体又は有機誘電体を含むいかなる層間(interlevel)又は層内(intralevel)誘電体も含む。第1及び第2の誘電体材料54A及び54Bはそれぞれ、多孔質又は非多孔質とすることができます。第1及び第2の誘電体材料54A及び54Bとして用いることができる適切な誘電体の幾つかの例には、これらに限定されるものではないが、SiO<sub>2</sub>、シリセスキオキサン、Si、C、O及びH原子を含むCドープ酸化物(すなわち、オルガノシリケート)、熱硬化性ポリアリーレンエーテル、又はそれらの多層が含まれる。「ポリアリーレン」という用語は、本出願においては、結合、縮合環、又は、例えば、酸素、硫黄、スルホン、スルホキシド、カルボニル等のような不活性結合基によって互いに結合された、アリール部分又は不活性に置換されたアリール部分を表すために用い

40

50

られる。

【0030】

第1及び第2の誘電体材料54A及び54Bは、それぞれ典型的には約4.0又はそれ以下の誘電率を有し、約2.8又はそれ以下の誘電率がさらに典型的である。本明細書において言及される全ての誘電率は、特に断りのない限り、真空に対しての誘電率である。これらの誘電体は、一般に、4.0より高い誘電率を有する誘電体材料と比較して、寄生クロストークがより低い。誘電体材料の厚さは、用いられる誘電体材料、並びに第1及び第2の誘電体材料内の誘電体層の正確な数に応じて異なり得る。典型的には、通常の相互接続構造体については、第1の誘電体材料54A及び第2の誘電体材料54Bは、各々が約50nmから約1000nmまでの厚さを有する。

10

【0031】

拡散障壁58及び58'は、同じ又は異なる材料とすることができます、Ta、TaN、Ti、TiN、Ru、RuN、RuTa、RuTaN、W、WN、又は任意の他の材料を含み、これらの材料は、導電性材料がそれを通して拡散することを防止する障壁として機能することができる。拡散障壁58及び58'の厚さは、用いられる堆積プロセス、並びに用いられる材料に応じて異なり得る。典型的には、拡散障壁58及び58'は、各々が約4nmから約40nmまでの厚さを有し、約7nmから約20nmまでの厚さがより典型的である。

【0032】

導電性構造部56を形成するのに用いられる導電性材料には、例えば、ポリSi、導電性金属、少なくとも1つの導電性金属を含む合金、導電性金属シリサイド又はそれらの組み合わせが含まれる。好ましくは、少なくとも1つの導電性構造部56を形成するために用いられる導電性材料は、Cu、W又はAlのような導電性金属であり、Cu又はCu合金(A1Cu等)が、本発明においては極めて好ましい。

20

【0033】

第2の相互接続レベル52Bを第1の相互接続レベル52Aから少なくとも部分的に分離する誘電体キャップ層60は、例えば、SiC、Si<sub>4</sub>NH<sub>3</sub>、SiO<sub>2</sub>、炭素ドープ酸化物、窒素及び水素ドープ炭化ケイ素SiC(N, H)又はこれらの多層のような、いずれかの適切な誘電体キャップ材料を含む。誘電体キャップ層60の厚さは、それを形成するのに用いられる技術、並びに層の材料組成に応じて異なり得る。典型的には、誘電体キャップ層60は約15nmから約100nmまでの厚さを有し、約25nmから約45nmまでの厚さがより典型的である。

30

【0034】

図7に示されるパターン形成された相互接続構造体50を準備した後に、導電性材料64(上部相互接続レベル52Bの第1の導電性領域を形成する)が、第2の誘電体材料54B内の少なくとも1つの開口部(ビア及び/又はライン開口部)内に部分的に形成される。導電性材料64は、少なくとも1つの導電性構造部56について上記で定義した材料と同じ又は異なる導電性材料を含むことができる。好ましくは、導電性材料64は、Cu、W又はAlであり、Cu又はCu合金(A1Cu等)が、本発明においてはより好ましい。導電性材料64は、第2の誘電体材料54B内の少なくとも1つの開口部を部分的に充填することによって、或いは少なくとも1つの開口部を完全に充填し、次いで第2の誘電体材料54Bの上面より下のレベルまで導電性材料を凹ませることによって形成することができる。化学気相成長法(CVD)、プラズマ増強化学気相成長法(PECVD)、スパッタリング、化学溶液堆積法、又は少なくとも1つの開口部を底部(ボトム)から上方に向かって充填するめっき法を含む、いずれかの従来の堆積プロセスを用いることができる。ボトムアップめっきプロセスを用いることが好ましい。

40

【0035】

陥凹ステップが用いられる場合には、導電性材料64の一部を選択的に除去するエッチング・プロセスを用いて、第2の誘電体材料54B内の少なくとも1つの開口部の部分的な充填が提供される。図8においては、理想的なボトムアップ充填が示されていることに

50

留意されたい。「理想的な」とは、充填が主として開口部の下部から上方向に向かって生じることを意味している。

【0036】

ここで、図8に示される構造体の全ての露出面（水平及び垂直を含む）上にEM防止ライナ66が形成された後の構造体を示す図9を参照する。EM防止ライナ66は、Ta、TaN、Ti、TiN、Ru、RuN、RuTa、RuTaN、Ir、IrCu、Co(W, B, P, Mo, Re)、又はEM故障を防止することができる任意の同様の材料を含む。図9に示される実施形態において、EM防止ライナ66は、例えばCVD及びスパッタリングのような、無指向性堆積プロセスを用いて形成される。EM防止ライナ66は、典型的には約1nmから約20nmまでの厚さを有し、約2nmから約8nmまでの厚さがより典型的である。

10

【0037】

本発明の別の実施形態において、EM防止ライナ66は、EM防止ライナを構造体の1つの水平面上のみに選択的に堆積させる指向性堆積プロセスを用いて形成することができる。本発明のこの実施形態は、例えば、図12に示される。本発明のこの実施形態は、触媒めっきプロセスも含むことに留意されたい。このプロセスにおいて、EM防止ライナ66が導電性材料64の露出された水平面上のみに形成される。そのような実施形態（図示せず）においては、EM防止ライナは、第2の誘電体材料54B上には形成されない。EM防止ライナ66の指向性堆積は、例えば図5及び図6に示される相互接続構造体、すなわち第2の誘電体材料54Bの導電性充填された開口部内に水平EM防止ライナを形成するのに用いられる。

20

【0038】

理解しやすいように、残りの処理ステップは、図9に示される構造体を用いる。このような例示が提供されているが、以下の処理ステップは、本発明のその他の実施形態にも適用される。

【0039】

次に、図10に示されるように、導電性材料64と同じ又は異なる、好ましくは同じ導体を含むことができる付加的な導電性材料68が形成される。図10に示される構造体を形成するために、いずれかの従来の堆積プロセスを用いることができる。導電性材料68は、上部相互接続レベル52Bの第2の導電性領域を形成することに留意されたい。

30

【0040】

図11は、付加的な導電性材料68をその上面が第2の誘電体材料54Bの上面と実質的に同一平面となるように平坦化した後の構造体を示す。この平坦化ステップの間に第2の誘電体材料54Bの上に位置するEM防止ライナはいずれも除去されることに留意されたい。平坦化は、化学的機械的研磨及び/又は研削によって達成することができる。

【0041】

平坦化後に、第2の誘電体キャップ層60'が、図3に示される構造体を提供するように図11に示される構造体上に形成される。第2の誘電体キャップ層60'は、第1の誘電体キャップ層60と同じ又は異なる材料から構成されるものとすることができます。

40

【0042】

本発明の別の実施形態において、第2の誘電体材料54B内の少なくとも1つの開口部を部分的に充填するときに、導電性材料64の非理想的な堆積が生じる。この実施形態は、まず、図7に示されるパターン形成された相互接続構造体50を準備することから開始する。次に、導電性材料64の非理想的な堆積が生じて、例えば、図13に示される構造体を提供する。非理想的な堆積が生じる場合には、第2の誘電体材料54Bの少なくとも1つの開口部のパターン形成された垂直壁に近接する部分もまた、導電性材料64を含む。従って、この実施形態は理想的なボトムアップ堆積ではない。この非理想的な堆積は、多くの場合に生じる。

【0043】

図13に示される構造体の形成に続いて、図5及び図6に示される構造体を形成するた

50

めに上述の処理ステップを用いることができる。

【0044】

上述のように、本発明は、EM防止ライナを金属相互接続部に組み込むことによって、向上したEM信頼度を有する相互接続構造体を提供する。本発明の他の利点には、突発的なデータ損失の防止及び半導体装置の寿命の向上が含まれる。

【0045】

上記のことと加えて、本発明の相互接続構造体の別の利点は、第2の誘電体材料54B内の導電性構造部とその上を覆う誘電体キャップ層60'との間の脆弱な界面が回避されることである。また、本発明の構造体は、従来技術の相互接続構造体よりも上手く応力を調節することができる。

10

【0046】

本発明を、その好ましい実施形態に関して具体的に示し、説明してきたが、当業者であれば、本発明の精神及び範囲から逸脱することなく、形態及び詳細において上記の及び他の変更を行うことができることを理解するであろう。従って、本発明は、説明され、図示されたそのままの形態及び詳細に限定されるものではなく、添付の特許請求の範囲内に含まれることが意図される。

【産業上の利用可能性】

【0047】

本発明は、半導体構造体の製造において、より具体的には、VLSIチップに必須のデバイス及び回路の設計及び製造の分野において、産業上の利用可能性を見出すものである。

20

【符号の説明】

【0048】

50：相互接続構造体

52A：第1の接続レベル

52B：第2の接続レベル

54A：第1の誘電体材料

54B：第2の誘電体材料

56：導電体構造部

58、58'：拡散障壁

30

60、60'：誘電体キャップ層

64、68：導電性材料

66：EM防止ライナ

【図1】

【図4】

【図3】

【図5】

【図6】

【図8】

【図7】

【図9】

【図10】

【図12】

【図11】

【図13】

【図2】

(従来技術)

---

フロントページの続き

(72)発明者 ヤン、チーチャオ

アメリカ合衆国 12077 ニューヨーク州 グレンモント ウィンダム・ヒル・ロード 29

(72)発明者 ワン、ピンチュアン

アメリカ合衆国 12533 ニューヨーク州 ホープウェル・ジャンクション クリアビュー・

サークル 52

(72)発明者 ワン、ユンユー

アメリカ合衆国 12570 ニューヨーク州 ポクアグ サイファー・レーン 34

審査官 瀧内 健夫

(56)参考文献 特開2000-174025(JP,A)

特開2000-260770(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3205

H01L 21/768