### (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2004/0268348 A1 Waki et al.

Dec. 30, 2004 (43) Pub. Date:

### (54) HIGH SPEED VIRTUAL MACHINE AND **COMPILER**

(76) Inventors: **Hiroyuki Waki**, Hirakata-shi (JP); Shinji Inoue, Neyagawa-shi (JP); Satoru Hayama, Kobe-shi (JP); Mitsuko Fujita, Tokyo-to (JP); Akira Ishikawa, Kashiba-shi (JP)

> Correspondence Address: **SNELL & WILMER LLP** 1920 MAIN STREET **SUITE 1200** IRVINE, CA 92614-7230 (US)

(21) Appl. No.: 10/899,920

(22) Filed: Jul. 27, 2004

### Related U.S. Application Data

Division of application No. 09/288,263, filed on Apr. 8, 1999.

### (30)Foreign Application Priority Data

(JP) ...... 10-96294 Apr. 8, 1998

### **Publication Classification**

(51) Int. Cl.<sup>7</sup> ...... G06F 9/46

### (57)ABSTRACT

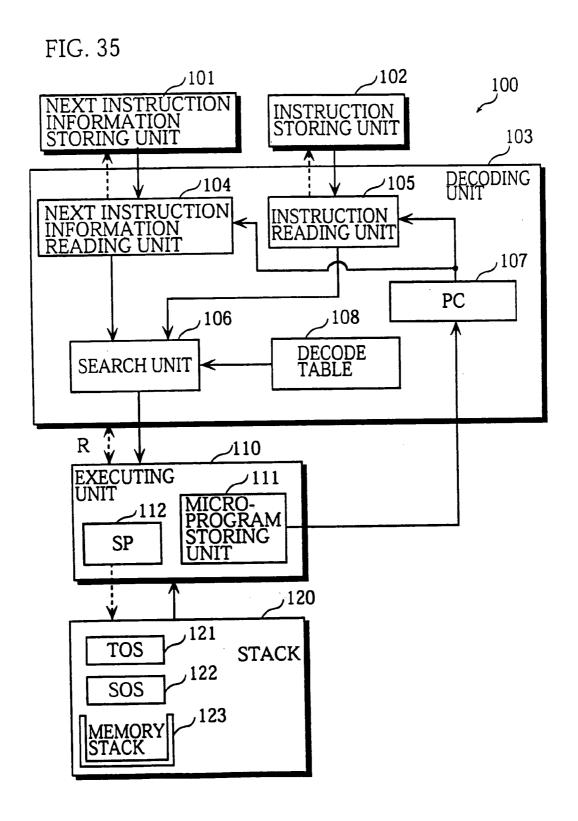

A virtual machine with a stack architecture includes: a stack 120 whose top level (TOS) and the second level from the top (SOS) are mapped to registers of a real machine 201; an instruction storing unit 102 for storing a virtual machine instruction sequence to be executed; next instruction information storing unit 101 for storing a plurality of sets of next instruction information that are each associated with a different virtual machine instruction in the virtual machine instruction sequence, the set of next instruction information for a given virtual machine instruction indicating a change in a number of sets of data stored in the stack 120 due to execution of a virtual machine instruction executed after the given virtual machine instruction; a decoding unit 103 for decoding a virtual machine instruction and an associated set of next instruction information after reading them from the instruction storing unit 102 and the next instruction information storing unit 101; and an executing unit 110 for executing the decoded virtual machine instruction and performing a stack handling in the stack 120 in advance for a virtual machine instruction that is to be executed next based on the set of next instruction information.

FIG. 1

|                               |                                                                       | HANGE IN STACK                   | SF VALOR  |

|-------------------------------|-----------------------------------------------------------------------|----------------------------------|-----------|

| FIG. 2                        | STNEEDING CONTENTS                                                    | CONTENTS                         |           |

| AACHINE<br>AACHINE<br>AACHINE |                                                                       | s0←operand                       | sp←sp+1   |

| Push PU                       | PUSH OPERAND ONTO STACK AND PLACE IT INTO                             | operand -s0                      | sp←sp-1   |

| Pop AE                        | ADDRESS INDICATED BY OPERAND ADDRESS INDICATED BY OPERAND             | s0←s0+s1                         | sp←sp-1   |

| Add                           | AND STORE RESULT ONTO STACK TOP<br>AND STORE RESULT ON TOP AND SECOND | s0+-s0*s1                        | sp←sp-1   |

| Mult                          | STACKS AND STORE RESULT ONTO STACK TO STACKS                          | 0s→0s                            | ds→ds     |

| Br 0                          | JUMP UNCONDITIONALL TO STACK TOP                                      | DELETE←s0                        | sp←sp-1   |

| Brz                           | JUMP TO ADDRESS OF OFER AND IF STACK TOP                              |                                  | sp←sp-1   |

| Brnz                          | JUMP TO ADDRESS OF OPENALUE IS NOT 0 VALUE IS NOT 0                   | SO ST<br>SO NEXT VIRTUAL MACHINE | Æ sp←sp+1 |

| Call                          | CALL FUNCTION SPECIFIED STATES OF OPERAND                             | DELETE - s0                      | sp←sp-1   |

| Ret                           | JUMP UNCONDITIONALL I TO STACK TOP VALUE                              | INITIAL STATE                    | 0→ds      |

| Stop                          | STOP VIRTUAL MACHINE PROCESSING                                       |                                  |           |

| 4406c      | NUMBER OF<br>OPERANDS | •• | 1                                      | 1                                      | 0                                     | 0                                     | 0                                     | 0                                      | 0                                     | 0                                     | ••                        |  |

|------------|-----------------------|----|----------------------------------------|----------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|---------------------------------------|---------------------------------------|---------------------------|--|

| 4406 4406b | JUMP ADDRESS          |    | YEAR A PUBESS OF CODE TO PERFORM Push> | < JUMP ADDRESS OF CODE TO PERFORM Pop> | CJUMP ADDRESS OF CODE TO PERFORM Add> | CJUMP ADDRESS OF CODE TO PERFORM Sub> | CJUMP ADDRESS OF CODE TO PERFORM Inc> | < JUMP ADDRESS OF CODE TO PERFORM Dec> | SUMP ADDRESS OF CODE TO PERFORM Mult> | CJUMP ADDRESS OF CODE TO PERFORM Div> | CJUMP ADDRESS OF COLL 101 |  |

| FIG. 3     | OPCODE                |    | ••                                     | Push                                   | Pop                                   | Add                                   | Sub                                   | Inc                                    | Dec                                   | Mult                                  | Div                       |  |

| FIG. 4A         |               |                                                                                                                                                              |

|-----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | AM FOR VII    | RTUAL MACHINE INSTRUCTION "Push"                                                                                                                             |

| 1:Inc<br>2:Load | r3<br>r0.[r2] | ; INCREMENT SP VALUE BY ONE ; EXTRACT OPERAND AND ; EXTRACT OPERAND AND                                                                                      |

| 3:Inc           | r2            | ; PLACE IT ONTO REGISTER #0<br>: INCREMENT VIRTUAL MACHINE PC BY ONE AND<br>: PREPARE FOR READING NEXT INSTRUCTION<br>: PUSH VALUE OF REGISTER #0 ONTO STACK |

| 4:Store         | (r3), r0      | ; PUSH VALUE OF REGISTER WOUNDERSTRUCTION >                                                                                                                  |

| < MICROPRO      | GRAW FUR      | JOHN MICE TE                                                                                                                                                 |

| FIG. 4B                                                                                                | RAM FOR VIF   | RTUAL MACHINE INSTRUCTION "Add"                                                                                                                     |

|--------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:Load                                                                                                 | r0,[r3]       | EXTRACT VALUE PROMISTAGE                                                                                                                            |

| 2:Dec<br>3:Load                                                                                        | r3<br>r1,[r3] | PLACE IT ONTO REGISTER #0 DECREMENT VALUE OF VIRTUAL MACHINE SP BY ONE EXTRACT VALUE FROM STACK PLACE IT ONTO REGISTER #1 PLACE IT ONTO REGISTER #1 |

| 4:Add                                                                                                  | 17,07,01      | ADD VALUES OF REGISTER #01#1                                                                                                                        |

| 5:Store                                                                                                | [r3],r0       | DI ACE VALUE OF REGISTER # 0 011-0                                                                                                                  |

| <micrope< td=""><td>ROGRAM FOR</td><td>JUMPING TO NEXT VIRTUAL MACHINE INSTRUCTION&gt;</td></micrope<> | ROGRAM FOR    | JUMPING TO NEXT VIRTUAL MACHINE INSTRUCTION>                                                                                                        |

| M FOR VI | RTUAL MACHINE INSTRUCTION "Mult"                                                                                                                                                |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                                                                                 |

| r0.[r3]  | ; EXTRACT VALUE FROM STACK AND<br>; PLACE IT ONTO REGISTER #0<br>; PLACE IT ONTO REGISTER #0                                                                                    |

| r3       | ; DECREMENT VALUE OF VIRTUAL MAGNATURE                                                                                                                                          |

| [1],[1]  | DI ACE IT ONTO REGISTER #1                                                                                                                                                      |

| r0,r0,r1 | : EXTRACT VALUE FROM STACK AND : PLACE IT ONTO REGISTER #1 : MULTIPLY VALUES OF REGISTERS #0 AND #1 AND : PLACE RESULT ONTO REGISTER #1 : PLACE VELUE OF REGISTER #0 ONTO STACK |

| (r3),r0  | R JUMPING TO NEXT VIRTUAL MACHINE INSTRUCTION                                                                                                                                   |

|          | r0,[r3]<br>r3<br>r1,[r3]<br>r0,r0,r1                                                                                                                                            |

| FIG. 4D        | OGRAM FOR        | JUMPING TO NEXT VIRTUAL MACHINE INSTRUCTION>                                                                             |

|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1:Load         | r0.[r2]          | READ VIRTUAL MACHINE IN BY PC (IUMP ADDRESS) INDICATED BY PC                                                             |

| 2:Inc<br>3:Jmp | <b>r</b> 2<br>r0 | INTO REGISTER #0 : INCREMENT VIRTUAL MACHINE PC VALUE BY ONE : JUMP UNCONDITIONALLY TO LOCATION INDICATED BY REGISTER #0 |

| 2    |  |

|------|--|

| FIG. |  |

| ilG. 5       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |          | EVAMPI F | ᄕ            |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|--------------|

| FAI. MACHINE | OPERATION CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NOTATION | NOIL     | CANINI   | }<br>'       |

| NSTRUCTION   | THAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Load     | x0,x1    | Load     | ص.<br>12,01  |

| Load         | PLACE VALUE OF DESIGNATED REGISTER (X1) OF MEMORY LOCATION ([x1]) DESIGNATED BY REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Load     | x0,[x1]  | Load     | r1,[r2]      |

|              | ONTO VALUE OF DESIGNATED REGISTER (x1) ONTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Store    | [x0],x1  | Store    | [10]<br>[10] |

| Store        | PLACE VALUE OF DESIGNATED BY REGISTER MEMORY LOCATION (x0) DESIGNATED BY REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Add      | x0,x1,x2 | Add      | 10,11,12     |

| Add          | ADD VALUES OF DESIGNATED REGISTERS (x1, x2) PLACE RESULT ONTO DESIGNATED REGISTER (x0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mult     | x0,x1,x2 | Mult     | 10,11,12     |

| Mult         | MULTIPLY VALUES OF DESIGNATED REGISTER (x0) AND PLACE RESULT ONTO DESIGNATED REGISTER (x0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Inc      | 0x       | Inc      | 14           |

| Inc          | ADD 1 TO VALUE OF DESIGNATED NEGOTIES (27) TO VALUE OF DESIGNATER STORE RESULT IN SAME REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Dec      | ×O×      | Dec      | 13           |

| Dec          | SUBTRACT 1 FROM VALUE OF DESIGNATED REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3        |          |          | C            |

|              | (x0), AND SI OKE RESOLT IN STAIN STAIN STAIN BY DESIGNATED REGISTER (x0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Jmb      | QX       | dur      | 71           |

| dw[          | JUMP TO ADDRESS INDICATED BY DESIGNATED REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Zſ       | x0,x1    | z[       | 71,01        |

| <b>Z</b> [   | JUMP TO ADDIKESS INDICATED RECISTER (x0) IS 0 (x1) IF VALUE OF DESIGNATED RECISTER (x0) IS 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ln7      | x0.x1    | Jnz      | r0,r2        |

| Juz          | JUMP TO ADDRESS INDICATED BY DESIGNALED REGISTER<br>JUMP TO ADDRESS INDICATED REGISTER (x0) IS NOT 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |          |          |              |

|              | (x1) IF VALUE OF DESIGNATED ASSESSMENT OF THE PROPERTY OF THE | Ž<br>—   | Nop      | doN      | d.           |

| Nop          | NOTHING PERFURMED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |          |          |              |

FIG. 6

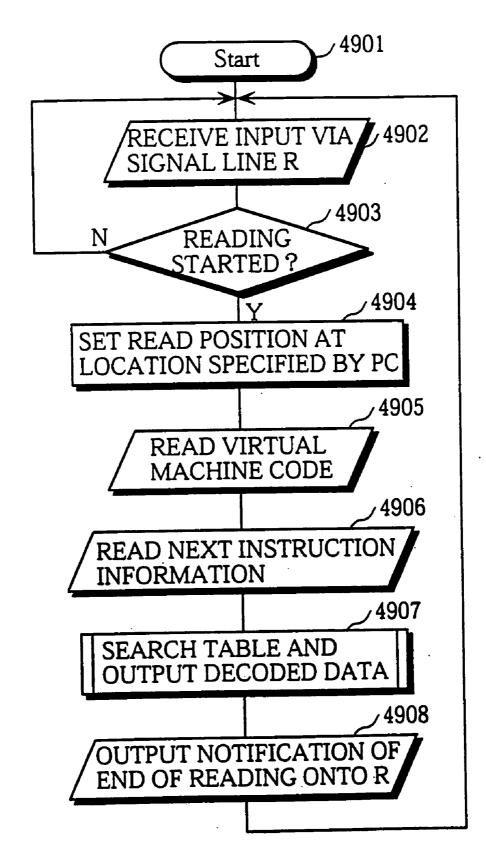

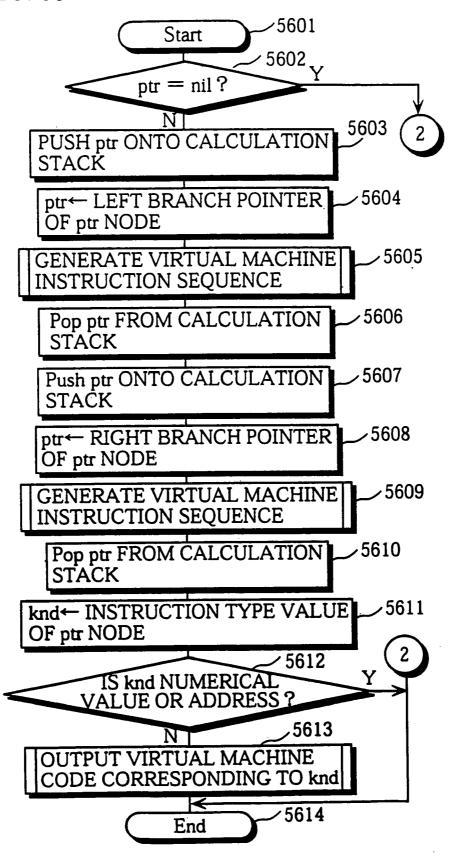

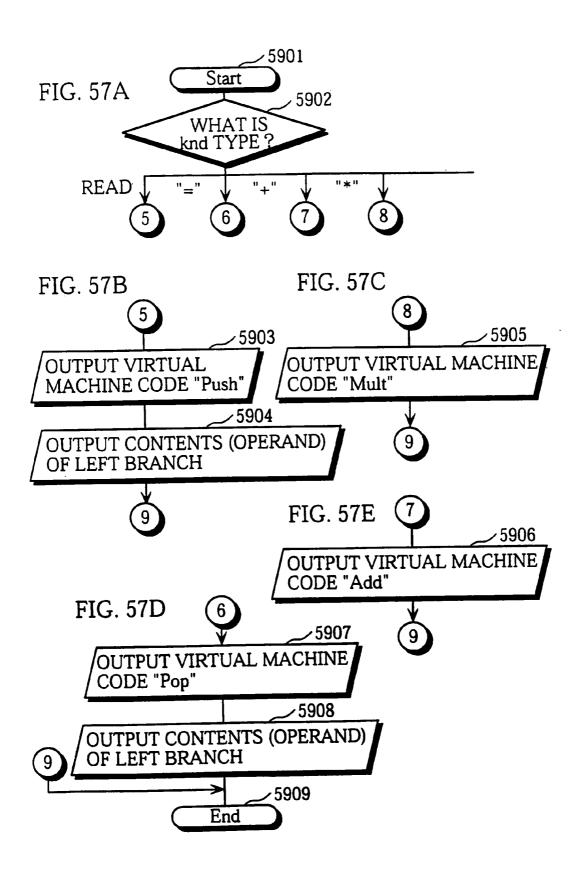

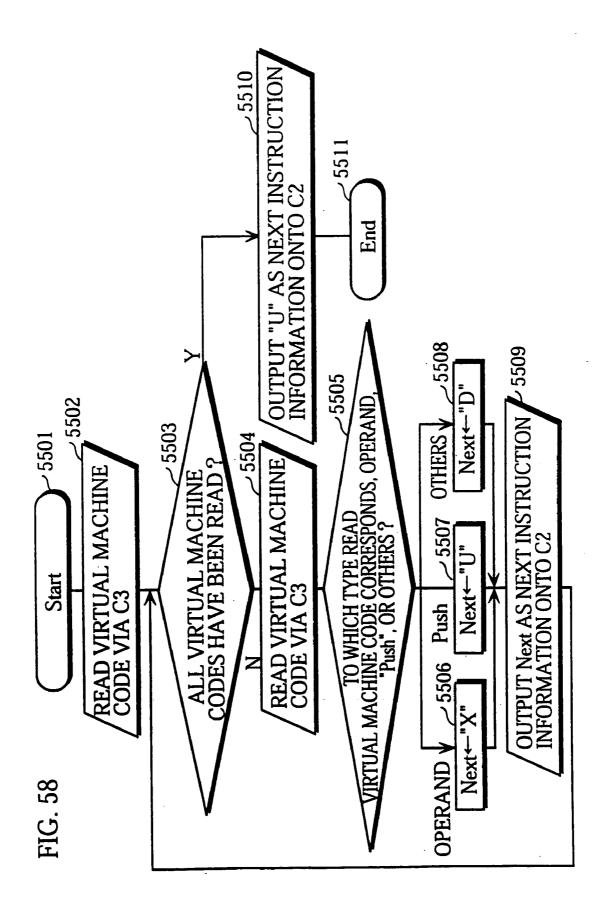

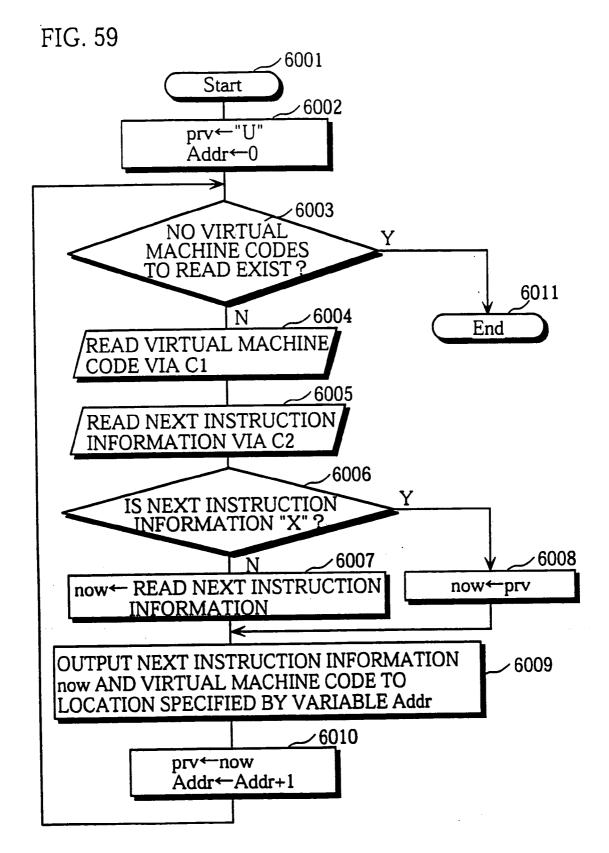

FIG. 7 **-4801** Start *4*802 VCa←READ VIRTUAL NACHINE CODE (OPCODE) 4803 i**←**0 4804 "i" INDICATES AST ENTRY OF √4805 VCb← ith VIRTUAL MACHINE CODE IN TABLE 4806 4808 VCa≡VCb? OUTPUT JUMP ADDRESS IN ith ENTRY 4807 N OF TABLE TO EXECUTING UNIT i←i+1 **∕4809** SUBSTITUE NUMBER OF OPERAND IN ith ENTRY OF TABLE INTO op Count **∠4810** i**←**0 4814 4811 ERROR HANDLING i≧op Count? **/4812** N READ OPERANDS TO OUTPUT TO EXECUTING UNIT 4813 √4815  $i\leftarrow i+1$ End

FIG. 8 4601 Start >< 4602 RECEIVE INPUT VIA SIGNAL LINE R 4603 INPUT FOR READ NUMBER RECEIVED VIA R? ,4604 Count← INPUT NUMBER i←0 4605 dPC←PC **- 4606** i≧ Count? 4607 RECEIVE INPUT VIA R 4608 NOTIFICATION FOR PC CHANGE RECEIVED VIA R? ſΝ **4609** 4614 dPC←dPC+i OUTPUT NOTIFICATION OF 4610 END OF READING VIA R SET READING POSITION AT dPC LOCATION READ VIRTUAL MACHINE 4611 CODE 4612 SEARCH DECODE TABLE AND OUTPUT DECODED DATA **4613**  $i \leftarrow i + 1$

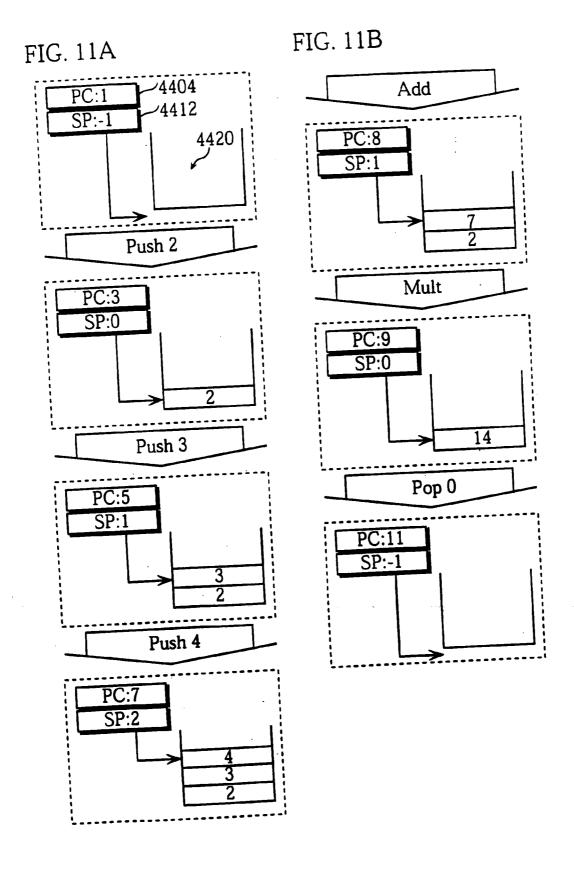

FIG. 10A

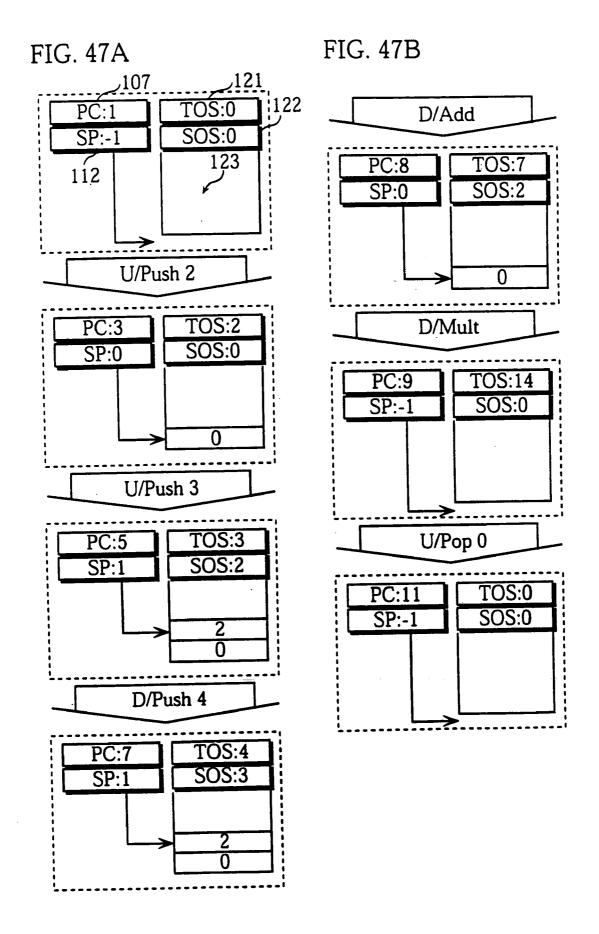

| 1:  | Push |

|-----|------|

| 2:  | 2    |

| 3:  | Push |

| 4:  | 3    |

| 5:  | Push |

| 6:  | 4    |

| 7:  | Add  |

| 8:  | Mult |

| 9:  | Pop  |

| 10: | 0    |

|     |      |

# FIG. 10B

ARITHMETIC EXPRESSION: <DATA AREA #0>=2\*(3+4)

# FIG. 10C

| CONTRACTOR ADDRESS OF CODE TO PERFORM Push                                       |

|----------------------------------------------------------------------------------|

| 1: <jump address="" code="" of="" perform="" push="" to=""></jump>               |

|                                                                                  |

| 2: OPERAND 2  3: <jump address="" code="" of="" perform="" push="" to=""></jump> |

| 3: CJUMP ADDICESO OF GGE                                                         |

| 4: OPERAND "3"                                                                   |

| 4: OPERAND 3 5: < JUMP ADDRESS OF CODE TO PERFORM Push>                          |

| THE PARTY HAT                                                                    |

| 6: OPERAND "4"                                                                   |

| 6: OPERAND 4 7: <jump add="" address="" code="" of="" perform="" to=""></jump>   |

| A PODESS OF CODE TO PERFURIMENT                                                  |

| 8: JUNIT ADDITION OF CODE TO PERFORM POP                                         |

| 8: < JUMP ADDRESS OF CODE TO PERFORM Pop>                                        |

| 10: OPERAND "0"                                                                  |

| 10.01 110 112                                                                    |

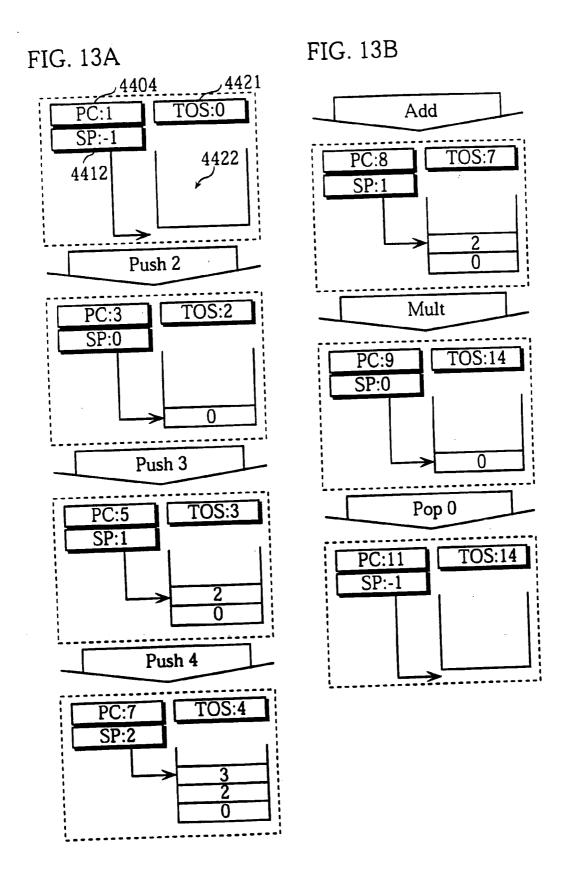

# FIG. 12A

| MICROPROGR                                                                                              | AM FOR VIR    | TUAL MACHINE INSTRUCTION "Push"                                                         |

|---------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------|

| 1:Inc<br>2:Store                                                                                        | r3<br>[r3],r0 | : INCREMENT SP VALUE BY ONE<br>: PLACE VALUE OF TOS REGISTER (#0)<br>: INTO STACK       |

| 3:Load                                                                                                  | r0,[r2]       | ; EXTRACT OPERAND AND                                                                   |

| 4:Inc                                                                                                   | . r2          | ; INCREMENT PC OF VIRTUAL MACHINE BY ONE TO FREI ARCE<br>; FOR READING NEXT INSTRUCTION |

| <micropro< td=""><td>GRAM FOR JU</td><td>MPING TO NEXT VIRTUAL MACHINE INSTRUCTION&gt;</td></micropro<> | GRAM FOR JU   | MPING TO NEXT VIRTUAL MACHINE INSTRUCTION>                                              |

## FIG. 12B

| FIG. 12B                                                                                                  |                | "UAL MACHINE INSTRUCTION "Add"                                                                                    |

|-----------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------|

| 1:Load                                                                                                    | r1,[r3]        | ; EXTRACT VALUE FROM STACK                                                                                        |

| 2:Dec<br>3:Add                                                                                            | r3<br>r0,r0,r1 | DECREMENT VALUE OF VIRTUAL MACHINE PC BY ONE ADD VALUES OF REGISTERS #0 AND #1 AND PLACE RESULT ONTO TOS REGISTER |

| <micropro< td=""><td>OGRAM FOR JU</td><td>IMPING TO NEXT VIRTUAL MACHINE INSTRUCTION&gt;</td></micropro<> | OGRAM FOR JU   | IMPING TO NEXT VIRTUAL MACHINE INSTRUCTION>                                                                       |

# FIG. 12C

|        | r1,[r3]  | UAL MACHINE INSTRUCTION "Mult" ; EXTRACT VALUE FROM STACK AND                    |

|--------|----------|----------------------------------------------------------------------------------|

| 1:Load | 11,(10)  | DI ACE IT ONTO REGISTER #1                                                       |

| 2:Dec  | r3       | DECREMENT VALUE OF VIRTUAL MACHINE SP BY ONE                                     |

| 3:Mult | 11,01,01 | : MULTIPLY VALUES OF REGISTERS #0 AND #1 AND<br>: PLACE RESULT ONTO TOS REGISTER |

# FIG. 12D

| FIG. 12D       |            | THE PROTECTION                                                                                          |

|----------------|------------|---------------------------------------------------------------------------------------------------------|

| < MICROPROC    | RAM FOR JU | MPING TO NEXT VIRTUAL MACHINE INSTRUCTION>                                                              |

| 1:Load         | r1,[r2]    | ; READ VIRTUAL MACHINE INSTRUCTION (JUMP ADDRESS)<br>; INDICATED BY PC INTO REGISTER #1                 |

| 2:Inc<br>3:Jmp | r2<br>rl   | ; INCREMENT VIRTUAL MACHINE PC BY ONE<br>: JUMP UNCONDITIONALLY TO LOCATION<br>INDICATED BY REGISTER #1 |

|                |            |                                                                                                         |

FIG. 14

| STAGE NAME                                                  | NOTATION        |

|-------------------------------------------------------------|-----------------|

| INSTRUCTION FETCH INSTRUCTION DECODE AND REGISTER REFERENCE | <u>IF</u><br>RF |

| EXECUTION                                                   | ALU<br>MEM      |

| MEMORY ACCESS RESULT WRITING TO REGISTER                    |                 |

FIG. 15

| CLOCK         | 1         | 2  | 3   | 4   | 5   | 6   | 7   | 8  |

|---------------|-----------|----|-----|-----|-----|-----|-----|----|

| INSTRUCTION A | IF        | RF | ALU | MEM | WB  |     |     |    |

| INSTRUCTION B | L <u></u> | IF | RF  | ALU | MEM | WB  |     |    |

| INSTRUCTION C |           |    | IF  | RF  | ALU | MEM | WB  |    |

| INSTRUCTION D |           |    |     | IF  | RF  | ALU | MEM | MR |

FIG. 16

| CLOCK                         | 1  | 2   | 3            | 4   | 5   | 6   | 7    | 8   |

|-------------------------------|----|-----|--------------|-----|-----|-----|------|-----|

| INSTRUCTION A1                | IF | RF  | ALU          | MEM | WB  |     |      |     |

| INSTRUCTION A2                | IF | RF  | ALU          | MEM | WB  | TID |      |     |

| INSTRUCTION B1                |    | IF  | RF           | ALU | MEM | WB  |      |     |

| INSTRUCTION B2                |    | 115 | Kr           | RF  | ALU | MEM | WB   |     |

| INSTRUCTION C1                |    |     | TF           | RF  | ALL | MEM | 1    |     |

| INSTRUCTION C2 INSTRUCTION D1 |    |     | <del> </del> | IF  | RF  | ALL | MEN  | WB  |

| INSTRUCTION D2                |    |     |              | IF  | RF  | ALL | JMEM | IMR |

FIG. 17

| CLOCK         | 1  | 2  | 3   | 4   | 5   | 6   | 7   | 8   | 9_ |

|---------------|----|----|-----|-----|-----|-----|-----|-----|----|

| INSTRUCTION A | TF | RF | ALU | MEM | WB  |     |     |     |    |

| INSTRUCTION B |    | ĪF | RF  | •   | ALU | MEM | WB  |     |    |

| INSTRUCTION C |    |    | IF  | •   | RF  | ALU | MEM | WB  |    |

| INSTRUCTION D |    |    |     | ·   | IF  | RF  | ALU | MEM | MB |

## FIG. 18

| CLOCK _        | 1  | 2  | 3   | 4   | 5   | 6        | 7    | 8        | 9_   |

|----------------|----|----|-----|-----|-----|----------|------|----------|------|

| INSTRUCTION A1 | ĪF | RF | ALU | MEM | WB  |          |      |          |      |

| INSTRUCTION A2 |    | RF | ALU | MEM | WB  |          |      |          |      |

| INSTRUCTION B1 |    | IF | RF  | •   | ALU | MEM      | WB   | <u> </u> |      |

| INSTRUCTION B2 |    | IF | RF  | ALU | MEM | WB       |      |          |      |

| INSTRUCTION C1 |    |    | IF  | RF  | ALU | MEM      | WB   |          | ł    |

| INSTRUCTION C2 |    | 1  | IF  | RF  | •   | ALL      | IMEN | IWB      | 1    |

| INSTRUCTION D1 |    |    |     | IF  | RF  | ALL      | IMEN | IWB      | I W  |

| INSTRUCTION D2 |    |    |     | IF  | RF  | <u> </u> | ALL  | MEN      | IVVD |

FIG. 19

| CLOCK                | 1 1 | 2         | 3 1  | 4        | 5                                            | 6    | 7    | 8      | 9   | 10    |

|----------------------|-----|-----------|------|----------|----------------------------------------------|------|------|--------|-----|-------|

| <u> </u>             | 177 | DE        | ATII | MEM      | WB                                           |      |      |        |     | l     |

| <b>INSTRUCTION A</b> | IF  | Kr        | VIO. | IATTIAL  | 1                                            | ATII | MEM  | WB     |     | 1     |

| INSTRUCTION B        |     | <u>IF</u> | Kr   | <u> </u> | <u> </u>                                     | VIO. | ATTI | MEM    | WAR | 1     |

| INSTRUCTION C        |     |           | IF   | •        | <u> </u>                                     | Kr   | ALU  | IVICIV | VEY | KX/DI |

| INSTRUCTION D        |     |           |      |          | <u>                                     </u> | IF   | RF   | ALU    | MCM | IVVD  |

FIG. 20

| CLOCK          | 1  | 2  | 3   | 4   | 5   | 6        | 7   | 8   | 9_   |

|----------------|----|----|-----|-----|-----|----------|-----|-----|------|

| INSTRUCTION A1 | IF | RF | ALU | MEM | WB  |          |     |     |      |

| INSTRUCTION A2 | IF | RF | ALU | MEM | WB  |          |     |     |      |

| INSTRUCTION B1 |    | IF | RF  | •   | •   | ALU      | MEM | WB  |      |

| INSTRUCTION B2 |    | IF | RF  | ALU | MEM | WB       |     |     |      |

| INSTRUCTION C1 |    |    | IF  | RF  | ALU | MEM      | WB  |     |      |

| INSTRUCTION C2 |    |    | IF  | RF  | ALU | MEM      | WB  |     |      |

| INSTRUCTION D1 |    |    |     | IF  | RF  | ALU      | MEM | WB  | <br> |

| INSTRUCTION D2 |    |    |     | IF  | RF  | <u> </u> | ALU | MEM | MR   |

FIG. 21

| CLOCK         | 1  | 2  | 3   | 4   | 5_  | 6   | 7  |

|---------------|----|----|-----|-----|-----|-----|----|

| INSTRUCTION A | IF | RF | ALU | MEM | WB  |     |    |

| INSTRUCTION B |    | IF | х   |     |     |     |    |

| INSTRUCTION C |    |    | IF  | RF  | ALU | MEM | MB |

FIG. 22

| CLOCK                 | 1  | 2  | 3   | 4   | 5   | 6   | 7  |

|-----------------------|----|----|-----|-----|-----|-----|----|

| <b>INSTRUCTION A1</b> | IF | RF | ALU | MEM | WB  |     |    |

|                       | IF | RF | ALU | MEM | WB  |     |    |

| INSTRUCTION B1        |    | IF | х   | 1   |     | '   |    |

| INSTRUCTION B2        |    | IF | X   |     |     |     |    |

| INSTRUCTION C1        |    |    | IF  | RF  | ALU | MEM | MR |

| INSTRUCTION C2        |    |    | IF  | RF  | ALU | MEM | WB |

FIG. 23

| CLOCK 1                 | 2  | 3   | 4   | 5   | 6   | 7   | 8  | 9   | 10  | 11 |

|-------------------------|----|-----|-----|-----|-----|-----|----|-----|-----|----|

| Load r1.[r2] IF         | RF | ALU | MEM | WB  |     |     |    |     | ,   |    |

| Inc r2                  | IF | RF  | ALU |     |     |     |    |     |     |    |

| Jmp r1                  |    | IF  | RF  | ALU | MEM | WB  |    |     |     |    |

| <u> </u>                |    |     | IF  | X   |     |     |    |     |     |    |

| Load r1,[r3]            |    |     |     | IF  | RF  | ALU |    |     |     |    |

|                         |    |     |     |     | IF  | RF  |    |     | WB  |    |

| Dec r3<br>Mult r0,r0,r1 |    |     |     |     |     | IF  | RF | ALU | MEM | WB |

FIG. 24

| CIO            | OCK_          | 1  | 2  | 3   | 4   | 5   | 6        | 7   | 8            | 9        | 10  | <u>11</u> |

|----------------|---------------|----|----|-----|-----|-----|----------|-----|--------------|----------|-----|-----------|

| Load           | r1.[r2]       | ĪF | RF | ALU | MEM | WB  |          |     |              | -        |     |           |

| Inc            | r2            | IF | RF | ALU | MEM | WB  |          |     |              |          |     |           |

|                | rl ,          |    | IF | RF  | ·   | ALU | MEM      | WB  |              |          |     |           |

| J <u>111</u> 1 |               |    | IF | RF  | ALU | х   |          | ] ' |              |          |     |           |

|                |               |    |    | IF  | RF  | x   |          |     |              |          | . ! |           |

|                |               |    | 1  | IF  | RF  | х   | <u> </u> | 1   |              |          |     |           |

|                |               |    | 1  |     | IF  | x   | ]        |     | 1            | 1        |     |           |

|                |               |    | Į. |     | IF  | X   |          |     | <del> </del> | <u> </u> |     | <b>├</b>  |

| Load           | r1,[r3]       |    |    |     |     | IF  | RF       | ALU | IMEN         | IME      | 4   | 1         |

|                |               |    | 1  |     | 1   | IF  | RF       | ALU | JIMEN        | IME      | 1   | 40.00     |

| Dec<br>Mult    | r3<br>r0.r0,1 | -1 | 1  |     | 1   |     | IF       | RF  | <u>'L</u>    | ALL      | MEN | (WB       |

| RZHIII         | 10,10,1       |    | 1  | 1   |     |     |          |     |              |          |     |           |

FIG. 25

| 13                                    |          |               |         |            |        |   |               |        |              | MEMWE   |         |   |

|---------------------------------------|----------|---------------|---------|------------|--------|---|---------------|--------|--------------|---------|---------|---|

| 12                                    |          |               |         |            |        |   |               |        |              | MEN     |         |   |

| 11                                    |          |               |         |            |        |   |               |        | MB<br> <br>  | A1 11 N | 2       |   |

| 10                                    |          |               |         |            |        |   | WB            |        | MEM          | ١.      |         |   |

| 6                                     |          |               |         |            |        |   | MEM           | 111111 | ALU          | C       | IF KF   |   |

| ~                                     | 1        |               |         | WB         |        |   | AI 11         | טבט    | RF           | 117     | 占[      |   |

| 7                                     | 1        |               |         | MEM WB     |        |   | TE DE ALLIMEN | 7      | IF           |         |         | _ |

| 5   6   7   8   9   10   11   12   13 | 1        |               | WB      | ALU        |        | × | 12            | 11     |              |         |         | _ |

| 5                                     | ,        | WB            | MEM     | •          |        | • |               | •      |              |         |         | _ |

| 4                                     | •        | MEM           | ALU     | RF         |        | 7 |               |        |              |         |         | _ |

| 3   4                                 | >        | FALU          | RF      | ഥ          | :      |   |               |        |              |         |         |   |

| 0                                     | J        | R             | 旦       | 1          |        |   | 1             |        |              |         |         |   |

| -                                     | <b>-</b> | 旦             |         |            |        |   |               |        |              |         |         | _ |

| 700                                   | くしつして    | 23 rt [r2] IF | 7,1,1,1 | <b>7</b> 1 | LI     |   |               | 1 [12] | Load 11, hol | 5       | 1-0-0   |   |

| 5                                     | ל        | 7000          | Load    | 111C       | Imp ri |   |               | 1000   | Load         | ည်      | 11. 11. |   |

| 26 |

|----|

| Ċ  |

| FI |

| 13                            |              |           |            |           |        |        |    |    |   |    |             |              | ALUMEM WB   |          |

|-------------------------------|--------------|-----------|------------|-----------|--------|--------|----|----|---|----|-------------|--------------|-------------|----------|

| 12                            |              |           |            |           |        |        |    |    |   |    |             |              | WE          |          |

| 7   8   9   10   11   12   13 |              |           |            |           |        |        |    |    |   |    |             |              | ALU         |          |

| 10                            |              |           |            |           |        |        |    |    |   |    | WB          | WB           | ٠           |          |

| 9                             |              |           |            |           |        |        |    |    |   |    | RF ALUMEMWB | RF ALUMEMWB  | ٠           |          |

| 8                             |              |           | MB         |           |        |        |    |    |   |    | ALU         | ALU          | RF          |          |

| 1                             |              |           | MEM        |           |        |        |    |    |   |    |             | _            | IF          |          |

| 9                             |              |           | ALU MEM WB | ×         | ×      | ×      | ×  | ×  | × | ×  | 出           | 当            |             | _        |

| 5                             | WB           |           | ٠          | MEM       | ALU    | ALU    | RF | RF | H | IF |             |              |             | _        |

| 4                             | MEM          | MEM       | •          | RF ALUMEM | RF ALU | RF ALU | IF | IF |   |    |             |              |             | _        |

| ~                             | ALU          | RF ALUMEM | R          | RF        | 出      | IF     |    |    |   |    |             |              |             | _        |

| 1 1 2 1                       | 吊吊           | RF        | 出          | H         |        |        |    |    |   |    |             |              |             | _        |

|                               | H            | IF        | 1          |           |        |        |    |    |   |    |             |              | <del></del> | <b>-</b> |

| <i>A</i> 00                   | I ad r1 [r2] | 2.        | ! "        |           |        |        |    |    |   |    | 1 [-3]      | 11,119<br>20 | Dec 13      | 1,01,01  |

| ζ                             |              | 1nc 1     | וווג       |           |        |        |    |    |   |    |             | Log<br>L     |             | m⊠       |

FIG. 27

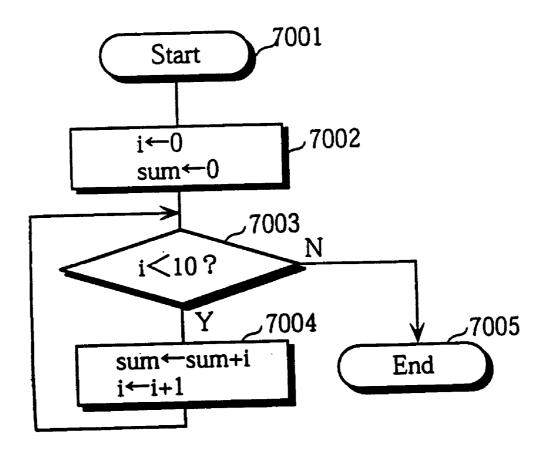

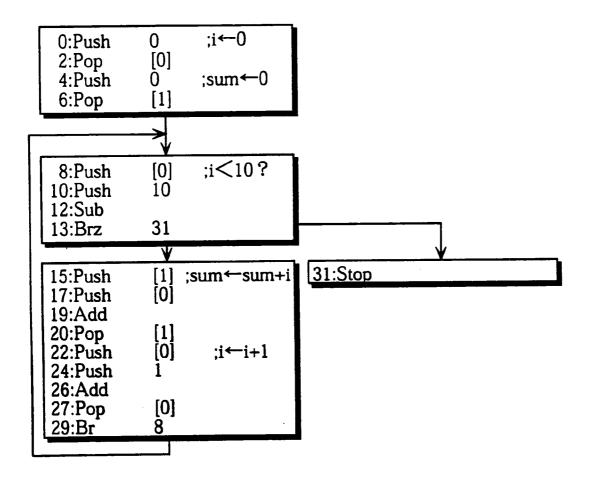

| 0:Push             | 0<br>[0]  | ;i <b>←</b> 0   |

|--------------------|-----------|-----------------|

| 2:Pop<br>4:Push    | Ŏ         | ;sum <b>←</b> 0 |

| 6:Pop              | [1]       |                 |

| 8:Push             | [0]<br>10 | ;i<10?          |

| 10:Push<br>12:Sub  | 10        |                 |

| 13:Brz             | 31        |                 |

| 15:Push            | [1]       | ;sum←sum+i      |

| 17:Push<br>19:Add  | [0]       | ·               |

| 20:Pop             | [1]       | ;i <b>←</b> i+1 |

| 22:Push<br>24:Push | [0]<br>1  | ,1, 141         |

| 26:Add             | (U)       |                 |

| 27:Pop<br>29:Br    | [0]<br>8  |                 |

| 31:Stop            |           |                 |

FIG. 28

FIG. 29

| VIRTUAL<br>MACHINE<br>INSTRICTION | SIZE OF REAL<br>MACHINE CODE<br>TEMPLATE | REAL MACHINE CODE<br>TEMPLATE     | NUMBER OF<br>OPERANDS |

|-----------------------------------|------------------------------------------|-----------------------------------|-----------------------|

|                                   |                                          |                                   | •                     |

| D.ch                              | 4 WORDS                                  | <b>CODE TO PERFORM Push&gt;</b>   | 1                     |

| Lusii                             | 5 WORDS                                  | <b>CODE TO PERFORM Pop&gt;</b>    | 1                     |

| LOD                               | 3 WORDS                                  | <b>CODE TO PERFORM Add&gt;</b>    | 0                     |

| Sub-                              | 3 WORDS                                  | <b>CODE TO PERFORM Sub&gt;</b>    | 0                     |

| N.1t                              | 3 WORDS                                  | <b>CODE TO PERFORM Mult&gt;</b>   | 0                     |

| Duch                              | 5 WORDS                                  | <b>CODE TO PERFORM Push[]&gt;</b> | 1                     |

| Rr                                | 3 WORDS                                  | <b>CODE TO PERFORM Br&gt;</b>     | 1                     |

| Rr7                               | 5 WORDS                                  | <b>CCODE TO PERFORM Brz&gt;</b>   | 1                     |

| Stop                              | 2 WORDS                                  | <b>CCODE TO PERFORM Stop&gt;</b>  | 0                     |

| •                                 | •                                        | • •                               | • •                   |

| •                                 |                                          |                                   |                       |

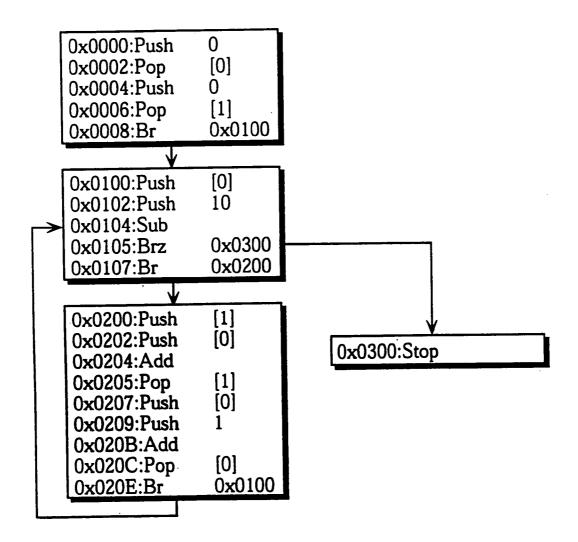

FIG. 30

| VIRTUAL<br>MACHINE<br>CODE<br>ADDRESS | VIRTUAL<br>MACHINE<br>CODE | REAL MACHINE<br>CODE SIZE | CORRESPONDING<br>REAL MACHINE<br>CODE ADDRESS |

|---------------------------------------|----------------------------|---------------------------|-----------------------------------------------|

| 0                                     | Push 0                     | 4                         | 0-3                                           |

| 2                                     | Pop [0]                    | 5                         | 4-8                                           |

| 4                                     | Push 0                     | 4                         | 9-12                                          |

| 6                                     | Pop [1]                    | 5                         | 13-17                                         |

| 8                                     | Push [0]                   | 5                         | 18-22                                         |

| 10                                    | Push 10                    | 4                         | 23-26                                         |

| 12                                    | Sub                        | 3                         | 27-29                                         |

| 13                                    | Brz 31                     | 5                         | 30-34                                         |

| 15                                    | Push [1]                   | 5                         | 35-39                                         |

| 17                                    | Push [0]                   | 5                         | 40-44                                         |

| 19                                    | Add                        | 3                         | 45-47                                         |

| 20                                    | Pop [1]                    | 5                         | 48-52                                         |

| 22                                    | Push [0]                   | 5                         | 53-57                                         |

| 24                                    | Push 1                     | 4                         | 58-61                                         |

| 26                                    | Add                        | 3                         | 62-64                                         |

| 27                                    | Pop [0]                    |                           | 65-69                                         |

| 29                                    | Br 8                       | 3                         | 70-72                                         |

| 31                                    | Stop                       | 2                         | 73-75                                         |

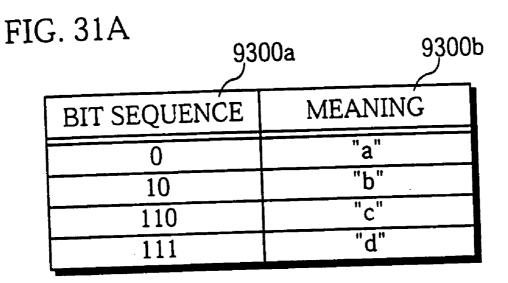

FIG. 31B

# FIG. 33

FIG. 36A

1: U

2: U

3: U

4: U

5: D

6: D

7: D

8: D

9: U

10: U

FIG. 36B

|     |      | 102ر |

|-----|------|------|

| 1:  | Push |      |

| 2:  | 2    |      |

| 3:  | Push |      |

| 4:  | 3    |      |

| 5:  | Push |      |

| 6:  | 4    |      |

| 7:  | Add  |      |

| 8:  | Mult |      |

| 9:  | Pop  |      |

| 10: | 0    |      |

|     |      |      |

| FIG. 37 | 00                                 | 108b 108c                                                                          | 108d                  |

|---------|------------------------------------|------------------------------------------------------------------------------------|-----------------------|

| OPCODE  | NEXT<br>INSTRUCTION<br>INFORMATION | JUMP ADDRESS                                                                       | NUMBER OF<br>OPERANDS |

|         | ••                                 |                                                                                    | • •                   |

| Push    | n                                  | <jump "u"="" address="" assigned="" code="" of="" perform="" push="" to=""></jump> |                       |

| Push    | Q                                  | <jump "d"="" address="" assigned="" code="" of="" perform="" push="" to=""></jump> | 1                     |

| Pop     | n                                  | <jump "u"="" address="" assigned="" code="" of="" perform="" pop="" to=""></jump>  | 1                     |

| Pop     | D                                  | <jump "d"="" address="" assigned="" code="" of="" perform="" pop="" to=""></jump>  | 1                     |

| Add     | Ω                                  | <jump "u"="" add="" address="" assigned="" code="" of="" perform="" to=""></jump>  | 0                     |

| Add     | Q                                  | <jump "d"="" add="" address="" assigned="" code="" of="" perform="" to=""></jump>  | 0                     |

| Sub     | n                                  | <jump "u"="" address="" assigned="" code="" of="" perform="" sub="" to=""></jump>  | 0                     |

| Sub     | D                                  | <jump "d"="" address="" assigned="" code="" of="" perform="" sub="" to=""></jump>  | 0                     |

| Inc     | n                                  | <jump "u"="" address="" assigned="" code="" inc="" of="" perform="" to=""></jump>  | 0                     |

| Inc     | D                                  | <jump "d"="" address="" assigned="" code="" inc="" of="" perform="" to=""></jump>  | 0                     |

| ••      | ••                                 |                                                                                    | ••                    |

|         |                                    |                                                                                    |                       |

FIG. 38A

| ſ | MICROPE          | ROGRA         | M FOR VIRTUAL MACHINE INSTRUCTION "Push" WITH "U"                                                     |

|---|------------------|---------------|-------------------------------------------------------------------------------------------------------|

|   | 1:Load           | r4,r0         | COPY VALUE OF TOS REGISTER (#0) INTO SOS REGISTER (#4)                                                |

|   | 2:Load           | r0,[r2]       | man man processor                                                                                     |

|   | 3:Inc            | r2            | INCREMENT VIRTUAL MACHINE PC BY ONE TO PREPARE FOR READING NEXT INSTRUCTION                           |

|   | 4:Inc<br>5:Store | r3<br>[r3],r4 | ;INCREMENT VIRTUAL MACHINE SP BY ONE<br>;PLACE SOS REGISTER VALUE INTO STACK                          |

|   | 6:Load           | r1,[r2]       | ;READ VIRTUAL MACHINE INSTRUCTION<br>(JUMP ADDRESS) INDICATED BY<br>PC INTO REGISTER #1               |

|   | 7:Inc<br>8:Jmp   | r2<br>r1      | ;INCREMENT VIRTUAL MACHINE PC BY ONE<br>;JUMP UNCONDITIONALLY TO LOCATION<br>INDICATED BY REGISTER #1 |

# FIG. 38B

| MICRO                   | PROGRAM  | M FOR VIRTUAL MACHINE INSTRUCTION "Push" WITH "D"                                                                            |

|-------------------------|----------|------------------------------------------------------------------------------------------------------------------------------|

| 1:Load                  | r4,r0    | ;COPY VALUE OF TOS REGISTER (#0)                                                                                             |

| 2:Load                  | r0,[r2]  | INTO SOS REGISTER (#4)<br>;READ OPERAND INTO TOS REGISTER                                                                    |

| 3:Inc                   | r2       | INCREMENT VIRTUAL MACHINE PC BY ONE TO PREPARE FOR READING NEXT INSTRUCTION                                                  |

| 6:Load                  | r1,[r2]  | READ VIRTUAL MACHINE INSTRUCTION (JUMP ADDRESS) INDICATED BY                                                                 |

| 7:Inc<br>8: <u>J</u> mp | r2<br>r1 | PC INTO REGISTER #1<br>:INCREMENT VIRTUAL MACHINE PC BY ONE<br>:JUMP UNCONDITIONALLY TO LOCATION<br>INDICATED BY REGISTER #1 |

MICROPROGRAM FOR VIRTUAL MACHINE INSTRUCTION "Add" WITH "U"

;ADD VALUES OF TOS REGISTER AND SOS REGISTER, r0,r0,r4

1:Add

AND PLACE RESULT INTO TOS REGISTER

<MICROPROGRAM FOR VIRTUAL MACHINE JUMP CODE WITH "U">

FIG. 39B

MICROPROGRAM FOR VIRTUAL MACHINE INSTRUCTION "Add" WITH "D"

1:Add r0,r0,r4; ADD VALUES OF TOS REGISTER AND SOS REGISTER AND PLACE RESULT INTO TOS REGISTER

<MICROPROGRAM FOR VIRTUAL MACHINE JUMP CODE WITH "D">

# FIG. 40A

MICROPROGRAM FOR VIRTUAL MACHINE INSTRUCTION "Mult" WITH "U"

1:Mult 10,10,14 ;MULTIPLY VALUES OF TOS REGISTER AND SOS REGISTER, AND PLACE RESULT INTO TOS REGISTER

<MICROPROGRAM FOR VIRTUAL MACHINE JUMP CODE WITH "U">

FIG. 40B

MICROPROGRAM FOR VIRTUAL MACHINE INSTRUCTION "Mult" WITH "D"

1:Mult 10,10,14 ;MULTIPLY VALUES OF TOS REGISTER AND SOS REGISTER, AND PLACE RESULT INTO TOS REGISTER

<MICROPROGRAM FOR VIRTUAL MACHINE JUMP CODE WITH "D">

# FIG. 41A

| A GODO | a          | MACHINE HIMP CODE WITH "U"                       |

|--------|------------|--------------------------------------------------|

| MICKUL | RUGE       | M FOR VINIONE MINISTER COLUMNIA                  |

| 1:Load | r1.[r2]    | 1:Load r1.[r2] ;READ VIRTUAL MACHINE INSTRUCTION |