(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-266662

(P2005-266662A)

(43) 公開日 平成17年9月29日(2005.9.29)

(51) Int.Cl.<sup>7</sup>

G10H 1/18

F 1

G10H 1/18

101

テーマコード(参考)

5D378

|           |                            | 審査請求 未請求 請求項の数 5 O L (全 14 頁)                       |

|-----------|----------------------------|-----------------------------------------------------|

| (21) 出願番号 | 特願2004-82414 (P2004-82414) |                                                     |

| (22) 出願日  | 平成16年3月22日 (2004.3.22)     |                                                     |

|           |                            | (71) 出願人 000001410<br>株式会社河合楽器製作所<br>静岡県浜松市寺島町200番地 |

|           |                            | (74) 代理人 100086863<br>弁理士 佐藤 英世                     |

|           |                            | (72) 発明者 ▲高▼氏 清己<br>静岡県浜松市寺島町200番地 株式会社<br>河合楽器製作所内 |

|           |                            | F ターム(参考) 5D378 BB03 CC42 CC46                      |

(54) 【発明の名称】音源装置

## (57) 【要約】

【課題】 特定のチャンネルに固定的な状態にならないようにして、外部のプロセッサから波形メモリへのアクセスができるようにした音源装置を提供する。

【解決手段】 波形メモリ101と、時分割チャンネル処理で動作し、楽音生成に関するパラメータに基づいて1又は複数チャンネル分の楽音波形データを波形メモリ101から読み出して、所望の楽音信号を生成すると共に、空きのあるチャンネルとその空きタイミングとを含む空きチャンネル情報を出力する楽音生成部1001と、該空きチャンネル情報に基づき、空きチャンネルの少なくとも1つを用いて、その空きタイミングの間、外部のCPU201から、波形メモリ101へアクセスさせるアクセス制御部1002とを有している。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

楽音波形データを記憶する波形メモリと、

時分割チャンネル処理で動作し、楽音生成に関するパラメータに基づいて 1 又は複数チャンネル分の楽音波形データを上記波形メモリから読み出して、所望の楽音信号を生成すると共に、空きのあるチャンネルとその空きタイミングとを含む空きチャンネル情報を出力する楽音生成手段と、

該空きチャンネル情報に基づき、空きチャンネルの少なくとも 1 つを用いて、その空きタイミングの間、外部のプロセッサから、上記波形メモリへアクセスさせるアクセス制御手段と

10

を有することを特徴とする音源装置。

**【請求項 2】**

空きチャンネルがない時に、上記楽音生成手段により、特定のチャンネルをトランケート処理して発音処理を終了させ、その空きチャンネル情報を受信した上記アクセス制御手段により、特定の空きチャンネルを使用して、外部のプロセッサから、上記波形メモリへアクセスさせることを特徴とする請求項 1 記載の音源装置。

**【請求項 3】**

上記楽音生成手段によるチャンネルのトランケート処理は、最も先に押されたキーが使用しているチャンネルに対して行われることを特徴とする請求項 2 記載の音源装置。

**【請求項 4】**

上記楽音生成手段によるチャンネルのトランケート処理は、特定の音域にあるキーが使用しているチャンネルに対して行われることを特徴とする請求項 2 記載の音源装置。

20

**【請求項 5】**

上記楽音生成手段によるチャンネルのトランケート処理は、最も発音レベルの小さなチャンネルに対して行われることを特徴とする請求項 2 記載の音源装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、外部のプロセッサ（CPUなどのマイクロプロセッサ）から波形メモリへのアクセスが可能な音源装置に関する。

30

**【背景技術】****【0002】**

従来電子楽器などにおいては、楽音波形のサンプル値データを記憶している波形メモリから波形データを順次読み出すことで、楽音信号を生成している。このような電子楽器では、複数の楽音信号を同時に発音するために、1サンプリングタイム時間内に、時分割処理により、複数のチャンネル毎に波形データを読み出し、該サンプリングタイム時間内に読み出された波形データを夫々のチャンネル毎に累算して、複数の波形データが同時に読み出されることになる。

**【0003】**

他方上記波形メモリには、波形データ以外にも例えば電子楽器に備えられた CPU が使用する特定のシーケンスデータなどを記憶しておくことが可能である。そのため、該 CPU から、波形メモリへのアクセスができるようにすることを目的として、複数のチャンネルのうち、1 チャンネルを CPU によるデータ読み出し書き込み専用にする構成が提案されている（後述する特許文献 1、特に段落番号 0011 の記載を参照のこと）。

40

**【特許文献 1】特開平 7 - 168574 号****【発明の開示】****【発明が解決しようとする課題】****【0004】**

しかし、上記従来構成では、特定のチャンネルが CPU アクセス専用に固定的に使用され、例えば或るタイミングで全てのチャンネルを楽音信号発生に使用したい場合などは、

50

それができないなど、チャンネルアサインにおいてフレキシブルさを欠くといった問題を生じていた。

#### 【0005】

本発明は、以上のような問題に鑑み創案されたもので、特定のチャンネルに固定的な状態にならないようにして、外部のプロセッサから波形メモリへのアクセスができるようにした音源装置を提供せんとするものである。

#### 【課題を解決するための手段】

#### 【0006】

そのため本発明に係る音源装置は、

楽音波形データを記憶する波形メモリと、

時分割チャンネル処理で動作し、楽音生成に関するパラメータに基づいて1又は複数チャンネル分の楽音波形データを上記波形メモリから読み出して、所望の楽音信号を生成すると共に、空きのあるチャンネルとその空きタイミングとを含む空きチャンネル情報を出力する楽音生成手段と、

該空きチャンネル情報に基づき、空きチャンネルの少なくとも1つを用いて、その空きタイミングの間、外部のプロセッサから、上記波形メモリへアクセスさせるアクセス制御手段と

を有することを基本的特徴としている。

#### 【0007】

上記構成によれば、楽音生成手段が、楽音信号の生成以外にも空きチャンネル情報をアクセス制御手段に対して出力しており、その空きチャンネル情報を基に、該アクセス制御手段が、空きチャンネルの少なくとも1つを用いて、その空きタイミングの間、外部のプロセッサ(CPUなどのマイクロプロセッサ)から、上記波形メモリへアクセスさせることになる。そのため、外部のプロセッサから波形メモリへのアクセスが特定のチャンネルに固定してしまわない状態にして、波形メモリへのアクセスを可能にしている。

#### 【0008】

他方、上記のような構成において、空きチャンネルがなくなったタイミングでは、上記楽音生成手段により、特定のチャンネルをトランケート処理して発音処理を終了させ、その空きチャンネル情報を受信した上記アクセス制御手段により、特定の空きチャンネルを使用して、外部のプロセッサから、上記波形メモリへアクセスさせるようにする構成とすることも可能である。

#### 【0009】

そのようなチャンネルのトランケート処理は、最も先に押されたキーが使用しているチャンネルに対して行われることでも良い。

#### 【0010】

また同じくチャンネルのトランケート処理は、特定の音域にあるキー(目立たない音域にあるキー)が使用しているチャンネルに対して行われることでも良い。

#### 【0011】

さらに上記トランケート処理は、最も発音レベルの小さなチャンネルに対して行われるようにしても良い。

#### 【発明の効果】

#### 【0012】

本発明の請求項1記載の音源装置によれば、楽音生成手段が、楽音信号の生成以外にも空きチャンネル情報をアクセス制御手段に対して出力しており、その空きチャンネル情報を基に、該アクセス制御手段が、空きチャンネルの少なくとも1つを用いて、その空きタイミングの間、外部のプロセッサから、上記波形メモリへアクセスされることになるため、外部のプロセッサから波形メモリへのアクセスが特定のチャンネルに固定してしまわない状態にして、波形メモリへのアクセスを可能になるという優れた効果を奏し得る。すなわち、外部のプロセッサから波形メモリへアクセスさせる構成の場合にも、そのアクセスについてフレキシブルなチャンネルアサインを可能にする。

## 【0013】

また請求項2～5の構成によれば、上記空きチャンネルを使用して外部のプロセッサから波形メモリへアクセスさせる請求項1の構成の場合に、空きチャンネルがなくなったタイミングでも、上記楽音生成手段により、特定のチャンネル（請求項3～5に記載）をトランケート処理して発音処理を終了させ、その空きチャンネル情報を受信した上記アクセス制御手段により、特定の空きチャンネルを使用して、外部のプロセッサから、上記波形メモリへアクセスするようになることが可能となる。

## 【発明を実施するための最良の形態】

## 【0014】

以下、本発明の実施の形態を図示例と共に説明する。

10

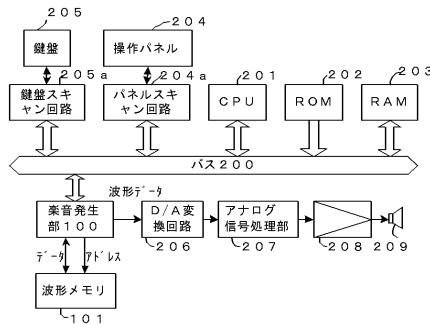

図1は、本発明に係る音源装置の構成を備えた電子楽器（例えば電子オルガン）の回路概略図である。

## 【0015】

本電子楽器は、電子ピアノの鍵盤で任意の音色を演奏したり、電子オルガンの上下手鍵盤及び足鍵盤などに夫々異なる音色を割り当てることができるようになっており、しかも鍵盤は、左右でスプリットされ、夫々の位置で同じく違う音色が設定できるようになっている。従って、これらの鍵盤などを押鍵すると、夫々の楽音が同時に発生するのに必要なチャンネル数は、64チャンネル数を超えることが多い。

## 【0016】

本電子楽器は、図1に示すように、システムバス200を介して、CPU201、ROM202、RAM203、パネルスキャン回路204a、鍵盤スキャン回路205a、楽音発生部100が相互に接続されて構成されている。システムバス200は、アドレス信号、データ信号又は制御信号等を送受するために使用される（アドレスバス、データバス、コントロール信号ラインよりなる信号バス）。

20

## 【0017】

CPU201は、本電子楽器の制御をつかさどる中央演算装置であって、後述するROM202に格納されているプログラムに従って、鍵盤スキャン回路205aとパネルスキャン回路204aを制御して鍵盤205のキー、操作パネル204の音色設定スイッチなどを走査し、鍵盤205の押鍵・離鍵に伴う押鍵データ[KEY-ON·OFF、キー識別情報（キー番号など）、キータッチレスポンス：キーデータ]の楽音発生部100への割り当て処理、操作パネル204の音色設定スイッチ、ボリュームに応じて楽音発生部100より所望の楽音信号を発生させるように制御する。また後述するように、必要に応じて、直接波形メモリ101のCPU用データエリアに、アクセス制御部の制御に従って、シーケンスデータなどの読み込み・書き込みを行う。

30

## 【0018】

上記ROM202は、上述したCPU201用のプログラムの他に、CPU201が楽音発生に参照する種々のパラメータデータを格納する読み出し専用メモリである。

## 【0019】

上記RAM203は、CPU201におけるプログラム処理での処理段階のデータを一時記憶しておいたり、エディット可能なパラメータデータを記憶しておく、読み書き可能でメモリである。一部はバッテリバックアップされており、操作パネル204の音色設定に応じた必要なデータを格納保持（電源がOFFとなっても格納保持）しておくことができる。また、このRAMには、必要に応じてレジスタ、カウンタ、フラグ機能等が定義されている。

40

## 【0020】

パネルスキャン回路204aは、CPU201からの指令に応答して操作パネル204上の各スイッチをスキャンし、このスキャンにより得られた各スイッチの開閉状態を示す信号に基づいて、各スイッチを1ビットに対応させたパネルデータを作成する。各ビットは、例えば「1」でスイッチオン状態、「0」でスイッチオフ状態を表す。このパネルデータは、システムバス200を介してCPU201に送られる。このパネルデータは、操

50

作パネル 204 上のスイッチのオンイベント又はオフイベントが発生したかどうかを判断するために使用される。

#### 【0021】

また、パネルスキャン回路 204a は、CPU201 から送られてきた表示データを操作パネル 204 上の LED 表示器及び LCD に送る。これにより、CPU201 から送られてきたデータに従って、LED 表示器が点灯 / 消灯され、また LCD にメッセージが表示される。

#### 【0022】

パネルスキャン回路 204a には、操作パネル 204 が接続されている。操作パネル 204 には、音色選択及び設定するためのスイッチやボリュームや、選択及び設定状態を表示する上記 LCD 乃至 LED 表示器などより構成される表示部を有している。操作パネル 204 の音色選択により音色設定フラグの設定がなされる。また、演奏者の操作パネル 204 の操作により、音色設定フラグが直接変更される場合もある。

#### 【0023】

上記鍵盤スキャン回路 205a は、鍵盤 205 で生成される押鍵データを検出する検出回路である。すなわち、これらの鍵盤 205 には、夫々 2 点スイッチが設けられており、任意の鍵盤 205 が所定以上の深さまで押し下げられたことを検出すると、その鍵盤の音高データ（キー番号）の押鍵信号を生成すると共に、2 点スイッチ間を通過する速度からベロシティを生成し、それらを押鍵データとして、鍵盤スキャン回路 205a に送る。2 点スイッチとしては、鍵が所定以上の深さまで押し下げられたことを検出できる光センサ、圧力センサ、その他のセンサを使用できる。鍵盤スキャン回路 205a は、2 点スイッチからの押鍵データを受け取ると、それを CPU201 に送る。

#### 【0024】

鍵盤スキャン回路 205a からの押鍵データは、CPU201 により、RAM203 上の音色設定フラグが参照され、夫々のチャンネルに対応する楽音発生部 100 に送られることになる。

#### 【0025】

楽音発生部 100 は、専用の LSI で設計されており、上記操作パネル 204 で選択及び設定された音色で、鍵盤 205 で演奏されたキーに応じた読み出しアドレスを発生して、本願の波形データ記憶手段に相当する後述の波形メモリ 101 から原データを読み出し、さらに、該原データの補間処理を行った後、同じく同回路で生成された音色毎のエンベロープを乗算し、夫々の音色の波形データを設定されたチャンネル分累算して、外部に楽音信号を発生する。この構成の詳細は後に説明する。また図示していないが、この楽音信号に所定の音響効果（残響効果を含む）を付加する音響効果付加構成も備えていても良い。さらに、楽音発生部 100 から出力された楽音信号は、D/A 変換回路 206 に入力され、デジタル - アナログ変換され、アナログ信号処理部 207 でノイズが除去され、アンプ 208 で増幅されて、スピーカ 209 から外部に楽音として放出される。

#### 【0026】

波形メモリ 101 は、本実施形態構成では、データの読み書きが可能なランダムアクセスメモリで構成されている。従って、本電子楽器がスイッチ ON されてイニシャル処理がなされた後などに、上記 ROM202 などから楽音波形データが読み出され、そこに記憶されることになる。該楽音波形データは、音色及び音域（音高）に対応しているため、音色選択及び押鍵データに応じて、所望の楽音周波数に従って上記楽音発生部 100 からの読み出し信号で該データが読み出されることになる。この波形データは、例えばヘッド部とループ部で構成される波形データとして音色・音域に関連して所定のエリアに記憶されている。またこの波形メモリ 101 の一部には、後述する図 5(b) に示すように、CPU 用データエリアが確保されている。

#### 【0027】

D/A 変換回路 206 は、上記楽音発生部 100 で生成されたデジタル楽音信号をアナログ楽音信号に変換するデジタル - アナログ変換器である。

10

20

30

40

50

## 【0028】

アナログ信号処理部207は、アナログ楽音信号に対して簡単なフィルタ処理（ノイズ除去）、増幅処理を施す信号処理回路である。

## 【0029】

アンプ208は、アナログ処理されたアナログ楽音信号をスピーカ209で発生させるために増幅するパワーアンプである。

## 【0030】

スピーカ209は、アナログ信号を可聴信号として放音するスピーカであり、1乃至複数個よりなる。

## 【0031】

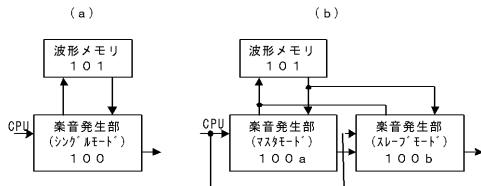

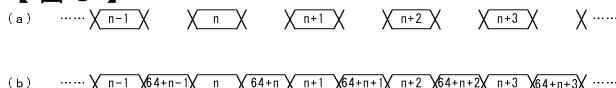

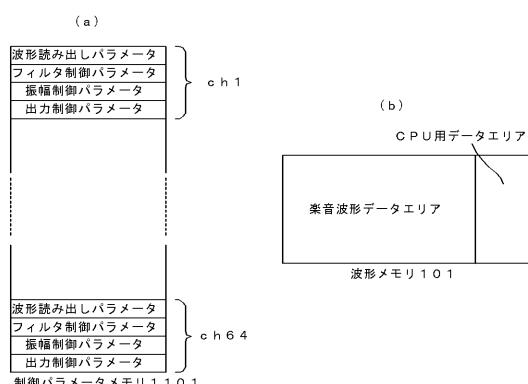

図2は、上記楽音発生部100（後述するようにこの構成は、さらに楽音生成部とアクセスト制御部により構成される）と波形メモリ101とで構成される本願発明に係る音源装置構成の概要図を示し、図3はその構成における波形データ読み出しタイミングのタイムチャートを示している。

10

## 【0032】

図2(a)に示される構成は、楽音発生部100が1つの場合であり、該楽音発生部100が波形メモリ101に対して記憶されている波形データを読み出すために1つのチャンネル（任意のチャンネルをnとしている）で一回アクセスしている。そのアクセスタイミングは、図3(a)に示されるように、1つおきになされており、半分のタイミングは余っている。この半分の空きタイミングにおいて、CPU201が該波形メモリ101に対してアクセスすることを可能にしている。

20

## 【0033】

図2(b)に示される構成は、楽音発生部100が2つの場合であり、マスタ楽音発生部100a及びスレーブ楽音発生部100bが、波形メモリ101に対して、夫々1つのチャンネルnと $64 + n$ （64は1つの楽音発生部が有するチャンネル数）で一回アクセスしている。この場合は、マスタ楽音発生部100a及びスレーブ楽音発生部100bが波形メモリ101から波形データを読み出すために、図3(b)に示されるように、アクセスタイミングが全て使われてあり、CPU201が波形メモリ101に対するアクセスタイミングがない。強制的にCPU201が波形メモリ101にアクセスするようにすることも可能であるが、そうすると発音中に楽音信号にCPU201とのデータが混じり込みノイズになってしまう。この点については本実施形態構成では後述する構成によりそのような不具合を回避できるようにしている。

30

## 【0034】

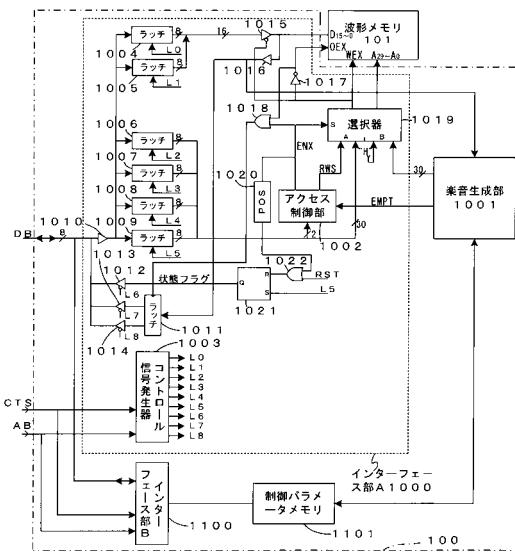

図4は、図1の波形メモリ101と楽音発生部100（一点鎖線で示している）に備えられたCPUインターフェースを中心とした説明図である。同図には、特に波形メモリ101とのCPUインターフェースを詳細にしたインターフェース部（点線で示している）が示されている。

40

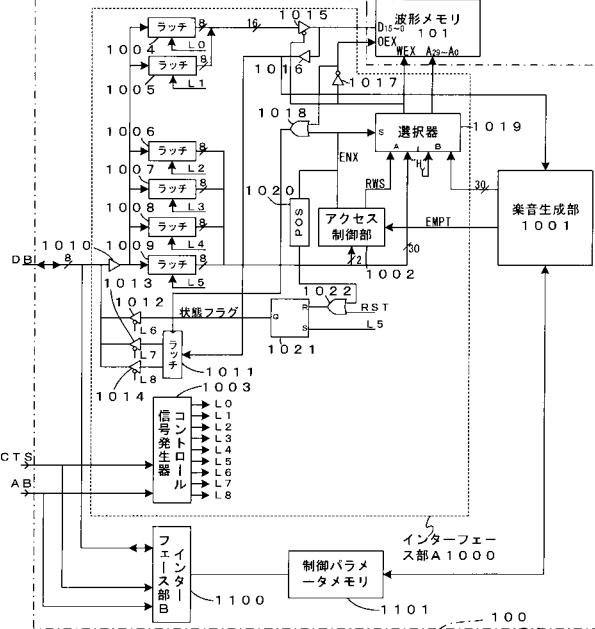

## 【0035】

楽音発生部100に構成されるCPUインターフェースのうち、点線で示されたCPUインターフェース部Aは、波形メモリ101に対してCPU201がアクセスするためのインターフェース回路である。該CPU201は、図5(b)に示される構成の波形メモリ101に対して、その楽音波形データエリアに楽音波形データを書き込んだり、必要に応じて設けられているCPU用データエリアに対して、CPU201が予め記憶されている楽音生成のパラメータを使用したり、或いは演算途中のデータを一時的に蓄えたりするために、それらのデータの読み書きを行う。

## 【0036】

一方点線の外側にあるCPUインターフェース部Bは、楽音発生のために使用するデータをCPU201から書き込む（一部読み出すことも想定される）ためのインターフェース回路である。上記CPU201は、図5(a)で示す構成の制御パラメータメモリに対して、例えば発音のために特定のチャンネルが割り当てられれば、該当するチャンネルに発

50

音に必要な制御パラメータ（波形読み出しパラメータ、フィルタ制御パラメータ、振幅制御パラメータ、出力制御パラメータ）をセットするようとする。

#### 【0037】

楽音発生部100に備えられた楽音生成部1001は、図5(a)に示された制御パラメータメモリ1101の制御パラメータに応答して、操作パネル204で選択・設定された音色で、鍵盤205で演奏されたキーに応じた楽音信号を発生する。またこの楽音生成部1001は、チャンネル毎に時分割で構成される各チャンネル毎の発音状態から、空きのあるチャンネルとその空きタイミングとを含む空きチャンネル情報EMPTを、後述するアクセス制御部1002に出力する。

#### 【0038】

同じく楽音発生部100に備えられたアクセス制御部1002は、CPU201側に波形メモリ101へのアクセスを許可する信号ENX（アクティプ“L”）とCPU201側からのアクセスがリード（Read）であるかライト（Write）であるかを表すリードライト信号RWSを出力する。その出力条件は、後述するラッチ1009における、図6(b)に示す上位2ビットとして保持されている制御信号C<sub>1</sub>、C<sub>0</sub>が、“10b”（データの波形メモリ201への書き込み）か“11b”（データを波形メモリ201より読み込み）で、上記楽音生成部1001より出力される空きチャンネル情報EMPTの出力があり、その情報から得られる空いているチャンネルと空きタイミングからCPU201からのアクセスが可能であることを示す時、出力される。すなわち、CPU201より波形メモリ101へのアクセス許可は、楽音生成部1001の空きチャンネル・空きタイミングを利用して行うことになる。

#### 【0039】

一方上記制御パラメータメモリ1101は、図5(a)に示すように、例えば64発音を制御するためにチャンネル1～64で構成されるエリアを持つメモリである。夫々のパラメータについては、次のように定義される。

#### 【0040】

波形読み出しパラメータ：押鍵データ[キーON・OFF、キー識別情報]と音色情報に応答して、波形メモリ101から記憶されている所望の楽音波形データを所望の楽音周波数に応じた速度で読み出すためのパラメータである。

#### 【0041】

フィルタ制御パラメータ：押鍵データ[キーON・OFF、キー識別情報(キー番号など)、キータッチレスポンス]と音色情報によって、楽音周波数に応じて出力される波形データに含まれる周波数成分を制御するパラメータである。

#### 【0042】

振幅制御パラメータ：押鍵データ[キーON・OFF、キー識別情報(キー番号など)、キータッチレスポンス]と音色情報に応答して、振幅を制御するためのパラメータである。

#### 【0043】

出力制御パラメータ：押鍵データ[キーON・OFF、キー識別情報(キー番号など)、キータッチレスポンス]と音色情報に応答して、出力信号のパンポット制御などをするためのパラメータである。

#### 【0044】

さらにインターフェース部A1000内のコントロール信号発生器1003は、CPU201からのアドレスバスAB及びコントロール信号CTS（チップセレクト信号CEX、ライトWEX、出力イネーブルOEXなどで構成）を受けて、CPU201からのアクセスに必要なコントロール信号L<sub>0</sub>～L<sub>8</sub>を発生する。図6(a)は、そのアドレスとコントロール信号の対応関係を示している。左欄はアドレス、その隣の欄は該アドレスに対するインターフェース部A内のジョブ内容、更に右欄はそれに対応するコントロール信号L<sub>0</sub>～L<sub>8</sub>と信号の形状種類（アクティブ“H”：CPU201からのデータライト、アクティブ“L”：CPU201からのデータリード）を示している。

10

20

30

40

50

## 【0045】

ラッチ1004及び1005は、8ビットのデータ保持器で、C P U 2 0 1から波形メモリ101に書き込みたいデータをセットしておくものである。

## 【0046】

ラッチ1006～1009は、8ビットのデータ保持器で、波形メモリ101にアクセスするために、アクセスしたいエリアを特定するアドレスをC P U 2 0 1からセットしておくものである。ラッチ1009に関しては、上述したように、C P U 2 0 1とのインターフェースのジョブの種類を示す制御情報[図6(b)に示す上位2ビットとして保持されている制御信号C<sub>1</sub>、C<sub>0</sub>]も含まれている。

## 【0047】

バッファ1010は、C P U 2 0 1からのデータバスD Bをバッファする構成である。

## 【0048】

ラッチ1011は、波形メモリ101からバッファ1016を経由して送られてきた、波形メモリ101から読み出したデータを保持しておく構成である。

## 【0049】

バッファ1012～1014は、入力される制御信号に応答して入力されている信号を出力側に出力するバッファで、制御信号がアクティブ以外の時はハイインピーダンス状態となる。そのうちバッファ1012は状態を読む(状態フラグで読み取られる)ためのもの、またバッファ1013及び1014はラッチ1011に蓄えられている波形メモリ101から読み出したデータを8ビット単位で読み込むための構成で、夫々C P U 2 0 1のデータバスD Bに出力する。

## 【0050】

バッファ1015は、入力される制御信号に応じて入力されている信号を出力側に出力するバッファで、制御信号がアクティブ以外の時はハイインピーダンス状態になり、ラッチ1004及び1005に保持されているC P U 2 0 1から波形メモリ101に書き込みたいデータを波形メモリ101のデータバス(D<sub>15</sub>～<sub>0</sub>)に供給する。

## 【0051】

バッファ1016は、波形メモリ101からのデータバスをバッファするものである。

## 【0052】

NOTバッファ1017は、入力信号を反転して出力するバッファで、ライト信号がアクティブ“L”の時“H”を出力して、波形メモリ101よりデータが出力されないようにする。

## 【0053】

ORゲート1018は、NOTバッファ1017からの出力が“L”(波形メモリ101からデータがリードされる場合)で、上述したアクセス制御部1002からの信号が“L”“H”になるのを出力するゲートで、この信号の立ち上がり(C P U 2 0 1アクセスジョブが終了したことを意味する)によってラッチ1011においてバッファ1016を経て供給される波形メモリ101からのデータを保持するためのラッチ用信号を供給する。

## 【0054】

選択器1019は、そのS端子に供給される信号に応じて入力される信号を選択出力するセレクタであり、“L”的時ラッチ1006～1009に記憶されているC P U 2 0 1よりセットされたアクセス用アドレス(A<sub>29</sub>～A<sub>0</sub>の30ビット；ラッチ1009の上位2ビットC<sub>1</sub>～C<sub>0</sub>はC P U 2 0 1とのインターフェースのジョブの種類を示す制御情報)とアクセス制御部1002より発生されたリードライト信号RWSが選択され、“H”的時楽音生成部1001より送られてくる押鍵データ[キーON・OFF、キー識別情報(キー番号など)]と音色情報に応答して、波形メモリ101から記憶されている所望の楽音波形データを所望の楽音周波数に応じた速度で読み出すためのアドレスとリード状態にする“H”が選択される。

## 【0055】

10

30

40

50

パルス発生器 P O S 1 0 2 0 は、ポジティブパルスを発生する発生器で、アクセスを C P U 2 0 1 側に許可する信号 E N X の立ち上がりを検出し（これは C P U 2 0 1 アクセスジョブが終了したことを意味する）、正方向のパルスを発生する。

#### 【 0 0 5 6 】

S R フリップフロップ 1 0 2 1 は、R 端子に入力があると出力 Q は “ L ” にされ、S 端子に入力があると出力 Q は “ H ” にされる S R フリップフロップで、その出力は C P U 2 0 1 用アクセスが現在作動中であるかを示す状態フラグとなる。状態フラグが “ H ” の時 10

がビジー状態である。S 端子に L 5 [ アクセス用アドレスの最上位ビットと制御情報をセットする信号；図 6 ( a ) 参照 ] が入力されると、セットされて状態フラグがビジー状態になる。

#### 【 0 0 5 7 】

O R ゲート 1 0 2 2 は、上記 S R フリップフロップ 1 0 2 1 の R 端子に信号を送るゲートで、電源投入時或いは意図的なシステムリセット時に発生されるリセット信号 R S T が発生された時と、パルス発生器 P O S 1 0 2 0 より C P U アクセスジョブ終了を示す信号が送られてきた時、S R フリップフロップ 1 0 2 1 をリセットする信号を供給する。

#### 【 0 0 5 8 】

図 5 は、上述の制御パラメータメモリ 1 1 0 1 と波形メモリ 1 0 1 の格納エリアに格納される内容を示す説明図である。その内容についてはすでに、説明した通りである。

#### 【 0 0 5 9 】

図 6 ( a ) は、上述したように、コントロール信号発生器 1 0 0 3 より発生されるコントロール信号 L<sub>0</sub> ~ L<sub>8</sub> の内容を示している。また ( b ) も既にその詳細は示されているが、さらに説明を付加すると、同図にはコントロール信号 L<sub>5</sub> の時、C P U 2 0 1 から書き込まれる「アクセス用アドレスの最上位と制御情報」の構成の詳細が示されており、上位 2 ビットで、C P U 2 0 1 とのインターフェースのジョブの種類を示している。 20

#### 【 0 0 6 0 】

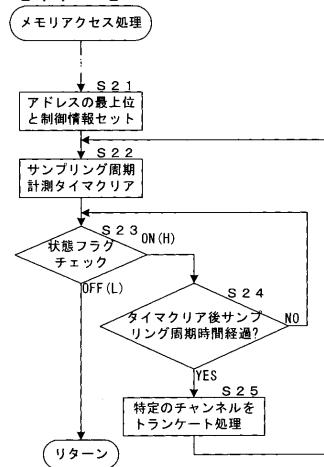

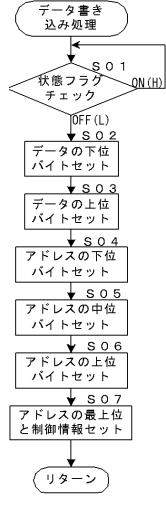

図 7 は、波形メモリ 1 0 1 に対して、C P U 2 0 1 からデータを書き込む、C P U 2 0 1 側の処理ルーチンを示すフロー・チャートである。

#### 【 0 0 6 1 】

最初に状態フラグがチェックされ、以前の C P U アクセスジョブがまだ行われていないかどうかがチェックされる（ステップ S 0 1）。以前の C P U アクセスジョブが終了していない場合（ステップ S 0 1 ; フラグ = O N “ H ” ）、再度フラグチェックがなされる。反対にそのジョブが終了していれば（ステップ S 0 1 ; フラグ = O F F “ L ” ）、次のステップに進む。 30

#### 【 0 0 6 2 】

次に書き込みたいデータの下位バイトをラッチ 1 0 0 4 へセットし（ステップ S 0 2 ）、書き込みたいデータの上位バイトをラッチ 1 0 0 5 へセットする（ステップ S 0 3 ）。

#### 【 0 0 6 3 】

また書き込みたいデータを格納する図 5 ( b ) に示す C P U 用データエリアを指定するアドレスの下位バイトをラッチ 1 0 0 6 へセットし（ステップ S 0 4 ）、同エリアのアドレスの中位バイトをラッチ 1 0 0 7 へセットし（ステップ S 0 5 ）、さらに同エリアのアドレスの上位バイトをラッチ 1 0 0 8 へセットする（ステップ S 0 6 ）。 40

#### 【 0 0 6 4 】

そして同エリアを指定するアドレスの最上位と制御情報をラッチ 1 0 0 9 へセットする（ステップ S 0 6 ）。

#### 【 0 0 6 5 】

C P U 2 0 1 と楽音生成部 1 0 0 1 は非同期で処理が行われるため、アクセス制御部 1 0 0 2 により、楽音生成部 1 0 0 1 から上記空きチャンネル情報が出力されてから、セットされたデータがセットされたアドレスに対応するデータ領域に書き込む処理が行われる。

#### 【 0 0 6 6 】

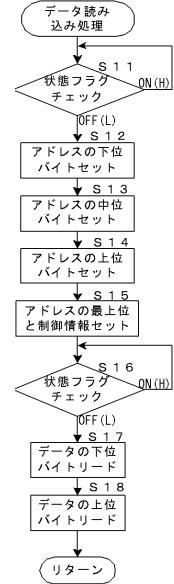

また図8は、C P U 2 0 1が、波形メモリ1 0 1にデータを読み込む処理を行う際のC P U 2 0 1側の処理ルーチンを示すフローチャートである。

#### 【0 0 6 7】

上記と同じく、最初に状態フラグがチェックされ、以前のC P Uアクセスジョブがまだ行われていないかどうかがチェックされる（ステップS 1 1）。以前のC P Uアクセスジョブが終了していない場合（ステップS 1 1；フラグ=ON “H”）、再度フラグチェックがなされる。反対にそのジョブが終了していれば（ステップS 1 1；フラグ=OFF “L”）、次のステップに進む。

#### 【0 0 6 8】

次に読み出したいデータが格納されているC P U用データエリアを指定するアドレスの下位バイトをラッチ1 0 0 6へセットし（ステップS 1 2）、同エリアのアドレスの中位バイトをラッチ1 0 0 7へセットし（ステップS 1 3）、さらに同エリアのアドレスの上位バイトをラッチ1 0 0 8へセットする（ステップS 1 4）。

#### 【0 0 6 9】

そして同エリアを指定するアドレスの最上位と制御情報をラッチ1 0 0 9へセットする（ステップS 1 5）。

#### 【0 0 7 0】

読み出したいアドレス及び制御情報が以上のラッチにセットされてから、インタフェース部Aが空きチャンネルを探して波形メモリ1 0 1の所望のアドレスのデータが読めたか否かが状態フラグでチェックされ（ステップS 1 6）、読み終わっていない場合（ステップS 1 6；フラグ=ON “H”）、再度フラグチェックがなされる。反対にそのジョブが終了していれば（ステップS 1 6；フラグ=OFF “L”）、次のステップに進む。

#### 【0 0 7 1】

そして波形メモリ1 0 1より読み出したいデータの下位バイトをC P U 2 0 1側（ラッチ1 0 0 1）へ読み込み（ステップS 1 7）、同データの上位バイトをC P U 2 0 1側（ラッチ1 0 0 1）へ読み込む（ステップS 1 8）。

#### 【0 0 7 2】

これまでの説明は、楽音生成部1 0 0 1の空きチャンネルを利用し、空きチャンネルのタイミングにC P Uアクセスジョブを実施することで、C P U 2 0 1から波形メモリ1 0 1へのアクセスを行っているが、図9に示されるフローチャートは、全てのチャンネルが発音中で空きチャンネルが存在しない時の処理に関するルーチンを示すものである。同図において、データの書き込み処理及び読み込み処理とも同じであるので、メモリアクセスとして示す。

#### 【0 0 7 3】

このメモリアクセスの最初の方のステップは、図面上省略されているが、アドレスの最上位と制御情報のセットの処理が起点になるので、以下その処理から説明する。

#### 【0 0 7 4】

上述のように、アドレスの最上位と制御情報がセットされる（ステップS 2 1）。

#### 【0 0 7 5】

すると、全てのチャンネルの処理を終了する周期を計測するサンプリング周期計測タイマがクリアされる（ステップS 2 2）。このタイマはサンプリング時間経過（サンプリング周波数4 4 . 1 K H zで約2 3マイクロ秒）を計測する。

#### 【0 0 7 6】

次に状態フラグがチェックされ、以前のC P Uアクセスジョブがまだ行われていないかどうかがチェックされる（ステップS 2 3）。以前のC P Uアクセスジョブが終了していない場合（ステップS 2 3；フラグ=ON “H”）、後述するステップS 2 4に進む。反対にそのジョブが終了していれば（ステップS 2 3；フラグ=OFF “L”）、次のC P Uアクセスジョブを行うようとする。

#### 【0 0 7 7】

ステップS 2 4では、タイマクリア後サンプリング周期時間が経過したか否かがチェック

10

20

30

40

50

クされる。経過していなければ(ステップS24;NO)、ステップS23に戻って状態フラグのチェックが行われる。反対にそのサンプリング周期時間が経過していれば(ステップS24;YES)、空きチャンネルがなくCPUアクセスジョブが完了していないことになるので、次のステップS25に進む。

#### 【0078】

ステップS25では、特定のチャンネルがトランケート処理され、発音が終了せしめられ、空きチャンネル状態が強制的に作られる。このトランケート処理が行われるチャンネルの特定に関しては、例えば、最も先に押されたキーが使用しているチャンネルに対して行われるようにしたり、特定の音域にあるキー(目立たない音域にあるキー)が使用しているチャンネルに対して行われるようにしたり、さらに最も発音レベルの小さなチャンネルに対して行われるようにして実行される。

#### 【0079】

その処理の後、上記ステップS22に戻り、以後の処理を実行する。

#### 【0080】

以上説明した本実施形態構成によれば、上記楽音生成部1001が、楽音信号の生成以外にも空きチャンネル情報をアクセス制御部1002に出力しており、その空きチャンネル情報を基に、該アクセス制御部1002が、空きチャンネルの少なくとも1つを用いて、その空きタイミングの間、外部のCPU201から、上記波形メモリ101へアクセスさせることになるため、該CPU201から波形メモリ101へのアクセスが特定のチャンネルに固定してしまわない状態にして、波形メモリ101へのアクセスを可能になる。すなわち、外部のCPU201から波形メモリ101へアクセスさせる構成の場合にも、そのアクセスについてフレキシブルなチャンネルアサインが可能になる。

#### 【0081】

また空きチャンネルがなくなったタイミングでも、上記楽音生成部1001により、特定のチャンネルをトランケート処理して発音処理を終了させ、その空きチャンネル情報を受信した上記アクセス制御部1002により、特定の空きチャンネルを使用して、外部のCPU201から、上記波形メモリ101へアクセスさせるようにすることもできるようになる。

#### 【0082】

尚、本発明の音源装置は、上述の図示例にのみ限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。

#### 【図面の簡単な説明】

#### 【0083】

【図1】本発明に係る音源装置の構成を備えた電子楽器の回路概略図である。

【図2】波形メモリ101にアクセスする楽音発生部が1つの場合と2つの場合の構成を示す説明図である。

【図3】上記2つの構成における波形データ読み出しタイミングを示すタイムチャートである。

【図4】楽音発生部100と波形メモリ101のCPUインターフェースを中心とした説明図である。

【図5】制御パラメータメモリ1101と波形メモリ101におけるデータ・パラメータの格納状態を示す説明図である。

【図6】コントロール信号発生器1003により発生せられるコントロール信号L<sub>0</sub>～L<sub>8</sub>の状態を示す説明図である。

【図7】波形メモリ101に対してCPU201からデータを書き込むCPU201側の処理ルーチンを示すフローチャートである。

【図8】CPU201が、波形メモリ101にデータを読み込む処理を行う際のCPU201側の処理ルーチンを示すフローチャートである。

【図9】全てのチャンネルが発音中で空きチャンネルが存在しない時の処理に関するルーチンを示すフローチャートである。

10

20

20

30

40

50

## 【符号の説明】

## 【0084】

|                             |             |    |

|-----------------------------|-------------|----|

| 1 0 0 、 1 0 0 a 、 1 0 0 b   | 楽音発生部       |    |

| 1 0 1                       | 波形メモリ       |    |

| 2 0 0                       | システムバス      |    |

| 2 0 1                       | CPU         |    |

| 2 0 2                       | ROM         |    |

| 2 0 3                       | RAM         |    |

| 2 0 4                       | 操作パネル       |    |

| 2 0 4 a                     | パネルスキャン回路   | 10 |

| 2 0 5                       | 鍵盤          |    |

| 2 0 5 a                     | 鍵盤スキャン回路    |    |

| 2 0 6                       | D/A変換回路     |    |

| 2 0 7                       | アナログ信号処理部   |    |

| 2 0 8                       | アンプ         |    |

| 2 0 9                       | スピーカ        |    |

| 1 0 0 0                     | インターフェース部A  |    |

| 1 0 0 1                     | 楽音生成部       |    |

| 1 0 0 2                     | アクセス制御部     |    |

| 1 0 0 3                     | コントロール信号発生器 | 20 |

| 1 0 0 4 ~ 1 0 0 9 、 1 0 1 1 | ラッチ         |    |

| 1 0 1 0 、 1 0 1 2 ~ 1 0 1 6 | バッファ        |    |

| 1 0 1 7                     | NOTバッファ     |    |

| 1 0 1 8 、 1 0 2 2           | ORゲート       |    |

| 1 0 1 9                     | 選択器         |    |

| 1 0 2 0                     | パルス発生器POS   |    |

| 1 0 2 1                     | SRフリップフロップ  |    |

| 1 1 0 0                     | インターフェース部B  |    |

| 1 1 0 1                     | 制御パラメータメモリ  |    |

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

| アドレス | ジョブ内容                 | コントロール信号 |

|------|-----------------------|----------|

| 0    | 書き込み用データの下位バイトセット     | L0       |

| 1    | 書き込み用データの上位バイトセット     | L1       |

| 2    | アクセス用アドレスの下位バイトセット    | L2       |

| 3    | アクセス用アドレスの中位バイトセット    | L3       |

| 4    | アクセス用アドレスの上位バイトセット    | L4       |

| 5    | アクセス用アドレスの最上位と制御情報セット | L5       |

| 6    | 状態フラグをチェック            | L6       |

| 7    | 読み込み用データの下位バイトリード     | L7       |

| 8    | 読み込み用データの上位バイトリード     | L8       |

| 9    |                       |          |

| A    |                       |          |

| B    |                       |          |

| C    |                       |          |

| D    |                       |          |

| E    |                       |          |

| F    |                       |          |

(b) CIC0

0 X : 何にもしない

1 0 : データの波形メモリへの書き込み

1 1 : データを波形メモリより読み込み

【図7】

【図8】

【図9】