# MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA NUMERO     | 102006901386111 |  |

|--------------------|-----------------|--|

| Data Deposito      | 15/02/2006      |  |

| Data Pubblicazione | 15/08/2007      |  |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| G       | 11     | С           |        |             |

#### Titolo

CIRCUITO PER DATI A LATCH SINGOLO IN UN DISPOSITIVO DI MEMORIA NON VOLATILE A CELLE A PIU' LIVELLI.

# RM 2006 A 000074

SIB BI3671R

400.415IT01

Descrizione dell'invenzione industriale dal titolo:

"CIRCUITO PER DATI A LATCH SINGOLO IN UN

DISPOSITIVO DI MEMORIA VOLATILE A CELLE A PIU'

LIVELLI"

a nome di Micron Technology, Inc. (Società dello Stato del Delaware)

di Boise, Idaho (U.S.A.)

#### DESCRIZIONE

### CAMPO TECNICO DELL'INVENZIONE

La presente invenzione fa riferimento in genere a dispositivi di memoria e, in particolare, la presente invenzione fa riferimento a dispositivi di memoria non volatile.

# FONDAMENTO DELL'INVENZIONE

Dispositivi di memoria vengono forniti tipicamente come circuiti integrati interni, di semiconduttore, nel computer o in altri dispositivi elettronici. Vi sono molti tipi differenti di memorie, inclusa la memoria di accesso casuale (RAM), la memoria a sola lettura (ROM), la memoria dinamica ad accesso casuale (DRAM), la memoria

dinamica sincrona ad accesso casuale (SDRAM), e la memoria flash.

di memoria flash sono Dispositivi sviluppati in una sorgente popolare di memoria non volatile per un'ampia gamma di applicazioni elettroniche. memoria Dispositivi di flash impiegano tipicamente una cella di memoria ad un transistore che consente alte densità di memoria, di alta affidabilità e basso consumo energia Impieghi comuni per memorie elettrica. flash includono personal computer, assistenti digitali personali (PDA), videocamere digitali, e telefoni cellulari. Codici di programma e dati di sistema, ad esempio un sistema di base ad ingresso/uscita tipicamente memorizzati in (BIOS) vengono dispositivi di memoria flash per l'utilizzazione in sistemi a personal computer.

Poiché la prestazione e la complessità dei elettronici crescono, cresce pure sistemi requisito di ulteriore memoria in un sistema. Tuttavia, per continuare a ridurre i costi del calcolo delle parti deve sistema, il mantenuto ad un minimo. Questo può realizzato aumentando la densità di memoria di un circuito integrato.

La densità di memoria può essere aumentata impiegando celle a più livelli (MLC). Una memoria a MLC può aumentare la quantità di dati memorizzati in un circuito integrato senza aggiungere ulteriori celle e/oppure aumentare la dimensione del die. Il metodo MLC memorizza due o più bit di dati in ciascuna cella di memoria.

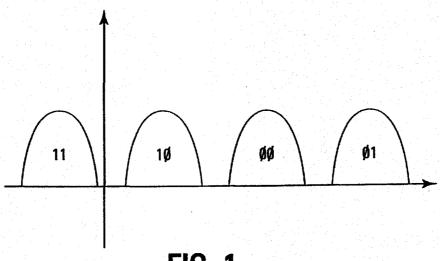

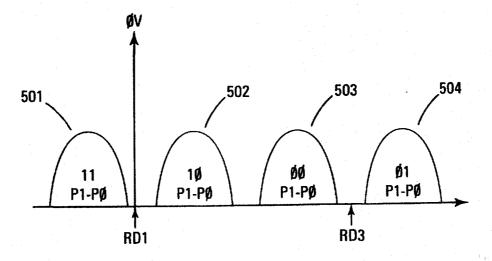

Una cella a più livelli ha più finestre,  $V_t$ , che indicano, ciascuna, uno stato differente, come mostrato in figura 1. Celle a più livelli assumono della natura analogica di il vantaggio una tradizionale cella flash, assegnando una configurazione di bit ad una specifica gamma di tensione memorizzata nella cella. Questa tecnologia consente la memorizzazione di due o più bit per cella, a seconda della quantità di gamme di tensione assegnate alla cella.

Ad esempio, ad una cella possono essere assegnate quattro differenti gamme di tensione di 200 mV per ciascuna gamma. Tipicamente, tra ciascuna gamma, si trova uno spazio morto, o margine, da 0,2 V a 0,4 V. Se la tensione di soglia della cella si trova all'interno della prima gamma, la cella sta memorizzando un 11. Se la tensione di soglia si trova all'interno della seconda gamma, la

cella sta memorizzando 10. Questo continua per tante gamme quante vengono impiegate per la cella. Il MLC richiede un controllo serrato della tensione di soglia per impiegare più livelli di soglia per cella.

Un parametro critico dei circuiti integrati a memoria flash MLC è il calcolo dei transistori dell'amplificatore di rilevazione che impiegato per leggere i valori programmati nelle celle. L'alto parallelismo di dispositivi a memoria flash richiede che venga impiegato almeno registro latch di dati dello stesso amplificatore di rilevazione per ciascuna fila di bit della schiera che sta venendo letta in estrazione. Questo problema è peggiore per dispositivi MLC, momento che è necessario che i circuiti manipolino due bit da ciascuna fila di bit. Ciò aumenta notevolmente il numero di transistori richiesti per operazioni di lettura-modifica-scrittura.

A causa della concorrenza intensa e del desiderio del consumatore di una maggiore vita delle batterie in dispositivi elettronici, i produttori devono costantemente trovare modi per ridurre la quantità di componenti nei dispositivi, mantenendo nel frattempo l'affidabilità. Per i

motivi sopra asseriti, e per altri motivi asseriti appresso che diventeranno evidenti a coloro che sono esperti nel ramo dopo aver letto e compreso la presente descrizione, c'è la necessità, nel ramo, di ridurre la quantità di transistori richiesti in registri latch di dati di amplificatore di rilevazione in dispositivi a memoria MLC.

#### SOMMARIO

I problemi sopra nominati con memorie flash ed altri problemi vengono rivolti dalla presente invenzione e verranno compresi leggendo e studiando la descrizione che segue.

La presente invenzione comprende un circuito latch di memoria. Il circuito comprende un registro latch avente un nodo ed un nodo invertito. Un primo transistore di controllo è accoppiato tra l'uscita del circuito ed il nodo. Un secondo transistore di controllo è accoppiato tra l'uscita e il nodo invertito. Un transistore di ripristino accoppiato al nodo invertito. I transistori controllo accoppiando in modo selettivo il nodo oppure nodo invertito all'uscita, in risposta a segnali di controllo sui gate di transistore. Il ripristino trascina transistore di il invertito al potenziale di massa, in risposta ad un segnale di ripristino.

include 10 scrivere i dati metodo desiderati in uno tra il bit meno significativo oppure il bit più significativo di una cella da seconda operazione di programmare. Una programmazione programma dati di consolidamento per dati bit della cella. rimanenti Τ consolidamento regolano il livello di soglia della cella alla tensione richiesta dai dati desiderati.

Ulteriori forme di realizzazione dell'invenzione includono metodi ed una apparecchiatura per variare l'ambito.

#### BREVE DESCRIZIONE DEI DISEGNI

La figura 1 mostra un diagramma delle distribuzioni delle tensioni di soglia di una memoria a celle a più livelli.

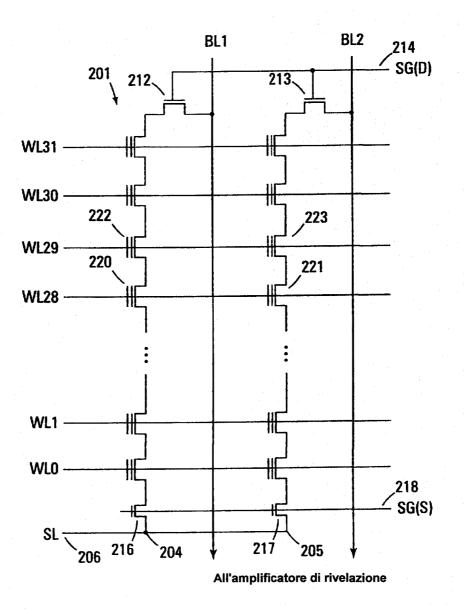

La figura 2 mostra un diagramma semplificato di una forma di realizzazione di una schiera di memoria flash NAND.

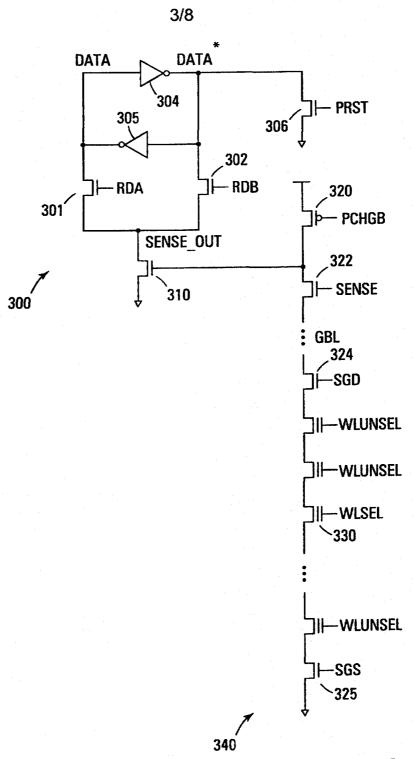

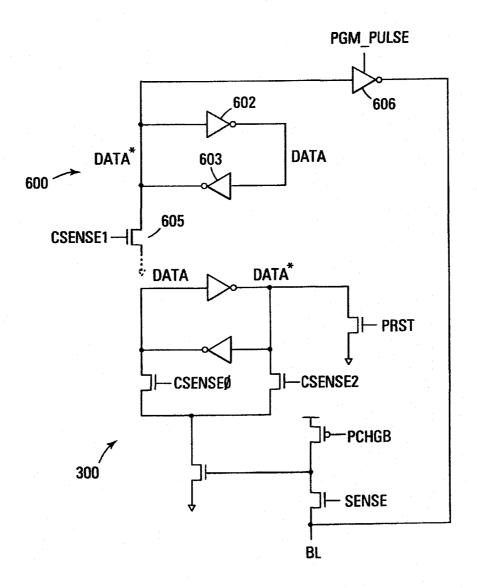

La figura 3 mostra uno schema di una forma di realizzazione di un registro latch di dati della presente invenzione.

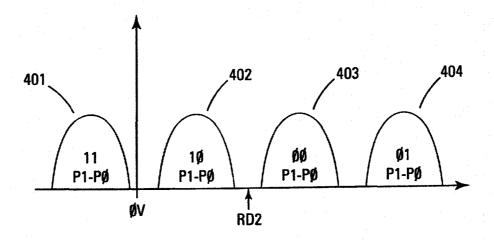

La figura 4 mostra uno schema della distribuzione delle tensioni di soglia secondo una operazione di lettura di pagina della presente

invenzione.

La figura 5 mostra uno schema della distribuzione delle tensioni di soglia secondo una operazione di lettura di pagina zero della presente invenzione.

La figura 6 mostra uno schema di una forma di realizzazione di due registri latch di dati secondo l'operazione di programmazione della presente invenzione.

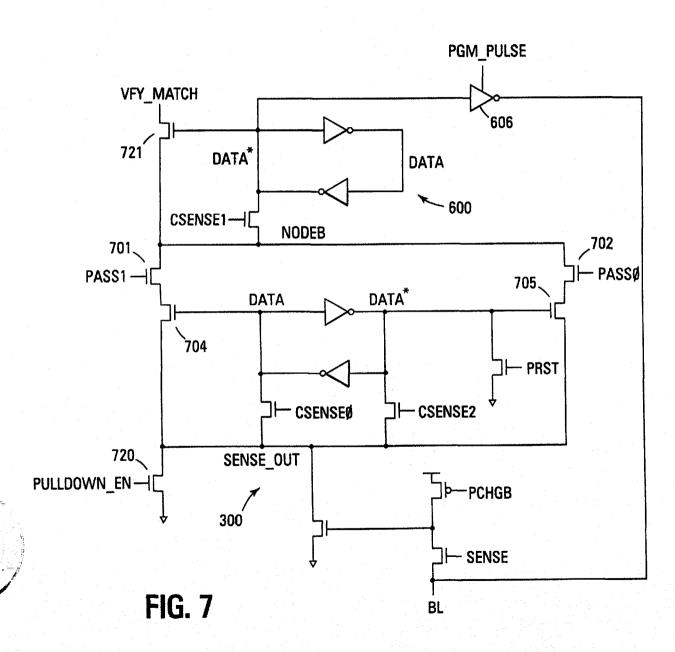

La figura 7 mostra uno schema dei circuiti latch di dati e della circuiteria di supporto della presente invenzione.

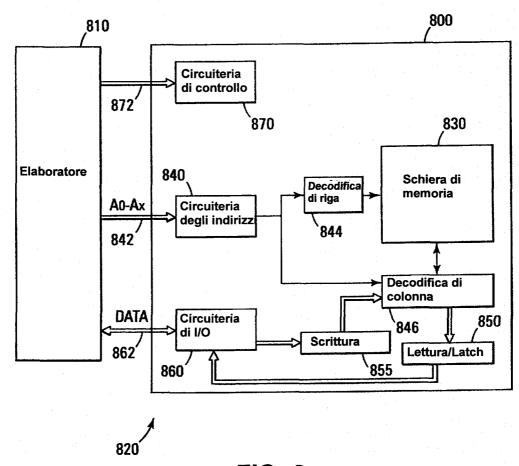

La figura 8 mostra uno schema a blocchi di una forma di realizzazione di un sistema a memoria della presente invenzione.

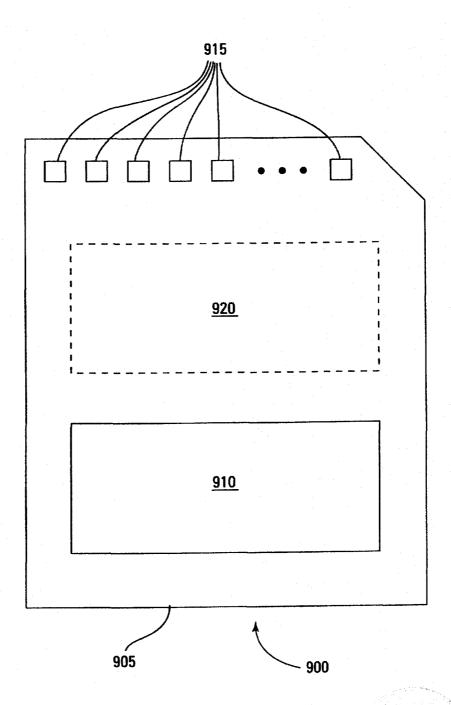

La figura 9 mostra uno schema a blocchi di una forma di realizzazione di un modulo di memoria della presente invenzione.

# DESCRIZIONE DETTAGLIATA

Nella seguente descrizione dettagliata dell'invenzione, si fa riferimento ai disegni annessi che ne formano una parte, ed in cui vengono mostrate, a titolo di illustrazione, forme di realizzazione specifiche in cui l'invenzione può essere realizzata. Nei disegni, numeri simili

descrivono sostanzialmente componenti simili ogni parte delle svariate viste. Queste forme di realizzazione vengono descritte in dettaglio sufficiente per consentire a coloro che esperti nel ramo di realizzare l'invenzione. impiegate altre forme di Possono essere effettuate possono essere realizzazione, е variazioni strutturali, logiche ed elettriche senza allontanarsi dall'ambito della presente invenzione. La seguente descrizione dettagliata, perciò, non deve essere assunta in senso limitativo, e l'ambito della presente invenzione viene definito soltanto relativi dalle rivendicazioni annesse е dai equivalenti.

La figura 2 illustra un diagramma semplificato di una forma di realizzazione per una schiera di memoria flash NAND a semiconduttore della presente invenzione. Questa schiera di memoria è soltanto per fini di illustrazione, dal momento che la presente invenzione non è limitata a ciascuna tecnologia o architettura di memorie non volatili.

La schiera di memoria di figura 2, per fini di chiarezza, non presenta tutti gli elementi tipicamente richiesti in una schiera di memoria. Ad esempio, vengono mostrate soltanto due file di bit

(BL1 e BL2) quando il numero richiesto di file di bit dipende in effetti dalla densità di memoria e dalla architettura di chip. Le file di bit vengono in seguito indicate come (BL1-BLN). Le file di bit (BL1-BLN) sono infine accoppiate ad amplificatori di rilevazione (non mostrati) che rivelano lo stato di ciascuna cella.

La schiera è formata da una schiera di celle a gate flottante 201 disposte in stringhe serie 204, 205. Ciascuna delle celle 201 a gate flottante è accoppiata da drain a source in ciascuna catena serie 204, 205. Una fila di parole (WLO-WL31) che si estende attraverso più stringhe serie 204, 205, è accoppiata alle porte di controllo di ciascuna cella a gate flottante in una riga, per controllare il In forma di funzionamento. una suo realizzazione, una schiera è costituita da 32 file di parole. Tuttavia, la presente invenzione non è limitata a ciascuna quantità di file di parole.

Durante il funzionamento, le file di parole (WLO-WL31) selezionano le singole celle di memoria a gate flottante nella catena serie 204, 205 su cui scrivere oppure da cui leggere, e agiscono sulle rimanenti celle di memoria a gate flottante in ciascuna stringa serie 204, 205, in un modo

passante. Ciascuna stringa serie 204, 205 di celle di memoria a gate flottante è accoppiata ad una fila di source 206 mediante un gate 216, 217 di selezione di source, e ad un'unica fila di bit (BL1-BLN), mediante un gate 212, 213 di selezione di drain. I gate 216, 217 di selezione di source vengono controllati mediante una fila di controllo di gate di selezione di source SG(S) 218 accoppiata ai loro gate di controllo. I gate 212, 213 di selezione di drain vengono controllati mediante una fila di controllo di gate di selezione di drain vengono controllati mediante una fila di controllo di gate di selezione di drain SG(D) 214.

Nella forma di realizzazione di figura 2, WLO si trova nella parte inferiore della pagina, e WL31 si trova nella sommità della pagina. Tuttavia, queste etichette sono soltanto per fini di illustrazione, dal momento che WLO può pure iniziare alla sommità della pagina, con il numero delle file di parole che aumenta verso il fondo della pagina.

Ciascuna cella può essere programmata come un unico bit per cella (cioè, una cella a livello singolo-SLC) o più bit per cella (cioè, cella a più livelli-MLC). Ciascuna tensione di soglia di cella ( $V_t$ ) determina i dati che sono memorizzati nella

cella. Ad esempio, in un unico bit per cella, un  $V_t$  di 0,5 V potrebbe indicare una cella programmata (cioè, stato logico 0), mentre un  $V_t$  di

-0,5 V potrebbe indicare una cella cancellata (cioè, stato logico 1). Il funzionamento delle celle a più livelli è stato discusso in precedenza.

Le forme di realizzazione della presente invenzione non sono limitate a due bit per cella. Talune forme di realizzazione possono memorizzare più di due bit per cella, a seconda della quantità delle differenti gamme di tensione che possono essere differenziate sulla cella.

tipica operazione dí Durante una programmazione di tecnica antecedente, la fila di parole selezionata per la cella di memoria flash da programmare viene polarizzata con una serie di impulsi di programmazione che iniziano ad una esempio, 20 V), con ciascuna tensione (ad successiva tensione impulsiva che aumenta in modo incrementale fino a che la cella non programmata oppure fino a che non si raggiunge una massima tensione di programmazione. File di parole non selezionate vengono polarizzate a V<sub>pass</sub> esempio, 10 V). File selezionate di bit vengono polarizzate a 0 V, mentre file non selezionate di

bit vengono polarizzate a  $V_{\text{cc}}$ , per impedire l'operazione di programmazione per quelle stringhe serie.

Viene quindi eseguita una operazione di verifica (lettura) con una tensione della fila di parole selezionata di 0 V, per determinare se il gate flottante si trova nella corretta tensione (ad esempio, 0,5 V). In una forma di realizzazione, le tensioni delle file di parole non selezionate possono essere qualsiasi tensione uguale al oppure maggiore del potenziale di massa. Le file di bit vengono precaricate a  $V_{\rm cc}$ , mentre vengono selezionati il SG(D) ed il SG(S). Ciascuna delle celle di memoria viene programmata/verificata in un modo sostanzialmente simile.

La figura 3 illustra uno schema di un circuito latch di dati 300 della presente invenzione, accoppiato ad una parte di una stringa serie di celle di memoria 340 di una schiera di memoria flash NAND.

Il circuito latch 300 è formato da due invertitori 304, 305 che sono accoppiati ad un nodo DATA e ad un nodo DATA\* che è l'inverso del noto DATA. Tre transistori di controllo 301, 302 e 306 sono accoppiati agli invertitori 304, 305 per

controllare l'operazione del circuito latch 300. Due dei transistori 301, 302 controllano quale lato (cioè, DATA oppure DATA\*) del circuito latch 304, 305, in risposta a segnali di controllo RDA e RDB attivi alti, è accoppiato al nodo SENSE\_OUT. L'altro transistore 306 è un transistore di ripristino che ha un segnale PRST attivo alto accoppiato al gate per controllare quanto il transistore viene attivato per vincolare a massa l'uscita DATA\* del registro latch.

La stringa serie di celle di memoria 340, in una forma di realizzazione, è formata da trentadue celle di memoria flash a gate flottante, come illustrato in figura 2. Ciascuna delle celle di memoria in righe non selezionate che vengono polarizzate dalla tensione "WLUNSEL" che è accoppiata a ciascuna delle file di parole "non selezionate". La fila di parole selezionata viene polarizzata dalla tensione "WLSEL". Forme di realizzazione alternative possono impiegare altre quantità di celle di memoria in ciascuna stringa serie, nonché una differente tecnologia di celle di memoria non volatile.

Il transistore di selezione gate source 325 ed il transistore di selezione gate drain 324 sono su

lati contrapposti della stringa 340. La stringa serie 340 è quindi accoppiata alla fila globale di bit GBL che è accoppiata ad un transistore di 322 che controlla 1'accesso controllo NMOS all'amplificatore di rilevazione mediante stringa 340. Il gate del transistore di controllo 322 è polarizzato da una tensione "SENSE" che controlla l'operazione del transistore 322.

Un transistore PMOS di precarica 320 accoppia il transistore di controllo NMOS 322 a  $V_{\rm cc}$  per prevaricare la fila di bit durante una operazione di lettura. Un livello logico basso sul gate del transistore PMOS 320 attiva il transistore.

Il transistore 310 di uscita dell'amplificatore di rilevazione ha il suo gate accoppiato tra il transistore NMOS 322 ed il transistore PMOS 320. Un alto logico sul gate di questo transistore 310 trascina a massa il circuito latch 300, come verrà descritto in seguito. Un basso logico sul gate fa sì che il circuito latch 300 veda uno stato ad alta impedenza.

L'operazione del circuito latch 300 di figura 3 viene discussa con riferimento alle distribuzioni delle tensioni di soglia illustrate nelle figure 4 e 5. Ciascuna distribuzione, 401-404 della figura 4

e 501-504 della figura 5 rappresenta uno stato differente di MLC. I dati MLC memorizzati in ciascuna cella rappresentano due pagine di dati, pagina 1 e pagina 0 (cioè, P1-P0).

La figura 4 illustra le distribuzioni delle tensioni di soglia 401-404 per leggere la pagina 1 (P1) delle celle di memoria. Lo stato più negativo 401 è lo stato logico "11". Lo stato successivo 402 è lo stato logico "10". Lo stato che segue 403 è lo stato logico "00". Lo stato più positivo 404 è lo stato logico "01". La tensione di lettura, RD2, che viene applicata alla fila selezionata di parole come tensione "WLSEL" viene illustrata tra i due stati di mezzo 402, 403.

La figura 5 illustra le distribuzioni delle tensioni di soglia 501-504 per leggere la pagina 0 (PO) delle celle di memoria. Lo stato più negativo 501 è lo stato logico "11". Il successivo stato più positivo 502 è lo stato logico "10". Lo stato seguente 503 è lo stato logico "00". Lo stato più positivo 504 è lo stato logico "01". Le tensioni di lettura, RD1 e RD3, vengono applicate alla linea di parole selezionata come tensione "WLSEL". La tensione di lettura 1 (cioè, RD1) si trova tra gli stati primo e secondo 501, 502. La tensione di

lettura 3 (cioè, RD3) si trova tra gli ultimi due stati 503, 504.

Con riferimento alle figure 3 e 4, il primo stato (cioè, 11 logico) 401 viene letto dalla procedura che segue. In un primo istante, t<sub>0</sub>, il segnale PRST è un 1 logico, e RDA è uno 0 logico. Questo ha come conseguenza che il segnale DATA\* del circuito latch è uno 0 logico, e che DATA viene caricato con un 1 logico.

Nell'istante  $t_1$ , il segnale PRST è uno 0 logico, per disattivare il transistore 306. Il transistore 330 della cella di memoria è accoppiato alla polarizzazione WLSEL della fila di parole selezionata che si trova ora alla tensione di lettura RD2, come illustrato in figura 4. quindi di rilevazione eseque L'amplificatore un'operazione di rilevazione, come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA si trova ad un 1 logico per attivare il suo rispettivo transistore 301, e RDB viene trattenuto in uno 0 logico per mantenere disattivato il transistore 302, collegando così il nodo DATA del circuito latch al nodo SENSE OUT che adesso è flottante. Questo ha come conseguenza che viene letto l'1 logico (cioè, DATA) di pagina 1 del primo stato

401.

Il secondo stato (cioè, 10 logico) 402 viene letto mediante la seguente procedura. In un primo istante,  $t_0$ , il segnale PRST è un 1 logico e RDA è uno 0 logico. Questo ha come conseguenza che il segnale DATA\* del circuito latch si trova in uno 0 logico, e DATA viene caricato con un 1 logico.

All'istante  $t_1$ , il segnale PRST si trova ad uno 0 logico per disattivare il transistore 306. Il transistore 330 della cella di memoria è accoppiato alla polarizzazione WLSEL della fila di parole selezionata che è adesso alla tensione di lettura RD2, come illustrato in figura 4. L'amplificatore di rilevazione eseque quindi una operazione di rilevazione, come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA si trova ad un 1 logico, per attivare il suo rispettivo transistore 301, e RDB viene trattenuto ad uno 0 logico, per disattivato mantenere il transistore collegando così il modo DATA del circuito latch al nodo SENSE OUT che è adesso flottante. Questo ha come conseguenza che viene letto l'1 logico (cioè, DATA) di pagina 1 del secondo stato 402.

Il terzo stato (cioè, 00 logico) 403 viene letto dalla procedura seguente. In un primo

istante,  $t_0$ , il segnale PRST è un 1 logico e RDA è uno 0 logico. Questo ha come conseguenza che il segnale DATA\* del circuito latch è uno 0 logico, e DATA viene caricato con 1 logico.

All'istante t<sub>1</sub>, il segnale PRST è uno 0 logico per disattivare il transistore 306. Il transistore della cella di memoria è accoppiato alla fila WLSEL della di parole polarizzazione selezionata che si trova adesso alla tensione di illustrato in figura lettura RD2, come L'amplificatore di rilevazione esegue quindi una operazione di rilevazione, come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA è un 1 logico per attivare il suo rispettivo transistore 301, e RDB viene mantenuto ad uno 0 logico per 302 disattivato, mantenere il transistore collegando così il nodo DATA del registro latch al nodo SENSE\_OUT che si trova adesso ad uno 0 logico. Questo ha come consequenza che viene letto lo 0 logico (cioè, DATA) di pagina 1 del terzo stato 403.

Il quarto stato (cioè, 01 logico) 404 viene letto mediante la seguente procedura. In un primo istante,  $t_0$ , il segnale PRST è un 1 logico, e RDA è uno 0 logico. Questo ha come conseguenza che il

segnale DATA\* del circuito latch è uno 0 logico, e DATA viene caricato con un 1 logico.

All'istante  $t_1$ , il segnale PRST si trova ad uno 0 logico per disattivare il transistore 306. Il transistore 330 della cella di memoria è accoppiato alla polarizzazione WLSEL della linea di parole selezionata che si trova adesso alla tensione di lettura RD2, come illustrato in figura L'amplificatore di rilevazione esegue quindi una operazione di rilevazione come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA si trova ad logico per attivare il suo rispettivo transistore 301, e RDB viene mantenuto ad uno 0 logico per mantenere disattivato il transistore 302, collegando così il nodo DATA del registro latch al nodo SENSE OUT che si trova adesso ad uno O logico. Questo ha come conseguenza che viene letto lo 0 logico (cioè, DATA) di pagina 1 del quarto stato 404

Con riferimento alle figure 3 e 5, il primo stato 501 di pagina 0 (cioè, P0) viene letto mediante la seguente procedura. In un primo istante,  $t_0$ , il segnale PRST è un 1 logico e RDA è uno 0 logico. Questo ha come conseguenza che il segnale DATA\* del circuito latch è uno 0 logico, e

DATA viene caricato con un 1 logico.

All'istante  $t_1$ , il segnale PRST si trova ad uno 0 logico per disattivare il transistore 306. Il transistore 330 della cella di memoria è accoppiato alla polarizzazione WLSEL della fila di parole selezionata che si trova adesso alla tensione di RD1, come illustrato in figura lettura L'amplificatore di rilevazione esegui quindi una operazione di rilevazione come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA si trova ad logico per attivare il suo rispettivo 1 un transistore 301, e RDB viene mantenuto ad uno 0 logico, per mantenere disattivato il transistore 302, collegando il nodo DATA del registro latch al nodo SENSE OUT che è adesso flottante. Questo ha come consequenza che il nodo DATA è un 1 logico.

Nell'istante t<sub>2</sub>, il segnale PRST si trova in uno 0 logico per disattivare il transistore 306, Il transistore 330 della cella di memoria è accoppiato alla polarizzazione WLSEL della fila di parole selezionata che si trova adesso alla tensione di lettura RD3, come illustrato in figura 5. L'amplificatore di rilevazione esegue quindi una operazione di rilevazione come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA si trova ad

uno 0 logico, RDB si trova ad un 1 logico per attivare il suo rispettivo transistore 302, collegando così il nodo DATA\* del registro latch formato dagli invertitori 304, 305 al nodo SENSE\_OUT che è adesso flottante. Questo ha come conseguenza che viene letto l'1 logico (cioè, DATA) di pagina 0 del primo stato 501.

Il secondo stato (cioè, 10 logico) 502 viene letto mediante la seguente procedura. In un primo istante,  $t_0$ , il segnale PRST si trova ad un 1 logico e RDA si trova ad uno 0 logico. QUesto ha come conseguenza che il segnale DATA\* del circuito latch si trova in uno 0 logico, e DATA viene caricato con un 1 logico.

Nell'istante t<sub>1</sub>, il segnale PRST si trova ad uno 0 logico per disattivare il transistore 306. Il transistore 330 della cella di memoria è accoppiato alla polarizzazione WLSEL della fila di parole selezionata che si trova adesso alla tensione di lettura RD1, come illustrato in figura L'amplificatore di rilevazione esegue quindi una operazione di reazione come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA si trova in logico per attivare il suo rispettivo transistore 301, e RDB viene mantenuto ad uno 0 logico per mantenere disattivato il transistore 302, collegando così il modo DATA del registro latch al nodo SENSE\_OUT che si trova adesso ad uno 0 logico. Questo ha come conseguenza che il nodo DATA è uno 0 logico.

Nell'istante t2, il segnale PRST è uno 0 logico per disattivare il transistore 306. transistore 330 della cella di memoria è accoppiato alla polarizzazione WLSEL della fila di parole selezionata che si trova adesso alla tensione di 5. lettura RD3, come illustrato in figura L'amplificatore di rilevazione esegue quindi una operazione di rilevazione, come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA è uno 0 logico, RDB è un 1 logico per attivare il suo rispettivo transistore 302, collegando così il nodo DATA\* del registro latch formato dagli invertitori 304, 305 al nodo SENSE OUT che è adesso flottante. Questo ha come conseguenza che viene letto lo 0 logico (cioè, DATA) di pagina 0 del secondo stato 502.

Il terzo stato (cioè, 00 logico) 503 viene letto mediante la seguente procedura. In un primo istante,  $t_0$ , il segnale PRST è un 1 logico e RDA è uno 0 logico. Questo ha come conseguenza che il

segnale DATA\* del circuito latch è uno 0 logico, e DATA è caricato con un 1 logico.

All'istante t<sub>1</sub>, il segnale PRST è uno 0 logico per disattivare il transistore 306. Il transistore della cella di memoria è accoppiato alla polarizzazione WLSEL della fila di parole selezionata che si trova adesso alla tensione di illustrato in figura 5. lettura RD1. come L'amplificatore di rilevazione esegue quindi una operazione di rilevazione come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA è un 1 logico per attivare il suo rispettivo transistore 301, e RDB viene mantenuto ad uno zero logico per mantenere disattivato il transistore 302. collegando così il nodo DATA del registro latch al nodo SENSE OUT che si trova adesso ad uno 0 logico. Questo ha come consequenza che il nodo DATA è uno 0 logico.

All'istante  $t_2$ , il segnale PRST è uno 0 logico per disattivare il transistore 306. Il transistore 330 della cella di memoria è accoppiato alla polarizzazione WLSEL della fila di parole selezionata che si trova adesso alla tensione di lettura RD3, come illustrato in figura 5. L'amplificatore di rilevazione esegue quindi una

operazione di rilevazione, come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA è uno 0 logico, RDB è 1 logico per attivare il suo rispettivo transistore 302, collegando così il nodo DATA\* del registro latch formato dagli invertitori 304, 305 al nodo SENSE\_OUT che è adesso flottante. Questo ha come conseguenza che viene letto lo 0 logico (cioè, DATA) di pagina 0 del terzo stato 503.

Il quarto stato (cioè, 01 logico) 504 viene letto mediante la seguente procedura. In un primo istante,  $t_0$ , il segnale PRST è un 1 logico e RDA è uno 0 logico. Questo ha come conseguenza che il segnale DATA\* del circuito latch è uno 0 logico, e DATA è caricato con un 1 logico.

All'istante  $t_1$ , il segnale PRST è uno 0 logico per disattivare il transistore 306. Il transistore 330 della cella di memoria è accoppiato alla fila polarizzazione WLSEL della di selezionata che si trova adesso alla tensione di lettura RD1, come illustrato in figura 5. L'amplificatore di rilevazione esegue quindi una operazione di rilevazione, come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA è un 1 logico per attivare il suo rispettivo transistore 301, e RDB viene mantenuto ad uno 0 logico per mantenere disattivato il transistore 302, collegando così il nodo DATA del registro latch al nodo SENSE\_OUT che si trova adesso in uno 0 logico. Questo ha come conseguenza che il nodo DATA è uno 0 logico.

All'istante t2, il segnale PRST è uno 0 logico per disattivare il transistore 306. Il transistore 330 della cella di memoria è accoppiato alla fila polarizzazione WLSEL della di parole selezionata che si trova adesso alla tensione di illustrato in figura 5. lettura RD3, come L'amplificatore di rilevazione eseque quindi una operazione di rilevazione, come è ben noto nel ramo. Dopo l'operazione di rilevazione, RDA è uno 0 logico, RDB un 1 logico per attivare il rispettivo transistore 302, collegando così il nodo DATA\* del registro latch formato dagli invertitori 304, 305 al nodo SENSE OUT che si trova adesso in uno 0 logico. Questo ha come conseguenza che viene letto l'1 logico (cioè, DATA) di pagina 0 del quarto stato 504.

Viene impiegata una tecnica di letturamodifica-scrittura per generare la tensione di

inibizione dell'operazione di programma di una

cella NAND quando il suo  $V_t$  passa il livello di verifica. Una forma di realizzazione per un circuito che realizza ciò viene illustrata in figura 6.

Il circuito è formato da un registro latch 600 costituito da due invertitori 602, 603 con un di controllo 605. Il gate del transistore transistore 605 è collegato ad un segnale di controllo "CSENSE1" che va alto quando una cella è stata verificata come programmata durante operazione di verifica. Il drain del transistore 605 viene mostrato accoppiato alla massa di circuito nelle linee punteggiate. Le linee punteggiate rappresentano l'equivalente funzionale del circuito a cui è accoppiato il transistore 605, come illustrato in seguito con riferimento alla figura 7.

La tecnica di lettura-modifica-scrittura coinvolge il memorizzare i dati da programmare nel registro latch 600 come DATA durante l'impulso di programma e quindi modificarli quando il  $V_{\rm t}$  della cella è diventato più alto di un valore di verifica predeterminato. In altri termini, la cella è stata programmata con successo. Ad esempio, ipotizzando che DATA da programmare sia uno 0 logico e che,

mentre il segnale "CSENSE1" è basso, il transistore 605 viene disattivato e l'uscita del registro latch attraverso il gate 606 di invertitore è uno 0 logico. Il gate 606 di invertitore viene abilitato ogni qual volta l'impulso di programma (cioè, pgm\_pulse) va alto. Durante questo tempo, il segnale logico basso viene applicato alla fila di bit, consentendo così alle celle sulla fila di parole selezionata di essere programmatae.

Quando CSENSE1 va alto dopo che è passata l'operazione di verifica, DATA\* viene vincolato ad uno 0 logico attraverso il transistore 605, e l'uscita della porta 606 di invertitore è un logico alto. Questa polarizzazione  $V_{\rm cc}$  viene applicata alla fila di bit, inibendo perciò l'operazione di programma.

La figura 7 illustra i registri latch di dati e la circuiteria di supporto della presente invenzione. Questo circuito include il primo circuito latch 300 di dati come illustrato in figura 3, ed il secondo circuito latch 600 di dati come illustrato in figura 6. Vengono pure mostrati i transistori di passaggio 701, 702 e la circuiteria di supporto 704, 705 che unisce insieme i registri latch 300, 600. Un transistore di pull-

up 721 è accoppiato ad un segnale VFY\_MATCH che un logico alto quando i dati programmati sono stati verificati. Un transistore di pull-down 720 è accoppiato al primo circuito latch 300 con un segnale "PULLDOWN\_EN" accoppiato al gate che va alto per attivare il transistore 720.

Dopo l'operazione di lettura-modificascrittura descritta in precedenza, VFY\_MATCH viene

precaricato o sottoposto a pull-up ad un livello

logico 1. Quindi, se tutti i bit da programmare

sono stati modificati da 0 a 1, il nodo DATA\* si

troverà in uno 0 logico, e la fila in comune VFYMATCH si troverà in un 1 logico. Se alcuni dei bit

da programmare si trovano ancora in uno 0 logico

dopo l'operazione di lettura-modificaa-scrittura,

può essere estratta l'informazione riguardo i bit

mancanti da verificare.

Per estrarre l'informazione di bit, PASS1 viene impostato alto, PASS0 viene impostato basso, e PULLDOWN\_EN viene impostato in uno stato alto. La fila VFY\_MATCH viene sottoposta a pull-down se una qualsiasi di pagina 0 (P0) non ha passato l'operazione di verifica durante una programmazione di PO.

Rendendo PASS1=0, PASS0=1, e PULLDOWN\_EN=1, la

fila VFY\_MATCH verrà sottoposta a pull down se una qualsiasi di P1, avente P0=0, non ha superato l'operazione di verifica. Rendendo PASS1=1, PASS0=1, e PULLDOWN\_EN=1, la fila VFY\_MATCH viene sottoposta a pull down se uno qualsiasi dei dati da programmare non ha superato l'operazione di verifica.

Per verificare la programmazione di PO, viene preimpostato il primo circuito latch 300 in modo tale che il nodo DATA sia un 1 logico. PO = 0 viene caricato nel secondo circuito latch 600 al nodo DATA. Una tensione di verifica, VFY1, viene applicata a WLSEL e PASS1 = 1. In una forma di realizzazione, la tensione VFY1 è localizzata tra i primi due stati di MLC. Viene quindi eseguita una operazione di rilevazione dall'amplificatore di elevazione, come è ben nodo nella tecnica. Dopo l'operazione di rilevazione, CSENSE1=1.

Se la tensione di soglia rilevata è maggiore di oppure uguale a VFY1, SENSE\_OUT=0, NODEB=0, e P0 diventa un 1 logico. La programmazione viene impedita, come spiegato in precedenza, per il successivo impulso di programmazione.

Se la tensione di soglia rilevata è minore di VFY1, SENSE\_OUT si trova in uno stato ad alta

impedenza e P0 rimane ad una logica bassa. L'operazione di programmazione viene quindi eseguita di nuovo.

Per verificare la programmazione di P1 con tensione VFY3 quando P0 = 1, P0 viene letto e memorizzato nel primo registro latch 300 al nodo DATA durante l'inizio dell'operazione di programmazione. P1=0 viene caricato nel secondo registro latch 600 al nodo DATA. Viene impiegata una tensione di verifica, VFY3, per polarizzare la fila di parole selezionata come WLSEL. VFY3, in una forma di realizzazione, è una tensione localizzata tra gli stati terzo e quarto di MLC. VFY2, im una forma di realizzazione, è una tensione localizzata tra gli stati secondo e terzo di MLC.

I gate dei transistori di passaggio 701, 702 vengono polarizzati come PASS1=1 e PASS0=0. Viene quindi eseguita una operazione di rilevazione. Dopo che l'amplificatore di rilevazione ha realizzato l'operazione di rilevazione, CSENSE1=1. Se la tensione di soglia, V<sub>t</sub>, è maggiore di oppure uguale a VFY3, il nodo SENSE\_OUT = 0 e NODEB=0. PO diventa un 1 logico, e l'operazione di programmazione viene impedita per il successivo impulso di programmazione soltanto per le celle aventi PO=1.

Se  $V_t$  è minore di VFY3, il nodo SENSE\_OUT è alta impedenza e P0 rimane come uno 0 logico. L'operazione di programmazione viene eseguita di nuovo.

Per verificare la programmazione di P1 con VFY2 quando P0=0, P0 viene letto e caricato nel primo circuito latch al nodo DATA durante l'inizio dell'operazione di programmazione. Il nodo DATA del secondo registro latch 600 viene caricato con P1=0. Una tensione di verifica, VFY2, polarizza la fila di parole selezionata come tensione WLSEL. PASS0=1 e PASS1=0. Viene quindi eseguita una operazione di rilevazione dall'amplificatore di rilevazione. Dopo l'operazione di rilevazione, CSENSE1=1.

Se la tensione di soglia rilevata,  $V_t$ , è maggiore di oppure uguale a VFY3, il nodo SENSE\_OUT è uno 0 logico, NODEB=0, e P0 diventa un 1 logico. La successiva operazione di programmazione viene impedita soltanto per le celle aventi P1=0.

Se la tensione rilevata è minore di VFY3, il nodo SENSE\_OUT si trova in uno stato di alta impedenza. In questo stato, P0 rimane come uno 0 logico, e l'operazione di programmazione viene eseguita di nuovo.

La figura 8 illustra uno schema a blocchi

funzionale di un dispositivo di memoria 800 che può incorporare la schiera di memoria flash e le forme di realizzazione del metodo di programmazione della presente invenzione. Il dispositivo di memoria 800 è accoppiato ad un elaboratore 810 in grado di sequire il pilotaggio software della presente invenzione per scrivere dati SLC in un dispositivo MLC. 810 L'elaboratore può essere un microprocessore oppure qualsiasi altro tipo circuiteria di controllo. Il dispositivo di memoria 800 e l'elaboratore 810 formano parte di un sistema di memoria 820. Il dispositivo di memoria 800 è focalizzarsi stato semplificato per sulle caratteristiche della memoria che sono utili per la compressione della presente invenzione.

Il dispositivo di memoria include una schiera di celle di memoria flash 830, come descritto sopra con riferimento alla figura 8. La schiera di memoria 830 è disposta in banchi di righe e colonne. I gate di controllo di ciascuna riga delle celle di memoria sono accoppiati con una fila di parole mentre i collegamenti drain e source delle celle di memoria sono accoppiati a file di bit. Come è ben nodo nel ramo, i collegamenti delle celle alle file di bit determinano se la schiera è

una architettura NAND, una architettura AND, oppure una architettuta NOR.

Viene fornito un circuito 840 del buffer di indirizzi per agganciare i segnali di indirizzo forniti sui collegamenti di immissione indirizzi A0-Ax 842. Segnali di indirizzo vengono ricevuti e decodificati da un decodificatore di riga 844 e da un decodificatore di colonna 846 per accedere alla schiera di memoria 830. Verrà compreso da coloro che sono esperti nel ramo, con il beneficio della presente descrizione, che il collegamenti di immissione numero di degli indirizzi dipende dalla densità dalla architettura della schiera di memoria 830. Cioè, il numero di indirizzi aumenta sia con gli aumentati calcoli delle celle di memoria sia con gli aumentati calcoli di banchi e blocchi.

Il dispositivo di memoria 800 legge dati nella schiera di memoria 830 rilevando variazioni di tensione o corrente nelle colonne della schiera di memoria impiegando una circuiteria di rivelazione/buffer 150. La circuiteria di rivelazione/buffer, in una forma di realizzazione, è accoppiata per leggere ed agganciare una riga di dati dalla schiera di memoria 830. Una circuiteria

buffer 860 di ingresso e di uscita di dati è inclusa per una comunicazione bidirezionale di dati su una molteplicità di collegamenti di dati 862 con l'unità di controllo 810. Viene fornita una circuiteria di scrittura 855 per scrivere dati nella schiera di memoria.

Una circuiteria di controllo 870 decodifica i segnali forniti sui collegamenti di controllo 872 dall'elaboratore 810. Questi segnali vengono impiegati per controllare le operazioni sulla schiera di memoria 830, comprese operazioni scrittura lettura di dati. (programma) cancellazione di dati. La circuiteria di controllo 870 può essere una macchina a stati, sequenziatore, oppure qualsiasi altro tipo di unità di controllo.

Il dispositivo di memoria flash illustrato in figura 8 è stato semplificato per facilitare la comprensione di base delle caratteristiche della memoria. Una comprensione più dettagliata della circuiteria interna delle funzioni di memoria flash è nota a coloro che sono esperti nel ramo.

La figura 9 è una illustrazione di un modulo di memoria 900 esemplificativo. Il modulo di memoria 900 viene illustrato come una scheda di

memorie sebbene i concetti discussi con riferimento ad un modulo di memoria 900 siano applicabili ad altri tipi di memoria amovibile o portatile, ad esempio, unità di pilotaggio flash USB, e sono progettati per essere all'interno dell'ambito del "modulo di memoria" come impiegato in questa sede. Inoltre, sebbene in figura 9 venga illustrato un fattore di forma esemplificativo, questi concetti sono applicabili pure ad altri fattori di forma.

In talune forme di realizzazione, un modulo di memoria 900 includerà un alloggiamento 905 (come illustrato) per racchiudere uno o più dispositivi di memoria 910, sebbene tale alloggiamento non sia essenziale per tutti i dispositivi le applicazioni di dispositivo. Almeno un dispositivo di memoria 910 è una memoria non volatile [che include oppure è adatta ad eseguire gli elementi dell'invenzione]. Dove presente, l'alloggiamento più contatti 915 include uno 0 comunicazione con un dispositivo host. Esempi di dispositivi host includono videocamere digitali, dispositivi digitali di registrazione riproduzione, PDA, personal computer, lettori di schede di memoria, hub di interfaccia e simili. Per talune forme di realizzazione, i contatti 915 sono

la forma di una interfaccia standardizzata. Ad esempio, con un dispositivo di pilotaggio flash USB, i contatti 915 potrebbero essere nella forma di connettore maschio USB del Tipo A. Per alcune forme di realizzazione, i contatti 915 sono nella forma di una interfaccia semiproprietaria, quale di trovarsi sulle schede memoria potrebbe COMPACTFLASH sotto licenza da parte di SANDISK Corporation, schede di memoria MEMORYSTICK sotto licenza da parte di SONY Corporation, schede di memoria SD SECURE DIGITAL sotto licenza da parte di TOSHIBA Corporation e simili. In genere, tuttavia, i contatti 915 forniscono una interfaccia per far passare segnali di controllo, di indirizzo e/oppure di dati tra il modulo di memoria 900 ed un host avente recettori compatibili per i contatti 915.

Il modulo di memoria 900 può facoltativamente includere una circuiteria addizionale 920 che può essere una o più circuiti integrati e/oppure componenti discreti. Per alcune forme di realizzazione, la circuiteria addizionale 920 può includere una unità di controllo di memoria per controllare l'accesso attraverso più dispositivi di memoria 910 e/oppure per fornire uno strato di traslazione tra un host esterno ed un dispositivo

di memoria 910. Ad esempio, può non esservi una corrispondenza da uno ad uno tra il numero contatti 915 ed il numero di collegamenti di I/O all'uno o più dispositivi di memoria 910. Così, una unità di controllo di memoria potrebbe accoppiare selettivamente un collegamento di I/O (non mostrato in figura 9) di un dispositivo di memoria 910 per segnale opportuno al collegamento ricevere il opportuno di I/O all'istante opportuno oppure fornire il segnale opportuno al contatto opportuno 915 all'instante opportuno. In modo simile, il protocollo di comunicazione tra un host ed il modulo di memoria 900 può essere differente da ciò che viene richiesto per l'accesso di un dispositivo di memoria 910. Una unità di controllo di memoria potrebbe quindi traslare le sequenze di comando ricevute da un host nelle opportune sequenze di comando, per ottenere l'accesso desiderato al dispositivo di memoria 910. Tale traslazione può includere inoltre variazioni nei livelli tensione di segnale in aggiunta a sequenze di comando.

La circuiteria addizionale 920 può inoltre includere una funzionalità non correlata al controllo di un dispositivo di memoria 910, quali

funzioni logiche come potrebbero essere eseguite da ASIC (circuito integrato di applicazione specifica). Inoltre, la circuiteria addizionale 920 includere una circuiteria per limitare può l'accesso in lettura o scrittura al modulo di memoria 900, ad esempio protezione di password, biometria, o simili. La circuiteria addizionale 920 può includere una circuiteria per indicare lo stato modulo del di memoria 900. Ad esempio, la circuiteria addizionale 920 può includere la funzionalità per determinare se energia elettrica sta venendo fornita al modulo di memoria 900 e se al modulo di memoria 900 si sta avendo attualmente accesso, e visualizzare una indicazione del suo stato, ad esempio luce piena mentre alimentato e lampeggiante in fase di accesso. La luce 920 circuiteria addizionale può includere ulteriormente dispositivi passivi, ad esempio capacitori di disaccoppiamento, per aiutare regolamentare i requisiti di energia elettrica all'interno del modulo di memoria 900.

In breve, le forme di realizzazione della presente invenzione manipolano due bit da un dispositivo di memoria MLC con un unico registro latch. Viene impiegato soltanto un ulteriore

registro latch per realizzare una programmazione MLC con una lettura-modifica-scrittura e verifica durante una operazione di programmazione.

Sebbene siano state illustrate e descritte in questa sede forme di realizzazione specifiche, verrà compreso da coloro che sono di capacità ordinaria nel ramo che qualsiasi disposizione che viene calcolata per ottenere gli stessi scopi può essere sostituita per le forme di realizzazione Molti adattamenti specifiche mostrate. dell'invenzione saranno evidenti a coloro che sono di capacità ordinaria nel ramo. Di conseguenza, intende questa domanda coprire qualsiasi adattamento 0 variazione dell'invenzione. intende chiaramente che questa invenzione venga limitata soltanto dalle rivendicazioni che seguono e dai relativi equivalenti.

Ciliberto Tonon

#### RIVENDICAZIONI

1. Circuito latch di memoria, comprendente:

un registro latch avente un nodo ed un nodo invertito;

un primo transistore accoppiato tra l'uscita ed il nodo;

un secondo transistore accoppiato tra l'uscita ed il nodo invertito; e

un transistore di ripristino accoppiato al nodo invertito.

- 2. Circuito latch della rivendicazione 1 e che include inoltre una stringa serie di memoria avente una fila di bit accoppiata all'uscita.

- 3. Circuito latch della rivendicazione 1, in cui il latch è formato da una coppia di gate di invertitori accoppiati in modo tale che l'ingresso di ciascun invertitore sia accoppiato all'uscita dell'altro invertitore.

- 4. Circuito latch della rivendicazione 2, in cui la stringa di memoria è formata da una molteplicità di celle di memoria non volatili disposte in una configurazione NAND.

- 5. Circuito latch della rivendicazione 1, in cui i transistori primo, secondo e di ripristino sono transistori NMOS.

- 6. Circuito latch della rivendicazione 1, in cui i transistori primo, secondo e di ripristino hanno collegamenti di gate che sono accoppiati a segnali attivi alto.

- 7. Circuito latch della rivendicazione 1, in cui l'uscita è accoppiata ad un transistore di uscita di amplificatore di rilevazione.

- 8. Circuito latch di memoria, comprendente:

un registro latch avente un nodo ed un nodo invertito;

un primo transistore di controllo accoppiato tra l'uscita ed il nodo per accoppiare il nodo all'uscita in risposta ad un primo segnale di controllo;

un secondo transistore di controllo accoppiato tra l'uscita ed il nodo invertito per accoppiare il nodo invertito all'uscita in risposta ad un secondo segnale di controllo;

un transistore di ripristino accoppiato al nodo invertito per vincolare a massa il nodo invertito in risposta ad un segnale di ripristino.

9. Registro latch di memoria della rivendicazione 8, in cui il primo segnale di controllo, il secondo segnale di controllo ed il segnale di ripristino sono collegati agli ingressi dei gate dei loro

rispettivi transistori, ed attivano il rispettivo transistore in risposta ad un alto logico.

10. Circuito latch di memoria per realizzare un'operazione di programmazione di celle di memoria a più livelli, il circuito comprendendo;

un primo registro latch avente un nodo ed un nodo invertito;

un primo transistore accoppiato tra l'uscita ed il nodo;

un secondo transistore accoppiato tra l'uscita ed il nodo invertito;

un transistore di ripristino accoppiato al nodo invertito;

un secondo registro latch avente un nodo ed un nodo invertito;

un transistore di controllo di rilevazione accoppiato al nodo invertito; e

un gate di uscita di invertitore accoppiato al nodo invertito in modo tale che l'uscita del gate di uscita di invertitore sia l'uscita del secondo registro latch.

11. Circuito della rivendicazione 10, in cui il transistore di controllo di rilevazione trascina selettivamente al potenziale di massa il nodo invertito in risposta ad un segnale di rilevazione

di controllo.

- 12. Circuito della rivendicazione 11, in cui il segnale di rilevazione di controllo è accoppiato al gate del transistore di controllo di rilevazione e attiva il transistore, quando nello stato logico alto, per vincolare al potenziale di massa il nodo invertito.

- 13. Circuito della rivendicazione 10, in cui i registri latch primo e secondo sono ciascuno formato da una coppia di gate di invertitore accoppiato in modo tale che l'uscita di ciascun gate sia collegata all'ingresso dell'altro gate.

#### 14. Dispositivo di memoria flash, comprendente:

una schiera di memoria che comprende una molteplicità di celle di memoria non volatile disposte in righe e colonne in modo tale che ciascuna colonna sia costituita da una stringa serie di celle di memoria accoppiate ad una fila di bit; e

un circuito latch di memoria per realizzare una operazione di programmazione di memoria a celle a più livelli sulla schiera di memoria, il circuito accoppiato dalla schiera di memoria, e comprendendo:

un primo registro latch avente un nodo ed un

nodo invertito;

un primo transistore accoppiato tra l'uscita

ed il nodo;

un secondo transistore accoppiato tra l'uscita ed il nodo invertito;

un transistore di ripristino accoppiato al nodo invertito;

un secondo registro latch avente un nodo ed un nodo invertito;

un transistore di controllo di rilevazione accoppiato al nodo invertito; e

un gate di uscita di invertitore accoppiato al nodo invertito in modo tale che l'uscita del gate di uscita di invertitore sia accoppiata alla fila di bit.

- 15. Dispositivo della rivendicazione 14, in cui la schiera di memoria è disposta in una architettura NAND.

- 16. Dispositivo della rivendicazione 14, ed includente ulteriormente un transistore di rilevazione che accoppia la fila di bit all'uscita del primo registro latch.

- 17. Dispositivo della rivendicazione 14, in cui ciascuna della molteplicità di celle di memoria è atta a memorizzare due bit di dati.

18. Sistema di memoria comprendente:

un elaboratore che genera segnali di memoria;

un dispositivo di memoria accoppiato all'elaboratore e che opera in risposta ai segnali di memoria, il dispositivo di memoria comprendendo:

una schiera di memoria comprendente una molteplicità di celle di memoria non volatile disposta in righe e colonne, in modo tale che ciascuna colonna sia costituita da una stringa serie di celle di memoria accoppiate ad una fila di bit; e

un circuito latch di memoria accoppiato a ciascuna fila di bit della schiera di memoria e comprendente:

un registro latch avente un nodo ed un nodo

invertito;

un primo transistore accoppiato tra l'uscita ed il nodo;

un secondo transistore accoppiato tra l'uscita ed il nodo invertito; e

un transistore di ripristino accoppiato al nodo invertito.

19. Sistema della rivendicazione 18, in cui la schiera di memoria è una schiera di memoria ad

architettura NAND.

20. Sistema della rivendicazione 18, ed includente inoltre un circuito di lettura-modifica-scrittura accoppiato a ciascuna fila di bit per impedire la programmazione di celle selezionate sulla fila di bit, il circuito comprendendo:

un registro latch avente un nodo ed un nodo invertito;

un transistore di controllo di rilevazione accoppiato al nodo invertito; e

un gate di uscita di invertitore accoppiato al nodo invertito in modo tale che l'uscita del gate di uscita di invertitore sia accoppiata alla fila di bit.

#### 21. Modulo di memoria comprendente:

almeno due dispositivi di memoria, ciascuno comprendendo una schiera di memoria a più livelli disposta in righe e colonne, in modo tale che le righe comprendano file di parole accoppiate ai gate controllo di una molteplicità di celle di memoria, e le colonne comprendano file di accoppiate a stringhe serie di celle di memoria, la memoria ulteriormente schiera di disposta blocchi la schiera di memoria di memoria, comprendendo inoltre:

un circuito latch di memoria accoppiato a ciascuna fila di bit della schiera di memoria e comprendente:

un registro latch avente un nodo ed un nodo invertito;

un primo transistore accoppiato tra l'uscita ed il nodo;

un secondo transistore accoppiato tra l'uscita ed il nodo invertito; e

un transistore di ripristino accoppiato al nodo invertito; e

una molteplicità di contatti configurati per fornire un contatto selettivo tra la schiera di memoria ed un sistema host.

- 22. Modulo della rivendicazione 21, ed includente ulteriormente una unità di controllo di memoria accoppiata alla schiera di memoria per controllare l'operazione del dispositivo di memoria in risposta al sistema host.

- 23. Metodo per leggere dati di pagina uno di più pagine di un dispositivo di memoria a celle a più livelli avente un singolo circuito latch accoppiato a ciascuna fila di bit, il circuito latch comprendendo un registro latch con nodi invertito e non invertito, un primo transistore di controllo

accoppiato tra il nodo non invertito e l'uscita di latch, un secondo transistore di controllo accoppiato tra il nodo invertito e l'uscita del registro latch, ed un transistore di ripristino accoppiato tra il nodo invertito e la massa di circuito, il metodo comprendendo:

ripristinare il registro latch in un primo istante;

polarizzare, in un primo istante, una fila di parole selezionata del dispositivo di memoria con potenziale di massa;

polarizzare, in un secondo istante, la fila di parole selezionata con una tensione di lettura maggiore del potenziale di massa; e

accoppiare, in un secondo istante, il nodo non invertito all'uscita del registro latch per leggere dati di pagina uno.

- 24. Metodo della rivendicazione 23, in cui il ripristinare il registro latch comprende l'accoppiare il nodo invertito alla massa di circuito attraverso il transistore di ripristino.

- 25. Metodo della rivendicazione 23, in cui l'accoppiamento comprende l'attivare il primo transistore di controllo con un segnale alto.

- 26. Metodo per leggere dati di pagina zero di più

pagine di un dispositivo di memoria a celle a a più livelli avente un unico circuito latch accoppiato a fila di bit, il circuito ciascuna comprendendo un registro latch con nodi invertito e non invertito, un primo transistore di controllo accoppiato tra il nodo non invertito e l'uscita di registro latch, un secondo transistore di controllo accoppiato tra il nodo invertito e l'uscita di registro latch, ed un transistore di ripristino accoppiato tra il nodo invertito e la massa di circuito, il metodo comprendendo:

ripristinare, in un primo istante, il registro latch;

polarizzare, in un primo istante, al potenziale di massa, una fila di parole selezionata del dispositivo di memoria;

accoppiare, in un secondo istante, il nodo non invertito all'uscita di registro latch;

polarizzare, ad un secondo istante, la fila selezionata di parole ad una prima tensione di lettura, maggiore del oppure uguale al potenziale di massa;

in un terzo istante, accoppiare il nodo invertito all'uscita del registro latch; e

polarizzare, ad un terzo istante, la riga di

parole selezionata ad una seconda tensione di lettura, maggiore della prima sezione di lettura, per leggere i dati di pagina zero.

- 27. Metodo della rivendicazione 26, in cui il transistore di ripristino viene attivato soltanto durante il primo istante.

- 28. Metodo della rivendicazione 26, in cui il nodo non invertito è accoppiato all'uscita attivando il primo transistore di controllo ed il nodo invertito è accoppiato all'uscita attivando il secondo transistore di controllo.

- 29. Metodo della rivendicazione 26, in cui la prima tensione di lettura si trova tra le distribuzioni delle tensioni di soglia prima e seconda, e la seconda tensione di lettura si trova tra le distribuzioni delle tensioni di soglia terza e quarta.

#### 30. Modulo di memoria comprendente:

un dispositivo di memoria comprendente una schiera di memoria a più livelli disposta in righe e colonne, in modo tale che le righe comprendano file di parole accoppiate ai gate di controllo di una molteplicità di celle di memoria, e le colonne comprendano file di bit accoppiate a stringhe serie di celle di memoria, la schiera di memoria

ulteriormente disposta in blocchi di memoria, la schiera di memoria comprendendo inoltre:

un circuito latch di memoria accoppiato a ciascuna fila di bit della schiera di memoria e comprendente:

un registro latch avente un nodo ed un nodo invertito;

un primo transistore accoppiato tra l'uscita

ed il nodo;

un secondo transistore accoppiato tra l'uscita ed il nodo invertito; e

un transistore di ripristino accoppiato al nodo invertito;

un alloggiamento per racchiudere il dispositivo di memoria; e

una molteplicità di contatti accoppiati all'alloggiamento e configurati per fornire un contatto selettivo tra la schiera di memoria ed un sistema host.

p.p. Micron Technology, Inc

Giberto Tonon

1/8

FIG. 1

p.p. Micron Technology, Inc.

Gilberto Tonon (Iscr. Albo n. 83 BM) SOCIETÀ ITALIANA BREVETTI

Aren

2/8

FIG. 2

p.p. Micron Technology, Inc.

Gilberto Tonon (Iscr. Albo n. 83 BM) SOCIETÀ ITALIANA BREVETTI

FIG. 3

P

p.p. Micron Technology, Inc.

Gilberto Tonon (Iscr. Albo n. 83 BM) SOCIETÀ ITALIANA BREVETTI fren

4/8

FIG. 4

FIG. 5

p.p. Micron Technology, Inc.

Gilberto Tonon (Iscr. Albo n. 83 BM) SOCIETÀ ITALIANA BREVETTI

FIG. 6

p.p. Micron Technology, Inc.

Gilberto Tonon (Iscr. Albo n. 83 BM) SOCIETÀ ITALIANA BREVETTI

I S 20 0 တ  $\bigcirc$ C

6/8

FIG. 8

Je)

p.p. Micron Technology, Inc.

Gilberto Tonon (Iscr. Albo n. 83 BM) SOCIETÀ ITALIANA BREVETTI

8/8

FIG. 9

p.p. Micron Technology, Inc.

Gilberto Tonon (Iscr. Albo n. 83 BM) SOCIETÀ ITALIANA BREVETTI Mer