(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-159077

(P2007-159077A)

(43) 公開日 平成19年6月21日(2007.6.21)

(51) Int.CI.

**H03B 5/32**

(2006.01)

F 1

H03B 5/32

テーマコード(参考)

J

5 J 0 7 9

審査請求 未請求 請求項の数 3 書面 (全 6 頁)

(21) 出願番号

特願2005-380816 (P2005-380816)

(22) 出願日

平成17年12月6日 (2005.12.6)

(71) 出願人 390009667

セイコーN P C株式会社

東京都中央区日本橋兜町 15番6号

(72) 発明者 佐藤 正敏

栃木県那須塩原市下田野531-1 日本

プレシジョン・サーティツ株式会社内

(72) 発明者 斎藤 直紀

栃木県那須塩原市下田野531-1 日本

プレシジョン・サーティツ株式会社内

F ターム(参考) 5J079 AA04 BA04 BA42 FA05 FA14

FA21 GA04 GA09 GA15 GA19

(54) 【発明の名称】発振回路

## (57) 【要約】

【課題】 発振特性の変動が少なく、また、低電圧からの安定発振を可能とする発振回路を提供する。

【解決手段】 インバータ回路と、インバータ回路に並列に接続された帰還抵抗と、帰還抵抗の一端と電源との間に接続された第1の容量と、帰還抵抗の他端と電源との間に接続された第2の容量とを有し、前記インバータ回路に水晶振動子を並列に接続することにより発振出力を生成する発振回路において、前記インバータ回路は、電源電圧と定電圧との間に直列に接続されたPchMOSトランジスタおよびNchMOSトランジスタと、第3の容量とを有し、これらトランジスタのうち前記定電位に電流通路の一端が接続された方のトランジスタのゲートに前記第3の容量を介してインバータ回路の入力信号が与えられる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

インバータ回路と、前記インバータ回路に並列に接続された帰還抵抗と、前記帰還抵抗の一端と電源との間に接続された第1の容量と、前記帰還抵抗の他端と電源との間に接続された第2の容量とを有し、前記インバータに水晶振動子を並列に接続することにより発振出力を生成する発振回路において、前記インバータ回路は、電源電圧と定電圧との間に直列に接続されたPchMOSトランジスタおよびNchMOSトランジスタと、第3の容量とを有し、前記トランジスタのうち前記定電位に電流通路の一端が接続された方のトランジスタのゲートには前記第3の容量を介してインバータ回路の入力信号が与えられることを特徴とする発振回路。

10

**【請求項 2】**

前記発振回路は定電圧回路により生成される電圧で駆動されることを特徴とする請求項1記載の発振回路。

**【請求項 3】**

前記発振回路は、前記インバータ回路の出力と前記帰還抵抗との間に直列に接続された出力抵抗を有することを特徴とする請求項1記載の発振回路。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は水晶振動子を用いた発振回路に関する。

20

**【背景技術】****【0002】**

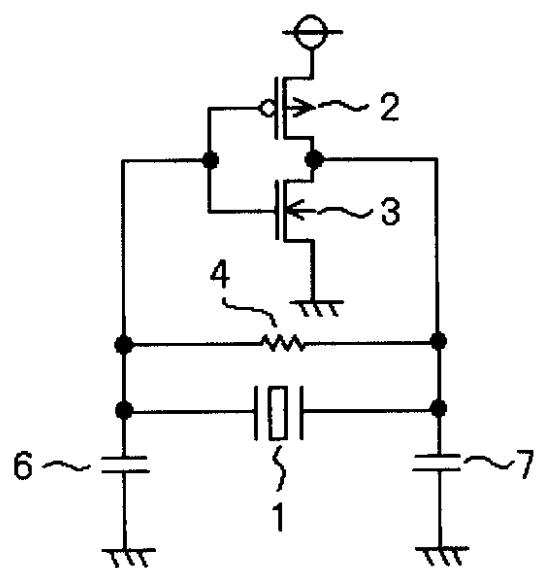

従来の発振回路の構成を図3に示す。発振回路は、PchMOSトランジスタ2とNchMOSトランジスタ3とが高電位電源(電源電圧)と低電位電源(接地電位)との間で直列接続し構成されるインバータ回路と、該インバータ回路の入出力端子間に接続された水晶振動子1及び帰還抵抗4とを有し、インバータ回路の入力端は第1の容量6を介して低電位電源と接続され、インバータ回路の出力端は第2の容量7を介して低電位電源と接続されている。かかる発振回路の構成は、例えば特開2004-80650に記載されている。

30

**【0003】**

【特許文献1】特開2004-80650

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

従来の発振回路では、インバータ回路が電源電圧と接地電位間に接続されるような電源電圧を印加する形式であったため、電源電圧の変動に起因して発振特性の変動が大きかった。さらに発振振幅が大きく、水晶振動子に流れる電流が大きいため異常発振が出易い問題があった。

**【0005】**

このような発振特性の変動を低減する手段として、インバータ回路の接続される高電位電源を、電源電圧ではなく定電圧回路を用いて定電圧にすることが考えられる。しかしながら、該定電圧はその動作上、インバータ回路に用いられているPchMOSトランジスタ2のしきい値とNchMOSトランジスタ3のしきい値との和以上に設定しなければいけないため、低電圧で安定発振させるのが困難であった。

40

**【課題を解決するための手段】****【0006】**

上記課題を解決するために、本発明の発振回路は、インバータ回路と、前記インバータ回路に並列に接続された帰還抵抗と、前記帰還抵抗の一端と電源との間に接続された第1の容量と、前記帰還抵抗の他端と電源との間に接続された第2の容量とを有しており、前記インバータに水晶振動子を並列に接続することにより発振出力を生成する発振回路にお

50

いて、前記インバータ回路は、電源電圧と定電圧との間に直列に接続された PchMOS ドランジスタおよびNchMOS ドランジスタと、第3の容量とを有し、前記ドランジスタのうち前記定電位に電流通路の一端が接続された方のドランジスタのゲートには前記第3の容量を介してインバータ回路の入力信号が与えられる。

【0007】

また、前記発振回路は定電圧回路により生成される電圧で駆動されることを特徴とする。

【0008】

また、前記発振回路は、前記インバータ回路の出力と前記帰還抵抗との間に直列に接続された出力抵抗を有することを特徴とする。

【発明の効果】

【0009】

本発明によれば、発振インバータ回路の PchMOS ドランジスタ又は NchMOS ドランジスタのゲートを容量を介して信号が入力されることにより、低電圧からの発振開始が可能となる。

また、発振回路を定電圧回路で駆動することにより、高安定、低消費電流を可能とする。

更に、インバータ回路の出力と前記帰還抵抗との間に直列に接続された出力抵抗を有することにより、安定発振が可能となる。

【0010】

また、本発明によれば、PchMOS ドランジスタのゲートをカップリングしているため、低電圧からの安定発振が可能となる。さらに、発振振幅が小さいため、水晶振動子に流れる電流が少なく、出力抵抗を接続することでさらなる水晶電流の削減を可能とし、異常発振が起こり難い発振回路となる。

【発明を実施するための最良の形態】

【0011】

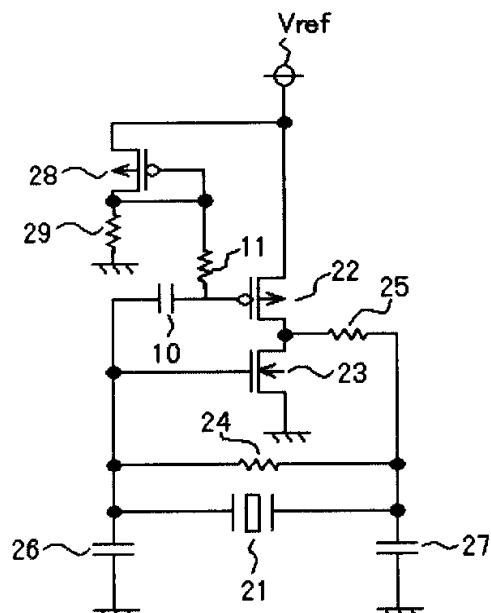

以下、本発明の好適な実施の形態を添付図面を参照し説明する。図1は本発明の第1の実施の形態に係わる発振回路を示している。発振回路は、インバータ回路と、該インバータ回路の出入力端子間に接続された水晶振動子21及び帰還抵抗24とを有し、インバータ回路の入力端は第1の容量26を介して低電位電源と接続され、インバータ回路の出力端は抵抗素子25、第2の容量27を介して低電位電源と接続されている。出力抵抗25は、帰還回路の位相の安定化および水晶振動子21に印加される振幅レベルの減少のために用いられている。

【0012】

本実施の形態の発振回路におけるインバータ回路は、高電位(定電位 Vref)と低電位電源(接地電位)との間で直列接続し構成される PchMOS ドランジスタ22と NchMOS ドランジスタ23とを有し、PchMOS ドランジスタ22が接続される高電位は、定電位回路を用いて生成される定電位(Vref)が供給される。更に、そのソースが定電位(Vref)に接続されドレインとゲートが共通接続された PchMOS ドランジスタ28と、一端が PchMOS ドランジスタ28のドレインに接続され他端が低電位電源に接続された抵抗素子29と、一端が PchMOS ドランジスタ28のドレインに接続され他端が PchMOS ドランジスタ22のゲートに接続された抵抗素子11と、PchMOS ドランジスタ22のゲートと第1の容量26との間に接続された第3の容量10とを有する。

【0013】

PchMOS ドランジスタ28及び抵抗素子29は、PchMOS ドランジスタ22のゲートバイアス電圧を印加するための素子であり、第3の容量10はインバータのバイアス回路と PchMOS ドランジスタ22のゲートを A C 的に分離するためのものである。

【0014】

PchMOS ドランジスタ22のゲートには、PchMOS ドランジスタ28及び抵抗

10

20

30

40

50

素子29で決定されるバイアス電圧を中心に、カップリング容量10を介して入力される信号が印加される。従って、PchMOSトランジスタ28及び抵抗素子29で決定されるバイアス電圧を適正に選択することにより、インバータ回路に印加される電圧が低い場合でも、PchMOSトランジスタ22のしきい値に影響されず、NchMOSトランジスタ23のしきい値+の電圧で発振開始することができる。さらに、発振回路を定電圧で動作させることにより、低電圧動作かつ発振特性の電源電圧依存性が少ない発振回路の構成が可能となる。

#### 【0015】

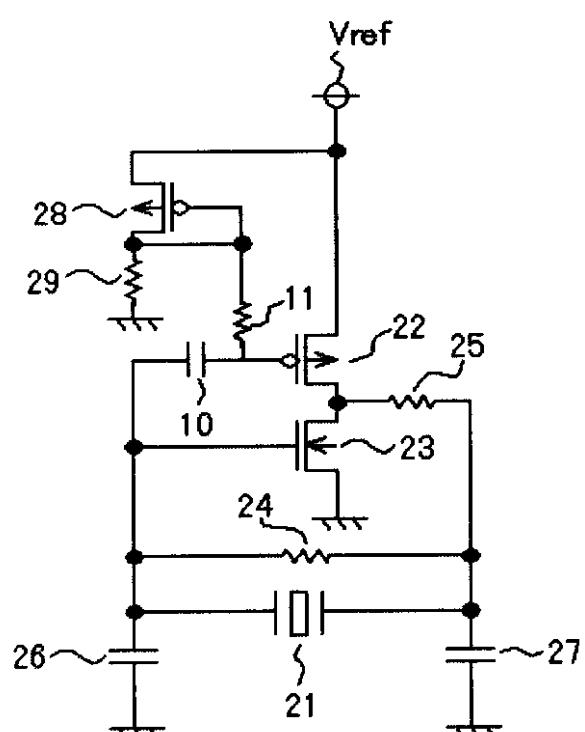

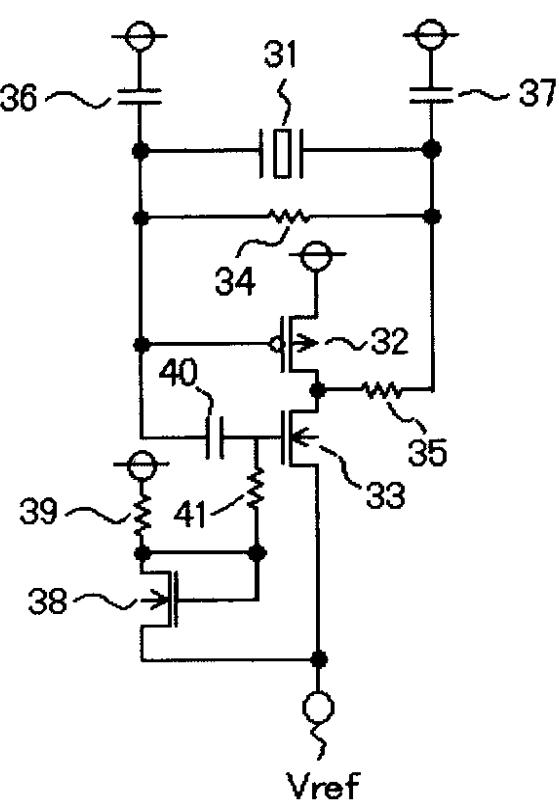

図2は本発明の第2の実施の形態に係わる発振回路であり、インバータ回路のNchMOSトランジスタのゲートをカップリングする場合の回路例である。10

発振回路は、インバータ回路と、該インバータ回路の入出力端子間に接続された水晶振動子31及び帰還抵抗34とを有し、インバータ回路の入力端は第1の容量36を介して高電位電源と接続され、インバータ回路の出力端は抵抗素子35、第2の容量37を介して高電位電源と接続されている。出力抵抗35は、帰還回路の位相の安定化および水晶振動子31に印加される振幅レベルの減少のために用いられている。

#### 【0016】

本実施の形態の発振回路におけるインバータ回路は、高電位電源（電源電位）と低電位電源（定電位）との間で直列接続し構成されるPchMOSトランジスタ32とNchMOSトランジスタ33とを有し、NchMOSトランジスタ33が接続される低電位は、定電位回路を用いて生成される定電位（Vref）が供給される。更に、そのソースが定電位（Vref）に接続されドレインとゲートが共通接続されたNchMOSトランジスタ38と、一端がNchMOSトランジスタ38のドレインに接続され他端が高電位電源に接続された抵抗素子39と、一端がNchMOSトランジスタ38のドレインに接続され他端がNchMOSトランジスタ33のゲートに接続された抵抗素子41と、NchMOSトランジスタ33のゲートと第1の容量36との間に接続された第3の容量40とを有する。20

#### 【0017】

NchMOSトランジスタ38及び抵抗素子39は、NchMOSトランジスタ33のゲートバイアス電圧を印加するための素子であり、第3の容量40はインバータのバイアス回路とNchMOSトランジスタ33のゲートをAC的に分離するためのものである。30

#### 【0018】

NchMOSトランジスタ33のゲートには、NchMOSトランジスタ38及び抵抗素子39で決定されるバイアス電圧を中心に、第3の容量40を介して入力される信号が印加される。従って、NchMOSトランジスタ38及び抵抗素子39で決定されるバイアス電圧を適正に選択することにより、インバータ回路に印加される電圧が低い場合でも、PchMOSトランジスタ32のしきい値+の電圧で発振開始することができる。さらに、発振回路を定電圧で動作させることにより、低電圧動作かつ発振特性の電源電圧依存性が少ない発振回路の構成が可能となる。

#### 【0019】

上記実施の形態では、インバータ回路を構成するPchMOSトランジスタ又はNchMOSトランジスタの一方のみを容量を介して信号を入力させたが、両方のトランジスタに適用することも可能である。40

#### 【図面の簡単な説明】

#### 【0020】

【図1】 本発明の第1の実施の形態に係わる発振回路を示す回路図である。

【図2】 本発明の第2の実施の形態に係わる発振回路を示す回路図である。

【図3】 従来技術における発振回路の一般的な構成を示した回路図である。

#### 【符号の説明】

#### 【0021】

1、21、31：水晶振動子

10

20

30

40

50

- 2、22、32：PchMOSトランジスタ

3、23、33：NchMOSトランジスタ

4、24、34：帰還抵抗

25、35：出力抵抗

6、26、36：第1の容量

7、27、37：第2の容量

10、40：第3の容量、

【図1】

【図2】

【図3】