(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6679748号

(P6679748)

(45) 発行日 令和2年4月15日(2020.4.15)

(24) 登録日 令和2年3月23日(2020.3.23)

(51) Int.Cl.

F 1

|                   |                  |      |       |       |

|-------------------|------------------|------|-------|-------|

| <b>H01L 23/12</b> | <b>(2006.01)</b> | H01L | 23/12 | 501 P |

| <b>H05K 3/46</b>  | <b>(2006.01)</b> | H05K | 3/46  | Q     |

| <b>H05K 1/02</b>  | <b>(2006.01)</b> | H05K | 3/46  | Q     |

|      |      |   |

|------|------|---|

| HO5K | 3/46 | N |

| HO5K | 3/46 | J |

| HO5K | 1/02 |   |

請求項の数 28 (全 40 頁)

(21) 出願番号 特願2018-549181 (P2018-549181)

(86) (22) 出願日 平成29年3月16日 (2017.3.16)

(65) 公表番号 特表2019-511120 (P2019-511120A)

(43) 公表日 平成31年4月18日 (2019.4.18)

(86) 國際出願番号 PCT/US2017/022829

(87) 國際公開番号 WO2017/161199

(87) 國際公開日 平成29年9月21日 (2017.9.21)

審査請求日 令和1年8月2日 (2019.8.2)

(31) 優先権主張番号 15/074,750

(32) 優先日 平成28年3月18日 (2016.3.18)

(33) 優先権主張国・地域又は機関

米国(US)

早期審査対象出願

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 デイク・キム

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

最終頁に続く

(54) 【発明の名称】バックサイドドリリング埋込みダイ基板

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の面と反対側の第2の面とを有する基板であって、導電層と、前記導電層の第1の表面に結合された第1の誘電体層と、前記導電層の反対側の第2の表面に結合された第2の誘電体層とを含むコア基板である基板と、

前記基板内に画定されるキャビティであって、

前記キャビティのフロアが、前記第2の誘電体層によって画定され、

前記キャビティの側壁が、前記第1の誘電体層の断面および前記導電層の断面により画定され、前記第1の誘電体層の断面および前記導電層の断面は共平面にある、キャビティと。

前記キャビティの前記フロアに結合されたダイであって、前記キャビティの前記フロアに対して遠方にある前記ダイの面上に導電性パッドを有するダイと、

前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延び、前記第2の誘電体層、前記ダイ、および前記導電性パッド内に画定される穴と、

前記穴内に位置し、前記第2の誘電体層と前記ダイと前記導電性パッドとの間を、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延びる導電性材料とを備えるデバイス。

## 【請求項 2】

前記穴は、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って連続している、請求項1に記載のデバイス。

**【請求項 3】**

前記穴は、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延びる直線軸に沿って同心である、請求項1に記載のデバイス。

**【請求項 4】**

前記穴は、前記穴の長さに沿った単一の直線穴である、請求項1に記載のデバイス。

**【請求項 5】**

前記導電性材料は、一体化した单一セグメントである、請求項1に記載のデバイス。

**【請求項 6】**

前記導電性材料は、1つの層のみを含む、請求項1に記載のデバイス。

**【請求項 7】**

前記導電性材料は、前記導電性パッド内から前記導電性パッドに結合し、前記キャビティの前記フロアに対して遠方にある前記導電性パッドの面の所で終わる、請求項1に記載のデバイス。

**【請求項 8】**

第1の面と反対側の第2の面とを有する基板であって、

導電層と、前記導電層の第1の表面に結合された第1の誘電体層と、前記導電層の反対側の第2の表面に結合された第2の誘電体層とを含むコア基板である基板と、

前記基板内に画定されるキャビティであって、

前記キャビティのフロアが、前記第2の誘電体層によって画定され、

前記キャビティの側壁が、前記第1の誘電体層の断面および前記導電層の断面により画定され、前記第1の誘電体層の断面および前記導電層の断面は共平面にある、キャビティと、

前記キャビティの前記フロアに結合されたダイであって、前記キャビティの前記フロアに対して遠方にある前記ダイの面上に導電性パッドを有するダイと、

前記基板の前記第2の面に結合された積層であって、前記第2の誘電体層が、前記ダイと前記積層との間にはさまれる積層と、

前記積層、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延び、前記積層、前記第2の誘電体層、前記ダイ、および前記導電性パッド内に画定される穴と、

前記穴内に位置し、前記積層と前記第2の誘電体層と前記ダイと前記導電性パッドとの間を、前記積層、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延びる導電性材料とを備えるデバイス。

**【請求項 9】**

前記穴は、前記積層、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って連続している、請求項8に記載のデバイス。

**【請求項 10】**

前記穴は、前記積層、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延びる直線軸に沿って同心である、請求項8に記載のデバイス。

**【請求項 11】**

前記穴は、前記穴の長さに沿った単一の直線穴である、請求項8に記載のデバイス。

**【請求項 12】**

前記導電性材料は、一体化した单一セグメントである、請求項8に記載のデバイス。

**【請求項 13】**

前記導電性材料は、1つの層のみを含む、請求項8に記載のデバイス。

**【請求項 14】**

前記デバイスは、モバイルデバイス、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末、ポータブルデータ端末、全地球測位システム(GPS)対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、固定ロケーション端末、通信デバイス、モバイル電話、スマートフォン、タブレットコンピュータ、コンピュータ、装着型デバイス、モノの

10

20

30

40

50

インターネット( I o T )デバイス、ラップトップコンピュータ、サーバ、ルータ、自動車に実装される電子デバイスのうちの少なくとも1つを含む群から選択されるデバイスに組み込まれる、請求項8に記載のデバイス。

**【請求項15】**

第1の面と反対側の第2の面とを有する基板であって、

導電層と、前記導電層の第1の表面に結合された第1の誘電体層と、前記導電層の反対側の第2の表面に結合された第2の誘電体層とを含むコア基板である基板と、

前記基板内に画定されるキャビティであって、

前記キャビティのフロアが、前記第2の誘電体層によって画定され、

前記キャビティの側壁が、前記第1の誘電体層の断面および前記導電層の断面により画定され、前記第1の誘電体層の断面および前記導電層の断面は共平面にある、キャビティと、

前記キャビティの前記フロアに結合されたダイであって、前記キャビティの前記フロアに対して遠方にある前記ダイの面上に導電性パッドを有するダイと、

前記基板および前記ダイを貫通し、前記導電性パッドを前記基板の前記第2の面上の、前記導電性パッドと反対側のノードに結合する相互接続部のための手段とを備えるデバイス。

**【請求項16】**

前記相互接続部のための前記手段は、

前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通じて延び、前記第2の誘電体層、前記ダイ、および前記導電性パッド内に画定される穴と、

前記穴内に位置し、前記第2の誘電体層と前記ダイと前記導電性パッドとの間を、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通じて延びる導電性材料とを備える、請求項15に記載のデバイス。

**【請求項17】**

前記相互接続部のための前記手段は、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通じて連続している、請求項15に記載のデバイス。

**【請求項18】**

前記相互接続部のための前記手段は、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通じて延びる直線軸に沿って同心である、請求項15に記載のデバイス。

**【請求項19】**

前記相互接続部のための前記手段は、前記穴の長さに沿った単一の直線穴を含む、請求項16に記載のデバイス。

**【請求項20】**

前記相互接続部のための前記手段は、前記導電性パッド内から前記導電性パッドに結合し、前記キャビティの前記フロアに対して遠方にある前記導電性パッドの面の所で終わる一体化した単一セグメントとして形成される導電性材料を含む、請求項15に記載のデバイス。

**【請求項21】**

埋込みダイ基板を製作する方法であって、

第1の面と反対側の第2の面とを有する基板を用意するステップであって、

前記基板が、導電層と、前記導電層の第1の表面に結合された第1の誘電体層と、前記導電層の反対側の第2の表面に結合された第2の誘電体層とを含むコア基板である、ステップと、

前記基板内に画定されるキャビティを形成するステップであって、

前記キャビティのフロアが、前記第2の誘電体層によって画定され、

前記キャビティの側壁が、前記第1の誘電体層の断面および前記導電層の断面により画定され、前記第1の誘電体層の断面および前記導電層の断面は共平面にある、ステップと、

前記キャビティの前記フロアにダイを結合するステップであって、前記ダイが、前記キ

10

20

30

40

50

ヤビティの前記フロアに対して遠方にある前記ダイの面上に導電性パッドを有する、ステップと、

前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延び、前記第2の誘電体層、前記ダイ、および前記導電性パッド内に画定される穴をドリリングするステップと、

前記第2の誘電体層と前記ダイと前記導電性パッドとの間を、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延び、前記穴内から前記導電性パッドに結合する導電性材料によって前記穴をめっきし、および／または充填するステップとを含む方法。

**【請求項22】**

10

前記ダイは、前記穴をドリリングするステップの前に、前記キャビティの前記フロアに結合される、請求項21に記載の方法。

**【請求項23】**

前記穴をドリリングするステップは、1度に実行される、請求項21に記載の方法。

**【請求項24】**

前記穴は、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延びる直線軸に沿って同心であるように形成される、請求項21に記載の方法。

**【請求項25】**

前記穴は、前記穴の長さに沿った单一の直線穴であるように形成される、請求項21に記載の方法。

20

**【請求項26】**

前記導電性材料は、一体化した単一セグメントとして形成される、請求項21に記載の方法。

**【請求項27】**

前記第2の誘電体層と前記ダイと前記導電性パッドとの間を、前記第2の誘電体層、前記ダイ、および前記導電性パッド内を通って延びる前記導電性材料は、1つだけの層として形成される、請求項21に記載の方法。

**【請求項28】**

前記基板の前記第2の面に積層を結合するステップをさらに含み、

前記穴は、前記積層内を通って延びて前記積層内に画定されるようにさらにドリリングされ、前記導電性材料は、前記積層内を通ってさらに延びる、請求項21に記載の方法。

30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

**関連出願の相互参照**

本出願は、2016年3月18日に米国特許商標庁に出願された非仮出願第15/074,750号の優先権および利益を主張し、その内容全体が、以下に全文が完全に記載されるかのように、すべての適用可能な目的のために参照により本明細書に組み込まれている。

**【0002】**

40

様々な特徴は概して、埋込みダイ基板に関し、より詳細には、ダイ内部から導電性パッドを露出させるためにバックサイドドリリングプロセスの間にダイが貫通される埋込みダイ基板に関する。

**【背景技術】**

**【0003】**

ハンドヘルド電子デバイスおよび装着型電子デバイスに対する需要が引き続き増大している。ハンドヘルド電子デバイスの例には、モバイル携帯電話、撮像デバイス（たとえば、カメラ）、音楽デバイス（たとえば、MP3プレーヤー）、および上述のデバイスのうちの1つまたは複数の機能を組み込んだデバイスが含まれる。装着型電子デバイスの例には、撮像デバイス、ビデオディスプレイ、およびインターネットアクセス端末の機能を組み

50

込んだ眼鏡が含まれる。装着型デバイスのさらなる例には、ユーザの生理学的パラメータ（たとえば、心拍数、血中酸素濃度、睡眠中の落ち着きのなさ）および／または地理的位置を監視／記録／送信するデバイスの機能が組み込まれる場合がある手首装着型デバイスが含まれる。手首装着型デバイスには、追加または代替として、カラーディスプレイを有するモバイル携帯デバイスの機能が組み込まれる場合がある。多くのハンドヘルド電子デバイスおよび装着型電子デバイスには、何らかの形態のワイヤレス通信が組み込まれる。ユーザは、電子デバイスのイタレーションごとに新しい機能、メモリの追加および性能の向上を期待している。さらに、ユーザは、新しい機能、追加のメモリ、および向上した性能が組み込まれるにもかかわらずユーザのデバイスのサイズが変わらないかまたは小さくなることを期待している。

10

#### 【0004】

サイズを小さくするために、デバイスは、トランジスタ密度を高くしおよび／またはデバイス内に組み込まれるダイのサイズを小さくするように設計される場合がある。少なくとも保護および集積を目的として、ダイをパッケージ内に実装することができる。パッケージサイズを小さくするために、ダイをパッケージ内にワイヤボンディングする手法はフリップチップボンディングに移行している。デバイスの全体的なサイズを小さくするためにボールグリッドアレイなどのパッケージ形態も使用される。

#### 【0005】

ダイ／パッケージの垂直集積も、電子デバイスの全体的なサイズを小さくする助けになっている。垂直集積構成では、ダイ／パッケージが互いに積層される場合がある。垂直に積層されたダイ／パッケージの例には、パッケージオンパッケージ（P o P）構造が含まれる。P o P構造は、ボールグリッドアレイパッケージの垂直スタックで構成される場合がある。

20

#### 【0006】

垂直集積に使用される別の構造は、埋込みダイ基板または埋込み積層基板（本明細書では一貫性のために埋込みダイ基板（E D S）と呼ばれる）と呼ばれる。E D Sは多層基板を使用する場合がある。垂直サイズを小さくするために、多層基板の上部に能動ダイおよび／または能動／受動構成要素を取り付ける代わりに、多層基板のキャビティ内に能動ダイおよび／または能動／受動構成要素が取り付けられる。

#### 【0007】

30

E D Sを使用すると垂直サイズは小さくなることがあるが、実装における問題は解消しない。たとえば、E D S実装形態では、ダイのトップサイド（たとえば、第1の面）上のパッドに、ダイの反対側のバックサイド（たとえば、第2の面）に隣接するノードから到達できるように、製作コストがかかるダイが使用される場合がある。したがって、たとえば、E D S実装形態において使用されるダイのコストを減らし、それにもかかわらずダイのバックサイドに隣接するノードからダイのトップサイド上のパッドに到達できるようにすることが望ましい。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0008】

40

本明細書に開示された態様は、埋込みダイ基板などのデバイスを製作するデバイスおよび方法を提供する。

#### 【0009】

一態様によれば、デバイスは、第1の面と反対側の第2の面とを有する基板を含んでもよい。デバイスは、第1の面から基板内に画定されたキャビティとキャビティのフロアに結合されたダイとをさらに含んでもよい。ダイは、キャビティのフロアに対して遠位側のダイの面上に導電性パッドを有してもよい。デバイスは、基板の第2の面、ダイ、および導電性パッド内を通って延び、基板の第2の面、ダイ、および導電性パッド内に画定される穴をさらに含んでもよい。デバイスは、この穴内に位置し、基板の第2の面と導電性パッドとの間を、基板の第2の面および導電性パッド内を通って延びる導電性材料をまたさ

50

らに含んでもよい。導電性材料は、相互接続部を形成することがあり、または相互接続部と呼ばれることがある。より具体的な用語では、導電性材料は、単一セグメントダイ貫通相互接続部を形成することがあり、または単一セグメントダイ貫通相互接続部と呼ばれることがある。

#### 【0010】

いくつかの実装形態では、基板は、基板の第1の面における第1の誘電体層と基板の第2の面における第2の誘電体層との間にはさまれた導電層を含むコア基板である。いくつかの例では、基板がそのようなコア基板であるとき、キャビティは、第1の誘電体層および導電層を含んでおらず、キャビティのフロアは、キャビティ内に露出された第2の誘電体層によって画定される。

10

#### 【0011】

一態様では、この穴は、基板の第2の面、ダイ、および導電性パッド内を通って連続している。一態様では、この穴は、基板の第2の面、ダイ、および導電性パッド内を通って延びる直線軸に沿って同心である。一態様では、この穴は、穴の長さに沿った单一の直線穴である。

#### 【0012】

一態様では、導電性材料はユニタリー単一セグメントである。導電性材料は1つの層のみを含む。

#### 【0013】

別の態様によれば、デバイスは、第1の面と反対側の第2の面とを有する基板を含んでもよい。デバイスは、第1の面から基板内に画定されたキャビティとキャビティのフロアに結合されたダイとをさらに含んでもよい。ダイは、キャビティのフロアに対して遠位側のダイの面上に導電性パッドを有してもよい。デバイスは、基板の第2の面に結合された積層をまたさらに含んでもよい。そのような態様では、基板の第2の面は、ダイと積層との間にはさまれる。デバイスは、積層、基板の第2の面、ダイ、および導電性パッド内を通って延び、積層、基板の第2の面、ダイ、および導電性パッド内に画定される穴をさらに含んでもよい。デバイスは、この穴内に位置し、積層と基板の第2の面とダイと導電性パッドとの間を、積層、基板の第2の面、ダイ、および導電性パッド内を通って延びる導電性材料をまたさらに含んでもよい。導電性材料は、相互接続部を形成することがあり、または相互接続部と呼ばれることがある。より具体的な用語では、導電性材料は、単一セグメントダイ貫通相互接続部を形成することがあり、または単一セグメントダイ貫通相互接続部と呼ばれることがある。

20

#### 【0014】

いくつかの実装形態では、基板は、基板の第1の面における第1の誘電体層と基板の第2の面における第2の誘電体層との間にはさまれた導電層を含むコア基板である。

#### 【0015】

一態様では、この穴は、積層、基板の第2の面、ダイ、および導電性パッド内を通って連続している。一態様では、この穴は、積層、基板の第2の面、ダイ、および導電性パッド内を通って延びる直線軸に沿って同心である。一態様では、この穴は、穴の長さに沿った单一の直線穴である。

30

#### 【0016】

一態様では、導電性材料はユニタリー単一セグメントである。導電性材料は1つの層のみを含む。

#### 【0017】

一態様では、デバイスは、モバイルデバイス、ハンドヘルドパーソナル通信システム（P C S）ユニット、携帯情報端末、ポータブルデータ端末、全地球測位システム（G P S）対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、固定ロケーション端末、通信デバイス、モバイル電話、スマートフォン、タブレットコンピュータ、コンピュータ、装着型デバイス、モノのインターネット（I o T）デバイス、ラップトップコンピュータ、サーバ、ルー

40

50

タ、自動車に実装される電子デバイスのうちの少なくとも1つを含む群から選択されるデバイスに組み込まれる。

#### 【0018】

別の態様によれば、デバイスは、第1の面と反対側の第2の面とを有する基板を含んでもよい。デバイスは、第1の面から基板内に画定されたキャビティとキャビティのフロアに結合されたダイとをさらに含んでもよい。ダイは、キャビティのフロアに対して遠位側のダイの面上に導電性パッドを有してもよい。デバイスは、基板およびダイを貫通し、基板の第2の面上の導電性パッドと反対側のノードに導電性パッドを結合する相互接続部のための手段をさらに含んでもよい。一例によれば、相互接続部のための手段は、基板の第2の面、ダイ、および導電性パッド内を通って延び、基板の第2の面、ダイ、および導電性パッド内に画定される穴を含んでもよく、この穴内に位置し、基板の第2の面と導電性パッドとの間を、基板の第2の面および導電性パッド内を通って延びる導電性材料をさらに含んでもよい。別の例によれば、相互接続部のための手段は、基板の第2の面、ダイ、および導電性パッド内を通って連続している。さらに別の例によれば、相互接続部のための手段は、基板の第2の面、ダイ、および導電性パッド内を通って延びる直線軸に沿って同心であってもよい。別の例では、相互接続部のための手段は、穴の長さに沿った单一の直線穴を含む。さらに別の例では、相互接続部のための手段は、導電性パッド内から導電性パッドに結合するユニタリー単一セグメントとして形成される導電性材料を含む。

10

#### 【0019】

本明細書で説明する別の態様は、埋込みダイ基板を製作する方法を提供する。この方法は、第1の面と反対側の第2の面とを有する基板を用意するステップを含む。この方法は、第1の面から基板内に画定されるキャビティを形成するステップをさらに含む。この方法は、キャビティのフロアにダイを結合するステップであって、ダイがキャビティのフロアに対して遠位側のダイの面上に導電性パッドを有する、ステップをさらに含む。一態様では、この方法は、基板の第2の面、ダイ、および導電性パッド内を通って延び、基板の第2の面、ダイ、および導電性パッド内に画定される穴をドリリングするステップをさらに含む。この方法は、基板の第2の面とダイと導電性パッドとの間を、基板の第2の面、ダイ、および導電性パッド内を通って延び、穴内から導電性パッドに結合する導電性材料によって穴をめっきしおよび／または充填するステップをまたさらに含む。

20

#### 【0020】

30

いくつかの実装形態では、ダイは、キャビティのフロアに結合され、その後穴がドリリングされる。一態様では、穴のドリリングは1度に実行される。したがって、この穴は、1回のプロセスにおいて基板の第2の面、ダイ、および導電性パッドを貫通するようにドリリングされる。一態様では、この穴は、基板の第2の面、ダイ、および導電性パッド内を通って延びる直線軸に沿って同心であるように形成される。一態様では、この穴は、穴の長さに沿った单一の直線穴であるように形成される。

#### 【0021】

一態様では、導電性材料はユニタリー単一セグメントとして形成される。いくつかの実装形態では、基板の第2の面とダイと導電性パッドとの間を、基板の第2の面、ダイ、および導電性パッド内を通って延びる導電性材料は、1つだけの層として形成される。別の態様では、この方法は、基板の第2の面に積層を結合するステップであって、穴が、積層内を通って延びて積層内に画定されるようにさらにドリリングされ、導電性材料が、積層内を通ってさらに延びる、ステップをさらに含んでもよい。

40

#### 【0022】

本明細書で説明する別の態様は、埋込みダイ基板を製作する別の方法を提供する。この方法は、第1の面と反対側の第2の面とを有する基板を用意するステップを含む。この方法は、第1の面から基板内に画定されるキャビティを形成するステップをさらに含む。この方法は、キャビティのフロアにダイを結合するステップであって、ダイがキャビティのフロアに対して遠位側のダイの面上に導電性パッドを有する、ステップをまたさらに含む。この方法は、基板の第2の面に積層を結合するステップをまたさらに含む。一態様では

50

、この方法は、積層、基板の第2の面、ダイ、および導電性パッド内を通って延び、積層、基板の第2の面、ダイ、および導電性パッド内に画定される穴をドリリングするステップをさらに含む。この方法は、積層と基板の第2の面とダイと導電性パッドとの間を、積層、基板の第2の面、ダイ、および導電性パッド内を通って延び、穴内から導電性パッドに結合する導電性材料によって穴をめっきしおよび／または充填するステップをまたさらに含む。

#### 【0023】

いくつかの実装形態では、ダイがキャビティのフロアに結合され、積層が基板の第2の面に結合され、その後穴がドリリングされる。一態様では、穴のドリリングは1度に行われる。一態様では、この穴は、積層、基板の第2の面、ダイ、および導電性パッド内を通って延びる直線軸に沿って同心であるように形成される。一態様では、この穴は、穴の長さに沿った単一の直線穴であるように形成される。10

#### 【0024】

一態様では、導電性材料はユニタリー単一セグメントとして形成される。いくつかの実装形態では、積層と基板の第2の面とダイと導電性パッドとの間を、積層、基板の第2の面、ダイ、および導電性パッド内を通って延びる導電性材料は、1つだけの層として形成される。一例では、導電性材料は、基板の第2の面の遠位側の積層の表面と導電性パッドとの間の相互接続部を形成する。

#### 【0025】

様々な特徴、性質、および利点は、以下に記載された詳細な説明を図面と併せて検討したときに明らかになることがあり、図面全体にわたって、同様の参照符号はそれに対応して同一視する。20

#### 【図面の簡単な説明】

#### 【0026】

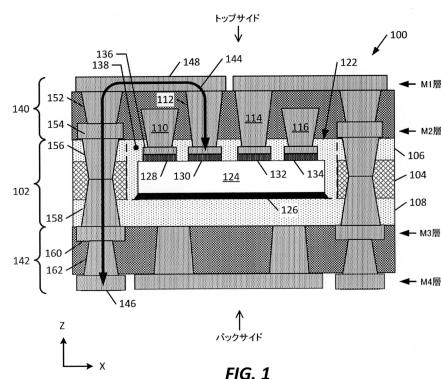

【図1】1手法による第1の種類のダイを実装する埋込みダイ基板（EDS）の一例の断面図である。

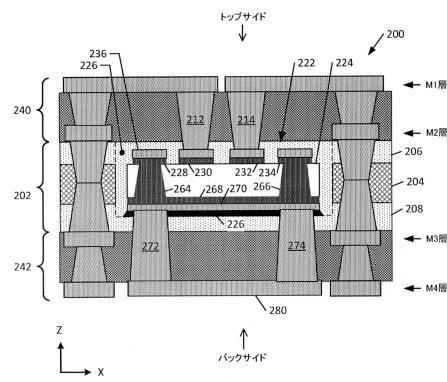

【図2】別の手法による第2の種類のダイを実装するEDSの一例の断面図である。

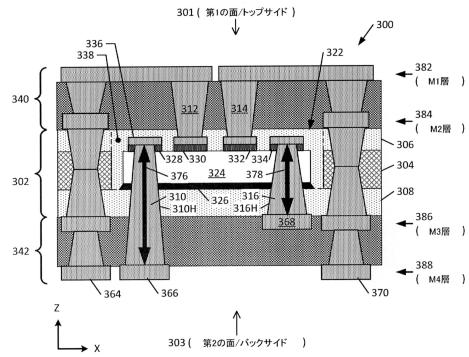

【図3】本明細書で説明する態様による第1の単一セグメントダイ貫通相互接続部と第2の単一セグメントダイ貫通相互接続部とを含むEDSの断面図である。

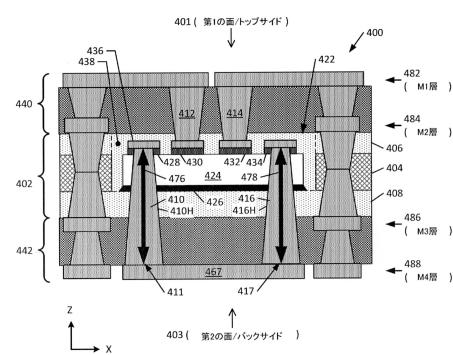

【図4】本明細書で説明する態様による第1の単一セグメントダイ貫通相互接続部と第2の単一セグメントダイ貫通相互接続部とを含む別のEDSの断面図である。30

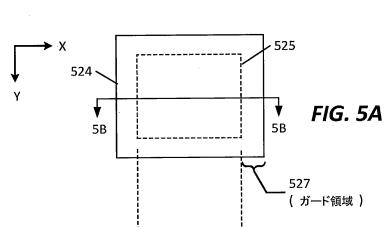

【図5A】本明細書で説明する態様によるEDSに設置される場合があるダイのバックサイド平面図である。

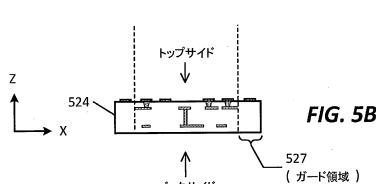

【図5B】線5B - 5Bに沿った図5Aのダイの断面図である。

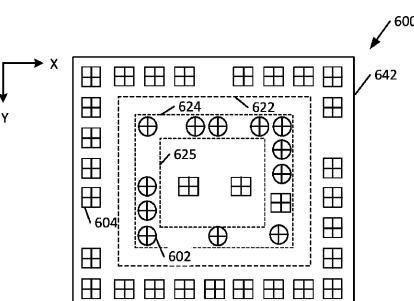

【図6A】本明細書で説明する態様による単一セグメントダイ貫通相互接続部を形成するために事前指定された第1の位置を有する第1のEDSのバックサイド平面図である。

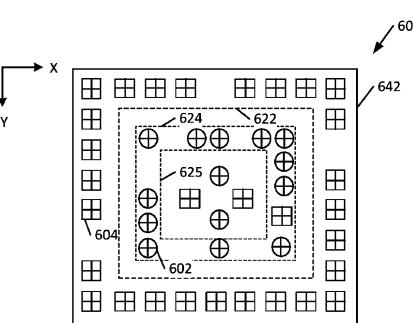

【図6B】本明細書で説明する態様による単一セグメントダイ貫通相互接続部を形成するために事前指定された第1の位置を有する第2のEDSのバックサイド平面図である。

【図7】本明細書で説明する態様による単一セグメントダイ貫通相互接続部を含むEDSを提供する／製作するための段階の例示的なシーケンスを示す図である（図7A～図7Cを含む）。40

【図8】本明細書で説明する態様による単一セグメントダイ貫通相互接続部を含むEDSを製作するための例示的な方法の流れ図である。

【図9】本明細書で説明する態様による単一セグメントダイ貫通相互接続部を含むEDSを製作するための例示的な方法の別の流れ図である。

【図10】本明細書で説明する態様による単一セグメントダイ貫通相互接続部を含むEDSを製作するための例示的な方法の別の流れ図である。

【図11】単一セグメントダイ貫通相互接続部を含む前述のEDSのいずれかと統合されることがある様々な電子デバイスを示す図である。

#### 【発明を実施するための形態】

10

20

30

40

50

**【 0 0 2 7 】**

以下の説明では、本開示の様々な態様を完全に理解できるように、具体的な詳細が与えられる。しかしながら、態様がこれらの具体的な詳細なしに実践される場合があることが、当業者によって理解されよう。たとえば、回路は、不必要的詳細で態様を曖昧にすることを避けるために、ブロック図で示されることがある。他の事例では、よく知られている回路、構造、および技法は、本開示の態様を曖昧にしないために、詳細に示されないことがある。

**【 0 0 2 8 】**

いくつかの実装形態では、ダイの高さは、本開示の図に示す、ダイのZ方向に沿って規定されてもよい。いくつかの実装形態では、ダイのZ方向は、ダイの第1の面（たとえば、トップサイド）と反対側の第2の面（たとえば、バックサイド）との間の軸に沿って画定されてもよい。トップサイド（または上）およびバックサイド（または底）という用語は任意に割り当てられてもよいが、一例として、ダイのトップサイド面は、入力／出力接続パッドの大部分を含む部分であってもよく、一方、ダイのバックサイド面は、基板に接合されるか、接着されるか、またはその他の方法で取り付けられる部分であってもよい。いくつかの実装形態では、ダイのトップサイド部分がダイのバックサイドであってよく、ダイのバックサイド部分がダイのトップサイドであってもよい。トップサイド部分がより低いバックサイド部分に対してより高い部分であってもよい。バックサイド部分がより高いトップサイド部分に対してより低い部分であってもよい。トップサイド部分およびバックサイド部分のさらなる例について以下でさらに説明する。ダイのX-Y方向は、ダイの横方向および／またはフットプリントを指す場合がある。X-Y方向の例について、本開示の図に示し、かつ／または以下でさらに説明する。本開示の図のうちの多くにおいて、EDSのダイおよび各部は、X-Z断面またはX-Z平面を横切って示される場合がある。ただし、いくつかの実装形態では、EDSのダイおよび各部は、Y-Z断面またはY-Z平面を横切って表されることがある。

**【 0 0 2 9 】**

いくつかの実装形態では、相互接続部とは、2つの点、要素、および／または構成要素の間の電気結合および／または熱結合を可能または容易にする、ダイ、EDS、デバイス、またはパッケージの要素または構成要素である。いくつかの実装形態では、相互接続部は、トレースならびに／あるいはめっきされた穴および／または充填された穴（たとえば、ビア）を含んでもよい。いくつかの実装形態では、相互接続部は、直列接続された複数のビアなどのカスケード接続されたセグメント（層）から形成されてもよく、そのような相互接続部は、本明細書ではセグメント化された相互接続部と呼ばれることがある。少なくとも処理時の別個の工程中に別個のセグメントが形成される場合があるので、セグメント化された相互接続部は、セグメント（たとえば、層）間のシームを含んでもよい。したがって、ビアのカスケード接続されたスタックから形成されたセグメント化された相互接続部などのセグメント化された相互接続部は、セグメント化された相互接続部の長さを横切るセグメント化された相互接続部の長さに沿って、セグメント間にシームを有してもよい。これに対して、いくつかの実装形態では、相互接続部が1つのセグメントのみ（たとえば、1つの層のみ）から形成される場合があり、そのような相互接続部は、本明細書では単一セグメント相互接続部と呼ばれる場合がある（すなわち、セグメント化されていない相互接続部）。単一セグメント相互接続部は、単一セグメント相互接続部の長さを横切る単一セグメント相互接続部の長さに沿って、シームを有さない場合がある。いくつかの実装形態では、相互接続部は、第1のノードから第2のノードへの信号（たとえば、データ信号、接地信号、電力信号）のための電気経路を形成するように構成されてもよい導電性の材料によって製作されてもよい。いくつかの実装形態では、相互接続部は、第1のノードから第2のノードへの熱経路を形成するように構成されてもよい熱伝導性材料によって製作されてもよい。相互接続部は、導電性および／または熱伝導性を有してもよい。相互接続部は、回路の一部であってもよい。導電性材料の例の非排他的リストは、金、銀、および銅を含む。導電性材料は、導電性ペーストであってもよい。

10

20

30

40

50

**【 0 0 3 0 】**

本明細書で使用されるドリリング（たとえば、穴を掘ること）は、たとえば、フォトリソグラフィプロセス、機械的プロセス、および／またはレーザードリリングプロセスを含むプロセスによって実施されてもよい。

**【 0 0 3 1 】**

本明細書で使用される穴は、対象物内に形成された側壁によって画定された対象物におけるキャビティ、開口部、または空隙であってもよい。

**【 0 0 3 2 】**

多層デバイスでは、最上メタライゼーション層を第1のメタライゼーション層または“M1”層として特定するのが通例である。各下部メタライゼーション層は通例1ずつ増分される。本明細書で提示する例示的なEDSは、4つのメタライゼーション層（M1、M2、M3、M4）を含むように示されている。しかし、本明細書で説明する様態によるEDSは、任意の数のメタライゼーション層を備えてもよい。本明細書では、EDSのメタライゼーション層の数を制限することは意図されていない。10

**【 0 0 3 3 】****概要**

いくつかの特徴は、向かい合う誘電体層間にはさまれた導電層を有する基板と、基板内のキャビティと、キャビティ内で基板に取り付けられたダイと、基板の両側で誘電体層と貼り合わせられたプリプレグ層とを含む埋込みダイ基板（EDS）に関する。少なくとも1つの単一セグメント相互接続部（たとえば、ある連続的な長さのある導電性材料によってめっきされおよび／または充填された穴）が、EDSのバックサイドのプリプレグ層、基板の誘電体層を貫通してダイ内部に延びている。単一セグメント相互接続部は、ダイの第1の面（たとえば、トップサイド）上の導電性パッドをプリプレグ層の反対側の第2の面（たとえば、バックサイド）上の導電性パッドに電気的および／または熱的に結合することができる。ダイの一部を含む単一セグメント相互接続部は、ダイがキャビティ内で基板に結合され（取り付けられ）た後にEDSのバックサイドドリリングプロセスの間に形成されてもよい。EDSのバックサイドドリリングプロセスの間に事前指定された位置に単一セグメント相互接続部（ダイ内の部分を含む）を形成すると、たとえば、EDSにおける事前指定された位置に対応する位置にあらかじめ形成された基板貫通ビア（TSV）を含むダイを使用する場合と比較して、ダイのコストを削減し、ダイをEDSに組み込むコストを削減することができる。さらに、EDSのバックサイドドリリングプロセスの間に事前指定された位置に単一セグメント相互接続部（ダイ内の部分を含む）を形成すると、熱放散接地抵抗を最小限に抑える材料を選択することができる1つの導電材料によって単一セグメント相互接続部をその全長に沿って製作することが可能になる。2030

**【 0 0 3 4 】****例示的な埋込みダイ基板ダイタイプ**

EDSは一般に、2種類のダイのうちの一方を使用する。第1の種類のダイは、ダイのトップサイド面上に入力／出力／接地／電力パッドを有する。EDSにおいて第1の種類のダイを使用すると、配線に関する問題が生じる。すべての配線は、ダイのトップサイド面から始まる（または終わる）ことができる。第1の種類のダイの下方のEDSの層への配線は、ダイから上にダイを越えて配線されるトレースを使用してもよい。トレースをダイから上にダイを越えて配線することは、2次元空間と3次元空間のどちらでも困難である場合がある。配線問題を解決するうえで伴う余分な時間によって、全体的な構成のコストが増すことがある。トレースを追加すると、メタライゼーションの開路または短絡の可能性が増すことに起因して信頼性が低下することがある。さらに、EDSにおいて第1の種類のダイを使用すると、性能が悪影響を受ける場合があり、少なくとも部分的に、トレースが遠回りに配線されることに起因してEDSの熱的要件および／または電気的要件が満たされなくなることがある。たとえば、メタライゼーションの配線が長いと、EDS内のダイから熱を除去することが困難になる場合がある。さらに、メタライゼーションの配線が長いと、不要な電磁エネルギーが、メタライゼーションに結合し、それによってダイ4050

の内部回路に到達し、ダイの動作に干渉する可能性が高くなる。

#### 【0035】

第2の種類のダイは、ダイのバックサイド面上に少なくともいくつかの入力／出力／接地／電力パッドに到達する場合がある。バックサイド面からパッドへの到達は、ダイにおける基板貫通ビア（TSV）（シリコン貫通ビアとも呼ばれる）を使用することによって実現される。TSVは、トップサイドパッドをバックサイドパッドと相互接続することができる。TSVは、ダイにおける2つの電気ノード間の垂直電気接続部として概念化されてもよい。2つの互いに向かい合う外面を有するダイの場合、第1のノードがダイの第1の（たとえば、トップサイド）面上に位置してもよく、一方、第2のノードがダイの第2の（たとえば、バックサイド）面上に位置してもよい。そのような場合、TSVは、ダイを完全に通過してもよい。10

#### 【0036】

ダイのTSVは、鋳物工場におけるダイ製作時に形成される。本明細書で使用する「鋳物工場」という用語は、半導体製作設備または半導体集積回路を製造する場所を指す。鋳物工場においてダイにおけるTSVを製作すると、少なくともダイマスク数の増加およびTSVを有するダイを製作するのに使用される工程の数の増加に起因してダイのコストが増す。鋳物工場においてダイにTSVを組み込むと、歩留まりに関連するコストが生じる。20。鋳物工場において製作されるTSVのいくつかは、適切に製作されないことがある。たとえば、TSV内に開路が生じることがあり、それによって、ダイの第1の面上の第1のノードがダイの第2の面上の第2のノードに接続されなくなる。鋳物工場において製作されるTSVに関連するエラーに起因して、歩留まりが低下することがあり、コストが生じる場合がある。

#### 【0037】

EDSにおいて第2の種類のダイ（すなわち、TSVを有するダイ）を使用すると、ダイにTSVが組み込まれることに起因してダイのコストが高くなる（すなわち、TSVを有するように製作されるダイは、TSVを有さないように製作されるダイよりもコストが高い）。TSVを有するように製作されるダイでは、ダイのトップサイドパッドとバックサイドパッドとの両方に、EDS組込み時にレーザーストップとして働くように金属めっきを使用するので、追加のコストが生じる。さらに、金から形成されるTSVに関連して、金製TSVに関連する熱伝導は、銅によってもたらされる熱伝導ほど良好ではない。30したがって、TSVを有するダイを使用するEDSにおける熱放散接地抵抗は、望まれるほど低くならない。

#### 【0038】

例示的な埋込みダイ基板（EDS）

図1は、1手法による第1の種類のダイ124（たとえば、TSVを有さないダイ）を実装する埋込みダイ基板（EDS）100の一例の断面図である。EDS100は、中央導電層104と、トップサイド誘電体層106と、バックサイド誘電体層108とを含むコア基板102を含むことができる。

#### 【0039】

ダイ124を保持するためのキャビティ122は、トップサイド誘電体層106および中央導電層104内に形成することができる。キャビティ122の底部は、キャビティ122の「フロア」と呼ばれることがある。ダイ124は、キャビティ122のフロアに結合されてもよい（たとえば、キャビティ122内のバックサイド誘電体層108に結合される）。キャビティ122は、フィラー材料138によって充填されてもよい。40

#### 【0040】

ダイ124は、ダイ124のトップサイド面上に第1の導電性パッド128、第2の導電性パッド130、第3の導電性パッド132、および第4の導電性パッド134を含む複数の導電性パッド128、130、132、134を含んでもよい。図1のダイ124はTSV（たとえば、ダイ製作時に鋳物工場においてダイの本体内に形成されるビア）を含まない。複数の導電性パッド128、130、132、134の各々に保護導電層1350

6が設けられてもよい。

**【0041】**

トップサイド誘電体層106にトップサイド積層140が設けられてもよい。バックサイド誘電体層108にバックサイド積層142が設けられてもよい。

**【0042】**

図1の例示的な図では、ダイ124のトップサイド上の複数の導電性パッド128、130、132、134のうちの1つが、ダイ124の下方のEDS100の層におけるノード（たとえば、導電性パッドまたはトレース）に接続されてもよい。第2の導電性パッド130とバックサイド積層142のバックサイド上のノード146との間の（電気エネルギーおよび熱エネルギー用の）例示的な配線経路144が、両矢印によって示されている。10

**【0043】**

トップサイドドリリングを使用してダイ124のトップサイドのダイ124の第2の導電性パッド130に到達してもよい。トップサイドドリリングは、トップサイド積層140、およびキャビティ122を充填するために使用されるフィラー材料138内を通って延びてもよい。トップサイドドリリングにレーザードリルが使用されてもよい。レーザーストップを目的として、保護導電層136は、ダイ124の第2の導電性パッド130を保護する。レーザーストップ（たとえば、保護導電層136）は、レーザードリルが第2の導電性パッド130を貫通してダイ124に進入するのを阻止する。バックサイドドリリングは、ノード146（たとえば、パッドまたはトレース）からコア基板102の中央導電層104に向かう経路を開放してもよい。20

**【0044】**

第2の導電性パッド130とノード146（たとえば、パッドまたはトレース）との間の導電性経路を実現するには、ダイ124の上および周りにメタライゼーションを配線することができる。メタライゼーションは、相互接続部112を介して（トップサイド積層140を介して）配線することができる。メタライゼーションは次いで、横方向においてダイ124の縁部を越えて、導電性トレース148によって形成される相互接続部の一部に沿って配線することができる。メタライゼーションは次いで、下方にダイを越えて、ピアおよびパッドの複数の垂直セグメント（たとえば、実質的にZ軸に沿って揃えられたセグメント）を貫通するように配線することができる。たとえば、メタライゼーションは、第1のピアセグメント152、第1のパッド154、第2のピアセグメント156、第3のピアセグメント158、第2のパッド160、および第4のピアセグメント162を貫通し、その後バックサイド積層142のノード146に接合するように配線することができる。任意の2つ以上の結合されたピアセグメントは、本明細書では「セグメント化された相互接続部」と呼ばれることがある。前述のメタライゼーションの遠回りの配線は、計画および実装が困難である場合がある。この遠回りの配線によって、EDS100の製作コストが増すことがあり、EDS100が電気的要件および/または熱的要件を満たさなくなる場合がある。30

**【0045】**

図2は、別の手法による第2の種類のダイ224（たとえば、TSVを有するダイ）を実装する埋込みダイ基板（EDS）200の一例の断面図である。EDS200は、中央導電層204と、トップサイド誘電体層206と、バックサイド誘電体層208とを含むコア基板202を含むことができる。40

**【0046】**

ダイ224を保持するためのキャビティ222は、トップサイド誘電体層206および中央導電層204内に形成することができる。キャビティ222の底部は、キャビティ222の「フロア」と呼ばれることがある。ダイ224は、キャビティ222のフロアに結合されてもよい（たとえば、キャビティ222内のバックサイド誘電体層208に結合される）。キャビティ222は、フィラー材料238によって充填されてもよい。

**【0047】**

ダイ224は、ダイ224のトップサイド面上に第1の導電性パッド228、第2の導電性パッド230、第3の導電性パッド232、第4の導電性パッド234を含む複数の導電性パッド228、230、232、234を含んでもよい。図2のダイ224は、第1の基板貫通ビア(TSV)264と第2のTSV266とを含む。第1のTSV264および第2のTSV266は、ダイ製作時に鑄物工場においてダイ224の本体内に形成されるビアであってもよい。複数の導電性パッド228、230、232、234の各々にトップサイド保護導電層236が設けられてもよい。

#### 【0048】

トップサイド誘電体層206にトップサイド積層240が設けられてもよい。バックサイド誘電体層208にバックサイド積層242が設けられてもよい。

10

#### 【0049】

図2の例示的な図では、第1のTSV264に結合された第1の導電性パッド228と、第2のTSV266に結合された第4の導電性パッド234とを有するダイ224が鑄物工場において製作される。第1のTSV264および第2のTSV266は、バックサイド導電性パッド268に結合される。すなわち、ダイ224は、ダイ224の本体内の第1のTSV264と第2のTSV266とを含む。第1のTSV264および第2のTSV266は、鑄物工場におけるダイ製作時にダイ224の本体内に形成された。そのような構成では、第1の導電性パッド228、第1のTSV264、第4の導電性パッド234、第2のTSV266、およびバックサイド導電性パッド268は金から形成されてもよい。

20

#### 【0050】

ダイ224のトップサイドのレーザーストップを目的として、トップサイド保護導電層236が、複数の導電性パッド228、230、232、234を保護する。たとえば、トップサイドドリリングプロセスにおいて、レーザーストップ(たとえば、トップサイド保護導電層236)は、レーザードリルが第2の導電性パッド230を貫通してダイ224に進入するのを阻止する。

#### 【0051】

ダイ224のバックサイドのレーザーストップを目的として、バックサイド保護導電層270が、バックサイド導電性パッド268を保護する。バックサイド保護導電層270をダイ224に追加すると、ダイ224のコストが増す。バックサイド保護導電層270は、EDS200のバックサイドからコア基板202の中央導電層204に向かうレーザードリリングによって形成される穴のためのレーザーストップとして働く。

30

#### 【0052】

相互接続部272、274は、EDS組込み時のバックサイドドリリングプロセス中に形成されてもよく、ダイ224内には延びずおよび/またはダイ224内を通って延びることがない。相互接続部は、たとえば、EDS組込み時にダイ224に穴(たとえば、ダイ内まで延びおよび/またはこのダイ内を通って延びる穴、ダイを貫通する穴)をドリリングすると、ダイ224を損傷する恐れがあるので、バックサイド導電性パッド268上に形成されたバックサイド保護導電層270(レーザーストップ層)において停止する。たとえば、EDS組込み時にダイ224を交換することは不可能である場合があるので、EDS組込み時にダイ224を損傷しないことが望ましい。ダイを損傷すると、EDS200が完全に失われる。

40

#### 【0053】

EDS200に第2の手法を使用するにはコストがかかる場合がある。TSVを有するダイは、TSVを有さないダイよりもコストが高い。さらに、上述のように、第1のTSV264および第2のTSV266は金から形成されてもよい。これに対して、相互接続部272、274は銅から形成されてもよい。金の熱伝導率は銅の熱伝導率よりも低い。したがって、ダイ224からたとえばバックサイド積層242のバックサイドのパッドまたはトレース280への熱エネルギーの伝達は最適ではない。

#### 【0054】

50

図 1 および図 2 に示す例示的な手法に対して、（鑄物工場で行われるのではない）E D S 組込み時のダイ内へのバックサイドドリリングによってダイ内に形成される少なくとも 1 つの単一セグメントダイ貫通相互接続部を有する例示的な E D S は、鑄物工場 T S V コストを減らすことによってコストを節約する場合があり、バックサイドドリリングに関するバックサイド銅めっきコストを減らすことがあり、金よりも高い熱伝導率を有する銅などの導体で全体的に形成された単一セグメントダイ貫通相互接続部を使用することによって性能を向上させることがある。

#### 【 0 0 5 5 】

改良された例示的な埋込みダイ基板（E D S）

図 3 は、本明細書で説明する態様による第 1 の単一セグメントダイ貫通相互接続部 3 1 0 と第 4 の単一セグメントダイ貫通相互接続部 3 1 6 を含む E D S 3 0 0 の断面図を示す。

#### 【 0 0 5 6 】

「単一セグメント」構造という用語は、本明細書では、ユニタリー構造、不可分構造、および / または未分割構造を表すために使用されることがある。本明細書で使用する「単一セグメントダイ貫通相互接続部」という用語は、本明細書では、ユニタリー相互接続部、不可分相互接続部、および / または未分割相互接続部を表すために使用されることがある、この場合、相互接続部の一部は、E D S 3 0 0 の 1 つの層（たとえば、基板層、誘電体層、積層）および E D S 3 0 0 のダイ 3 2 4 の少なくとも一部内を通って延びる（たとえば、それを貫通する、それを貫く、それに入り込む、それを通過する、それに進入する）。単一セグメントダイ貫通相互接続部の一例は、規定された非ゼロ高さを有する側壁を有する柱状構造、めっきされた穴、および / または第 1 の端部（たとえば、第 2 の積層 3 4 2（たとえば、バックサイド積層）もしくは第 2 の誘電体層 3 0 8 の所の第 1 の端部および / または第 2 の積層 3 4 2 もしくは第 2 の誘電体層 3 0 8 内の第 1 の端部）と、第 2 の遠位端部（たとえば、第 1 の端部の終端、E D S 3 0 0 のダイ 3 2 4 の第 1 の導電性パッド 3 2 8 の所の第 2 の端部および / または第 1 の導電性パッド 3 2 8 内の第 2 の端部、あるいは第 1 の導電性パッド 3 2 8 上に設けられた保護導電層 3 3 6（たとえば、レーザーストップ、金属層、銅層）の所の第 2 の端部および / または保護導電層 3 3 6 内の第 2 の端部）とを有する 1 つの導電性材料から形成された充填された穴を含んでもよい。本明細書で使用される単一セグメントダイ貫通相互接続部（たとえば、第 1 の単一セグメントダイ貫通相互接続部 3 1 0）は、たとえば、E D S 3 0 0 の基板 3 0 2 を介して E D S 3 0 0 のダイ 3 2 4 内およびダイ 3 2 4 の導電性パッド 3 2 8 内に第 1 の穴 3 1 0 H をドリリングし、第 1 の穴 3 1 0 H 内から導電性パッド 3 2 8 に結合する 1 つの導電性材料によって第 1 の穴 3 1 0 H をめっきしおよび / または充填することによって形成されてもよい。導電性材料は、第 1 の穴 3 1 0 H の側壁をめっきしおよび / または第 1 の穴 3 1 0 H を完全に充填してもよい。いくつかの実装形態では、第 1 の穴 3 1 0 H は、一定の直径または線形に減少する直径を有してもよい（たとえば、穴が全長に沿って一定の直径または線形に減少する直径を有するように穴のドリリングが実施される）。

#### 【 0 0 5 7 】

いくつかの実装形態では、E D S 3 0 0 の単一セグメントダイ貫通相互接続部の断面分析または並列ラッピング（p - ラッピング）では層の形成（たとえば、複数のセグメントを備える導電層）は検出されない。いくつかの実装形態では、本明細書で説明する態様による単一セグメントダイ貫通相互接続部は、たとえば、複数の接合された（たとえば、突き合わされた）ビアのスタックとは異なり、1 つのセグメント（たとえば、層）のみを含む。

#### 【 0 0 5 8 】

第 1 の単一セグメントダイ貫通相互接続部 3 1 0 は、その全長に沿って導電性材料によってめっきされおよび / または充填されてもよい。いくつかの実装形態では、1 つの導電性材料のみが使用される。言い換えれば、いくつかの実装形態では、単一セグメントダイ貫通相互接続部 3 1 0 の全長に沿って 1 つの導電性材料が分散される。1 つの導電性材料

10

20

30

40

50

が、ユニタリー構造、不可分構造、および／または未分割構造を形成してもよい。いくつかの実装形態では、導電性材料は銅であってもよい。いくつかの実装形態では、導電性材料は、導電性ペーストであってもよい。第1の単一セグメントダイ貫通相互接続部310は、ダイ324が基板302に結合された（たとえば、物理的に取り付けられた）後にE D S 3 0 0 のバックサイドドリリングプロセスの間に形成されてもよい。いくつかの実装形態では、E D S 3 0 0 において使用されるダイ324は、鋳物工場において第1の単一セグメントダイ貫通相互接続部310用に事前指定された位置にT S Vを設けずに作製されてもよい。

#### 【0059】

E D S 3 0 0 は、基板302を含んでもよい。基板302は、第1の面301と反対側の第2の面303とを有してもよい。基板302は、コア基板であってもよい。基板302は、基板302の第1の面301における第1の誘電体層306と基板302の第2の面303における第2の誘電体層308との間にはさまれた導電層304を含んでもよい。導電性層304は、銅などの金属から形成されてもよい。導電層304は、E D S 3 0 0 内の他の導電層（たとえば、M1層382、M2層384、M3層386、M4層388）よりも厚くてもよい。導電層304の厚さは、E D S 3 0 0 に剛性および／または構造的支持をもたらすことがある。導電層304は、E D S 3 0 0 の接地平面または電力面として使用されてもよい。

#### 【0060】

代替態様では、基板302は、コア基板であってもよい。代替態様では、基板302は、基板302の第1の面301における第1の導電層（図示せず）と基板302の第2の面303における第2の導電層（図示せず）との間にはさまれた誘電体層（図示せず）を含んでもよいことが企図される。言い換えれば、代替態様では、基板302は、両側を導電層で覆われた非導電性誘電体層を有してもよい。誘電体の各側の導電層への短絡を防止するために、様々な層内を通って延びる相互接続部の周りに適切な絶縁体が形成されてもよい。

#### 【0061】

基板302内にキャビティ322が形成されてもよい。本明細書で説明するように、キャビティ322は、基板302内の側壁によって画定される開口部または空隙であってもよい。キャビティ322は、基板302の第1の面301から基板302内に画定されてもよい。キャビティ322は、基板内に形成されてもよい。キャビティ322は、ダイ324を保持するのに十分な大きさを有してもよい。キャビティ322は、たとえば、フォトリソグラフィックプロセス、機械的プロセス、および／またはレーザードリリングプロセスを含む方法によって形成されてもよい。キャビティ322の底部は、キャビティ322の「フロア」と呼ばれることがある。いくつかの実装形態では、キャビティ322は、第1の誘電体層306および導電層304を含んでいなくともよく、キャビティ322のフロアは、キャビティ322内に露出された第2の誘電体層308によって画定されてもよい。

#### 【0062】

ダイ324は、能動および／または受動回路／構成要素を含んでもよい。ダイ324は、一般にピックアンドプレスマシン、ダイボンディングマシン、またはチップショーターと呼ばれる表面実装技術（S M T）構成要素配置システムを使用してキャビティ322のフロアに結合されてもよい（たとえば、キャビティ322内の第2の誘電体層308に結合されてもよい）。ダイ324は、たとえば、接着剤、はんだ、またはエポキシ326を使用してキャビティ322のフロアに結合されてもよい。

#### 【0063】

ダイ324は、キャビティ322のフロアに対して遠位側のダイ324の面上に第1の導電性パッド328、第2の導電性パッド330、第3の導電性パッド332、および第4の導電性パッド334を含む複数の導電性パッド328、330、332、334を含んでもよい。図3における例示的な図のダイ324は、ダイ324の製作時に鋳物工場に

10

20

30

40

50

おいてダイ324内に形成された基板貫通ビア(TSV)を示していない。いくつかの実装形態では、ダイ324は、製作時に铸物工場においてダイ324内に形成された1つまたは複数のTSVを含んでもよい。ただし、第1の単一セグメントダイ貫通相互接続部310および第4の単一セグメントダイ貫通相互接続部316などの単一セグメントダイ貫通相互接続部用に事前指定された位置にはTSVは含まれない。

#### 【0064】

複数の導電性パッド328、330、332、334は、任意の導電性材料(たとえば、金)から形成されてもよい。複数の導電性パッド328、330、332、334の各々に保護導電層336が印刷されてもよく、堆積されてもよく、形成されてもよく、または他の方法で設けられてもよい。保護導電層336は、第1の単一セグメントダイ貫通相互接続部310、第2の相互接続部312、第3の相互接続部314、および/または第4の単一セグメントダイ貫通相互接続部316の一部を形成する際にレーザードリリングが使用される場合にレーザーストップとして使用されてもよい。10

#### 【0065】

キャビティ322は、ダイ324をカプセル化し、保護し、および/または不動化するためにフィラー材料338によって充填されている。フィラー材料338は、たとえば、カプセル化材料、すなわち、第1の誘電体層306を形成するために使用される材料、または第1の誘電体層306のトップサイド面に積層されるプリプレグ材料などのプリプレグ材料であってもよい。

#### 【0066】

第1の誘電体層306に第1の積層340(たとえば、トップサイド積層)が設けられてもよい。第2の誘電体層308に第2の積層342(たとえば、バックサイド積層)が設けられてもよい。第1の積層340および第2の積層342の各々は、プリプレグ(予備含浸された)層と呼ばれることがある。第1の積層340および第2の積層342の各々は、1つまたは複数の誘電および導電層を含んでもよい。プリプレグ層は、たとえば、各層を噴霧によってそれぞれの表面上に堆積させることによって設けられてもよい。当業者には、基板302上にプリプレグ層および/または追加の層を設けるための他の方法(たとえば、積層、接合、取付け、接着、形成)が知られている。20

#### 【0067】

図3の例示的な図では、ダイ324は、第1の単一セグメントダイ貫通相互接続部310および第4の単一セグメントダイ貫通相互接続部316用に事前指定された位置にTSVを設けないように铸物工場において製作されてもよい。他の位置におけるTSVは省略可能である。所与のダイにおけるTSVの数を少なくすると、ダイのコストが削減されることがある。铸物工場におけるダイ製作時に第1の単一セグメントダイ貫通相互接続部310および第4の単一セグメントダイ貫通相互接続部316用に事前指定された位置にTSVを形成するのではなく、基板302およびダイ324の少なくとも一部をバックサイドドリリングすることによって、EDS組込み時に第1の単一セグメントダイ貫通相互接続部310および第4の単一セグメントダイ貫通相互接続部316を形成してもよい。30

#### 【0068】

ダイ324の能動回路および/または受動回路に(それぞれ、第1の単一セグメントダイ貫通相互接続部310および第4の単一セグメントダイ貫通相互接続部316に結合することができる)第1の導電性パッド328および第4の導電性パッド334が結合されてもよい。同様に、ダイ324の能動回路および/または受動回路に第2の導電性パッド330および第3の導電性パッド332が結合されてもよい。40

#### 【0069】

第2の相互接続部312および第3の相互接続部314に関連するトップサイドドリリングプロセスに関連して、レーザーストップ(たとえば、保護導電層336)は、レーザードリルによって形成される穴が(金から形成される場合がある)導電性パッド330、332を貫通することおよびダイ324内まで延びることを阻止する。第2の相互接続部312および第3の相互接続部314は、ダイ324内まで延びずおよび/またはダイ350

24内を通って延びることはない。

**【0070】**

バックサイドドリリングプロセスに関連して、第1の単一セグメントダイ貫通相互接続部310および第4の単一セグメントダイ貫通相互接続部316は、ダイ324内まで延びおよび／またはダイ324内を通って延びる。言い換えれば、第1の単一セグメントダイ貫通相互接続部310および第4の単一セグメントダイ貫通相互接続部316は、第2の積層342（必要に応じて）、第2の誘電体層308（たとえば、基板302内に形成されたキャビティ322のフロア）を貫通し、キャビティ322のフロアに結合されたダイ324内に進入しおよび／またはダイ324を貫通するようにドリリングすることによって、それぞれの第1の穴310Hおよび第4の穴316H内に形成されてもよい。

10

**【0071】**

第1の単一セグメントダイ貫通相互接続部310および第4の単一セグメントダイ貫通相互接続部316に関するバックサイドドリリングプロセスに関連して、ダイ324のバックサイドのレーザースポットは存在しないことに留意されたい。そればかりでなく、レーザーストップは、レーザードリルによって実施されるバックサイドドリリングプロセスの間に第1の単一セグメントダイ貫通相互接続部310および第4の単一セグメントダイ貫通相互接続部316の形成を妨げることがある。少なくとも単一セグメントダイ貫通相互接続部を形成するために事前指定された位置のレーザーストップを無くすと、コストが節約されることがある。

**【0072】**

20

図3の例示的な図では、ダイ324のトップサイド上の第2の導電性パッド330および第3の導電性パッド332のうちの1つまたは複数が、ダイ324の下方のEDS300の層における第1のノード364および第4のノード370（たとえば、導電性パッドまたはトレース）に接続されてもよい。そのような接続を実現するための配線経路の例は、上記で図1に関連して提示されており、これについては説明を完結するために繰り返さない。

**【0073】**

第1の単一セグメントダイ貫通相互接続部310を実装することの利点には、第1の導電性パッド328（または第1の導電性パッド328上の保護導電層336）から第2の積層342上のM4層388のパッドまたはトレース366まである導電性材料（たとえば、銅）内を通る伝導経路376が設けられることが含まれる場合がある。伝導経路376は、ダイ324と、ダイ324と第2の積層342との間の基板302の部分を通過することができる。単一セグメントダイ貫通相互接続部310を1つの伝導材料で作ることができるので、伝導材料としては、熱放散接地抵抗を最小限に抑え熱伝導率を最大にする材料を選択することができる。伝導経路376は、図3において両矢印によって示されている。

30

**【0074】**

図3に示す第4の単一セグメントダイ貫通相互接続部316を実装することの利点には、第4の導電性パッド334（または第4の導電性パッド334上の保護導電層336）から第2の誘電体層308上の第3のノード368（たとえば、M3層386の第3のノード368（たとえば、パッド、トレース））までの伝導経路378を含めてもよい。伝導経路378は、ダイ324と、ダイ324と第2の積層342との間の基板302の部分を通過することができる。第4の単一セグメントダイ貫通相互接続部316を1つの伝導材料で作ることができるので、伝導材料としては、熱放散接地抵抗を最小限に抑え熱伝導率を最大にする材料を選択することができる。伝導経路378は、図3において両矢印によって示されている。

40

**【0075】**

本明細書で説明する構造および方法を実施すると、たとえば、第1の導電性パッド328とバックサイドパッドまたはトレース366との間の伝導経路（たとえば、伝導経路376）の熱放散接地抵抗を最小限に抑え、かつ熱伝導率を最大にすることができる。たと

50

えば、銅から形成された第1の単一セグメントダイ貫通相互接続部310を使用すると、(たとえば、図2に関連して説明した例と同様に)銅めっきされたビアセグメント上に積層された金製TSVビアセグメントに対して熱伝導率を約30%向上させることができる。

#### 【0076】

要約すると、一態様によれば、EDS300などのデバイスは、第1の面301および反対側の第2の面303を有する基板302と、第1の面301から基板302内に画定されたキャビティ322と、キャビティ322のフロアに結合され、キャビティ322のフロアに対して遠位側のダイ324の面上に導電性パッド(たとえば、第4の導電性パッド334)を有するダイ324とを含んでもよい。EDS300は、基板302の(たとえば、第2の誘電体層308内の)第2の面303、ダイ324、および導電性パッド(たとえば、第4の導電性パッド334)内を通って延び、基板302の第2の面303、ダイ324、および導電性パッド内に画定された穴(たとえば、第4の穴316H)をさらに含んでもよい。EDS300は、穴(たとえば、第4の穴316H)内に位置し、基板302の(たとえば、第2の誘電体層308内の)第2の面303と導電性パッド(たとえば、第4の導電性パッド334)との間を、基板302の第2の面303および導電性パッド内を通って延びる導電性材料(たとえば、第4の単一セグメントダイ貫通相互接続部316)をさらに含んでもよい。言い換えれば、図3のEDS300のいくつかの実装形態では、穴(たとえば、第4の穴316H)は、基板302の(たとえば、第2の誘電体層308内の)第2の面303、ダイ324、および導電性パッド(たとえば、第4の導電性パッド334)内を通って連続してもよい。いくつかの実装形態では、穴(たとえば、第4の穴316H)は、基板302の(たとえば、第2の誘電体層308内の)第2の面303、ダイ324、および導電性パッド(たとえば、第4の導電性パッド334)内を通って延びる直線軸に沿って同心であってもよい。いくつかの実装形態では、穴(たとえば、第4の穴316H)は、穴(たとえば、第4の穴316H)の長さに沿った単一の直線穴であってもよい。いくつかの実装形態では、(たとえば、第4の単一セグメントダイ貫通相互接続部316を形成する)導電性材料は、ユニタリー単一セグメントであってもよい。いくつかの実装形態では、(たとえば、第4の単一セグメントダイ貫通相互接続部316を形成する)導電性材料は、1つの層のみを含んでもよい。言い換えれば、穴(たとえば、第4の穴316H)内にめっきされおよび/または充填される導電性材料は、単一セグメントダイ貫通相互接続部(たとえば、第4の単一セグメントダイ貫通相互接続部316)として識別されてもよい。

#### 【0077】

要約すると、一態様によれば、EDS300などのデバイスは、第1の面301および反対側の第2の面303を有する基板302と、第1の面301から基板302内に画定されたキャビティ322と、キャビティ322のフロアに結合され、キャビティ322のフロアに対して遠位側のダイ324の面上に導電性パッド(たとえば、第1の導電性パッド328)を有するダイ324とを含nでもよい。EDS300は、キャビティ322のフロアに隣接する、基板302の第2の面303(たとえば、第2の誘電体層308)に結合された積層(たとえば、第2の積層342)をさらに含んでもよい。いくつかの態様では、基板302の第2の面303(たとえば、第2の誘電体層308)は、ダイ324と積層(たとえば、第2の積層342)との間にはさまれてもよい。EDS300は、積層(たとえば、第2の積層342)、基板302の第2の面303(たとえば、第2の誘電体層308)、ダイ324、および導電性パッド(たとえば、第1の導電性パッド328)内を通って延び、積層、基板302の第2の面303、ダイ324、および導電性パッド内に画定された穴(たとえば、第1の穴310H)をさらに含nでもよい。EDS300は、穴(たとえば、第1の穴310H)内に位置し、積層(たとえば、第2の積層342)と基板302の第2の面303(たとえば、第2の誘電体層308)とダイ324と導電性パッド(たとえば、第1の導電性パッド328)との間を、積層、基板302の第2の面303、および導電性パッド内を通って延びる導電性材料(たとえば、第1の单

10

20

30

40

50

一セグメントダイ貫通相互接続部 310 ) をさらに含んでもよい。いくつかの実装形態では、穴(たとえば、第1の穴 310H )は、積層(たとえば、第2の積層 342 )、基板 302 の第2の面 303 (たとえば、第2の誘電体層 308 )、ダイ 324 、および導電性パッド(たとえば、第1の導電性パッド 328 )内を通って連続していてもよい。いくつかの実装形態では、穴(たとえば、第1の穴 310H )は、積層(たとえば、第2の積層 342 )、基板 302 の第2の面 303 (たとえば、第2の誘電体層 308 )、ダイ 324 、および導電性パッド(たとえば、第1の導電性パッド 328 )内を通って延びる直線軸に沿って同心であってもよい。いくつかの実装形態では、穴(たとえば、第1の穴 310H )は、穴(たとえば、第1の穴 310H )の長さに沿った単一の直線穴であってもよい。いくつかの実装形態では、(たとえば、第1の単一セグメントダイ貫通相互接続部 310 を形成する)導電性材料は、ユニタリー単一セグメントであってもよい。いくつかの実装形態では、(たとえば、第1の単一セグメントダイ貫通相互接続部 310 を形成する)導電性材料は、1つの層のみを含んでもよい。言い換えれば、穴(たとえば、第1の穴 310H )内にめっきされおよび / または充填される導電性材料は、単一セグメントダイ貫通相互接続部(たとえば、第1の単一セグメントダイ貫通相互接続部 310 )として識別されてもよい。

#### 【0078】

導電層 304 および / または接着剤、はんだ、もしくはエポキシ 326 への短絡を防止するために、様々な層内を通って延びる相互接続部の周りに適切な絶縁体が形成されてもよい。

10

#### 【0079】

図4は、本明細書で説明する態様による第1の単一セグメントダイ貫通相互接続部 410 と第4の単一セグメントダイ貫通相互接続部 416 とを含む EDS400 の断面図を示す。図3の EDS300 と図4の EDS400 との間の差は、すべての単一セグメントダイ貫通相互接続部が同じ層(たとえば、M4層 488 )に第1の端部 411 、417 を有することである。したがって、図4の態様では、単一セグメントダイ貫通相互接続部(410 、416 )は、単一のバックサイドドリーリングプロセスの間に形成されてもよい。

20

#### 【0080】

EDS400 は、基板 402 を含んでもよい。基板 402 は、第1の面 401 と反対側の第2の面 403 とを有してもよい。基板 402 は、コア基板であってもよい。基板 402 は、基板 402 の第1の面 401 における第1の誘電体層 406 と基板 402 の第2の面 403 における第2の誘電体層 408 との間にはさまれた導電層 404 を含んでもよい。導電層 404 は、銅などの金属で形成されてもよい。導電層 404 は、EDS400 内の他の導電層(たとえば、M1層 482 、M2層 484 、M3層 486 、M4層 488 )よりも厚くてもよい。導電層 404 の厚さは、EDS400 に剛性および / または構造的支持をもたらすことがある。導電層 404 は、EDS400 の接地平面または電力面として使用されてもよい。

30

#### 【0081】

代替態様では、基板 402 は、コア基板であってもよい。代替態様では、基板 402 は、基板 402 の第1の面 401 における第1の導電層(図示せず)と基板 402 の第2の面 403 における第2の導電層(図示せず)との間にはさまれた誘電体層(図示せず)を含んでもよいことが企図される。言い換えれば、代替態様では、基板 402 は、両側を導電層で覆われた非導電性誘電体層を有してもよい。たとえば、誘電体の各側の導電層への短絡を防止するために、様々な層内を通って延びる相互接続部の周りに適切な絶縁体が形成されてもよい。

40

#### 【0082】

基板 402 内にキャビティ 422 が形成されてもよい。本明細書で説明するように、キャビティ 422 は、基板 402 内の側壁によって画定された開口部または空隙であってもよい。キャビティ 422 は、基板 402 の第1の面 401 から基板 402 内に画定されてもよい。キャビティ 422 は、基板内に形成されてもよい。キャビティ 422 は、ダイ 4

50

24を保持するのに十分な大きさを有してもよい。キャビティ422は、たとえば、フォトリソグラフィックプロセス、機械的プロセス、および／またはレーザードリリングプロセスを含む方法によって形成されてもよい。キャビティ422の底部は、キャビティ422の「フロア」と呼ばれることがある。いくつかの実装形態では、キャビティ422は、第1の誘電体層406および導電層404を含んでいなくてもよく、キャビティ422のフロアは、キャビティ422内に露出された第2の誘電体層408によって画定されてもよい。

#### 【0083】

ダイ424は、能動および／または受動回路／構成要素を含んでもよい。ダイ424は、一般にピックアンドプレスマシン、ダイボンディングマシン、またはチップショーターと呼ばれる表面実装技術(SMT)構成要素配置システムを使用して(たとえば、キャビティ422内の第2の誘電体層408に結合された)キャビティ422のフロアに結合されてもよい。ダイ424は、たとえば、接着剤、はんだ、またはエポキシ426を使用してキャビティ422のフロアに結合されてもよい。

10

#### 【0084】

ダイ424は、キャビティ422のフロアの遠位側のダイ424の面上に第1の導電性パッド428、第2の導電性パッド430、第3の導電性パッド432、第4の導電性パッド434を含む複数の導電性パッド428、430、432、434を含んでもよい。図4における例示的な図のダイ424は、ダイ424の製作時に鋳物工場においてダイ424内に形成された基板貫通ビア(TSV)を示していない。いくつかの実装形態では、ダイ424は、製作時に鋳物工場においてダイ424内に形成された1つまたは複数のTSVを含んでもよい。ただし、第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416などの単一セグメントダイ貫通相互接続部用に事前指定された位置にはTSVは含まれない。

20

#### 【0085】

複数の導電性パッド428、430、432、434は、任意の導電性材料(たとえば、金)で形成されてもよい。複数の導電性パッド428、430、432、434の各々に保護導電層436が印刷されてもよく、堆積されてもよく、形成されてもよく、または他の方法で設けられてもよい。保護導電層436は、第1の単一セグメントダイ貫通相互接続部410、第2の相互接続部412、第3の相互接続部414、および／または第4の単一セグメントダイ貫通相互接続部416の一部を形成する際にレーザードリリングが使用される場合にレーザーストップとして使用されてもよい。

30

#### 【0086】

キャビティ422は、ダイ424をカプセル化し、保護し、および／または不動化するためにフィラー材料438によって充填されている。フィラー材料438は、たとえば、カプセル化材料、すなわち、第1の誘電体層406を形成するために使用される材料、または第1の誘電体層406のトップサイド面に積層されるプリプレグ材料などのプリプレグ材料であってもよい。

#### 【0087】

第1の誘電体層406に第1の積層440(たとえば、トップサイド積層)が設けられてもよい。第2の誘電体層408に第2の積層442(たとえば、バックサイド積層)が設けられてもよい。第1の積層440および第2の積層442の各々は、プリプレグ(予備含浸された)層と呼ばれることがある。第1の積層440および第2の積層442の各々は、1つまたは複数の誘電および導電層を含んでもよい。プリプレグ層は、たとえば、各層を噴霧によってそれぞれの表面上に堆積させることによって設けられてもよい。当業者には、基板402上にプリプレグ層および／または追加の層を設けるための他の方法(たとえば、積層、接合、取付け、接着、形成)が知られている。

40

#### 【0088】

図4の例示的な図では、ダイ424は、第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416用に事前指定された位置にTS

50

Vを設けないように鑄物工場において製作することができる。他の位置におけるTSVは省略可能であってもよい。所与のダイにおけるTSVの数を少なくすると、ダイのコストが削減されることがある。鑄物工場におけるダイ製作時に第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416用に事前指定された位置にTSVを形成するのではなく、基板402およびダイ424の少なくとも一部をバックサイドドリリングすることによって、EDS組込み時に第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416を形成してもよい。

#### 【0089】

ダイ424の能動回路および/または受動回路に(それぞれ、第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416に結合することができる)第1の導電性パッド428および第4の導電性パッド434が結合されてもよい。同様に、ダイ424の能動回路および/または受動回路に第2の導電性パッド430および第3の導電性パッド432が結合されてもよい。

10

#### 【0090】

第2の相互接続部412および第3の相互接続部414に関連するトップサイドドリリングプロセスに関連して、レーザーストップ(たとえば、保護導電層436)は、レーダードリルによって形成される穴が(金から形成される場合がある)導電性パッド430、432およびダイ424を貫通することを阻止する。第2の相互接続部412および第3の相互接続部414は、ダイ424内まで延びずおよび/またはダイ424内を通って延びることはない。

20

#### 【0091】

バックサイドドリリングプロセスに関連して、第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416は、ダイ424内に延びおよび/またはダイ424内を通って延びる。言い換えれば、第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416は、第2の積層442、第2の誘電体層408(たとえば、基板402内に形成されたキャビティ422のフロア)を貫通し、キャビティ422のフロアに結合されたダイ424内に進入しおよび/またはダイ424を貫通するようにドリリングすることによって、それぞれの第1の穴410Hおよび第4の穴416H内に形成されてもよい。

30

#### 【0092】

第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416に関連するバックサイドドリリングプロセスに関連して、ダイ424のバックサイドのレーザーストップは存在しないことに留意されたい。そればかりでなく、レーザーストップは、レーダードリルによって実施されるバックサイドドリリングプロセスの間に第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416の形成を妨げることがある。少なくとも単一セグメントダイ貫通相互接続部を形成するために事前指定された位置のレーザーストップを無くすと、コストが節約されることがある。

40

#### 【0093】

第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416を実装することの利点には、1つの導電性材料(たとえば、銅)内を通る伝導経路476、478を設けることを含んでもよい。第1の単一セグメントダイ貫通相互接続部410に関連する伝導経路476は、第1の導電性パッド428(または第1の導電性パッド428上の保護導電層436)から第2の積層442上のM4層488のパッドまたはトレース467まで延びることができる。第4の単一セグメントダイ貫通相互接続部416に関連する伝導経路478は、第4の導電性パッド434(または第4の導電性パッド434上の保護導電層436)から第2の積層442上の同じM4層488のパッドまたはトレース467まで延びることができる。伝導経路476、478は、ダイ424と、ダイ424と第2の積層442との間の基板402の部分と、第2の積層4

50

42とを通過することができる。第1の単一セグメントダイ貫通相互接続部410および第4の単一セグメントダイ貫通相互接続部416を1つの伝導材料で作ることができるので、伝導材料としては、熱放散接地抵抗を最小限に抑え熱伝導率を最大にする材料を選択することができる。伝導経路476、478は、図4において両矢印によって示されている。

#### 【0094】

本明細書で説明する構造および方法を実施すると、たとえば、トップサイド導電性パッド（たとえば、第1の導電性パッド428、第4の導電性パッド434）と第2の積層442上のパッドまたはトレース467との間の伝導経路（たとえば、伝導経路476、478）の熱放散接地抵抗を最小限に抑え、かつ熱伝導率を最大にすることができる。たとえば、銅から形成された単一セグメントダイ貫通相互接続部（たとえば、410、416）を使用すると、（たとえば、図2に関連して説明した例と同様に）銅めっきされたビアセグメント上に積層された金製TSVビアセグメントに対して熱伝導率を約30%向上させることができる。

10

#### 【0095】

導電層404および/または接着剤、はんだ、もしくはエポキシ426への短絡を防止するために、様々な層内を通って延びる相互接続部の周りに適切な絶縁体が形成されてもよい。

#### 【0096】

図5Aは、本明細書で説明する態様によるEDSに設置される場合があるダイ524のバックサイド平面図を示す。たとえば、ダイ524は、図3、図4、図6A、および/または図6BのEDSに設置されてもよい。ダイ524は、能動回路および/または受動回路が存在する領域525をダイ524の縁部の内側に有してもよい。能動回路および/または受動回路が存在する領域525の縁部は、図5Aにおいて点線によって区画されている。ダイ524の縁部と能動回路および/または受動回路が存在する領域525の縁部との間のガード領域527が確立されてもよい。いくつかの実装形態では、ガード領域527には回路がほとんど存在しない。

20

#### 【0097】

図5Bは、線5B-5Bに沿った図5Aのダイ524の断面図を示す。図5Bは、ガード領域527には回路がほとんど存在しないことを示す。いくつかの実装形態では、ガード領域527内に単一セグメントダイ貫通相互接続部が配置されてもよい。しかし、ダイ524上のどこかに単一セグメントダイ貫通相互接続部が配置されてもよい。

30

#### 【0098】

図6Aは、単一セグメントダイ貫通相互接続部を形成するために事前指定された第1の位置602を有する第1のEDS600のバックサイド平面図を示す。点線は、能動回路および/または受動回路が存在する領域625をダイ624の縁部の内側に区画している。円で囲まれた「+」記号は、第1の位置602の各々を表している。第1の位置602は、ダイ624の境界に隣接しあつ境界（たとえば、縁部）内に配置される。指定された第1の位置602に形成されたすべての単一セグメントダイ貫通相互接続部は、ダイ624内まで延びおよび/またはダイ624内を通って延びてもよい。図6Aは、ダイ624内まで延びずおよび/またはダイ624内を通って延びることのない、他の相互接続部を形成するために事前指定された第2の位置604をさらに示す。正方形で囲まれた「+」記号は、第2の位置604の各々を表している。第2の位置604は、ダイ624の境界の外側に位置してもよく、またはダイ624の境界内に位置してもよい。

40

#### 【0099】

第1のEDS600の平面図は、バックサイドドリリングプロセスよりも前の段階を示す。（図3のM4層388と同様の）導電層を追加する前の、第2の積層642のバックサイド面が表されている。この平面図では、ダイ624が第1のEDS600に結合される場合でも、ダイ624は第1のEDS600のバックサイドから見えないので、第1のEDS600内に埋め込まれたダイ624の概略図が点線で示されている。さらに、キャ

50

ビティ 622 も同様に第 1 の EDS600 のバックサイドから見えないので、ダイ 624 が内部に存在するキャビティ 622 (たとえば、側壁によって画定される開口部または空隙) の概略図が点線で示されている。

#### 【0100】

いくつかの実装形態では、バックサイドドリリングプロセスの間に、レザードリルが第 1 の位置 602 の各々において穴をドリリングすることによって複数の穴を形成してもよい。第 1 の位置 602 の各々に形成された各穴は、第 2 の積層 642、キャビティ 622 のフロア、ダイ 624、およびダイ 624 のトップサイド上の導電性パッド (図示せず) の内部まで延び、ならびに / あるいは第 2 の積層 642、キャビティ 622 のフロア、ダイ 624、および上記の導電性パッド内を通って延びてもよい (さらに、ダイ 624 のトップサイド上の導電性パッド (図示せず) に関連するレザーストップ層 (図示せず) の下面を露出させてもよい)。

10

#### 【0101】

いくつかの実装形態では、バックサイドドリリングプロセスの間に、レザードリルが第 2 の位置 604 の各々において穴をドリリングすることによって複数の穴を形成してもよい。第 2 の位置 604 に形成された各穴は、ダイ 624 内まで延びずおよび / またはダイ 624 内を通って延びることはない。

#### 【0102】

いくつかの実装形態では、第 1 の位置 602 および第 2 の位置 604 の各々において穴がドリリングされた後、導電性材料を使用して穴をめっきしおよび / または充填し、したがって、穴内に相互接続部を形成してもよい。導電性材料は、穴の側壁をめっきしおよび / または穴を完全に充填してもよい。穴を導電性材料によってめっきしおよび / または充填することにより、穴の側壁上に (および / または第 1 の位置 602 の各々、ダイ 624 のトップサイド上の導電性パッド (図示せず) および / またはレザーストップ (図示せず) において) 露出されるメタライゼーションの縁部と相互接続部の残りの部分が結合されてもよい。たとえば、M4 層のパッドおよびトレースを形成するための追加のメタライゼーションが第 2 の積層 642 に追加されてもよい。

20

#### 【0103】

図 6Aにおいて、単一セグメントダイ貫通相互接続部を形成するために事前指定された第 1 の位置 602 は、ダイ 624 の外縁部の近くに配置されるように示されている。ダイの外縁部の周りの領域はガード領域 (たとえば、図 5、527) と呼ばれることがある。ガード領域は、ダイ 624 上またはダイ 624 内の能動回路および / または受動回路に関して、ダイの縁部の内側の領域 625 よりも密度が低くてもよい。いくつかの実装形態では、ダイ 624 は、ドリル (たとえば、レザードリル) と第 1 の位置 602 とのずれを許容するように構成されてもよい。いくつかの実装形態では、単一セグメントダイ貫通相互接続部用の穴をドリリングすることが課されたドリルは、レザードリルであってよく、約 10 μm から 200 μm の間または約 30 μm から 100 μm の間の直径の穴をドリリングすることができるが、提示された範囲よりも小さいかまたは大きい直径が許容されかつ企図される。当業者に知られているように、たとえば、穴の直径はダイの厚さによって決まってもよい。いくつかの実装形態では、ダイは、サイズの範囲が約 1.5 × 1.5 mm ~ 約 10 × 10 mm 程度であってもよく、一実装形態では、ダイは約 2 × 2 mm であってもよいが、ダイは本明細書に記載された寸法に限定されず、たとえば、パッケージサイズに応じてそれより大きくてよくあるいは小さくてもよい。

30

40

#### 【0104】

図 6B は、単一セグメントダイ貫通相互接続部を形成するために事前指定された第 1 の位置 602 を有する第 2 の EDS601 のバックサイド平面図を示す。点線は、能動回路および / または受動回路が存在する領域 625 をダイ 624 の縁部の内側に区画している。図 6B の構成の説明は、図 6A の構成要素と同じであるかまたは同様であり、この説明については、簡潔のために繰り返さない。しかし、図 6B では、単一セグメントダイ貫通相互接続部を形成するために事前指定された第 1 の位置 602 は、ダイ 624 に隣接する

50

ように配置されるとともに、(たとえば、ダイ624のガード領域内の)ダイ624の外縁部上とダイ624の縁部の内側の領域625(たとえば、高密度の能動回路および/または受動回路を有する領域)内に配置されるように示されている。図6Bの態様は、ダイ624上またはダイ624内の能動回路および/または受動回路の密度は、ダイ624の縁部に隣接する領域内よりもダイ624の縁部の内側の領域625内の方が高い場合があるにもかかわらず、ダイ624の縁部の内側の領域625内に単一セグメントダイ貫通相互接続部を収容するようにダイ624を設計することが可能であることを示すことが意図されている。

#### 【0105】

埋込みダイ基板(EDS)デバイスを製作するための例示的なシーケンス

10

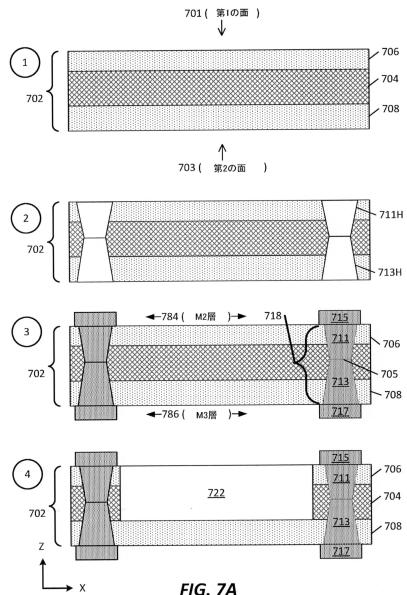

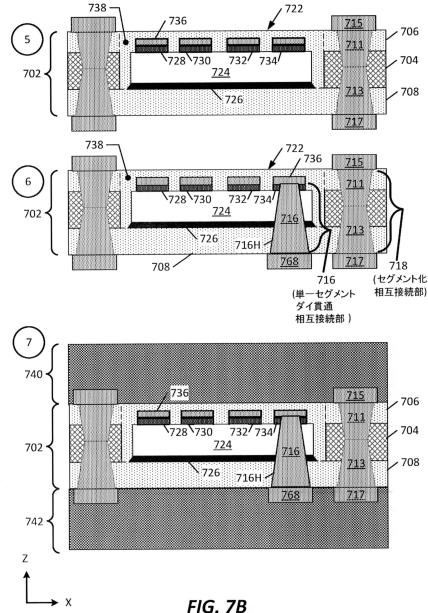

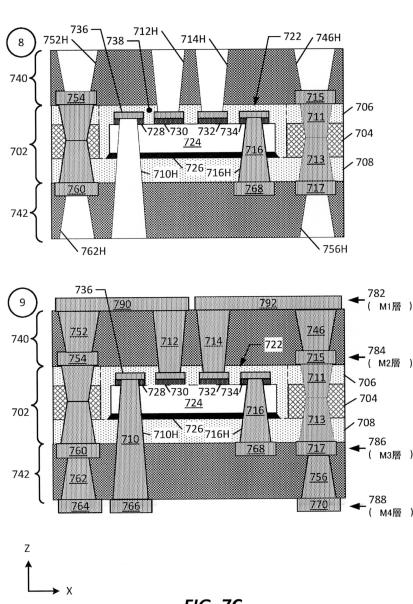

図7A～図7Cは、本明細書で説明する態様による単一セグメントダイ貫通相互接続部を含むEDSを提供する/製作するための段階の例示的なシーケンスを示す。いくつかの実装形態では、単一セグメントダイ貫通相互接続部を含むEDSを提供する/製作することはいくつかのプロセス段階を含む。図7は、単一セグメントダイ貫通相互接続部を含むEDSを提供する/製作するための段階の例示的なシーケンスを示す図である(図7A～図7Cを含む)。いくつかの実装形態では、図3、図4、図6A、および/または図6Bの単一セグメントダイ貫通相互接続部を含むEDSを製作するために図7A～図7Cの例示的なシーケンスが使用されてもよい。しかしながら、簡略化のために、図7A～図7Cについては、図3のEDSを提供する/製作することの文脈において説明する。

#### 【0106】

20

図7A～図7Cのシーケンスでは、単一セグメントダイ貫通相互接続部を含むEDSを提供するためのシーケンスを単純化しおよび/または明確にするために、1つまたは複数の段階を組み合わせてもよいことに留意されたい。いくつかの実装形態では、プロセス段階の順序は変更または修正されてもよい。

#### 【0107】

図7Aに示されるように、段階1は、基板702が用意された後の状態を示す。基板702は、コア基板(たとえば、コア層)であってもよい。基板702は、両面基板であってもよい。基板702は、銅などの金属から形成されてもよい導電層704を含んでもよい。導電層704は、EDS内の他の導電層(たとえば、M1層782、M2層784、M3層786、M4層788)よりも厚くてもよい。導電層704の厚さは、EDSに剛性および/または構造的支持をもたらすことがある。導電層704は、EDSの接地平面または電力面として使用されてもよい。基板702は、基板702の第1の面701における第1の誘電体層706(たとえば、トップサイド誘電体層)と基板702の第2の面703における第2の誘電体層708(たとえば、バックサイド誘電体層)とを含んでもよい。第1の誘電体層706と第2の誘電体層708は、間に導電層704をはさんでもよい。基板702は、形成されてもよく、または供給元によって提供されてもよい。

30

#### 【0108】

段階2は、基板702に複数の穴711H、713Hが形成された後の状態を示す。複数の穴711H、713Hは基板702によって画定されてもよい。複数の穴711H、713Hは、セグメント化された相互接続部を収容することができる。複数の穴711H、713Hは、たとえば、フォトリソグラフィプロセス、機械的プロセス、および/またはレーザードリリングプロセスによって形成されてもよい。

40

#### 【0109】

段階3は、基板702上および/または基板702内にM2層784(たとえば、金属層)のパッドまたはトレース715およびM3層786(たとえば、金属層)のパッドまたはトレース717が形成された後の状態を示す。例示的な図では、M2層784のパッドまたはトレース715は第1の誘電体層706上に形成されてもよい。M3層786のパッドまたはトレース717は第2の誘電体層708上および/または第2の誘電体層708内に形成されてもよい。複数の穴711H、713Hには、M2層784のパッドまたはトレース715およびM3層786のパッドまたはトレース717に使用される金属

50

と同じ金属などの導電性材料が充填されおよび／またはめっきされてもよい。（複数の穴 711H、713H 内で）導電性材料 711 と導電性材料 713 を接続することによってパッドまたはトレース 715 とパッドまたはトレース 717 との間に第 1 のセグメント化された相互接続部 718 が形成されてもよい。第 1 のセグメント化された相互接続部 718 は、（それぞれ）複数の穴 711H、713H 内の導電性材料 711、713 から形成されたセグメント（たとえば、層）から構成されるので、「セグメント化」相互接続部と呼ばれる。第 1 のセグメント化相互接続部 718 は段階 3 における完全な状態で示されているが、穴 713H における導電性材料 713 の形成とは異なる段階、異なる時間に穴 711H における導電性材料 711 の形成が行われている場合があることを示すシーム 705 がセグメント間に示されている。第 1 のセグメント化相互接続部 718 は、複数の層から形成され、たとえば、各層は異なるセグメントから形成される。

10

#### 【0110】

段階 4 は、基板 702 内にキャビティ 722（たとえば、側壁によって画定される開口部または空隙）が形成された後の状態を示す。キャビティ 722 は、たとえば、フォトリソグラフィ、機械的プロセス、および／またはレーザードリリングを含む方法によって形成されてもよい。キャビティ 722 は、の第 1 の面 701 から基板 702 内に画定されてもよい。キャビティ 722 は、第 1 の誘電体層 706 および導電層 704 から材料を除去することによって形成されてもよい。いくつかの実装形態では、キャビティ 722 は第 1 の誘電体層 706 および導電層 704 を含んでいなくてもよい。キャビティ 722 の幅および深さとしては、キャビティ 722 内に配置することができるダイ 724 用の空間を形成する幅および深さが選択されてもよい。いくつかの実装形態では、キャビティ 722 の深さは、ダイ 724 の高さに、キャビティ 722 の底部（たとえば、フロア）にダイ 724 を結合するのに使用される場合がある接着剤、はんだ、またはエポキシ 726 の厚さを加えた値以上であってもよい。したがって、少なくともダイ 724 の高さに応じて、上記よりも多い材料または上記よりも少ない材料を基板 702 から除去し、基板 702 によって画定されるキャビティ 722 を形成してもよい。

20

#### 【0111】

いくつかの実装形態では、導電層 704 のある部分がキャビティ 722 内に残ってもよいが、そのような実装形態では、ダイの底部上のメタライゼーションおよび／またはキャビティ 722 のフロアを貫通する単一セグメントダイ貫通相互接続部のメタライゼーションが導電層 704 との不要な短絡回路を形成しないようにアンチパッド部分および／または絶縁部分などの手段が実装されてもよい。

30

#### 【0112】

いくつかの実装形態では、キャビティ 722 を形成する間に第 2 の誘電体層 708（たとえば、バックサイド誘電体層）のある部分が除去されてもよい。いくつかの実装形態では、キャビティ 722 は、基板 702 におけるキャビティ 722 を画定する側壁内から第 1 の誘電体層 706、導電層 704、および第 2 の誘電体層 708 のすべてを除去することによって形成されてもよい。そのような実装形態では、ダイは、第 2 の誘電体層 708（の下方）に隣接する層に結合されてもよい。

40

#### 【0113】

段階 5 は、ダイ 724 が、キャビティ 722 のフロアに結合された（たとえば、キャビティ 722 内の第 2 の誘電体層 708 に結合された）後の状態を示す。ダイ 724 は、たとえば、接着剤、はんだ、またはエポキシ 726 を使用して結合されてもよい。ダイ 724 は、キャビティ 722 のフロアの遠位側のダイ 724 の面上に第 1 の導電性パッド 728、第 2 の導電性パッド 730、第 3 の導電性パッド 732、および第 4 の導電性パッド 734 を含む複数の導電性パッド 728、730、732、734 を含んでもよい。複数の導電性パッド 728、730、732、734 は、たとえば金から形成されてもよい。複数の導電性パッド 728、730、732、734 の各々は、パッド上に堆積され、めつきされ、または追加されるレーザーストップ層 736（たとえば、保護導電層）（たとえば、複数の導電性パッド 728、730、732、734 の各々上のレーザーストップ

50

層 7 3 6 ) を有してもよい。第 1 のレーザーストップ層 7 3 6 は、たとえば、銅であってもよい。

#### 【 0 1 1 4 】

段階 5 は、キャビティ 7 2 2 がダイ 7 2 4 をカプセル化し、保護し、および / または不動化するためにフィラー材料 7 3 8 を受け入れた後の状態をさらに示す。フィラー材料 7 3 8 は、ダイ 7 2 4 を少なくとも部分的にカプセル化する場合がある。いくつかの実装形態では、フィラー材料 7 3 8 は、フィラー材料 7 3 8 の表面が第 1 の誘電体層 7 0 6 のトップサイド面と実質的に共面になるように塗布され（たとえば、形成され、設けられ）てもよい。

#### 【 0 1 1 5 】

段階 6 は、穴 7 1 6 H 内に第 4 の単一セグメントダイ貫通相互接続部 7 1 6 が形成された後の状態を示す。穴 7 1 6 H は、たとえば、第 2 の誘電体層 7 0 8 （たとえば、基板 7 0 2 の一部、基板 7 0 2 内に形成されたキャビティ 7 2 2 のフロア）を貫通し、キャビティ 7 2 2 のフロアに結合されたダイ 7 2 4 に進入するようにドリリングすることによって形成されてもよい。穴 7 1 6 H は、基板 7 0 2 の第 2 の面 7 0 3 （たとえば、基板の第 2 の面は第 2 の誘電体層 7 0 8 を含んでもよい）、ダイ 7 2 4 、および導電性パッド 7 3 4 内を通って延びてもよく、かつ基板 7 0 2 の第 2 の面 7 0 3 、ダイ 7 2 4 、および導電性パッド 7 3 4 内に画定されてもよい。たとえば、例示的な図では、穴 7 1 6 H は、基板 7 0 2 の第 2 の誘電体層 7 0 8 、ダイ 7 2 4 、および導電性パッド 7 3 4 内を通って延び、基板 7 0 2 の第 2 の誘電体層 7 0 8 、ダイ 7 2 4 、および導電性パッド 7 3 4 内に画定される。いくつかの実装形態では、穴 7 1 6 H は、導電性パッド 7 3 4 上のレーザーストップ層 7 3 6 の所で終わり、および / またはレーザーストップ層 7 3 6 内で終わってもよい。導電性材料（たとえば、第 4 の単一セグメントダイ貫通相互接続部 7 1 6 を形成する導電性材料）が、穴 7 1 6 H をめっきしおよび / または充填しており、穴 7 1 6 H 内から導電性パッド 7 3 4 に結合している。導電性材料は、キャビティのフロアに対して遠位側の第 2 の誘電体層 7 0 8 の表面と導電性パッド 7 3 4 との間に相互接続部（第 4 の単一セグメントダイ貫通相互接続部 7 1 6 ）を形成している。第 2 の誘電体層 7 0 8 上および / または第 2 の誘電体層 7 0 8 内にパッドまたはトレース 7 6 8 が形成されてもよい。

#### 【 0 1 1 6 】

第 4 の単一セグメントダイ貫通相互接続部 7 1 6 の右側には、対照的な第 1 のセグメント化相互接続部 7 1 8 が位置している。第 4 の単一セグメントダイ貫通相互接続部 7 1 6 は、ユニタリー単一セグメント、ユニタリー構造、不可分構造、および / または未分割構造と呼ばれることもある。第 4 の単一セグメントダイ貫通相互接続部 7 1 6 は、基板 7 0 2 、ダイ 7 2 4 、および導電性パッド 7 3 4 内を通って延び、基板 7 0 2 、ダイ 7 2 4 、および導電性パッド 7 3 4 内に画定される構造と呼ばれることもある。これに対して、第 1 のセグメント化相互接続部 7 1 8 は、導電性材料 7 1 1 の第 1 のセグメントおよび導電性材料 7 1 3 の第 2 のセグメントの積層セットから形成されており、ダイ 7 2 4 および / またはダイ 7 2 4 のトップサイド上の任意の導電性パッド内まで延びずならびに / あるいはダイ 7 2 4 および / または導電性パッド内を通って延びることはない。

#### 【 0 1 1 7 】

段階 7 は、第 1 の誘電体層 7 0 6 に第 1 の積層 7 4 0 （たとえば、トップサイド積層）を設け、第 2 の誘電体層 7 0 8 に第 2 の積層 7 4 2 を設けた後の状態を示す。第 1 の積層 7 4 0 および第 2 の積層 7 4 2 の各々は、プリプレグ（予備含浸された）層と呼ばれることがある。第 1 の積層 7 4 0 および第 2 の積層 7 4 2 の各々は、1 つまたは複数の誘電および導電層を含んでもよい。プリプレグ層は、たとえば、各層を噴霧によってそれぞれの表面上に堆積させることによって設けられてもよい。当業者には、基板 7 0 2 上にプリプレグ層および / または追加の層を設けるための他の方法（たとえば、積層、接合、取付け、接着、形成）が知られている。

#### 【 0 1 1 8 】

段階 8 は、第 1 の積層 7 4 0 （たとえば、第 1 のプリプレグ層）から事前指定された位

10

20

30

40

50

置をドリリングすることによって第1のトップサイド外側穴752Hと、第1のトップサイド内側穴712Hと、第2のトップサイド内側穴714Hと、第2のトップサイド外側穴746Hとを含む第1の複数の穴が形成された後の状態を示す。第1の複数の穴は、トップサイドドリリングプロセスの間に形成されてもよい。第2の積層742（たとえば、第2のプリプレグ層）から事前指定された位置をドリリングすることによって、第1の外側穴762Hと、第2の外側穴756Hと、内側穴710Hとを含む第2の複数の穴が形成されてもよい。第2の複数の穴は、バックサイドドリリングプロセスの間に形成されてもよい。

#### 【0119】

トップサイドドリリングプロセスの間に、第1のトップサイド内側穴712Hおよび第2のトップサイド内側穴714Hは、第1の積層740およびキャビティ722内のフィラー材料738の部分内を通って延びる。第1のトップサイド内側穴712Hおよび第2のトップサイド内側穴714Hは、レーザーストップ層736層の所で終わる。第1のトップサイド内側穴712Hおよび第2のトップサイド内側穴714Hはダイ724内まで延びずおよび／またはダイ724内を通って延びることはない（ならびに／あるいはダイ724の所の導電性パッド730、732内まで延びずおよび／または導電性パッド730、732内を通って延びることはない）。第1のトップサイド外側穴752Hおよび第2のトップサイド外側穴746Hも、第1の積層740内を通って延びる。第1のトップサイド外側穴752Hは、第1の誘電体層706上のパッドまたはトレース754上で終わる。第2のトップサイド外側穴746Hは、第1の誘電体層706上のパッドまたはトレース715上で終わる。10

#### 【0120】

バックサイドドリリングプロセスの間に、第1の外側穴762Hは、第2の積層742内を通って延び、第2の積層742によって画定され、第2の誘電体層708上のM3層786のパッドまたはトレース760の所で終わる。第2の外側穴756Hは、第2の積層742内を通って延び、第2の積層742によって画定され、第2の誘電体層708上のM3層786のパッドまたはトレース717の所で終わる。バックサイドドリリングプロセスの間に、（第1の単一セグメントダイ貫通相互接続部710を形成するように導電性材料によってめっきしある／または充填することができる）内側穴710Hは、第2の積層742、基板702（たとえば、第2の誘電体層708、ダイ724と第2の積層742（たとえば、キャビティ722のフロア）との間に位置する基板702の一部）、ダイ724、および導電性パッド728内を通って延び、第2の積層742、基板702、ダイ724、および導電性パッド728によって画定される。たとえば、例示的な図では、内側穴710Hは、第2の積層742、基板702の第2の誘電体層708、ダイ724、および導電性パッド728内を通って延び、第2の積層742、第2の誘電体層708、ダイ724、および導電性パッド728によって画定される。内側穴710Hは、導電性パッド728上のレーザーストップ層736の所で終わり、および／またはレーザーストップ層736内で終わってもよい。20

#### 【0121】

複数の第1の穴（第1のトップサイド外側穴752H、第1のトップサイド内側穴712H、第2のトップサイド内側穴714H、および第2のトップサイド外側穴746Hを含む）ならびに第2の複数の穴（第1の外側穴762H、第2の外側穴756H、および内側穴710Hを含む）は、たとえばフォトリソグラフィプロセス、機械的プロセス、および／またはレーザードリリングプロセスを含む方法によって形成されてもよい。40

#### 【0122】

段階9は、導電性材料を使用して内側穴710H内に第1の単一セグメントダイ貫通相互接続部710が形成された後の状態を示す。導電性材料は、基板702の第2の面703に対して遠位側の第2の積層742の表面（たとえば、基板の第2の面は第2の誘電体層708を含んでもよい）と導電性パッド734との間に相互接続部（第1の単一セグメントダイ貫通相互接続部710）を形成する。さらに、段階9は、第1のトップサイド外50

側穴 752H 内の導電性材料 752、第 1 のトップサイド内側穴 712H 内の導電性材料 712、第 2 のトップサイド内側穴 714H 内の導電性材料 714、第 2 のトップサイド外側穴 746H 内の導電性材料 746、第 1 の外側穴 762H 内の導電性材料 762、第 2 の外側穴 756H 内の導電性材料 756 を示す。ステージ 9 は、第 1 の積層 740 上および / または第 1 の積層 740 内に形成された M1 層 782、ならびに第 2 の積層 742 上および / または第 2 の積層 742 内に形成された M4 層 788 をさらに示す。M1 層 782 は、第 1 の水平トレース 790 と第 2 の水平トレース 792 とを含む場合がある。M4 層 788 は、第 1 のノード 764 と、第 2 のノード 766 と、第 4 のノード 770 とを含んでもよい（たとえば、ノードは導電性パッドであってもまたは導電性トレースであってもよい）。

10

#### 【0123】

ダイ 724 を基板 702 に結合するために使用される接着剤、はんだ、またはエポキシ 726 を含まないアンチパッド部分および / または絶縁部分などのガード領域（図示せず）が、実装されてもよく、たとえば、接着剤、はんだ、またはエポキシ 726 が導電性である場合に接着剤、はんだ、またはエポキシ 726 への短絡を妨げるために第 1 の単一セグメントダイ貫通相互接続部 710 および第 4 の単一セグメントダイ貫通相互接続部 716 の周りに設けられてもよい。

#### 【0124】

いくつかの実装形態では、いくつかの EDS がコア基板上に同時に製作されてもよく、コア基板を個々の EDS に切り分けるためにシンギュレーションプロセスが実行されてもよい。

20

#### 【0125】

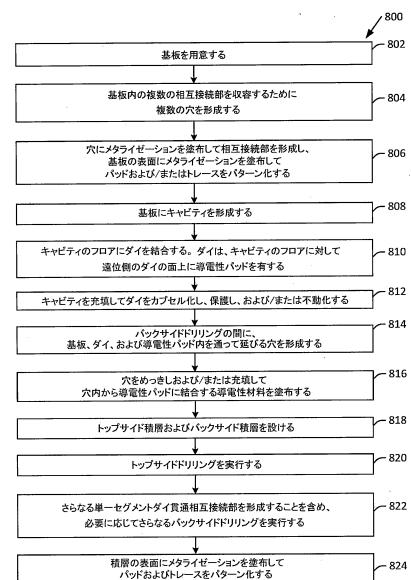

埋込みダイ基板（EDS）を製作するための例示的な方法

図 8 は、単一セグメントダイ貫通相互接続部を含む EDS を製作するための例示的な方法の流れ図 800 を示す。いくつかの実装形態では、図 3、図 4、図 6A、および / または図 6B の単一セグメントダイ貫通相互接続部を含む EDS を製作するために図 8 の例示的な方法が使用されてもよい。しかしながら、簡略化のために、図 8 については、図 3 の EDS を提供する / 製作することの文脈において説明する。

#### 【0126】

図 8 に提示されたブロックのシーケンスでは、単一セグメントダイ貫通相互接続部を含む EDS を製作するための方法を単純化しある / または明確にするために、1つまたは複数の工程を組み合わせてもよいことに留意されたい。いくつかの実装形態では、プロックの順序は変更または修正されてもよい。

30

#### 【0127】

基板が用意されてもよい（802）。基板は、第 1 の面と反対側の第 2 の面とを有してもよい。基板は、両面基板であってもよい。基板は、コア基板（たとえば、コア層）であってもよい。基板は、銅などの金属から形成されてもよい導電層を含んでもよい。基板は、基板の第 1 の面（たとえば、トップサイド誘電体層）上に第 1 の誘電体層を含んでもよく、基板の第 2 の面（たとえば、バックサイド誘電体層）上に第 2 の誘電体層を含んでもよい。第 1 の誘電体層と第 2 の誘電体層は、間に導電層をはさんでもよい。

40

#### 【0128】

複数の相互接続部を収容するように基板に複数の穴が形成されてもよい（804）。たとえば、フォトリソグラフィプロセス、機械的プロセス、および / またはレーザードリーリングプロセスを使用して複数の穴が形成されてもよい。いくつかの実装形態では、複数の穴は、レーザードリルを使用して形成されてもよい。

#### 【0129】

メタライゼーション（たとえば、導電性材料）を複数の穴に塗布して相互接続部を形成してもよく（806）、第 1 の誘電体層および第 2 の誘電体層上にパターン化してパッドおよび / またはトレースを形成してもよい。

#### 【0130】

50

基板内にキャビティが形成されてもよい(808)。基板内にキャビティが形成されてもよい。本明細書で説明するように、キャビティは、基板内の側壁によって画定される開口部または空隙であってもよい。キャビティは、基板の第1の面から基板内に形成および画定されてもよい。キャビティは、第1の誘電体層および導電層から材料を除去することによって形成されてもよい。キャビティの幅および深さとしては、キャビティ内に配置されてもよいダイ用の空間を形成する幅および深さが選択されてもよい。いくつかの実装形態では、キャビティの深さは、ダイの高さに、キャビティの底部(またはフロア)にダイを結合する接着剤、はんだ、またはエポキシの厚さを加えた値以上であってもよい。

#### 【0131】

ダイは、キャビティのフロアに結合されてもよい(たとえば、キャビティ内に露出された第2の誘電体層に結合される)(810)。ダイは、キャビティのフロアに結合された第1の面とキャビティのフロアに対して遠位側の、反対側の第2の面とを有してもよい。ダイは、たとえば、接着剤、はんだ、またはエポキシを使用して結合されてもよい。ダイは、複数の導電性パッドを含んでもよい。複数の導電性パッドは、たとえば金から形成されてもよい。ダイは、キャビティのフロアに対して遠位側のダイの面(ダイの反対側の第2の面)上に少なくとも1つの導電性パッドを有してもよい。複数の導電性パッドの各々は、パッド上に堆積され、めっきされ、追加されたレーザーストップ層を有してもよい。レーザーストップ層は、銅などの金属のカバー層であってもよい。レーザーストップ層の金属は、下方の導電性パッドの金属とは異なっていてもよい。

#### 【0132】

キャビティは、ダイをカプセル化し、保護し、および/または不動化するためにフィラー材料を受け入れてもよい(812)。フィラー材料は、ダイを少なくとも部分的にカプセル化する場合がある。いくつかの実装形態では、フィラー材料は、フィラー材料の表面が第1の誘電体層の表面と実質的に共面になるように塗布され(たとえば、形成され、設けられ)てもよい。

#### 【0133】

基板、ダイ、および導電性パッド内を通って延びるようにドリリングによって穴が形成されてもよい(814)(たとえば、設けられてもよい)。たとえば、穴は、基板の第2の面(たとえば、ダイが結合された基板の層、キャビティのフロアと呼ばれる表面を有する基板の層、第2の誘電体層を含む基板の層)内を通って延び、基板の第2の面内に画定され、キャビティのフロアに結合されたダイ内まで延びおよび/またはこのダイ内を通って延び、かつキャビティのフロアに対して遠位側のダイの面上の導電性パッド内まで延びおよび/またはこの導電性パッド内を通って延びてもよい。いくつかの実装形態では、穴は、ダイ内まで延びおよび/またはこのダイ内を通って延び、ダイ上の導電性パッドの表面の所で終わるかあるいはこの表面を露出させてもよい。導電性パッドの表面は、導電性パッドの下面であってもよい。導電性パッドの下面是、ダイの上部と導電性パッドの底部との間の界面に実質的に沿って位置する平面内に位置してもよい。

#### 【0134】

穴をめっきしおよび/または充填して穴内から導電性パッドに結合するように導電性材料が塗布されてもよい(816)。導電性材料は、穴の側壁をめっきしおよび/または穴を完全に充填してもよい。穴は、基板の第2の誘電体層およびダイ内を通って延び、基板の第2の誘電体層およびダイ内に画定され、導電性パッド内まで延びおよび/またはこの導電性パッド内を通って延び、一度に形成されてもよく、あるいは言い換えれば、1つのプロセスの間または1つの措置内で形成されてもよい。導電性材料は、EDSの第2の誘電体層からダイ内を通って延び、キャビティのフロアに結合されたダイの面に対して遠位側のダイの面上の導電性パッド内まで延びおよび/またはこの導電性パッド内を通って延びてもよく、ユニタリー構造、不可分構造、および/または未分割構造であってもよい。したがって、導電性材料は、基板、ダイ、および導電性パッド内を通って延び、ユニタリーセグメント、不可分セグメント、および/または未分割セグメント(たとえば、1つの構造、1つのセグメント、単一のセグメント)として形成されてもよいので、單一セグメ

10

20

30

40

50

ントダイ貫通相互接続部と呼ばれることがある。さらに、穴は、E D S組込みの間、たとえば、E D S組込み時のバックサイドドリリングプロセス（たとえば、工程、措置）の間に形成される。前記のように、各エンティティは、ダイを損傷する恐れがあるのでE D S組込みの間にダイに穴をドリリングすることを嫌う。しかし、本明細書で説明する態様が、ダイから少なくともいくらかのT S Vを除去する（それによってダイマスク数およびダイを製作するうえで使用される工程の数を少なくする）ことによってダイのコストを削減する場合があることがわかっている。さらに、本明細書で説明する態様に従って形成される単一セグメントダイ貫通相互接続部は1つの導電性材料から単一セグメントとして形成される場合があるので、金などの、ダイ内にT S Vを製作するために使用される材料よりも高い熱伝導率を有する導電性材料から形成することができる。たとえば、いくつかの実装形態では、単一セグメントダイ貫通相互接続部の形成に使用される場合がある導電性材料は銅であってもよい。銅単一セグメントダイ貫通相互接続部の熱伝導率は、ヒ化ガリウム（G a A s）ダイ用の金よりも30%高く、バルク／シリコンオンインシュレータ（S O I）C M O S（S O I C M O S）用のタンゲステンよりも100%高いことがわかっている。10

#### 【0135】

第1の誘電体層に第1の積層が設けられ、第2の誘電体層に第2の積層が設けられてもよい（818）。

#### 【0136】

必要に応じてトップサイドドリリングプロセスが実行されてもよい（820）。20

#### 【0137】

必要に応じてさらなるバックサイドドリリングが実行されてもよく（822）、バックサイドドリリングは、必要に応じてさらなる単一セグメントダイ貫通相互接続部用の追加の穴を形成することを含んでもよい。バックサイドドリリングプロセスの間に全体的なE D S構造にさらなる層（第2の積層）が追加されたので、単一セグメントダイ貫通相互接続部として指定された穴が、第2の積層、ダイと第2の積層（たとえば、キャビティのフロア）との間の基板の層、ダイ、およびダイのトップサイド上の導電性パッド内を通って延び、第2の積層、上記の基板の層、ダイ、および上記の導電性パッド内に画定されてもよい。いくつかの実装形態では、穴は、導電性パッド上のレーザーストップ層の所で終わってもよい。30

#### 【0138】

第1の積層上および／または第1の積層内にM1層（たとえば、導電性材料／導電層／メタライゼーション層）が形成されてもよく、パッドおよび／またはトレースをパターン化するように第2の積層上および／または第2の積層内にM4層が形成されてもよい（824）。

#### 【0139】

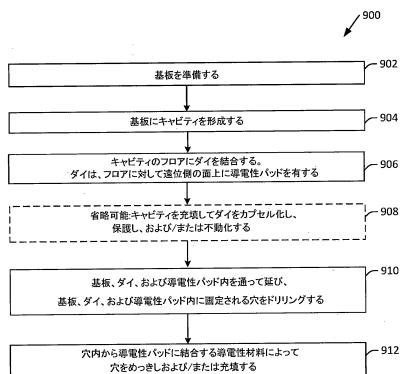

図9は、単一セグメントダイ貫通相互接続部を含むE D Sを製作するための例示的な方法の別の流れ図900を示す。いくつかの実装形態では、図3、図4、図6A、および／または図6Bの単一セグメントダイ貫通相互接続部を含むE D Sを製作するために図9の例示的な方法が使用されてもよい。しかしながら、簡略化のために、図9については、図3のE D Sを提供する／製作することの文脈において説明する。40

#### 【0140】

図9に提示されたブロックのシーケンスでは、単一セグメントダイ貫通相互接続部を含むE D Sを製作するための方法を単純化しある／または明確にするために、1つまたは複数の工程を組み合わせてもよいことに留意されたい。いくつかの実装形態では、ブロックの順序は変更または修正されてもよい。

#### 【0141】

第1の面と反対側の第2の面とを有する基板が用意されてもよい（902）。基板内に画定されるキャビティ（たとえば、基板内に側壁によって画定される開口部または空隙）が基板内に形成されてもよい（904）。基板内に画定されるキャビティは、基板の第150

の面から形成される。キャビティのフロアにダイが結合されてもよく(906)、このダイは、キャビティのフロアに対して遠位側のダイの面上に導電性パッドを有する。場合によっては、キャビティにフィラー材料が付加されてもよい(908)。フィラー材料は、たとえばダイをカプセル化し、保護し、および/または不動化するように働いてもよい。

#### 【0142】

基板、ダイ、および導電性パッド内を通って延び、基板、ダイ、および導電性パッド内に画定される穴をドリリングするプロセスが実行されてもよい(910)。穴は、導電性パッドの表面(たとえば、穴内から到達でき/見える導電性パッドの表面)を露出させてよい。穴は、穴内から導電性パッドに結合する導電性材料によってめっきされおよび/または充填されてもよい(912)。いくつかの実装形態では、ダイは、キャビティのフロアに結合されてもよく、その後穴がドリリングされる。いくつかの実装形態では、穴のドリリングは1度に実行されてもよい。言い換えれば、1回のプロセス(たとえば、バックサイドドリリングプロセス)の間に穴の全長が形成されてもよい。いくつかの実装形態では、この穴は、基板の第2の面、ダイ、および導電性パッド内を通って延びる直線軸に沿って同心であるように形成されてもよい。いくつかの実装形態では、この穴は、穴の長さに沿った単一の直線穴であるように形成されてもよい。いくつかの実装形態では、穴をめっきしあおよび/または充填する導電性材料は、ユニタリー単一セグメントとして形成されてもよい。いくつかの実装形態では、導電性材料は、基板の第2の面とダイと導電性パッドとの間を延び、基板の第2の面、ダイ、および導電性パッド内を通って延びてもよく、1つだけの層(たとえば、1つの導電性材料の1つだけのセグメント、1つの導電性材料の1つだけの層)として形成されてもよい。いくつかの実装形態では、導電性材料は、キャビティのフロアに対して遠位側の基板の第2の面の表面と導電性パッドとの間の相互接続部を形成してもよい。いくつかの実装形態では、導電性材料は、基板のバックサイド面上の穴の開口部と導電性パッドとの間の相互接続部を形成してもよい。いくつかの実装形態では、相互接続部は単一のセグメント(たとえば、単一セグメントダイ貫通相互接続部)として形成されてもよい。いくつかの実装形態では、相互接続部は、ユニタリー構造、不可分構造、および/または未分割構造である。

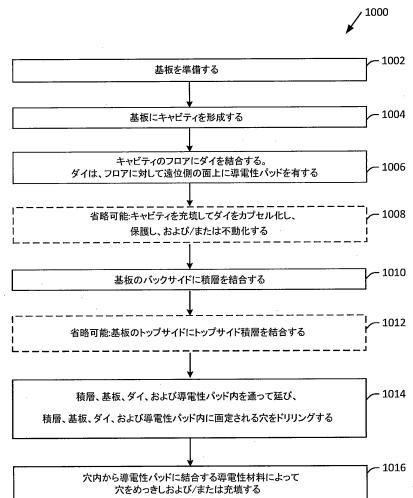

#### 【0143】

図10は、単一セグメントダイ貫通相互接続部を含むEDSを製作するための例示的な方法の別の流れ図1000を示す。いくつかの実装形態では、図3、図4、図6A、および/または図6Bの単一セグメントダイ貫通相互接続部を含むEDSを製作するために図10の例示的な方法が使用されてもよい。しかしながら、簡略化のために、図10については、図4のEDSを提供する/製作することの文脈において説明する。

#### 【0144】

図10に提示されたブロックのシーケンスでは、単一セグメントダイ貫通相互接続部を含むEDSを製作するための方法を単純化しあおよび/または明確にするために、1つまたは複数の工程を組み合わせてもよいことに留意されたい。いくつかの実装形態では、ブロックの順序は変更または修正されてもよい。

#### 【0145】

第1の面と反対側の第2の面とを有する基板が用意されてもよい(1002)。基板内に画定されるキャビティ(たとえば、基板内に側壁によって画定される開口部または空隙)が基板内に形成されてもよい(1004)。基板内に画定されるキャビティは、基板の第1の面から形成されてもよい。キャビティのフロアにダイが結合されてもよく(1006)、このダイは、キャビティのフロアに対して遠位側のダイの面上に導電性パッドを有する。場合によっては、キャビティにフィラー材料が付加されてもよい(1008)。フィラー材料は、たとえばダイをカプセル化し、保護し、および/または不動化するように働いてもよい。

#### 【0146】

基板の第2の面(たとえば、基板のバックサイド)に積層(たとえば、第2の積層)が結合されてもよい(1010)。場合によっては、基板の第1の面(たとえば、基板のト

10

20

30

40

50

ップサイド)に第1の積層が結合されてもよい(1012)。

#### 【0147】

第2の積層、基板、ダイ、および導電性パッド内を通って延び、第2の積層、基板、ダイ、および導電性パッド内に画定される穴をドリリングするプロセスが実行されてもよい(1014)。穴は、導電性パッドの表面(たとえば、穴内から到達でき/見える導電性パッドの表面)を露出させてもよい。穴は、穴内から導電性パッドに結合する導電性材料によってめっきされおよび/または充填されてもよい(1016)。

#### 【0148】

いくつかの実装形態では、ダイがキャビティのフロアに結合されてもよく、積層が基板の第2の面に結合されてもよく、その後穴がドリリングされる。いくつかの実装形態では、穴のドリリングは1度に行われてもよい。言い換れば、1回のプロセス(たとえば、バックサイドドリリングプロセス)の間に穴の全長が形成されてもよい。いくつかの実装形態では、この穴は、積層、基板の第2の面、ダイ、および導電性パッド内を通って延びる直線軸に沿って同心であるように形成されてもよい。いくつかの実装形態では、この穴は、穴の長さに沿った单一の直線穴であるように形成されてもよい。いくつかの実装形態では、穴をめっきしおよび/または充填する導電性材料は、ユニタリー単一セグメントとして形成されてもよい。いくつかの実装形態では、導電性材料は、積層と基板の第2の面とダイと導電性パッドとの間を延び、積層、基板の第2の面、ダイ、および導電性パッド内を通って延びてもよく、1つだけの層(たとえば、1つの導電性材料の1つだけのセグメント、1つの導電性材料の1つだけの層)として形成されてもよい。いくつかの実装形態では、導電性材料は、キャビティのフロアに対して遠位側の積層の表面と導電性パッドとの間の相互接続部を形成してもよい。いくつかの実装形態では、導電性材料は、第2の積層のバックサイド面上の穴の開口部と導電性パッドとの間の相互接続部を形成してもよい。いくつかの実装形態では、相互接続部は単一のセグメント(たとえば、単一セグメントダイ貫通相互接続部)として形成されてもよい。いくつかの実装形態では、相互接続部は、ユニタリー構造、不可分構造、および/または未分割構造である。

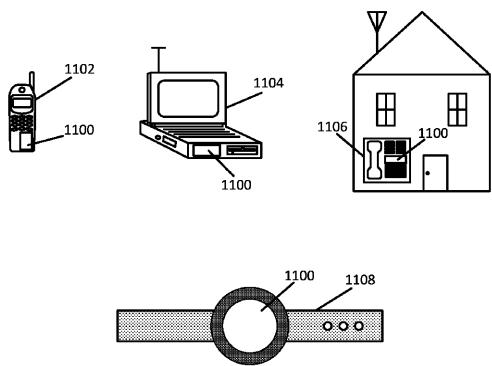

#### 【0149】

例示的な電子デバイス

図11は、単一セグメントダイ貫通相互接続部を含む前述のEDSのいずれかと統合されることがある様々な電子デバイスを示す。たとえば、モバイル電話デバイス1102、ラップトップコンピュータデバイス1104、固定ロケーション端末デバイス1106、装着型デバイス1108などの電子デバイスが、本明細書で説明するような単一セグメントダイ貫通相互接続部1100を含むEDSを含んでよい。図11に示す電子デバイスは例示的なデバイスである。たとえば、本明細書で説明する単一セグメントダイ貫通相互接続部1100を含むEDSは、限定はしないが、モバイルデバイス、ハンドヘルドパソコン通信システム(PC)ユニット、携帯情報端末、ポータブルデータ端末、全地球測位システム(GPS)対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、固定ロケーション端末(たとえば、メーター読み取り機器)、通信デバイス、モバイル電話、スマートフォン、タブレットコンピュータ、コンピュータ、装着型デバイス(たとえば、腕時計、眼鏡)、モノのインターネット(IoT)デバイス、ラップトップコンピュータ、サーバ、ルータ、自動車(たとえば、自律型自動車を含む)に実装される電子デバイス、またはデータもしくはコンピュータ命令を記憶するかもしくは取り込む任意の他のデバイス、あるいはそれらの任意の組合せを含むデバイスの群を含む他の電子デバイスに組み込まれてもよい。

#### 【0150】

図3、図4、図5A、図5B、図6A、図6B、図7A~図7C、図8、図9、および/または図10に示す構成要素、プロセス、特徴、および/または機能のうちの1つまたは複数は、単一の構成要素、プロセス、特徴、または機能として再構成されおよび/または組み合わされてもよく、あるいはいくつかの構成要素、プロセス、または機能として具現化されてもよい。本開示から逸脱することなく、追加の要素、構成要素、プロセス、お

10

20

30

40

50

および／または機能が追加されてもよい。本開示における図3、図4、図5A、図5B、図6A、図6B、図7A～図7C、図8、図9、および／または図10と、その対応する説明とは、ダイおよび／またはICに限定されないことにも留意されたい。いくつかの実施態様では、図3、図4、図5A、図5B、図6A、図6B、図7A～図7C、図8、図9、および／または図10ならびにその対応する説明を使用して、集積デバイスを製造し、作成し、提供し、および／または生産してもよい。いくつかの実装形態では、デバイスは、ダイ、集積デバイス、ダイパッケージ、集積回路（IC）、デバイスパッケージ、集積回路（IC）パッケージ、ウエハ、半導体デバイス、パッケージオンパッケージ（POP）デバイス、埋込みダイ基板、および／またはインターポーラを含んでもよい。

## 【0151】

10

「例示的」という語は、本明細書では「例、事例、または例示としての働きをすること」を意味するために使用される。本明細書で「例示的」として説明されている任意の実施形態または態様は、必ずしも本開示の他の態様よりも好ましいまたは有利であると解釈されるべきではない。同様に、「態様」という用語は、本開示のすべての態様が、論じられた特徴、利点、または動作モードを含むことを必要としない。「結合される」という用語は、2つの物体間の直接的または間接的な結合を指すために本明細書において使用される。たとえば、物体Aが物体Bに物理的に接触し、物体Bが物体Cに接触する場合、物体AとCはやはり、直接的に物理的に互いに接触しない場合であっても、互いに結合されると見なされることがある。

## 【0152】

20

加えて、本明細書に含まれる様々な開示が、フローチャート、フロー図、構造図、またはブロック図として示されるプロセスと呼ばれる場合があることに留意されたい。フローチャートは工程を逐次プロセスとして説明することがあるが、工程の多くは同時にまたは並行して実行することができる。加えて、工程の順序は並べ替えられてよい。プロセスは、その工程が完了するときに終了される。

## 【0153】

30

本明細書で説明した本開示の様々な特徴は、本開示から逸脱することなく様々なシステムにおいて実施することができる。本開示の上記の態様が例にすぎず、本開示を限定するものとして解釈すべきでないことに留意されたい。本開示の態様の説明は、例示的であることを意図しており、特許請求の範囲を限定することを意図していない。したがって、本教示は、他のタイプの装置に容易に適用することができ、多くの代替、修正、および変形が当業者には明らかであろう。

## 【符号の説明】

## 【0154】

- 100 埋込みダイ基板（EDS）

- 102 コア基板

- 104 中央導電層

- 106 トップサイド誘電体層

- 108 バックサイド誘電体層

- 112 相互接続部

- 122 キャビティ

- 124 ダイ

- 128、130、132、134 導電性パッド

- 136 保護導電層

- 138 フィラー材料

- 140 トップサイド積層

- 142 バックサイド積層

- 144 配線経路

- 146 ノード

- 148 導電トレース

40

50

|                         |                       |    |

|-------------------------|-----------------------|----|

| 1 5 2                   | 第 1 のビアセグメント          |    |

| 1 5 4                   | 第 1 のパッド              |    |

| 1 5 6                   | 第 2 のビアセグメント          |    |

| 1 5 8                   | 第 3 のビアセグメント          |    |

| 1 6 0                   | 第 2 のパッド              |    |

| 1 6 2                   | 第 4 のビアセグメント          |    |

| 2 0 0                   | E D S                 |    |

| 2 0 2                   | コア基板                  |    |

| 2 0 4                   | 中央導電層                 |    |

| 2 0 6                   | トップサイド誘電体層            | 10 |

| 2 0 8                   | バックサイド誘電体層            |    |

| 2 2 2                   | キャビティ                 |    |

| 2 2 4                   | ダイ                    |    |

| 2 2 8、2 3 0、2 3 2、2 3 4 | 導電性パッド                |    |

| 2 3 6                   | トップサイド保護導電層           |    |

| 2 3 8                   | フィラー材料                |    |

| 2 4 0                   | トップサイド積層              |    |

| 2 4 2                   | バックサイド積層              |    |

| 2 6 4                   | 第 1 の基板貫通ビア ( T S V ) |    |

| 2 6 6                   | 第 2 の T S V           | 20 |

| 2 6 8                   | バックサイド導電性パッド          |    |

| 2 7 0                   | バックサイド保護導電層           |    |

| 2 7 2、2 7 4             | 相互接続部                 |    |

| 2 8 0                   | パッドまたはトレース            |    |

| 3 0 0                   | E D S                 |    |

| 3 0 1                   | 第 1 の面                |    |

| 3 0 2                   | 基板                    |    |

| 3 0 3                   | 第 2 の面                |    |

| 3 0 4                   | 導電層                   |    |

| 3 0 6                   | 第 1 の誘電体層             | 30 |

| 3 0 8                   | 第 2 の誘電体層             |    |

| 3 1 0                   | 第 1 の単一セグメントダイ貫通相互接続部 |    |

| 3 1 0 H                 | 第 1 の穴                |    |

| 3 1 2                   | 第 2 の相互接続部            |    |

| 3 1 4                   | 第 3 の相互接続部            |    |

| 3 1 6                   | 第 4 の単一セグメントダイ貫通相互接続部 |    |

| 3 1 6 H                 | 第 4 の穴                |    |

| 3 2 2                   | キャビティ                 |    |

| 3 2 4                   | ダイ                    |    |

| 3 2 6                   | 接着剤、はんだ、またはエポキシ       | 40 |

| 3 2 8                   | 第 1 の導電性パッド           |    |

| 3 3 0、3 3 2、3 3 4       | 導電性パッド                |    |

| 3 3 6                   | 保護導電性パッド              |    |

| 3 3 8                   | フィラー材料                |    |

| 3 4 0                   | 第 1 の積層               |    |

| 3 4 2                   | 第 2 の積層               |    |

| 3 6 4                   | 第 1 のノード              |    |

| 3 6 6                   | バックサイドパッドまたはトレース      |    |

| 3 7 0                   | 第 4 のノード              |    |

| 3 7 6                   | 伝導経路                  | 50 |

|                         |                       |    |

|-------------------------|-----------------------|----|

| 3 7 8                   | 伝導経路                  |    |

| 3 8 2                   | M 1 層                 |    |

| 3 8 4                   | M 2 層                 |    |

| 3 8 6                   | M 3 層                 |    |

| 3 8 8                   | M 4 層                 |    |

| 4 0 0                   | E D S                 |    |

| 4 0 1                   | 第 1 の面                |    |

| 4 0 2                   | 基板                    |    |

| 4 0 3                   | 第 2 の面                |    |

| 4 0 4                   | 導電層                   | 10 |

| 4 0 6                   | 第 1 の誘電体層             |    |

| 4 0 8                   | 第 2 の誘電体層             |    |

| 4 1 0                   | 第 1 の相互接続部            |    |

| 4 1 0 H                 | 第 1 の穴                |    |

| 4 1 1、4 1 7             | 第 1 の端部               |    |

| 4 1 2                   | 第 2 の相互接続部            |    |

| 4 1 4                   | 第 3 の相互接続部            |    |

| 4 1 6                   | 第 4 の相互接続部            |    |

| 4 1 6 H                 | 第 4 の穴                |    |

| 4 2 2                   | キャビティ                 | 20 |

| 4 2 4                   | ダイ                    |    |

| 4 2 6                   | 接着剤、はんだ、またはエポキシ       |    |

| 4 2 8、4 3 0、4 3 2、4 3 4 | 導電性パッド                |    |

| 4 3 6                   | 保護導電性パッド              |    |

| 4 3 8                   | フィラー材料                |    |

| 4 4 0                   | 第 1 の積層               |    |

| 4 4 2                   | 第 2 の積層               |    |

| 4 6 7                   | パッドまたはトレース            |    |

| 4 7 6、4 7 8             | 伝導経路                  |    |

| 4 8 2                   | M 1 層                 | 30 |

| 4 8 4                   | M 2 層                 |    |

| 4 8 6                   | M 3 層                 |    |

| 4 8 8                   | M 4 層                 |    |

| 5 2 4                   | ダイ                    |    |

| 5 2 5                   | 領域                    |    |

| 5 2 7                   | ガード領域                 |    |

| 6 0 0                   | 第 1 の E D S           |    |

| 6 0 2                   | 第 1 の位置               |    |

| 6 0 4                   | 第 2 の位置               |    |

| 6 2 4                   | 領域                    | 40 |

| 6 2 5                   | 領域                    |    |

| 7 0 1                   | 第 1 の面                |    |

| 7 0 2                   | 基板                    |    |

| 7 0 3                   | 第 2 の面                |    |

| 7 0 4                   | 導電層                   |    |

| 7 0 6                   | 第 1 の誘電体層             |    |

| 7 0 8                   | 第 2 の誘電体層             |    |

| 7 1 0                   | 第 1 の単一セグメントダイ貫通相互接続部 |    |

| 7 1 0 H                 | 内側穴                   |    |

| 7 1 1、7 1 3             | 導電性材料                 | 50 |

|                                |    |

|--------------------------------|----|

| 7 1 1 H、7 1 3 H 穴              |    |

| 7 1 2 H 第1のトップサイド内側穴           |    |

| 7 1 4 H 第2のトップサイド内側穴           |    |

| 7 1 5 パッドまたはトレース               |    |

| 7 1 6 第4の単一セグメントダイ貫通相互接続部      |    |

| 7 1 7 パッドまたはトレース               |    |

| 7 1 8 第1のセグメント化相互接続部           |    |

| 7 2 2 キャビティ                    |    |

| 7 2 4 ダイ                       |    |

| 7 2 6 接着剤、はんだ、またはエポキシ          | 10 |

| 7 2 8、7 3 0、7 3 2、7 3 4 導電性パッド |    |

| 7 3 6 レーザーストップ層                |    |

| 7 3 8 フィラー材料                   |    |

| 7 4 0 第1の積層                    |    |

| 7 4 2 第2の積層                    |    |

| 7 4 6 H 第2のトップサイド外側穴           |    |

| 7 5 2 導電性材料                    |    |

| 7 5 2 H 第1のトップサイド外側穴           |    |

| 7 5 6 H 第2の外側穴                 |    |

| 7 6 0 パッドまたはトレース               | 20 |

| 7 6 2 導電性材料                    |    |

| 7 6 2 H 第1の外側穴                 |    |

| 7 6 4 第1のノード                   |    |

| 7 6 6 第2のノード                   |    |

| 7 7 0 第4のノード                   |    |

| 7 8 2 M 1 層                    |    |

| 7 8 4 M 2 層                    |    |

| 7 8 6 M 3 層                    |    |

| 7 8 8 M 4 層                    |    |

| 7 9 0 第1の水平トレース                | 30 |

| 7 9 2 第2の水平トレース                |    |

| M 1、M 2、M 3、M 4 メタライゼーション層     |    |

| 1 1 0 0 単一セグメントダイ貫通相互接続部       |    |

| 1 1 0 2 モバイル電話デバイス             |    |

| 1 1 0 6 ラップトップコンピュータデバイス       |    |

| 1 1 0 8 装着型デバイス                |    |

【図1】

FIG. 1

【図2】

**FIG. 2**

【図 5 A】

FIG. 5A

【 5 B 】

FIG. 5B

【図3】

FIG. 3

【図4】

FIG. 4

〔 四 6 A 〕

FIG. 6A

(図 6 B)

FIG. 6B

【図7A】

【図7B】

【図7C】

【図8】

【図9】

【図10】

【図11】

**FIG. 11**

---

フロントページの続き

(72)発明者 ジエ・フ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 チャンハン・ユン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 チン・クアン・キム

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 マニュエル・アルドレー・テ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 チェンジエ・ズオ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 マリオ・ベレス

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 ジョンヘ・キム

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

審査官 正山 旭

(56)参考文献 特開2006-245574(JP,A)

米国特許出願公開第2015/0318246(US,A1)

米国特許出願公開第2016/0013151(US,A1)

米国特許出願公開第2008/0048310(US,A1)

独国特許出願公開第102014112407(DE,A1)

米国特許出願公開第2004/0113261(US,A1)

中国特許第101563773(CN,B)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H05K 1/02

H05K 3/46