(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4908006号

(P4908006)

(45) 発行日 平成24年4月4日(2012.4.4)

(24) 登録日 平成24年1月20日(2012.1.20)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| HO1L 27/04   | (2006.01) |

| HO1L 21/822  | (2006.01) |

| HO1L 27/06   | (2006.01) |

| HO1L 21/8234 | (2006.01) |

|            |      |

|------------|------|

| HO1L 27/04 | C    |

| HO1L 27/06 | 102A |

| HO1L 27/04 | G    |

請求項の数 5 (全 11 頁)

(21) 出願番号

特願2006-26782 (P2006-26782)

(22) 出願日

平成18年2月3日(2006.2.3)

(65) 公開番号

特開2007-208101 (P2007-208101A)

(43) 公開日

平成19年8月16日(2007.8.16)

審査請求日

平成20年8月5日(2008.8.5)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100075812

弁理士 吉武 賢次

(74) 代理人 100088889

弁理士 橋谷 英俊

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100096921

弁理士 吉元 弘

(74) 代理人 100103263

弁理士 川崎 康

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

MOS構造のドレイン領域とソース領域とが共通に接続され、この共通に接続された前記ドレイン領域、前記ソース領域と前記MOS構造のゲート電極との間に静電容量を形成するMOSキャパシタと、

前記MOSキャパシタ上に層間絶縁膜を介して形成され前記MOSキャパシタのゲート電極と接続されるとともに櫛歯状に延出した延出部を有する第1の櫛型配線、および、前記MOSキャパシタ上に層間絶縁膜を介して形成されるとともに前記第1の櫛型配線と線間絶縁膜を介して配置され前記ドレイン領域および前記ソース領域に接続されるとともに櫛歯状に延出した延出部を有する第2の櫛型配線、を有する配線キャパシタと、を備え、

前記第2の櫛型配線の延出部は、前記第1の櫛型配線の延出部と交互に並んで配置されているとともに、前記MOSキャパシタの前記ドレイン領域と前記ソース領域を結ぶチャネル方向に対して垂直に配置されていることを特徴とする半導体装置。

## 【請求項 2】

前記第1の櫛型配線と前記第2の櫛型配線とは、同じ配線層内に配置されていることを特徴とする請求項1に記載の半導体装置。

## 【請求項 3】

前記配線キャパシタは、前記第1の櫛型配線上に層間絶縁膜を介して形成され前記第1の櫛型配線とコンタクトで接続されるとともに櫛歯状に延出した延出部を有する第3の櫛型配線と、前記第2の櫛型配線上に層間絶縁膜を介して形成されるとともに前記第3の櫛

10

20

型配線と線間絶縁膜を介して配置され、前記第2の櫛型配線とコンタクトで接続されるとともに櫛歯状に延出した延出部を有する第4の櫛型配線と、が層間絶縁膜を介して積層された、多層配線層をさらに有し、

前記第4の櫛型配線の延出部は、前記第3の櫛型配線の延出部と交互に並んで配置されていることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記第2の櫛型配線の延出部は、前記ドレイン領域および前記ソース領域と複数のコンタクトで接続されていることを特徴とする請求項1ないし3の何れかに記載の半導体装置。

【請求項5】

MOS構造のドレイン領域とソース領域とが共通に接続され、この共通に接続された前記ドレイン領域、ソース領域と前記MOS構造のゲート電極との間に静電容量を形成するMOSキャパシタと、前記MOSキャパシタ上に層間絶縁膜を介して形成され前記MOSキャパシタのゲート電極と接続されるとともに櫛歯状に延出した延出部を有する第1の櫛型配線、および、前記MOSキャパシタ上に層間絶縁膜を介して形成されるとともに前記第1の櫛型配線と線間絶縁膜を介して配置され前記ドレイン領域および前記ソース領域に接続されるとともに櫛歯状に延出した延出部を有する第2の櫛型配線、を有する配線キャパシタと、を備え、前記第2の櫛型配線の延出部は、前記第1の櫛型配線の延出部と交互に並んで配置されているとともに、前記MOSキャパシタの前記ドレイン領域と前記ソース領域を結ぶチャネル方向に対して垂直に配置された半導体装置と、

電源電圧が印加される入力端子にソース領域が接続された入力MOSトランジスタと、

前記入力MOSトランジスタのドレイン領域と昇圧された電圧が出力される出力端子との間で直列に接続された複数の昇圧MOSトランジスタと、を備え、

前記昇圧MOSトランジスタのソース領域に各々前記第1の櫛型配線が接続され、

隣接する前記半導体装置の前記第2の櫛型配線には、それぞれ互いに相補的なパルス信号が入力されることを特徴とするチャージポンプ回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体基板上に形成されるMOSキャパシタを備えた半導体装置に関するものである。

【背景技術】

【0002】

従来、半導体基板上に形成されるキャパシタ素子には、MOSキャパシタやPIP(Poly-Insulator-Poly)キャパシタ、MIM(Metal-Insulator-Metal)キャパシタ等がある。これらのうちPIPキャパシタやMIMキャパシタは、電極間に挟まれる誘電体層に、より誘電率の高い材料が使用される。したがって、製造プロセスが増加したり、プロセスコストが高くなったりする場合がある。このためCMOSプロセスで作成する回路には、他のMOSトランジスタと整合させることを考えて、MOSキャパシタを使用することが多い。

【0003】

上記従来のMOSキャパシタには、p型半導体基板と、このp型半導体基板に形成されたn型ウェルと、このn型ウェルに形成されたn<sup>+</sup>拡散層と、n型ウェル上に設けられたゲート絶縁膜と、このゲート絶縁膜上に設けられたポリシリコンまたは金属で形成されたゲート電極と、このゲート電極上に設けられるとともにコンタクトにより接続された第1の金属配線層と、この第1の金属配線層上に設けられるとともにコンタクトによりn<sup>+</sup>拡散層にコンタクトにより接続された第2の金属配線層と、を備えるものがある(例えば、特許文献1参照。)。

【0004】

このような構造により、ゲート絶縁膜を挟んでゲート電極とP型半導体基板との間に静

10

20

30

40

50

電容量が形成され、MOSキャパシタとして機能するものである。このMOSキャパシタは、薄いゲート絶縁膜を有するため、比較的大きな静電容量が得られる。

【0005】

上記のようなMOS構造を持つMOSキャパシタのC-V特性は、ゲート電圧  $V_g < 0$  のときは、ゲート電極直下のシリコン表面に空乏層が形成され、それにより生じる空乏層容量とゲート絶縁膜容量が直列接続された状態になる。そのため全体容量Cが減少する。

【0006】

しかし、 $0 < V_g$  ではn型ウェル内に浮遊している電子がシリコン表面近傍に引き寄せられるため、全体容量Cはゲート絶縁膜の容量に等しくなっていく。

【0007】

このようにMOSキャパシタはその印加電圧の変化により容量値が変動する電圧依存性を持っている。

【0008】

さらに、C-V特性は、電源周波数が低周波の場合と、高周波の場合とは異なる。この理由は高周波の場合、MOSキャパシタのオンオフの切り替えが早いので反転層にキャリアが溜まるまでの時間がなく、反転層の容量がないのと同じ状態になるためである。

【0009】

ここで、既述のようなMOSキャパシタは、昇圧電源を生成するチャージポンプ回路などによく用いられる。チャージポンプ回路は、低電圧電源を昇圧して内部回路に高電圧を供給する回路である。このチャージポンプ回路で利用されるMOSキャパシタは、そのゲート電極に印加される電圧の変化により容量値が変動する電圧依存性を有し、したがって、チャージポンプの昇圧能力が制限されるという問題がある。

【0010】

さらに、MOSキャパシタは、チャージポンプ回路のポンプ動作による充放電によりその電圧が常に変動する。MOSキャパシタのチャネル領域は、拡散層やウェルの抵抗値が高い。これにより、印加される電圧が変化してから所望の容量になるまでに時間を要する。したがって、MOSキャパシタの周波数特性にも十分注意しなければならないという問題があった。

【特許文献1】特開2002-217304号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

本発明は、上記課題を解決するものであり、容量値の電圧依存性を低減しつつ、容量値の周波数特性を向上することが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明の一態様に係る半導体装置は、

MOS構造のドレイン領域とソース領域とが共通に接続され、この共通に接続された前記ドレイン領域、前記ソース領域と前記MOS構造のゲート電極との間に静電容量を形成するMOSキャパシタと、

前記MOSキャパシタ上に層間絶縁膜を介して形成され前記MOSキャパシタのゲート電極と接続されるとともに櫛歯状に延出した延出部を有する第1の櫛型配線、および、前記MOSキャパシタ上に層間絶縁膜を介して形成されるとともに前記第1の櫛型配線と線間絶縁膜を介して配置され前記ドレイン領域および前記ソース領域に接続されるとともに櫛歯状に延出した延出部を有する第2の櫛型配線、を有する配線キャパシタと、を備え、

前記第2の櫛型配線の延出部は、前記第1の櫛型配線の延出部と交互に並んで配置されているとともに、前記MOSキャパシタの前記ドレイン領域と前記ソース領域を結ぶチャネル方向に対して垂直に配置されていることを特徴とする。

【0013】

また、本発明の一態様に係るチャージポンプ回路は、

10

20

30

40

50

MOS構造のドレイン領域とソース領域とが共通に接続され、この共通に接続された前記ドレイン領域、ソース領域と前記MOS構造のゲート電極との間に静電容量を形成するMOSキャパシタと、前記MOSキャパシタ上に層間絶縁膜を介して形成され前記MOSキャパシタのゲート電極と接続されるとともに櫛歯状に延出した延出部を有する第1の櫛型配線、および、前記MOSキャパシタ上に層間絶縁膜を介して形成されるとともに前記第1の櫛型配線と線間絶縁膜を介して配置され前記ドレイン領域および前記ソース領域に接続されるとともに櫛歯状に延出した延出部を有する第2の櫛型配線、を有する配線キャパシタと、を備え、前記第2の櫛型配線の延出部は、前記第1の櫛型配線の延出部と交互に並んで配置されているとともに、前記MOSキャパシタの前記ドレイン領域と前記ソース領域を結ぶチャネル方向に対して垂直に配置された半導体装置と、

10

電源電圧が印加される入力端子にソース領域が接続された入力MOSトランジスタと、前記入力MOSトランジスタのドレイン領域と昇圧された電圧が出力される出力端子との間で直列に接続された複数の昇圧MOSトランジスタと、を備え、

前記昇圧MOSトランジスタのソース領域に各々前記第1の櫛型配線が接続され、隣接する前記半導体装置の前記第2の櫛型配線には、それぞれ互いに相補的なパルス信号が入力されることを特徴とする。

#### 【発明の効果】

#### 【0014】

本発明の一態様に係る半導体装置によれば、容量値の電圧依存性を低減しつつ、容量値の周波数特性の向上を図ることができる。

20

#### 【発明を実施するための最良の形態】

#### 【0015】

本発明の一態様に係る半導体装置は、例えば、MOSキャパシタと、このMOSキャパシタ上に形成される金属の配線層を櫛型形状にし、対向する電極から延出する延出部を交互に配置して構成される配線キャパシタと、を備える。これにより、半導体装置は、印加電圧により変動するMOSキャパシタの容量を配線キャパシタの容量により補うものである。

#### 【0016】

以下、本発明を適用した各実施例について図面を参照しながら説明する。

#### 【実施例1】

30

#### 【0017】

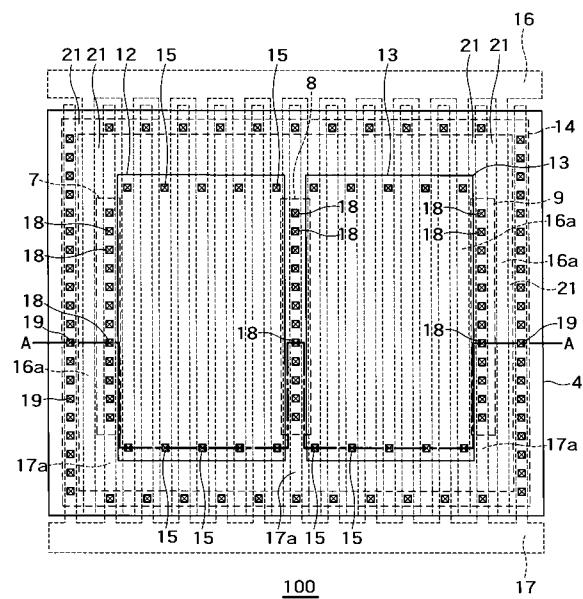

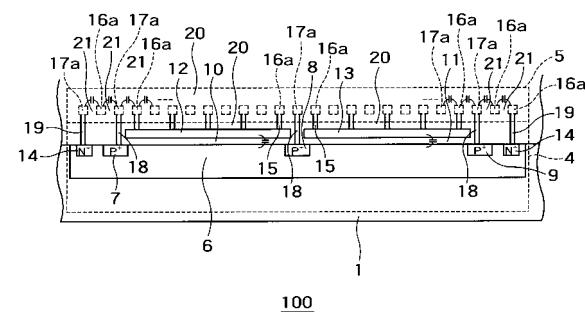

図1は、本発明の実施例1に係る半導体装置の要部の構成を示す平面図である。また、図2は、図1の半導体装置100のA-A線に沿った断面図である。

#### 【0018】

なお、ここでは、2つのMOS構造によりMOSキャパシタが構成される場合について説明する。また、MOSキャパシタがp型半導体基板上に設けられた場合について説明するが、導電型を逆にした場合でも適用される回路の極性を逆にすることにより同様に適用される。

#### 【0019】

図1および図2に示すように、半導体装置100は、p型半導体基板1に形成されたMOS構造から構成されるMOSキャパシタ4と、このMOSキャパシタ4上に設けられた配線キャパシタ5とを備える。

40

#### 【0020】

上記MOS構造は、p型半導体基板1に形成されたn型ウェル6と、このn型ウェル6の表面に選択的に並んで形成されたドレイン領域、ソース領域となるp<sup>+</sup>拡散層7、8、9と、このp<sup>+</sup>拡散層7、8、9に挟まれた領域上に設けられたゲート絶縁膜10、11と、このゲート絶縁膜10、11上に設けられたゲート電極12、13と、バックゲートに電圧を印加するためのp<sup>+</sup>拡散層7、8、9を囲むようにn型ウェル6に形成されたn<sup>+</sup>拡散層14とを有する。

#### 【0021】

50

MOSキャパシタ4は、上記MOS構造のドレイン領域となるp<sup>+</sup>拡散層7とソース領域となるp<sup>+</sup>拡散層8とが共通に接続されている。同様に、MOSキャパシタ4は、MOS構造のソース領域となるp<sup>+</sup>拡散層8とドレイン領域となるp<sup>+</sup>拡散層9とが共通に接続されている。

【0022】

配線キャパシタ5は、MOSキャパシタ4上に層間絶縁膜20を介して形成され、MOSキャパシタ4のゲート電極12、13とコンタクト15で接続されるとともに櫛歯状に延出した延出部16aを有する第1の櫛型配線16を有する。さらに、配線キャパシタ5は、MOSキャパシタ4上に層間絶縁膜20を介して形成されるとともに第1の櫛型配線16と線間絶縁膜21を介して配置され、p<sup>+</sup>拡散層7、8、9およびn<sup>+</sup>拡散層14に複数のコンタクト18、19で接続されるとともに櫛歯状に延出した延出部17aを有する第2の櫛型配線17、を有する。この第2の櫛型配線17と第1の櫛型配線16とは、対向して配置されている。

【0023】

第2の櫛型配線17の延出部17aは、第1の櫛型配線16の延出部16aと交互に並んで配置されている。さらに、第2の櫛型配線17の延出部17aは、MOSキャパシタ4のドレイン領域となるp<sup>+</sup>拡散層7とソース領域となるp<sup>+</sup>拡散層8を結ぶチャネル方向に対して、同様にソース領域となるp<sup>+</sup>拡散層8とドレイン領域となるp<sup>+</sup>拡散層9を結ぶチャネル方向に対して、垂直に配置されている。

【0024】

ここで、既述のように、第2の櫛型配線17の延出部17aは、線間絶縁膜21を介して第1の櫛型配線16の延出部16aと交互に並んで配置されている。そして、第1の櫛型配線16と第2の櫛型配線17とは、同じ配線層内に配置されている。これにより、第1の櫛型配線16の延出部16aと第2の櫛型配線17の延出部17aとが接近し、延出部16aと延出部17aとの間の線間絶縁膜21の容量を増加することができる。

【0025】

また、既述のように、第2の櫛型配線17の延出部17aは、MOSキャパシタ4のチャネル方向に対して垂直に配置されているので、第2の櫛型配線17の延出部17aは、p<sup>+</sup>拡散層7、8、9と複数のコンタクト18で接続することができる。これにより、コンタクト18によるコンタクト抵抗を低減することができる。

【0026】

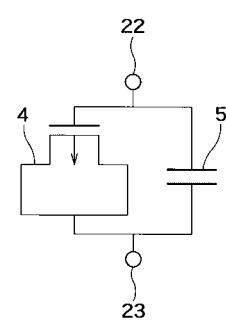

以上のような構成を有する半導体装置100の回路図は図3のように示される。図3に示すように、所望の電圧が印加される端子22と端子23の間に、MOSキャパシタ4と配線キャパシタ5とが接続される。

【0027】

ここで、以上のような構成を有する半導体装置100の電圧依存性について説明する。

【0028】

まず、MOSキャパシタ4は、ゲート電圧Vg < 0のときは、チャネルが形成されないが、アキュムレーション(accumulation)と呼ばれる蓄積状態であり空乏層が形成されないため容量Cは、ほぼゲート絶縁膜10、11の容量に等しい。したがって、半導体装置100の全体容量は、ほぼゲート絶縁膜10、11の容量と配線キャパシタ5の容量との和になる。

【0029】

次に、MOSキャパシタ4は、0 < ゲート電圧Vg < しきい値電圧Vtのときは、ゲート電極直下のシリコン表面に空乏層が形成され、それにより生じる空乏層容量とゲート絶縁膜容量が直列接続された状態になる。したがって、MOSキャパシタ4の容量Cはゲート絶縁膜10、11の容量よりも小さくなる。しかし、配線キャパシタ5に形成される容量はゲート電圧に関係なく維持される。したがって、配線キャパシタ5を含めた半導体装置100の全体の容量として考えると、従来と比較して、電圧依存性を低減することができる。

10

20

30

40

50

## 【0030】

次に、MOSキャパシタ4は、しきい値 $V_t$ 以上のゲート電圧が印加されチャネルが形成されると、共通に接続された $p^+$ 拡散層7、8、9とMOS構造のゲート電極12、13との間にゲート絶縁膜10、11の静電容量を形成する。したがって、MOSキャパシタ4の容量Cは、ほぼゲート絶縁膜10、11の容量に等しい。これにより、半導体装置100の全体容量は、ほぼゲート絶縁膜10、11の容量と配線キャパシタ5の容量との和になる。

## 【0031】

以上のように、半導体装置100は、従来と比較して、容量を増加しつつ、電圧依存性を低減することができる。

10

## 【0032】

次に、以上のような構成を有する半導体装置100の周波数特性について説明する。

## 【0033】

まず、MOSキャパシタ4は、電源周波数が低周波である場合、MOSキャパシタ4のオンオフの切り替えで十分に反転層にキャリアが溜まるので反転層の容量が生じる。したがって、半導体装置100の全体容量は、ほぼゲート絶縁膜10、11の容量と配線キャパシタ5の容量との和になる。

## 【0034】

一方、MOSキャパシタ4は、電源周波数が低周波である場合、MOSキャパシタ4のオンオフの切り替えが速く反転層にキャリアが溜まらず反転層の容量が生じないことになる。しかし、配線キャパシタ5に形成される容量は電源周波数に関係なく維持される。したがって、配線キャパシタ5を含めた半導体装置100の全体の容量として考えると、従来と比較して、周波数特性を向上することができる。

20

## 【0035】

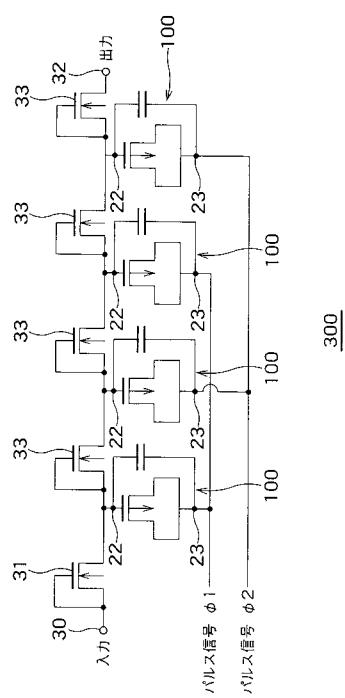

ここで、上記半導体装置100をチャージポンプ回路に適用した一例について説明する。

## 【0036】

図4は、本発明の実施例1に係る半導体装置を適用したチャージポンプ回路300を示す回路図である。

30

## 【0037】

図4に示すように、チャージポンプ回路300は、電源電圧が印加される入力端子30にソース領域が接続されるとともに、このソース領域にゲート電極が接続された入力MOSトランジスタ31と、この入力MOSトランジスタ31のドレイン領域と昇圧された電圧が出力される出力端子32との間で直列に接続されるとともにそのゲート電極がそのソース領域に接続された複数の昇圧MOSトランジスタ33と、この昇圧MOSトランジスタ33のソースに各々端子22(図2の第1の櫛型配線16)が接続された請求項1ないし4の何れかに記載の前記半導体装置と、を備える。

## 【0038】

隣接する半導体装置100の端子23(図2の第2の櫛型配線17)には、それぞれ互いに相補的なパルス信号1、2が入力される。

40

## 【0039】

上記チャージポンプ回路300は、入力端子に電源電圧が印加されるとともに相補的なクロック信号1、2が端子23にそれぞれ入力されると、昇圧動作し、出力端子32から昇圧された電圧を出力する。

## 【0040】

ここで、既述のように、半導体装置100は、従来のMOSキャパシタと比較して容量の電圧依存性が低減され周波数特性が向上されている。したがって、上記構成を有するチャージポンプ回路300は、従来と比較して、容量値の電圧依存性を低減しつつ容量値の周波数特性の向上し、昇圧能力を向上することができる。

## 【0041】

50

以上のように、本実施例に係る半導体装置によれば、容量値の電圧依存性を低減しつつ、容量値の周波数特性を向上することができる。

【実施例 2】

【0042】

実施例 1 では、配線キャパシタの櫛型配線の層が 1 層である場合について述べたが、本実施例では、配線キャパシタの櫛型配線の層が複数層である場合について述べる。

【0043】

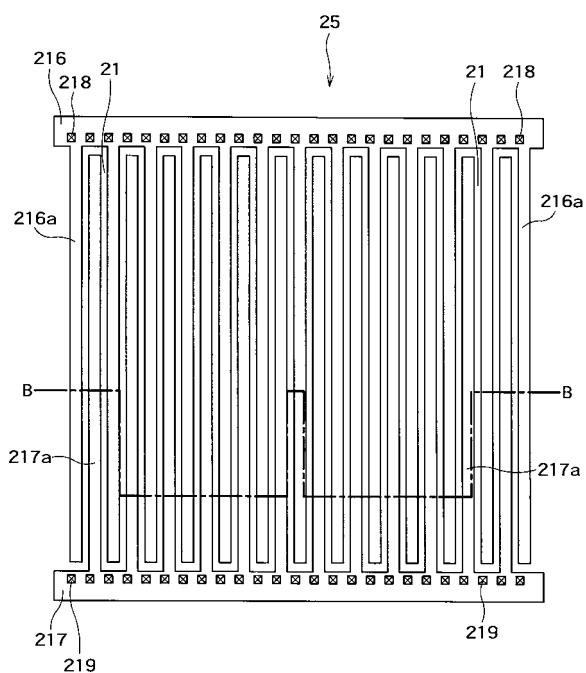

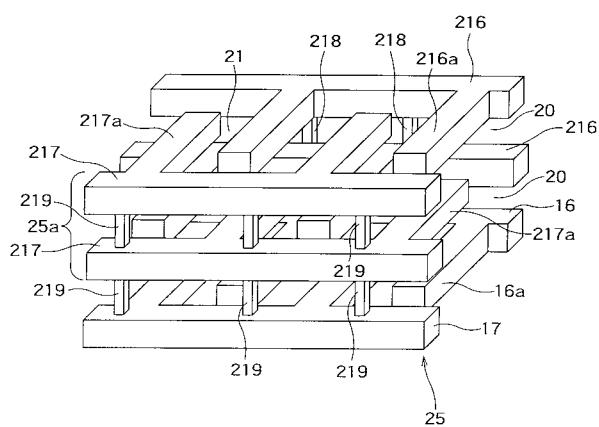

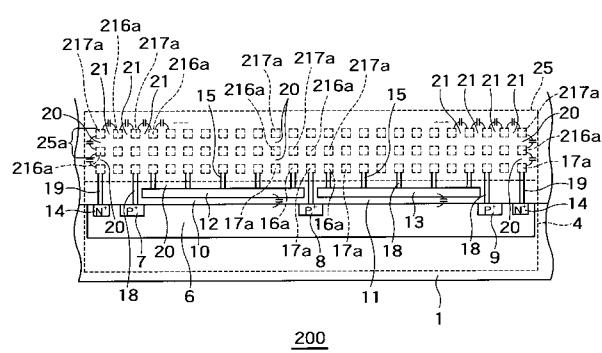

図 5 は、本発明の実施例 2 に係る半導体装置の配線キャパシタの要部構成を示す平面図である。また、図 6 は、図 5 の配線キャパシタの要部構成を示す斜視図である。また、図 7 は、図 5 の B - B 線に沿った本発明の一態様である実施例 2 に係る半導体装置 200 の断面を示す断面図である。なお、図中、実施例 1 と同じ符号は、実施例 1 と同様の構成を示している。また、図 5 において、説明のため配線キャパシタの下層側については省略している。

【0044】

図 5 ないし図 7 に示すように、半導体装置 200 は、p 型半導体基板 1 に形成された MOS 構造で構成される MOS キャパシタ 4 と、この MOS キャパシタ 4 上に設けられた配線キャパシタ 25 を備える。

【0045】

図 6、図 7 に示すように、配線キャパシタ 25 は、MOS キャパシタ 4 上に層間絶縁膜 20 を介して形成され、MOS キャパシタ 4 のゲート電極 12、13 とコンタクト 15 で接続されるとともに櫛歯状に延出した延出部 16a を有する第 1 の櫛型配線 16 を有する。

【0046】

さらに、配線キャパシタ 25 は、MOS キャパシタ 4 上に層間絶縁膜 20 を介して形成されるとともに第 1 の櫛型配線 16 と線間絶縁膜 21 を介して配置され、p<sup>+</sup> 拡散層 7、8、9 および n<sup>+</sup> 拡散層 14 に複数のコンタクト 18、19 で接続されるとともに櫛歯状に延出した延出部 17a を有する第 2 の櫛型配線 17 を有する。

【0047】

また、配線キャパシタ 25 は、第 1 の櫛型配線 16 上に層間絶縁膜 20 を介して形成され、第 1 の櫛型配線 16 とコンタクト 218 で接続されるとともに櫛歯状に延出した延出部 216a を有する第 3 の櫛型配線 216 を有する。

【0048】

さらに、配線キャパシタ 25 は、第 2 の櫛型配線 17 上に層間絶縁膜 20 を介して形成されるとともに第 3 の櫛型配線 216 と線間絶縁膜 21 を介して配置され、第 2 の櫛型配線 17 とコンタクト 219 で接続されるとともに櫛歯状に延出した延出部 217a を有する第 4 の櫛型配線 217 を有する。

【0049】

すなわち、配線キャパシタ 25 は、実施例 1 の配線キャパシタ 5 と比較して、第 3 の櫛型配線 216 と第 4 の櫛型配線 217 とが層間絶縁膜 20 を介して交互に積層された、多層配線層 25a をさらに有する。

【0050】

ここで、図 5 ないし図 7 に示すように、第 4 の櫛型配線 217 の延出部 217a は、第 3 の櫛型配線 216 の延出部 216a と交互に並んで配置されている。そして、対となる第 3 の櫛型配線 216 と第 4 の櫛型配線 217 とは、同じ配線層内に配置されている。これにより、第 3 の櫛型配線 216 の延出部 216a と第 4 の櫛型配線 217 の延出部 217a とが接近し、延出部 216a と延出部 217a との間の線間絶縁膜 21 の静電容量を増加することができる。

【0051】

既述のように、第 4 の櫛型配線 217 の延出部 217a の下には層間絶縁膜 20 を介して第 1 の櫛型配線 16 の延出部 16a が位置するとともに、第 4 の櫛型配線 217 の延出

10

20

30

40

50

部 217a の上には層間絶縁膜 20 を介して第 3 の櫛型配線 216 の延出部 216a が位置している。

【 0052 】

したがって、配線キャパシタ 25 の容量としては、これらの層間絶縁膜 20 の静電容量も含まれると考えられる。

【 0053 】

以上のような構成を有する半導体装置 200 の回路図は、実施例 1 と同様に図 3 のように示される。

【 0054 】

また、以上のような構成を有する半導体装置 200 の周波数特性、電圧依存性について 10 も、配線キャパシタ 25 による容量が増加する点以外は、実施例 1 と同様である。

【 0055 】

以上のように、本実施例に係る半導体装置によれば、容量値の電圧依存性を低減し容量値の周波数特性を向上しつつ、実施例 1 よりも大きな容量を得ることができる。

【 0056 】

なお、本実施例についても、実施例 1 と同様にチャージポンプ回路に適用することにより、従来と比較して、容量値の電圧依存性を低減しつつ容量値の周波数特性の向上し、昇圧能力を向上することができる。

【 0057 】

また、本実施例においては、配線キャパシタの櫛型配線の多層配線層が 2 層である場合について説明したが、多層配線層を 3 層以上積層することにより、より有効にレイアウト面積を維持しつつ大きな静電容量を得ることができる。 20

【 図面の簡単な説明 】

【 0058 】

【 図 1 】本発明の一態様である実施例 1 に係る半導体装置の要部構成を示す平面図である。

【 図 2 】図 1 の半導体装置 100 の A - A 線に沿った断面を示す断面図である。

【 図 3 】本発明の一態様である実施例 1 に係る半導体装置 100 の回路図である。

【 図 4 】本発明の実施例 1 に係る半導体装置を適用したチャージポンプ回路 300 を示す回路図である。 30

【 図 5 】本発明の実施例 2 に係る半導体装置の配線キャパシタの要部構成を示す平面図である。

【 図 6 】図 5 の配線キャパシタの要部構成を示す斜視図である。

【 図 7 】図 5 の B - B 線に沿った本発明の一態様である実施例 2 に係る半導体装置の断面を示す断面図である。

【 符号の説明 】

【 0059 】

1 p 型半導体基板

4 M O S キャパシタ

5 配線キャパシタ

6 n 型ウェル

7、8、9 p<sup>+</sup> 拡散層

10、11 ゲート絶縁膜

12、13 ゲート電極

14 n<sup>+</sup> 拡散層

15 コンタクト

16 第 1 の櫛型配線

16a 延出部

17 第 2 の櫛型配線

17a 延出部

10

20

30

40

50

- 18、19 コンタクト

20 層間絶縁膜

21 線間絶縁膜

22、23 端子

25 配線キャパシタ

25a 多層配線層

30 入力端子

31 入力MOSトランジスタ

32 出力端子

33 昇圧MOSトランジスタ

100、200 半導体装置

216 第3の櫛型配線

216a 延出部

217 第4の櫛型配線

217a 延出部

218、219 コンタクト

300 チャージポンプ回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 和田 修

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 行川 敏正

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 中野 浩明

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 伊藤 洋

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 中山 篤

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

審査官 宇多川 勉

(56)参考文献 特開2000-057790 (JP, A)

特開2004-241762 (JP, A)

特開2002-217304 (JP, A)

特開2005-353760 (JP, A)

国際公開第98/43298 (WO, A1)

特表2002-532903 (JP, A)

特開平09-116027 (JP, A)

特開平04-073960 (JP, A)

特開平03-293759 (JP, A)

特開昭61-263251 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 21/8234

H01L 27/04

H01L 27/06