(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5632658号

(P5632658)

(45) 発行日 平成26年11月26日(2014.11.26)

(24) 登録日 平成26年10月17日(2014.10.17)

(51) Int.Cl.

F 1

|             |              |                  |      |      |      |

|-------------|--------------|------------------|------|------|------|

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 622M |

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/20 | 611J |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G09G | 3/20 | 621M |

|             |              |                  | G09G | 3/20 | 622B |

|             |              |                  | G09G | 3/20 | 622E |

請求項の数 5 (全 30 頁) 最終頁に続く

(21) 出願番号

特願2010-136754 (P2010-136754)

(22) 出願日

平成22年6月16日(2010.6.16)

(65) 公開番号

特開2011-28237 (P2011-28237A)

(43) 公開日

平成23年2月10日(2011.2.10)

審査請求日

平成25年6月14日(2013.6.14)

(31) 優先権主張番号

特願2009-150617 (P2009-150617)

(32) 優先日

平成21年6月25日(2009.6.25)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 梅崎 敦司

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 武田 悟

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の端子が第1の配線と電気的に接続された第1のトランジスタと、

第1の端子が前記第1のトランジスタの第2の端子と電気的に接続された第2のトランジスタと、

第1の端子が第2の配線と電気的に接続され、第2の端子が第3の配線と電気的に接続され、且つゲートが前記第1のトランジスタの第2の端子と電気的に接続された第3のトランジスタと、

第1の端子が前記第3の配線と電気的に接続された第4のトランジスタと、

第1の端子が前記第3の配線と電気的に接続された第5のトランジスタと、

第1の端子が前記第5のトランジスタの第2の端子と電気的に接続された第6のトランジスタと、

第1の端子が第4の配線と電気的に接続され、第2の端子が前記第2のトランジスタのゲートと電気的に接続され、且つゲートが前記第5のトランジスタの第2の端子と電気的に接続された第7のトランジスタと、

第1の端子が前記第7のトランジスタの第2の端子と電気的に接続された第8のトランジスタと、

第1の端子が前記第7のトランジスタの第2の端子と電気的に接続された第9のトランジスタと、

第1の端子が前記第9のトランジスタの第2の端子と電気的に接続された第10のトランジスタと、

第1の端子が前記第9のトランジスタの第2の端子と電気的に接続された第10のトランジ

10

20

ンジスタと、

第1の端子が前記第2の配線と電気的に接続され、第2の端子が第5の配線と電気的に接続され、且つゲートが前記第9のトランジスタの第2の端子と電気的に接続された第1のトランジスタと、

第1の端子が前記第5の配線と電気的に接続された第12のトランジスタと、を有し、

前記第1の配線は、スタートパルスを供給する機能を有し、

前記第2の配線は、第1のクロック信号を供給する機能を有し、

前記第3の配線は、第1の画素と電気的に接続され、

前記第4の配線は、第2のクロック信号を供給する機能を有し、

前記第5の配線は、第2の画素と電気的に接続され、

前記第3のトランジスタの第2の端子又は前記第4のトランジスタの第1の端子の負荷は、前記第7のトランジスタの第2の端子又は前記第8のトランジスタの第1の端子の負荷よりも大きく、

前記第1のトランジスタのチャネル幅は、前記第5のトランジスタのチャネル幅よりも大きいことを特徴とする表示装置。

【請求項2】

請求項1において、

前記第2のトランジスタのチャネル幅は、前記第6のトランジスタのチャネル幅よりも大きいことを特徴とする表示装置。

【請求項3】

請求項1又は請求項2において、

前記第3のトランジスタのチャネル幅は、前記第7のトランジスタのチャネル幅よりも大きいことを特徴とする表示装置。

【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記第4のトランジスタのチャネル幅は、前記第8のトランジスタのチャネル幅よりも大きいことを特徴とする表示装置。

【請求項5】

請求項1乃至請求項4のいずれか一項において、

前記第1乃至第8のトランジスタのいずれか一基は、酸化物半導体を有することを特徴とする表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の一態様は、アクティブマトリクス方式で駆動される表示装置に関する。また、当該表示装置を備えた電子機器に関する。

【背景技術】

【0002】

アクティブマトリクス方式で駆動される表示装置は、各画素にトランジスタ等のスイッチとして機能する素子と、該スイッチがオン時に画素に電気的に接続され、当該画素へ映像信号を出力する駆動回路(ソースドライバ)と、当該スイッチのスイッチングを制御する駆動回路(ゲートドライバ)とを有する。

【0003】

また、各画素のスイッチのみならずゲートドライバをトランジスタで構成することも可能である。そのため、絶縁基板上に設けられた非単結晶半導体を用いて形成されたトランジスタを用いて、各画素のスイッチ及びゲートドライバを構成した表示装置も開発されている。

【0004】

上述したゲートドライバは、表示装置の画素部に近接して設けられる。しかしながら、画素部の一辺に近接してゲートドライバが設けられる場合、表示部が表示装置の片側に偏

10

20

30

40

50

ることになる。そのため、ゲートドライバを画素部の左右に分割した構成の表示装置が開発されている（例えば、特許文献1参照）。

#### 【0005】

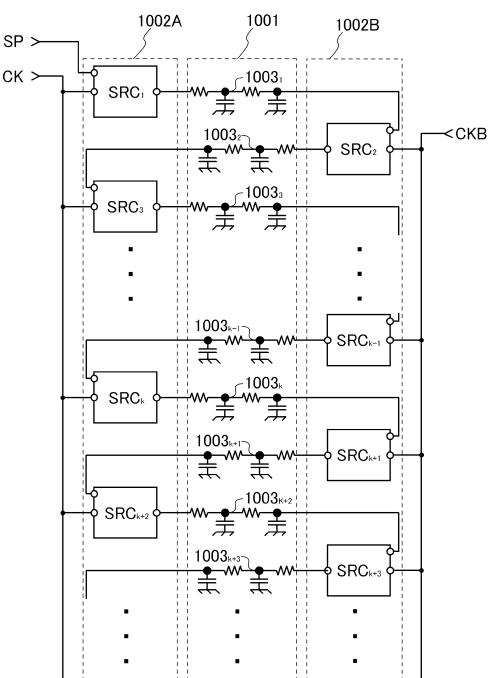

特許文献1で開示される表示装置の構成を図10に示す。図10に示した表示装置は、画素部1001を挟んで、第1のゲートドライバ1002Aと第2のゲートドライバ1002Bが対向するように設けられている。第1のゲートドライバ1002Aは、奇数行目のゲート線に出力端子が電気的に接続され、第2のゲートドライバ1002Bは、偶数行目のゲート線に出力端子が電気的に接続される。つまり、第1のゲートドライバ1002Aによって、画素部1001の奇数行に配列された画素とソースドライバの電気的な接続が制御され、第2のゲートドライバ1002Bによって、画素部の偶数行に配列された画素とソースドライバの電気的な接続が制御される。

10

#### 【0006】

さらに、第1のゲートドライバ1002A及び第2のゲートドライバ1002Bは、それぞれ複数のシフトレジスタを有する。第1のシフトレジスタ（SRC<sub>1</sub>）の出力端子は、第1のゲート線1003<sub>1</sub>を介して第2のシフトレジスタ（SRC<sub>2</sub>）の入力端子の一つに電気的に接続され、第2のシフトレジスタ（SRC<sub>2</sub>）の出力端子は、第2のゲート線1003<sub>2</sub>を介して第3のシフトレジスタ（SRC<sub>3</sub>）の入力端子の一つに電気的に接続される。以下、同様に第kのシフトレジスタ（SRC<sub>k</sub>）の出力端子は、第kのゲート線1003<sub>k</sub>を介して第k+1のシフトレジスタ（SRC<sub>k+1</sub>）の入力端子の一つに電気的に接続される。つまり、ある行に配置された画素のそれぞれとソースドライバとを電気的に接続させる信号が、出力端子が次の行に配列された画素のそれぞれと電気的に接続されたシフトレジスタのスタートパルス信号として用いられている。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

#### 【特許文献1】特許第4163416号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

画素部内に延在するゲート線には様々な寄生容量及び寄生抵抗が生じる。特に、画素部の高精細化によって、ゲート線に生じる寄生容量及び寄生抵抗の影響が大きくなる。上述したように、図10に示した表示装置は、ゲート線を介してシフトレジスタのスタートパルス信号が入力される。そのため、図10に示した表示装置は、高精細化又は大型化によって、信号が遅延又は鈍ってしまう可能性が高い表示装置であると言える。

30

#### 【0009】

上述した問題に鑑み、本発明の一態様は、良好な映像表示が可能な表示装置を提供することを課題の一とする。

#### 【0010】

また、本発明の一態様は、単極性のトランジスタを用いてゲートドライバが構成された表示装置を提供することを課題の一とする。

40

#### 【0011】

また、本発明の一態様は、回路面積が低減されたゲートドライバを有する表示装置を提供することを課題の一とする。

#### 【課題を解決するための手段】

#### 【0012】

本発明の一態様は、各々が平行又は略平行に配列された複数のゲート線と、ゲート線の奇数行目の各々に電気的に接続された第1のゲートドライバと、ゲート線の偶数行目の各々に電気的に接続された第2のゲートドライバと、を有し、第1のゲートドライバは、出力端子が第k（kは3以上の奇数）のゲート線に電気的に接続され、第1の入力端子が第k-2の転送信号生成回路の出力端子に電気的に接続され、第2の入力端子がクロック信

50

号線に電気的に接続され、第3の入力端子が第kのフリップフロップ回路用ストップパルス信号線に電気的に接続された、第kのフリップフロップ回路と、出力端子が第k+2のフリップフロップ回路の第1の入力端子に電気的に接続され、第1の入力端子が第kのフリップフロップ回路の出力端子に電気的に接続され、第2の入力端子が反転クロック信号線に電気的に接続され、第3の入力端子が第kの転送信号生成回路用ストップパルス信号線に電気的に接続された、第kの転送信号生成回路と、を有し、第2のゲートドライバは、出力端子が第k+1のゲート線に電気的に接続され、第1の入力端子が第k-1の転送信号生成回路の出力端子に電気的に接続され、第2の入力端子が前記反転クロック信号線に電気的に接続され、第3の入力端子が第k+1のフリップフロップ回路用ストップパルス信号線に電気的に接続された、第k+1のフリップフロップ回路と、出力端子が第k+3のフリップフロップ回路の第1の入力端子に電気的に接続され、第1の入力端子が前記第k+1のフリップフロップ回路の出力端子に電気的に接続され、第2の入力端子が前記クロック信号線に電気的に接続され、第3の入力端子が第kの転送信号生成回路用ストップパルス信号線に電気的に接続された、第k+1の転送信号生成回路と、を有する表示装置である。

【0013】

また、上記第kのフリップフロップ回路と上記第kの転送信号生成回路の回路構成が同一である表示装置も本発明の一態様である。

【0014】

なお、上述のストップパルス信号線とは、各回路にストップパルス信号を入力する配線である。

【0015】

具体的には、第kのフリップフロップ回路用ストップパルス信号として、第kの転送信号生成回路の出力信号を適用することができる。

【0016】

また、第kのフリップフロップ回路用ストップパルス信号として、第k+1のフリップフロップ回路の出力信号を適用することもできる。

【0017】

同様に、第kの転送信号生成回路用ストップパルス信号として、第k+2のフリップフロップ回路の出力信号を適用することができる。

【0018】

また、第kの転送信号生成回路用ストップパルス信号として、第k+1の転送信号生成回路の出力信号を適用することもできる。

【0019】

さらに、上記構成を有する表示装置を備えた電子機器も本発明の一態様である。

【発明の効果】

【0020】

本発明の一態様の表示装置が有する第1のゲートドライバ及び第2のゲートドライバは、入力された信号を半クロック周期遅らせて出力する転送信号生成回路を有する。そのため、信号の遅延又は鈍りが生じることがなく、良好な表示を行うことが可能な表示装置を提供することができる。

【図面の簡単な説明】

【0021】

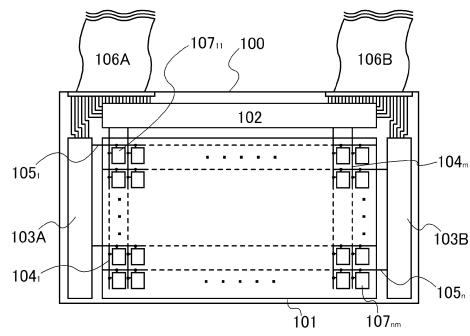

【図1】実施の形態1で説明する表示装置を示す図

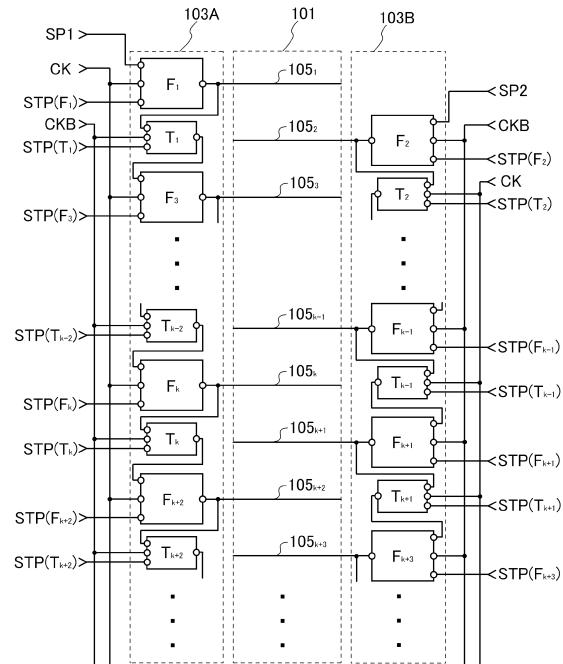

【図2】実施の形態1で説明するゲートドライバの構成を示す図

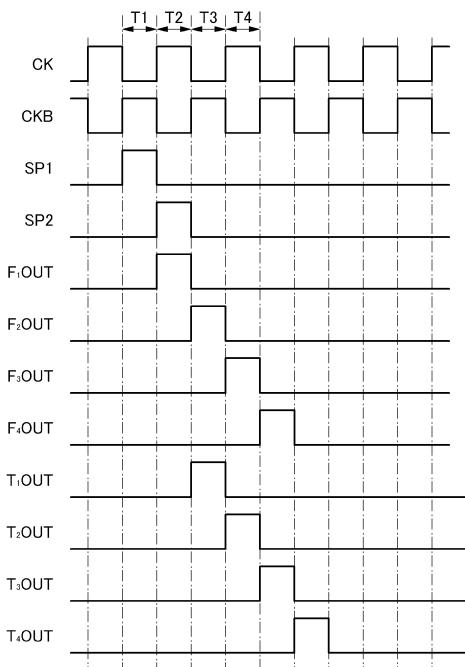

【図3】実施の形態1で説明するゲートドライバのタイミングチャートを示す図

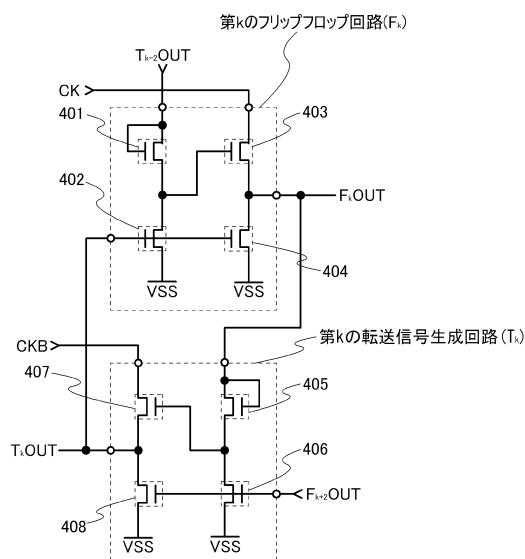

【図4】実施の形態2で説明する回路構成の具体例を示す図。

【図5】実施の形態2で説明する回路のタイミングチャートを示す図。

【図6】実施の形態3で説明する回路構成の具体例を示す図。

【図7】実施の形態3で説明するインバータ回路の具体例を示す図。

10

20

30

40

50

【図8】実施の形態4で説明する回路構成の具体例を示す図。

【図9】実施の形態4で説明する制御回路の具体例を示す図。

【図10】特許文献1のゲートドライバの構成を説明する図。

【図11】実施の形態6で説明する電子機器の具体例を示す図。

【図12】実施の形態6で説明する電子機器の具体例を示す図。

【図13】実施の形態6で説明する電子機器の具体例を示す図。

【図14】実施例1で説明する(A)従来の回路構成を示す図(B)本明細書の回路構成を示す図。

【図15】実施例1で説明する従来のゲートドライバのフリップフロップ回路の出力信号と本明細書で開示されるゲートドライバのフリップフロップ回路の出力信号を示す図。 10

【発明を実施するための形態】

【0022】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0023】

(実施の形態1)

本実施の形態では、本発明の一態様である表示装置の一例を示す。具体的には、第1及び第2のゲートドライバを有するアクティブマトリクス型の表示装置について図1乃至図3を用いて説明する。 20

【0024】

<表示装置の構成例>

図1は、アクティブマトリクス型の表示装置100を示す図である。表示装置100は、画素部101と、ソースドライバ102と、第1のゲートドライバ103Aと、第2のゲートドライバ103Bと、各々が平行又は略平行に配列されたm(mは正の整数)本のソース線104<sub>1</sub>～104<sub>m</sub>と、各々が平行又は略平行に配列されたn(nは正の整数)本のゲート線105<sub>1</sub>～105<sub>n</sub>とを有する。なお、画素部101は、表示装置100の中央部に設けられ、ソースドライバ102は、画素部101の一辺に近接して設けられ、第1のゲートドライバ103Aと第2のゲートドライバ103Bは、ソースドライバ102が設けられた辺とは異なる辺に近接し、且つ画素部101を間に挟んで対向するように設けられる。また、ソースドライバ102は、m本のソース線104<sub>1</sub>～104<sub>m</sub>を介して画素部101に電気的に接続され、第1のゲートドライバ103Aは、n本のゲート線105<sub>1</sub>～105<sub>n</sub>の奇数番目を介して、画素部101に電気的に接続され、第2のゲートドライバ103Bは、n本のゲート線105<sub>1</sub>～105<sub>n</sub>の偶数番目を介して、画素部101に電気的に接続される。 30

【0025】

また、ソースドライバ102、第1のゲートドライバ103A、及び第2のゲートドライバ103Bには、フレキシブルプリント基板106A、106Bを介して外部から信号(クロック信号、スタートパルス信号など)が入力される。 40

【0026】

さらに、画素部101は、n×m個の画素107<sub>1,1</sub>～107<sub>n,m</sub>を有する。なお、画素107<sub>1,1</sub>～107<sub>n,m</sub>は、n行m列に配列している。また、m本のソース線104<sub>1</sub>～104<sub>m</sub>の各々は、各列に配列したn個の画素に電気的に接続され、n本のゲート線105<sub>1</sub>～105<sub>n</sub>の各々は、各行に配列したm個の画素に電気的に接続される。別言すると、i行j列(i、jは正の整数、ただし1≤i≤n、1≤j≤m)に配置された画素107<sub>i,j</sub>は、ソース線104<sub>j</sub>及びゲート線105<sub>i</sub>に電気的に接続される。

【0027】

つまり、ソースドライバ102は、m本のソース線104<sub>1</sub>～104<sub>m</sub>を介して、画素部101が有する各画素に電気的に接続され、第1のゲートドライバ103Aは、n本の 50

ゲート線  $105_1 \sim 105_n$  の奇数番目を介して、画素部  $101$  が有する奇数行に配列された各画素に電気的に接続され、第 2 のゲートドライバ  $103B$  は、 $n$  本のゲート線  $105_1 \sim 105_n$  の偶数番目を介して、画素部  $101$  が有する偶数行に配列された各画素に電気的に接続される。

【0028】

<表示装置の動作例>

表示装置  $100$  において、ソースドライバ  $102$  は、画素部  $101$  が有する各画素  $107_{1,1} \sim 107_{n,m}$  へ映像信号を出力する回路であり、第 1 のゲートドライバ  $103A$  及び第 2 のゲートドライバ  $103B$  は、ソースドライバ  $102$  と画素  $107_{1,1} \sim 107_{n,m}$  の電気的な接続を制御する回路である。

10

【0029】

表示装置  $100$  は、 $n \times m$  個の画素  $107_{1,1} \sim 107_{n,m}$  の各々に映像信号を入力することで、画素部  $101$  に映像の表示をさせる。表示装置  $100$  の具体的な動作について以下に述べる。

【0030】

まず、第 1 のゲートドライバ  $103A$  が 1 行目に配列した  $m$  個の画素を選択し（ソースドライバ  $102$  と 1 行目に配列された  $m$  個の画素が電気的に接続され）、ソース線  $104_1 \sim 104_m$  を介して、1 行目に配列された  $m$  個の画素  $107_{1,1} \sim 107_{1,m}$  に映像信号が入力される。次いで、第 2 のゲートドライバ  $103B$  が 2 行目に配列された  $m$  個の画素を選択し、ソース線  $104_1 \sim 104_m$  を介して、2 行目に配列された  $m$  個の画素  $107_{2,1} \sim 107_{2,m}$  に映像信号が入力される。以下、同様にして第 1 のゲートドライバ  $103A$  及び第 2 のゲートドライバ  $103B$  が交互に各行の  $m$  個の画素を選択し、各画素に映像信号が入力される。表示装置  $100$  は、以上の動作を連続的に行うことによって、映像を表示している。

20

【0031】

<ゲートドライバの構成例>

図 2 は、アクティブマトリクス型の表示装置  $100$  が有する第 1 のゲートドライバ  $103A$  及び第 2 のゲートドライバ  $103B$  の詳細な構成例を示すブロック図である。

【0032】

第 1 のゲートドライバ  $103A$  及び第 2 のゲートドライバ  $103B$  は、少なくとも 3 つの入力端子と 1 つの出力端子を有するフリップフロップ回路及び転送信号生成回路をそれぞれ複数有する。

30

【0033】

第 1 のゲートドライバ  $103A$  が有する第 1 のフリップフロップ回路 ( $F_1$ ) は、出力端子が第 1 のゲート線  $105_1$  に電気的に接続され、第 1 の入力端子が第 1 のスタートパルス信号 ( $SP1$ ) 線に電気的に接続され、第 2 の入力端子がクロック信号 ( $CK$ ) 線に電気的に接続され、第 3 の入力端子が第 1 のフリップフロップ回路用ストップパルス信号 ( $STP(F_1)$ ) 線に電気的に接続される。

【0034】

また、第 1 のゲートドライバ  $103A$  が有する第 1 の転送信号生成回路 ( $T_1$ ) は、出力端子が第 3 のフリップフロップ回路 ( $F_3$ ) の第 1 の入力端子に電気的に接続され、第 1 の入力端子が第 1 のフリップフロップ回路 ( $F_1$ ) の出力端子に電気的に接続され、第 2 の入力端子が反転クロック信号 ( $CKB$ ) 線に電気的に接続され、第 3 の入力端子が第 1 の転送信号生成回路用ストップパルス信号 ( $STP(T_1)$ ) 線に電気的に接続される。

40

【0035】

第 2 のゲートドライバ  $103B$  が有する第 2 のフリップフロップ回路 ( $F_2$ ) は、出力端子が第 2 のゲート線  $105_2$  に電気的に接続され、第 1 の入力端子が第 2 のスタートパルス信号 ( $SP2$ ) 線に電気的に接続され、第 2 の入力端子が反転クロック信号 ( $CKB$ ) 線に電気的に接続され、第 3 の入力端子が第 2 のフリップフロップ回路用ストップパル

50

ス信号 (S T P (F<sub>2</sub>)) 線に電気的に接続される。

【0036】

また、第2のゲートドライバ103Bが有する第2の転送信号生成回路 (T<sub>2</sub>) は、出力端子が第4のフリップフロップ回路 (図示しない) の第1の入力端子に電気的に接続され、第1の入力端子が第2のフリップフロップ回路 (F<sub>2</sub>) の出力端子に電気的に接続され、第2の入力端子がクロック信号 (CK) 線に電気的に接続され、第3の入力端子が第2の転送信号用ストップパルス信号 (S T P (T<sub>2</sub>)) 線に電気的に接続される。

【0037】

第1のゲートドライバ103Aが有する第k (kは3以上の奇数) のフリップフロップ回路 (F<sub>k</sub>) は、出力端子が第kのゲート線105<sub>k</sub>に電気的に接続され、第1の入力端子が第k-2の転送信号生成回路 (T<sub>k-2</sub>) の出力端子に電気的に接続され、第2の入力端子がクロック信号 (CK) 線に電気的に接続され、第3の入力端子が第kのフリップフロップ回路用ストップパルス信号 (S T P (F<sub>k</sub>)) 線に電気的に接続される。

【0038】

また、第1のゲートドライバ103Aが有する第kの転送信号生成回路 (T<sub>k</sub>) は、出力端子が第k+2のフリップフロップ回路 (F<sub>k+2</sub>) に電気的に接続され、第1の入力端子が第kのフリップフロップ回路 (F<sub>k</sub>) の出力端子に電気的に接続され、第2の入力端子が反転クロック信号 (CKB) 線に電気的に接続され、第3の入力端子が第kの転送信号生成回路用ストップパルス信号 (S T P (T<sub>k</sub>)) 線に電気的に接続される。

【0039】

第2のゲートドライバ103Bが有する第k+1のフリップフロップ回路 (F<sub>k+1</sub>) は、出力端子が第k+1のゲート線105<sub>k+1</sub>に電気的に接続され、第1の入力端子が第k-1の転送信号生成回路 (T<sub>k-1</sub>) の出力端子に電気的に接続され、第2の入力端子が反転クロック信号 (CKB) 線に電気的に接続され、第3の入力端子が第k+1のフリップフロップ回路用ストップパルス信号 (S T P (F<sub>k+1</sub>)) 線に電気的に接続される。

【0040】

また、第2のゲートドライバ103Bが有する第k+1の転送信号生成回路 (T<sub>k+1</sub>) は、出力端子が第k+3のフリップフロップ回路 (F<sub>k+3</sub>) の第1の入力端子に電気的に接続され、第1の入力端子が第k+1のフリップフロップ回路 (F<sub>k+1</sub>) の出力端子に電気的に接続され、第2の入力端子がクロック信号 (CK) 線に電気的に接続され、第3の入力端子が第k+1の転送信号用ストップパルス信号 (S T P (T<sub>k+1</sub>)) 線に電気的に接続される。

【0041】

上述した第1のゲートドライバ103A及び第2のゲートドライバ103Bが有する複数のフリップフロップ回路と複数の転送信号生成回路は、それぞれの電気的な接続関係が共通する点と相違する点を有する。具体的な相違点について以下に列挙する。

【0042】

まず、第1のゲートドライバが有するフリップフロップ回路及び転送信号生成回路と、第2のゲートドライバが有するフリップフロップ回路及び転送信号生成回路とにおいて、電気的な接続関係が相違する点について述べる。

【0043】

第1のゲートドライバ103Aが有するフリップフロップ回路の第2の入力端子はクロック信号 (CK) 線に電気的に接続され、転送信号生成回路の第2の入力端子は反転クロック信号 (CKB) 線に電気的に接続されるのに対し、第2のゲートドライバ103Bが有するフリップフロップ回路の第2の入力端子は反転クロック信号 (CKB) 線に電気的に接続され、転送信号生成回路の第2の入力端子はクロック信号 (CK) 線に電気的に接続される。

【0044】

次いで、全てのフリップフロップ回路と転送信号生成回路において、電気的な接続関係

10

20

30

40

50

が相違する点について述べる。

【0045】

第1のフリップフロップ( $F_1$ )回路の出力端子が第1のゲート線 $105_1$ に電気的に接続されるのをはじめ、各フリップフロップ回路の出力端子は、同じ行に設けられたゲート線に電気的に接続される。一方、第1の転送信号生成回路( $T_1$ )の出力端子が第3のフリップフロップ回路( $F_3$ )の第1の入力端子に電気的に接続されるのをはじめ、各転送信号生成回路の出力端子は、下段に設けられたフリップフロップ回路の第1の入力端子に電気的に接続される。なお、上段に転送信号生成回路が設けられていない第1のフリップフロップ回路( $F_1$ )及び第2のフリップフロップ回路( $F_2$ )の第1の入力端子は、それぞれ第1のスタートパルス信号( $SP1$ )線及び第2のスタートパルス信号( $SP2$ )線に電気的に接続される。10

【0046】

また、全てのフリップフロップ回路の第3の入力端子及び転送信号生成回路の第3の入力端子は、それぞれ異なるストップパルス信号( $STP$ )線に電気的に接続される。

【0047】

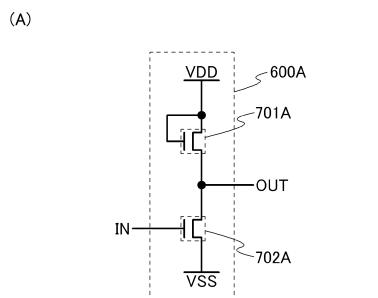

<ゲートドライバの動作例>

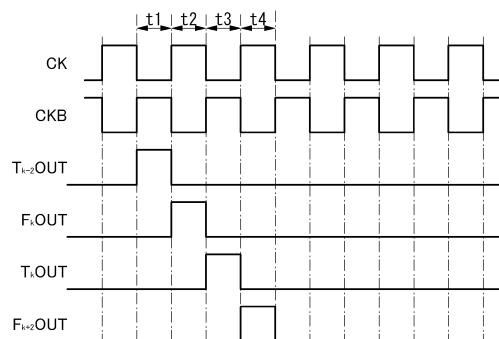

図3は、タイミングチャートを示す図である。なお、図3には、クロック信号( $CK$ )、反転クロック信号( $CKB$ )、第1のスタートパルス信号( $SP1$ )、第2のスタートパルス信号( $SP2$ )、第1のフリップフロップ回路の出力信号( $F_{1OUT}$ )乃至第4のフリップフロップ回路の出力信号( $F_{4OUT}$ )、及び第1の転送信号生成回路の出力信号( $T_{1OUT}$ )乃至第4の転送信号生成回路の出力信号( $T_{4OUT}$ )を示している。20なお、クロック信号( $CK$ )は、一定周期でハイ(以下、Hと示す)レベルの信号とロー(以下、Lと示す)レベルの信号を繰り返す信号であり、反転クロック信号( $CKB$ )は、クロック信号のHレベルとLレベルが反転した信号である。

【0048】

期間 $T1$ において、第1のスタートパルス信号( $SP1$ )がHレベルに上昇し、Hレベルの信号が第1のフリップフロップ回路( $F_1$ )の第1の入力端子に入力される。

【0049】

期間 $T2$ において、第2のスタートパルス信号( $SP2$ )がHレベルに上昇し、Hレベルの信号が第2のフリップフロップ回路( $F_2$ )の第1の入力端子に入力される。また、第1のフリップフロップ回路( $F_1$ )からHレベルの信号が出力される。なお、第1のフリップフロップ回路( $F_1$ )から出力されたHレベルの信号は、第1のゲート線 $105_1$ を介して、画素部 $101$ に配列された1行目の各画素 $107_{11} \sim 107_{1m}$ に入力される。これにより、1行目の各画素 $107_{11} \sim 107_{1m}$ とソースドライバ $102$ が電気的に接続し、ソースドライバ $102$ から1行目に配列された各画素 $107_{11} \sim 107_{1m}$ へ映像信号が入力される。また、第1の転送信号生成回路( $T_1$ )の第1の入力端子にも第1のフリップフロップ回路( $F_1$ )から出力されたHレベルの信号が入力される。30

【0050】

期間 $T3$ において、第2のフリップフロップ回路( $F_2$ )からHレベルの信号が出力される。前述の第1のフリップフロップ回路( $F_1$ )の出力信号がHレベルの時と同様に、第2のフリップフロップ回路( $F_2$ )から出力されたHレベルの信号は、第2のゲート線 $105_2$ を介して、画素部 $101$ に配列された2行目の各画素 $107_{21} \sim 107_{2m}$ に入力される。これにより、2行目の各画素 $107_{21} \sim 107_{2m}$ とソースドライバ $102$ が電気的に接続し、ソースドライバ $102$ から2行目に配列された各画素 $107_{21} \sim 107_{2m}$ へ映像信号が入力される。また、第1の転送信号生成回路( $T_1$ )からHレベルの信号が出力され、第3のフリップフロップ回路( $F_3$ )の第1の入力端子に入力される。40

【0051】

期間 $T4$ 以降においては前述の説明の動作の繰り返しである。つまり、第3のフリップフロップ回路( $F_3$ )以降のフリップフロップ回路から順次Hレベルの信号が出力され、50

それに伴い、配列された複数の画素への映像信号の入力が行毎に行われる。

【0052】

本実施の形態で述べた表示装置は、第1及び第2のゲートドライバを有するアクティブマトリクス型の表示装置である。また、第1及び第2のゲートドライバは、それぞれ複数のフリップフロップ回路と、複数の転送信号生成回路とを有する。フリップフロップ回路と転送信号生成回路は共に、第1の入力端子に入力された信号をクロック信号の1/2周期遅らせて出力する回路である。また、転送信号生成回路の出力端子は、後段のフリップフロップ回路の第1の入力端子に直結される。そのため、転送信号生成回路からフリップフロップ回路へ入力される信号の遅延若しくは鈍りを低減することができる。

【0053】

なお、本実施の形態では、1つのソースドライバと、2つのゲートドライバとを有する表示装置の例について示したが、本発明の実施の形態はこの構成に限定されない。例えば、表示装置が2つのゲートドライバのみを有し、外部から映像信号が入力される構成、2つのソースドライバと2つのゲートドライバを有し、映像信号が2つのソースドライバから入力される構成、又は各画素が2本のゲート線を介してゲートドライバと電気的に接続された構成なども本発明の一態様である。

【0054】

(実施の形態2)

本実施の形態では、実施の形態1に示したフリップフロップ回路及び転送信号生成回路に適用可能な回路の具体例について図4及び図5を用いて説明する。具体的には、トランジスタを用いてフリップフロップ回路及び転送信号生成回路を構成する例について示す。なお、トランジスタのソース端子及びドレイン端子は、トランジスタの構造や動作条件等によって替わるため、いずれがソース端子又はドレイン端子であるかを特定することが困難である。そこで、以下においては、ソース端子及びドレイン端子の一方を第1端子、ソース端子及びドレイン端子の他方を第2端子と表記し、区別することとする。

【0055】

<回路構成例>

図4は、実施の形態1に示した第1のゲートドライバ103Aが有する第kのフリップフロップ回路( $F_k$ )及び第kの転送信号生成回路( $T_k$ )に適用可能な回路の一例を示す図である。なお、本実施の形態で示す第kのフリップフロップ回路( $F_k$ )は、第1のトランジスタ401乃至第4のトランジスタ404を有し、第kの転送信号生成回路( $T_k$ )は、第5のトランジスタ405乃至第8のトランジスタ408を有する。また、本実施の形態では、第kのフリップフロップ回路用ストップパルス信号( $S T P (F_k)$ )として第kの転送信号生成回路の出力信号( $T_k O U T$ )を用い、第kの転送信号生成回路用ストップパルス信号( $S T P (T_k)$ )として第k+2のフリップフロップ回路の出力信号( $F_{k+2} O U T$ )を用いる。

【0056】

第1のトランジスタ401は、ゲート端子及び第1端子が第k-2の転送信号生成回路(図示しない)の出力端子に電気的に接続される。

【0057】

第2のトランジスタ402は、ゲート端子が第kの転送信号生成回路( $T_k$ )の出力端子に電気的に接続され、第1端子が接地電位(VSS)線に電気的に接続され、第2端子が第1のトランジスタ401の第2端子に電気的に接続される。

【0058】

第3のトランジスタ403は、ゲート端子が第1のトランジスタ401の第2端子及び第2のトランジスタ402の第2端子に電気的に接続され、第1端子がクロック信号( $C_K$ )線に電気的に接続され、第2端子が第kの転送信号生成回路( $T_k$ )の第1の入力端子に電気的に接続される。

【0059】

第4のトランジスタ404は、ゲート端子が第kの転送信号生成回路( $T_k$ )の出力端

10

20

30

40

50

子に電気的に接続され、第1端子が接地電位(VSS)線に電気的に接続され、第2端子が第kの転送信号生成回路(T<sub>k</sub>)の第1の入力端子及び第3のトランジスタ403の第2端子に電気的に接続される。

【0060】

第5のトランジスタ405は、ゲート端子及び第1端子が第kのフリップフロップ回路(F<sub>k</sub>)の出力端子に電気的に接続される。

【0061】

第6のトランジスタ406は、ゲート端子が第k+2のフリップフロップ回路(図示しない)の出力端子に電気的に接続され、第1端子が接地電位(VSS)線に電気的に接続され、第2端子が第5のトランジスタ405の第2端子に電気的に接続される。 10

【0062】

第7のトランジスタ407は、ゲート端子が第5のトランジスタ405の第2端子及び第6のトランジスタ406の第2端子に電気的に接続され、第1端子が反転クロック信号(CKB)線に電気的に接続され、第2端子が第kのフリップフロップ回路(F<sub>k</sub>)の第3の入力端子及び第k+2のフリップフロップ回路(図示しない)の第1の入力端子に電気的に接続される。

【0063】

第8のトランジスタ408は、ゲート端子が第k+2のフリップフロップ回路(図示しない)の出力端子に電気的に接続され、第1端子が接地電位(VSS)線に電気的に接続され、第2端子が、第kのフリップフロップ回路(F<sub>k</sub>)の第3の入力端子、第k+2のフリップフロップ回路(図示しない)の第1の入力端子、及び第7のトランジスタ407の第2端子に電気的に接続される。 20

【0064】

図4に示したように第kのフリップフロップ回路(F<sub>k</sub>)と第kの転送信号生成回路(T<sub>k</sub>)は、同一構成の回路を適用する事ができる。ただし、回路を設計する際には以下の点に留意することが好ましい。

【0065】

第kのフリップフロップ回路(F<sub>k</sub>)は、第kのゲート線を駆動する回路であり、第kの転送信号生成回路(T<sub>k</sub>)は、第k+2のフリップフロップ回路を駆動する回路である。第kのゲート線には、上述したように様々な寄生抵抗及び寄生容量が存在する。そのため、第kのフリップフロップ回路(F<sub>k</sub>)の負荷は、第kの転送信号生成回路(T<sub>k</sub>)の負荷よりも大きくなる。つまり、上述の回路を設計する際には、第1のトランジスタ401の電流駆動能力が、第5のトランジスタ405の電流駆動能力よりも高いことが好ましい。例えば、第1のトランジスタ401のチャネル幅を第5のトランジスタ405のチャネル幅よりも大きくすればよい。同じ理由により、第2のトランジスタ402の電流駆動能力が第6のトランジスタ406の電流駆動能力よりも高いこと、第3のトランジスタ403の電流駆動能力が第7のトランジスタ407の電流駆動能力よりも高いこと、第4のトランジスタ404の電流駆動能力が第8のトランジスタ408の電流駆動能力よりも高いことが好ましい。例えば、電流駆動能力は、チャネル長に対するチャネル幅の比(チャネル幅/チャネル長(W/L))を大きくするなどによって、向上させることが可能である。 30 40

【0066】

また、第kのフリップフロップ回路(F<sub>k</sub>)が有する第1のトランジスタ401～第4のトランジスタ404の中でも、直接的に第kのゲート線の駆動に関与する第3のトランジスタ403の電流駆動能力が最も高いことが好ましい。同様に、第kの転送信号生成回路(T<sub>k</sub>)が有する第5のトランジスタ405～第8のトランジスタ408の中でも、直接的に第k+2のフリップフロップ回路の駆動に関与する第7のトランジスタ407の電流駆動能力が最も高いことが好ましい。

【0067】

また、第1のゲートドライバ103Aが有する第1のフリップフロップ回路(F<sub>1</sub>)及 50

び第1の転送信号生成回路( $T_1$ )として図4に示した回路構成を適用することができる。ただし、第1のフリップフロップ回路( $F_1$ )においては、第1のトランジスタ401のゲート端子及び第1端子が第1のスタートパルス信号( $S P 1$ )線に電気的に接続される点が図4の構成とは異なる。

【0068】

また、第2のゲートドライバ103Bが有する第 $k+1$ のフリップフロップ回路( $F_{k+1}$ )及び第 $k+1$ の転送信号生成回路( $T_{k+1}$ )も、図4に示した回路構成を適用することができる。ただし、第 $k+1$ のフリップフロップ回路( $F_{k+1}$ )及び第 $k+1$ の転送信号生成回路( $T_{k+1}$ )においては、第3のトランジスタ403の第1端子が反転クロック信号( $C K B$ )線に電気的に接続され、第7のトランジスタ407の第1端子がクロック信号( $C K$ )線に電気的に接続される点が図4の構成とは異なる。

10

【0069】

また、第2のゲートドライバ103Bが有する第2のフリップフロップ回路( $F_2$ )及び第2の転送信号生成回路( $T_2$ )も、図4に示した回路構成を適用することができる。ただし、第2のフリップフロップ回路( $F_2$ )及び第2の転送信号生成回路( $T_2$ )においては、第1のトランジスタ401のゲート端子及び第1端子が第2のスタートパルス信号( $S P 2$ )線に電気的に接続される点、並びに第3のトランジスタ403の第1端子が反転クロック信号( $C K B$ )線に電気的に接続され、第7のトランジスタ407の第1端子がクロック信号( $C K$ )線に電気的に接続される点が図4の構成とは異なる。

20

【0070】

なお、本実施の形態では、第 $k$ の転送信号生成回路用ストップパルス信号( $S T P (T_k)$ )として第 $k+2$ のフリップフロップ回路の出力信号( $F_{k+2} O U T$ )を用いている。そのため、 $n$ 行に配列された複数の画素に対し、第1のゲートドライバ103Aには、第 $n+1$ のフリップフロップ回路がダミー回路として設けられ、第2のゲートドライバ103Bには、第 $n+2$ のフリップフロップ回路がダミー回路として設けられる必要がある。なお、当該ダミー回路として、転送信号生成回路用ストップパルス信号の供給のみを担い且つゲート線の駆動を担わないフリップフロップ回路を適用することができる。また、当該ダミー回路と共に表示に関与しない配線(ダミーのゲート線)を設けることで、当該ダミー回路として、転送信号生成回路用ストップパルス信号の供給及び当該配線の駆動を担うフリップフロップ回路を適用することもできる。

30

【0071】

<回路動作例>

図5は、図4に示した第 $k$ のフリップフロップ回路( $F_k$ )及び第 $k$ の転送信号生成回路( $T_k$ )の入力信号及び出力信号のタイミングチャートを示す図である。以下に、第 $k$ のフリップフロップ回路( $F_k$ )及び第 $k$ の転送信号生成回路( $T_k$ )の動作について説明する。

【0072】

期間 $t_1$ において、第 $k-2$ の転送信号生成回路の出力信号( $T_{k-2} O U T$ )がHレベルに上昇する。これにより、ダイオード接続された第1のトランジスタ401がオンし、第3のトランジスタ403のゲート端子の電位がHレベルまで上昇する。そのため、期間 $t_1$ におけるクロック信号( $C K$ )であるLレベルの信号が第 $k$ のフリップフロップ回路の出力信号( $F_k O U T$ )として出力される。

40

【0073】

期間 $t_2$ において、第 $k-2$ の転送信号生成回路の出力信号( $T_{k-2} O U T$ )がLレベルに低下すると共にクロック信号( $C K$ )がHレベルに上昇する。これにより、ダイオード接続された第1のトランジスタ401がオフし、浮遊状態となった第3のトランジスタ403のゲート端子の電位が、第3のトランジスタ403の第1端子に入力されたHレベルの信号によって持ち上げられ(ブーストストラップ動作)、さらに上昇する。また、第3のトランジスタ403はオン状態を維持し、Hレベルの信号が第 $k$ のフリップフロップ回路( $F_k$ )の出力信号( $F_k O U T$ )として出力される。このHレベルの信号は、第5

50

のトランジスタ405のゲート端子及び第1端子へ入力される。これにより、ダイオード接続された第5のトランジスタ405がオンし、第7のトランジスタ407のゲート端子の電位がHレベルまで上昇する。そのため、期間 $t_2$ における反転クロック信号(CKB)であるLレベルの信号が第kの転送信号生成回路の出力信号( $T_k$ OUT)として出力される。

#### 【0074】

期間 $t_3$ において、クロック信号(CK)がLレベルに低下すると共に反転クロック信号(CKB)がHレベルに上昇する。これにより、ダイオード接続された第5のトランジスタ405がオフし、浮遊状態となった第7のトランジスタ407のゲート端子の電位が、第7のトランジスタ407の第1端子に入力されたHレベルの信号によって持ち上げられ(ブートストラップ動作)、さらに上昇する。また、第7のトランジスタ407はオン状態を維持し、Hレベルの信号が第kの転送信号生成回路( $T_k$ )の出力信号( $T_k$ OUT)として出力される。このHレベルの信号は、第2のトランジスタ402及び第4のトランジスタ404のゲート端子へ入力される。これにより、第2のトランジスタ402がオンし、第3のトランジスタ403のゲート端子の電位がLレベルに低下する。そのため、第3のトランジスタ403がオフする。また、第4のトランジスタ404もオンするため、Lレベルの信号が第kのフリップフロップ回路( $F_k$ )の出力信号( $F_k$ OUT)として出力される。

#### 【0075】

期間 $t_4$ において、第 $k+2$ のフリップフロップ回路の出力信号( $F_{k+2}$ OUT)がHレベルに上昇する。これにより、第6のトランジスタ406がオンし、第7のトランジスタ407のゲート端子の電位がLレベルに低下する。そのため、第7のトランジスタ407がオフする。また、第8のトランジスタ408もオンするため、Lレベルの信号が第kの転送信号生成回路( $T_k$ )の出力信号( $T_k$ OUT)として出力される。

#### 【0076】

なお、第1のフリップフロップ回路及び第1の転送信号生成回路、第 $k+1$ のフリップフロップ回路及び第 $k+1$ の転送信号生成回路、並びに第2のフリップフロップ回路及び第2の転送信号生成回路の回路動作は、上述した第kのフリップフロップ回路( $F_k$ )及び第kの転送信号生成回路( $T_k$ )と同じである。

#### 【0077】

##### <変形例>

本実施の形態では、第kのフリップフロップ回路用ストップパルス信号(STP( $F_k$ ))及び第kの転送信号生成回路用ストップパルス信号(STP( $T_k$ ))として、それぞれ第kの転送信号生成回路( $T_k$ )の出力信号及び第 $k+2$ のフリップフロップ回路( $F_{k+2}$ )の出力信号を適用したが、本実施の形態の構成は、当該構成に限定されない。

#### 【0078】

例えば、第kのフリップフロップ回路用ストップパルス信号(STP( $F_k$ ))及び第kの転送信号生成回路用ストップパルス信号(STP( $T_k$ ))として、それぞれ第 $k+1$ のフリップフロップ回路( $F_{k+1}$ )の出力信号及び第 $k+1$ の転送信号生成回路( $T_{k+1}$ )の出力信号を適用することが可能である。この場合、第kのフリップフロップ回路用ストップパルス信号(STP( $F_k$ ))及び第kの転送信号生成回路用ストップパルス信号(STP( $T_k$ ))が上述した構成と比較して遅延又は鈍った信号となるが、当該期間における第kのフリップフロップ回路( $F_k$ )及び第kの転送信号生成回路( $T_k$ )の出力信号はLレベルとなるため、ストップパルス信号(STP)の遅延及び鈍りが問題になることはない。

#### 【0079】

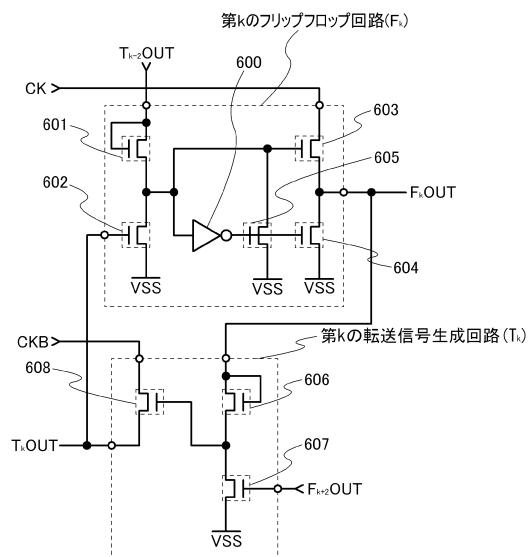

##### (実施の形態3)

本実施の形態では、実施の形態1に示したフリップフロップ回路及び転送信号生成回路に適用可能な回路の実施の形態2とは異なる具体例について図6及び図7を用いて説明する。

10

20

30

40

50

## 【0080】

## &lt;回路構成例&gt;

図6は、実施の形態1に示した第1のゲートドライバ103Aが有する第kのフリップフロップ回路( $F_k$ )及び第kの転送信号生成回路( $T_k$ )に適用可能な回路の一例を示す図である。本実施の形態で示す第kのフリップフロップ回路( $F_k$ )は、第1のトランジスタ601乃至第5のトランジスタ605と、インバータ回路600とを有し、第kの転送信号生成回路( $T_k$ )は、第6のトランジスタ606乃至第8のトランジスタ608を有する。なお、図6に示す回路は、図4に示した第kのフリップフロップ回路( $F_k$ )にインバータ回路600と、第5のトランジスタ605とを付与し、且つ第kの転送信号生成回路( $T_k$ )における第8のトランジスタ408を削除した回路であると言い換えることができる。10

## 【0081】

第1のトランジスタ601、第2のトランジスタ602、及び第3のトランジスタ603の電気的な接続関係は、図4に示した回路と同一であるため、実施の形態2の説明を援用することとする。

## 【0082】

インバータ回路600は、入力端子が第1のトランジスタ601の第2端子、第2のトランジスタ602の第2端子、及び第3のトランジスタ603のゲート端子に電気的に接続される。

## 【0083】

第4のトランジスタ604は、ゲート端子がインバータ回路600の出力端子に電気的に接続され、第1端子が接地電位(VSS)線に電気的に接続され、第2端子が第3のトランジスタ603の第2端子及び第kの転送信号生成回路( $T_k$ )の第1の入力端子に電気的に接続される。20

## 【0084】

第5のトランジスタ605は、ゲート端子がインバータ回路600の出力端子に電気的に接続され、第1端子が接地電位(VSS)線に電気的に接続され、第2端子が第1のトランジスタ601の第2端子、第2のトランジスタ602の第2端子、第3のトランジスタ603のゲート端子、及びインバータ回路600の入力端子に電気的に接続される。30

## 【0085】

図6に示した第kの転送信号生成回路( $T_k$ )は、図4に示した第kの転送信号生成回路( $T_k$ )から第8のトランジスタ408を削除した回路であり、その他のトランジスタの電気的な接続関係は、図4に示した回路と同一であるため、実施の形態2の説明を援用することとする。

## 【0086】

ただし、図6に示した回路を設計する際には以下のように設計する必要がある。

## 【0087】

第kのフリップフロップ回路( $F_k$ )内(ダイオード接続された第1のトランジスタ601)にHレベルの信号が入力された際に、インバータ回路600の入力端子にHレベルの信号が確実に入力されるよう設計される必要がある。より具体的には、第5のトランジスタ605の電流駆動能力よりも第1のトランジスタ601の電流駆動能力を高くする必要がある。例えば、第1のトランジスタ601のチャネル幅を第5のトランジスタ605のチャネル幅よりも大きくする必要がある。40

## 【0088】

また、図5に示した期間 $t_4$ において、第kの転送信号生成回路の出力信号( $T_k$ OU $T$ )がLレベルとなるように設計する必要がある。より具体的には、第7のトランジスタ607の電流駆動能力よりも第8のトランジスタ608の電流駆動能力を高くする必要がある。これにより、第7のトランジスタ607のゲート端子にHレベルの信号が入力されることにより、第7のトランジスタ607がオンし、接地電位(VSS)が第8のトランジスタ608のゲート端子に入力され、第8のトランジスタ608がオフするという動作50

が行われる前に、期間  $t_4$  における反転クロック信号 (CKB) であるLレベルにまで第  $k$  の転送信号生成回路の出力信号 ( $T_k$  OUT) を低下させることができる。

【0089】

また、図6に示した回路を設計する際にも実施の形態2で述べた点について留意することが好ましい。

【0090】

すなわち、第1のトランジスタ601の電流駆動能力が、第6のトランジスタ606の電流駆動能力よりも高いこと、第2のトランジスタ602の電流駆動能力が第7のトランジスタ607の電流駆動能力よりも高いこと、第3のトランジスタ603の電流駆動能力が第8のトランジスタ608の電流駆動能力よりも高いことが好ましい。

10

【0091】

また、第  $k$  のフリップフロップ回路 ( $F_k$ ) が有する第1のトランジスタ601～第5のトランジスタ605の中でも第3のトランジスタ603の電流駆動能力が最も高いこと、第  $k$  の転送信号生成回路 ( $T_k$ ) が有する第6のトランジスタ606～第8のトランジスタ608の中でも、第8のトランジスタ608の電流駆動能力が最も高いことが好ましい。

10

【0092】

なお、図6には第  $k$  のフリップフロップ回路 ( $F_k$ ) 及び第  $k$  の転送信号生成回路 ( $T_k$ ) についてのみ示すが、第  $k+1$  のフリップフロップ回路及び第  $k+1$  の転送信号生成回路などにも図6の回路は適用可能である。ただし、実施の形態2で述べたように一部の端子の電気的な接続関係は異なる。具体的な接続関係の相違は、実施の形態2の説明を援用することとする。

20

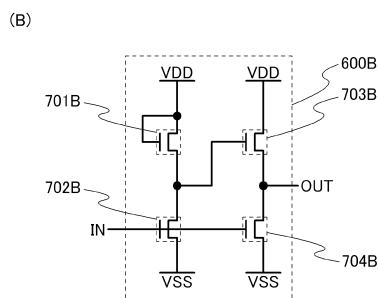

【0093】

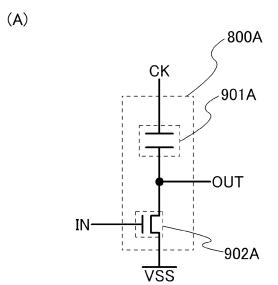

図7(A)、(B)は、図6に示したインバータ回路600に適用可能な回路の具体例を示す図である。なお、図7(A)、(B)において、「IN」と付記された配線が入力配線であり、「OUT」と付記された配線が出力配線である。

【0094】

図7(A)に示したインバータ回路600Aは、ダイオード接続されたトランジスタ701Aと、トランジスタ702Aとによって構成される。

30

【0095】

トランジスタ701Aのゲート端子及び第1端子は電源電位 (VDD) 線に電気的に接続され、第2端子はインバータ回路600Aの出力端子に電気的に接続される。

【0096】

トランジスタ702Aのゲート端子はインバータ回路600Aの入力端子に電気的に接続され、第1端子は接地電位 (VSS) 線に電気的に接続され、第2端子はインバータ回路600Aの出力端子及びトランジスタ701Aの第2端子に電気的に接続される。

30

【0097】

図7(A)に示したインバータ回路600Aは、2つのトランジスタ701A、702Aによって構成されるため、回路面積の増大を最小限に留めることができる。

【0098】

ただし、図6におけるインバータ回路600として図7(A)に示したインバータ回路600Aを適用する場合、トランジスタ702Aがオン時において、出力信号がLレベルとなるよう設計する必要がある。より具体的には、トランジスタ702Aの電流駆動能力をトランジスタ701Aの電流駆動能力よりも高くすることが必要である。例えば、トランジスタ702Aのチャネル長をトランジスタ701Aのチャネル長よりも小さくする、又はトランジスタ702Aのチャネル幅をトランジスタ701Aのチャネル幅よりも大きくする必要がある。

40

【0099】

図7(B)に示したインバータ回路600Bは、ダイオード接続されたトランジスタ701Bと、トランジスタ702B、703B、704Bとによって構成される。

50

## 【0100】

トランジスタ701Bのゲート端子及び第1端子は電源電位(VDD)線に電気的に接続される。

## 【0101】

トランジスタ702Bのゲート端子はインバータ回路600Bの入力端子に電気的に接続され、第1端子は接地電位(VSS)線に電気的に接続され、第2端子はトランジスタ701Bの第2端子に電気的に接続される。

## 【0102】

トランジスタ703Bのゲート端子はトランジスタ701Bの第2端子及びトランジスタ702Bの第2端子に電気的に接続され、第1端子は電源電位(VDD)線に電気的に接続され、第2端子はインバータ回路600Bの出力端子に電気的に接続される。

10

## 【0103】

トランジスタ704Bのゲート端子はインバータ回路600Bの入力端子に電気的に接続され、第1端子は接地電位(VSS)線に電気的に接続され、第2端子はインバータ回路600Bの出力端子及びトランジスタ703Bの第2端子に電気的に接続される。

## 【0104】

図7(B)に示したインバータ回路600Bは、ダイオード接続されたトランジスタ701Bがインバータ回路600Bの出力端子と直結しない。そのため、出力信号が、電源電位(VDD)から低下、又は接地電位(VSS)から増加することを抑制することができる。

20

## 【0105】

ただし、図6におけるインバータ回路600として図7(B)に示したインバータ回路600Bを適用する場合、トランジスタ702Bがオン時において、トランジスタ703Bがオフするよう設計する必要がある。より具体的には、トランジスタ702Bの電流駆動能力をトランジスタ701Bの電流駆動能力よりも高くすることが必要である。例えば、トランジスタ702Bのチャネル長をトランジスタ701Bのチャネル長よりも小さくする、又はトランジスタ702Bのチャネル幅をトランジスタ701Bのチャネル幅よりも大きくする必要がある。

## 【0106】

<実施の形態2に示した回路との相違>

30

図6に示した第kのフリップフロップ回路( $F_k$ )は、インバータ回路600と、ゲート端子がインバータ回路600の出力端子に電気的に接続され、第1端子が接地電位(VSS)線に電気的に接続され、第2端子がインバータ回路600の入力端子に電気的に接続された第5のトランジスタ605とを有する。このように、インバータ回路600と電気的に接続された第5のトランジスタ605は、一度オンすると常にオンし続けることになる。第5のトランジスタ605がオン状態にあると、第3のトランジスタ603のゲート端子の電位が接地電位(VSS)に保たれることになる。そのため、第3のトランジスタ603のゲート端子にノイズが侵入した場合であっても、第3のトランジスタ603がオンすることができない。つまり、表示装置の画像若しくは映像に不良をきたすことがなく、表示装置の性能を向上させることができる。

40

## 【0107】

図6に示した第kの転送信号生成回路( $T_k$ )は、3つのトランジスタ606～608によって構成されるため、回路面積を低減させることができる。

## 【0108】

<変形例>

本実施の形態では、フリップフロップ回路が5つのトランジスタ601～605及びインバータ回路600で構成され、転送信号生成回路が3つのトランジスタ606～608で構成される例について示したが、実施の形態は、当該構成に限定されない。例えば、第kのフリップフロップ回路( $F_k$ )及び第kの転送信号生成回路( $T_k$ )が共に、図6に示した第kのフリップフロップ回路( $F_k$ )又は第kの転送信号生成回路( $T_k$ )と同一

50

の構成であってもよい。また、実施の形態2(図4)に示した回路と、本実施の形態(図6)に示した回路とを組み合わせてフリップフロップ回路及び転送信号生成回路を構成してもよい。

#### 【0109】

また、本実施の形態では、第kのフリップフロップ回路用ストップパルス信号(STP(F<sub>k</sub>))及び第kの転送信号生成回路用ストップパルス信号(STP(T<sub>k</sub>))として、それぞれ第kの転送信号生成回路(T<sub>k</sub>)の出力信号及び第k+2のフリップフロップ回路(F<sub>k+2</sub>)の出力信号を適用したが本実施の形態の構成は、当該構成に限定されない。

#### 【0110】

##### (実施の形態4)

10

本実施の形態では、実施の形態1に示したフリップフロップ回路及び転送信号生成回路に適用可能な回路の実施の形態2及び3とは異なる具体例について図8及び図9を用いて説明する。

#### 【0111】

##### <回路構成例>

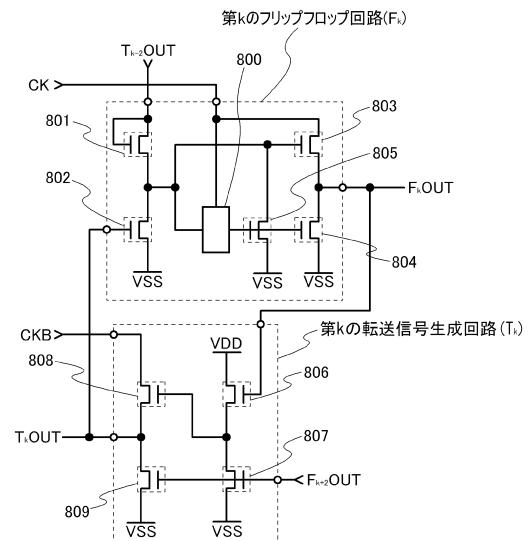

図8は、実施の形態1に示した第1のゲートドライバ103Aが有する第kのフリップフロップ回路(F<sub>k</sub>)及び第kの転送信号生成回路(T<sub>k</sub>)に適用可能な回路の一例を示す図である。本実施の形態で示す第kのフリップフロップ回路(F<sub>k</sub>)は、第1のトランジスタ801乃至第5のトランジスタ805と、制御回路800とを有し、第kの転送信号生成回路(T<sub>k</sub>)は、第6のトランジスタ806乃至第9のトランジスタ809を有する。なお、図8に示す回路は、図4に示した回路に制御回路800及び第5のトランジスタ805を付与し、且つ第6のトランジスタ806(図4における第5のトランジスタ405に相当)の第1端子がゲート端子ではなく、電源電位(VDD)線に電気的に接続された回路であると言い換えることができる。

20

#### 【0112】

第1のトランジスタ801、第2のトランジスタ802、及び第3のトランジスタ803の電気的な接続関係は、図4及び図6に示した回路と同一であるため、実施の形態2の説明を援用することとする。

#### 【0113】

30

制御回路800は、第1の入力端子が第1のトランジスタ801の第2端子、第2のトランジスタ802の第2端子、及び第3のトランジスタ803のゲート端子に電気的に接続され、第2の入力端子がクロック信号(CK)線に電気的に接続される。

#### 【0114】

第4のトランジスタ804は、ゲート端子が制御回路800の出力端子に電気的に接続され、第1端子が接地電位(VSS)線に電気的に接続され、第2端子が第3のトランジスタ803の第2端子及び第kの転送信号生成回路(T<sub>k</sub>)の第1の入力端子に電気的に接続される。

#### 【0115】

40

第5のトランジスタ805は、ゲート端子が制御回路800の出力端子に電気的に接続され、第1端子が接地電位(VSS)線に電気的に接続され、第2端子が第1のトランジスタ801の第2端子、第2のトランジスタ802の第2端子、第3のトランジスタ803のゲート端子、及び制御回路800の第1の入力端子に電気的に接続される。

#### 【0116】

第6のトランジスタ806は、ゲート端子が第kのフリップフロップ回路(F<sub>k</sub>)の出力端子に電気的に接続され、第1端子が電源電位(VDD)線に電気的に接続される。

#### 【0117】

第7のトランジスタ807、第8のトランジスタ808、及び第9のトランジスタ809の電気的な接続関係は、図6に示した第6のトランジスタ606、第7のトランジスタ607、及び第8のトランジスタ608と同一であるため、実施の形態2の説明を援用す

50

ることとする。

【0118】

ただし、図8に示した回路を設計する際には以下のように設計する必要がある。

【0119】

第kのフリップフロップ回路( $F_k$ )内(ダイオード接続された第1のトランジスタ801)にHレベルの信号が入力された際に、制御回路800の入力端子にHレベルの信号が確実に入力されるよう設計される必要がある。より具体的には、第5のトランジスタ805の電流駆動能力よりも第1のトランジスタ801の電流駆動能力を高くする必要がある。例えば、第1のトランジスタ801のチャネル幅を第5のトランジスタ805のチャネル幅よりも大きくする必要がある。

10

【0120】

また、図8に示した回路を設計する際にも実施の形態2で述べた点について留意することが好ましい。

【0121】

すなわち、第1のトランジスタ801の電流駆動能力が、第6のトランジスタ806の電流駆動能力よりも高いこと、第2のトランジスタ802の電流駆動能力が第7のトランジスタ807の電流駆動能力よりも高いこと、第3のトランジスタ803の電流駆動能力が第8のトランジスタ808の電流駆動能力よりも高いこと、第4のトランジスタ804の電流駆動能力が第9のトランジスタ809の電流駆動能力よりも高いことが好ましい。

【0122】

また、第kのフリップフロップ回路( $F_k$ )が有する第1のトランジスタ801～第5のトランジスタ805の中でも第3のトランジスタ803の電流駆動能力が最も高いこと、第kの転送信号生成回路( $T_k$ )が有する第6のトランジスタ806～第9のトランジスタ809の中でも、第8のトランジスタ808の電流駆動能力が最も高いことが好ましい。

20

【0123】

なお、図8には第kのフリップフロップ回路( $F_k$ )及び第kの転送信号生成回路( $T_k$ )についてのみ示すが、第k+1のフリップフロップ回路( $F_{k+1}$ )及び第k+1の転送信号生成回路( $T_{k+1}$ )などにも図8の回路は適用可能である。ただし、実施の形態2で述べたように一部の端子の電気的な接続関係は異なる。具体的な接続関係の相違は、実施の形態2の説明を援用することとする。

30

【0124】

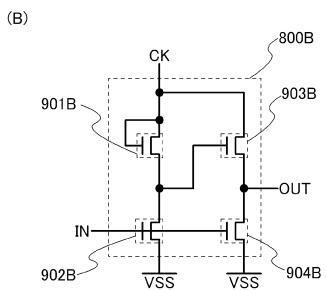

図9(A)、(B)は、図8に示した制御回路800に適用可能な回路の具体例を示す図である。図9(A)、(B)において、「IN」と付記された配線が第1の入力配線であり、「CK」と付記された配線がクロック信号(CK)線に電気的に接続された第2の入力配線であり、「OUT」と付記された配線が出力配線である。

【0125】

図9(A)に示した制御回路800Aは、容量素子901Aと、トランジスタ902Aとによって構成される。

【0126】

容量素子901Aの一方の端子はクロック信号(CK)線に電気的に接続され、他方の端子は制御回路800Aの出力端子に電気的に接続される。

40

【0127】

トランジスタ902Aのゲート端子は制御回路800Aの第1の入力端子に電気的に接続され、第1端子は接地電位(VSS)線に電気的に接続され、第2端子は制御回路800Aの出力端子及び容量素子901Aの他方の端子に電気的に接続される。

【0128】

図5に示した期間t3以降において、制御回路800Aの第1の入力端子には、Lレベルの信号が入力され、トランジスタ902Aがオフする。これにより、制御回路800Aの出力信号が浮遊状態になる。そのため、制御回路800Aの出力信号として、クロック

50

信号 (CK) と同調した信号が出力される。

【0129】

ただし、図8における制御回路800として図9(A)に示した制御回路800Aを適用する場合、期間t2から期間t3へ変化する際に、容量素子901Aの一方の端子の電位がLレベルに低下した後に制御回路800Aの出力端子が浮遊状態になるように設計する必要がある。

【0130】

図9(B)に示した制御回路800Bは、ダイオード接続されたトランジスタ901Bと、トランジスタ902Bと、トランジスタ903Bと、トランジスタ904Bとによって構成される。

10

【0131】

トランジスタ901Bのゲート端子及び第1端子はクロック信号(CK)線に電気的に接続される。

【0132】

トランジスタ902Bのゲート端子は制御回路800Bの第1の入力端子に電気的に接続され、第1端子は接地電位(VSS)線に電気的に接続され、第2端子はトランジスタ901Bの第2端子に電気的に接続される。

20

【0133】

トランジスタ903Bのゲート端子はトランジスタ901Bの第2端子及びトランジスタ902Bの第2端子に電気的に接続され、第1端子はクロック信号(CK)線に電気的に接続され、第2端子は制御回路800Bの出力端子に電気的に接続される。

【0134】

トランジスタ904Bのゲート端子は制御回路800Bの入力端子に電気的に接続され、第1端子は接地電位(VSS)線に電気的に接続され、第2端子は制御回路800Bの出力端子及びトランジスタ903Bの第2端子に電気的に接続される。

20

【0135】

ただし、図8における制御回路800として図9(B)に示した制御回路800Bを適用する場合、トランジスタ902Bがオン時において、トランジスタ903Bがオフするよう設計する必要がある。より具体的には、トランジスタ902Bの電流駆動能力をトランジスタ901Bの電流駆動能力よりも高くすることが必要である。例えば、トランジスタ902Bのチャネル長をトランジスタ901Bのチャネル長よりも小さくする、又はトランジスタ902Bのチャネル幅をトランジスタ901Bのチャネル幅よりも大きくする必要がある。

30

【0136】

<実施の形態2及び3に示した回路との相違>

図9(A)、(B)に示した制御回路800A、800Bは、クロック信号(CK)又はクロック信号(CK)に同調した信号を出力する。そのため、第3のトランジスタ803のゲート端子にノイズが侵入した場合であっても、第4のトランジスタ804及び第5のトランジスタ805がオンすることによって、ノイズを除去することができる。また、第4のトランジスタ804及び第5のトランジスタ805が常にオンすることなく、第4のトランジスタ804及び第5のトランジスタ805の劣化を抑制することができる。つまり、表示装置の映像に不良をきたすことがなく、表示装置の性能及び信頼性を向上させることができる。

40

【0137】

<変形例>

本実施の形態では、フリップフロップ回路が5つのトランジスタ801～805及び制御回路800で構成され、転送信号生成回路が4つのトランジスタ806～809で構成される例について示したが、実施の形態は、当該構成に限定されない。例えば、第kのフリップフロップ回路(F<sub>k</sub>)及び第kの転送信号生成回路(T<sub>k</sub>)が共に、図8に示した第kのフリップフロップ回路(F<sub>k</sub>)又は第kの転送信号生成回路(T<sub>k</sub>)と同一の構成

50

であってもよい。また、実施の形態2(図4)又は実施の形態3(図6)に示した回路と、本実施の形態(図8)に示した回路とを組み合わせて、フリップフロップ回路及び転送信号生成回路を構成してもよい。

【0138】

また、本実施の形態では、第kのフリップフロップ回路用ストップパルス信号(STP( $F_k$ ))及び第kの転送信号生成回路用ストップパルス信号(STP( $T_k$ ))として、それぞれ第kの転送信号生成回路( $T_k$ )の出力信号及び第k+2のフリップフロップ回路( $F_{k+2}$ )の出力信号を適用したが本実施の形態の構成は、当該構成に限定されない。

【0139】

(実施の形態5)

10

本実施の形態では、実施の形態2乃至4に示したフリップフロップ回路及び転送信号生成回路が有するトランジスタの具体例について説明する。

【0140】

当該トランジスタとして、様々な材料、構造のトランジスタを適用することができる。つまり、用いるトランジスタの種類に限定はない。例えば、非晶質シリコン、多結晶シリコン、微結晶(マイクロクリスタル、ナノクリスタル、セミアモルファスとも言う)シリコンなどに代表される非単結晶半導体膜を有する薄膜トランジスタ(TFT)などを用いることができる。

【0141】

20

薄膜トランジスタを用いて表示装置を製造する場合、様々なメリットがある。まず、薄膜トランジスタは、単結晶シリコンを利用したトランジスタよりも低温で製造できるため、表示装置の製造コストの削減、又は製造装置の大型化を図ることができる。また、薄膜トランジスタは、製造温度が低いため、耐熱性の低い基板上に製造することができる。そのため、耐熱性の低い透光性を有する基板上にトランジスタを製造できる。また、薄膜トランジスタは、膜厚が薄いため、トランジスタを形成する膜の一部に光を透過させることができる。そのため、開口率を向上させることができる。

【0142】

30

また、当該トランジスタとして、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどを用いることも出来る。なお、当該トランジスタとしてMOS型トランジスタを用いることにより、トランジスタのサイズを小さくすることができる。また、当該トランジスタとしてバイポーラトランジスタを用いることにより、大きな電流を流すことが出来る。そのため、回路を高速動作させることができる。なお、MOS型トランジスタとバイポーラトランジスタとを1つの基板に混在させて形成してもよい。これにより、低消費電力、小型化、高速動作などが実現できる。

【0143】

なお、多結晶シリコンを製造するときに、触媒(ニッケルなど)を用いることにより、結晶性をさらに向上させ、電気特性のよい薄膜トランジスタを製造することができる。その結果、ゲートドライバ、ソースドライバ、及び信号処理回路(信号生成回路、ガンマ補正回路、D/A変換回路など)を基板上に一体形成することができる。

40

【0144】

また、微結晶シリコンを製造するときに、触媒(ニッケルなど)を用いることにより、結晶性をさらに向上させ、電気特性のよいトランジスタを製造することができる。このとき、レーザー照射を行うことなく、熱処理を加えるだけで、結晶性を向上させることも可能である。その結果、ソースドライバの一部(アナログスイッチなど)及びゲートドライバを基板上に一体形成することができる。なお、レーザー照射を行わない場合は、シリコンの結晶性のムラを抑えることができる。そのため、画質の向上した画像を表示することができる。

【0145】

ただし、触媒(ニッケルなど)を用いずに、多結晶シリコン又は微結晶シリコンを製造

50

することもできる。

#### 【0146】

また、シリコンの結晶性の向上は、シリコン全体に対して行うことが望ましいが、それに限定されない。一部の領域のみにおいて、シリコンの結晶性を向上させてもよい。選択的に結晶性を向上させることは、レーザー光を選択的に照射することなどにより可能である。例えば、ゲートドライバ及びソースドライバなどの領域にのみレーザー光を照射してもよい。その結果、回路の高速動作が必要である領域のみのシリコンの結晶性を向上させることができる。画素部は、高速に動作させる必要性が低いため、結晶性が向上されなくても、問題なく画素回路を動作させることができる。これにより、結晶性を向上させる領域が少なくて済むため、製造工程も短くすることができる。そのため、スループットが向上し、表示装置の製造コストを低減できる。

10

#### 【0147】

また、当該トランジスタは、シリコンを用いたトランジスタに限定されない。当該トランジスタとして、シリコングルマニウム、ガリウムヒ素などの化合物半導体、又は酸化亜鉛、インジウム及びガリウムを含む酸化亜鉛などの酸化物半導体を用いたトランジスタを適用することもできる。また、これらの化合物半導体又は酸化物半導体の薄膜を有する薄膜トランジスタを適用することもできる。これらは、低温において製造可能であるので、例えば、室温でトランジスタを製造することが可能となる。その結果、耐熱性の低い基板、例えば、プラスチック基板又はフィルム基板などに直接トランジスタを形成することができる。なお、これらの化合物半導体又は酸化物半導体を、トランジスタのチャネル部分に用いるだけでなく、それ以外の用途で用いることも出来る。例えば、これらの化合物半導体又は酸化物半導体を配線、抵抗素子、画素電極、又は透光性を有する電極などとして用いることもできる。それらは、トランジスタと同時に成膜又は形成することができたため、表示装置の製造コストが低減できる。

20

#### 【0148】

また、当該トランジスタとして、有機半導体やカーボンナノチューブを有するトランジスタを用いることもできる。これらにより、曲げることが可能な基板上にトランジスタを形成することができる。このような基板を用いた表示装置は、衝撃耐性が高い。

#### 【0149】

また、当該トランジスタの製造方法は限定されない。当該製造方法として、フォトリソグラフィ法、インクジェット法、又は印刷法等を適用することができる。なお、インクジェット法及び印刷法では、製造時にマスク（レチクル）を用いないため、トランジスタのレイアウトを容易に変更することができる。さらに、レジストを用いずに製造することができるため、材料費が安くなり、工程数を削減できる。また、必要な部分にのみ膜を付けることが可能であるため、材料が無駄にならず、表示装置の製造コストを低減できる。

30

#### 【0150】

また、当該トランジスタとして、ゲート端子が2個以上のマルチゲート構造のトランジスタを用いることもできる。マルチゲート構造にすると、チャネル領域が直列に接続されるため、複数のトランジスタが直列に接続された構造となる。よって、マルチゲート構造により、トランジスタのオフ電流の低減及び耐圧向上（信頼性の向上）を図ることができる。

40

#### 【0151】

また、当該トランジスタとして、チャネル領域の上下にゲート端子が配置されている構造のトランジスタを適用することもできる。チャネル領域の上下にゲート端子が配置される構造にすることにより、複数のトランジスタが並列に接続されたような回路構成となる。つまり、チャネル領域が増えることになる。そのため、電流値の増加を図ることができる。さらに、チャネル領域の上下にゲート端子を配置することにより、空乏層ができやすくなるため、S値の改善を図ることができる。

#### 【0152】

また、当該トランジスタとして、チャネル領域の上にゲート端子が配置されている構造

50

、チャネル領域の下にゲート端子が配置されている構造、順スタガ構造、逆スタガ構造、チャネル領域を複数の領域に分けた構造、チャネル領域を並列に接続した構造、又はチャネル領域が直列に接続する構造などのトランジスタを適用することもできる。

【0153】

また、当該トランジスタとして、チャネル領域（もしくはその一部）にソース端子やドレイン端子が重なっている構造のトランジスタを用いることもできる。チャネル領域（もしくはその一部）にソース端子やドレイン端子が重なる構造にすることによって、チャネル領域の一部に電荷が溜まることにより、動作が不安定化することを防ぐことができる。

【0154】

また、当該トランジスタとして、LDD領域を設けた構造を適用することもできる。LDD領域を設けることにより、オフ電流の低減又はトランジスタの耐圧向上（信頼性の向上）を図ることができる。また、LDD領域を設けることにより、飽和領域で動作する時に、ドレインとソースとの間の電圧が変化しても、ドレイン電流があまり変化せず、電圧・電流特性の傾きがフラットな特性にすることができる。

10

【0155】

なお、当該トランジスタは、様々な基板を用いて形成することができる。つまり、基板の種類は、特定のものに限定されることはない。その基板の一例としては、半導体基板（例えば単結晶基板又はシリコン基板）、SOI基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タングステン基板、タングステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、纖維状の材料を含む紙、又は基材フィルムなどがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート（PET）、ポリエチレンナフタレート（PEN）、ポリエーテルサルファン（PES）に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂などがある。貼り合わせフィルムの一例としては、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、又は塩化ビニルなどがある。基材フィルムの一例としては、ポリエステル、ポリアミド、ポリイミド、無機蒸着フィルム、又は紙類などがある。特に、半導体基板、単結晶基板、又はSOI基板などを用いてトランジスタを製造することによって、特性、サイズ、又は形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、又は回路の高集積化を図ることができる。

20

【0156】

また、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。

30

【0157】

（実施の形態6）

本実施の形態では、実施の形態1に示した表示装置を備えた電子機器の一例について、図11乃至図13を用いて説明する。

【0158】

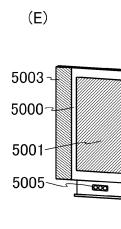

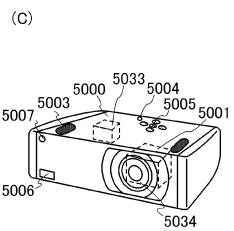

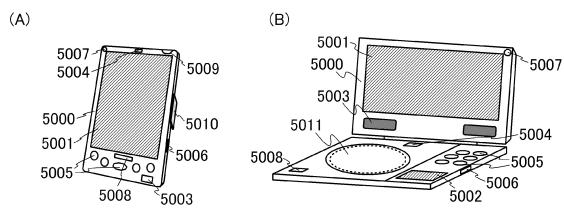

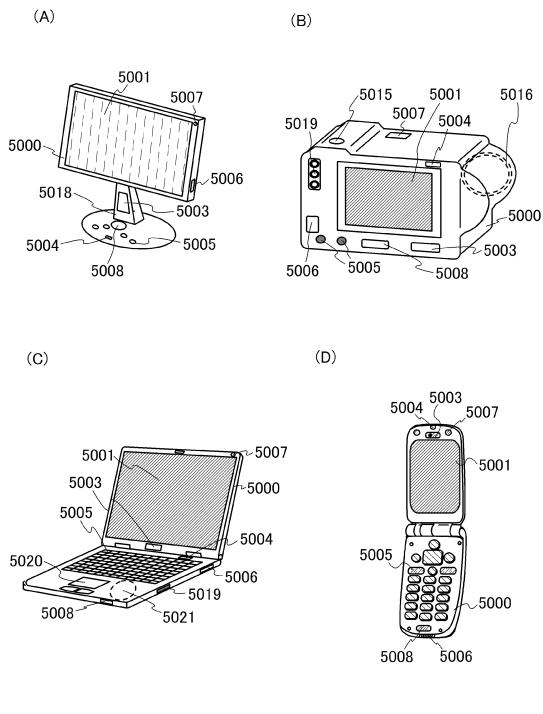

図11（A）～（F）、図12（A）～（D）は、実施の形態1に示した表示装置を有する電子機器を示す図である。これらの電子機器は、筐体5000、表示部5001、スピーカ5003、LEDランプ5004、操作キー5005（電源スイッチ、又は操作スイッチを含む）、接続端子5006、センサ5007（力、変位、位置、速度、加速度、

40

50

角速度、回転数、距離、可視光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、におい又は赤外線を測定する機能を含むもの)、マイクロフォン 5008、等を有することができる。これらの電子機器は、表示部 5001 に実施の形態 1 に示した表示装置が組み込まれている。

【0159】

図 11 (A) はモバイルコンピュータを示した図であり、上述したものその他に、スイッチ 5009、赤外線ポート 5010、等を有することができる。図 11 (B) は記録媒体を備えた携帯型の画像再生装置(たとえば、DVD 再生装置)を示した図であり、上述したものその他に、第 2 表示部 5002、記録媒体読込部 5011、等を有することができる。図 11 (C) はプロジェクタを示した図であり、上述したものその他に、光源 5033、投射レンズ 5034、等を有することができる。図 11 (D) は携帯型遊技機を示した図であり、上述したものその他に、記録媒体読込部 5011、等を有することができる。図 11 (E) はテレビ受像器を示した図であり、上述したものその他に、チューナ、画像処理部、等を有することができる。図 11 (F) は持ち運び型テレビ受像器を示した図であり、上述したものその他に、信号の送受信が可能な充電器 5017、等を有することができる。図 12 (A) はディスプレイを示した図であり、上述したものその他に、支持台 5018、等を有することができる。図 12 (B) はカメラを示した図であり、上述したものその他に、外部接続ポート 5019、シャッターボタン 5015、受像部 5016、等を有することができる。図 12 (C) はコンピュータを示した図であり、上述したものその他に、ポイントティングデバイス 5020、外部接続ポート 5019、リーダ/ライタ 5021、等を有することができる。図 12 (D) は携帯電話機を示した図であり、上述したものその他に、アンテナ、携帯電話・移動端末向けの 1 セグメント部分受信サービス用チューナ、等を有することができる。

10

20

30

【0160】

図 11 (A) ~ (F)、図 12 (A) ~ (D) に示した電子機器は、様々な機能を有することができる。例えば、様々な情報(静止画、動画、テキスト、画像など)を表示部に表示する機能、タッチパネル機能、カレンダー、日付又は時刻などを表示する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、無線通信機能、無線通信機能を用いて様々なコンピュータネットワークに接続する機能、無線通信機能を用いて様々なデータの送信又は受信を行う機能、記録媒体に記録されているプログラム又はデータを読み出して表示部に表示する機能、等を有することができる。さらに、複数の表示部を有する電子機器においては、一つの表示部を主として画像情報を表示し、別の一つの表示部を主として文字情報を表示する機能、または、複数の表示部に視差を考慮した画像を表示することで立体的な画像を表示する機能、等を有することができる。さらに、受像部を有する電子機器においては、静止画を撮影する機能、動画を撮影する機能、撮影した画像を自動または手動で補正する機能、撮影した画像を記録媒体(外部又はカメラに内蔵)に保存する機能、撮影した画像を表示部に表示する機能、等を有することができる。なお、図 11 (A) ~ (F)、図 12 (A) ~ (D) に示した電子機器が有することのできる機能はこれらに限定されず、様々な機能を有することができる。

40

【0161】

次に、建造物と一体にして設けられた電子機器の一例を、図 13 (A)、(B) を用いて説明する。

【0162】

図 13 (A) は、建造物と一体にして設けられた電子機器の一例を示した図である。当該電子機器は、筐体 5022、表示部 5023、スピーカ 5025 等を備える。また、当該電子機器は、リモコン装置 5024 によって操作することができる。当該電子機器は、壁かけ型として建物と一体となっており、設置するスペースを広く必要とすることなく設置可能である。

【0163】

図 13 (B) は、建造物と一体にして設けられた電子機器の一例を示した図である。当

50

該電子機器は、表示部 5026 を備え、浴槽 5027 の近傍に取り付けられている。入浴者は、表示部 5026 の視聴が可能になる。

【0164】

なお、本実施の形態において、建造物として壁、浴室を例としたが、本実施の形態はこれに限定されず、様々な建造物に表示パネルを設置することができる。

【0165】

次に、移動体と一体として電子機器が設けられた例を、図13(C)、(D)を用いて説明する。

【0166】

図13(C)は、自動車に設けられた電子機器の一例を示した図である。当該電子機器は、表示部 5028 を備え、自動車の車体 5029 に取り付けられている。当該電子機器は、車体の動作又は車体内外から入力される情報をオンデマンドに表示することができる。なお、当該電子機器は、ナビゲーション機能を有していてもよい。

10

【0167】

図13(D)は、旅客用飛行機に設けられた電子機器の一例を示した図である。より具体的には、図13(D)は、旅客用飛行機の座席上部の天井 5030 に設けられた当該電子機器の使用時の形状について示した図である。当該電子機器は、天井 5030 とヒンジ部 5032 を介して一体に取り付けられており、ヒンジ部 5032 の伸縮により乗客は表示部 5031 の視聴が可能になる。当該電子機器は乗客が操作することで情報を表示する機能を有する。

20

【0168】

なお、本実施の形態において、移動体としては自動車車体、飛行機機体について例示したがこれに限定されず、自動二輪車、自動四輪車（自動車、バス等を含む）、電車（モノレール、鉄道等を含む）、船舶等、様々なものに設置することができる。

【0169】

本実施の形態において述べた電子機器は、何らかの情報を表示するための表示部を有し、当該表示部に実施の形態1に示した表示装置が組み込まれていることを特徴とする。

【実施例1】

【0170】

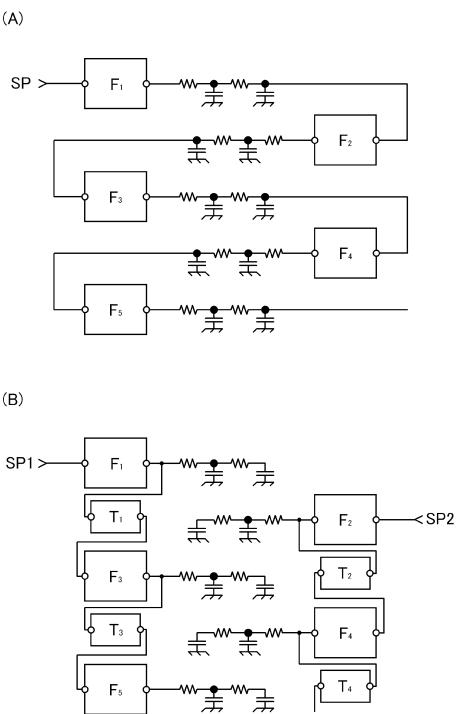

本実施例では、転送信号生成回路を備えたゲートドライバにおける信号の鈍り及び遅延の抑制効果を回路シミュレーションにより従来例と比較することで検証する。

30

【0171】

図14に従来のゲートドライバと本明細書のゲートドライバの回路シミュレーション用のモデルを示す。図14(A)は従来のゲートドライバの構成を表す図であり、各フリップフロップ回路の出力信号を次段のフリップフロップ回路のスタートパルス信号として用いている。図14(B)は本明細書のゲートドライバの構成を表す図であり、フリップフロップ回路の間に転送信号生成回路が設けられている。

【0172】

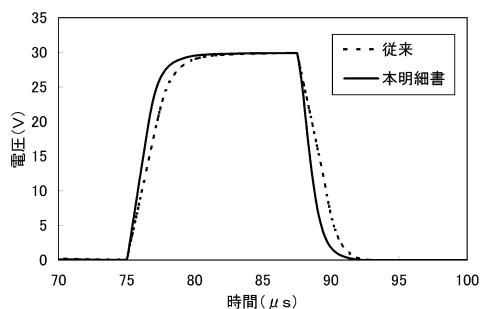

本実施例では、フリップフロップ回路及び転送信号生成回路が図4に示した回路によって構成される場合のフリップフロップ回路の出力信号を回路シミュレーションによって計算した。なお、計算ソフトには、P Spiceを用いた。また、フリップフロップ回路及び転送信号生成回路を構成するトランジスタのしきい値電圧を 8 (V)、電界効果移動度を 0.5 (cm<sup>2</sup> / V s) と仮定した。また、各ゲート線には、それぞれ 100 (pF) の寄生容量が形成されていると仮定した。さらに、クロック信号の電圧振幅を 30 (V) (H レベルの電位を 30 V、L レベルの電位を 0 V)、接地電位を 0 (V)、クロック周波数を 41.7 (kHz) (周期: 24 (μs)) と仮定した。

40

【0173】

図15に回路シミュレーションによって求めたフリップフロップ回路の出力信号を示す。図15に示すように本明細書のゲートドライバは信号の遅延及び鈍りが低減されていることが確認できた。

50

## 【符号の説明】

## 【0174】

|                      |              |    |

|----------------------|--------------|----|

| 1 0 0                | 表示装置         |    |

| 1 0 1                | 画素部          |    |

| 1 0 2                | ソースドライバ      |    |

| 1 0 3 A              | 第1のゲートドライバ   |    |

| 1 0 3 B              | 第2のゲートドライバ   |    |

| 1 0 4 <sub>1</sub>   | ソース線         |    |

| 1 0 4 <sub>n</sub>   | ソース線         |    |

| 1 0 5 <sub>1</sub>   | ゲート線         | 10 |

| 1 0 5 <sub>2</sub>   | ゲート線         |    |

| 1 0 5 <sub>3</sub>   | ゲート線         |    |

| 1 0 5 <sub>m</sub>   | ゲート線         |    |

| 1 0 6 A              | フレキシブルプリント基板 |    |

| 1 0 6 B              | フレキシブルプリント基板 |    |

| 1 0 7 <sub>1 1</sub> | 画素           |    |

| 1 0 7 <sub>n m</sub> | 画素           |    |

| 4 0 1                | トランジスタ       |    |

| 4 0 2                | トランジスタ       |    |

| 4 0 3                | トランジスタ       | 20 |

| 4 0 4                | トランジスタ       |    |

| 4 0 5                | トランジスタ       |    |

| 4 0 6                | トランジスタ       |    |

| 4 0 7                | トランジスタ       |    |

| 4 0 8                | トランジスタ       |    |

| 6 0 0                | インバータ回路      |    |

| 6 0 0 A              | インバータ回路      |    |

| 6 0 0 B              | インバータ回路      |    |

| 6 0 1                | トランジスタ       |    |

| 6 0 2                | トランジスタ       | 30 |

| 6 0 3                | トランジスタ       |    |

| 6 0 4                | トランジスタ       |    |

| 6 0 5                | トランジスタ       |    |

| 6 0 6                | トランジスタ       |    |

| 6 0 7                | トランジスタ       |    |

| 6 0 8                | トランジスタ       |    |

| 7 0 1 A              | トランジスタ       |    |

| 7 0 1 B              | トランジスタ       |    |

| 7 0 2 A              | トランジスタ       |    |

| 7 0 2 B              | トランジスタ       | 40 |

| 7 0 3 B              | トランジスタ       |    |

| 7 0 4 B              | トランジスタ       |    |

| 8 0 0                | 制御回路         |    |

| 8 0 0 A              | 制御回路         |    |

| 8 0 0 B              | 制御回路         |    |

| 8 0 1                | トランジスタ       |    |

| 8 0 2                | トランジスタ       |    |

| 8 0 3                | トランジスタ       |    |

| 8 0 4                | トランジスタ       |    |

| 8 0 5                | トランジスタ       | 50 |

|           |             |    |

|-----------|-------------|----|

| 8 0 6     | トランジスタ      |    |

| 8 0 7     | トランジスタ      |    |

| 8 0 8     | トランジスタ      |    |

| 8 0 9     | トランジスタ      |    |

| 9 0 1 A   | 容量素子        |    |

| 9 0 1 B   | トランジスタ      |    |

| 9 0 2 A   | トランジスタ      |    |

| 9 0 2 B   | トランジスタ      |    |

| 9 0 3 B   | トランジスタ      |    |

| 9 0 4 B   | トランジスタ      | 10 |

| 1 0 0 1   | 画素部         |    |

| 1 0 0 2 A | 第1のゲートドライバ  |    |

| 1 0 0 2 B | 第2のゲートドライバ  |    |

| 1 0 0 3 1 | ゲート線        |    |

| 1 0 0 3 2 | ゲート線        |    |

| 1 0 0 3 k | ゲート線        |    |

| 5 0 0 0   | 筐体          |    |

| 5 0 0 1   | 表示部         |    |

| 5 0 0 2   | 第2表示部       |    |

| 5 0 0 3   | スピーカ        | 20 |

| 5 0 0 4   | L E D ランプ   |    |

| 5 0 0 5   | 操作キー        |    |

| 5 0 0 6   | 接続端子        |    |

| 5 0 0 7   | センサ         |    |

| 5 0 0 8   | マイクロフォン     |    |

| 5 0 0 9   | スイッチ        |    |

| 5 0 1 0   | 赤外線ポート      |    |

| 5 0 1 1   | 記録媒体読込部     |    |

| 5 0 1 5   | シャッターボタン    |    |

| 5 0 1 6   | 受像部         | 30 |

| 5 0 1 8   | 支持台         |    |

| 5 0 1 9   | 外部接続ポート     |    |

| 5 0 2 0   | ポインティングデバイス |    |

| 5 0 2 1   | リーダ/ライタ     |    |

| 5 0 2 2   | 筐体          |    |

| 5 0 2 3   | 表示部         |    |

| 5 0 2 4   | リモコン装置      |    |

| 5 0 2 5   | スピーカ        |    |

| 5 0 2 6   | 表示部         |    |

| 5 0 2 7   | 浴槽          | 40 |

| 5 0 2 8   | 表示部         |    |

| 5 0 2 9   | 車体          |    |

| 5 0 3 0   | 天井          |    |

| 5 0 3 1   | 表示部         |    |

| 5 0 3 2   | ヒンジ部        |    |

| 5 0 3 3   | 光源          |    |

| 5 0 3 4   | 投射レンズ       |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

(D)

【図14】

【図15】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 2 2 G

G 0 9 G 3/36

G 0 2 F 1/133 5 5 0

(56)参考文献 特開2006-24350 (JP, A)

特開2006-351165 (JP, A)

特開2008-112550 (JP, A)

特開2000-347628 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3