(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5153058号

(P5153058)

(45) 発行日 平成25年2月27日(2013.2.27)

(24) 登録日 平成24年12月14日(2012.12.14)

|               |           |              |         |

|---------------|-----------|--------------|---------|

| (51) Int.Cl.  | F 1       |              |         |

| HO 1 L 21/02  | (2006.01) | HO 1 L 27/12 | B       |

| HO 1 L 27/12  | (2006.01) | HO 1 L 29/78 | 6 1 3 Z |

| HO 1 L 29/78  | (2006.01) | HO 1 L 29/78 | 6 2 7 D |

| HO 1 L 21/336 | (2006.01) | HO 1 L 27/10 | 4 3 1   |

| HO 1 L 27/10  | (2006.01) | HO 1 L 27/10 | 4 4 8   |

請求項の数 4 (全 39 頁) 最終頁に続く

(21) 出願番号 特願2005-51883 (P2005-51883)

(22) 出願日 平成17年2月25日 (2005.2.25)

(65) 公開番号 特開2006-237402 (P2006-237402A)

(43) 公開日 平成18年9月7日 (2006.9.7)

審査請求日 平成20年2月21日 (2008.2.21)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 伊藤 恒介

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 萩原 周治

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、剥離層を形成し、

前記剥離層上に、薄膜トランジスタと、前記薄膜トランジスタ上に形成され前記剥離層に達するコンタクトホールが設けられた絶縁層と、前記絶縁層上に形成され前記コンタクトホールにおいて前記剥離層に達し且つ前記薄膜トランジスタと電気的に接続される配線層と、を有する薄膜回路部を形成した後、

前記剥離層を除去して前記基板から前記薄膜回路部を剥離することにより、前記配線層を露出させ、

前記薄膜回路部の前記配線層が露出した領域に、フッ化炭素基を有する物質を含む層を形成し、

前記フッ化炭素基を有する物質を含む層上に、流動性を有する導電性材料を含む組成物を液滴吐出法により付着させ、前記薄膜トランジスタと電気的に接続し、アンテナとしての機能を有する導電層を形成することを特徴とする半導体装置の作製方法。

## 【請求項 2】

基板上に、剥離層を形成し、

前記剥離層上に、薄膜トランジスタと、前記薄膜トランジスタ上に形成され前記剥離層に達するコンタクトホールが設けられた絶縁層と、前記絶縁層上に形成され前記コンタクトホールにおいて前記剥離層に達し且つ前記薄膜トランジスタと電気的に接続される配線層と、を有する薄膜回路部を形成した後、

10

20

前記剥離層を除去して前記基板から前記薄膜回路部を剥離することにより、前記配線層を露出させ、

前記薄膜回路部の前記配線層が露出した領域に、シランカップリング剤を含む層を形成し、

前記シランカップリング剤を含む層上に、流動性を有する導電性材料を含む組成物を液滴吐出法により付着させ、前記薄膜トランジスタと電気的に接続し、アンテナとしての機能を有する導電層を形成することを特徴とする半導体装置の作製方法。

【請求項3】

基板上に、剥離層を形成し、

前記剥離層上に、薄膜トランジスタと、前記薄膜トランジスタ上に形成され前記剥離層に達するコンタクトホールが設けられた絶縁層と、前記絶縁層上に形成され前記コンタクトホールにおいて前記剥離層に達し且つ前記薄膜トランジスタと電気的に接続される配線層と、を有する薄膜回路部を形成した後、

前記剥離層を除去して前記基板から前記薄膜回路部を剥離することにより、前記配線層を露出させ、

前記薄膜回路部の前記配線層が露出した面に、フッ化炭素基を有する物質を含む層をスピンドルコート法により形成し、

前記フッ化炭素基を有する物質を含む層上に、流動性を有する導電性材料を含む組成物を液滴吐出法により付着させ、前記薄膜トランジスタと電気的に接続し、アンテナとしての機能を有する導電層を形成した後、前記フッ化炭素基を有する物質を含む層のうち前記導電層に覆われていない領域をアッシングまたはエッチングにより除去することを特徴とする半導体装置の作製方法。

【請求項4】

基板上に、剥離層を形成し、

前記剥離層上に、薄膜トランジスタと、前記薄膜トランジスタ上に形成され前記剥離層に達するコンタクトホールが設けられた絶縁層と、前記絶縁層上に形成され前記コンタクトホールにおいて前記剥離層に達し且つ前記薄膜トランジスタと電気的に接続される配線層と、を有する薄膜回路部を形成した後、

前記剥離層を除去して前記基板から前記薄膜回路部を剥離することにより、前記配線層を露出させ、

前記薄膜回路部の前記配線層が露出した面に、シランカップリング剤を含む層をスピンドルコート法により形成し、

前記フッ化炭素基を有する物質を含む層上に、流動性を有する導電性材料を含む組成物を液滴吐出法により付着させ、前記薄膜トランジスタと電気的に接続し、アンテナとしての機能を有する導電層を形成した後、前記シランカップリング剤を含む層のうち前記導電層に覆われていない領域をアッシングまたはエッチングにより除去することを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置、及び半導体装置の作製方法に関する。

【背景技術】

【0002】

近年、個々の対象物にID（個体識別番号）を与えることで、その対象物の履歴等の情報を明確にし、生産・管理等に役立てるといった個体認識技術が注目されている。その中でも、非接触でデータの送受信が可能な半導体装置の開発が進められている。このような半導体装置として、特に、RFID（Radio Frequency Identification）（IDタグ、ICタグ、ICチップ、RFタグ（Radio Frequency）、無線タグ、電子タグ、無線チップともよばれる）等が企業内、市場等で導入され始めている。

【0003】

10

20

30

40

50

これらの半導体装置の多くは、シリコン(Si)等の半導体基板を用いた回路(以下、IC(Integrated Circuit)チップとも記す)とアンテナとを有し、当該ICチップは記憶回路(以下、メモリとも記す)や制御回路等から構成されている。また、半導体装置の用途によって、要求される機能は多種多様に及ぶ。より目的に即したサービスが安定して提供できる半導体装置の開発が盛んに行われている(例えば特許文献1)。

【特許文献1】特開2002-151947号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

本発明では、工程、装置を複雑化することなく、要求される特性を有する半導体装置を提供することを目的とする。また、半導体装置を低成本で、歩留まりよく作製できる技術を提供することも目的とする。

10

【課題を解決するための手段】

【0005】

本発明の半導体装置は、主にトランジスタなどからなる薄膜回路(ICチップとも呼ばれる)とアンテナとを有しており、薄膜回路は記憶回路(以下、メモリとも記す)や制御回路等から構成されている。本明細書中において、薄膜回路とは、厚さ1μm以下の半導体膜で薄膜トランジスタ、ダイオードなどの能動素子、抵抗などの受動素子を形成した回路であり、トランジスタなどより構成される記憶回路や制御回路等を総称して薄膜回路部と呼ぶ。薄膜回路部と電気的に接続している導電層をアンテナ、又はアンテナ部とも呼ぶ。薄膜回路部とアンテナである導電層は、薄膜回路部の有する配線層に導電層が接して形成されることによって、電気的に接続する。

20

【0006】

本発明では、薄膜回路部を基板上に複数形成し、その薄膜回路部を選択的に剥離し、封止するフィルムでもある基板上に貼り付け設置する。基板上の薄膜回路部の設置される位置は、薄膜回路部のアンテナの構造や大きさによって、間隔などを制御する。制御は、基板上にアライメント制御用のマーカを形成し、機械を用いた量産も可能である。

【0007】

基板上に設置された薄膜回路部の有する配線層に接するように、薄膜回路部及び基板に、流動性を有する導電性材料を含む組成物を付着させることによってアンテナとして機能する導電層を形成する。よって基板上に設けられた薄膜回路部と薄膜回路部に電気的に接続するアンテナからなる半導体装置を形成することができる。アンテナを直接薄膜回路部に形成するため、熱や圧力などを薄膜回路部に加えないで、薄膜回路部へのダメージが防げ、信頼性が向上する。また、工程も簡略化するので、低成本で生産性も向上する。

30

【0008】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置を指す。本発明を用いて多層配線層や、プロセッサチップなどの半導体装置を作製することができる。

【0009】

本発明の半導体装置の一は、基板上に設けられた薄膜回路部と、薄膜回路部と電気的に接続し、基板上及び薄膜回路部上に連続的に設けられた導電層とを有する。

40

【0010】

上記構成において、基板上及び薄膜回路部上にフッ化炭素基を有する物質を含む層と、前記フッ化炭素基を有する物質を含む層上に前記導電層を有してよい。

【0011】

本発明の半導体装置の一は、第1の可撓性を有する基板上に設けられた薄膜回路部と、薄膜回路部と電気的に接続し、第1の可撓性を有する基板上及び薄膜回路部上に連続的に設けられた導電層と、薄膜回路部上及び導電層上を覆う第2の可撓性を有する基板とを有する。

50

**【 0 0 1 2 】**

上記構成において、第1の可撓性を有する基板上及び薄膜回路部上にフッ化炭素基を有する物質を含む層と、フッ化炭素基を有する物質を含む層上に前記導電層を有してもよい。

**【 0 0 1 3 】**

本発明の半導体装置の作製方法の一は、基板上に薄膜回路部を設置し、基板上及び薄膜回路部上に、流動性を有する導電性材料を含む組成物を付着させ、薄膜回路部と電気的に接続する導電層を形成する。

**【 0 0 1 4 】**

本発明の半導体装置の作製方法の一は、基板上に薄膜回路部を設置し、基板上及び薄膜回路部上に導電性材料を含む組成物を印刷し、薄膜回路部と電気的に接続する導電層を形成する。 10

**【 0 0 1 5 】**

本発明の半導体装置の作製方法の一は、基板上に複数の薄膜回路部を形成し基板から薄膜回路部を選択的に剥離し、可撓性を有する基板上に接着し、可撓性を有する基板上及び薄膜回路部上に、流動性を有する導電性材料を含む組成物を付着させ、薄膜回路部と電気的に接続する導電層を形成する。

**【 0 0 1 6 】**

本発明の半導体装置の作製方法の一は、基板上に複数の薄膜回路部を形成し、基板から薄膜回路部を選択的に剥離し、可撓性を有する基板上に接着し、可撓性を有する基板上及び薄膜回路部上に導電性材料を含む組成物を印刷し、薄膜回路部と電気的に接続する導電層を形成する。 20

**【発明の効果】****【 0 0 1 7 】**

本発明により、より高性能、高信頼性の半導体装置を低成本で、歩留まりよく作製することができる。

**【発明を実施するための最良の形態】****【 0 0 1 8 】**

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。 30

**【 0 0 1 9 】****(実施の形態 1 )**

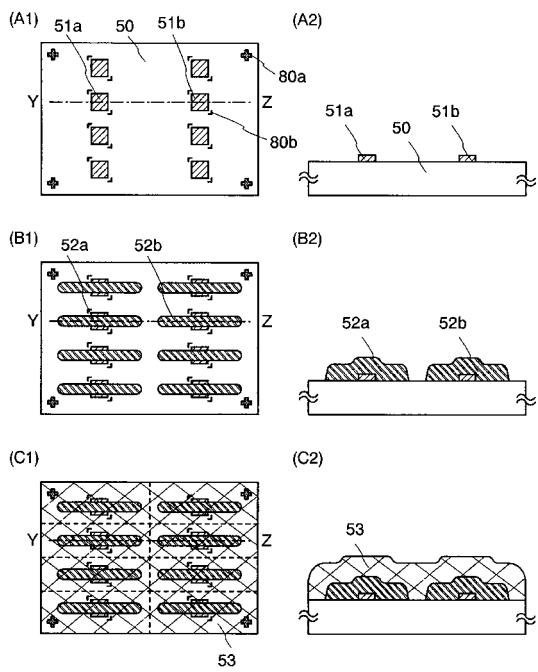

本実施の形態では、本発明の半導体装置の作製方法に関して図1を用いて説明する。

**【 0 0 2 0 】**

本発明の半導体装置は、主にトランジスタなどからなる薄膜回路（薄膜回路ともよばれる）とアンテナとを有しており、薄膜回路は記憶回路（以下、メモリとも記す）や制御回路等から構成されている。本明細書中において、薄膜回路とは、厚さ1μm以下の半導体膜で薄膜トランジスタ、ダイオードなどの能動素子、抵抗などの受動素子を形成した回路であり、トランジスタなどより構成される記憶回路や制御回路等を総称して薄膜集積回路部と呼ぶ。また薄膜回路を有する基板を薄膜回路付き基板とも記す。 40

**【 0 0 2 1 】**

本実施の形態では、薄膜回路部を基板上に複数形成し、その薄膜回路を選択的に剥離し、封止するフィルムでもある基板上に貼り付け設置する。基板上の薄膜回路の設置される位置は、薄膜回路のアンテナの構造や大きさによって、間隔などを制御する。制御は、基板上にマーカを形成しアライメントをとることでき、機械を用いた量産も可能である。剥離、及び接着には、剥離層、接着層などを用いて行う。 50

## 【0022】

基板上に設置された薄膜回路部の有する配線層に接するように、薄膜回路部及び基板に、流動性を有する導電性材料を含む組成物を付着させることによってアンテナとして機能する導電層を形成する。よって基板上に設けられた薄膜回路部と薄膜回路部に電気的に接続するアンテナからなる半導体装置を形成することができる。アンテナを他の基板に形成し、異方性導電性ペースト（ACP）や異方性導電性フィルム（ACF）などを介して、熱と圧力によって圧着し、電気的導通と接続をとる実装方法と比較し、本実施の形態は、アンテナを直接薄膜回路部に形成するため、熱や圧力などを薄膜回路部に加えないで、薄膜回路部へのダメージが防げ、信頼性が向上する。また、工程も簡略化するので、低コストで生産性も向上する。

10

## 【0023】

また、半導体装置の用途によって求められる機能が異なり、アンテナの構造や大きさも変化する。アンテナの特性は、アンテナの形態に依存するからである。アンテナがリーダライタで共振したときに発生する起電力は、アンテナのコイルの周波数、巻数、面積等に依存し、起電力が高い時の周波数である共振周波数は、コイルのインダクタンス、容量に依存する。そしてコイルのインダクタンスは、コイルの大きさ、形状、巻き数、隣接するコイル間の距離など、コイルの形態に依存するからである。従って、受信すべき周波数によっては、アンテナが薄膜回路部のサイズよりも大きくなる場合がある。この場合、基板上に薄膜回路部及びアンテナを形成後、フィルムなどの可撓性を有する基板に貼り付けると、基板上に形成できる半導体装置は、アンテナの大きさで決まってしまうため数が減少し、生産性が悪い。

20

## 【0024】

本実施の形態を用いると、薄膜回路部を基板に選択的に貼り付けた後、アンテナを形成するので、基板上に形成できる半導体装置の数は、薄膜回路部の大きさで決定することができる。薄膜回路部を基板上に設置する位置を制御することによって、多種多様なアンテナを自由に形成することができる。また、アンテナは、流動性を有する導電性材料を含む組成物を用いて形成することができる印刷法などを用いるので、アンテナの膜厚の増加も可能であり、膜厚の大きさの設定の自由度が高い。

## 【0025】

基板50上に、基板50上に設けられたアライメント用のマーカ80a、マーカ80bを用いて位置あわせを行いながら、薄膜回路部51a、薄膜回路部51bを設置し固定する。固定は接着層を用いることができる。また、薄膜回路部の配置は、フリップチップボンダ装置などを用いて機械的に行うと生産性が向上する。図示しないが、薄膜回路部51a、薄膜回路部51bは接着層によって基板50に接着される（図1（A1）（A2）参照。）。なお、図1（A1）、（B1）、（C1）は半導体装置の上面図であり、図1（A2）、（B2）、（C2）は、各上面図における線Y-Zに対応する断面図である。

30

## 【0026】

基板50上に設けられた薄膜回路部51a、薄膜回路部51b上にアンテナとして機能する導電層52a、導電層52bを印刷法により形成する（図1（B1）（B2）参照。）。薄膜回路部51a、薄膜回路部51bは、表面に露出した配線層を有しており、その配線層と導電層52a、導電層52bとが接するように形成することで、薄膜回路部51aと導電層52a、薄膜回路部51bと導電層52bとがそれぞれ電気的に接続する。本実施の形態では、アンテナとして機能する導電層52a及び導電層52bは、薄膜回路部51a及び薄膜回路部51bと比較して大きなサイズであるため、導電層52a、導電層52bは、薄膜回路部51a、薄膜回路部51bを跨ぐようにして基板50上にも接するように形成される。またこの時、本実施の形態のように薄膜回路部51a、薄膜回路部51bの側端部にも導電層52a、導電層52bが接して形成される場合もある。薄膜回路部51a、薄膜回路部51bの側端部の形状、及び導電層52a、導電層52bの膜厚によっては、導電層52a、導電層52bが薄膜回路部51a、薄膜回路部51bの側端部に接しない場合、一部のみ接する場合などがある。

40

50

## 【0027】

基板 50、薄膜回路部 51a、薄膜回路部 51b、導電層 52a、導電層 52b を覆うように絶縁層 53 を形成する。本実施の形態では、絶縁層 53 も印刷法を用いて形成する。絶縁層 53 は、スピンドルコート法などの塗布法や、液滴吐出法などによって形成してもよい(図 1 (C1)、(C2) 参照。)。絶縁層 53 のみで十分封止ができる場合はよいが、絶縁層 53 上を、フィルムなどの可撓性を有する基板で覆うように封止することが好みしい。図 1 (C1) で示す点線によって分断することで個々の半導体装置とすることができる。以上の工程によって薄膜回路及びアンテナを備えた半導体装置を作製することができる。

## 【0028】

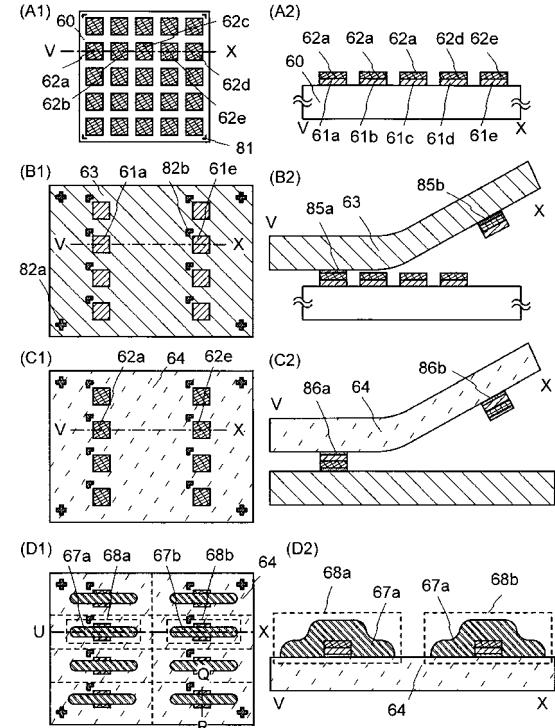

より具体的な例を、図 2 を用いて詳しく説明する。基板 60 上に複数の薄膜回路部が形成されている。薄膜回路部は基板 60 と剥離層を介して接している。図 2 では、配線層が露出して形成されている薄膜回路部の領域を明らかに示すため、薄膜回路部と配線層を有する領域を上下 2 つの領域に分けて示している。基板 60 上に、薄膜回路部は、配線層を表面に露出して形成されており、図 2 (A1) における上面図では、配線層 62a、配線層 62b、配線層 62c、配線層 62d、配線層 62e が確認でき、基板 60 側に面している薄膜回路部 61a、薄膜回路部 61b、薄膜回路部 61c、薄膜回路部 61d、薄膜回路部 61e は図 2 (A2) で示すように各配線層の下側に積層して形成されている。図 2 はあくまで模式図であり、配線層の露出領域が薄膜回路部においてどこに有しているのかを示すものであり、形状などは図 2 に限定されず、薄膜回路部上全面に配線層が形成されている必要はない。これは図 3 の模式図においても同様である。

## 【0029】

基板 60 上には、アライメント制御用のマーカ 81 が形成されている。図 2 (A1)、(B1)、(C1)、(D1) は半導体装置の上面図であり、図 2 (A2)、(B2)、(C2)、(D2) は、各上面図における線 V-X に対応する断面図である。可撓性を有する転写用基板 63 の、剥離する薄膜回路部の領域に接着層 85a、接着層 85b を形成する。薄膜回路部 61a、薄膜回路部 61b、薄膜回路部 61c、薄膜回路部 61d、薄膜回路部 61e と基板 60 との間に設けられている剥離層を一部、もしくは全部除去した後、選択的に接着層を有する転写用基板 63 を、接着層が配線層と向き合うように、貼り合わせ、剥離する。図 2 (B2) のように、基板 60 上に形成された薄膜回路部 61a の有する配線層 62a は接着層 85a と、薄膜回路部 61e の有する配線層 62e は接着層 85b と接着し、基板 60 より剥離され、転写用基板 63 に接着する(図 2 (B1) 参照。)。

## 【0030】

この剥離工程も、アライメント制御用のマーカ 82a、82b を用いて位置制御行うことができる。図 2 においては、マーカを転写用基板 63 の角の 4 個所と、薄膜回路を接着する各領域に形成する例を示すが、マーカは単数でもよいし、より多くの個所に複数形成してもよい。マーカは、その位置制御の要求される正確さや、アライメント制御する基板のサイズなどによって適宜設定すればよい。これは図 3 においても同様である。マーカは、フォトリソグラフィ法を用いて、基板をエッチングして形成することができる。その他、レーザ光の照射や、印刷法によって形成することもできる。また、印刷法によって導電性材料を含む組成物よりマーカを形成し、その後アンテナとして機能する導電層をそのマーカ上に形成し、マーカを導電層の一部とすることもできる。またマーカはどのような形状を有していてもよく、十字、丸状、角状、線状等を有することができる。

## 【0031】

図 2 (B1) では、薄膜回路部 61a、薄膜回路部 61e 上面に露出しており、配線層 62a、配線層 62b が転写用基板 63 側に接している。配線層と、アンテナとして機能する導電層とを接して形成し、電気的に接続させなければならないため、もう一度可撓性を有する基板による剥離、転写工程を行い、配線層を表面に露出させる。選択的に接着層 86a、接着層 86b が設けられた可撓性を有する基板 64 を、薄膜回路部 61a、薄

10

20

30

40

50

膜回路部 61e に接着させ、転写用基板 63 より剥離する(図 2 (C2) 参照。)。剥離工程の後、配線層 62a、配線層 62b に残存する接着層 85a、接着層 85b を除去し、図 2 (C1) の上面図で示すように、基板 64 上に薄膜回路部 61a、薄膜回路部 61b が、配線層 62a、配線層 62b を表面に露出した状態で設置される。接着層 85a、接着層 85b より、接着層 86a、接着層 86b の方がより接着力が強い接着層を用いてもよいし、接着層 85a、接着層 85b に紫外線剥離性の接着層、接着層 86a、接着層 86b に紫外線硬化性の接着層を用いて、紫外線照射により接着力を制御してもよい。これは、本明細書中において、接着層の接着力を用いて行う剥離、接着の工程でも同様である。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。

10

#### 【0032】

露出している配線層 62a、配線層 62b、及び基板 64 に接するようにアンテナとして機能する導電層 67a、導電層 67b を印刷法により形成し、導電層 67a、導電層 67b を覆う絶縁層、又は基板を設け(図示せず)、半導体装置 68a、半導体装置 68b を作製する(図 2 (D1) (D2) 参照。)。半導体装置 68a、半導体装置 68b は、図 2 (D1) で示す点線で分断することで個々の半導体装置 68a、半導体装置 68b となる。

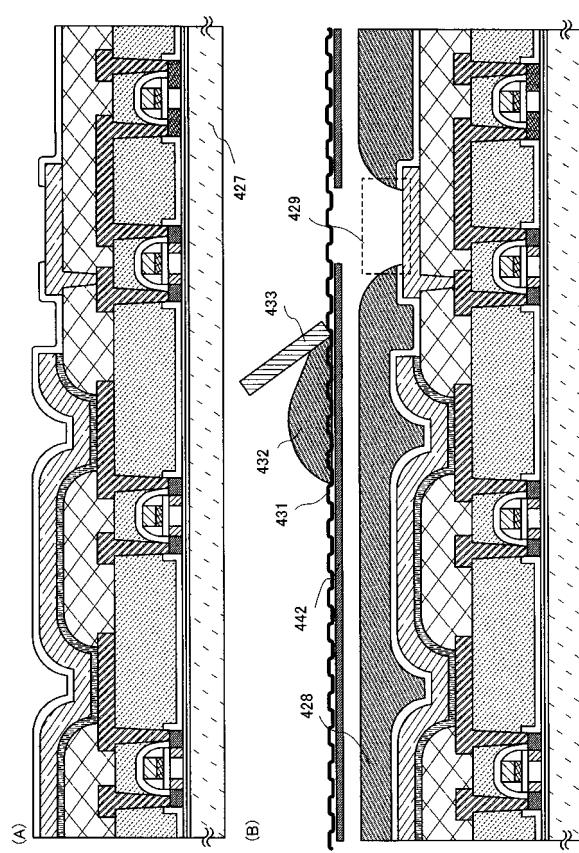

#### 【0033】

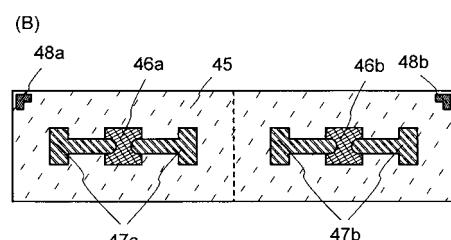

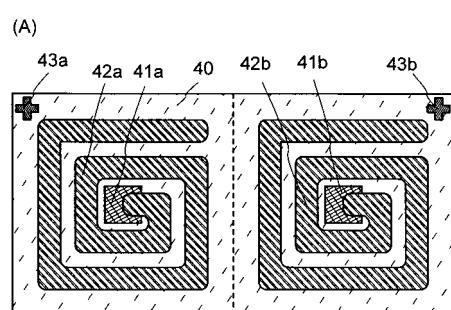

なお、本実施の形態に示した例はごく一例であり、アンテナの形状を限定するものではない。あらゆる形状のアンテナについて本発明は実施することが可能である。図 1 では直線状のアンテナ形状を示したが、例えば矩形状に巻かれたアンテナ、又は円状のアンテナであってもよい。アンテナ形状の他の例を図 20 に示す。図 20 (A) (B) の半導体装置は、基板 40、又は基板 45 上に形成された 2 つの半導体装置であり、点線部分で分断することで、個々の半導体装置とすることができます。図 20 (A) の半導体装置はそれぞれ、薄膜回路部 41a 及びアンテナとして機能する導電層 42a、薄膜回路部 41b 及びアンテナとして機能する導電層 42b とで構成され、基板 40 上にはアライメント制御用のマーカ 43a、マーカ 43b とが設けられている。導電層 42a、導電層 42b はコイル状に巻かれた形状となっている。また、図 20 (B) の半導体装置はそれぞれ、薄膜回路部 46a 及びアンテナとして機能する導電層 47a、薄膜回路部 46b 及びインテナとして機能する導電層 47b とで構成され、基板 45 上にはアライメント制御用のマーカ 48a、マーカ 48b とが設けられている。導電層 47a、導電層 47b は T 字型の形状の 2 つの導電層が向き合うように、薄膜回路部 46a、薄膜回路部 46b に 2 個所で接続している。図 20 (B) のように、アンテナは複数設けてもよく、薄膜回路部との接続個所も複数でもよい。

20

#### 【0034】

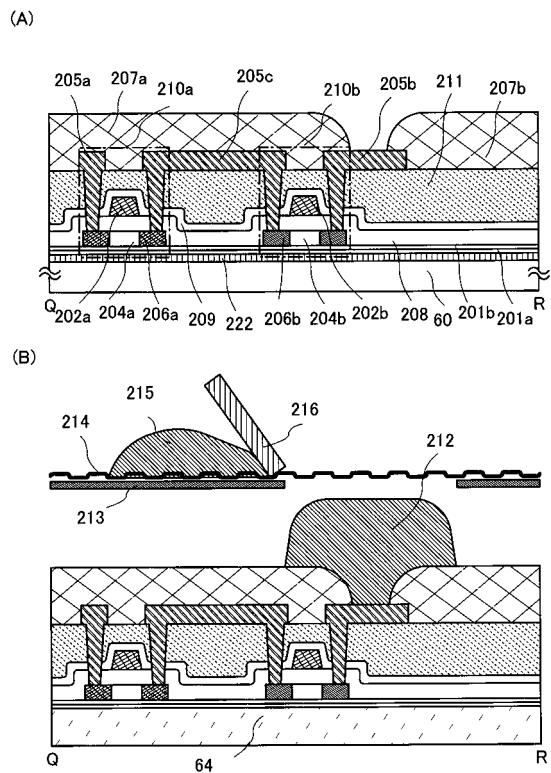

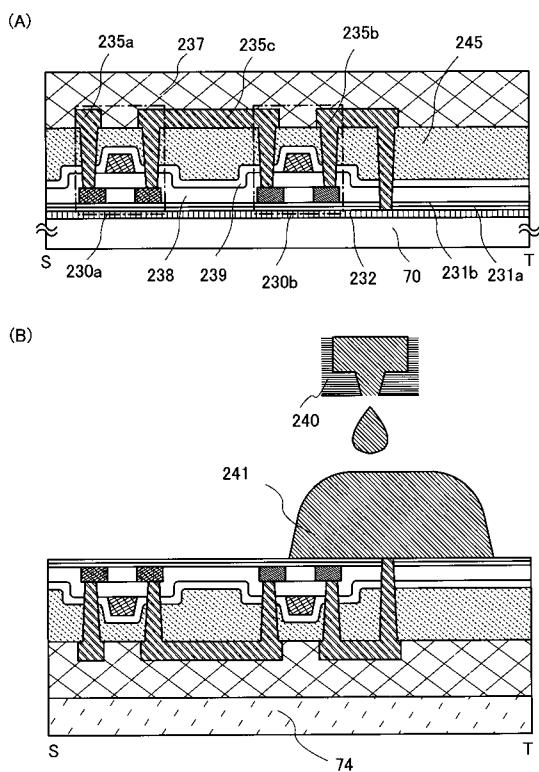

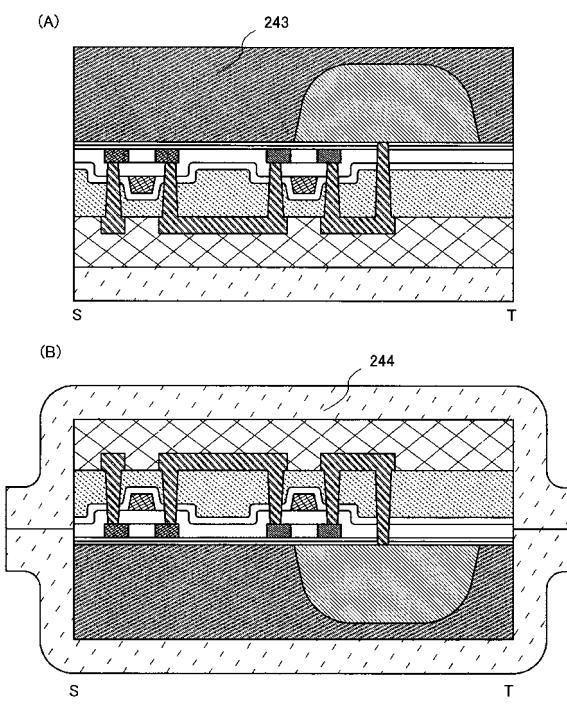

図 2 における半導体装置の作製工程を、図 2 (D) 線 Q - R に対応する断面図である図 5、図 6 を用いて説明する。

#### 【0035】

図 5 (A) は、図 2 (A1) の工程に対応しており、基板 60 に薄膜回路部が配線層 205b を露出して形成されている。基板 60 上に、剥離層 222、絶縁層 201a、絶縁層 201b、ゲート絶縁層 208、p 型不純物領域 206a を含む半導体層 204a 及びゲート電極層 202a を有する p チャネル型薄膜トランジスタ 210a、n 型不純物領域 206b を含む半導体層 204b 及びゲート電極層 202b を有する n チャネル型薄膜トランジスタ 210b、絶縁層 209、絶縁層 211 が形成されている。p チャネル型薄膜トランジスタ 210a、n チャネル型薄膜トランジスタ 210b の半導体層 204a、半導体層 204b とそれぞれに接続する配線層 205a、配線層 205b、配線層 205c は絶縁層 211 上に形成され、配線層 205b 上の一部を露出するように絶縁層 207a、絶縁層 207b が形成されている。p チャネル型薄膜トランジスタ 210a と n チャネル型薄膜トランジスタ 210b とは電気的に接続しており CMOS 構造となっている。

30

#### 【0036】

40

50

その後図2のように、剥離層222を除去し、剥離工程を行い、図2(D1)の工程に対応する図5(B)のように、アンテナとして機能する導電層212が印刷法により形成される。各種印刷法(スクリーン(孔版)印刷、オフセット(平版)印刷、凸版印刷やグラビア(凹版)印刷などを用いることができる。図5(B)においてはスクリーン印刷法を用いる。具体的には、金網(メッシュ)214及びマスク用の乳剤213が枠に設けられたスクリーン印刷版を配線層205b上に設ける。次に、スクリーン印刷版上に組成物(ペースト)215を設け、スキージ216やローラー等を用いて組成物(ペースト)215を押し出す。この結果、配線層205b上に組成物(ペースト)を塗布印刷することができる。なお、スキージやローラーでペーストを押し出す前に、スクレッパでペーストをスクリーン印刷版上に広げてもよい。印刷塗布された組成物(ペースト)を乾燥・焼成することで、導電層212を形成することができる(図5(B)参照。)。

#### 【0037】

導電層212及び薄膜回路部を覆うように絶縁層220を形成し、可撓性を有する基板221で封止し半導体装置を作製する(図6(A)(B)参照。)。図6(A)では、絶縁層220を導電層212と同様にスクリーン印刷法によって形成する。

#### 【0038】

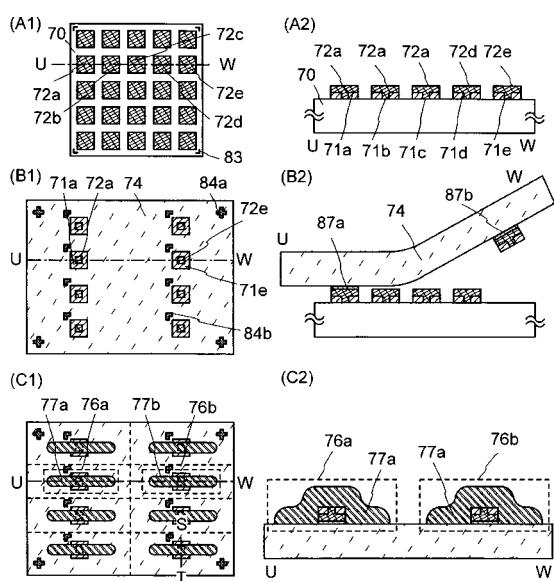

他の例を、図3を用いて詳しく説明する。図2においては、薄膜回路部が形成される基板上に、配線層が上部表面に露出している例を示したが、図3では、配線層が基板側に達して形成されている例を示す。図3にも図2と同様に基板70上に複数の薄膜回路部が形成されている。また、薄膜回路部は基板70と剥離層を介して接している。図3でも、配線層が露出して形成されている薄膜回路部の領域を明らかに示すため、薄膜回路部と配線層を有する領域を図中のハッチを変えて示している。基板70上に、薄膜回路部は、配線層が基板70側に一部露出して形成されており、図3(A1)における上面図では、配線層72a、配線層72b、配線層72c、配線層72d、配線層72eが確認でき、基板70側に面している薄膜回路部71a、薄膜回路部71b、薄膜回路部71c、薄膜回路部71d、薄膜回路部71eは図3(A2)で示すように各配線層の下側に積層して形成されている。

#### 【0039】

基板70上には、アライメント制御用のマーカ83が形成されている。図3(A1)、(B1)、(C1)は半導体装置の上面図であり、図3(A2)、(B2)、(C2)は、各上面図における線U-Wに対応する断面図である。可撓性を有する基板74に、剥離する薄膜回路部の領域に接着層87a、接着層87bを形成する。薄膜回路部71a、薄膜回路部71b、薄膜回路部71c、薄膜回路部71d、薄膜回路部71eと基板70との間に設けられている剥離層を一部、もしくは全部除去した後、選択的に接着層を有する基板74を、接着層が配線層と向き合うように、貼り合わせ、剥離する。図3(B2)のように、基板70上に形成された薄膜回路部71aの有する配線層72aは接着層87aと、薄膜回路部71eの有する配線層72eは接着層87bと接着し、基板70より剥離され、基板74に接着する(図3(B1)参照。)。この剥離工程も、アライメント制御用のマーカ84a、84bを用いて位置制御を行うことができる。

#### 【0040】

図3(C1)の上面図で示すように、基板74上に薄膜回路部71a、薄膜回路部71bが、配線層72aの一部、配線層72bの一部を表面に露出した状態で設置される。露出している配線層72a、配線層72b、及び基板74に接するようにアンテナとして機能する導電層77a、導電層77bを印刷法により形成し、導電層77a、導電層77bを覆う絶縁層、又は基板を設け(図示せず)、半導体装置76a、半導体装置76bを作製する(図3(C1)(C2)参照。)。半導体装置76a、半導体装置76bは、図3(C1)で示す点線によって分断することで個々の半導体装置76a、半導体装置76bとなる。

#### 【0041】

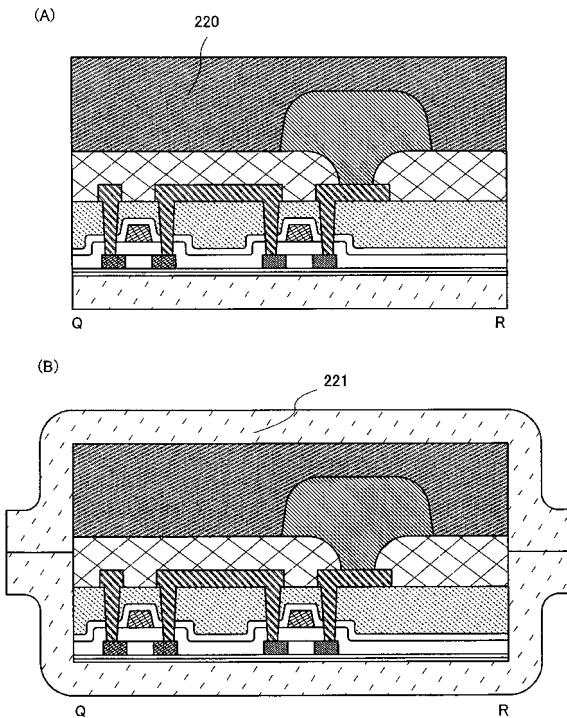

図3における半導体装置の作製工程を、図3(D)線S-Tに対応する断面図である

10

20

30

40

50

図7、図8を用いて説明する。

【0042】

図7(A)は、図3(A1)の工程に対応しており、基板70に薄膜回路部が配線層235bを基板70に達する様にコンタクトホールに形成されている。基板70上に、剥離層232、絶縁層231a、絶縁層231b、ゲート絶縁層238、図5と同様の構造のpチャネル型薄膜トランジスタ230a、nチャネル型薄膜トランジスタ230b、絶縁層239、絶縁層245が形成されている。pチャネル型薄膜トランジスタ230aとnチャネル型薄膜トランジスタ230bとは電気的に接続しておりCMOS構造となっている。pチャネル型薄膜トランジスタ230a、nチャネル型薄膜トランジスタ230bの半導体層とそれぞれに接続する配線層235a、配線層235b、配線層235cは絶縁層211上に形成され、配線層235bは、絶縁層245、絶縁層239、ゲート絶縁層238、絶縁層231b、絶縁層231aに形成されたコンタクトホールに基板70と接するように形成されている。また、薄膜回路部を覆うように絶縁層237が形成されている。

【0043】

その後図3のように、剥離層232を除去し、剥離工程を行い、図3(C1)の工程に対応する図7(B)のように、アンテナとして機能する導電層241が液滴吐出装置240を用いた液滴吐出法により形成される。液滴吐出法とは流動体である構成物形成材料を含む組成物を、液滴として吐出(噴出)し、所望なパターン形状に形成する方法である。構成物の被形成領域に、構成物形成材料を含む液滴を吐出し、焼成、乾燥等を行って固定化し所望なパターンの構成物を形成する。

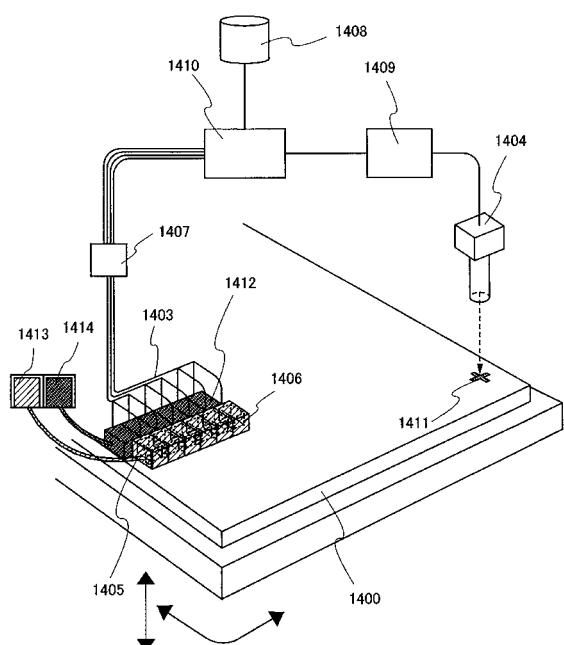

【0044】

液滴吐出法に用いる液滴吐出装置の一態様を図19に示す。液滴吐出手段1403の個々のヘッド1405、ヘッド1412は制御手段1407に接続され、それがコンピュータ1410で制御することにより予めプログラミングされたパターンに描画することができる。描画するタイミングは、例えば、基板1400上に形成されたマーカ1411を基準に行けば良い。或いは、基板1400の縁を基準にして基準点を確定させても良い。これを撮像手段1404で検出し、画像処理手段1409にてデジタル信号に変換したものをコンピュータ1410で認識して制御信号を発生させて制御手段1407に送る。撮像手段1404としては、電荷結合素子(CCD)や相補型金属酸化物半導体(CMOS)を利用したイメージセンサなどを用いることができる。勿論、基板1400上に形成されるべきパターンの情報は記憶媒体1408に格納されたものであり、この情報を基にして制御手段1407に制御信号を送り、液滴吐出手段1403の個々のヘッド1405、ヘッド1412を個別に制御することができる。吐出する材料は、材料供給源1413、材料供給源1414より配管を通してヘッド1405、ヘッド1412にそれぞれ供給される。

【0045】

ヘッド1405内部は、点線1406が示すように液状の材料を充填する空間と、吐出口であるノズルを有する構造となっている。図示しないが、ヘッド1412もヘッド1405と同様な内部構造を有する。ヘッド1405とヘッド1412のノズルを異なるサイズで設けると、異なる材料を異なる幅で同時に描画することができる。一つのヘッドで、導電性材料や有機、無機材料などをそれぞれ吐出し、描画することができ、層間膜のような広領域に描画する場合は、スループットを向上させるため複数のノズルより同材料を同時に吐出し、描画することができる。大型基板を用いる場合、ヘッド1405、ヘッド1412は基板上を、矢印の方向に自在に走査し、描画する領域を自由に設定することができ、同じパターンを一枚の基板に複数描画することができる。

【0046】

液滴吐出法を用いて導電層を形成する場合、粒子状に加工された導電性材料を含む組成物を吐出し、焼成によって融合や融着接合させ固化することで導電層を形成する。このように導電性材料を含む組成物を吐出し、焼成することによって形成された導電層(また

は絶縁層)においては、スパッタ法などで形成した導電層(または絶縁層)が、多くは柱状構造を示すのに対し、多くの粒界を有する多結晶状態を示すことが多い。

【0047】

導電層241及び薄膜回路部を覆うように絶縁層243を形成し、可撓性を有する基板244で封止し半導体装置を作製する(図7(A)(B)参照。)。図7(A)では、絶縁層220をスピンドルコート法によって形成する。

【0048】

流動性を有する組成物は、導電性材料を溶媒に溶解又は分散させたものを用いる。導電性材料とは、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al等の金属、Cd、Znの金属硫化物、Fe、Ti、Si、Ge、Si、Zr、Baなどの酸化物、ハロゲン化銀の微粒子又は分散性ナノ粒子に相当する。また、透明導電膜として用いられるインジウム錫酸化物(ITO)、インジウム錫酸化物と酸化珪素からなるITO、有機インジウム、有機スズ、酸化亜鉛、窒化チタン等に相当する。但し、吐出口から吐出する組成物は、比抵抗値を考慮して、金、銀、銅のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。但し、銀、銅を用いる場合には、不純物対策のため、合わせてバリア膜を設けるとよい。バリア膜としては、窒化珪素膜やニッケルボロン(NiB)を用いることができる。溶媒は、酢酸ブチル、酢酸エチル等のエステル類、イソプロピルアルコール、エチルアルコール等のアルコール類、メチルエチルケトン、アセトン等の有機溶剤等、又は水を用いる。

【0049】

吐出する組成物は、導電性材料を溶媒に溶解又は分散させたものであるが、他にも分散剤や、バインダーと呼ばれる熱硬化性樹脂が含まれている。特にバインダーに関しては、焼成時にクラックや不均一な焼きムラが発生するのを防止する働きを持つ。よって、形成される導電層には、有機材料が含まれることがある。含まれる有機材料は、加熱温度、雰囲気、時間により異なる。この有機材料は、金属粒子のバインダー、溶媒、分散剤、及び被覆剤として機能する有機樹脂などであり、代表的には、ポリイミド、アクリル、ノボラック樹脂、メラミン樹脂、フェノール樹脂、エポキシ樹脂、珪素樹脂、フラン樹脂、ジアリルフタレート樹脂等や、公知の有機樹脂が挙げられる。

【0050】

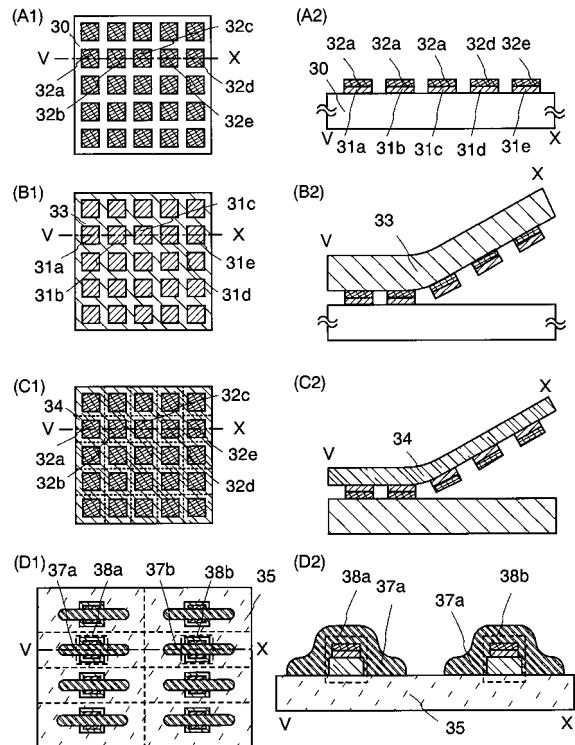

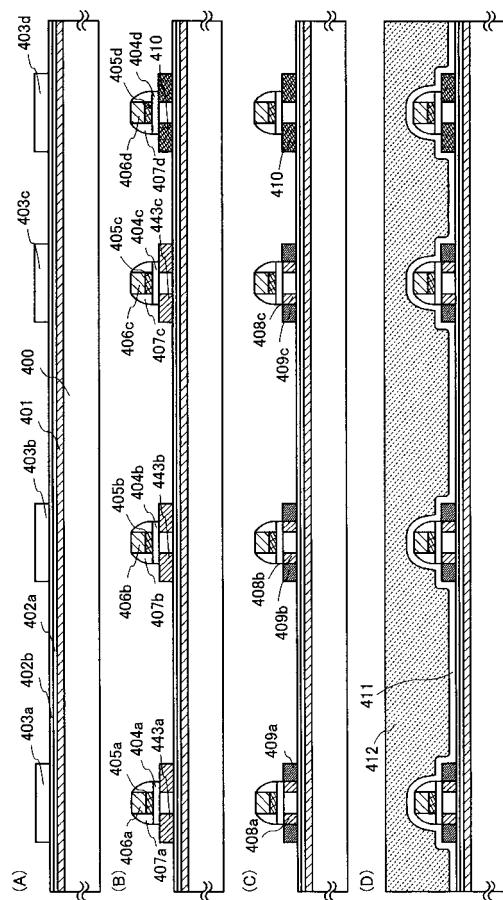

図2、図3では、基板上に形成された薄膜回路部を選択的に封止フィルムとなる基板に剥離、接着して半導体装置を作製する例を示した。他の薄膜回路部の設置例を図4に示す。

【0051】

図4でも図2と同様、基板30上に複数の薄膜回路部が剥離層を介して形成されている。薄膜回路部31a、薄膜回路部31b、薄膜回路部31c、薄膜回路部31d、薄膜回路部31eはそれぞれ、配線層32a、配線層32b、配線層32c、配線層32d、配線層32eを有している(図4(A1)(A2)参照。)。薄膜回路部31a、薄膜回路部31b、薄膜回路部31c、薄膜回路部31d、薄膜回路部31e下の剥離層を一部、又は全部除去し、基板30から剥離しやすい状態にする。接着面を有する可撓性の基板33を薄膜回路部31a、薄膜回路部31b、薄膜回路部31c、薄膜回路部31d、薄膜回路部31eの配線層32a、配線層32b、配線層32c、配線層32d、配線層32e側に接着し、剥離する(図4(B1)(B2)参照。)。図2と同様に配線層が再度上面に露出するように、接着面を有する可撓性の基板34を薄膜回路部31a、薄膜回路部31b、薄膜回路部31c、薄膜回路部31d、薄膜回路部31e側に接着し、配線層32a、配線層32b、配線層32c、配線層32d、配線層32eが露出した状態とする(図4(C1)(C2)参照。)。その後、図4(C1)の点線部で基板34を分断し、個々の薄膜回路部とする。個々に分断された基板を有する薄膜回路部38a、38bは、基板34ごと封止材となる可撓性の基板35に選択的に設置される。配線層及び基板35上に、アンテナとして機能する導電層37a、導電層37bを印刷法により形成する。その後導電層37a、導電層37bを覆う絶縁層、又は基板を設け封止し、レーザ光などで

10

20

30

40

50

図4(D1)における点線で分断して半導体装置を作製する。図4の場合、導電層37aは、基板を有する薄膜回路部38aを覆うように形成するため、導電層37aの膜厚は、基板を有する薄膜回路部38aの膜厚と同程度以上が好ましい。導電層37aの膜厚は、導電層37aの被形成領域の、流動性を有する導電性材料を含む組成物に対するぬれ性を制御することで、調整することができる。実施の形態2で詳述するが、流動性を有する導電性材料を含む組成物に対する接触角が大きくなるように被形成領域を制御すれば、組成物はぬれ広がらないので、膜厚を厚く形成することができる。また、導電層37aの膜厚が薄く、膜として連続性を有さない場合は、導電層を再度印刷法によって積層することもできる。

## 【0052】

10

薄膜回路部を作製する基板、としては、ガラス基板や可撓性基板の他、石英基板、シリコン基板、金属基板、ステンレス基板等を用いることができる。可撓性を有する基板としては、折り曲げることができる(フレキシブル)基板のことであり、例えば、ポリカーボネート、ポリアリレート、ポリエーテルスルファン等からなるプラスチック基板等が挙げられる。また、ラミネートフィルム(ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなる)、纖維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)などを用いることもできる。本明細書において、基板とは薄膜回路部及びアンテナを封止することができる支持材であり、前述の様々な材料からなる基材等を含む。

## 【0053】

20

薄膜回路部及びアンテナを、可撓性を有する基板上に接着し、設置することで、可撓性を有する半導体装置を得ることができる。フィルムは、熱圧着により、被処理体と加熱処理と加圧処理が行われるものであり、加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、又は最外層に設けられた層(接着層ではない)を加熱処理によって溶かし、加圧により接着する。また、基板に接着層が設けられていてもよいし、接着層が設けられていてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。

## 【0054】

以上のように、本発明により高性能、高信頼性の半導体装置を低成本で、歩留まりよく作製することができる。

30

## 【0055】

## (実施の形態2)

本実施の形態では、薄膜トランジスタ、記憶素子及びアンテナを含む本発明の半導体装置の作製方法について、図面を参照して説明する。本実施の形態で示す半導体装置は、非接触でデータの読み出しこと書き込みが可能であることを特徴としており、データの伝送形式は、一対のコイルを対向に配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別されるが、いずれの方式を用いてもよい。

## 【0056】

まず、基板400の一表面に、剥離層401を形成する。基板400は、ガラス基板、石英基板、金属基板やステンレス基板の一表面に絶縁層を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いるとよい。このような基板400であれば、その面積や形状に大きな制限はないため、基板400として、例えば、1辺が1メートル以上あって、矩形状のものを用いれば、生産性を格段に向上させることができる。このような利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。なお、本工程では、剥離層401は、基板400の全面に設けているが、必要に応じて、基板400の全面に剥離層を設けた後に、フォトリソグラフィ法によりパターニングして、選択的に設けてもよい。また、基板400に接するように剥離層401を形成しているが、必要に応じて、基板400に接するように下地となる絶縁層を形成し、当該絶縁層に接するように剥離層401を形成してもよい。

40

50

## 【0057】

剥離層401は、公知の手段（スパッタリング法やプラズマCVD法等）により、タンゲステン（W）、モリブデン（Mo）、チタン（Ti）、タンタル（Ta）、ニオブ（Nb）、ニッケル（Ni）、コバルト（Co）、ジルコニウム（Zr）、亜鉛（Zn）、ルテニウム（Ru）、ロジウム（Rh）、鉛（Pd）、オスミウム（Os）、イリジウム（Ir）、珪素（Si）から選択された元素または前記元素を主成分とする合金材料若しくは化合物材料からなる層を、単層又は積層して形成する。珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。

## 【0058】

剥離層401が単層構造の場合、例えば、タンゲステン層、モリブデン層またはタンゲステンとモリブデンの混合物を含む層を形成する。あるいは、タンゲステンの酸化物若しくは酸化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層またはタンゲステンとモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。なお、タンゲステンとモリブデンの混合物とは、例えば、タンゲステンとモリブデンの合金に相当する。また、タンゲステンの酸化物は、酸化タンゲステンと表記することがある。

10

## 【0059】

剥離層401が積層構造の場合、1層目としてタンゲステン層、モリブデン層またはタンゲステンとモリブデンの混合物を含む層を形成し、2層目として、タンゲステン、モリブデンまたはタンゲステンとモリブデンの混合物の酸化物、窒化物、酸化窒化物又は窒化酸化物を形成する。

20

## 【0060】

なお、剥離層401として、タンゲステンを含む層とタンゲステンの酸化物を含む層の積層構造を形成する場合、タンゲステンを含む層を形成し、その上層に酸化珪素を含む層を形成することで、タンゲステン層と酸化珪素層との界面に、タンゲステンの酸化物を含む層が形成されることを活用してもよい。これは、タンゲステンの窒化物、酸化窒化物及び窒化酸化物を含む層を形成する場合も同様であり、タンゲステンを含む層を形成後、その上層に窒化珪素層、酸化窒化珪素層、窒化酸化珪素層を形成するとよい。また、タンゲステンの酸化物は、 $W_{O_x}$ で表され、Xは2~3であり、Xが2の場合( $W_{O_2}$ )、Xが2.5の場合( $W_2O_5$ )、Xが2.75の場合( $W_4O_{11}$ )、Xが3の場合( $W_{O_3}$ )などがある。タンゲステンの酸化物を形成するにあたり、上記に挙げたXの値に特に制約はなく、エッチングレート等を基に、どの酸化物を形成するかを決めるとい。なお、エッチングレートとして最も良いものは、酸素雰囲気下で、スパッタリング法により形成するタンゲステンの酸化物を含む層( $W_{O_x}$ 、 $0 < X < 3$ )である。従って、作製時間の短縮のため、剥離層として、酸素雰囲気下でスパッタリング法によりタンゲステンの酸化物を含む層を形成するとよい。

30

## 【0061】

剥離層401上に下地膜として、スパッタリング法、PVD法（Physical Vapor Deposition）、減圧CVD法（LPCVD法）、またはプラズマCVD法等のCVD法（Chemical Vapor Deposition）などにより窒化酸化珪素膜（Si<sub>x</sub>N<sub>y</sub>）を用いて下地膜101aを10~200nm（好ましくは50~100nm）形成し、酸化窒化珪素膜（Si<sub>x</sub>O<sub>y</sub>N）を用いて下地膜101bを50~200nm（好ましくは100~150nm）積層する。また、塗布法、印刷法などによって絶縁層を形成しても良い。本実施の形態では、プラズマCVD法を用いて絶縁層402a、絶縁層402bを形成する。

40

## 【0062】

絶縁層402a、絶縁層402bとしては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素などを用いることができ、単層でも2層、3層といった積層構造でもよい。なお本明細書中において酸化窒化珪素とは酸素の組成比が窒素の組成比より大きい物質であり、窒素を含む酸化珪素とも言える。同様に、窒化酸化珪素とは、窒素の組成比が酸素の組成比より大きい物質であり、酸素を含む窒化珪素とも言える。本実施の形態では、基板上にSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>O、N<sub>2</sub>及びH<sub>2</sub>を反応ガスとして窒化酸化珪素膜を膜厚50nm

50

形成し、 $\text{SiH}_4$ 及び $\text{N}_2\text{O}$ を反応ガスとして酸化窒化珪素膜を膜厚100nmで形成する。また窒化酸化珪素膜の膜厚を140nm、積層する酸化窒化珪素膜の膜厚を100nmとしてもよい。

#### 【0063】

次いで、下地膜上に半導体膜を形成する。半導体膜は25~200nm(好ましくは30~150nm)の厚さで公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により成膜すればよい。本実施の形態では、非晶質半導体膜を、レーザ結晶化し、結晶性半導体膜とするものを用いるのが好ましい。

#### 【0064】

半導体膜を形成する材料は、シランやゲルマンに代表される半導体材料ガスを用いて10

気相成長法やスパッタリング法で作製される非晶質半導体(以下「アモルファス半導体:AS」ともいう。)、該非晶質半導体を光エネルギーや熱エネルギーを利用して結晶化させた多結晶半導体、或いはセミアモルファス(微結晶若しくはマイクロクリスタルとも呼ばれる。以下「SAS」ともいう。)半導体などを用いることができる。

#### 【0065】

SASは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいる。少なくとも膜中の一部の領域には、0.5~20nmの結晶領域を観測することが出来、珪素を主成分とする場合にはラマンスペクトルが520cm<sup>-1</sup>よりも低波数側にシフトしている。X線回折では珪素結晶格子に由来するとされる(111)、(220)の回折ピークが観測される。未結合手(ダンギリングボンド)の中和剤として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。SASは、珪化物気体をグロー放電分解(プラズマCVD)して形成する。珪化物気体としては、 $\text{SiH}_4$ 、その他にも $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$ などを用いることが可能である。また $\text{F}_2$ 、 $\text{GeF}_4$ を混合させても良い。この珪化物気体を $\text{H}_2$ 、又は、 $\text{H}_2$ と $\text{He}$ 、 $\text{Ar}$ 、 $\text{Kr}$ 、 $\text{Ne}$ から選ばれた一種または複数種の希ガス元素で希釈しても良い。希釈率は2~1000倍の範囲、圧力は概略0.1Pa~133Paの範囲、電源周波数は1MHz~120MHz、好ましくは13MHz~60MHzである。基板加熱温度は300以下が好ましく、100~200の基板加熱温度でも形成可能である。ここで、主に成膜時に取り込まれる不純物元素として、酸素、窒素、炭素などの大気成分に由来する不純物は $1 \times 10^{20}$ atoms/cm<sup>3</sup>以下とすることが望ましく、特に、酸素濃度は $5 \times 10^{19}$ atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{19}$ atoms/cm<sup>3</sup>以下となるようにすることが好ましい。また、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なSASが得られる。また半導体膜としてフッ素系ガスより形成されるSAS層に水素系ガスより形成されるSAS層を積層してもよい。

#### 【0066】

非晶質半導体としては、代表的には水素化アモルファシリコン、結晶性半導体としては代表的にはポリシリコンなどがあげられる。ポリシリコン(多結晶シリコン)には、800以上のプロセス温度を経て形成されるポリシリコンを主材料として用いた所謂高温ポリシリコンや、600以下の中間温度で形成されるポリシリコンを主材料として用いた所謂低温ポリシリコン、また結晶化を促進する元素などを添加し結晶化させたポリシリコンなどを含んでいる。もちろん、前述したように、セミアモルファス半導体又は半導体膜の一部に結晶相を含む半導体を用いることもできる。

#### 【0067】

また、半導体として、有機半導体材料を用い、印刷法、スプレー法、スピンドル塗布法、液滴吐出法などで形成することができる。この場合、上記エッチング工程が必要ないため、工程数を削減することができる。有機半導体としては、低分子材料、高分子材料などが用いられ、有機色素、導電性高分子材料などの材料も用いることができる。本発明に用いる有機半導体材料としては、その骨格が共役二重結合から構成される電子共役系の高

10

20

30

40

50

分子材料が望ましい。代表的には、ポリチオフェン、ポリフルオレン、ポリ(3-アルキルチオフェン)、ポリチオフェン誘導体、ペンタセン等の可溶性の高分子材料を用いることができる。

【0068】

その他にも本発明に用いることができる有機半導体材料としては、可溶性の前駆体を成膜した後で処理することにより半導体層を形成することができる材料がある。なお、このような前駆体を経由する有機半導体材料としては、ポリチエニレンビニレン、ポリ(2,5-チエニレンビニレン)、ポリアセチレン、ポリアセチレン誘導体、ポリアリレンビニレンなどがある。

【0069】

前駆体を有機半導体に変換する際には、加熱処理だけではなく塩化水素ガスなどの反応触媒を添加することがなされる。また、これらの可溶性有機半導体材料を溶解させる代表的な溶媒としては、トルエン、キシレン、クロロベンゼン、ジクロロベンゼン、アニソール、クロロフォルム、ジクロロメタン、ブチルラクトン、ブチルセルソルブ、シクロヘキサン、NMP(N-メチル-2-ピロリドン)、シクロヘキサン、2-ブタノン、ジオキサン、ジメチルホルムアミド(DMF)または、THF(テトラヒドロフラン)などを適用することができる。

【0070】

半導体膜に、結晶性半導体膜を用いる場合、その結晶性半導体膜の作製方法は、公知の方法(レーザ結晶化法、熱結晶化法、またはニッケルなどの結晶化を助長する元素を用いた熱結晶化法等)を用いれば良い。また、SASである微結晶半導体をレーザ照射して結晶化し、結晶性を高めることもできる。結晶化を助長する元素を導入しない場合は、非晶質半導体膜にレーザ光を照射する前に、窒素雰囲気下500で1時間加熱することによって非晶質半導体膜の含有水素濃度を $1 \times 10^{20}$ atoms/cm<sup>3</sup>以下にまで放出させる。これは水素を多く含んだ非晶質半導体膜にレーザ光を照射すると膜が破壊されてしまうからである。結晶化のための加熱処理は、加熱炉、レーザ照射、若しくはランプから発する光の照射(ランプアニールともいう)などを用いることができる。加熱方法としてGRTA(Gas Rapid Thermal Anneal)法、LRTA(Lamp Rapid Thermal Anneal)法等のRTA法がある。

【0071】

非晶質半導体膜への金属元素の導入の仕方としては、当該金属元素を非晶質半導体膜の表面又はその内部に存在させ得る手法であれば特に限定はなく、例えばスパッタ法、CVD法、プラズマ処理法(プラズマCVD法も含む)、吸着法、金属塩の溶液を塗布する方法を使用することができる。このうち溶液を用いる方法は簡便であり、金属元素の濃度調整が容易であるという点で有用である。また、このとき非晶質半導体膜の表面のぬれ性を改善し、非晶質半導体膜の表面全体に水溶液を行き渡らせるため、酸素雰囲気中のUV光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を成膜することが望ましい。

【0072】

連続発振が可能な固体レーザを用い、基本波の第2高調波～第4高調波のレーザ光を照射することで、大粒径の結晶を得ることができる。例えば、代表的には、Nd:YVO<sub>4</sub>レーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いるのが望ましい。具体的には、連続発振のYVO<sub>4</sub>レーザから射出されたレーザ光を非線形光学素子により高調波に変換し、出力数W以上のレーザ光を得る。そして、好ましくは光学系により照射面にて矩形状または橜円形状のレーザ光に成形して、半導体膜に照射する。このときのエネルギー密度は0.001～100MW/cm<sup>2</sup>程度(好ましくは0.1～10MW/cm<sup>2</sup>)が必要である。そして、走査速度を0.5～2000cm/sec程度(好ましくは10～200cm/sec)とし、照射する。

【0073】

レーザのビーム形状は、線状とすると好ましい。その結果、スループットを向上させ

10

20

30

40

50

ることができる。またさらにレーザは、半導体膜に対して入射角（ $0 < \theta < 90$  度）を持たせて照射させるとよい。レーザの干渉を防止することができるからである。

【0074】

このようなレーザと、半導体膜とを相対的に走査することにより、レーザ照射を行うことができる。またレーザ照射において、ビームを精度よく重ね合わせたり、レーザ照射開始位置やレーザ照射終了位置を制御するため、マーカを形成することもできる。マーカは非晶質半導体膜と同時に、基板上へ形成すればよい。

【0075】

なおレーザは、連続発振またはパルス発振の気体レーザ、固体レーザ、銅蒸気レーザまたは金蒸気レーザなどを用いることができる。気体レーザとして、エキシマレーザ、Arレーザ、Krレーザ、He-Cdレーザなどがあり、固体レーザとして、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、Y<sub>2</sub>O<sub>3</sub>レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライドレーザ、Ti:サファイアレーザなどが挙げられる。

【0076】

また、パルス発振のレーザ光の発振周波数を0.5MHz以上とし、通常用いられている数十Hz～数百Hzの周波数帯よりも著しく高い周波数帯を用いてレーザ結晶化を行っても良い。パルス発振でレーザ光を半導体膜に照射してから半導体膜が完全に固化するまでの時間は数十nsec～数百nsecと言われている。よって上記周波数帯を用いることで、半導体膜がレーザ光によって溶融してから固化するまでに、次のパルスのレーザ光を照射できる。したがって、半導体膜中において固液界面を連続的に移動させることができるので、走査方向に向かって連続的に成長した結晶粒を有する半導体膜が形成される。具体的には、含まれる結晶粒の走査方向における幅が10～30μm、走査方向に対して垂直な方向における幅が1～5μm程度の結晶粒の集合を形成することができる。該走査方向に沿って長く伸びた単結晶の結晶粒を形成することで、少なくとも薄膜トランジスタのチャネル方向には結晶粒界のほとんど存在しない半導体膜の形成が可能となる。

【0077】

また、希ガスや窒素などの不活性ガス雰囲気中でレーザ光を照射するようにしても良い。これにより、レーザ光の照射により半導体表面の荒れを抑えることができ、界面準位密度のばらつきによって生じるしきい値のばらつきを抑えることができる。

【0078】

非晶質半導体膜の結晶化は、熱処理とレーザ光照射による結晶化を組み合わせてもよく、熱処理やレーザ光照射を単独で、複数回行っても良い。

【0079】

本実施の形態では、絶縁層402b上に、非晶質半導体膜を形成し、非晶質半導体膜を結晶化させることによって結晶性半導体膜を形成する。非晶質半導体膜としては、SiH<sub>4</sub>、H<sub>2</sub>の反応ガスにより形成する非晶質珪素を用いる。本実施の形態において、絶縁層402a、絶縁層402b、非晶質半導体膜は、同チャンバー内で真空を破らずに330の同一温度下で、反応ガスを切り替えながら連続的に形成する。

【0080】

非晶質半導体膜上に形成された酸化膜を除去した後、酸素雰囲気中のUV光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を10～50nm形成する。本実施の形態では、結晶化を助長する元素としてNiを用いる。Ni酢酸塩10ppmを含有した水溶液をスピンドルティング法により塗布する。

【0081】

本実施の形態では、熱処理をRTA法により750℃で3分間行った後、半導体膜上に形成される酸化膜を除去し、レーザ光を照射する。非晶質半導体膜は以上の結晶化処理により結晶化し、結晶性半導体膜として形成される。

【0082】

金属元素を用いた結晶化を行った場合、金属元素を低減、又は除去するためにゲッタリング工程を施す。本実施の形態では、非晶質半導体膜をゲッタリングシンクとして金属

10

20

30

40

50

元素を捕獲する。まず、結晶性半導体膜上に酸素雰囲気中でのUV光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を形成する。酸化膜は加熱処理によって厚膜化することが望ましい。次いでプラズマCVD法（本実施の形態における条件350W、35Pa）を用いて、非晶質半導体膜を50nmの膜厚で形成する。

【0083】

その後、RTA法により744で3分間熱処理を行い、金属元素を低減、又は除去する。熱処理は窒素雰囲気下で行ってもよい。そして、ゲッタリングシンクとなっていた非晶質半導体膜、及び非晶質半導体膜上に形成された酸化膜をフッ酸等により除去し、金属元素が低減、又は除去された結晶性半導体膜を得ることができる。本実施の形態では、ゲッタリングシンクとなった非晶質半導体膜の除去をTMASH（Tetramethyl ammonium hydroxide）を用いて行う。

【0084】

このようにして得られた半導体膜に対して、薄膜トランジスタのしきい値電圧を制御するために微量な不純物元素（ボロンまたはリン）のドーピングを行ってもよい。この不純物元素のドーピングは、結晶化工程の前の非晶質半導体膜に行ってもよい。非晶質半導体膜の状態で不純物元素をドーピングすると、その後の結晶化のための加熱処理によって、不純物の活性化も行うことができる。また、ドーピングの際に生じる欠陥等も改善することができる。

【0085】

次に結晶性半導体膜をマスクを用いてパターニングする。本実施の形態では結晶性半導体膜上に形成された酸化膜を除去した後、新たに酸化膜を形成する。そして、フォトマスクを作製し、フォトリソグラフィ法を用いたパターニング処理により、半導体層403a、半導体層403b、半導体層403c、及び半導体層403dを形成する。

【0086】

パターニングの際のエッチング加工は、プラズマエッチング（ドライエッチング）又はウェットエッチングのどちらを採用しても良いが、大面積基板を処理するにはプラズマエッチングが適している。エッチングガスとしては、CF<sub>4</sub>、NF<sub>3</sub>、Cl<sub>2</sub>、BCl<sub>3</sub>、などのフッ素系又は塩素系のガスを用い、HeやArなどの不活性ガスを適宜加えても良い。また、大気圧放電のエッチング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

【0087】

本発明において、配線層若しくは電極層を形成する導電層や、所定のパターンを形成するためのマスク層などを、液滴吐出法のような選択的にパターンを形成できる方法により形成してもよい。液滴吐出（噴出）法（その方式によっては、インクジェット法とも呼ばれる。）は、特定の目的に調合された組成物の液滴を選択的に吐出（噴出）して所定のパターン（導電層や絶縁層など）を形成することができる。この際、被形成領域にぬれ性や密着性を制御する処理を行ってもよい。また、パターンが転写、または描写できる方法、例えば印刷法（スクリーン印刷やオフセット印刷などパターンが形成される方法）なども用いることができる。

【0088】

本実施の形態において、用いるマスクは、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、透過性を有するポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いることもできる。或いは、感光剤を含む市販のレジスト材料を用いてもよく、例えば、代表的なポジ型レジストである、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物、ネガ型レジストであるベース樹脂、ジフェニルシランジオール及び酸発生剤などを用いてもよい。液滴吐出法を用いる場合、いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりし

10

20

30

40

50

て適宜調整する。

【0089】

半導体層上の酸化膜を除去し、半導体層403a、半導体層403b、半導体層403c、及び半導体層403dを覆うゲート絶縁層を形成する。ゲート絶縁層はプラズマCVD法またはスパッタ法などを用い、厚さを10～150nmとして珪素を含む絶縁膜で形成する。ゲート絶縁層としては、窒化珪素、酸化珪素、酸化窒化珪素、窒化酸化珪素に代表される珪素の酸化物材料又は窒化物材料等の公知の材料で形成すればよく、積層でも単層でもよい。また、絶縁層は窒化珪素膜、酸化珪素膜、窒化珪素膜の3層の積層、酸化窒化珪素膜の単層、2層からなる積層でも良い。好適には、緻密な膜質を有する窒化珪素膜を用いるとよい。さらに半導体層とゲート絶縁層の間に、膜厚1～100nm、好ましくは1～10nm、さらに好ましくは2～5nmである膜厚の薄い酸化珪素膜を形成してもよい。薄い酸化珪素膜の形成方法としては、GRTA法、LRTA法等を用いて半導体領域表面を酸化し、熱酸化膜を形成することで、膜厚の薄い酸化珪素膜を形成することができる。なお、低い成膜温度でゲートリーク電流に少ない緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。本実施の形態では、ゲート絶縁層107として酸化窒化珪素膜を膜厚115nm形成する。

【0090】

次いで、ゲート絶縁層上にゲート電極層として用いる膜厚20～100nmの第1の導電膜と、膜厚100～400nmの第2の導電膜とを積層して形成する。第1の導電膜及び第2の導電膜は、スパッタリング法、蒸着法、CVD法等の公知の手法により形成することができる。第1の導電膜及び第2の導電膜はタンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジウム(Nd)から選ばれた元素、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、第1の導電膜及び第2の導電膜としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、2層構造に限定されず、例えば、第1の導電膜として膜厚50nmのタングステン膜、第2の導電膜として膜厚500nmのアルミニウムとシリコンの合金(Al-Si)膜、第3の導電膜として膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタングステンに代えて窒化タングステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金(Al-Si)膜に代えてアルミニウムとチタンの合金膜(Al-Ti)を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。また、単層構造であってもよい。本実施の形態では、第1の導電膜として窒化タンタル(TaN)を膜厚30nm形成し、第2の導電膜としてタングステン(W)を膜厚370nm形成する。

【0091】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、第1の導電膜及び第2の導電膜をパターニングし、第1のゲート電極層405a、第1のゲート電極層405b、第1のゲート電極層405c、及び第1のゲート電極層405d、第2のゲート電極層406a、第2のゲート電極層406b、第2のゲート電極層406c、第2のゲート電極層406dを形成する。ICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッチング法を用い、エッチング条件(コイル型の電極層に印加される電力量、基板側の電極層に印加される電力量、基板側の電極温度等)を適宜調節することにより、第1のゲート電極層405a、第1のゲート電極層405b、第1のゲート電極層405c、及び第1のゲート電極層405d、第2のゲート電極層406a、第2のゲート電極層406b、第2のゲート電極層406c、第2のゲート電極層406dを所望のテーパー形状を有するようにエッチングすることもできる。また、テーパー形状は、マスクの形状によつても角度等を制御することができる。なお、エッチング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>もしくはCCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、CF<sub>5</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素系ガス又はO<sub>2</sub>を適宜用いることができる。本

実施の形態では、 $\text{C F}_5$ 、 $\text{C l}_2$ 、 $\text{O}_2$ からなるエッティング用ガスを用いて第2の導電膜のエッティングを行い、連続して $\text{C F}_5$ 、 $\text{C l}_2$ からなるエッティング用ガスを用いて第1の導電膜をエッティングする。

【0092】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成して、半導体層403a、半導体層403b、半導体層403cに、イオンドープ法又はイオン注入法により、n型を付与する不純物元素を低濃度に添加して、n型不純物領域443a、n型不純物領域443b、n型不純物領域443cを形成する。n型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン(P)、砒素(As)を用いる。

【0093】

次に、フォトリソグラフィ法によりレジストからなるマスクを形成して、半導体層403dに、p型を付与する不純物元素を添加して、p型不純物領域410とチャネル形成領域を形成する。P型を付与する不純物元素は、例えばボロン(B)を用いる。

【0094】

次に、ゲート絶縁層と第1のゲート電極層405a、第1のゲート電極層405b、第1のゲート電極層405c、及び第1のゲート電極層405d、第2のゲート電極層406a、第2のゲート電極層406b、第2のゲート電極層406c、第2のゲート電極層406dを覆うように、絶縁層を形成する。絶縁層は、公知の手段(プラズマCVD法やスパッタ法)により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む層や、有機樹脂などの有機材料を含む層を、単層又は積層して形成する。次に、絶縁層を、垂直方向を主体とした異方性エッティングにより選択的にエッティングして、第1のゲート電極層405a、第1のゲート電極層405b、第1のゲート電極層405c、及び第1のゲート電極層405d、第2のゲート電極層406a、第2のゲート電極層406b、第2のゲート電極層406c、第2のゲート電極層406dの側面に接する絶縁層(サイドウォールともよばれる)407a、絶縁層407b、絶縁層407c、絶縁層407dを形成する。また、絶縁層407a、絶縁層407b、絶縁層407c、絶縁層407dの作製と同時に、ゲート絶縁層もエッティングし、絶縁層404a、絶縁層404b、絶縁層404c、絶縁層404dを形成する。絶縁層404a、絶縁層404b、絶縁層404cは、後にLDD(Lightly Doped drain)領域を形成する際のドーピング用のマスクとして用いる。

【0095】

次に、フォトリソグラフィ法により形成したレジストからなるマスクと、絶縁層404a、絶縁層404b、絶縁層404cをマスクとして用いて、半導体層403a、半導体層403b、半導体層403cにn型を付与する不純物元素を添加して、低濃度n型不純物領域(LDD領域ともよぶ)408a、低濃度n型不純物領域408b、低濃度n型不純物領域408c、高濃度不純物領域409a、高濃度不純物領域409b、高濃度不純物領域409cとを形成する(図9(C)参照)。低濃度n型不純物領域408a、低濃度n型不純物領域408b、低濃度n型不純物領域408cが含む不純物元素の濃度は、高濃度不純物領域409a、高濃度不純物領域409b、高濃度不純物領域409cの不純物元素の濃度よりも低い。

【0096】

なお、LDD領域を形成するためには、ゲート電極を2層以上の積層構造として、当該ゲート電極にテーパーエッティングや異方性エッティングを行って、当該ゲート電極を構成する下層の導電層をマスクとして用いる手法と、サイドウォールの絶縁層をマスクとして用いる手法がある。前者の手法を採用して形成された薄膜トランジスタは、ゲート絶縁膜を介してLDD領域をゲート電極と重ねて配置させた構造となっているが、この構造は、ゲート電極のテーパーエッティングや異方性エッティングを利用するため、LDD領域の幅を制御することが難しく、エッティング工程が良好に行われなければ、LDD領域を形成することが出来ない場合がある。一方、後者のサイドウォールの絶縁層をマスクとして用いる手法は、前者の手法と比較すると、LDD領域の幅の制御が容易であり、また、LDD領

10

20

30

40

50

域を確実に形成することができる。

【0097】

不純物元素を活性化するために加熱処理、強光の照射、又はレーザ光の照射を行ってもよい。活性化と同時にゲート絶縁層へのプラズマダメージやゲート絶縁層と半導体層との界面へのプラズマダメージを回復することができる。

【0098】

次いで、パッシベーション膜として水素を含む絶縁層411を形成する。この絶縁層411としては、プラズマCVD法またはスパッタ法を用い、厚さを100～200nmとして珪素を含む絶縁膜で形成する。絶縁層411は窒化珪素膜に限定されるものでなく、プラズマCVDを用いた窒化酸化珪素(SiNO)膜でもよく、他の珪素を含む絶縁膜を単層または積層構造として用いてもよい。

10

【0099】

さらに、窒素雰囲気中で、300～550で1～12時間の熱処理を行い、半導体層を水素化する工程を行う。好ましくは、400～500で行う。この工程は絶縁層411に含まれる水素により半導体層のダングリングボンドを終端する工程である。

【0100】

絶縁層411は窒化珪素、酸化珪素、酸化窒化珪素(SiON)、窒化酸化珪素(SiNO)、窒化アルミニウム(AlN)、酸化窒化アルミニウム(AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム(AlNO)または酸化アルミニウム、ダイアモンドライカーボン(DLC)、窒素含有炭素膜(CN)を含む物質から選ばれた材料で形成することができる。また、シリコン(Si)と酸素(O)との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、もしくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いてもよい。

20

【0101】

次いで、層間絶縁層となる絶縁層412を形成する(図9(D)参照。)。本発明において、平坦化のために設ける層間絶縁膜としては、耐熱性および絶縁性が高く、且つ、平坦化率の高いものが要求されている。こうした絶縁層の形成方法としては、スピンドル法で代表される塗布法を用いると好ましい。

【0102】

本実施の形態では、絶縁層412の材料としては、シロキサン樹脂を用いる。なお、シロキサン樹脂とは、Si-O-Si結合を含む樹脂に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

30

【0103】

絶縁層412は、ディップ、スプレー塗布、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー、CVD法、蒸着法等を採用することができる。液滴吐出法により絶縁層109を形成してもよい。液滴吐出法を用いた場合には材料液を節約することができる。また、液滴吐出法のようにパターンが転写、または描写できる方法、例えば印刷法(スクリーン印刷やオフセット印刷などパターンが形成される方法)なども用いることができる。スピンドル、また、無機材料を用いてもよく、その際には、酸化珪素、窒化珪素、酸窒化珪素、を用いることができる。

40

【0104】

絶縁層412は、シロキサン樹脂の他に、耐熱性が高く、平坦化性がよいものであれば、無機材料(酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素PSG(リンガラス)、BPSG(リンボロンガラス)、アルミナ膜など)、感光性または非感光性の有機材料(有機樹脂材料)(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジスト、ベンゾシクロブテンなど)、低誘電率であるLow-k材料などの一種、もしくは複数種からなる膜、またはこれらの膜の積層などを用いることができる。

50

## 【0105】

次いで、レジストからなるマスクを用いて絶縁層412、絶縁層411に半導体層に達するコンタクトホール（開口部）を形成する。

## 【0106】

導電膜を形成し、導電膜をエッチングして各ソース領域又はドレイン領域である不純物領域の一部とそれぞれ電気的に接続するソース電極層又はドレイン電極層として機能する配線層413a、配線層413b、配線層414a、配線層414b、配線層415a、配線層415b、配線層415cを形成する。配線層413a、配線層413b、配線層414a、配線層414b、配線層415a、配線層415b、配線層415cは、PVD法、CVD法、蒸着法等により導電膜を成膜した後、所望の形状にエッチングして形成することができる。また、液滴吐出法、印刷法、電界メッキ法等により、所定の場所に選択的に導電層を形成することができる。更にはリフロー法、ダマシン法を用いても良い。配線層413a、配線層413b、配線層414a、配線層414b、配線層415a、配線層415b、配線層415cの材料は、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Si、Ge、Zr、Ba等の金属又はその合金、若しくはその金属窒化物を用いて形成する。また、これらの積層構造としても良い。本実施の形態では、Ti、Al、Tiを積層したのち、所望の形状にパターニングして、配線層413a、配線層413b、配線層414a、配線層414b、配線層415a、配線層415b、配線層415cを形成する。また、配線層414a、配線層414bは、記憶素子を構成する第1の導電層としても機能する。

10

20

## 【0107】

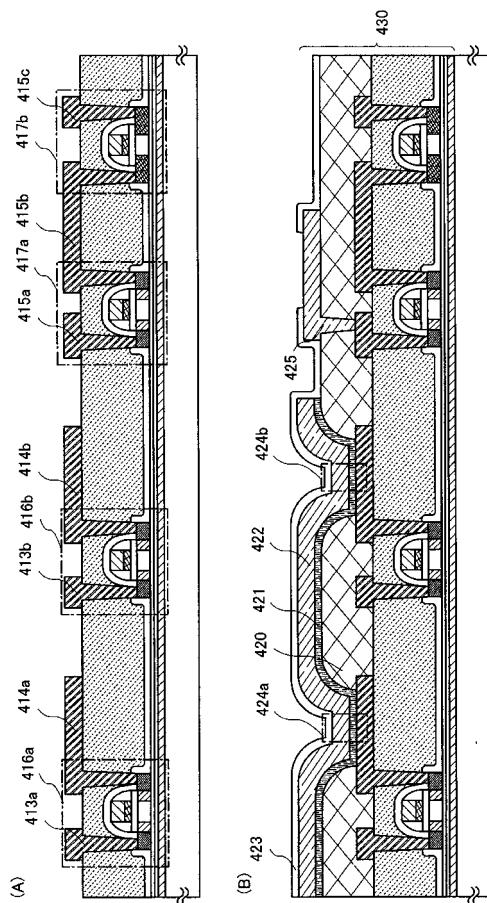

上記工程を経て、後に記憶素子に接続するn型の薄膜トランジスタ416a及びn型の薄膜トランジスタ416b、後にアンテナとして機能する導電層と接続するCMOS構造のn型の薄膜トランジスタ417a及びp型の薄膜トランジスタ417bが完成する（図10（A）参照。）。

## 【0108】

本実施の形態に限定されず、薄膜トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、二つ形成されるダブルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。また、周辺駆動回路領域の薄膜トランジスタも、シングルゲート構造、ダブルゲート構造もしくはトリプルゲート構造であっても良い。またソース、ドレイン領域の一方または両方にシリサイド層を形成してもよい。シリサイド層の材料としては、ニッケル、タングステン、モリブデン、コバルト、白金等を用いることができる。

30

## 【0109】

なお、本実施の形態で示した薄膜トランジスタの作製方法に限らず、トップゲート型（プレーナー型、順スタガ型）、ボトムゲート型（逆スタガ型）、あるいはチャネル領域の上下にゲート絶縁膜を介して配置された2つのゲート電極層を有する、デュアルゲート型やその他の構造においても適用できる。

## 【0110】

配線層414a、配線層414b、配線層415aの一部に開口部を有して絶縁層（隔壁、土手とも呼ばれる）420を形成する。絶縁層420としては、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド（polyimide）、芳香族ポリアミド、ポリベンゾイミダゾール（polybenzimidazole）などの耐熱性高分子、又は珪素、酸素、水素からなる化合物のうちSi-O-Si結合を含む無機シリコサン、珪素に結合されている水素がメチルやフェニルのような有機基に置換された有機シリコサンの絶縁材料で形成することができる。また、ポリビニルアルコール、ポリビニルブチラールなどのビニル樹脂、エポキシ樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、ポリイミドなどの有機材料、シリコサンポリマー等の重合によ

40

50

つてできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いてもよい。作製法としては、プラズマCVD法や熱CVD法などの気相成長法やスパッタリング法を用いることができる。また、液滴吐出法や、印刷法（スクリーン印刷やオフセット印刷などパターンが形成される方法）を用いることもできる。塗布法で得られるTOF膜やSOG膜なども用いることができる。

#### 【0111】

また、液滴吐出法により、導電層、絶縁層などを、組成物を吐出し形成した後、その平坦性を高めるために表面を圧力によってプレスして平坦化してもよい。プレスの方法としては、ローラー状のものを表面に走査することによって、凹凸をならすように軽減したり、平坦な板状な物で表面を垂直にプレスしたりしてもよい。プレスする時に、加熱工程を行っても良い。また溶剤等によって表面を軟化、または融解させエアナイフで表面の凹凸部を除去しても良い。また、CMP法を用いて研磨しても良い。この工程は、液滴吐出法によって凹凸が生じる場合に、その表面の平坦化する場合適用することができる。

10

#### 【0112】

配線層414a、配線層414b上に絶縁層421、導電層422が積層される。また、配線層415a上にも導電層422と同工程で配線層425が形成される。

#### 【0113】

絶縁層421は、有機絶縁物、電気的作用または光学的作用により導電性が変化する有機化合物、無機絶縁物、又は有機化合物と無機化合物とが混合してなる層で形成する。絶縁層421は、単層で設けてもよいし、複数の層を積層させて設けてもよい。また、有機化合物と無機化合物との混合層及び他の電気的作用または光学的作用により導電性が変化する有機化合物からなる層とを積層させて設けてもよい。

20

#### 【0114】

絶縁層421を構成することが可能な無機絶縁物としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素等を用いることができる。

#### 【0115】

絶縁層421を構成することが可能な有機絶縁物としては、ポリイミド、アクリル、ポリアミド、ベンゾシクロブテン、エポキシ等に代表される有機樹脂を用いることができる。

#### 【0116】

30

また、絶縁層421を構成することが可能な、電気的作用または光学的作用により導電性が変化する有機化合物としては、正孔輸送性が高い有機化合物材料又は電子輸送性が高い有機化合物材料を用いることができる。

#### 【0117】

正孔輸送性の高い有機化合物材料としては、4,4'-ビス[N-(1-ナフチル)-N-フェニル-アミノ]-ビフェニル（略称：-NPD）や4,4'-ビス[N-(3-メチルフェニル)-N-フェニル-アミノ]-ビフェニル（略称：TPD）や4,4',4'''-トリス(N,N-ジフェニル-アミノ)-トリフェニルアミン（略称：TDA-TA）、4,4',4'''-トリス[N-(3-メチルフェニル)-N-フェニル-アミノ]-トリフェニルアミン（略称：MTDATA）や4,4'-ビス(N-(4-(N,N-ジ-m-トリルアミノ)フェニル)-N-フェニルアミノ)ビフェニル（略称：DNTPD）などの芳香族アミン系（即ち、ベンゼン環-窒素の結合を有する）の化合物やフタロシアニン（略称：H<sub>2</sub>Pc）、銅フタロシアニン（略称：CuPc）、バナジルフタロシアニン（略称：VOPc）等のフタロシアニン化合物を用いることができる。ここに述べた物質は、主に10<sup>-6</sup> cm<sup>2</sup>/Vs以上の正孔移動度を有する物質である。但し、電子よりも正孔の輸送性が高い物質であれば、上記の物質以外のものを用いてもよい。

40

#### 【0118】

なお、有機化合物と無機化合物との混合層を設ける場合には、正孔輸送性の高い有機化合物材料と電子を受け取りやすい無機化合物材料とを混合させることができが好ましい。このような構成とすることによって、本来内在的なキャリアをほとんど有さない有機化合物に多く

50

のホールキャリアが発生し、極めて優れたホール注入性・輸送性を示す。その結果、有機化合物層は優れた導電性を得ることが可能となる。

#### 【0119】

電子を受け取りやすい無機化合物材料として、周期表第4族乃至第12族のいずれかの遷移金属の金属酸化物、金属窒化物または金属酸化窒化物を用いることができる。具体的には、チタン酸化物( $TiO_x$ )、ジルコニウム酸化物( $ZrO_x$ )、バナジウム酸化物( $VO_x$ )、モリブデン酸化物( $MoO_x$ )、タンクス滕酸化物( $WO_x$ )、タンタル酸化物( $TaO_x$ )、ハフニウム酸化物( $HfO_x$ )、ニオブ酸化物( $NbO_x$ )、コバルト酸化物( $Co_x$ )、レニウム酸化物( $ReO_x$ )、ルテニウム酸化物( $RuO_x$ )、亜鉛酸化物( $ZnO$ )、ニッケル酸化物( $NiO_x$ )、銅酸化物( $CuO_x$ )等を用いることができる。また、ここでは具体例として酸化物を例に挙げたが、もちろんこれらの窒化物や酸化窒化物を用いてもよい。

#### 【0120】

電子輸送性の高い有機化合物材料としては、トリス(8-キノリノラト)アルミニウム(略称:  $Alq_3$ )、トリス(4-メチル-8-キノリノラト)アルミニウム(略称:  $Almq_3$ )、ビス(10-ヒドロキシベンゾ[ $h$ ]-キノリナト)ベリリウム(略称:  $BeBq_2$ )、ビス(2-メチル-8-キノリノラト)-4-フェニルフェノラト-アルミニウム(略称:  $BAlq$ )等キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる材料を用いることができる。また、この他、ビス[2-(2-ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称:  $Zn(BOX)_2$ )、ビス[2-(2-ヒドロキシフェニル)ベンゾチアゾラト]亜鉛(略称:  $Zn(BTZ)_2$ )などのオキサゾール系、チアゾール系配位子を有する金属錯体などの材料も用いることができる。さらに、金属錯体以外にも、2-(4-ビフェニリル)-5-(4-tert-ブチルフェニル)-1,3,4-オキサジアゾール(略称:  $PBD$ )、1,3-ビス[5-(p-tert-ブチルフェニル)-1,3,4-オキサジアゾール-2-イル]ベンゼン(略称:  $OXD-7$ )、3-(4-tert-ブチルフェニル)-4-フェニル-5-(4-ビフェニリル)-1,2,4-トリアゾール(略称:  $TAZ$ )、3-(4-tert-ブチルフェニル)-4-(4-エチルフェニル)-5-(4-ビフェニリル)-1,2,4-トリアゾール(略称:  $p-EtTAZ$ )、バソフェナントロリン(略称:  $BPhen$ )、バソキュブロイン(略称:  $BCP$ )等を用いることができる。ここに述べた物質は、主に  $10^{-6} \text{ cm}^2/\text{Vs}$  以上の電子移動度を有する物質である。但し、正孔よりも電子の輸送性の高い物質であれば、上記の物質以外のものを用いてもよい。

#### 【0121】

なお、有機化合物と無機化合物との混合層を設ける場合には、電子輸送性の高い有機化合物材料と電子を与えやすい無機化合物材料とを混合させることが好ましい。このような構成とすることによって、本来内在的なキャリアをほとんど有さない有機化合物に多くの電子キャリアが発生し、極めて優れた電子注入性・輸送性を示す。その結果、有機化合物層は優れた導電性を得ることが可能となる。

#### 【0122】

電子を与えやすい無機化合物材料として、アルカリ金属酸化物、アルカリ土類金属酸化物、希土類金属酸化物、アルカリ金属窒化物、アルカリ土類金属窒化物、希土類金属窒化物を用いることができる。具体的には、リチウム酸化物( $LiO_x$ )、ストロンチウム酸化物( $SrO_x$ )、バリウム酸化物( $BaO_x$ )、エルビウム酸化物( $ErO_x$ )、ナトリウム酸化物( $NaO_x$ )、リチウム窒化物( $LiNx$ )、マグネシウム窒化物( $MgNx$ )、カルシウム窒化物( $CaNx$ )、イットリウム窒化物( $YNx$ )、ランタン窒化物( $LaNx$ )等を用いることができる。

#### 【0123】

さらには、無機化合物材料として、有機化合物から電子を受け取りやすい無機化合物材料または有機化合物に電子を与えやすい無機化合物材料であれば何でもよく、アルミニウム酸化物( $AlO_x$ )、ガリウム酸化物( $GaO_x$ )、ケイ素酸化物( $SiO_x$ )、ゲル

10

20

30

40

50

マニウム酸化物 (GeO<sub>x</sub>)、インジウム錫酸化物 (ITO) 等のほか、種々の金属酸化物、金属窒素化物または金属酸化窒化物を用いることができる。

#### 【0124】

また、絶縁層421が金属酸化物または金属窒化物の中から選ばれた化合物と正孔輸送性の高い化合物とから形成される場合、さらに立体障害の大きな(平面構造とは異なり空間的な広がりを有する構造をもつ)化合物を加えた構成としてもよい。立体障害の大きな化合物としては、5,6,11,12-テトラフェニルテトラセン(略称:ルブレン)が好ましい。但し、これ以外に、ヘキサフェニルベンゼン、t-ブチルペリレン、9,10-ジ(フェニル)アントラセン、クマリン545T等も用いることができる。この他、デンドリマー等も有効である。

10

#### 【0125】

さらには、電子輸送性の高い有機化合物材料で形成される層と、正孔輸送性の高い有機化合物材料層との間に、4-ジシアノメチレン-2-メチル-6-(1,1,7,7-テトラメチルジュロリジル-9-エニル)-4H-ピラン(略称:DCJT)、4-ジシアノメチレン-2-t-ブチル-6-(1,1,7,7-テトラメチルジュロリジル-9-エニル)-4H-ピラン、ペリフランテン、2,5-ジシアノ-1,4-ビス(10-メトキシ-1,1,7,7-テトラメチルジュロリジル-9-エニル)ベンゼン、N,N'-ジメチルキナクリドン(略称:DMQd)、クマリン6、クマリン545T、トリス(8-キノリノラト)アルミニウム(略称:Alq<sub>3</sub>)、9,9'-ビアントリル、9,10-ジフェニルアントラセン(略称:DPA)や9,10-ビス(2-ナフチル)アントラセン(略称:DNA)、2,5,8,11-テトラ-t-ブチルペリレン(略称:TCP)等の発光物質を設けてもよい。

20

#### 【0126】

また、絶縁層421には、光学的作用により、電気抵抗が変化する材料を用いることができる。例えば、光を吸収することによって酸を発生する化合物(光酸発生剤)をドープした共役高分子を用いることができる。共役高分子として、ポリアセチレン類、ポリフェニレンビニレン類、ポリチオフェン類、ポリアニリン類、ポリフェニレンエチニレン類等を用いることができる。また、光酸発生剤としては、アリールスルホニウム塩、アリールヨードニウム塩、o-ニトロベンジルトシレート、アリールスルホン酸p-ニトロベンジルエステル、スルホニルアセトフェノン類、Fe-アレン錯体PF<sub>6</sub>塩等を用いることができる。

30

#### 【0127】

絶縁層421は、蒸着法、電子ビーム蒸着法、スパッタリング法、CVD法等を用いて形成することができる。また、有機化合物と無機化合物とを含む混合層は、各々の材料を同時に成膜することにより形成することができ、抵抗加熱蒸着同士による共蒸着法、電子ビーム蒸着同士による共蒸着法、抵抗加熱蒸着と電子ビーム蒸着による共蒸着法、抵抗加熱蒸着とスパッタリングによる成膜、電子ビーム蒸着とスパッタリングによる成膜など、同種、異種の方法を組み合わせて形成することができる。他の形成方法として、スピンコート法、ゾル-ゲル法、印刷法または液滴吐出法等を用いてもよいし、上記方法とこれらを組み合わせて絶縁層421を形成してもよい。

40

#### 【0128】

なお、絶縁層421は、電気的作用又は光学的作用により記憶素子の導電性が変化する膜厚で形成する。

#### 【0129】

導電層422、配線層425は、配線層414a、配線層414bと同様な材料を用いることができ、同様な工程で形成できる。本実施の形態において、記憶素子へのデータの書き込みは電気的作用または光学的作用を加えることによって行うが、光学的作用によりデータの書き込みを行う場合、配線層414a及び配線層414b、または導電層422のうち、一方または両方は透光性を有するように設ける。透光性を有する導電層は、透明な導電性材料を用いて形成するか、または、透明な導電性材料でなくても光を透過する厚

50

さで形成する。透明な導電性材料としては、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZO)などその他の透光性酸化物導電材料を用いることが可能である。ITO及び酸化珪素を含む酸化インジウムスズ(以下、ITSOと記す)や、酸化珪素を含んだ酸化インジウムに、さらに2~20%の酸化亜鉛(ZnO)を混合したものを用いても良い。

#### 【0130】

記憶素子424aは配線層414a上に、絶縁層421及び導電層422が積層して構成され、記憶素子424bは、配線層414b上に、絶縁層421及び導電層422が積層して設けられている。また、導電層422を覆って保護膜として機能する絶縁層423が形成されている(図10(B)参照。)。また、記憶素子424a、記憶素子424bが形成される配線層414a、配線層414bは、薄膜トランジスタ416a、薄膜トランジスタ416bそれぞれのソース領域又はドレイン領域に、接続されている。すなわち、記憶素子はそれぞれひとつの薄膜トランジスタに接続されている。また、絶縁層421が配線層414a、配線層414b及び絶縁層420を覆うように全面に形成されているが、各記憶素子に選択的に形成されていてもよい。

#### 【0131】

配線層414a、配線層414b、導電層422の材料には導電性の高い元素や化合物等用いる。本実施の形態で絶縁層421の材料には電気的作用や光学的作用により、結晶状態や導電性、形状が変化する物質を用いる。上記構成を有する記憶素子は電圧印加前後で導電性が変化するので、「初期状態」と「導電性変化後」とに対応した2つの値を記憶させることができる。

#### 【0132】

絶縁層423は、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又は珪素、酸素、水素からなる化合物のうちSi-O-Si結合を含む無機シロキサン、珪素に結合されている水素がメチルやフェニルのような有機基に置換された有機シロキサンの絶縁材料で形成することができる。また、ポリビニルアルコール、ポリビニルブチラールなどのビニル樹脂、エポキシ樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いる。また、ベンゾシクロブテン、パリレン、フレア、ポリイミドなどの有機材料、シロキサンポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いてもよい。作製法としては、プラズマCVD法や熱CVD法などの気相成長法やスパッタリング法を用いることができる。また、液滴吐出法や、印刷法(クリーン印刷やオフセット印刷などパターンが形成される方法)を用いることができる。塗布法で得られるTOF膜やSOG膜なども用いることができる。また、炭素膜、 DLC膜を用いてもよい。DLC膜は室温から100以下の温度範囲で成膜可能であるため、絶縁層421が耐熱性の低い材料であっても上方に容易に成膜することができる。DLC膜は、プラズマCVD法(代表的には、RFプラズマCVD法、マイクロ波CVD法、電子サイクロトロン共鳴(ECR)CVD法、熱フィラメントCVD法など)、燃焼炎法、スパッタ法、イオンビーム蒸着法、レーザ蒸着法などで形成することができる。成膜に用いる反応ガスは、水素ガスと、炭化水素系のガス(例えばCH<sub>4</sub>、C<sub>2</sub>H<sub>2</sub>、C<sub>6</sub>H<sub>6</sub>など)とを用い、グロー放電によりイオン化し、負の自己バイアスがかかったカソードにイオンを加速衝突させて成膜する。また、CN膜は反応ガスとしてC<sub>2</sub>H<sub>4</sub>ガスとN<sub>2</sub>ガスとを用いて形成すればよい。DLC膜は酸素に対するブロッキング効果が高い。

#### 【0133】

また、本実施の形態では、上記構成において、配線層414a、配線層414bと、絶縁層421との間に、整流性を有する素子を設けてもよい。整流性を有する素子とは、ゲート電極とドレイン電極を接続したトランジスタ、またはダイオードである。このように

10

20

30

40

50

、整流性があるダイオードを設けることにより、1つの方向にしか電流が流れないために、誤差が減少し、読み出しまージンが向上する。なお、整流性を有する素子は、絶縁層421と導電層422との間に設けてよい。

【0134】

以上の工程によって、基板400上に薄膜回路部430が形成される。

【0135】

次に、剥離層401が露出するように、フォトリソグラフィ法により絶縁層をエッチングして、開口部426a、開口部426bを形成する(図11(A))。

【0136】

次に、開口部426a、開口部426bにエッチング剤を導入して、剥離層401を除去する(図11(B))。エッチング剤は、フッ化ハロゲン又はハロゲン間化合物を含む気体又は液体を使用する。例えば、フッ化ハロゲンを含む気体として三フッ化塩素(C1F3)を使用する。そうすると、薄膜回路部430は、基板400から剥離された状態となる。なお、剥離層401は、全て除去せず一部分を残存させておいてよい。こうすることによって、処理時間を短縮することが可能となる。

【0137】

薄膜回路部430が剥離された基板400は、コストの削減のために、再利用するとよい。実施の形態1で示したように、薄膜回路部430の一方の面を、転写用基板445に接着させて、基板400から完全に剥離し、薄膜回路部430の配線層425が露出していない絶縁層402aの面に第1の基板427を接着する。(図11(B)、図12(A)参照。)。

【0138】

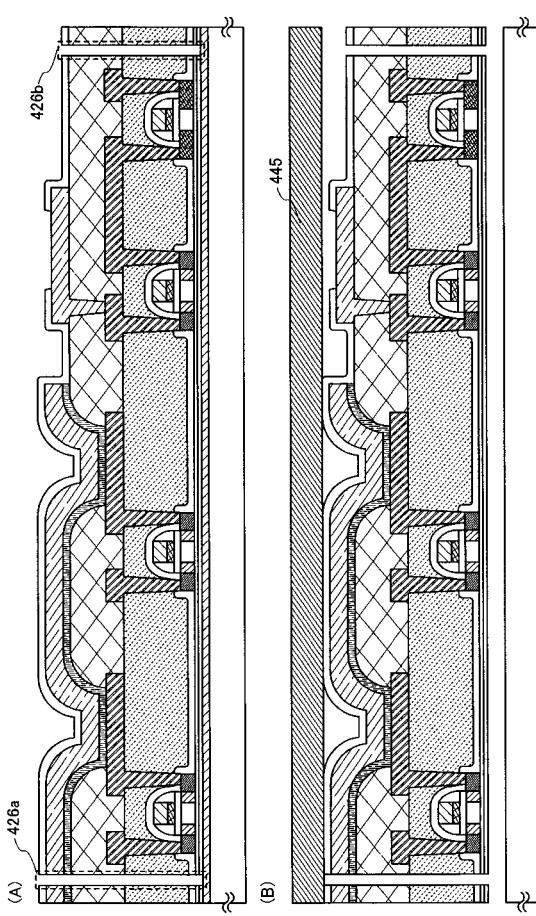

次に、絶縁層428を印刷法によって形成する。各種印刷法(スクリーン(孔版)印刷、オフセット(平版)印刷、凸版印刷やグラビア(凹版)印刷などを用いることができる。本実施の形態ではスクリーン印刷法を用いる。金網(メッシュ)431及びマスク用の乳剤442が枠に設けられたスクリーン印刷版を絶縁層423上に設ける。次に、スクリーン印刷版上に組成物(ペースト)432を設け、スキージ433やローラー等を用いて組成物(ペースト)438を押し出す。この結果、絶縁層423上に組成物(ペースト)を塗布印刷することができる。なお、スキージやローラーでペーストを押し出す前に、スクレッパでペーストをスクリーン印刷版上に広げてもよい。印刷塗布された組成物(ペースト)を乾燥・焼成することで、開口部429を有する絶縁層428を形成することができる(図12(B)参照。)。

【0139】

次に、アンテナとして機能する導電層435を印刷法によって形成する。本実施の形態では、導電層435を形成する前に、導電層435の被形成領域の組成物に対するぬれ性を制御する前処理を行う。ぬれ性の程度は、形成する導電層の線幅やパターン形状、膜厚によって適宜設定すればよく、以下に示す処理によってぬれ性を制御することができる。

【0140】

固体表面のぬれ性は、表面の状態に影響をうける。液状の組成物に対して、ぬれ性が低い物質を形成するとその表面は液状の組成物に対してぬれ性の低い領域(以下、低ぬれ性領域ともいう)となり、逆に液状の組成物に対して、ぬれ性の高い物質を形成するとその表面は、液状の組成物に対してぬれ性の高い領域(以下、高ぬれ性領域ともいう)となる。本発明において表面のぬれ性を制御するという処理は、液状の組成物の付着領域を、液状の組成物に対して所望の形状の形成物を形成するのに適した状態とすることである。

【0141】

ぬれ性の程度は接触角の値にも影響する。液状の組成物の接触角が大きい領域はよりぬれ性が低い領域(以下、低ぬれ性領域ともいう)となり、接触角が小さい領域はぬれ性の高い領域(以下、高ぬれ性領域ともいう)となる。接触角が大きいと、流動性を有する液状の組成物は、領域表面上で広がらず、組成物をはじくので、表面をぬらさないが、接

10

20

30

40

50

触角が小さいと、表面上で流動性を有する組成物は広がり、よく表面をぬらすからである。よって、ぬれ性が異なる領域は、表面エネルギーも異なる。ぬれ性が低い領域における表面の、表面エネルギーは小さく、ぬれ性の高い領域表面における表面エネルギーは大きい。

#### 【0142】

まず、ぬれ性制御物質を形成し、被形成領域表面のぬれ性を低めるように制御する方法を示す。このようなぬれ性制御物質として、フッ化炭素基（フッ化炭素鎖）を含む物質、あるいはシランカップリング剤を含む物質を用いることができる。シランカップリング剤は、 $R_n - Si - X_{(4-n)}$  ( $n = 1, 2, 3$ ) の化学式で表される。ここで、Rは、アルキル基などの比較的不活性な基を含む物である。また、Xはハロゲン、メトキシ基、エトキシ基又はアセトキシ基など、基質表面の水酸基あるいは吸着水との縮合により結合可能な加水分解基からなる。

#### 【0143】

また、シランカップリング剤の代表例として、Rにフルオロアルキル基を有するフッ素系シランカップリング剤（フルオロアルキルシラン（FAS））を用いることにより、よりぬれ性を低めることができる。FASのRは、 $(CF_3)(CF_2)_x(CH_2)_y$  ( $x : 0$  以上  $10$  以下の整数、 $y : 0$  以上  $4$  以下の整数) で表される構造を持ち、複数個のR又はXがSiに結合している場合には、R又はXはそれぞれすべて同じでも良いし、異なっていてもよい。代表的なFASとしては、ヘプタデカフルオロテトラヒドロデシルトリエトキシシラン、ヘプタデカフルオロテトラヒドロデシルトリクロロシラン、トリデカフルオロテトラヒドロオクチルトリクロロシラン、トリフルオロプロピルトリメトキシシラン等のフルオロアルキルシラン（以下、FASともいう。）が挙げられる。

#### 【0144】

ぬれ性制御物質として、シランカップリング剤のRにフッ化炭素鎖を有さず、アルキル基を有す物質も用いることができ、例えば有機シランとしてオクタデシルトリメトキシシラン等を用いることができる。

#### 【0145】

ぬれ性制御物質を含む溶液の溶媒としては、n-ペンタン、n-ヘキサン、n-ヘプタン、n-オクタン、n-デカン、ジシクロヘキサン、ベンゼン、トルエン、キシレン、デュレン、インデン、テトラヒドロナフタレン、デカヒドロナフタレン、スクワランなどの炭化水素系溶媒又はテトラヒドロフランなどを用いる。

#### 【0146】

また、低ぬれ性領域を形成するぬれ性制御物質の一例として、フッ化炭素（フルオロカーボン）鎖を有する材料（フッ素系樹脂）を用いることができる。フッ素系樹脂として、ポリテトラフルオロエチレン（PTFE；四フッ化エチレン樹脂）、パーフルオロアルコキシアルカン（PFA；四フッ化エチレンパーフルオロアルキルビニルエーテル共重合樹脂）、パーフルオロエチレンプロパンコーポリマー（PFE；四フッ化エチレン-六フッ化プロピレン共重合樹脂）、エチレン-テトラフルオロエチレンコポリマー（ETFE；四フッ化エチレン-エチレン共重合樹脂）、ポリビニリデンフルオライド（PVDF；フッ化ビニリデン樹脂）、ポリクロロトリフルオロエチレン（PCFE；三フッ化塩化エチレン樹脂）、エチレン-クロロトリフルオロエチレンコポリマー（ECTFE；三フッ化塩化エチレン-エチレン共重合樹脂）、ポリテトラフルオロエチレン-パーフルオロジオキソールコポリマー（TFE/PDD）、ポリビニルフルオライド（PVF；フッ化ビニル樹脂）等を用いることができる。

#### 【0147】

また、無機材料、有機材料に $CF_4$ プラズマ等による処理を行うと、ぬれ性を低めることができる。例えば、有機材料としてポリビニルアルコール（PVA）のような水溶性樹脂を、 $H_2O$ 等の溶媒に混合した材料を用いることができる。また、PVAと他の水溶性樹脂を組み合わせて使用してもよい。有機材料（有機樹脂材料）（ポリイミド、アクリル）やシリコン（Si）と酸素（O）との結合で骨格構造が構成され、置換基に少なくとも

10

20

30

40

50

水素を含む材料、もしくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いてもよい。

【0148】

本実施の形態では、ぬれ性制御物質434としてFASをスピンドルコート法により絶縁層428及び配線層425上に形成し、導電層被形成領域のぬれ性を調整する。このぬれ性は後工程で形成する導電層を構成する液状の導電性材料を含む組成物に対してである。また、ぬれ性制御物質434として、FAS試薬を含む密閉容器に基板を封入し、50度～200度、好ましくは100～200度で5分以上加熱して、FASを絶縁層428及び配線層425表面に吸着させて形成することもできる。ぬれ性制御物質434は、その形成方法により膜として連続して形成されない場合もある。また、ぬれ性制御物質434は導電層435の被形成領域及びその近傍に選択的に形成してもよい。導電層435を所望なパターンに形成後、残存するぬれ性制御物質を残してもよいし、不必要的部分は除去してしまってもよい。除去は、酸素等によるアッシング、エッチングなどにより除去すればよい。

【0149】

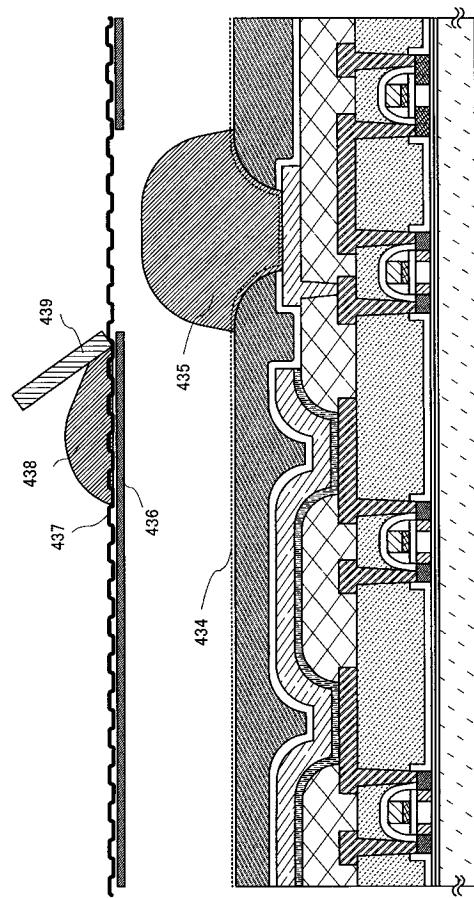

ぬれ性制御物質434によって、ぬれ性の制御された領域に、印刷法を用いて導電層435を形成する。各種印刷法（スクリーン（孔版）印刷、オフセット（平版）印刷、凸版印刷やグラビア（凹版）印刷、又は液滴吐出法などを用いることができる。本実施の形態ではスクリーン印刷法を用いる。絶縁層428同様、金網（メッシュ）437及びマスク用の乳剤436が枠に設けられたスクリーン印刷版を絶縁層428及び配線層425上に設ける。次に、スクリーン印刷版上に組成物（ペースト）438を設け、スキージ439やローラー等を用いて組成物（ペースト）438を、開口部429へ押し出す。この結果、配線層425上に組成物（ペースト）を塗布印刷することができる。なお、スキージやローラーでペーストを押し出す前に、スクレッパーでペーストをスクリーン印刷版上に広げてもよい。印刷塗布された組成物（ペースト）を乾燥・焼成することで、導電層435を形成することができる（図13参照。）。以上のぬれ性の制御は、本明細書中の印刷法や液滴吐出法で導電層、絶縁層を形成する場合、用いることができる。

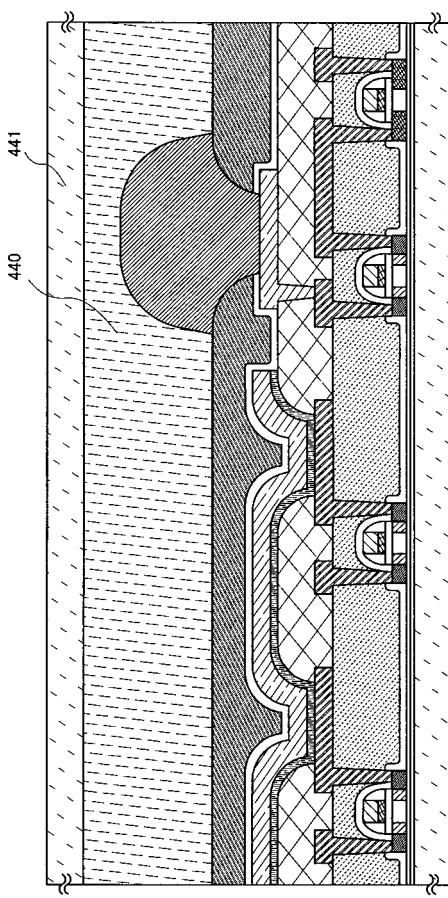

【0150】

導電層435及び薄膜回路部330を覆うように絶縁層440を形成し、可撓性を有する基板441で封止し半導体装置を作製する（図14参照。）。本実施の形態では、絶縁層440を導電層435と同様にスクリーン印刷法によって形成する。

【0151】

以上のように、本発明により高性能、高信頼性の半導体装置を低成本で、歩留まりよく作製することができる。

【0152】

（実施の形態3）

本実施の形態では、実施の形態2で示す記憶装置を有する半導体装置の他の例に関して図面を用いて説明する。

【0153】

本実施の形態で示す半導体装置は、非接触でデータの読み出しと書き込みが可能であることを特徴としており、データの伝送形式は、一対のコイルを対向に配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別されるが、いずれの方式を用いてもよい。

【0154】

次に、パッシブマトリクス型の記憶装置を有する半導体装置の一構成例に関して図15を用いて説明する。

【0155】

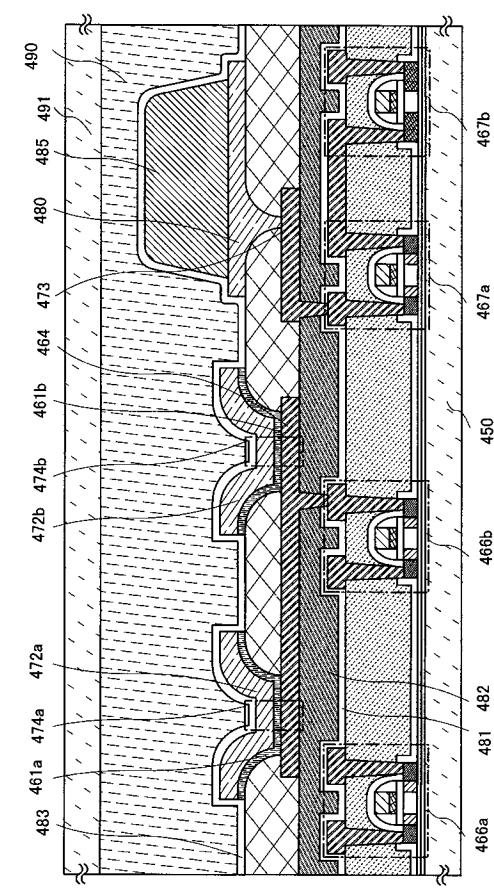

図15はパッシブマトリクス型の記憶装置を有する半導体装置を示しており、基板450上にトランジスタ466a、トランジスタ466b、トランジスタ467a、トランジスタ467bが設けられ、絶縁層481、絶縁層482を介してトランジスタの上方に記

10

20

30

40

50

憶素子 474a、記憶素子 474b が設けられ、トランジスタ 467a 及びトランジスタ 467b と接続する配線層 473、配線層 480 上にアンテナとして機能する導電層 485 が設けられている。

【0156】

記憶素子 474a はトランジスタ 466b と接続する第 1 の導電層 464 上に、絶縁層 461a 及び第 2 の導電層 472a が積層して構成され、記憶素子 474b は、第 1 の導電層 464 上に、絶縁層 461b 及び第 2 の導電層 472b が積層して設けられている。また、第 2 の導電層 472a、472b、導電層 485 を覆って保護膜として機能する絶縁層 483 が形成され、絶縁層 483 上に絶縁層 490 を設けて基板 491 によって封止されている。また、複数の記憶素子 474a、474b が形成される第 1 の導電層 464 は、トランジスタ 466b ひとつのソース電極層又はドレイン電極層に、接続されている。すなわち、記憶素子は同じひとつのトランジスタに接続されている。また、絶縁層 461a、絶縁層 461b は記憶素子ごとに絶縁層を分離するための隔壁となる絶縁層を設けているが、隣接する記憶素子において横方向への電界の影響が懸念されない場合は、全面に形成してもよい。なお、記憶素子 474a、474b は上記実施の形態で示した材料または作製方法を用いて形成することができる。

【0157】

次に、アンテナとして機能する導電層を薄膜回路部下方に設けるアクティブマトリクス型の記憶装置を有する半導体装置の一構成例に関して図 16 を用いて説明する。

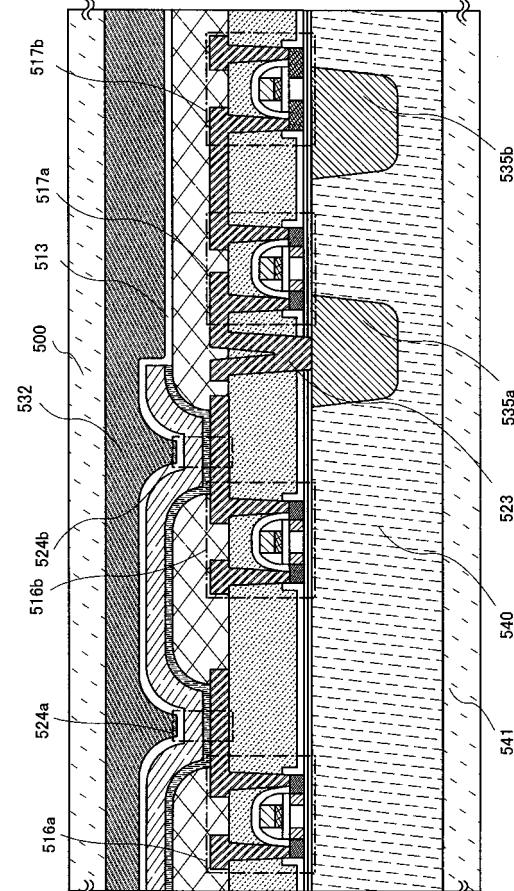

【0158】

図 16 はアクティブマトリクス型の記憶装置を有する半導体装置を示しており、基板 541 上にトランジスタ 516a、トランジスタ 516b、トランジスタ 517a、トランジスタ 517b が設けられ、トランジスタの上方に記憶素子 524a、記憶素子 524b が設けられている。トランジスタ 517a 及びトランジスタ 517b と接続する配線層 523 は、絶縁層に設けられたコンタクトホールに形成され、トランジスタ 517a 及びトランジスタ 517b 下方に設けられたアンテナとして機能する導電層 485 と電気的に接続する。また導電層 535b もアンテナとして機能する。一方は、記憶素子 524a、記憶素子 524b を覆って保護膜として機能する絶縁層 513 が形成され、絶縁層 513 上に絶縁層 532 を設けて基板 500 によって封止され、他方は導電層 535a、導電層 535b を覆って絶縁層 540 が形成され、基板 541 で封止されている。

【0159】

アクティブマトリクス型であるので、実施の形態 2 で示した半導体装置と同様に、記憶素子はそれぞれひとつのトランジスタに接続されている。なお、記憶素子 524a、524b は上記実施の形態で示した材料または作製方法を用いて形成することができる。

【0160】

このように、記憶装置およびアンテナを備えた半導体装置を形成することができる。また、本実施の形態では、基板上に薄膜トランジスタを形成して素子形成層を設けることができるし、基板として Si 等の半導体基板を用いて、基板上に電界効果トランジスタを形成することによって素子形成層を設けてもよい。また、基板として SOI 基板を用いて、その上に素子形成層を設けてもよい。この場合、SOI 基板はウェハの貼り合わせによる方法や酸素イオンを Si 基板内に打ち込むことにより内部に絶縁層を形成する SIMOX と呼ばれる方法を用いて形成すればよい。またトランジスタに接続するセンサを設けてもよい。

【0161】

また、薄膜回路部は蒸着、スパッタ法、CVD 法、印刷法または液滴吐出法等を用いて形成することができる。なお、各場所によって異なる方法を用いて形成してもかまわない。例えば、高速動作が必要とされるトランジスタは基板上に Si 等からなる半導体層を形成した後に熱処理により結晶化させて設け、その後、素子形成層の上方にスイッチング素子として機能するトランジスタを印刷法や液滴吐出法を用いて有機トランジスタとして設けることができる。

10

20

30

40

50

## 【0162】

なお、トランジスタに接続するセンサを設けてもよい。センサとしては、温度、湿度、照度、ガス（気体）、重力、圧力、音（振動）、加速度、その他の特性を物理的又は化学的手段により検出する素子が挙げられる。センサは、代表的には抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換素子、熱起電力素子、トランジスタ、サーミスタ、ダイオードなどの半導体素子で形成される。

## 【0163】

なお、本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。また本実施の形態で示した、基板450、基板491、基板500、基板541は、可撓性を有する基板を用いており、可撓性を有する基板上に接着し、設置することで、可撓性を有する半導体装置を得ることができる。可撓性を有する基板とは、ポリプロピレン、ポリエチル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、纖維質な材料からなる紙、基材フィルム（ポリエチル、ポリアミド、無機蒸着フィルム、紙類等）と接着性合成樹脂フィルム（アクリル系合成樹脂、エポキシ系合成樹脂等）との積層フィルムなどに相当する。フィルムは、熱圧着により、被処理体と加熱処理と加圧処理が行われるものであり、加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、又は最外層に設けられた層（接着層ではない）を加熱処理によって溶かし、加圧により接着する。また、基板に接着層が設けられていてもよいし、接着層が設けられていてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。

10

## 【0164】

以上のように、本発明により高性能、高信頼性の半導体装置を低成本で、歩留まりよく作製することができる

## 【0165】

## （実施の形態4）

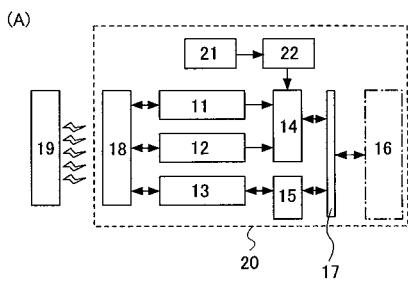

本実施形態の半導体装置の構成について、図17を参照して説明する。図17に示すように、本発明の半導体装置20は、非接触でデータを交信する機能を有し、電源回路11、クロック発生回路12、データ復調/変調回路13、他の回路を制御する制御回路14、インターフェース回路15、記憶回路16、データバス17、アンテナ（アンテナコイル）18、センサ21、センサ回路22を有する。

30

## 【0166】

電源回路11は、アンテナ18から入力された交流信号を基に、半導体装置20の内部の各回路に供給する各種電源を生成する回路である。クロック発生回路12は、アンテナ18から入力された交流信号を基に、半導体装置20の内部の各回路に供給する各種クロック信号を生成する回路である。データ復調/変調回路13は、リーダライタ19と交信するデータを復調/変調する機能を有する。制御回路14は、記憶回路16を制御する機能を有する。アンテナ18は、電磁界或いは電波の送受信を行う機能を有する。リーダライタ19は、半導体装置との交信、制御及びそのデータに関する処理を制御する。なお、半導体装置は上記構成に制約されず、例えば、電源電圧のリミッタ回路や暗号処理専用ハードウェアといった他の要素を追加した構成であってもよい。

40

## 【0167】

記憶回路16は、一対の導電層間に絶縁層又は相変化層が挟まれた記憶素子を有することを特徴とする。なお、記憶回路16は、一対の導電層間に絶縁層又は相変化層が挟まれた記憶素子のみを有していてもよいし、他の構成の記憶回路を有していてもよい。他の構成の記憶回路とは、例えば、DRAM、SRAM、FRAM、マスクROM、PROM、EPROM、EEPROM及びフラッシュメモリから選択される1つ又は複数に相当する。

## 【0168】

センサ21は抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換素子、熱起電力素子、トランジスタ、サーミスタ、ダイオードなどの半導体素子で形成される。

50

センサ回路 22 はインピーダンス、リアクタンス、インダクタンス、電圧又は電流の変化を検出し、アナログ / デジタル変換 (A / D 変換) して制御回路 14 に信号を出力する。

【 0169 】

( 実施の形態 5 )

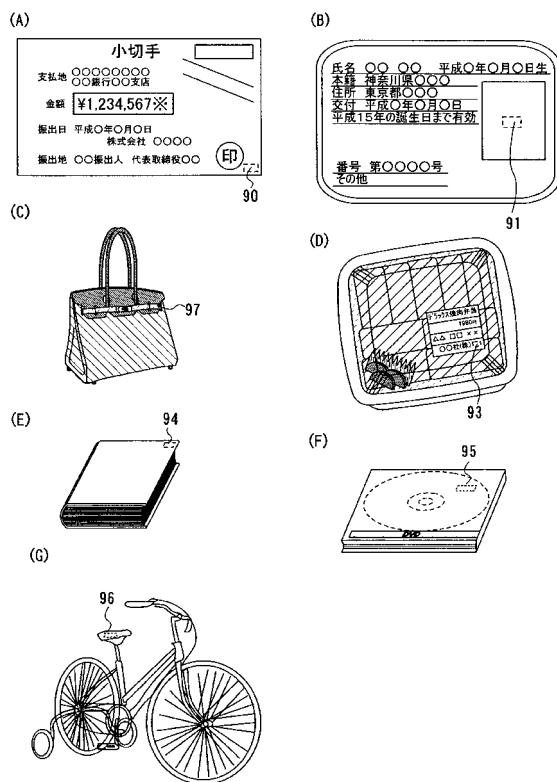

本発明によりプロセッサチップ ( 無線チップ、無線プロセッサ、無線メモリ、無線タグともよぶ ) として機能する半導体装置を形成することができる。本発明の半導体装置の用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。

【 0170 】

紙幣、硬貨とは、市場に流通する金銭であり、特定の地域で貨幣と同じように通用するもの ( 金券 ) 、記念コイン等を含む。有価証券類とは、小切手、証券、約束手形等を指し、プロセッサチップ 90 を設けることができる ( 図 18 ( A ) 参照 ) 。証書類とは、運転免許証、住民票等を指し、プロセッサチップ 91 を設けることができる ( 図 18 ( B ) 参照 ) 。乗物類とは、自転車等の車両、船舶等を指し、プロセッサチップ 97 を設けることができる ( 図 18 ( C ) 参照 ) 。無記名債券類とは、切手、おこめ券、各種ギフト券等を指す。包装用容器類とは、お弁当等の包装紙、ペットボトル等を指し、プロセッサチップ 93 を設けることができる ( 図 18 ( D ) 参照 ) 。書籍類とは、書物、本等を指し、プロセッサチップ 94 を設けることができる ( 図 18 ( E ) 参照 ) 。記録媒体とは、DVD ソフト、ビデオテープ等を指し、プロセッサチップ 95 を設けることができる ( 図 18 ( F ) 参照 ) 。身の回り品とは、鞄、眼鏡等を指し、プロセッサチップ 96 を設けることができる ( 図 18 ( G ) 参照 ) 。食品類とは、食料品、飲料等を指す。衣類とは、衣服、履物等を指す。保健用品類とは、医療器具、健康器具等を指す。生活用品類とは、家具、照明器具等を指す。薬品類とは、医薬品、農薬等を指す。電子機器とは、液晶表示装置、EL 表示装置、テレビジョン装置 ( テレビ受像機、薄型テレビ受像機 ) 、携帯電話等を指す。

【 0171 】

本発明の半導体装置は、プリント基板に実装したり、表面に貼ったり、埋め込んだりして、物品に固定される。例えば、本なら紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりして、各物品に固定される。本発明の半導体装置は、小型、薄型、軽量を実現するため、物品に固定した後も、その物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等に本発明の半導体装置を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に本発明の半導体装置を設けることにより、検品システム等のシステムの効率化を図ることができる。

【 0172 】

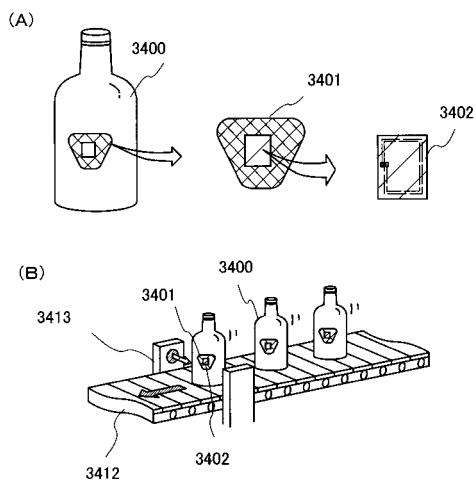

また、物の管理や流通のシステムに応用することが可能な例を、図 21 を用いて説明する。ここでは、商品へプロセッサチップを実装する例を説明する。図 21 ( A ) に示すように、ビール瓶 3400 にラベル 3401 を用いてプロセッサチップ 3402 を実装する。

【 0173 】

プロセッサチップ 3402 には、製造日、製造場所、使用材料等の基本事項を記録する。このような基本事項は、書き換える必要がないためマスク ROM や本発明の記憶素子等の書き換え不能な記憶素子 ( メモリ ) を用いて記録するとよい。製造日、製造場所、使用材料等の基本事項は、消費者が商品を購入する際に正確に入手したい情報である。このような情報を書き換え不可能な記憶素子に記録するということによって、情報の改ざんなどを防ぐことができるので、消費者へ信頼性のある正確な情報を伝達することができる。加えてプロセッサチップ 3402 には、各ビール瓶の配送先、配送日時等の個別事項を記録する。例えば、図 21 ( B ) に示すように、ビール瓶 3400 がベルトコンベア 3412 により流れ、ライタ装置 3413 を通過するときに、各配送先、配送日時を記録すること

10

20

30

40

50

ができる。このような個別事項は、EEPROM等の書き換え、消去可能なメモリを用いて記録するとよい。

【0174】

また配達先から購入された商品情報がネットワークを通じて物流管理センターへ送信されると、この商品情報に基づき、ライタ装置又は当該ライタ装置を制御するパーソナルコンピュータ等が配送先や配送日時を算出し、プロセッサチップへ記録するようなシステムを構築するとよい。

【0175】

また配達はケース毎に行われるため、ケース毎、又は複数のケース毎にプロセッサチップを実装し、個別事項を記録することもできる。

10

【0176】

このような複数の配達先が記録されうる商品は、プロセッサチップを実装することにより、手作業で行う入力にかかる時間を削減でき、それに起因した入力ミスを低減することができる。加えて物流管理の分野において最もコストのかかる人件費用を削減することができる。従って、プロセッサを実装したことにより、ミスの少ない、低成本な物流管理を行うことができる。

【0177】

さらに配達先において、ビールに合う食料品や、ビールを使った料理法等の応用事項を記録してもよい。その結果、食料品等の宣伝を兼ねることができ、消費者の購買意欲を高めることができる。このような応用事項は、EEPROM等の書き換え、消去可能なメモリを用いて記録するとよい。このようにプロセッサチップを実装することにより、消費者へ提供できる情報を増大させることができるため、消費者は安心して商品を購入することができる。

20

【0178】

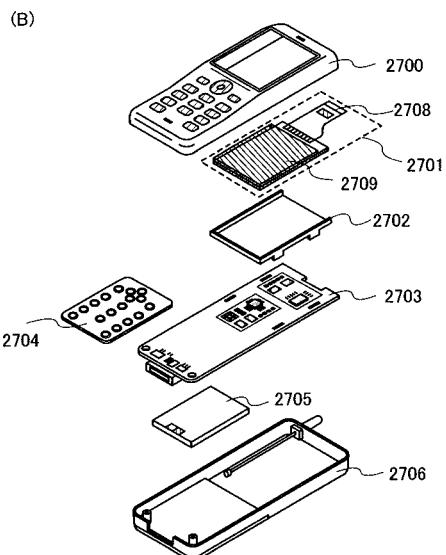

次に、本発明の半導体装置を実装した電子機器の一態様について図面を参照して説明する。ここで例示する電子機器は携帯電話機であり、筐体2700、2706、パネル2701、ハウジング2702、プリント配線基板2703、操作ボタン2704、バッテリ2705を有する(図17(B)参照)。パネル2701はハウジング2702に脱着自在に組み込まれ、ハウジング2702はプリント配線基板2703に嵌着される。ハウジング2702はパネル2701が組み込まれる電子機器に合わせて、形状や寸法が適宜変更される。プリント配線基板2703には、パッケージングされた複数の半導体装置が実装されており、このうちの1つとして、本発明の半導体装置を用いることができる。プリント配線基板2703に実装される複数の半導体装置は、コントローラ、中央処理ユニット(CPU, Central Processing Unit)、メモリ、電源回路、音声処理回路、送受信回路等のいずれかの機能を有する。

30

【0179】

パネル2701は、接続フィルム2708を介して、プリント配線基板2703と一体化される。上記のパネル2701、ハウジング2702、プリント配線基板2703は、操作ボタン2704やバッテリ2705と共に、筐体2700、2706の内部に収納される。パネル2701が含む画素領域2709は、筐体2700に設けられた開口窓から視認できるように配置されている。

40

【0180】

上記の通り、本発明の半導体装置は、小型、薄型、軽量であることを特徴としており、上記特徴により、電子機器の筐体2700、2706内部の限られた空間を有効に利用することができる。

【0181】

また、本発明の半導体装置は、一対の導電層間に絶縁層が挟まれた単純な構造の記憶素子を有するため、安価な半導体装置を用いた電子機器を提供することができる。また、本発明の半導体装置は高集積化が容易なため、大容量の記憶回路を有する半導体装置を用いた電子機器を提供することができる。

50

## 【0182】

また、本発明の半導体装置が有する記憶装置は、光学的作用又は電気的作用によりデータの書き込みを行うものであり、不揮発性であって、データの追記が可能であることを特徴とする。上記特徴により、書き換えによる偽造を防止することができ、新たなデータを追加して書き込むことができる。従って、高機能化と高付加価値化を実現した半導体装置を用いた電子機器を提供することができる。

## 【0183】

なお、筐体2700、2706は、携帯電話機の外観形状を一例として示したものであり、本実施の形態に係る電子機器は、その機能や用途に応じて様々な態様に変容しうる。

## 【図面の簡単な説明】

10

## 【0184】

【図1】本発明を説明する概念図。

【図2】本発明の半導体装置の作製方法を説明する図。

【図3】本発明の半導体装置の作製方法を説明する図。

【図4】本発明の半導体装置の作製方法を説明する図。

【図5】本発明の半導体装置の作製方法を説明する図。

【図6】本発明の半導体装置の作製方法を説明する図。

【図7】本発明の半導体装置の作製方法を説明する図。

【図8】本発明の半導体装置の作製方法を説明する図。

【図9】本発明の半導体装置の作製方法を説明する図。

20

【図10】本発明の半導体装置の作製方法を説明する図。

【図11】本発明の半導体装置の作製方法を説明する図。

【図12】本発明の半導体装置の作製方法を説明する図。

【図13】本発明の半導体装置の作製方法を説明する図。

【図14】本発明の半導体装置を説明する図。

【図15】本発明の半導体装置を説明する図。

【図16】本発明の半導体装置を説明する図。

【図17】本発明の半導体装置の適用例を説明する図。

【図18】本発明の半導体装置の適用例を説明する図。

【図19】本発明に適用することのできる液滴吐出装置の構成を説明する図。

30

【図20】本発明の半導体装置を説明する図。

【図21】本発明の半導体装置の適用例を説明する図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図 2 1】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/105 (2006.01) H 01 L 29/78 627C

H 01 L 51/05 (2006.01) H 01 L 29/28

(56)参考文献 特開2005-013985 (JP, A)

特開平10-206896 (JP, A)

特開2003-178874 (JP, A)

特開2004-363049 (JP, A)

特開2004-158815 (JP, A)

特開2003-243164 (JP, A)

特開2004-310069 (JP, A)

特開2002-319495 (JP, A)

特開2004-273367 (JP, A)

特開2004-228373 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 27 / 12

H 01 L 21 / 02

H 01 L 21 / 336

H 01 L 21 / 8229

H 01 L 21 / 8239 - 21 / 8247

H 01 L 27 / 10 - 27 / 115

H 01 L 29 / 786

H 01 L 51 / 05 - 51 / 40