(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5692889号

(P5692889)

(45) 発行日 平成27年4月1日(2015.4.1)

(24) 登録日 平成27年2月13日(2015.2.13)

(51) Int.Cl.

F 1

H01L 29/78 (2006.01)

H01L 29/06 (2006.01)H01L 29/78 652H

H01L 29/78 652P

H01L 29/78 652S

H01L 29/78 653A

請求項の数 31 外国語出願 (全 15 頁)

(21) 出願番号 特願2009-215803 (P2009-215803)

(22) 出願日 平成21年9月17日 (2009.9.17)

(65) 公開番号 特開2010-80963 (P2010-80963A)

(43) 公開日 平成22年4月8日 (2010.4.8)

審査請求日 平成24年9月14日 (2012.9.14)

(31) 優先権主張番号 12/284,086

(32) 優先日 平成20年9月18日 (2008.9.18)

(33) 優先権主張国 米国(US)

(73) 特許権者 501315784

パワー・インテグレーションズ・インコーポレーテッド

アメリカ合衆国・95138・カリフォルニア州・サンホゼ・ヘリヤー・アベニュー

·5245

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

最終頁に続く

(54) 【発明の名称】縦型高電圧電界効果トランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

縦型高電圧電界効果トランジスタ(HVFEET)であって、ループレイアウトに配置された半導体材料からなるピラーを備え、前記ループレイアウトは、各々第1の幅を有する少なくとも2つの平行で線形のフィレット領域と、少なくとも2つの丸みのある領域とを有し、前記丸みのある領域は、前記第1の幅よりも狭い第2の幅を有し、前記ピラーの最上面または最上面の近くに第1の導電型のソース領域が配置されており、前記ピラーの中、前記ソース領域の下に第2の導電型のボディ領域が配置されており、さらに

前記ピラーの対向する側にそれぞれ配置された第1および第2の誘電体領域を備え、前記第1の誘電体領域は、前記ピラーによって横方向に囲まれており、前記第2の誘電体領域は、前記ピラーを横方向に囲んでおり、さらに

前記第1および第2の誘電体領域中にそれぞれ配置された第1および第2のフィールドプレートを備える、縦型HVFEET。

## 【請求項 2】

前記第1および第2の誘電体領域中にそれぞれ、前記ピラーの前記最上面にまたは前記最上面の近くに、前記ボディ領域に隣接して配置された第1および第2のゲート部材をさらに備え、前記第1および第2のゲート部材は、前記ボディ領域からゲート酸化物によって隔てられている、請求項1に記載の縦型HVFEET。

## 【請求項 3】

10

20

前記ピラーは、前記第1および第2のフィールドプレートの各々から、前記ピラーに沿ったすべての箇所で一定の第1の横方向距離を隔てられている、請求項1に記載の縦型H V F E T。

**【請求項4】**

前記距離は、前記フィールドプレートを前記ピラーからそれぞれ隔てる前記第1および第2の誘電体領域の横方向の厚みと等しい、請求項3に記載の縦型H V F E T。

**【請求項5】**

前記ピラーは、移行領域をさらに含み、各移行領域は、第2の横方向距離に亘って前記フィレット領域の一方の端部の前記第1の幅を前記第2の幅まで狭める少なくとも1つの先細になった端縁を有する、請求項1に記載の縦型H V F E T。

10

**【請求項6】**

前記ピラーは、延長領域をさらに含み、各延長領域は、線形であり、前記第2の幅を有し、各延長領域は前記少なくとも2つの丸みのある領域のうち1つの一方の端部に結合される、請求項1に記載の縦型H V F E T。

**【請求項7】**

前記第1および第2のゲート部材は、前記第1および第2のフィールドプレートから完全に絶縁されている、請求項2に記載の縦型H V F E T。

**【請求項8】**

各移行領域は、1対の先細になった端縁を含む、請求項5に記載の縦型H V F E T。

**【請求項9】**

前記少なくとも2つの丸みのある領域は、前記ループレイアウトの対向する端部に配置された1対の半円領域を含む、請求項1に記載の縦型H V F E T。

20

**【請求項10】**

縦型高電圧電界効果トランジスタ(H V F E T)であって、

縦方向の厚みを有する半導体材料からなるピラーを備え、前記ピラーは、ループレイアウトに形成されており、前記ループレイアウトは、

1対の平行で線形のフィレット領域を含み、各前記フィレット領域は、第1の幅を有し、前記フィレット領域は、第1の横方向に延在し、さらに

1対の丸みのある先端領域を含み、前記丸みのある先端領域は、前記第1の幅よりも狭い第2の幅を有し、

30

前記ピラーの前記縦方向の厚みは、前記フィレット領域の前記第1の幅よりも少なくとも12倍大きく、前記先端領域の前記第2の幅よりも少なくとも15倍大きい、縦型H V F E T。

**【請求項11】**

前記ピラーは、各前記フィレット領域の各端部に移行領域をさらに含み、前記移行領域は、前記ピラーを前記第1の幅から前記第2の幅まで第1の横方向距離に亘って狭めている、請求項10に記載の縦型H V F E T。

**【請求項12】**

前記移行領域は、少なくとも1つの先細になった端縁を有する、請求項11に記載の縦型H V F E T。

40

**【請求項13】**

前記移行領域は、前記ピラーの対向する側に位置した1対の先細になった端縁を含む、請求項11に記載の縦型H V F E T。

**【請求項14】**

各前記フィレット領域の各端部は、前記先端領域のうち1つの一方の端部と、前記第1の幅から前記第2の幅への急な段移行で直接結合されている、請求項10に記載の縦型H V F E T。

**【請求項15】**

前記ピラーは、前記移行領域の端部を前記先端領域のうち1つの一方の端部と結合する線形の延長領域をさらに含み、前記延長領域は、第2の横方向距離に亘って延在する前記

50

第2の幅を有する、請求項11に記載の縦型HVFET。

**【請求項16】**

前記1対の丸みのある先端領域の各々は、半円形状を有し、前記1対の丸みのある先端領域の各々は、前記ループレイアウトの対向する端部に配置されている、請求項10に記載の縦型HVFET。

**【請求項17】**

前記ループレイアウトは、レーストラック形状に形成されている、請求項10に記載の縦型HVFET。

**【請求項18】**

縦型高電圧電界効果トランジスタ(HVFET)であって、

10

第1の導電型の基板上に形成された半導体材料からなるピラーを備え、前記ピラーは、縦方向の厚みを有し、ループレイアウトに形成されており、前記ループレイアウトは、

1対の平行で線形のフィレット領域を含み、各前記フィレット領域は、第1の幅を有し、前記フィレット領域は、第1の横方向に延在し、さらに

1対の半円形先端領域を含み、前記先端領域は、前記第1の幅よりも狭い第2の幅を有し、

前記ピラーは、前記ピラーの最上面にまたは最上面の近くに配置された前記第1の導電型のソース領域と、前記ピラーの中、前記ソース領域の下に配置された第2の導電型のボディ領域と、前記ボディ領域から前記基板まで縦に延在する前記第1の導電型の延長ドレイン領域とをさらに含み、前記縦型HVFETは、さらに

20

前記ピラーの対向する側にそれぞれ配置された第1および第2の誘電体領域を備え、前記第1の誘電体領域は、前記ピラーによって横方向に囲まれてあり、前記第2の誘電体領域は、前記ピラーを横方向に囲んでおり、さらに

前記第1および第2の誘電体領域中にそれぞれ配置された第1および第2のフィールドプレートを備え、前記ピラーは、前記第1および第2のフィールドプレートの各々から、前記ピラーに沿ってすべての箇所で一定の距離を隔てられている、縦型HVFET。

**【請求項19】**

前記ループレイアウトは、レーストラック形状に形成されている、請求項18に記載の縦型HVFET。

**【請求項20】**

30

前記第1の幅の範囲は、2.4-3.0 μm幅である、請求項18に記載の縦型HVFET。

**【請求項21】**

前記第2の幅の範囲は、1.5-2.2 μm幅である、請求項18に記載の縦型HVFET。

**【請求項22】**

前記ピラーは、前記フィレット領域の前記第1の幅よりも少なくとも12倍大きく、かつ前記先端領域の前記第2の幅よりも少なくとも15倍大きい縦方向の厚みを有する、請求項18に記載の縦型HVFET。

**【請求項23】**

40

前記ピラーは、移行領域をさらに含み、各前記移行領域は、第1の横方向距離に亘って前記フィレット領域の前記第1の幅を前記第2の幅まで狭める少なくとも1つの先細になつた端縁を有する、請求項18に記載の縦型HVFET。

**【請求項24】**

前記ピラーは、延長領域をさらに含み、各前記延長領域は、前記第2の幅を有し、前記移行領域のうち対応する1つを前記先端領域の一方の端部と結合する、請求項23に記載の縦型HVFET。

**【請求項25】**

縦型高電圧電界効果トランジスタ(HVFET)であって、

閉じたループレイアウトに配置された半導体材料からなるピラーを備え、前記ループレ

50

イアウトは、各々第1の幅を有する少なくとも2つの平行で線形のフィレット領域と、少なくとも2つの丸みのある領域とを有し、前記丸みのある領域は、前記第1の幅よりも狭い第2の幅を有し、前記ピラーの最上面または最上面の近くに第1の導電型のソース領域が配置されており、さらに

前記ピラーの対向する側にそれぞれ配置された第1および第2の誘電体領域を備え、前記第1の誘電体領域は、前記ピラーによって横方向に囲まれてあり、前記第2の誘電体領域は、前記ピラーを横方向に囲んでおり、さらに

前記第1および第2の誘電体領域中にそれぞれ配置された第1および第2のフィールドプレートを備える、縦型HVFET。

**【請求項26】**

10

前記ピラーの中、前記ソース領域の下に配置される、第2の導電型のボディ領域をさらに備える、請求項25に記載の縦型HVFET。

**【請求項27】**

前記ループレイアウトは、レーストラック形状に形成されている、請求項25に記載の縦型HVFET。

**【請求項28】**

前記ピラーの中、基板より上に配置される第1導電型の延長ドレイン領域をさらに含み、前記ボディ領域は前記ソース領域を前記延長ドレイン領域から縦方向に分離する、請求項26に記載の縦型HVFET。

**【請求項29】**

20

前記第1および第2の誘電体領域中にそれぞれ、前記ピラーの前記最上面にまたは前記最上面の近くに、前記ボディ領域に隣接して配置された第1および第2のゲート部材をさらに備え、前記第1および第2のゲート部材は、前記ボディ領域からゲート酸化物によって隔てられている、請求項26に記載の縦型HVFET。

**【請求項30】**

前記ピラーは、前記第1および第2のフィールドプレートの各々から、前記ピラーに沿ったすべての箇所で一定の第1の横方向距離を隔てられている、請求項25に記載の縦型HVFET。

**【請求項31】**

30

前記第1の横方向距離は、前記フィールドプレートを前記ピラーからそれぞれ隔てる前記第1および第2の誘電体領域の横方向の厚みと等しい、請求項30に記載の縦型HVFET。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

この開示は、高電圧に耐えることができる電界効果半導体トランジスタ構造に関する。

**【背景技術】**

**【0002】**

**背景**

高電圧電界効果トランジスタ(HVFET)は、半導体技術分野において周知である。多くのHVFETは、デバイスが「オフ」状態にあるときに印加された高電圧(たとえば数100ボルト)を維持または遮断する延長ドレイン領域を含むデバイス構造を使用する。この種類のHVFETは、一般にオフライン電源、モータ制御などのためのAC/DC変換器などの電力変換用途において用いられる。こういったデバイスは、高電圧で切換えられ、オフ状態で高い遮断電圧を達成し、その一方で「オン」状態で電流への抵抗を最小化することができる。遮断または降伏電圧は、一般的に、略してV<sub>bd</sub>またはBVと表わす。頭文字Rdsは、延長ドレイン領域における抵抗と表面積との積を指し、一般的に、デバイスのオン状態性能を説明するために用いられる。

**【発明の概要】**

**【発明が解決しようとする課題】**

40

50

## 【0003】

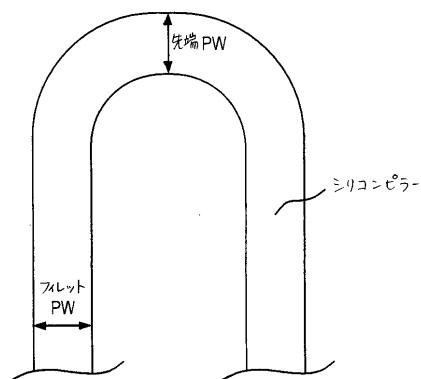

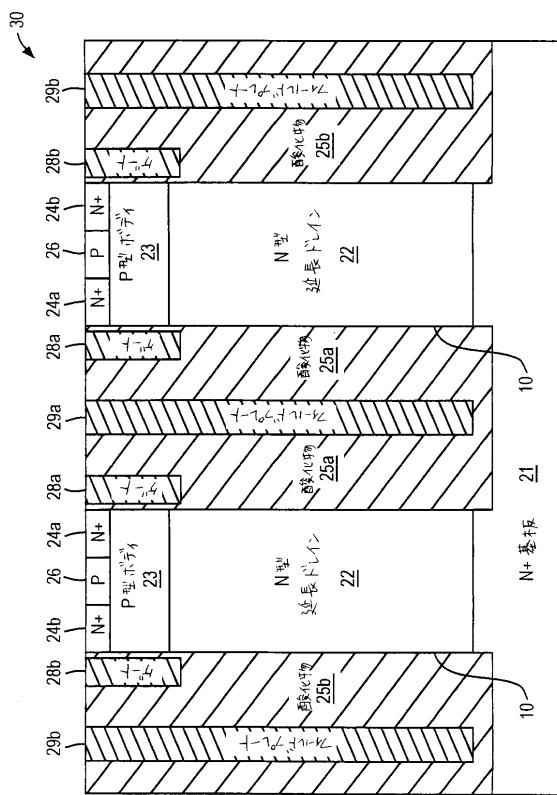

先行技術の縦型 H V F E T 構造において、半導体材料からなるメサまたはピラーは、オン状態での電流のための延長ドレインまたはドリフト領域を形成する。シリコンピラー構造は、典型的に、レーストラック形状で形成され、ピラー構造は、ピラー長に直交する方向に繰返される。図 1 には、従来の高電圧縦型トランジスタのためのシリコンピラーレイアウトの一方の端部が示されている。この構造は、半円形の（すなわち放射状の）先端領域によって接続された 1 対の長い直線状のフィレット領域によって特徴付けられる。先端領域およびフィレット領域におけるピラー幅 (P W) は、全体を通して一定である。

## 【課題を解決するための手段】

## 【0004】

縦型デバイス構造は、トレンチゲートが、基板の最上部近くに、かつボディ領域が延長ドレイン領域の上に堆積されたピラーの側壁領域に近接して形成されていることによって特徴付けられる。適切な電圧電位をゲートに印加すると、導電チャネルが、ボディ領域の縦の側壁部分に沿って形成されて、電流が半導体材料を通って縦方向に、すなわち電流がソース領域が堆積された基板の最上面からドリフト領域を通ってドレイン領域が位置する基板の底部まで下に流れるようにすることが起こる。ドリフト領域は、通常、低濃度にドープされて、デバイスがオフのときドレインに印加される高電圧を維持する。したがって、ドーピングの減少および延長ドレイン領域の長さの増大は、両方ともオン状態抵抗の増大を引起すので、デバイスのオン状態性能に悪影響を及ぼす。言い換えれば、従来の高電圧 F E T 設計は、B V と R d s との間のトレードオフによって特徴付けられる。

## 【図面の簡単な説明】

## 【0005】

この開示は、以下の詳細な説明および添付の図面からより完全に理解されるだろうが、この説明および図面は、この発明を、示された特定的な実施例に限定するものとして捉えられるべきではなく、説明および理解のためのものにすぎない。

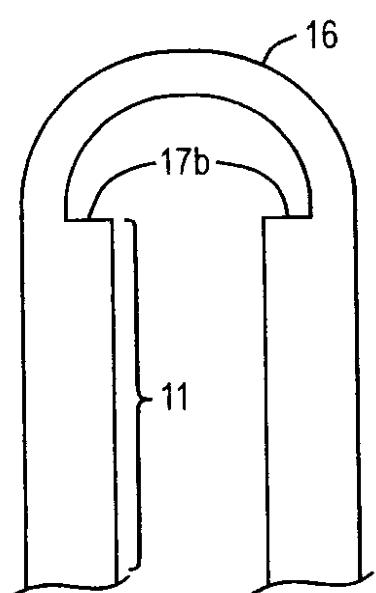

【図 1】先行技術の縦型高電圧縦型電界効果トランジスタ (H V F E T) の一部分のレイアウトの上面図である。

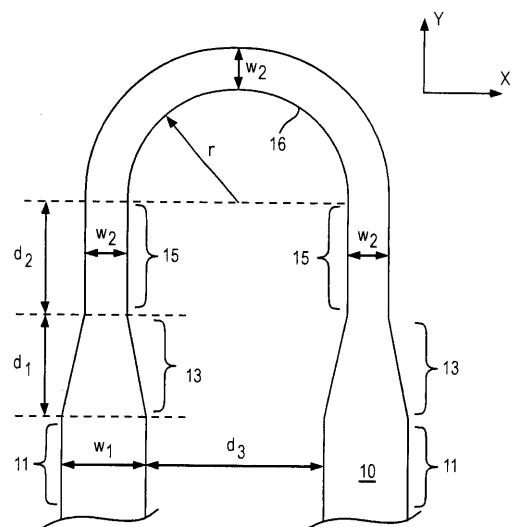

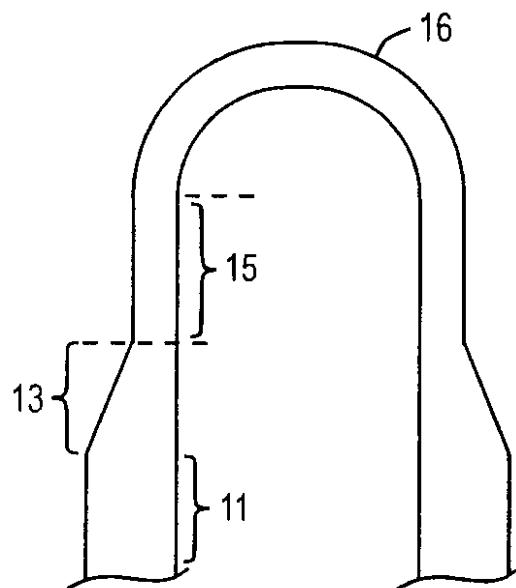

【図 2】ピラー幅がフィレット領域よりも先端領域で相対的に狭い縦型 H V F E T 構造の一方の端部のレイアウト例を示す図である。

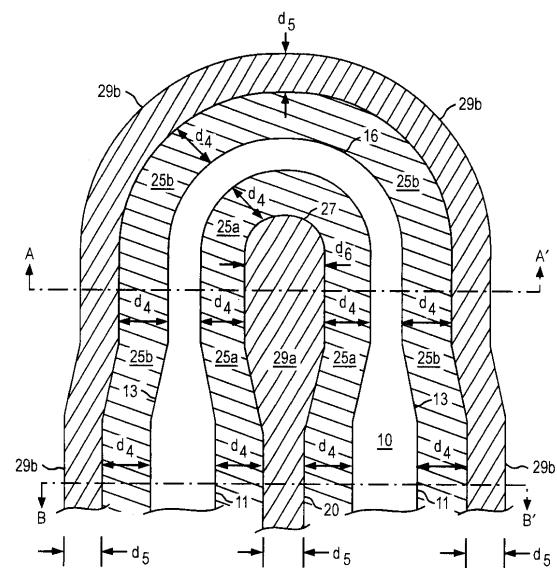

【図 3】図 2 のレイアウト例に誘電体領域とフィールドプレート部材とを加えて説明する図である。

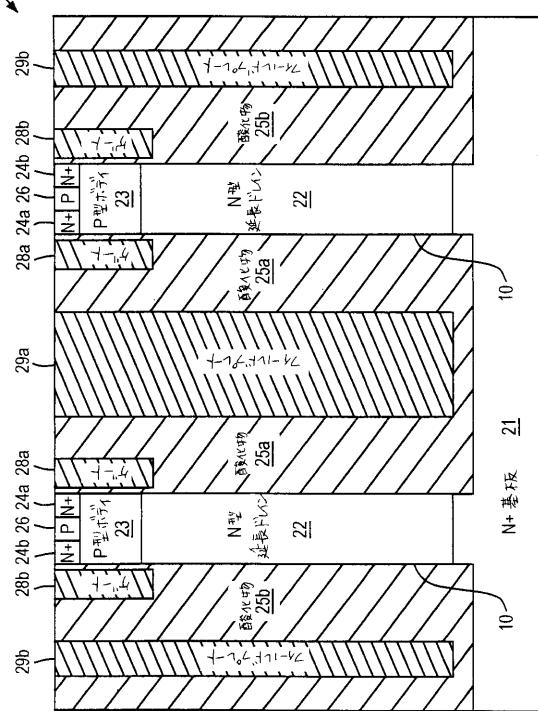

【図 4】図 2 に示された縦型 H V F E T 構造の (A - A 切断線に沿って取った) 例示的な断面側面図である。

【図 5】図 2 に示された縦型 H V F E T 構造の (B - B 切断線に沿って取った) 例示的な断面側面図である。

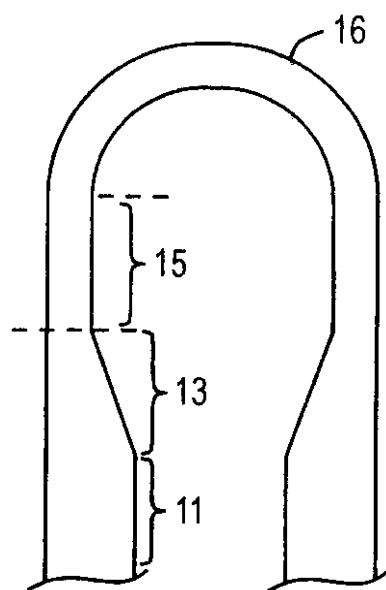

【図 6 A】縦型 H V F E T 構造のレーストラック形状シリコンピラーの一方の端部のさまざまなレイアウト例を示す図である。

【図 6 B】縦型 H V F E T 構造のレーストラック形状シリコンピラーの一方の端部のさまざまなレイアウト例を示す図である。

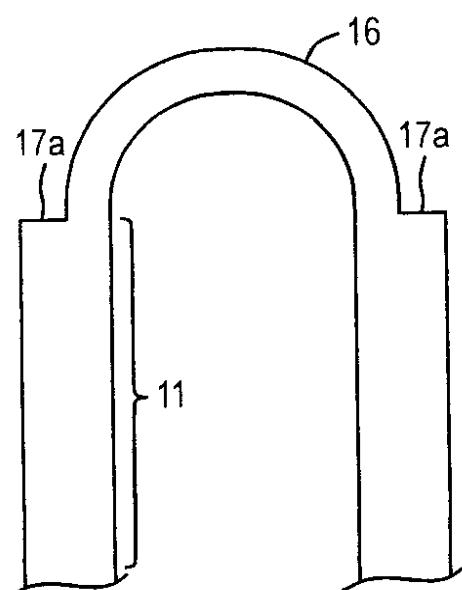

【図 6 C】縦型 H V F E T 構造のレーストラック形状シリコンピラーの一方の端部のさまざまなレイアウト例を示す図である。

【図 6 D】縦型 H V F E T 構造のレーストラック形状シリコンピラーの一方の端部のさまざまなレイアウト例を示す図である。

【図 6 E】縦型 H V F E T 構造のレーストラック形状シリコンピラーの一方の端部のさまざまなレイアウト例を示す図である。

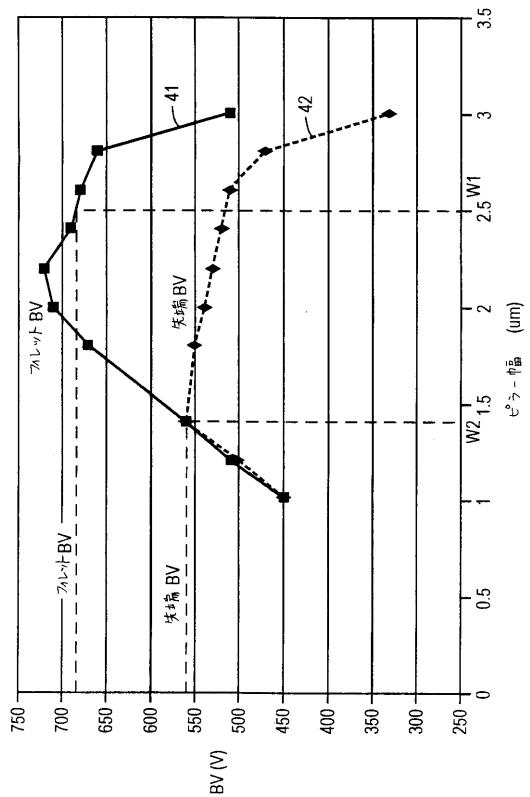

【図 7】図 2 に示すレイアウトを有する縦型 H V F E T 構造例についてピラー幅に対するドレイン降伏電圧を示すグラフである。

## 【発明を実施するための形態】

## 【0006】

例示的な実施例の説明

以下の説明において、この明細書中の開示の完全な理解を提供するために、材料の種類、寸法、構造的特徴、処理ステップなどの特定的な詳細が述べられる。しかしながら、当業者は、こういった特定的な詳細は、説明された実施例を実行するために必要でないことがあることを理解するであろう。図中の要素は、説明上のものであり、わかりやすくするために、一律の縮尺に従わずに描かれていることも理解されるべきである。

#### 【0007】

図2には、縦型HVFETのシリコンピラー10のレイアウト例が示されている。図2の上面図には、対向する側を誘電体領域によって囲まれた半導体材料からなるピラーを含む連続した細長いレーストラック形状ループ(たとえば輪または橈円)構造の一方の端部が示されている。ピラー10の両側にある誘電体領域内には、それぞれのゲート部材および導電性フィールドプレートが配置されている。わかりやすくするため図2には示されていないが、誘電体要素およびフィールドプレート要素は、以下に述べられる図3から図5に示されている。

10

#### 【0008】

図2の例において、レーストラック形状のピラー10の幅(すなわちピッチ)は、直線状のフィレット領域から丸みのある先端領域まで変化する。たとえば、フィレット11は、Y方向に延在し実質的に平行なピラー10の2つの側面領域を含む。500-700VのHVFETデバイス構造の典型的な例において、各フィレット11の幅W<sub>1</sub>は、およそ2.4-2.8μmである。フィレット11は、およそ10-12μmの距離d<sub>3</sub>で隔てられている。ピラー10は、移行領域13に亘ってフィレット11の各端部での幅W<sub>1</sub>から幅W<sub>2</sub>まで狭まる。500-700VのHVFETデバイス構造例については、幅W<sub>2</sub>は、およそ1.8-2.2μmである。他の実施例において、設計考慮事項、面積の制約、光リソグラフィイメージングの限界などによっては、幅W<sub>1</sub>は、2.8μmより広くてもよく、幅W<sub>2</sub>は1.8μmより狭くてもよいことが理解される。

20

#### 【0009】

示された例において、ピラー10の両側は、移行領域の距離d<sub>1</sub>に亘って同様に線形に変化して(すなわち両側が同じ傾きで先細になって)示されている。1つの実施例において、距離d<sub>1</sub>は、およそ3-10μmの長さである。移行領域13は、他の実施例においてより長くてもよい。さらに他の実施例において、移行領域は、より短いまたは全くなくされていてもよく、すなわち、ピラー10がより幅の広いフィレットからより幅の狭い先端まで先細になっているのではなく、フィレット11は、各端部での幅W<sub>1</sub>から幅W<sub>2</sub>へ急に移行してもよい。移行領域13の形状は、ピラー10の各側で対称である必要はないことも理解されるべきである。言い換えれば、幅W<sub>1</sub>から幅W<sub>2</sub>への移行は、さまざまなレイアウト形状を使用して、異なる方法で実現化されてもよい。

30

#### 【0010】

引続き図2の例について、移行領域13を丸みのある先端領域16と接続する延長領域15が示されている。各延長領域15の幅W<sub>2</sub>は、先端領域16の幅と同じである。先端領域16は、内径rと全体を通して一定の幅W<sub>2</sub>とを有する、シリコンからなる半円形状領域を含む。示された実施例において、各延長領域15の長さd<sub>2</sub>は、典型的に、3-10μmの長さである。他の実施例は、より長いまたはより短い延長領域15を使用してもよい。さらに、ある実施例は、延長領域を完全になくしてもよいことが理解されるべきである。言い換えれば、図2に示されたピラーレイアウトにおいて延長領域15を含むことは、任意選択である。

40

#### 【0011】

その上、図2の例には、単一の移行領域(各側に1つ)が示されているが、他の実施例は、複数の移行領域、またはピラー10のより幅の広いフィレットからより狭い先端領域への複数の急な(たとえば段の付いた)幅の変化を含んでもよいことが理解されるべきである。さらに他の実施例において、先端領域の幅自体が、半径rの周りで変化してもよい。たとえば、各移行領域15の端部での先端領域16の幅W<sub>2</sub>は、半円の中心での幅W<sub>3</sub>まで徐々に狭まってもよい。

50

## 【0012】

より幅の広いフィレットとより狭い先端とを有するシリコンピラーを備えて製造されたトランジスタデバイスの性能上の利点は、図7に示されるグラフを考慮することによって最もよく理解される。図7は、図2に示されるレイアウトを有する縦型HVFET構造例について、ピラー幅に対するドレイン降伏電圧(BV)を示すグラフである。プロット41は、所与のエピタキシャルドーピングレベルについて、フィレット領域におけるBVをピラー幅の関数として示す。プロット42は、同じエピタキシャルドーピングレベルについて、先端領域におけるBVをピラー幅の関数として示す。この明細書中で開示された主題の発明者らが発見し、かつ彼らの実験以前は従来未知であったことは、レーストラック形状のピラーを有する縦型HVFET構造のフィレット領域における、先端領域と比較して相当高い降伏電圧の存在であり、これは、フィレットピラー幅が先端ピラー幅よりも遙かに広い場合においてさえ存在した。言い換えれば、実験を通じて発見されたことは、所与のエピタキシャルドーピングについて、幅 $W_2$ での先端領域における最適BVに対して、フィレットBVは、 $W_2$ よりも大きなピラー幅で(たとえば $W_1$ で)先端BVよりも高いことである。

## 【0013】

シリコンピラーにおけるエピタキシャルドーピングを最適化することによって、フィレットにおけるピラー幅よりも相対的に狭いピラーの先端領域におけるピラー幅で、ドレインBVが最大化されることが理解される。これは、ドレインBVの増大に寄与する。なぜなら、薄いシリコンピラーにおけるピーク電場が、より狭いピラーについて増大されるからである。ピーク電気の増大は、ピラー中のキャリアアドーズ量の対応した増大を可能にする。ドーズ量はドーピングにピラー幅を乗じたものに等しいので、ピラー中のドーピング濃度は、さらに一層増大されてもよい。違う言い方をすれば、(図2に示されるように)先端領域においてピラー幅をより狭めることによって、ドーピングを比例的に増大させることができる。

## 【0014】

このデバイス構造のフィレット領域において、ピラー幅を増大させてRspを最小化してもよい。なぜなら、フィレット領域におけるBVは、先端におけるBVよりも大幅に高いためである。当業者は、実際的な実施例において、フィレット領域は、先端領域よりもはるかに長く、フィレット領域は、製造されるデバイスのRspの決定に著しく影響することを理解するであろう。また、BVが急速に低下する臨界ピラー幅は、フィレット領域についての方が、デバイスの先端領域と比較して大きい。当業者は、これにより、フィレット幅を増大させるとき、一層のプロセス余裕度が可能になることを理解するであろう。

## 【0015】

図3には、図2のレイアウト例が、誘電体領域とフィールドプレート部材とを加えて示されている。ゲート部材、コンタクト領域、メタライズ層などの他のデバイス構造は、わかりやすくするために図3には示されていない。図3の上面図には、隣接する内側誘電体領域25aによって、内側フィールドプレート部材29aから隔てられたシリコンピラー10が示されている。内側フィールドプレート部材29aは、球状で丸みのついた指先領域27で急に成端する。内側フィールドプレート部材29aの中央部分20は、フィレット11の中間に形成されており、幅 $d_5$ を有し、指先領域27は、より広い幅 $d_6$ を有する。より広い指先領域27の輪郭は、同心状に配置された隣接領域として形成されたピラー10の内側端縁または表面の輪郭に沿っている。このようにして、内側誘電体領域25aの幅 $d_4$ は、ピラー10の周りのすべての横方向箇所で一定であり続ける。図3に示された構造の1つの実現化例において、幅 $d_4$ の範囲は、2μmから5μmであり、幅 $d_5$ の範囲は、1μmから3μmである。示された例において、幅 $d_6$ は、典型的に、幅 $d_4$ よりも0.6μmから1.2μm広い。

## 【0016】

図3のレイアウト例には、隣接する外側誘電体領域25bによって、ピラー10の外側端縁から距離 $d_4$ 隔てられた隣接する外側フィールドプレート部材29bも示されている

。外側フィールドプレート部材 29b および外側誘電体領域 25b は両方とも、ピラー 10 を横方向に囲み、外側誘電体領域 25b の幅  $d_4$  がピラー 10 の周りのすべての横方向箇所で同じであるよう、ピラー 10 の外側端縁の変化する形状に沿っている。

#### 【0017】

特定の実施例において、内側フィールドプレート部材はなくしてもよいことが理解される。さらに他の実施例において、レーストラック形状の複数のシリコンピラーを、互いに隣接させ、併合された領域を備えて形成して、外側フィールドプレート部材が、併合されたピラー構造全体を横方向に囲む 1 つの大きな輪または直線の構造として形成されるようにもよい。こういった代替的な実施例の各々において、シリコンピラーの丸みのある先端または曲がり角領域は、より幅の広いフィレット領域よりも相対的に狭まる。

10

#### 【0018】

さらにその上、他の実施例において、酸化物誘電体の幅  $d_4$  は、先端領域の周りのすべての箇所で同じ（すなわち一定）である必要はない。つまり、ピラー 10 のフィレット 11 と内側フィールドプレート部材 29a とを隔てる横方向の距離は、ピラー 10 の丸みのある先端領域 16 と内側フィールドプレート部材 29a の球状で丸みのある指先領域 27 とを隔てる距離と異なっていてもよい。加えて、丸みのあるピラー先端領域 16 の形状は、半円形である必要はない。たとえば、特定の実施例において、ピラー先端は、四半円形で、シリコンピラー構造の形状を幾分より矩形に、または正方形にさえし得る。

#### 【0019】

図 4 には、図 2 に示された縦型 HVFET 構造の (A - A 切断線に沿って取った) 例示的な断面側面図が示されている。縦型 HVFET 30 は、N+ をドープされたシリコン基板 21 上に形成された N 型シリコンからなる延長ドレイン領域 22 を含む構造を有して示されている。基板 21 は、高濃度にドープされて、ドレイン電極まで流通する電流に対する基板の抵抗を最小化する。このドレイン電極は、完成されたデバイスにおいて、基板の底部に位置する。1 つの実施例において、延長ドレイン領域 22 は、ピラー 10 を含みかつ基板 21 からシリコンウェハの最上面まで延在するエピタキシャル層の一部である。P 型ボディ領域 23 と、P 型領域 26 によって横方向に隔てられており、N+ をドープされたソース領域 24a および 24b とは、エピタキシャル層の最上面近くに形成されている。理解されるように、P 型ボディ領域 23 は、延長ドレイン領域 22 の上に配置されており、延長ドレイン領域 22 を、N+ ソース領域 24a および 24b ならびに P 型領域 26 から縦方向に隔てる。

20

#### 【0020】

1 つの実施例において、エピタキシャル層の、延長ドレイン領域 22 を含む部分のドーピング濃度は、線形に勾配されて、実質的に均一な電場分布を示す延長ドレイン領域を生み出す。線形勾配は、エピタキシャル層の最上面より下の、ある箇所で終わってもよい。

#### 【0021】

延長ドレイン領域 22 、ボディ領域 23 、ソース領域 24a および 24b 、ならびに P 型領域 26 は、集合的に、図 4 に示された縦型トランジスタ構造例においてシリコン材料からなるメサまたはピラー 10 (どちらの用語も本願中で同義に用いられる) を構成する。ピラー 10 の対向する側に形成された縦のトレントチは、誘電体領域 25a および 25b を構成する誘電体材料 (たとえば酸化物) の層で充填されている。なお、縦のトレントチの深さは、この例においては、エピタキシャル層の厚みよりも約 5 μm 深い。

30

#### 【0022】

ピラー 10 の高さおよび幅、ならびに隣接する縦のトレントチ間の間隔は、デバイスの降伏電圧要請によって決定されてもよい。たとえば、典型的な 500 - 700 V の HVFET において、ピラー 10 の縦方向の高さ (厚み) の範囲は、約 40 μm から 60 μm 厚である。横方向の酸化物の厚み (厚み  $d_4$ ) 、約 3 - 5 μm であり、エピタキシャル層ドーピングは、延長ドレイン領域 22 の最上部でのおよそ 1 - 2 E 15 / cm<sup>3</sup> から底部での約 2 - 3 E 16 / cm<sup>3</sup> まで線形に変化する。

#### 【0023】

40

50

別の実施例において、P型領域26を(図4に示すように)N+ソース領域24aと24bとの間にピラー10の横方向の幅に亘って配置するのではなく、N+ソース領域とP型領域とを交互に、ピラー10の最上部にピラー10の横方向の長さに亘って形成してもよい。言い換えれば、図4に示されるような所与の断面図は、どこで断面が取られるかに応じて、ピラー10の横方向の幅全体に亘って延在するN+ソース領域24か、P型領域26かのいずれかを有するであろう。そのような実施例において、各N+ソース領域24は、両側に(ピラーの横方向の長さに沿って)P型領域26が隣接している。同様に、各P型領域26は、両側に(ピラーの横方向の長さに沿って)N+ソース領域24が隣接している。

## 【0024】

10

誘電体領域25aおよび25bは、二酸化シリコン、窒化シリコン、または他の適切な誘電体材料を含んでもよい。誘電体領域25は、熱成長および化学気相成長法を含めてさまざまな周知の方法を用いて形成されてもよい。内側誘電体層25aの内部に配置され、基板21およびピラー10から完全に絶縁されているのは、内側フィールドプレート部材29aである。外側フィールドプレート部材29bは、外側誘電体層25bの中に配置されて示されており、同様に、基板21およびピラー10から絶縁されている。フィールドプレート29を形成するために用いられた誘電性材料は、高濃度にドープされたポリシリコン、金属(または金属合金)、シリサイド、または他の適切な材料を含んでもよい。完成したデバイス構造において、フィールドプレート29aおよび29bは、通常、HVFETがオフ状態のとき(すなわちドレインが高電圧電位に上げられたとき)、延長ドレン領域から電荷を空乏化するために用いられてもよい容量プレートとして機能する。

## 【0025】

20

縦型HVFETトランジスタ30のトレンチゲート構造は、ゲート部材28aおよび28bを含み、各ゲート部材はそれぞれ、酸化物領域25aおよび25bの中、ピラー10の対向する側、かつフィールドプレート29aおよび29bとボディ領域23との間に配置されている。高品質で薄い(たとえば~500nm)ゲート酸化物層は、ゲート部材28をボディ領域23に隣接したピラー10の側壁から隔てている。ゲート部材28は、ポリシリコンまたは何らかの他の適切な材料を含んでもよい。1つの実施例において、各ゲート部材28は、横方向の幅がおよそ1.5μmであり、深さが約3.5μmである。

## 【0026】

30

当業者は、ピラー10の最上部近くにあるN+ソース領域24およびP型ボディ領域23は各々、普通の堆積、拡散、および/または注入処理技術を用いて形成されてもよいことを理解するであろう。N+ソース領域24の形成後、HVFET30は、ソース、ドレン、ゲート、およびデバイスのそれぞれの領域/材料と電気的に接続するフィールドプレート電極を、従来の製造方法を用いて形成することによって完成されてもよい(わかりやすくするために図示せず)。

## 【0027】

図5には、図2に示された縦型HVFET構造の(B-B'切断線に沿って取られた)例示的な断面側面図が示されている。図5に示された構成要素は、内側フィールドプレート29aの横方向の幅およびピラー10の横方向の幅を除いて、図4中の構成要素(上述)と同じである。図4において、断面側面図は、ピラーのより狭い延長領域に沿って取られており、内側フィールドプレートは、図5に示されるフィールドプレート29aの中央フィレット領域と比較して相対的に幅が広い。図5の断面側面図は、フィレット領域に移されているので、デバイス構造の延長または先端領域と比較して、フィールドプレート29aは相対的に狭く、ピラー10は相対的に幅が広い。

40

## 【0028】

図6Aから図6Eには、縦型HVFET構造のレーストラック形状のシリコンピラーの一方の端部のさまざまなレイアウト例が示されている。たとえば、図6Aには、ピラーをフィレット11から延長領域15まで外側端縁でのみ先細りさせるまたは狭める移行領域13を備えたある実施例が示されている。シリコンピラーの内側端縁は、フィレット11

50

から先端領域 1 6 まで直線状であり続ける。同様に、図 6 B の上面図には、内側端縁でのみ先細りする - 外側端縁はフィレット 1 1 から領域 1 3 および 1 5 を通って先端領域 1 6 まで変化しない（すなわち直線状または線形である） - 移行領域 1 3 を備えた代替実施例が示されている。

#### 【 0 0 2 9 】

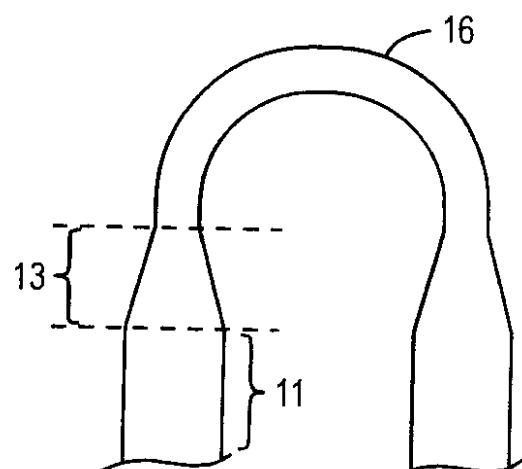

図 6 C には、さらに別の変形例が示されており、この変形例において、フィレット 1 1 は、先端部 1 6 に至るまで延在し、本質的に、移行領域 1 3 および延長領域 1 5 をなくしている。先細りに狭まる代わりに、より幅の広いフィレット領域 1 1 からより幅の狭い先端領域 1 6 への移行は、ピラーの外側端縁に位置する切欠または段 1 7 a で急に起こる。図 6 D には、図 6 C と同様のアプローチが示されているが、ピラー幅の急な移行が起こっている段 1 7 b は、シリコンピラーの内側端縁にある。

10

#### 【 0 0 3 0 】

図 6 E には、図 2 の例示的な実施例に類似するが、延長領域 1 5 をなくしたさらに別の変形例が示されている。言い換えれば、移行領域 1 3 は、ピラーの幅をフィレット 1 1 と先端領域 1 6 との間で直接先細りさせてまたは狭めている。当業者は、図 6 A から図 6 D に示された任意の実施例は、同様に延長領域 1 5 なしに、すなわち移行領域 1 3 の端部で始まる先端領域を備えて、実現化してもよいことを理解するであろう。さらに他の実施例は、複数の段または例として示されたさまざまなパラメータの組合せを備えて製造されてもよい。

#### 【 0 0 3 1 】

20

1 つの実施例において、縦型トランジスタデバイス構造のレーストラックトランジスタセグメントの各々は、X 方向の幅（すなわちピッチ）があよそ  $13 \mu\text{m}$  であり、Y 方向の長さの範囲が約  $400 \mu\text{m}$  から  $1000 \mu\text{m}$  であり、ピラーの高さが約  $60 \mu\text{m}$  である。言い換えれば、縦型 H V F E T を構成する個々のレーストラックトランジスタセグメントの長さの幅に対する比の範囲は、約 30 から 80 である。特定的な実施例において、各レーストラック形状のセグメントの長さは、そのピッチまたは幅よりも少なくとも 20 倍大きい。

#### 【 0 0 3 2 】

当業者は、完成されたデバイス構造において、パターン形成された金属層が用いられて、個々のトランジスタセグメントのシリコンピラー 1 0 の各々を相互接続することを理解するであろう。つまり、実際的な実施例において、ソース領域、ゲート部材、およびフィールドプレートはすべてそれぞれ、半導体ダイ上の対応する電極に共に配線されている。示されたレイアウト例において、シリコンピラーを隔てる誘電体領域の幅およびフィールドプレートの幅は、半導体ダイに亘って実質的に均一である。均一な幅および離隔距離でトランジスタセグメントをレイアウトすると、誘電体領域 2 5 とフィールドプレート 2 9 とを含む層を形状適合に堆積するために用いられる処理ステップの後で、空隙または孔が形成されることが予防される。

30

#### 【 0 0 3 3 】

上記実施例は、特定的なデバイス種類に関連して説明されたが、当業者は、数多くの変形例および変更例がこの発明の十分に範囲内であることを理解するであろう。たとえば、H V F E T が説明されたが、示された方法、レイアウト、および構造は、ショットキー（Schottky）、ダイオード、I G B T およびバイポーラ構造を含めて他の構造およびデバイス種類に等しく適用可能である。したがって、明細書および図面は、限定的意味ではなく例示的意味で考えられるべきである。

40

#### 【 符号の説明 】

#### 【 0 0 3 4 】

1 0 ピラー、1 1 フィレット、1 3 移行領域、1 5 延長領域、1 6 先端領域、1 7 a , 1 7 b 段、2 0 中央部分、2 1 基板、2 2 延長ドレイン領域、2 3 ボディ領域、2 4 a , 2 4 b ソース領域、2 5 a 内側誘電体領域、2 5 b 外側誘電体領域、2 6 P 型領域、2 7 指先領域、2 8 a , 2 8 b ゲート部材、2 9 a 内側

50

フィールドプレート部材、29b 外側フィールドプレート部材、30 縦型HVFET

。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6 A】

【図 6 B】

【図 6 C】

【図 6 D】

【図 6 E】

【図7】

---

フロントページの続き

(74)代理人 100109162

弁理士 酒井 將行

(74)代理人 100111246

弁理士 荒川 伸夫

(74)代理人 100124523

弁理士 佐々木 真人

(72)発明者 スジット・パネルジー

アメリカ合衆国、95125 カリフォルニア州、サンノゼ、ハクスリー・コート、1901

(72)発明者 ビジェイ・バルササラシー

アメリカ合衆国、94040 カリフォルニア州、マウンテン・ビュー、ボニータ・アベニュー、1

055

(72)発明者 リン・チュー

アメリカ合衆国、95129 カリフォルニア州、サンノゼ、アルバニー・ドライブ、4300、

エル・135

審査官 工藤 一光

(56)参考文献 特開2008-205483(JP,A)

特開2007-266505(JP,A)

特開2001-217419(JP,A)

特開平6-291311(JP,A)

特開平5-259454(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L29/06

H01L29/78-29/792