등록특허 10-2254104

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년05월20일

(11) 등록번호 10-2254104

(24) 등록일자 2021년05월13일

(51) 국제특허분류(Int. Cl.)

H01L 23/34 (2006.01) H01L 23/48 (2006.01)

(21) 출원번호 10-2014-0130335

(22) 출원일자 2014년09월29일

심사청구일자 2019년09월16일

(65) 공개번호 10-2016-0037582

(43) 공개일자 2016년04월06일

(56) 선행기술조사문현

KR1020120005185 A\*

(뒷면에 계속)

(73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

조차제

인천광역시 부평구 경원대로 1269, 105동 802호

(산곡동, 현대1차아파트)

임윤혁

경기도 화성시 동탄반석로 277, 111동 2803호 (석

우동, 예당마을우미린제일풍경채아파트)

조태제

경기도 용인시 수지구 성복1로164번길 13, 207동

402호 (성복동, 벼들치마을성복힐스테이트2차)

(74) 대리인

리엔록특허법인

심사관 : 오순영

전체 청구항 수 : 총 15 항

(54) 발명의 명칭 반도체 패키지

### (57) 요 약

다른 종류의 반도체 칩이 포함되는 반도체 패키지 내부로부터 발열을 효율적으로 외부로 방출할 수 있는 반도체 패키지를 제공한다. 본 발명에 따른 반도체 패키지는 패키지 베이스 기판, 패키지 베이스 기판 상에 부착되는 적어도 하나의 제1 반도체 칩 및 적어도 하나의 제1 반도체 칩과 인접하도록 패키지 베이스 기판 상에 부착되며 복수의 제2 반도체 칩이 적층된 적어도 하나의 적층 반도체 칩 구조체를 포함하며, 적어도 하나의 제1 반도체 칩과 인접하는 적어도 하나의 적층 반도체 칩 구조체의 변에 복수의 관통 전극이 형성된 관통 전극 영역이 인접하도록 배치된다.

### 대 표 도

(56) 선행기술조사문현

KR1020120036128 A\*

KR1020130044052 A\*

KR1020140078915 A\*

JP2014179612 A

KR1020130042936 A

\*는 심사관에 의하여 인용된 문현

---

## 명세서

### 청구범위

#### 청구항 1

패키지 베이스 기판;

상기 패키지 베이스 기판 상에 부착되는 적어도 하나의 제1 반도체 칩; 및

상기 적어도 하나의 제1 반도체 칩과 인접하도록 상기 패키지 베이스 기판 상에 부착되며, 복수의 제2 반도체 칩이 적층된 적어도 하나의 적층 반도체 칩 구조체;를 포함하며,

상기 적어도 하나의 적층 반도체 칩 구조체의 관통 전극 영역은, 상기 적어도 하나의 제1 반도체 칩의 한 변과 대향하는 적어도 하나의 적층 반도체 칩 구조체의 한 변을 따라 수직 적층되는 복수의 관통 전극을 포함하고,

상기 복수의 관통 전극이 적어도 하나의 상기 제1 반도체 칩으로부터의 열을 방출하도록, 상기 적어도 하나의 제1 반도체 칩은 상기 복수의 관통 전극에 인접하여 배치되는 반도체 패키지.

#### 청구항 2

제1 항에 있어서,

상기 복수의 관통 전극과 상기 적어도 하나의 적층 반도체 칩 구조체의 한 변에 대향하는 상기 적어도 하나의 제1 반도체 칩의 측면을 감싸되, 상기 적어도 하나의 제1 반도체 칩의 상면 및 상기 적어도 하나의 적층 반도체 칩 구조체의 상면을 덮지 않도록 상기 패키지 베이스 기판 상에 형성되는 패키지 몰딩층을 더 포함하며,

상기 적어도 하나의 제1 반도체 칩의 상면 및 상기 적어도 하나의 적층 반도체 칩 구조체의 상면은 상기 패키지 베이스 기판으로부터 동일 레벨에 위치하는 것을 특징으로 하는 반도체 패키지.

#### 청구항 3

제2 항에 있어서,

열 전달 물질층(TIM, Thermal Interface Material)을 사이에 두고 상기 적어도 하나의 제1 반도체 칩 및 상기 적어도 하나의 적층 반도체 칩 구조체 상에 부착되는 방열 부재;를 더 포함하는 것을 특징으로 하는 반도체 패키지.

#### 청구항 4

제3 항에 있어서,

상기 복수의 제2 반도체 칩 중 최상단의 반도체 칩에 형성된 상기 복수의 관통 전극은 상기 열 전달 물질층과 접하는 것을 특징으로 하는 반도체 패키지.

#### 청구항 5

삭제

#### 청구항 6

제1 항에 있어서,

상기 적어도 하나의 적층 반도체 칩 구조체는 제1 및 제2 적층 반도체 칩 구조체를 포함하며,

상기 제1 및 제2 적층 반도체 칩 구조체 각각의 한 변은, 상기 적어도 하나의 제1 반도체 칩의 서로 반대되는 양 변과 각각 대향하는 것을 특징으로 하는 반도체 패키지.

#### 청구항 7

삭제

## 청구항 8

삭제

## 청구항 9

제1 항에 있어서,

상기 적어도 하나의 제1 반도체 칩은, MPU(Micro Processor Unit) 또는 GPU(Graphic Processor Unit)인 것을 특징으로 하는 반도체 패키지.

## 청구항 10

제1 항에 있어서,

상기 복수의 제2 반도체 칩은, 메모리 반도체 칩을 포함하는 것을 특징으로 하는 반도체 패키지.

## 청구항 11

제1 항에 있어서,

상기 복수의 제2 반도체 칩은, 로직 반도체 칩 및 상기 로직 반도체 칩 상에 적층되는 복수의 메모리 반도체 칩으로 이루어지는 것을 특징으로 하는 반도체 패키지.

## 청구항 12

제1 항에 있어서,

상기 적어도 하나의 제1 반도체 칩은, 상기 복수의 제2 반도체 칩 각각보다 단위 면적당 발열량이 많은 것을 특징으로 하는 반도체 패키지.

## 청구항 13

패키지 베이스 기판;

상기 패키지 베이스 기판 상에 부착되며, 서브 패키지 베이스 기판 상에 부착되는 하나의 제1 반도체 칩을 포함하는 적어도 하나의 서브 반도체 패키지;

상기 적어도 하나의 서브 반도체 패키지와 인접하도록 상기 패키지 베이스 기판 상에 부착되며, 복수의 관통 전극이 형성된 관통 전극 영역을 각각 가지는 복수의 제2 반도체 칩이 적층되고, 상기 하나의 제1 반도체 칩의 상면과 상기 복수의 제2 반도체 칩 중 최상단의 제2 반도체 칩의 상면이 동일 레벨에 위치하는 적어도 하나의 적층 반도체 칩 구조체;

상기 적어도 하나의 서브 반도체 패키지 및 상기 적어도 하나의 적층 반도체 칩 구조체 각각의 측면을 감싸도록 상기 패키지 베이스 기판 상에 형성되는 패키지 몰딩층; 및

열 전달 물질층을 사이에 두고 상기 적어도 하나의 서브 반도체 패키지 및 상기 적어도 하나의 적층 반도체 칩 구조체 상에 부착되는 방열 부재를 포함하며,

상기 관통 전극 영역은,

상기 제1 반도체 칩의 한 변과 대향하는, 상기 적어도 하나의 적층 반도체 칩 구조체의 한 변에 인접하도록 배치되는 반도체 패키지.

## 청구항 14

제13 항에 있어서,

상기 관통 전극 영역은, 상기 적어도 하나의 적층 반도체 칩 구조체의 서로 반대되는 두 변에 인접하도록 배치되며,

상기 적어도 하나의 서브 반도체 패키지는, 상기 관통 전극 영역이 인접하도록 배치되는 상기 적층 반도체 칩 구조체의 서로 반대되는 두 변에 각각 인접하는 제1 서브 반도체 패키지 및 제2 서브 반도체 패키지를 가지는

것을 특징으로 하는 반도체 패키지.

### 청구항 15

제13 항에 있어서,

상기 적어도 하나의 적층 반도체 칩 구조체는, 상기 적어도 하나의 서브 반도체 패키지의 서로 반대되는 두 변에 각각 인접하는 제1 적층 반도체 칩 구조체 및 제2 적층 반도체 칩 구조체를 가지는 것을 특징으로 하는 반도체 패키지.

### 청구항 16

삭제

### 청구항 17

제13 항에 있어서,

상기 열 전달 물질층은,

상기 제1 반도체 칩의 상면 및 상기 복수의 제2 반도체 칩 중 최상단의 제2 반도체 칩의 상면과 접하는 것을 특징으로 하는 반도체 패키지.

### 청구항 18

패키지 베이스 기판;

상기 패키지 베이스 기판 상에 부착되는 제1 반도체 칩;

상기 제1 반도체 칩과 인접하도록 상기 패키지 베이스 기판 상에 부착되며, 복수의 관통 전극을 통하여 전기적으로 연결되도록 수직 적층된 복수의 제2 반도체 칩;

상기 제1 반도체 칩의 측면 및 상기 복수의 제2 반도체 칩의 측면을 감싸도록 상기 패키지 베이스 기판 상에 형성되는 몰딩층; 및

상기 몰딩층 상에 부착되는 방열 부재를 포함하되,

상기 복수의 관통 전극은, 상기 제1 반도체 칩으로부터 열을 방출하도록, 상기 제1 반도체 칩의 한 변과 대향하는 상기 복수의 제2 반도체 칩의 한 변을 따라서 배치되는 반도체 패키지.

### 청구항 19

삭제

### 청구항 20

제18 항에 있어서,

상기 몰딩층은,

상기 패키지 베이스 기판으로부터 동일 레벨인 상기 제1 반도체 칩의 상면과 상기 복수의 제2 반도체 칩 중 최상단의 반도체 칩의 상면을 덮지 않으며,

상기 방열 부재는, 열 전달 물질층을 사이에 두고, 상기 제1 반도체 칩 및 상기 복수의 제2 반도체 칩 상에 부착되는 것을 특징으로 하는 반도체 패키지.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 반도체 패키지에 관한 것으로, 더욱 상세하게는 관통 전극을 이용하여 적층된 복수의 반도체 칩과 이에 인접하도록 배치되는 반도체 칩을 포함하는 반도체 패키지에 관한 것이다.

## 배경기술

- [0002] 전자 산업의 비약적인 발전 및 사용자의 요구에 따라 전자기기는 더욱 더 소형화, 경량화 및 대용량화되고 있다. 이에 따라 메모리 반도체 칩과 MPU/GPU 반도체 칩을 함께 포함하는 반도체 패키지가 개발되고 있다. 또한 반도체 패키지에 포함되는 메모리의 용량을 증가시키기 위하여, 관통 전극을 이용하여 복수의 메모리 반도체 칩을 적층시키는 반도체 패키지도 개발되고 있다.

- [0003] 그러나 하나의 반도체 패키지에 다른 종류의 반도체 칩이 포함됨에 따라, 반도체 패키지 내부의 일부분에서 발열량이 증가하는 문제가 발생하고 있다.

## 발명의 내용

### 해결하려는 과제

- [0004] 본 발명의 기술적 과제는 상기 문제점을 해결하고자, 다른 종류의 반도체 칩이 포함되는 반도체 패키지 내부로부터 발열을 효율적으로 외부로 방출할 수 있는 반도체 패키지를 제공하는 데에 있다.

### 과제의 해결 수단

- [0005] 상기 기술적 과제를 달성하기 위하여, 본 발명은 다음과 같은 반도체 패키지를 제공한다. 본 발명에 따른 반도체 패키지는 패키지 베이스 기판; 상기 패키지 베이스 기판 상에 부착되는 적어도 하나의 제1 반도체 칩; 및 상기 적어도 하나의 제1 반도체 칩과 인접하도록 상기 패키지 베이스 기판 상에 부착되며, 복수의 제2 반도체 칩이 적층된 적어도 하나의 적층 반도체 칩 구조체;를 포함하며, 상기 적어도 하나의 제1 반도체 칩과 인접하는, 상기 적어도 하나의 적층 반도체 칩 구조체의 변에, 복수의 관통 전극이 형성된 관통 전극 영역이 인접하도록 배치된다.

- [0006] 상기 제1 반도체 칩 및 상기 적층 반도체 칩 구조체 각각의 측면을 감싸되 상면을 덮지 않도록 상기 패키지 베이스 기판 상에 형성되는 패키지 몰딩층을 더 포함하며, 상기 제1 반도체 칩의 상면 및 상기 적어도 하나의 적층 반도체 칩 구조체의 상면은 상기 패키지 베이스 기판으로부터 동일 레벨일 수 있다.

- [0007] 상기 반도체 패키지는, 열 전달 물질층(TIM, Thermal Interface Material)을 사이에 두고 상기 제1 반도체 칩 및 상기 적어도 하나의 적층 반도체 칩 구조체 상에 부착되는 방열 부재;를 더 포함할 수 있다.

- [0008] 상기 복수의 제2 반도체 칩 중 최상단의 반도체 칩에 형성된 상기 복수의 관통 전극은 상기 열 전달 물질층과 접할 수 있다.

- [0009] 상기 관통 전극 영역은, 상기 적어도 하나의 제1 반도체 칩의 한 변과 대향하는, 상기 적층 반도체 칩 구조체의 변에 인접하도록 배치될 수 있다.

- [0010] 상기 적어도 하나의 적층 반도체 칩 구조체는 제1 및 제2 적층 반도체 칩 구조체를 포함하며, 상기 제1 및 제2 적층 반도체 칩 구조체 각각의 한 변은, 상기 제1 반도체 칩의 서로 반대되는 양 변과 각각 대향할 수 있다.

- [0011] 상기 적어도 하나의 적층 반도체 칩 구조체는 제1 내지 제4 적층 반도체 칩 구조체를 포함하며, 제1 내지 제4 적층 반도체 칩 구조체 각각의 한 변은, 상기 제1 반도체 칩의 네 변과 각각 대향할 수 있다.

- [0012] 상기 관통 전극 영역은, 상기 적어도 하나의 제1 반도체 칩의 한 변과 대향하는, 상기 적층 반도체 칩 구조체의 꼭지점을 이루는 두 변 중 적어도 한 변에 인접하도록 배치될 수 있다.

- [0013] 상기 적어도 하나의 적층 반도체 칩 구조체는, 제1 내지 제4 적층 반도체 칩 구조체를 가지며, 상기 제1 내지 제4 적층 반도체 칩 구조체 각각은, 상기 제1 반도체 칩의 네 변 각각과 대향하는 꼭지점을 가질 수 있다.

- [0014] 상기 관통 전극 영역은, 상기 적어도 하나의 제1 반도체 칩의 한 변과 대향하는, 상기 적층 반도체 칩 구조체의 꼭지점을 이루는 두 변에 인접하도록 L자 형을 가지며 배치될 수 있다.

- [0015] 상기 적어도 하나의 제1 반도체 칩은, MPU(Micro Processor Unit) 또는 GPU(Graphic Processor Unit)일 수 있다.

- [0016] 상기 제2 반도체 칩은, 메모리 반도체 칩일 수 있다.

- [0017] 상기 복수의 제2 반도체 칩은, 로직 반도체 칩 및 상기 로직 반도체 칩 상에 적층되는 복수의 메모리 반도체 칩

으로 이루어질 수 있다.

[0018] 상기 로직 반도체 칩의 면적은 상기 복수의 메모리 반도체 칩의 면적보다 클 수 있다.

[0019] 상기 적어도 하나의 적층 반도체 칩 구조체는, 상기 복수의 메모리 반도체 칩의 측면을 감싸되, 상기 복수의 메모리 반도체 칩 중 최상단의 메모리 반도체 칩의 상면을 덮지 않도록, 상기 로직 반도체 칩 상에 형성되는 서브 패키지 몰딩층을 더 포함할 수 있다.

[0020] 상기 제1 반도체 칩은, 상기 제2 반도체 칩보다 단위 면적당 발열량이 많을 수 있다.

[0021] 본 발명에 따른 반도체 패키지는, 패키지 베이스 기판; 상기 패키지 베이스 기판 상에 부착되며 제1 반도체 칩을 포함하는 적어도 하나의 서브 반도체 패키지; 상기 적어도 하나의 서브 반도체 패키지와 인접하도록 상기 패키지 베이스 기판 상에 부착되며, 복수의 관통 전극이 형성된 관통 전극 영역을 가지는 복수의 제2 반도체 칩이 적층된 적어도 하나의 적층 반도체 칩 구조체; 상기 서브 반도체 패키지 및 상기 적어도 하나의 적층 반도체 칩 구조체 각각의 측면을 감싸도록 상기 패키지 베이스 기판 상에 형성되는 패키지 몰딩층; 및 열 전달 물질층을 사이에 두고 상기 서브 반도체 패키지 및 상기 적어도 하나의 적층 반도체 칩 구조체 상에 부착되는 방열 부재를 포함하며, 상기 관통 전극 영역은, 상기 적어도 하나의 제1 반도체 칩의 한 변과 대향하는, 상기 적어도 하나의 적층 반도체 칩 구조체의 변에 인접하도록 배치된다.

[0022] 상기 관통 전극 영역은, 상기 적층 반도체 칩 구조체의 서로 반대되는 두 변에 인접하도록 배치되며, 상기 적어도 하나의 서브 반도체 패키지는, 상기 관통 전극 영역이 인접하도록 배치되는 상기 적층 반도체 칩 구조체의 서로 반대되는 두 변에 각각 인접하는 제1 서브 반도체 패키지 및 제2 서브 반도체 패키지를 가질 수 있다.

[0023] 상기 관통 전극 영역은, 상기 적층 반도체 칩 구조체의 네 변에 인접하도록 배치되며, 상기 적어도 하나의 서브 반도체 패키지는, 상기 관통 전극 영역이 인접하도록 배치되는 상기 적층 반도체 칩 구조체의 네 변에 각각 인접하는 제1 내지 제4 서브 반도체 패키지를 가질 수 있다.

[0024] 상기 적어도 하나의 적층 반도체 칩 구조체는, 상기 서브 반도체 패키지의 서로 반대되는 두 변에 각각 인접하는 제1 적층 반도체 칩 구조체 및 제2 적층 반도체 칩 구조체를 가질 수 있다.

[0025] 상기 적어도 하나의 적층 반도체 칩 구조체는, 상기 서브 반도체 패키지의 네 변에 각각 인접하는 제1 내지 제4 적층 반도체 칩 구조체를 가질 수 있다.

[0026] 상기 서브 반도체 패키지는, 서브 패키지 베이스 기판, 상기 서브 패키지 베이스 기판 상에 부착되는 상기 제1 반도체 칩 및 상기 제1 반도체 칩의 측면을 감싸되 상면을 덮지 않도록 상기 서브 패키지 베이스 기판 상에 형성되는 서브 패키지 몰딩층을 포함할 수 있다.

[0027] 상기 제1 반도체 칩의 상면 및 상기 복수의 제2 반도체 칩 중 최상단의 반도체 칩의 상면은 상기 패키지 베이스 기판으로부터 동일 레벨일 수 있다.

[0028] 상기 열 절단 물질층은, 상기 제1 반도체 칩의 상면 및 상기 복수의 제2 반도체 칩 중 최상단의 반도체 칩의 상면과 접할 수 있다.

[0029] 상기 복수의 제2 반도체 칩은, 로직 반도체 칩 및 상기 로직 반도체 칩 상에 적층되는 복수의 DRAM 반도체 칩으로 이루어지며, 상기 로직 반도체 칩은 상기 복수의 DRAM 반도체 칩을 제어하기 위한 콘트롤러 칩일 수 있다.

[0030] 본 발명에 따른 반도체 패키지는, 패키지 베이스 기판; 상기 베이스 기판 상에 부착되는 제1 반도체 칩; 상기 제1 반도체 칩과 인접하도록 상기 베이스 기판 상에 부착되며, 복수의 관통 전극을 통하여 전기적으로 연결되도록 수직 적층된 복수의 제2 반도체 칩; 상기 제1 반도체 칩의 측면 및 상기 복수의 제2 반도체 칩의 측면을 감싸도록 상기 패키지 베이스 기판 상에 형성되는 몰딩층; 및 상기 몰딩층 상에 부착되는 방열 부재를 포함하되, 상기 복수의 제2 반도체 칩을 전기적으로 연결하는 상기 복수의 관통 전극은, 상기 제1 반도체 칩과 인접하는, 상기 복수의 제2 반도체 칩의 변을 따라서 배치된다.

[0031] 상기 복수의 관통 전극은, 상기 제1 반도체 칩의 한 변과 대향하는 상기 복수의 제2 반도체 칩의 변을 따라서 배치될 수 있다.

[0032] 상기 몰딩층은, 상기 패키지 베이스 기판으로부터 동일 레벨인 상기 제1 반도체 칩의 상면과 상기 복수의 제2 반도체 칩 중 최상단의 반도체 칩의 상면을 덮지 않으며, 상기 방열 부재는, 열 전달 물질층을 사이에 두고, 상기 제1 반도체 칩 및 상기 복수의 제2 반도체 칩 상에 부착될 수 있다.

[0033] 상기 복수의 관통 전극은, 상기 열 전달 물질층에 의하여 상기 방열 부재와 전기적으로 절연될 수 있다.

[0034] 상기 복수의 관통 전극은, 상기 복수의 제2 반도체 칩을 위한 신호, 전원 또는 그라운드 중 적어도 하나를 제공할 수 있다.

### 발명의 효과

[0035] 본 발명에 따른 반도체 패키지는, 적층 반도체 칩 구조체의 관통 전극 영역을 발열량이 많은 반도체 칩에 인접하도록 배치하여, 반도체 패키지 내부에서 발생할 수 있는 부분적인 열집중 현상을 방지할 수 있고, 이에 따라서 반도체 패키지의 동작 신뢰성을 얻을 수 있다.

### 도면의 간단한 설명

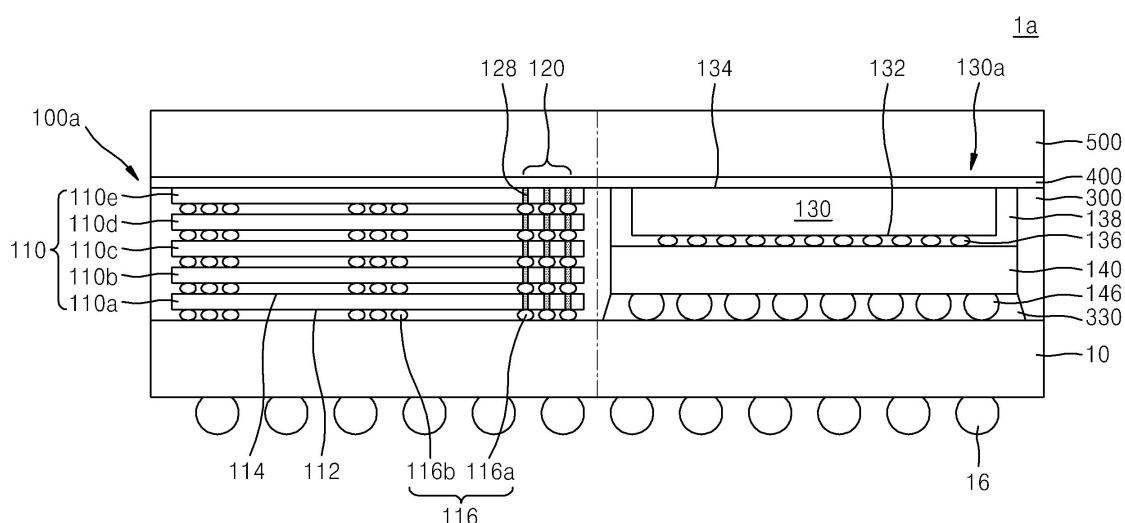

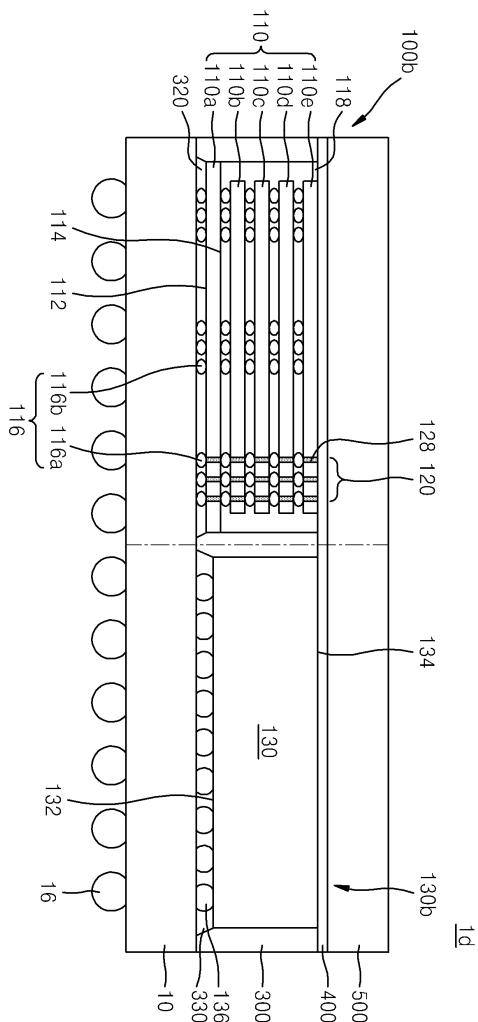

[0036] 도 1은 본 발명의 일 실시 예에 따른 반도체 패키지를 나타내는 단면도이다.

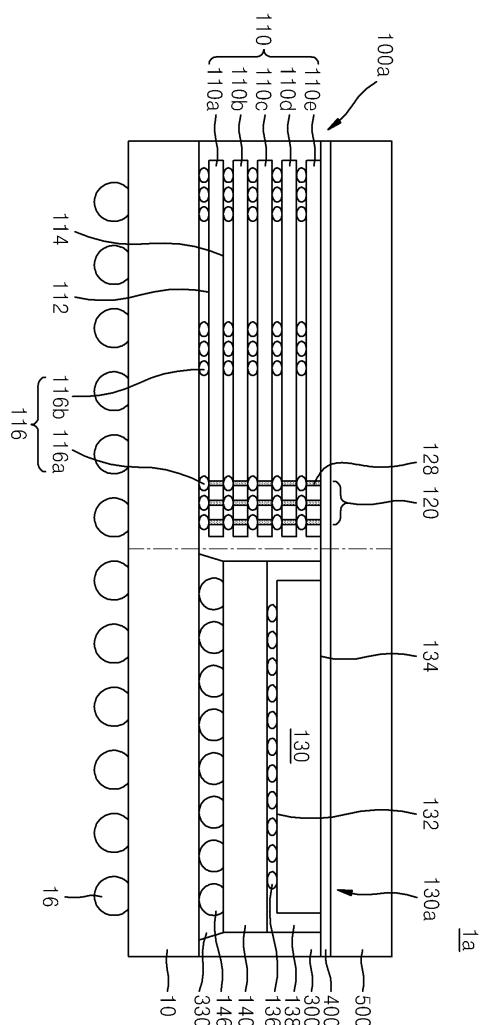

도 2는 본 발명의 일 실시 예에 따른 반도체 패키지를 나타내는 단면도이다.

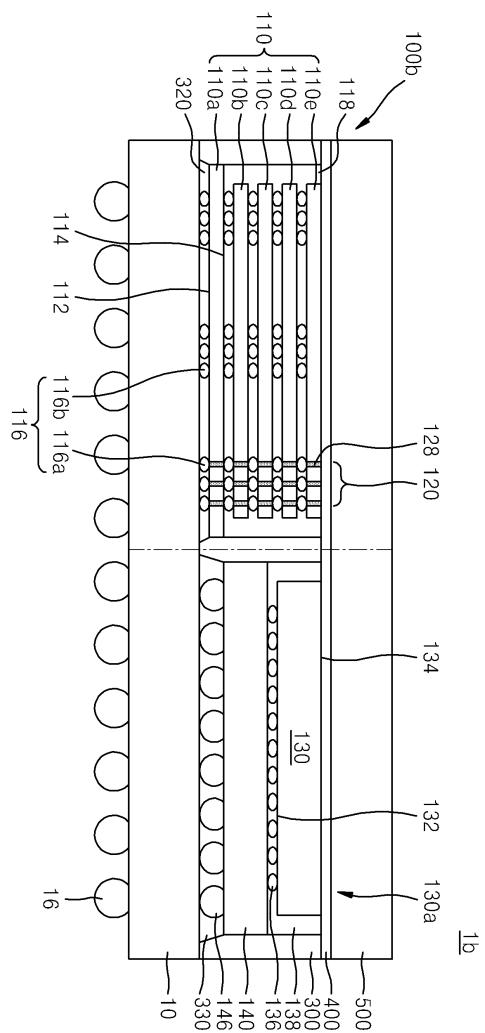

도 3은 본 발명의 일 실시 예에 따른 반도체 패키지를 나타내는 단면도이다.

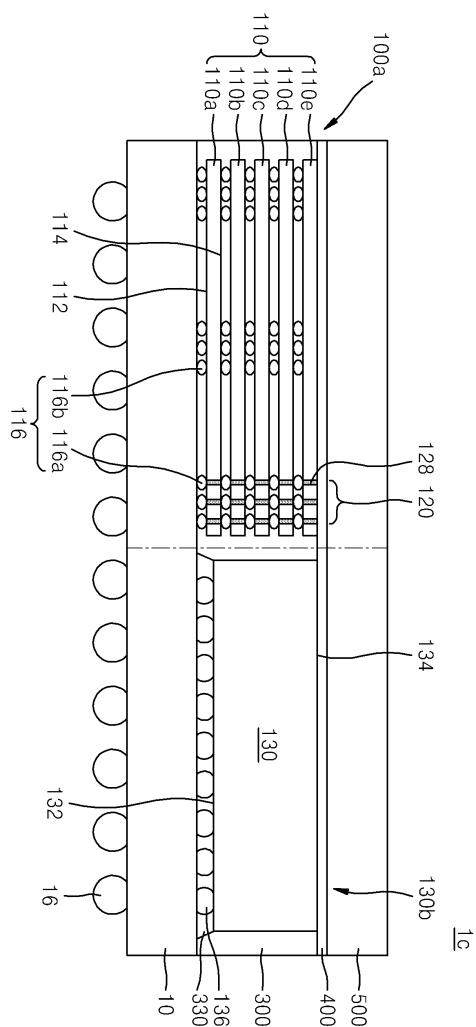

도 4는 본 발명의 일 실시 예에 따른 반도체 패키지를 나타내는 단면도이다.

도 5는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 6은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 7은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 8은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 9는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 10은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 11은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 12는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 13은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 14는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 15는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 16은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

도 17은 본 발명의 일 실시 예에 따른 반도체 패키지의 구성을 개략적으로 나타내는 도면이다.

도 18은 본 발명의 일 실시 예에 따른 반도체 패키지를 포함하는 전자 시스템을 나타내는 도면이다.

도 19는 본 발명의 실시 예에 따른 반도체 패키지가 응용된 전자 장치를 개략적으로 보여주는 사시도이다.

## 발명을 실시하기 위한 구체적인 내용

[0037]

본 발명의 구성 및 효과를 충분히 이해하기 위하여, 첨부한 도면을 참조하여 본 발명의 바람직한 실시 예들을 설명한다. 그러나 본 발명은 이하에서 개시되는 실시 예들에 한정되는 것이 아니라, 여러 가지 형태로 구현될 수 있고 다양한 변경을 가할 수 있다. 단지, 본 실시 예들에 대한 설명은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술 분야의 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위하여 제공되는 것이다. 첨부된 도면에서 구성 요소들은 설명의 편의를 위하여 그 크기를 실제보다 확대하여 도시한 것이며, 각 구성 요소의 비율은 과장되거나 축소될 수 있다.

[0038]

어떤 구성 요소가 다른 구성 요소에 "상에" 있다거나 "접하여" 있다고 기재된 경우, 다른 구성 요소에 상에 직접 맞닿아 있거나 또는 연결되어 있을 수 있지만, 중간에 또 다른 구성 요소가 존재할 수 있다고 이해되어야 할 것이다. 반면, 어떤 구성 요소가 다른 구성 요소의 "바로 위에" 있다거나 "직접 접하여" 있다고 기재된 경우에 는, 중간에 또 다른 구성 요소가 존재하지 않는 것으로 이해될 수 있다. 구성 요소들 간의 관계를 설명하는 다른 표현들, 예를 들면, "~사이에"와 "직접 ~사이에" 등도 마찬가지로 해석될 수 있다.

[0039]

제1, 제2 등의 용어는 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안된다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로만 사용될 수 있다. 예를 들어, 본 발명의 권리 범위를 벗어나지 않으면서 제1 구성요소는 제2 구성요소로 명명될 수 있고, 유사하게 제2 구성요소도 제1 구성요소로 명명될 수 있다.

[0040]

단수의 표현은 문맥상 명백하게 다르게 표현하지 않는 한, 복수의 표현을 포함한다. "포함한다" 또는 "가진다" 등의 용어는 명세서 상에 기재된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하기 위한 것으로, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들이 부가될 수 있는 것으로 해석될 수 있다.

[0041]

본 발명의 명세서에서, 특별한 언급이 없는 한 변과 꼭지점이라는 용어는 평면 배치도를 기준으로 2차원으로 나타낸 구성 요소의 변과 꼭지점을 의미한다. 예를 들어, 구성 요소가 직육면체의 형상을 가지는 경우, 변이란 용어는 측면을 의미하고 꼭지점이란 용어는 2개의 측면이 이루는 모서리를 의미한다.

[0042]

본 발명의 실시 예들에서 사용되는 용어들은 다르게 정의되지 않는 한, 해당 기술 분야에서 통상의 지식을 가진 자에게 통상적으로 알려진 의미로 해석될 수 있다.

[0043]

이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시 예를 설명함으로써 본 발명을 상세히 설명한다.

[0044]

도 1은 본 발명의 일 실시 예에 따른 반도체 패키지를 나타내는 단면도이다.

[0045]

도 1을 참조하면, 반도체 패키지(1a)는 패키지 베이스 기판(10), 서브 반도체 패키지(130a) 및 적층 반도체 칩 구조체(100a)를 포함한다. 서브 반도체 패키지(130a)와 적층 반도체 칩 구조체(100a)는 서로 인접하도록 패키지 베이스 기판(10) 상에 부착될 수 있다.

[0046]

패키지 베이스 기판(10)은 예를 들면, 인쇄회로기판, 세라믹 기판 또는 인터포저(interposer)일 수 있다.

[0047]

패키지 베이스 기판(10)이 인쇄회로기판인 경우, 패키지 베이스 기판(10)은 기판 베이스, 그리고 상면 및 하면에 각각 형성된 상면 패드(도시 생략) 및 하면 패드(도시 생략)를 포함할 수 있다. 상기 상면 패드 및 상기 하면 패드는 각각 상기 기판 베이스의 상면 및 하면을 덮는 솔더레지스트층(도시 생략)에 의하여 노출될 수 있다. 상기 기판 베이스는 폐놀 수지, 에폭시 수지, 폴리이미드 중에서 선택되는 적어도 하나의 물질로 이루어질 수 있다. 예를 들면, 상기 기판 베이스는 FR4, 사관능성 에폭시(Tetrafunctional epoxy), 폴리페닐렌 에테르(Polyphenylene ether), 에폭시/폴리페닐렌 옥사이드(Epoxy/polyphenylene oxide), BT(Bismaleimide triazine), 써마운트(Thermount), 시아네이트 에스터(Cyanate ester), 폴리이미드(Polyimide) 및 액정 고분자(Liquid crystal polymer) 중에서 선택되는 적어도 하나의 물질을 포함할 수 있다. 상기 상면 패드 및 하면 패드는 구리, 니켈, 스테인레스 스틸 또는 베릴륨구리(beryllium copper)로 이루어질 수 있다. 상기 기판 베이스 내에는 상기 상면 패드와 상기 하면 패드를 전기적으로 연결되는 내부 배선(도시 생략)이 형성될 수 있다. 상기 상면 패드 및 상기 하면 패드는 상기 기판 베이스의 상면 및 하면에 동박(Cu foil)을 입힌 후 패터닝된 회로 배선 중 각각 상기 솔더레지스트층에 의하여 노출된 부분일 수 있다.

[0048]

패키지 베이스 기판(10)이 인터포저인 경우, 패키지 베이스 기판(10)은 반도체 물질로 이루어진 기판 베이스 및 상기 기판 베이스의 상면 및 하면에 각각 형성된 상면 패드(도시 생략) 및 하면 패드(도시 생략)를 포함할 수

있다. 상기 기판 베이스는 예를 들면, 실리콘 웨이퍼로부터 형성될 수 있다. 또한 상기 기판 베이스의 상면, 하면 또는 내부에는 내부 배선(도시 생략)이 형성될 수 있다. 또한 상기 기판 베이스의 내부에는 상기 상면 패드와 상기 하면 패드를 전기적으로 연결하는 관통 비아(도시 생략)이 형성될 수 있다.

[0049] 패키지 베이스 기판(10)의 하면에는 외부 연결 단자(16)가 부착될 수 있다. 외부 연결 단자(16)는 예를 들면, 상기 하면 패드 상에 부착될 수 있다. 외부 연결 단자(16)는 예를 들면, 솔더볼 또는 범프일 수 있다. 외부 연결 단자(16)는 반도체 패키지(1a)와 외부 장치 사이를 전기적으로 연결할 수 있다.

[0050] 서브 반도체 패키지(130a)는 서브 패키지 베이스 기판(140), 서브 패키지 베이스 기판(140) 상에 부착되는 제1 반도체 칩(130)을 포함할 수 있다. 제1 반도체 칩(130)은 활성면(132)이 서브 패키지 베이스 기판(140)을 향하도록, 서브 패키지 베이스 기판(140) 상에 부착될 수 있다. 제1 반도체 칩(130)은 활성면(132) 상에 배치된 제1 연결 단자(136)에 의하여 서브 패키지 베이스 기판(140)과 전기적으로 연결될 수 있다. 제1 연결 단자(136)는 예를 들면, 솔더볼 또는 범프일 수 있다. 서브 반도체 패키지(130a)는 제1 반도체 칩(130)의 측면을 감싸도록 서브 패키지 베이스 기판(140) 상에 형성되는 제1 서브 패키지 몰딩층(138)을 더 포함할 수 있다. 제1 서브 패키지 몰딩층(138)은 제1 반도체 칩(130)의 상면, 즉 비활성면(134)을 덮지 않을 수 있다. 제1 서브 패키지 몰딩층(138)은 제1 반도체 칩(130)과 서브 패키지 베이스 기판(140) 사이의 공간을 채우도록 형성될 수 있다. 제1 서브 패키지 몰딩층(138)은 예를 들면, EMC(Epoxy Mold Compound)로 이루어질 수 있다. 제1 서브 패키지 몰딩층(138)은 후술할 패키지 몰딩층(300)과 함께 형성될 수도 있다.

[0051] 서브 패키지 베이스 기판(140)은 예를 들면, 인쇄회로기판일 수 있다. 서브 패키지 베이스 기판(140)이 인쇄회로기판인 경우, 서브 패키지 베이스 기판(140)은 상술한 패키지 베이스 기판(10)이 인쇄회로기판인 경우와 유사한 구성을 포함할 수 있는 바, 자세한 설명은 생략하도록 할 수 있다.

[0052] 서브 패키지 베이스 기판(140)의 하면에는 제1 내부 연결 단자(146)가 부착될 수 있다. 제1 내부 연결 단자(146)는 예를 들면, 솔더볼 또는 범프일 수 있다. 제1 내부 연결 단자(146)는 서브 반도체 패키지(130a)와 패키지 베이스 기판(10) 사이를 전기적으로 연결할 수 있다. 서브 반도체 패키지(130a)와 패키지 베이스 기판(10) 사이의 공간을 채우도록 제1 언더필 물질층(330)이 형성될 수 있다. 제1 언더필 물질층(330)은 예를 들면, 에폭시 수지로 이루어질 수 있다. 제1 언더필 물질층(330)은 예를 들면, MUF(Molded Under-fil) 방식으로 형성되는 후술할 물질층(300)의 일부분일 수 있다.

[0053] 제1 반도체 칩(130)을 이루는 반도체 기판은 예를 들면, 실리콘(Si, silicon)을 포함할 수 있다. 또는 제1 반도체 칩(130)을 이루는 반도체 기판은 저마늄(Ge, germanium)과 같은 반도체 원소, 또는 SiC (silicon carbide), GaAs(gallium arsenide), InAs (indium arsenide), 및 InP (indium phosphide)와 같은 화합물 반도체를 포함할 수 있다. 또는 제1 반도체 칩(130)을 이루는 반도체 기판은 SOI (silicon on insulator) 구조를 가질 수 있다. 예를 들면, 제1 반도체 칩(130)을 이루는 반도체 기판은 BOX 층(buried oxide layer)을 포함할 수 있다. 제1 반도체 칩(130)을 이루는 반도체 기판은 도전 영역, 예를 들면 불순물이 도핑된 웰 (well)을 포함할 수 있다. 제1 반도체 칩(130)을 이루는 반도체 기판은 STI (shallow trench isolation) 구조와 같은 다양한 소자분리 구조를 가질 수 있다.

[0054] 제1 반도체 칩(130)은 다양한 종류의 복수의 개별 소자 (individual devices)를 포함하는 반도체 소자가 형성될 수 있다. 상기 복수의 개별 소자 다양한 미세 전자 소자 (microelectronic devices), 예를 들면 CMOS 트랜지스터 (complementary metal-insulator-semiconductor transistor) 등과 같은 MOSFET (metal-oxide-semiconductor field effect transistor), 시스템 LSI (large scale integration), CIS (CMOS imaging sensor) 등과 같은 이미지 센서, MEMS (micro-electro-mechanical system), 능동 소자, 수동 소자 등을 포함할 수 있다. 상기 복수의 개별 소자는 제1 반도체 칩(130)을 이루는 반도체 기판의 상기 도전 영역에 전기적으로 연결될 수 있다. 상기 반도체 소자는 상기 복수의 개별 소자 중 적어도 2개, 또는 상기 복수의 개별 소자와 제1 반도체 칩(130)을 이루는 반도체 기판의 상기 도전 영역을 전기적으로 연결하는 도전성 배선 또는 도전성 플러그를 더 포함할 수 있다. 또한, 상기 복수의 개별 소자는 각각 절연막에 의하여 이웃하는 다른 개별 소자들과 전기적으로 분리될 수 있다.

[0055] 제1 반도체 칩(130)은 프로세스 유닛(Processor Unit)일 수 있다. 제1 반도체 칩(130)은 예를 들면, MPU(Micro Processor Unit) 또는 GPU(Graphic Processor Unit)일 수 있다. 서브 반도체 패키지(130a)는 예를 들면, 정상 동작이 검증된 KGP(Known Good Package)일 수 있다.

[0056] 적층 반도체 칩 구조체(100a)는 순차적으로 적층된 복수의 제2 반도체 칩(110)을 포함할 수 있다. 복수의 제2

반도체 칩(110)은 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)이 수직 방향으로 적층될 수 있다. 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e) 각각을 이루는 반도체 기판 및 형성된 반도체 소자는 제1 반도체 칩(130)을 이루는 반도체 기판과 유사한 바, 자세한 설명은 생략하도록 한다. 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e) 각각은 활성면(112)이 패키지 베이스 기판(10)을 향할 수 있다.

[0057] 본 발명의 명세서에서 '복수의 제2 반도체 칩'이라 함은, '하나의 적층 반도체 칩 구조체'를 이루도록 수직 방향으로 적층된 반도체 칩들을 의미한다. 따라서 2개 이상의 적층 반도체 칩 구조체가 있는 경우, 각 적층 반도체 칩 구조체는 각각 '복수의 제2 반도체 칩'을 포함하며, 특별한 언급이 없는 한 '복수의 제2 반도체 칩'이라는 기재는 2개 이상의 적층 반도체 칩 구조체에 포함되는 반도체 칩들을 함께 지칭하는 것이 아니고, '하나의 적층 반도체 칩 구조체에 포함되는 반도체 칩들만을 지칭한다. 이는 '복수의 제2 반도체 칩'이 수직 방향으로 적층된 '하나의 적층 반도체 칩 구조체'를 마치 하나의 반도체 칩인 것처럼 취급할 수 있기 때문이다.

[0058] 복수의 제2 반도체 칩(110)은 예를 들면, 메모리 반도체 칩일 수 있다. 메모리 반도체 칩은 예를 들면, DRAM(Dynamic Random Access Memory) 또는 SRAM(Static Random Access Memory)과 같은 휘발성 메모리 반도체 칩이거나, PRAM(Phase-change Random Access Memory), MRAM(Magnetoresistive Random Access Memory), FeRAM(Ferroelectric Random Access Memory) 또는 RRAM(Resistive Random Access Memory)과 같은 비휘발성 메모리 반도체 칩일 수 있다.

[0059] 복수의 제2 반도체 칩(110) 중 적어도 하나는 로직 반도체 칩이고, 나머지는 메모리 반도체 칩일 수 있다. 예를 들면, 복수의 제2 반도체 칩(110) 중 최하단의 반도체 칩(110a)은 로직 반도체 칩이고, 나머지 반도체 칩(110b, 110c, 110d, 110e)은 메모리 반도체 칩일 수 있다. 예를 들면, 복수의 제2 반도체 칩(110) 중 최하단의 반도체 칩(110a)은 나머지 반도체 칩(110b, 110c, 110d, 110e)을 제어하기 위한 콘트롤러 칩일 수 있고, 나머지 반도체 칩(110b, 110c, 110d, 110e)은 HBM(High Bandwidth Memory) DRAM 반도체 칩일 수 있다.

[0060] 도 1에는 복수의 제2 반도체 칩(110)에 5개의 반도체 칩들((110a, 110b, 110c, 110d, 110e)이 포함되는 것으로 도시되었으나, 이에 한정되지 않으며, 2개 내지 4개 또는 6개 이상의 반도체 칩이 포함될 수 있다. 복수의 제2 반도체 칩(110)이 모두 메모리 반도체 칩인 경우, 복수의 제2 반도체 칩(110)은 2의 배수 개일 수 있다. 복수의 제2 반도체 칩(110) 중 적어도 하나는 로직 반도체 칩이고, 나머지는 메모리 반도체 칩인 경우, 복수의 제2 반도체 칩(110)에 포함되는 메모리 반도체 칩은 2의 배수 개일 수 있다. 복수의 제2 반도체 칩(110)에 포함되는 메모리 반도체 칩은 모두 동종의 메모리 반도체 칩일 수 있다.

[0061] 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)은 각각 복수의 관통 전극(128)을 포함할 수 있다. 복수의 관통 전극(128)은 관통 전극 영역(120)에 형성될 수 있다. 관통 전극 영역(120)에는 예를 들면, 수백 개 내지 수천 개의 관통 전극(128)이 형성될 수 있다. 관통 전극 영역(120)에 형성되는 복수의 관통 전극(128)은 예를 들면, 수십  $\mu\text{m}$ 의 피치(pitch)를 가지고 매트릭스 배열로 배치될 수 있다. 복수의 관통 전극(128)은 예를 들면, 각각 수  $\mu\text{m}$  내지 수십  $\mu\text{m}$ 의 직경을 가질 수 있다. 복수의 관통 전극(128) 각각의 직경은 복수의 관통 전극(128)들이 배치되는 피치보다 작은 값을 가질 수 있다. 예를 들면, 복수의 관통 전극(128)은 5  $\mu\text{m}$  내지 15  $\mu\text{m}$ 의 직경을 가지며, 25  $\mu\text{m}$  내지 50  $\mu\text{m}$ 의 피치를 가지고 배치될 수 있다.

[0062] 관통 전극 영역(120)은 적층 반도체 칩 구조체(100a)의 적어도 하나의 변에 인접하도록 배치될 수 있다. 관통 전극 영역(120)은 제1 반도체 칩(130)과 인접하는 적층 반도체 칩 구조체(100a)의 변 또는 꼭지점에 인접하도록 배치될 수 있다.

[0063] 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)은 서로 대응되는 관통 전극(128)에 의하여 서로 전기적으로 연결될 수 있다. 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)은 복수의 관통 전극(128)에 의하여 패키지 베이스 기판(10)과 전기적으로 연결될 수 있다. 복수의 관통 전극(128)은 복수의 제2 반도체 칩(110)을 위한 신호, 전원 또는 그라운드 중 적어도 하나를 제공할 수 있다.

[0064] 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e) 각각의 하면에는 관통 전극(128)과 연결되는 제2 연결 단자(116a)가 부착될 수 있다. 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e) 각각의 하면에는 더미 연결 단자(116b)가 더 부착될 수 있다. 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)은 제2 연결 단자(116a) 및 더미 연결 단자(116b)를 포함하는 연결 단자군(116)에 의하여 지지될 수 있다. 더미 연결 단자

(116b)는 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)과 전기적으로 절연될 수 있다.

[0065] 제2 연결 단자(116a)는 예를 들면 수십  $\mu\text{m}$ 의 직경을 가질 수 있다. 제2 연결 단자(116a)의 직경은 관통 전극(128)의 직경보다 크고, 복수의 관통 전극(128)이 배치되는 폐치보다 작은 값을 가질 수 있다. 예를 들면, 제2 연결 단자(116a)는 약 20  $\mu\text{m}$ 의 직경을 가질 수 있다.

[0066] 관통 전극(128)은 TSV(Through Silicon Via)로 형성될 수 있다. 관통 전극(128)은 배선 금속층(도시 생략) 및 이를 둘러싸는 장벽 금속층(도시 생략)을 포함할 수 있다. 상기 배선 금속층은 Cu 또는 W을 포함할 수 있다. 예를 들면, 상기 배선 금속층은 Cu, CuSn, CuMg, CuNi, CuZn, CuPd, CuAu, CuRe, CuW, W, 또는 W 합금으로 이루어질 수 있으나, 이에 제한되는 것은 아니다. 예컨대, 상기 배선 금속층은 Al, Au, Be, Bi, Co, Cu, Hf, In, Mn, Mo, Ni, Pb, Pd, Pt, Rh, Re, Ru, Ta, Te, Ti, W, Zn, Zr 중의 하나 또는 그 이상을 포함할 수 있고, 하나 또는 둘 이상의 적층 구조를 포함할 수 있다. 상기 장벽 금속층은 W, WN, WC, Ti, TiN, Ta, TaN, Ru, Co, Mn, WN, Ni, 또는 NiB 중에서 선택되는 적어도 하나의 물질을 포함할 수 있고 단일층 또는 다중층으로 이루어질 수 있다. 그러나 관통 전극(128)의 재질이 상기의 물질에 한정되는 것은 아니다. 상기 장벽 금속층 및 배선 금속층은 PVD(physical vapor deposition) 공정 또는 CVD(chemical vapor deposition) 공정에 의해 형성될 수 있으나, 이에 한정되는 것은 아니다. 관통 전극(128)과 복수의 제2 반도체 칩(110) 각각을 이루는 반도체 기판 사이에는 스페이서 절연층(도시 생략)이 개재될 수 있다. 상기 스페이서 절연층은 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)에 형성된 반도체 소자 관통 전극(128)이 직접 접촉되는 것을 막아줄 수 있다. 상기 스페이서 절연층은 산화막, 질화막, 탄화막, 폴리머, 또는 이들의 조합으로 이루어질 수 있다. 일부 실시예들에서, 상기 스페이서 절연층을 형성하기 위하여 CVD 공정을 이용할 수 있다. 상기 스페이서 절연층은 저압 CVD(sub-atmospheric CVD) 공정에 의해 형성된 O<sub>3</sub>/TEOS(ozone/tetra-ethyl ortho-silicate) 기반의 HARP(high aspect ratio process) 산화막으로 이루어질 수 있다.

[0067] 관통 전극(128)은 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)의 활성면(112)과 비활성면(114) 사이를 직접 연결하는 것으로 개시되었으나, 이에 한정되지 않으며, 비아-퍼스트(Via-first), 비아-미들(Via-middle) 또는 비아-라스트(Via-last) 구조 중 어느 하나로 형성될 수 있음을 물론이다. 비아-퍼스트, 비아-미들, 또는 비아-라스트 구조 및 제조 방법에 대해서는 Springer에서 2011년 출간된 Three Dimensional System Integration, CRC Press에서 2012년 출간된 3D Integration for VLSI Systems, Springer에서 2013년 출간된 Designing TSVs for 3D Integrated Circuits 등의 도서를 비롯한 다수의 문헌에 개시된 바, 자세한 설명은 생략하도록 한다.

[0068] 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)의 활성면(112)과 비활성면(114)에는 각각 관통 전극(128)과 전기적으로 연결되는 전면 패드(도시 생략) 및 후면 패드(도시 생략)이 형성될 수 있다. 상기 전면 패드 및 상기 후면 패드는 관통 전극(128)에 대응되는 위치에 형성되어 관통 전극(128)과 전기적으로 연결될 수 있으나, 이에 제한되지 않으며, 관통 전극(128)부터 떨어진 위치에 형성되어, 재배선층을 통하여 관통 전극(128)과 전기적으로 연결될 수도 있다.

[0069] 패키지 베이스 기판(10) 상에는 제1 반도체 칩(130)을 포함하는 서브 반도체 패키지(130a) 및 적층 반도체 칩 구조체(100a) 각각의 측면을 감싸는 패키지 몰딩층(300)이 더 형성될 수 있다. 패키지 몰딩층(300)은 예를 들면, EMC로 이루어질 수 있다. 패키지 몰딩층(300)은 제1 서브 패키지 몰딩층(138)과 함께 형성될 수도 있다. 패키지 몰딩층(300)은 서브 반도체 패키지(130a)의 상면 및 적층 반도체 칩 구조체(100a)의 상면을 덮지 않도록 형성될 수 있다. 예를 들면, 패키지 몰딩층(300)은 서브 반도체 패키지(130a)에 포함되는 제1 반도체 칩(130)의 상면 및 적층 반도체 칩 구조체(100a)에 포함되는 복수의 제2 반도체 칩(110) 중 최상단의 반도체 칩(110e)의 상면을 덮지 않도록 형성될 수 있다.

[0070] 제1 반도체 칩(130)의 상면과 복수의 제2 반도체 칩(110) 중 최상단의 반도체 칩(110e)의 상면은 패키지 베이스 기판(10)으로부터 동일 레벨을 가질 수 있다. 예를 들면, 제1 반도체 칩(130)과 복수의 제2 반도체 칩(110) 중 최상단의 반도체 칩(110e)이 상대적으로 큰 두께를 가지는 상태로 패키지 베이스 기판(10) 상에 부착하고, 패키지 몰딩층(300)이 제1 반도체 칩(130)과 복수의 제2 반도체 칩(110) 중 최상단의 반도체 칩(110e)의 덩도록 형성한 후 제1 반도체 칩(130)과 복수의 제2 반도체 칩(110) 중 최상단의 반도체 칩(110e)의 상면이 모두 노출될 때까지 패키지 몰딩층(300)의 상측 일부분을 제거하여, 제1 반도체 칩(130)의 상면과 복수의 제2 반도체 칩(110) 중 최상단의 반도체 칩(110e)의 상면이 패키지 베이스 기판(10)으로부터 동일 레벨을 가지도록 할 수 있다. 이 경우, 제1 반도체 칩(130)의 상면, 복수의 제2 반도체 칩(110) 중 최상단의 반도체 칩(110e)의 상면, 및

패키지 몰딩층(300)의 상면은 패키지 베이스 기판(10)으로부터 모두 동일 레벨을 가질 수 있다.

[0071] 제1 반도체 칩(130)을 포함하는 서브 반도체 패키지(130a) 및 적층 반도체 칩 구조체(100a) 상에는 열 전달 물질층(400, TIM, Thermal Interface Material)을 형성한다. 열 전달 물질층(400)은 제1 반도체 칩(130)의 상면, 복수의 제2 반도체 칩(110) 중 최상단의 반도체 칩(110e)의 상면, 및 패키지 몰딩층(300)의 상면을 덮을 수 있다. 열 전달 물질층(400)은 절연 물질로 이루어지거나, 절연 물질을 포함하여 전기적 절연성을 유지할 수 있는 물질로 이루어질 수 있다. 열 전달 물질층(400)은 예를 들면, 에폭시 수지를 포함할 수 있다. 열 전달 물질층(400)은 예를 들면, 미네랄 오일(mineral oil), 그리스(grease), 갭 필러 퍼티(gap filler putty), 상변화 젤(phase change gel), 상변화물질 패드(hase change Material pads) 또는 분말 충전 에폭시(particle filled epoxy)일 수 있다.

[0072] 방열 부재(500)은 열 전달 물질층(400)을 사이에 두고 제1 반도체 칩(130) 및 적층 반도체 칩 구조체(100a) 상에 부착될 수 있다. 방열 부재(500)은 예를 들면, 히트 싱크(heat sink), 히트 스프레더(heat spreader), 히트 파이프(heat pipe), 또는 수냉식 냉각판(liquid cooled cold plate)일 수 있다.

[0073] 반도체 패키지(1a)는 패키지 베이스 기판(10) 상에 제1 반도체 칩(130)을 포함하는 서브 반도체 패키지(130a)와 복수의 제2 반도체 칩(110)을 포함하는 적층 반도체 칩 구조체(100a)를 인접하도록 배치시키고, 이를 상에 열 전달 물질층(400)과 방열 부재(500)를 부착하여 형성할 수 있다.

[0074] 복수의 제2 반도체 칩(110) 중 최상단의 반도체 칩(100e)에 형성된 복수의 관통 전극(128)은 열 전달 물질층(400)과 접할 수 있다. 방열 부재(500)가 도전성인 경우, 복수의 관통 전극(128)은 열 전달 물질층(400)에 의하여 방열 부재(500)와 전기적으로 절연될 수 있다.

[0075] 관통 전극 영역(120)은 제1 반도체 칩(130)과 인접하는 복수의 제2 반도체 칩(110)을 포함하는 적층 반도체 칩 구조체(100a)의 꼭지점 또는 적어도 한 변에 인접하도록 배치될 수 있다. 예를 들면, 관통 전극 영역(120)은 제1 반도체 칩(130)의 한 변과 대향하는 적층 반도체 칩 구조체(100a)의 꼭지점 또는 적어도 한 변에 인접하도록 배치될 수 있다.

[0076] 서브 반도체 패키지(130a)는 적층 반도체 칩 구조체(100a)보다 단위 면적당 발열량(W/cm<sup>2</sup>)이 많을 수 있다. 구체적으로 제1 반도체 칩(130)은 복수의 제2 반도체 칩(110)보다 단위 면적당 발열량이 많을 수 있다. 제1 반도체 칩(130)이 예를 들면, MPU(Micro Processor Unit) 또는 GPU(Graphic Processor Unit)이고, 복수의 제2 반도체 칩(110)이 메모리 반도체 칩을 포함하는 경우, 제1 반도체 칩(130)은 복수의 제2 반도체 칩(110)에 비하여 전력 소모가 많고 발열량이 많을 수 있다. 따라서 반도체 패키지(1a) 내의 발열량은 제1 반도체 칩(130)에 상대적으로 집중될 수 있다.

[0077] 제1 반도체 칩(130)에서 발생한 열 중 일부는 제1 반도체 칩(130)의 비활성면(134)에서 열 전달 물질층(400) 및 방열 부재(500)를 통하여 반도체 패키지(1a)의 외부로 방출될 수 있다. 제1 반도체 칩(130)의 측면을 통하여 방출되는 열은 반도체 패키지(1a)의 외부로의 방출 경로가 상대적으로 길기 때문에 쉽게 외부로 방출될 수 없고, 이에 따라 반도체 패키지(1a) 내부에서 부분적인 열집중 현상이 발생할 수 있다. 그러나 적층 반도체 칩 구조체(100a)의 관통 전극 영역(120)을 제1 반도체 칩(130)에 인접하도록 배치하면, 제1 반도체 칩(130)의 측면을 통하여 방출되는 열은 관통 전극 영역(120)의 관통 전극(128)을 거쳐서 열 전달 물질층(400) 및 방열 부재(500)를 통하여 빠르게 반도체 패키지(1a)의 외부로 방출될 수 있기 때문에 반도체 패키지(1a) 내부에서 발생할 수 있는 부분적인 열집중 현상을 방지할 수 있고, 이에 따라서 반도체 패키지(1a)의 동작 신뢰성을 얻을 수 있다.

[0078] 도 1에서는 반도체 패키지(1a)에 포함되는 1개의 서브 반도체 패키지(130a)와 1개의 적층 반도체 칩 구조체(100a)만을 도시하였으나, 이는 관통 전극 영역(120)과 1개의 서브 반도체 패키지(130a)와의 배치를 설명하기 위한 것으로, 본 발명의 기술적 사상은 이에 한정되지 않는다. 예를 들면, 반도체 패키지(1a)는 복수의 1개의 서브 반도체 패키지(130a) 및/또는 복수의 적층 반도체 칩 구조체(100a)를 포함할 수 있다.

[0079] 또한 관통 전극 영역(120)이 적층 반도체 칩 구조체(100a)의 일측에만 배치된 것으로 도시되었으나, 본 발명의 기술적 사상은 이에 한정되지 않는다. 예를 들면, 적층 반도체 칩 구조체(100a)의 양측에 인접하도록 2개의 제1 반도체 칩(130)이 배치되는 경우, 관통 전극 영역(120)도 2개의 제1 반도체 칩(130)에 각각 인접하도록 적층 반도체 칩 구조체(100a)의 양측에 각각 배치될 수 있다. 이에 대해서는 도 5 내지 도 16에서 도시하는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도들을 통하여 자세히 설명하도록 한다.

- [0080] 또한 1개의 서브 반도체 패키지(130a)의 단면과 적층 반도체 칩 구조체(100a)의 단면은 동일 방향을 따라서 절단한 단면일 수도 있으나, 1개의 서브 반도체 패키지(130a)과 적층 반도체 칩 구조체(100a)의 배치에 따라서, 1개의 서브 반도체 패키지(130a)의 단면과 적층 반도체 칩 구조체(100a)의 단면이 서로 다른 방향을 따라서 절단한 단면일 수도 있다.

- [0081] 도 2는 본 발명의 일 실시 예에 따른 반도체 패키지를 나타내는 단면도이다. 도 2에 대한 설명 중 도 1에 대한 설명과 중복되는 내용은 생략될 수 있다.

- [0082] 도 2를 참조하면, 반도체 패키지(1b)는 패키지 베이스 기판(10), 서브 반도체 패키지(130a) 및 적층 반도체 칩 구조체(100b)를 포함한다. 서브 반도체 패키지(130a)와 적층 반도체 칩 구조체(100b)는 서로 인접하도록 패키지 베이스 기판(10) 상에 부착될 수 있다.

- [0083] 적층 반도체 칩 구조체(100b)는 순차적으로 적층된 복수의 제2 반도체 칩(110)을 포함할 수 있다. 복수의 제2 반도체 칩(110)은 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)이 수직 방향으로 적층될 수 있다.

- [0084] 복수의 제2 반도체 칩(110) 중 적어도 하나는 로직 반도체 칩이고, 나머지는 메모리 반도체 칩일 수 있다. 예를 들면, 복수의 제2 반도체 칩(110)은 상기 로직 반도체 칩 및 상기 로직 반도체 칩 상에 적층되는 복수의 메모리 반도체 칩으로 이루어질 수 있다. 예를 들면, 복수의 제2 반도체 칩(110) 중 최하단의 반도체 칩(110a)은 로직 반도체 칩이고, 나머지 반도체 칩(110b, 110c, 110d, 110e)은 메모리 반도체 칩일 수 있다. 예를 들면, 복수의 제2 반도체 칩(110) 중 최하단의 반도체 칩(110a)은 나머지 반도체 칩(110b, 110c, 110d, 110e)을 제어하기 위한 콘트롤러 칩일 수 있고, 나머지 반도체 칩(110b, 110c, 110d, 110e)은 HBM(High Bandwidth Memory) DRAM 반도체 칩일 수 있다.

- [0085] 복수의 제2 반도체 칩(110) 중 상기 로직 반도체 칩의 면적은 상기 복수의 메모리 반도체 칩의 면적보다 클 수 있다. 예를 들면, 복수의 제2 반도체 칩(110) 중 최하단의 반도체 칩(110a)의 면적은 나머지 반도체 칩(110b, 110c, 110d, 110e)의 면적보다 클 수 있다.

- [0086] 적층 반도체 칩 구조체(100b)는 상기 복수의 메모리 반도체 칩의 측면을 감싸되, 상기 복수의 메모리 반도체 칩 중 최상단의 메모리 반도체 칩의 상면을 덮지 않도록 상기 로직 반도체 칩 상에 형성되는 제2 서브 패키지 몰딩층(118)을 더 포함할 수 있다. 예를 들면, 적층 반도체 칩 구조체(100b)는 복수의 제2 반도체 칩(110) 중 최하단의 반도체 칩(110a) 상에 형성되어 나머지 반도체 칩(110b, 110c, 110d, 110e)의 측면을 감싸되, 최상단의 반도체 칩(110e)의 상면을 덮지 않도록 형성되는 제2 서브 패키지 몰딩층(118)을 더 포함할 수 있다. 제2 서브 패키지 몰딩층(118)은 예를 들면, EMC로 이루어질 수 있다. 제2 서브 패키지 몰딩층(118)은 후술할 패키지 몰딩층(300)과 함께 형성될 수도 있다.

- [0087] 적층 반도체 칩 구조체(100b)와 패키지 베이스 기판(10) 사이의 공간을 채우도록 제2 언더필 물질층(320)이 형성될 수 있다. 제1 언더필 물질층(330)은 예를 들면, 에폭시 수지로 이루어질 수 있다. 제2 언더필 물질(320)은 예를 들면, MUF 방식으로 형성되는 물딩층(300)의 일부분일 수 있다.

- [0088] 도 1에 보인 반도체 패키지(1a)와 도 2에 보인 반도체 패키지(1b)는, 도 1에 보인 적층 반도체 칩 구조체(100a)와 도 2에 보인 적층 반도체 칩 구조체(100b)의 구조에 전술한 것과 같은 차이가 있다는 점을 제외하고는 동일한 바, 자세한 설명은 생략하도록 한다.

- [0089] 도 3은 본 발명의 일 실시 예에 따른 반도체 패키지를 나타내는 단면도이다. 도 3에 대한 설명 중 도 1에 대한 설명과 중복되는 내용은 생략될 수 있다.

- [0090] 도 3를 참조하면, 반도체 패키지(1c)는 패키지 베이스 기판(10), 서브 반도체 패키지(130b) 및 적층 반도체 칩 구조체(100a)를 포함한다. 서브 반도체 패키지(130b)와 적층 반도체 칩 구조체(100a)는 서로 인접하도록 패키지 베이스 기판(10) 상에 부착될 수 있다.

- [0091] 서브 반도체 패키지(130b)는 제1 반도체 칩(130)을 포함할 수 있다. 제1 반도체 칩(130)은 활성면(132)이 패키지 베이스 기판(10)을 향하도록, 패키지 베이스 기판(10) 상에 부착될 수 있다. 제1 반도체 칩(130)은 활성면(132) 상에 배치된 제1 연결 단자(136)에 의하여 패키지 베이스 기판(10)과 전기적으로 연결될 수 있다. 제1 연결 단자(136)는 예를 들면, 솔더볼 또는 범프일 수 있다. 서브 반도체 패키지(130b)와 패키지 베이스 기판(10) 사이의 공간을 채우도록 제1 언더필 물질층(330)이 형성될 수 있다. 제1 언더필 물질층(330)은 예를 들면, 에폭시 수지로 이루어질 수 있다. 제1 언더필 물질(330)은 예를 들면, MUF 방식으로 형성되는 물딩층(300)의 일부분일 수 있다. 서브 반도체 패키지(130b)는 예를 들면, 웨이퍼 레벨 패키지(WLP, Wafer Level Package)일 수 있

다.

[0092] 도 1에 보인 반도체 패키지(1a)와 도 3에 보인 반도체 패키지(1c)는, 도 1에 보인 서브 반도체 패키지(130a)와 도 3에 보인 서브 반도체 패키지(130b)의 구조에 전술한 것과 같은 차이가 있다는 점을 제외하고는 동일한 바, 자세한 설명은 생략하도록 한다.

[0093] 도 4는 본 발명의 일 실시 예에 따른 반도체 패키지를 나타내는 단면도이다. 도 4에 대한 설명 중 도 1 내지 도 3에 대한 설명과 중복되는 내용은 생략될 수 있다.

[0094] 도 4를 참조하면, 반도체 패키지(1d)는 패키지 베이스 기판(10), 서브 반도체 패키지(130b) 및 적층 반도체 칩 구조체(100b)를 포함한다. 서브 반도체 패키지(130b)와 적층 반도체 칩 구조체(100b)는 서로 인접하도록 패키지 베이스 기판(10) 상에 부착될 수 있다.

[0095] 도 4에 보인 적층 반도체 칩 구조체(100b)는 도 2에 보인 적층 반도체 칩 구조체(100b)와 동일한 구조를 가질 수 있다. 도 4에 보인 서브 반도체 패키지(130b)는 도 3에 보인 서브 반도체 패키지(130b)와 동일한 구조를 가질 수 있다.

[0096] 도 1 내지 도 3에 보인 반도체 패키지(1a, 1b, 1c)와 도 4에 보인 반도체 패키지(1d)는, 전술한 것과 같은 차이가 있다는 점을 제외하고는 동일한 바, 자세한 설명은 생략하도록 한다.

[0097] 도 5 내지 도 16은 본 발명의 일 실시 예들에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도들이다. 도 5 내지 도 16에 도시되는 반도체 패키지들에 포함되는 서브 반도체 패키지 및 적층 반도체 칩 구조체의 단면은 도 1 내지 도 4에 보인 반도체 패키지(1a, 1b, 1c, 1d)에 보인 제1 반도체 칩(130) 및 복수의 제2 반도체 칩(110)이 모두 적용 가능하다.

[0098] 또한 도 1 내지 도 4에서 보인 복수의 제2 반도체 칩(110)에 포함되는 복수의 반도체 칩들(110a, 110b, 110c, 110d, 110e)은 수직 적층되어 하나의 적층 반도체 칩 구조체(100a, 100b)를 이루는 바, 이후에서는 설명하는 평면 배치도들에서는 복수의 제2 반도체 칩을 적층 반도체 칩 구조체라고 병용하여 호칭할 수 있다.

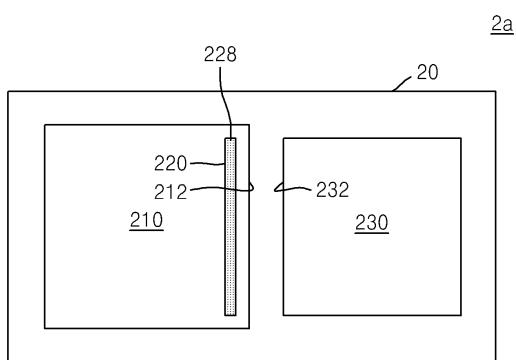

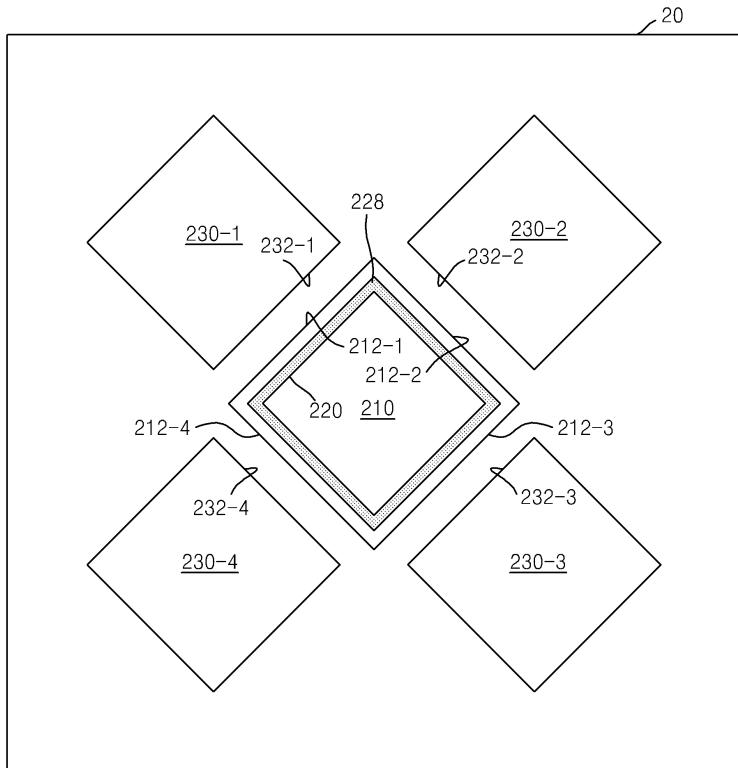

[0099] 도 5는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

[0100] 도 5를 참조하면, 반도체 패키지(2a)는 패키지 베이스 기판(20) 상에 부착되며, 서로 인접하도록 배치되는 제1 반도체 칩(230)과 적층 반도체 칩 구조체(210)를 포함한다.

[0101] 적층 반도체 칩 구조체(210)의 한 변(212)과 제1 반도체 칩(230)의 한 변(232)은 서로 대향할 수 있다. 관통 전극 영역(220)에는 복수의 관통 전극(228)이 형성될 수 있다. 관통 전극 영역(220)은 제1 반도체 칩(230)의 한 변(232)과 대향하는 적층 반도체 칩 구조체(210)의 한 변(212)에 인접하도록 배치될 수 있다. 관통 전극 영역(220)은 제1 반도체 칩(230)의 한 변(232)과 대향하는 적층 반도체 칩 구조체(210)의 한 변(212)을 따라서 연장되며 배치될 수 있다.

[0102] 관통 전극 영역(220)에는 수백 개 내지 수천 개의 관통 전극(228)이 형성될 수 있다. 관통 전극 영역(220)은 복수의 관통 전극(228)이 비교적 일정한 간격을 가지고 배치되는 영역을 의미한다. 예를 들면, 복수의 관통 전극(228)은 관통 전극 영역(220)내에서 수십  $\mu\text{m}$ 의 피치(pitch)를 가지고 배치될 수 있다. 예를 들면, 복수의 관통 전극(228)은 관통 전극 영역(220)내에서 25  $\mu\text{m}$  내지 50  $\mu\text{m}$ 의 피치를 가지고 배치될 수 있다.

[0103] 적층 반도체 칩 구조체(210)에 메모리 반도체 칩이 포함되는 경우, 메모리 반도체 칩에 포함되는 메모리 셀들(도시 생략)은 관통 전극 영역(220)과는 별도의 영역에 형성될 수 있다. 상기 메모리 반도체 칩에 포함되는 메모리 셀들이 배치되는 메모리 셀 블록은 관통 전극 영역(220)을 중심으로 제1 반도체 칩(230)과는 반대 방향에 배치될 수 있다. 상기 메모리 셀 블록을 위한 연결 패드(도시 생략)가 상기 메모리 반도체 칩의 중앙에 배치되는 센터 패드 배치인 경우, 상기 메모리 반도체 칩에는 상기 연결 패드와 관통 전극(228)을 연결하기 위한 채배선 패턴(도시 생략)이 형성될 수 있다. 또는 상기 메모리 셀 블록을 위한 연결 패드(도시 생략)가 관통 전극 영역(220)에 형성될 수 있도록, 상기 메모리 반도체 칩에는 내부 배선이 형성될 수 있다.

[0104] 제1 반도체 칩(230)이 적층 반도체 칩 구조체(210)보다 단위 면적당 발열량이 많을 경우, 제1 반도체 칩(230)에서 발생한 열 중 적층 반도체 칩 구조체(210)를 향하여 전달되는 열은 관통 전극(228)을 통하여 외부로 방출될 수 있다. 따라서 제1 반도체 칩(230)과 적층 반도체 칩 구조체(210) 사이에서 열집중 현상이 발생하는 것을 방지할 수 있고, 제1 반도체 칩(230)에서 발생한 열에 의하여 적층 반도체 칩 구조체(210)에 포함되는 반도체 소

자, 예를 들면 메모리 셀의 동작에 영향을 주는 것을 방지할 있기 때문에, 반도체 패키지(2a)의 동작 신뢰성을 얻을 수 있다.

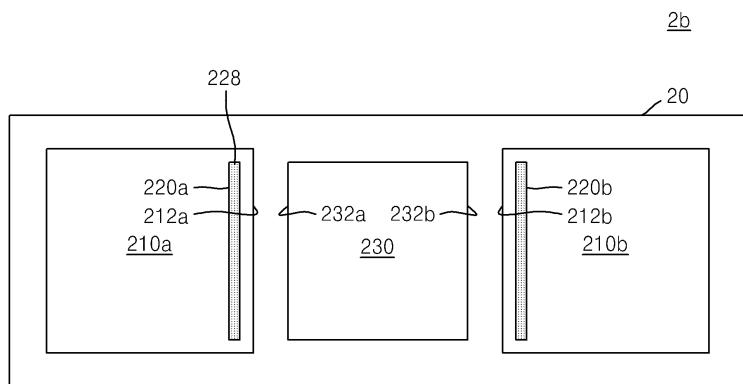

[0105] 도 6은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 6에 대한 설명 중 전술한 설명과 중복되는 내용은 생략될 수 있다.

[0106] 도 6을 참조하면, 반도체 패키지(2b)는 패키지 베이스 기판(20) 상에 부착되는 제1 반도체 칩(230)과 패키지 베이스 기판(20) 상에 부착되되 제1 반도체 칩(230)과 서로 인접하도록 배치되는 2개의 적층 반도체 칩 구조체(210a, 210b)를 포함한다. 제1 적층 반도체 칩 구조체(210a)와 제2 적층 반도체 칩 구조체(210b)는 각각 제1 반도체 칩(230)의 서로 반대되는 제1 변(232a)과 제2 변(232b)에 인접하도록 배치될 수 있다.

[0107] 제1 반도체 칩(230)의 제1 변(232a)과 제1 적층 반도체 칩 구조체(210a)의 한 변(212a)은 서로 대향할 수 있다. 제1 반도체 칩(230)의 제2 변(232b)과 제2 적층 반도체 칩 구조체(210b)의 한 변(212b)은 서로 대향할 수 있다.

[0108] 제1 및 제2 적층 반도체 칩 구조체(210a, 210b)는 각각 복수의 관통 전극(228)이 형성되는 관통 전극 영역(220a, 220b)을 가질 수 있다. 제1 적층 반도체 칩 구조체(210a)의 관통 전극 영역(220a)은 제1 반도체 칩(230)의 제1 변(232a)과 대향하는 제1 적층 반도체 칩 구조체(210a)의 한 변(212a)에 인접하도록 배치될 수 있다. 제1 적층 반도체 칩 구조체(210a)의 관통 전극 영역(220a)은 제1 반도체 칩(230)의 제1 변(232a)과 대향하는 제1 적층 반도체 칩 구조체(210a)의 한 변(212a)을 따라서 연장되어 배치될 수 있다. 제2 적층 반도체 칩 구조체(210b)의 관통 전극 영역(220b)은 제1 반도체 칩(230)의 제2 변(232b)과 대향하는 제2 적층 반도체 칩 구조체(210b)의 관통 전극 영역(220b)은 제1 반도체 칩(230)의 제2 변(232b)과 대향하는 제2 적층 반도체 칩 구조체(210b)의 한 변(212b)을 따라서 연장되어 배치될 수 있다.

[0109] 제1 반도체 칩(230)이 제1 및 제2 적층 반도체 칩 구조체(210a, 210b)보다 단위 면적당 발열량이 많을 경우, 제1 반도체 칩(230)에서 발생한 열 중 제1 및 제2 적층 반도체 칩 구조체(210a, 210b)를 향하여 전달되는 열은 관통 전극(228)을 통하여 외부로 방출될 수 있다. 따라서 제1 반도체 칩(230)과 제1 및 제2 적층 반도체 칩 구조체(210a, 210b) 사이에서 열집중 현상이 발생하는 것을 방지할 수 있고, 제1 반도체 칩(230)에서 발생한 열에 의하여 제1 및 제2 적층 반도체 칩 구조체(210a, 210b)에 포함되는 반도체 소자, 예를 들면 메모리 셀의 동작에 영향을 주는 것을 방지할 있기 때문에, 반도체 패키지(2b)의 동작 신뢰성을 얻을 수 있다.

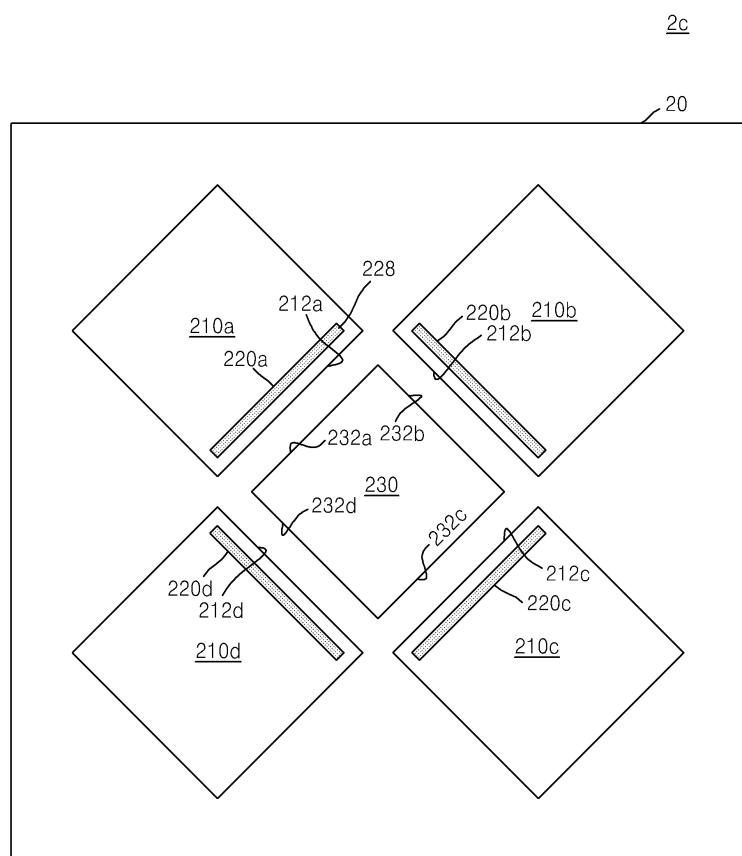

[0110] 도 7은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 7에 대한 설명 중 전술한 설명과 중복되는 내용은 생략될 수 있다.

[0111] 도 7을 참조하면, 반도체 패키지(2c)는 패키지 베이스 기판(20) 상에 부착되는 제1 반도체 칩(230)과 패키지 베이스 기판(20) 상에 부착되되 제1 반도체 칩(230)과 서로 인접하도록 배치되는 4개의 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)를 포함한다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)에 인접하도록 배치될 수 있다.

[0112] 제1 반도체 칩(230)의 제1 변(232a)과 제1 적층 반도체 칩 구조체(210a)의 한 변(212a)은 서로 대향할 수 있다. 제1 반도체 칩(230)의 제2 변(232b)과 제2 적층 반도체 칩 구조체(210b)의 한 변(212b)은 서로 대향할 수 있다. 제1 반도체 칩(230)의 제3 변(232c)과 제3 적층 반도체 칩 구조체(210c)의 한 변(212c)은 서로 대향할 수 있다. 제1 반도체 칩(230)의 제4 변(232d)과 제4 적층 반도체 칩 구조체(210d)의 한 변(212d)은 서로 대향할 수 있다.

[0113] 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 복수의 관통 전극(228)이 형성되는 관통 전극 영역(220a, 220b, 220c, 220d)을 가질 수 있다. 제1 적층 반도체 칩 구조체(210a)의 관통 전극 영역(220a)은 제1 반도체 칩(230)의 제1 변(232a)과 대향하는 제1 적층 반도체 칩 구조체(210a)의 한 변(212a)에 인접하도록 배치될 수 있다. 제1 적층 반도체 칩 구조체(210a)의 관통 전극 영역(220a)은 제1 반도체 칩(230)의 제1 변(232a)과 대향하는 제1 적층 반도체 칩 구조체(210a)의 한 변(212a)을 따라서 연장되어 배치될 수 있다. 제2 적층 반도체 칩 구조체(210b)의 관통 전극 영역(220b)은 제1 반도체 칩(230)의 제2 변(232b)과 대향하는 제2 적층 반도체 칩 구조체(210b)의 한 변(212b)에 인접하도록 배치될 수 있다. 제2 적층 반도체 칩 구조체(210b)의 관통 전극 영역(220b)은 제1 반도체 칩(230)의 제2 변(232b)과 대향하는 제2 적층 반도체 칩 구조체(210b)의 한 변(212b)을 따라서 연장되어 배치될 수 있다.

[0114] 제3 적층 반도체 칩 구조체(210c)의 관통 전극 영역(220c)은 제1 반도체 칩(230)의 제3 변(232c)과 대향하는 제3 적층 반도체 칩 구조체(210c)의 한 변(212c)에 인접하도록 배치될 수 있다. 제3 적층 반도체 칩 구조체(210c)의 관통 전극 영역(220c)은 제1 반도체 칩(230)의 제3 변(232c)과 대향하는 제3 적층 반도체 칩 구조체(210c)의 한 변(212c)을 따라서 연장되어 배치될 수 있다.

c)의 한 변(212c)을 따라서 연장되며 배치될 수 있다. 제4 적층 반도체 칩 구조체(210d)의 관통 전극 영역(220d)은 제1 반도체 칩(230)의 제4 변(232d)과 대향하는 제4 적층 반도체 칩 구조체(210d)의 한 변(212d)에 인접하도록 배치될 수 있다. 제4 적층 반도체 칩 구조체(210d)의 관통 전극 영역(220d)은 제1 반도체 칩(230)의 제4 변(232d)과 대향하는 제4 적층 반도체 칩 구조체(210d)의 한 변(212d)을 따라서 연장되며 배치될 수 있다.

[0115] 제1 반도체 칩(230)이 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)보다 단위 면적당 발열량이 많을 경우, 제1 반도체 칩(230)에서 발생한 열 중 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)를 향하여 전달되는 열은 관통 전극(228)을 통하여 외부로 방출될 수 있다. 따라서 제1 반도체 칩(230)과 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d) 사이에서 열집중 현상이 발생하는 것을 방지할 수 있고, 제1 반도체 칩(230)에서 발생한 열에 의하여 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)에 포함되는 반도체 소자, 예를 들면 메모리 셀의 동작에 영향을 주는 것을 방지할 있기 때문에, 반도체 패키지(2c)의 동작 신뢰성을 얻을 수 있다.

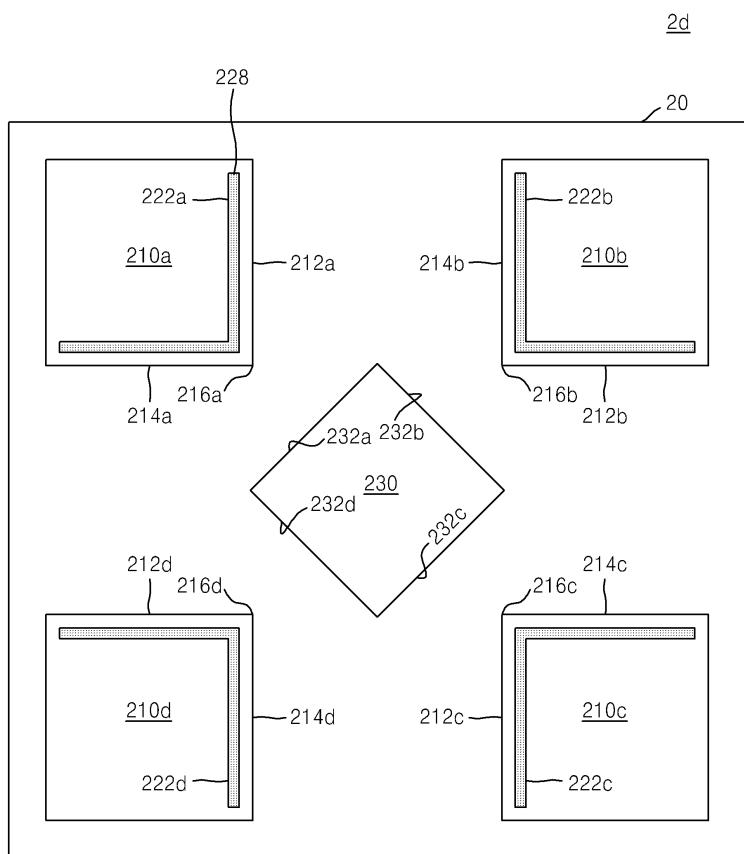

[0116] 도 8은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 8에 대한 설명 중 전술한 설명과 중복되는 내용은 생략될 수 있다.

[0117] 도 8을 참조하면, 반도체 패키지(2d)는 패키지 베이스 기판(20) 상에 부착되는 제1 반도체 칩(230)과 패키지 베이스 기판(20) 상에 부착되되 제1 반도체 칩(230)과 서로 인접하도록 배치되는 4개의 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)를 포함한다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)에 인접하도록 배치될 수 있다.

[0118] 제1 반도체 칩(230)의 제1 변(232a)과 제1 적층 반도체 칩 구조체(210a)의 한 꼭지점(216a)은 서로 대향할 수 있다. 제1 반도체 칩(230)의 제2 변(232b)과 제2 적층 반도체 칩 구조체(210b)의 한 꼭지점(216b)은 서로 대향할 수 있다. 제1 반도체 칩(230)의 제3 변(232c)과 제3 적층 반도체 칩 구조체(210c)의 한 꼭지점(216c)은 서로 대향할 수 있다. 제1 반도체 칩(230)의 제4 변(232d)과 제4 적층 반도체 칩 구조체(210d)의 한 꼭지점(216d)은 서로 대향할 수 있다. 즉, 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 한 꼭지점(216a, 216b, 216c, 216d)이 각각 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)을 향하도록, 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)은 배치될 수 있다.

[0119] 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 복수의 관통 전극(228)이 형성되는 관통 전극 영역(222a, 222b, 222c, 222d)을 가질 수 있다. 제1 적층 반도체 칩 구조체(210a)의 관통 전극 영역(222a)은 제1 반도체 칩(230)의 제1 변(232a)과 대향하는 제1 적층 반도체 칩 구조체(210a)의 한 꼭지점(216a)을 이루는 두 변(212a, 214a)에 인접하도록 배치될 수 있다. 제1 적층 반도체 칩 구조체(210a)의 관통 전극 영역(222a)은 제1 반도체 칩(230)의 제1 변(232a)과 대향하는 제1 적층 반도체 칩 구조체(210a)의 한 꼭지점(216a)을 이루는 두 변(212a, 214a)을 따라서 연장되어 L자 형을 가지며 배치될 수 있다. 제2 적층 반도체 칩 구조체(210b)의 관통 전극 영역(222b)은 제1 반도체 칩(230)의 제2 변(232b)과 대향하는 제2 적층 반도체 칩 구조체(210b)의 한 꼭지점(216b)을 이루는 두 변(212b, 214b)에 인접하도록 배치될 수 있다. 제2 적층 반도체 칩 구조체(210b)의 관통 전극 영역(222b)은 제1 반도체 칩(230)의 제2 변(232b)과 대향하는 제2 적층 반도체 칩 구조체(210b)의 한 꼭지점(216b)을 이루는 두 변(212b, 214b)을 따라서 연장되어 L자 형을 가지며 배치될 수 있다.

[0120] 제3 적층 반도체 칩 구조체(210c)의 관통 전극 영역(222c)은 제1 반도체 칩(230)의 제3 변(232c)과 대향하는 제3 적층 반도체 칩 구조체(210c)의 한 꼭지점(216c)을 이루는 두 변(212c, 214c)에 인접하도록 배치될 수 있다. 제3 적층 반도체 칩 구조체(210c)의 관통 전극 영역(222c)은 제1 반도체 칩(230)의 제3 변(232c)과 대향하는 제3 적층 반도체 칩 구조체(210c)의 한 꼭지점(216c)을 이루는 두 변(212c, 214c)을 따라서 연장되어 L자 형을 가지며 배치될 수 있다. 제4 적층 반도체 칩 구조체(210d)의 관통 전극 영역(222d)은 제1 반도체 칩(230)의 제4 변(232d)과 대향하는 제4 적층 반도체 칩 구조체(210d)의 한 꼭지점(216d)을 이루는 두 변(212d, 214d)에 인접하도록 배치될 수 있다. 제4 적층 반도체 칩 구조체(210d)의 관통 전극 영역(222d)은 제1 반도체 칩(230)의 제4 변(232d)과 대향하는 제4 적층 반도체 칩 구조체(210d)의 한 꼭지점(216d)을 이루는 두 변(212d, 214d)을 따라서 연장되어 L자 형을 가지며 배치될 수 있다.

[0121] 제1 반도체 칩(230)이 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)보다 단위 면적당 발열량이 많을 경우, 제1 반도체 칩(230)에서 발생한 열 중 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)를 향하여 전달되는 열은 관통 전극(228)을 통하여 외부로 방출될 수 있다. 따라서 제1 반도체 칩(230)과 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d) 사이에서 열집중 현상이 발생하는 것을 방지할

수 있고, 제1 반도체 칩(230)에서 발생한 열에 의하여 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)에 포함되는 반도체 소자, 예를 들면 메모리 셀의 동작에 영향을 주는 것을 방지할 있기 때문에, 반도체 패키지(2d)의 동작 신뢰성을 얻을 수 있다.

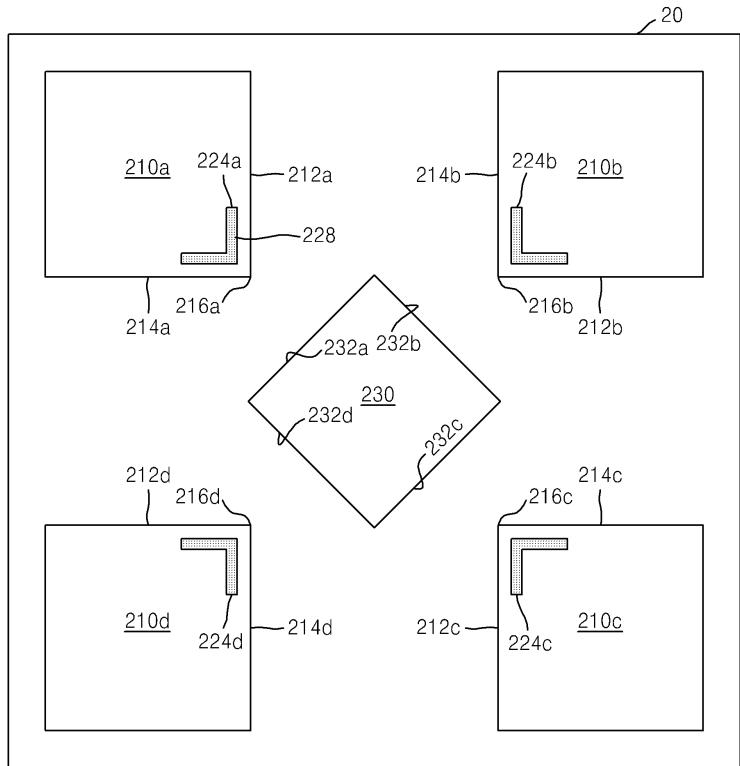

[0122] 도 9는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 9에 대한 설명 중 도 8에 대한 설명과 중복되는 내용은 생략될 수 있다.

[0123] 도 9를 참조하면, 반도체 패키지(2e)는 패키지 베이스 기판(20) 상에 부착되는 제1 반도체 칩(230)과 패키지 베이스 기판(20) 상에 부착되어 제1 반도체 칩(230)과 서로 인접하도록 배치되는 4개의 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)를 포함한다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)에 인접하도록 배치될 수 있다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 복수의 관통 전극(228)이 형성되는 관통 전극 영역(224a, 224b, 224c, 224d)을 가질 수 있다.

[0124] 도 9에 보인 반도체 패키지(2e)와 도 8에 보인 반도체 패키지(2d)는 도 9에 보인 반도체 패키지(2e)의 관통 전극 영역(224a, 224b, 224c, 224d)의 크기가 도 8에 보인 반도체 패키지(2d)의 관통 전극 영역(222a, 222b, 222c, 222d)의 크기와 다르다는 점을 제외하고는 동일한 바, 자세한 설명은 생략하도록 한다.

[0125] 도 9에 보인 반도체 패키지(2e)의 관통 전극 영역(224a, 224b, 224c, 224d)은 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 한 꼭지점(216a, 216b, 216c, 216d)을 이루는 두 변(212a, 212b, 212c, 212d)과 214a, 214b, 214c, 214d)을 따라서 연장되는 길이가 도 8에 보인 반도체 패키지(2d)의 관통 전극 영역(222a, 222b, 222c, 222d)에 비하여 짧아서, 상대적으로 작은 L자 형을 가지며 배치될 수 있다.

[0126] 도 1 내지 도 4를 함께 참조하면, 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d) 각각을 이루는 복수의 제2 반도체 칩(110a, 110b, 110c, 110d, 110e) 중 적어도 하나가 로직 반도체 칩인 경우, 반도체 패키지(2e)는 상기 로직 반도체 칩과 제1 반도체 칩(230)을 전기적으로 연결하기 위하여 패키지 베이스 기판(20)과 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d) 사이에 배치되는 연결 단자(도시 생략)를 더 포함할 수 있다. 예를 들어, 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d) 각각을 이루는 복수의 제2 반도체 칩(110a, 110b, 110c, 110d, 110e) 중 최하단의 반도체 칩(110a)이 로직 반도체 칩인 경우, 복수의 제2 반도체 칩(110a, 110b, 110c, 110d, 110e)들을 패키지 베이스 기판(10 또는 20)과 전기적으로 연결하기 위한 관통 전극(128)과 전기적으로 연결되는 제2 연결 단자(116a)와는 별도로 최하단의 반도체 칩(110a)과 제1 반도체 칩(230)을 전기적으로 연결하기 위하여, 최하단의 반도체 칩(110a)과 패키지 베이스 기판(10 또는 20) 사이에 연결 단자(도시 생략)를 더 배치할 수 있으며, 상기 연결 단자는 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 한 꼭지점(216a, 216b, 216c, 216d)을 이루는 두 변(212a, 212b, 212c, 212d)과 214a, 214b, 214c, 214d)에 인접하는 부분 중 관통 전극 영역(224a, 224b, 224c, 224d)이 배치되지 않은 부분에 배치될 수 있다.

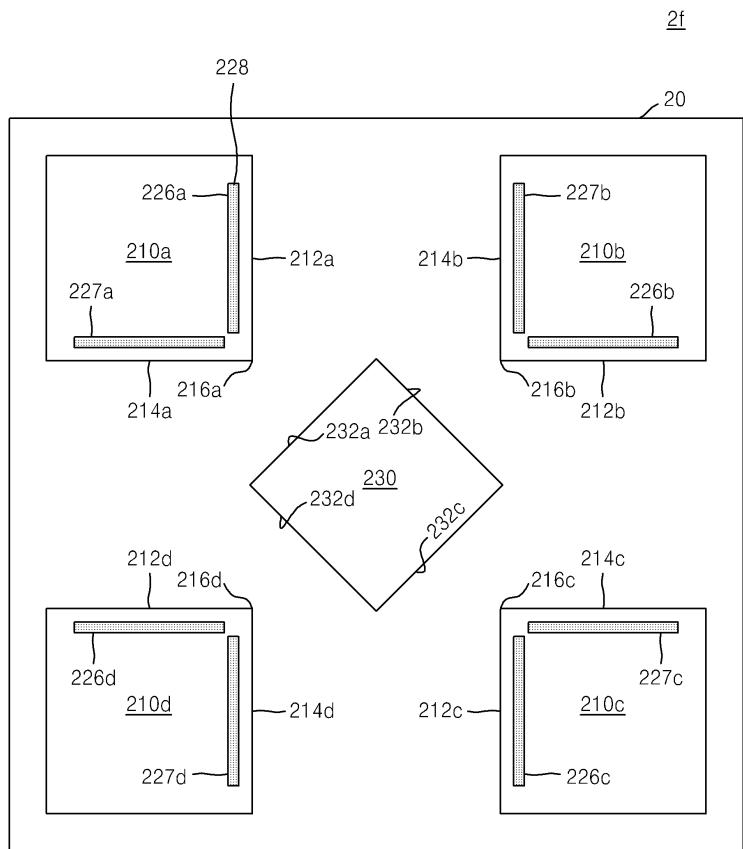

[0127] 도 10은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 10에 대한 설명 중 도 8 및 도 9에 대한 설명과 중복되는 내용은 생략될 수 있다.

[0128] 도 10을 참조하면, 반도체 패키지(2f)는 패키지 베이스 기판(20) 상에 부착되는 제1 반도체 칩(230)과 패키지 베이스 기판(20) 상에 부착되어 제1 반도체 칩(230)과 서로 인접하도록 배치되는 4개의 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)를 포함한다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)에 인접하도록 배치될 수 있다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 복수의 관통 전극(228)이 형성되는 관통 전극 영역(226a와 227a, 226b와 227b, 226c와 227c, 226d와 227d)을 가질 수 있다.

[0129] 도 10에 보인 반도체 패키지(2f)와 도 8에 보인 반도체 패키지(2d)는 도 10에 보인 반도체 패키지(2f)의 관통 전극 영역(226a와 227a, 226b와 227b, 226c와 227c, 226d와 227d)이 도 8에 보인 반도체 패키지(2d)의 관통 전극 영역(222a, 222b, 222c, 222d)과 달리 두 부분으로 분리되어 있다는 점을 제외하고는 동일한 바, 자세한 설명은 생략하도록 한다.

[0130] 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d) 각각의 관통 전극 영역(226a와 227a, 226b와 227b, 226c와 227c, 226d와 227d)은 각각의 한 꼭지점(216a, 216b, 216c, 216d)을 이루는 두 변(212a와 214a, 212b와 214b, 212c와 214c, 212c와 214c)을 따라서 연장되어, 각각의 한 꼭지점(216a, 216b, 216c, 216d) 부근에서 분리되도록 배치될 수 있다.

- [0131] 이와 같이, 관통 전극 영역(226a와 227a, 226b와 227b, 226c와 227c, 226d와 227d)을 두 개 이상의 부분으로 분리하는 것은 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 설계상 선택적으로 적용하거나, 도 10에서 설명한 로직 반도체 칩과 제1 반도체 칩(230)을 전기적으로 연결하기 위한 연결 단자(도시 생략)를 한 꼭지점(216a, 216b, 216c, 216d)에 인접하도록 배치하기 위하여 적용할 수 있다.

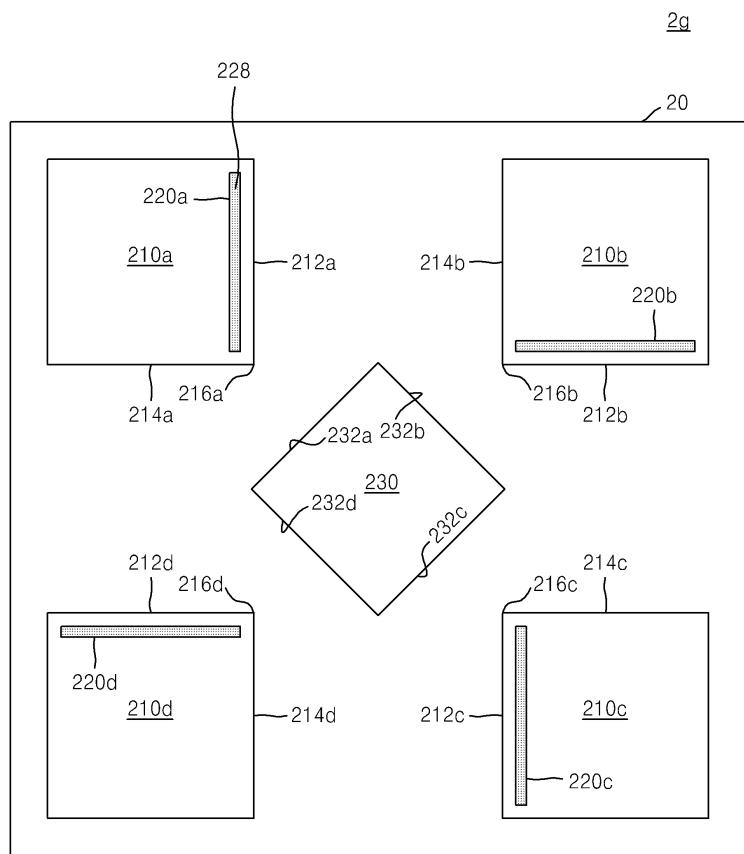

- [0132] 도 11은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 11에 대한 설명 중 도 7 및 도 8에 대한 설명과 중복되는 내용은 생략될 수 있다.

- [0133] 도 11을 참조하면, 반도체 패키지(2g)는 패키지 베이스 기판(20) 상에 부착되는 제1 반도체 칩(230)과 패키지 베이스 기판(20) 상에 부착되며 제1 반도체 칩(230)과 서로 인접하도록 배치되는 4개의 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)를 포함한다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)에 인접하도록 배치될 수 있다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 한 꼭지점(216a, 216b, 216c, 216d)과 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)은 각각 서로 대향할 수 있다.

- [0134] 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 복수의 관통 전극(228)이 형성되는 관통 전극 영역(220a, 220b, 220c, 220d)을 가질 수 있다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 관통 전극 영역(220a, 220b, 220c, 220d)은 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)과 대향하는 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 한 꼭지점(216a, 216b, 216c, 216d)을 이루는 두 변(212a와 214a, 212b와 214b, 212c와 214c, 212c와 214c) 중 한 변(212a, 212b, 212c, 212d)에 인접하며 연장되도록 배치될 수 있다.

- [0135] 도 12는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 12에 대한 설명 중 도 11에 대한 설명과 중복되는 내용은 생략될 수 있다.

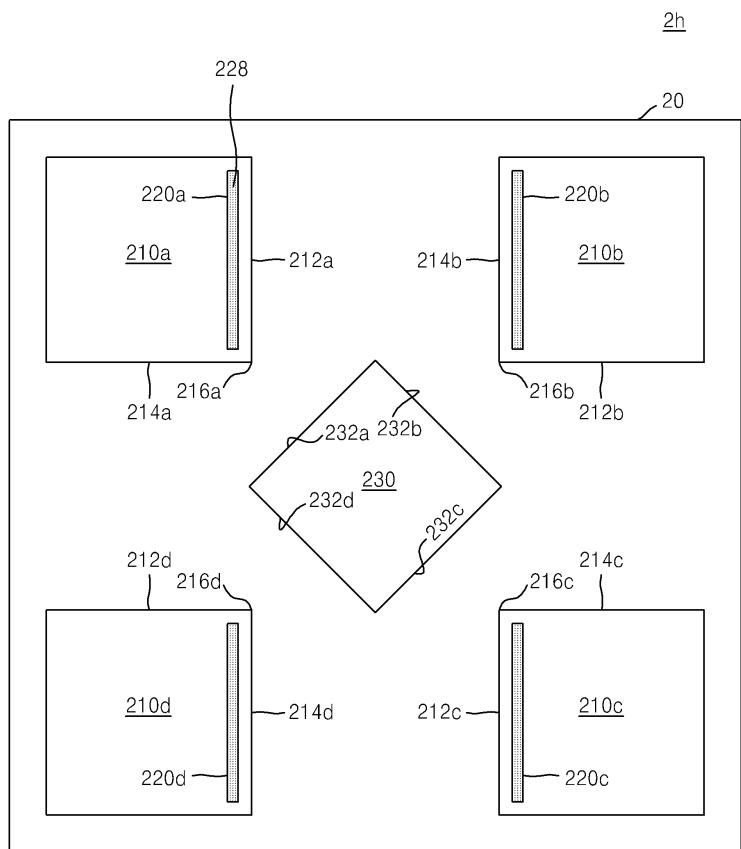

- [0136] 도 12를 참조하면, 반도체 패키지(2h)는 패키지 베이스 기판(20) 상에 부착되는 제1 반도체 칩(230)과 패키지 베이스 기판(20) 상에 부착되며 제1 반도체 칩(230)과 서로 인접하도록 배치되는 4개의 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)를 포함한다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)에 인접하도록 배치될 수 있다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 한 꼭지점(216a, 216b, 216c, 216d)과 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)은 각각 서로 대향할 수 있다.

- [0137] 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 각각 복수의 관통 전극(228)이 형성되는 관통 전극 영역(220a, 220b, 220c, 220d)을 가질 수 있다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 관통 전극 영역(220a, 220b, 220c, 220d)은 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)과 대향하는 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 한 꼭지점(216a, 216b, 216c, 216d)을 이루는 두 변(212a와 214a, 212b와 214b, 212c와 214c, 212c와 214c) 중 한 변(212a, 214b, 212c, 214d)에 인접하며 연장되도록 배치될 수 있다.

- [0138] 도 11 및 도 12를 함께 참조하면, 도 11에 보인 반도체 패지키(2g)는 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)가 마치 시계 방향으로 90도씩 회전한 것 같은 형태로, 제1 반도체 칩(230)의 주위에 배치된다. 반면에 도 12에 보인 반도체 패지키(2h)는 제1 및 제2 적층 반도체 칩 구조체(210a, 210b)와 제3 및 제4 적층 반도체 칩 구조체(210c, 210d)가 상하 대칭(또는 제1 및 제4 적층 반도체 칩 구조체(210a, 210d)와 제2 및 제3 적층 반도체 칩 구조체(210b, 210c)가 좌우 대칭)인 것 같은 형태로, 제1 반도체 칩(230)의 주위에 배치된다.

- [0139] 예를 들면, 제1 반도체 칩(230) 내에서도 빌열량이 더 큰 부분이 있는 경우, 그 부분에 관통 전극 영역(220a, 220b, 220c, 220d)이 인접하도록 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)을 회전 또는 대칭시켜서 제1 반도체 칩(230)의 주위에 배치할 수 있으며, 도 11 및 도 12에 보인 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 배치 이외에도, 다양한 변형이 가능함은 통상의 기술자에게 자명하다.

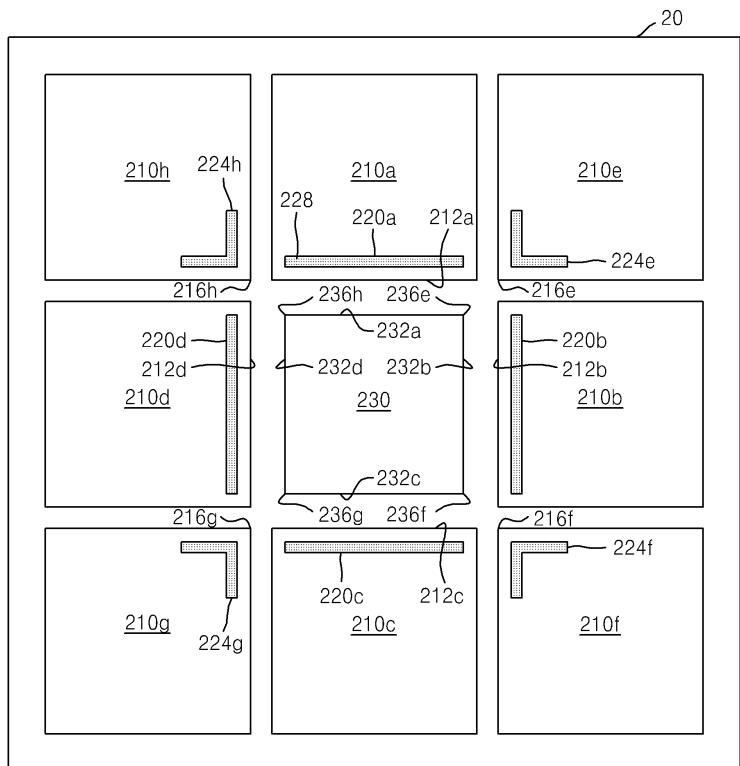

- [0140] 도 13은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 13에 대한 설명 중 도 5 내지 도 12에 대한 설명과 중복되는 내용은 생략될 수 있다.

- [0141] 도 13을 참조하면, 반도체 패지키(2i)는 패지키 베이스 기판(20) 상에 부착되는 제1 반도체 칩(230)과 패지키 베이스 기판(20) 상에 부착되며 제1 반도체 칩(230)과 서로 인접하도록 배치되는 8개의 적층 반도체 칩 구조체

(210a, 210b, 210c, 210d, 210e, 210f, 210g, 210h)를 포함한다. 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 한 변(212a, 212b, 212c, 212d)과 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)은 각각 서로 대향할 수 있다. 제5 내지 제8 적층 반도체 칩 구조체(210e, 210f, 210g, 210h)는 각각 제1 반도체 칩(230)의 제1 내지 제4 꼭지점(236e, 236f, 236g, 236h)에 인접하도록 배치될 수 있다. 제5 내지 제8 적층 반도체 칩 구조체(210e, 210f, 210g, 210h)의 한 꼭지점(216e, 216f, 216g, 216h)과 제1 반도체 칩(230)의 제1 내지 제4 꼭지점(236e, 236f, 236g, 236h)은 각각 서로 대향할 수 있다.

[0142] 도 13에 보인 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)는 도 7에 보인 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)와 동일한 구조를 가지도록, 각각 복수의 관통 전극(228)이 형성되는 관통 전극 영역(220a, 220b, 220c, 220d)을 가질 수 있다.

[0143] 도 13에 보인 제5 내지 제8 적층 반도체 칩 구조체(210e, 210f, 210g, 210h)는 도 9에 보인 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)와 동일한 구조를 가지도록, 각각 복수의 관통 전극(228)이 형성되는 관통 전극 영역(220e, 220f, 220g, 220h)을 가질 수 있다.

[0144] 도 13에 보인 반도체 패키지(2i)는 제1 반도체 칩(230)의 제1 내지 제4 변(232a, 232b, 232c, 232d)에 인접하도록 배치되는 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)의 관통 전극 영역(220a, 220b, 220c, 220d)과 제1 반도체 칩(230)의 제1 내지 제4 꼭지점(236e, 236f, 236g, 236h)에 인접하도록 배치되는 제5 내지 제8 적층 반도체 칩 구조체(210e, 210f, 210g, 210h)의 관통 전극 영역(220e, 220f, 220g, 220h)의 형상을 다르도록 형성할 수 있다. 또한 예를 들면, 제5 내지 제8 적층 반도체 칩 구조체(210e, 210f, 210g, 210h)를 도 8, 도 10, 도 11 및 도 12에 보인 제1 내지 제4 적층 반도체 칩 구조체(210a, 210b, 210c, 210d)으로 치환하여 반도체 패키지를 구성하는 것 또한 당업자에게 자명하다.

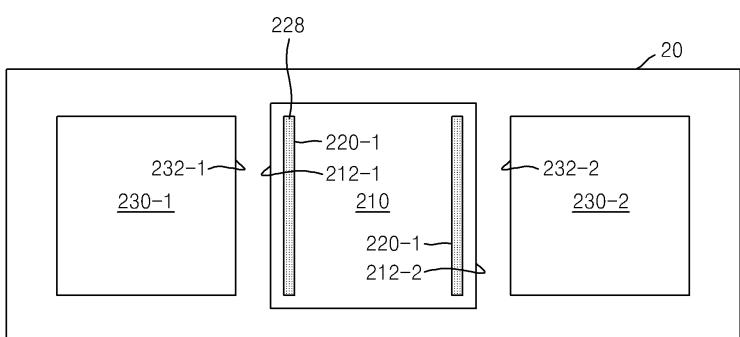

[0145] 도 14는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다.

[0146] 도 14를 참조하면, 반도체 패키지(2j)는 패키지 베이스 기판(20) 상에 부착되는 적층 반도체 칩 구조체(210)와 패키지 베이스 기판(20) 상에 부착되어 적층 반도체 칩 구조체(210)와 서로 인접하도록 배치되는 2개의 제1 반도체 칩(230-1, 230-2)을 포함한다. 2개의 제1 반도체 칩(230-1, 230-2)은 각각 적층 반도체 칩 구조체(210)의 서로 반대되는 제1 변(212-1)과 제2 변(212-2)에 인접하도록 배치될 수 있다. 2개의 제1 반도체 칩(230-1, 230-2) 각각의 한 변(232-1, 232-2)과 적층 반도체 칩 구조체(210)의 서로 반대되는 제1 변(212-1)과 제2 변(212-2)은 각각 서로 대향할 수 있다.

[0147] 2개의 제1 반도체 칩(230-1, 230-2) 각각은 도 1 내지 도 4에 보인 것과 같은 서브 반도체 패키지(130a, 130b)를 구성하여, 패키지 베이스 기판(20) 상에 부착될 수 있는 바, 하나의 제1 반도체 칩(230-1)이 구성하는 서브 반도체 패키지를 제1 서브 반도체 패키지라 호칭할 수 있고, 다른 하나의 제1 반도체 칩(230-2)이 구성하는 서브 반도체 패키지를 제2 서브 반도체 패키지라 호칭할 수 있다.

[0148] 적층 반도체 칩 구조체(210)는, 2개의 제1 반도체 칩(230-1, 230-2)이 각각 인접하는, 제1 변(212-1)과 제2 변(212-2)에 인접하며 연장되는 관통 전극 영역(220-1, 220-2)을 각각 포함할 수 있다.

[0149] 2개의 제1 반도체 칩(230-1, 230-2)이 적층 반도체 칩 구조체(210)보다 단위 면적당 발열량이 많을 경우, 2개의 제1 반도체 칩(230-1, 230-2)에서 발생한 열 중 적층 반도체 칩 구조체(210)를 향하여 전달되는 열은 관통 전극(228)을 통하여 외부로 방출될 수 있다. 따라서 2개의 제1 반도체 칩(230-1, 230-2)과 적층 반도체 칩 구조체(210) 사이에서 열집중 현상이 발생하는 것을 방지할 수 있고, 2개의 제1 반도체 칩(230-1, 230-2)에서 발생한 열에 의하여 적층 반도체 칩 구조체(210)에 포함되는 반도체 소자, 예를 들면 메모리 셀의 동작에 영향을 주는 것을 방지할 있기 때문에, 반도체 패키지(2j)의 동작 신뢰성을 얻을 수 있다.

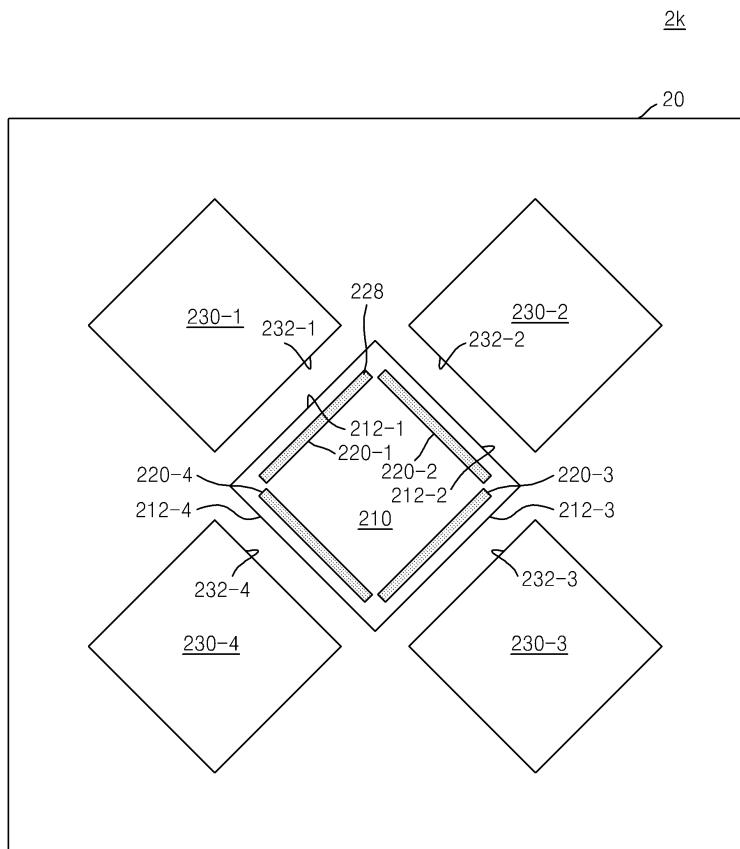

[0150] 도 15는 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 15에 대한 설명 중 도 14에 대한 설명과 중복되는 내용은 생략될 수 있다.

[0151] 도 15를 참조하면, 반도체 패키지(2k)는 패키지 베이스 기판(20) 상에 부착되는 적층 반도체 칩 구조체(210)와 패키지 베이스 기판(20) 상에 부착되어 적층 반도체 칩 구조체(210)와 서로 인접하도록 배치되는 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4)을 포함한다. 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4)은 각각 적층 반도체 칩 구조체(210)의 제1 내지 제4 변(212-1, 212-2, 212-3, 212-4)에 인접하도록 배치될 수 있다. 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4) 각각의 한 변(232-1, 232-2, 232-3, 232-4)과 적층 반도체

칩 구조체(210)의 제1 내지 제4 변(212-1, 212-2, 212-3, 212-4)은 각각 서로 대향할 수 있다.

[0152] 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4) 각각은 도 1 내지 도 4에 보인 것과 같은 서브 반도체 패키지(130a, 130b)를 구성하여, 패키지 베이스 기판(20) 상에 부착될 수 있는 바, 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4)이 구성하는 서브 반도체 패키지를 각각 제1 내지 제4 서브 반도체 패키지라 호칭할 수 있다.

[0153] 적층 반도체 칩 구조체(210)는, 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4)이 각각 인접하는, 제1 내지 제4 변(212-1, 212-2, 212-3, 212-4)에 인접하며 연장되는 관통 전극 영역(220-1, 220-2, 220-3, 220-4)을 각각 포함할 수 있다.

[0154] 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4)이 적층 반도체 칩 구조체(210)보다 단위 면적당 발열량이 많을 경우, 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4)에서 발생한 열 중 적층 반도체 칩 구조체(210)를 향하여 전달되는 열은 관통 전극(228)을 통하여 외부로 방출될 수 있다. 따라서 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4)과 적층 반도체 칩 구조체(210) 사이에서 열집중 현상이 발생하는 것을 방지할 수 있고, 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4)에서 발생한 열에 의하여 적층 반도체 칩 구조체(210)에 포함되는 반도체 소자, 예를 들면 메모리 셀의 동작에 영향을 주는 것을 방지할 있기 때문에, 반도체 패키지(2k)의 동작 신뢰성을 얻을 수 있다.

[0155] 도 16은 본 발명의 일 실시 예에 따른 반도체 패키지에 포함되는 반도체 칩들의 배치를 나타내는 평면 배치도이다. 도 16에 대한 설명 중 도 15에 대한 설명과 중복되는 내용은 생략될 수 있다.

[0156] 도 16을 참조하면, 반도체 패키지(21)는 패키지 베이스 기판(20) 상에 부착되는 적층 반도체 칩 구조체(210)와 패키지 베이스 기판(20) 상에 부착되며 적층 반도체 칩 구조체(210)와 서로 인접하도록 배치되는 4개의 제1 반도체 칩(230-1, 230-2, 230-3, 230-4)을 포함한다.

[0157] 도 15에 보인 반도체 패키지(2k)와 도 16에 보인 반도체 패키지(21)는, 도 15에 보인 적층 반도체 패키지(210)는 제1 내지 제4 변(212-1, 212-2, 212-3, 212-4)에 인접하며 연장되는 관통 전극 영역(220-1, 220-2, 220-3, 220-4)이 서로 분리되어 있으나, 도 16에 보인 적층 반도체 패키지(210)는 제1 내지 제4 변(212-1, 212-2, 212-3, 212-4)에 인접하며 연장되는 관통 전극 영역(220)이 서로 연결된 형상을 가지고 있다는 점을 제외하고는 동일한 바, 자세한 설명은 생략하도록 한다.

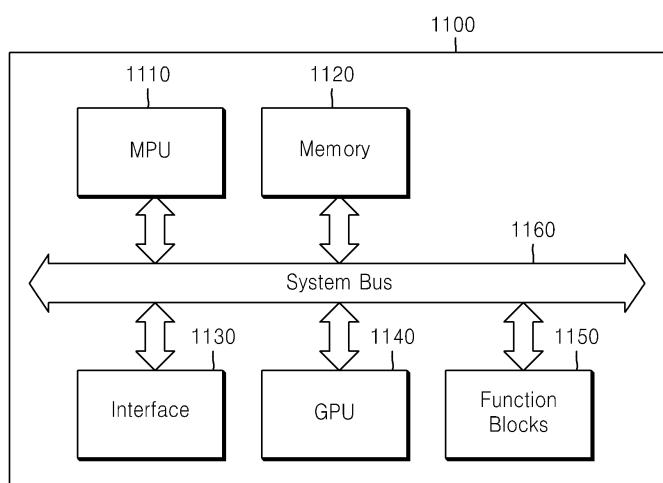

[0158] 도 17은 본 발명의 일 실시 예에 따른 반도체 패키지의 구성을 개략적으로 나타내는 도면이다.

[0159] 도 17을 참조하면, 반도체 패키지(1100)는 마이크로 처리 유닛(1110), 메모리(1120), 인터페이스(1130), 그래픽 처리 유닛(1140), 기능 블록들(1150) 및 이를 연결하는 버스(1160)을 포함할 수 있다. 반도체 패키지(1100)는 마이크로 처리 유닛(1110) 및 그래픽 처리 유닛(1140)을 모두 포함할 수도 있으나, 그 중 하나만을 포함할 수도 있다.

[0160] 마이크로 처리 유닛(1110)은 코어(core) 및 L2 캐시(cache)를 포함할 수 있다. 예를 들어, 마이크로 처리 유닛(1110)은 멀티-코어를 포함할 수 있다. 멀티-코어의 각 코어는 성능이 서로 동일하거나 상이할 수 있다. 또한 멀티-코어의 각 코어는 동시에 활성화되거나 서로 활성화되는 시점을 달리할 수 있다. 메모리(1120)는 마이크로 처리 유닛(1110)의 제어에 의해 기능 블록들(1150)에서 처리한 결과 등 저장할 수 있다. 예를 들어, 마이크로 처리 유닛(1110)은 의 L2 캐시에 저장된 내용이 플러시(flush)됨에 따라 메모리(1120)에 저장될 수 있다. 인터페이스(1130)는 외부의 장치들과의 인터페이스를 수행할 수 있다. 예를 들어, 인터페이스(1130)는 카메라, LCD 및 스피커 등과의 인터페이스를 수행할 수 있다.

[0161] 그래픽 처리 유닛(1140)은 그래픽 기능들을 수행할 수 있다. 예를 들면, 그래픽 처리 유닛(1140)은 비디오 코덱을 수행하거나, 3D 그래픽을 처리할 수 있다.

[0162] 기능 블록들(1150)은 다양한 기능들을 수행할 수 있다. 예를 들어, 반도체 패키지(1100)가 모바일 장치에 사용되는 AP인 경우, 기능 블록들(1150) 중 일부는 통신 기능을 수행할 수 있다.

[0163] 반도체 패키지(1100)는 도 1 내지 도 16에서 예시한 반도체 패키지(1a, 1b, 1c, 1d, 2a, 2b, 2c, 2d, 2e, 2f, 2g, 2h, 2i, 2j, 2k, 2l)일 수 있다. 마이크로 처리 유닛(1110) 및/또는 그래픽 처리 유닛(1140)은 도 1 내지 도 16에 예시한 제1 반도체 칩(130, 130-1, 130-2, 130-3, 130-4)일 수 있다. 메모리(1120)는 도 1 내지 도 16에서 예시한 적층 반도체 칩 구조체(100a, 100b, 210, 210a, 210b, 210c, 210d, 210e, 210f, 210g, 210h)이거나, 적층 반도체 칩 구조체(100a, 100b, 210, 210a, 210b, 210c, 210d, 210e, 210f, 210g, 210h)를 구성하는

복수의 제2 반도체 칩(110a, 110b, 110c, 110d, 110e) 중 적어도 하나의 반도체 칩일 수 있다.

[0164] 인터페이스(1130) 및 기능 블록들(1150)은 도 1 내지 도 16에 예시한 제1 반도체 칩(130, 130-1, 130-2, 130-3, 130-4)의 일부분에 해당되거나, 로직 반도체 칩인 제2 반도체 칩(110e)에 해당될 수 있다.

[0165] 반도체 패키지(1100)는 마이크로 처리 유닛(1110) 및/또는 그래픽 처리 유닛(1140)과 메모리(1120)를 함께 포함하며, 마이크로 처리 유닛(1110) 및/또는 그래픽 처리 유닛(1140)에서 발생하는 열을 빠르게 반도체 패키지(1100)의 외부로 방출할 수 있기 때문에, 반도체 패키지(1100) 내부에서 발생할 수 있는 부분적인 열집중 현상을 방지할 수 있고, 이에 따라서 반도체 패키지(1100)의 동작 신뢰성을 얻을 수 있다. 따라서 반도체 패키지(1100)는 고용량, 고성능 및 고신뢰성을 가질 수 있다.

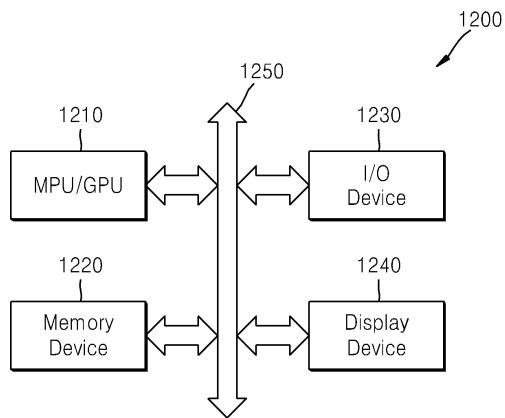

[0166] 도 18은 본 발명의 일 실시 예에 따른 반도체 패키지를 포함하는 전자 시스템을 나타내는 도면이다.

[0167] 도 18을 참조하면, 전자 시스템(1200)은 MPU/GPU(1210)가 장착될 수 있다. 전자 시스템(1200)은 예를 들면, 모바일 기기, 데스크 탑 컴퓨터 또는 서버일 수 있다. 또한, 전자 시스템(1200)은 메모리 장치(1220), 입출력 장치(1230), 디스플레이 장치(1240)를 더 포함할 수 있으며, 이를 구성요소들은 각각 버스(1250)에 전기적으로 연결될 수 있다. MPU/GPU(1210)와 메모리 장치(1220)는 도 1 내지 도 16에서 예시한 반도체 패키지(1a, 1b, 1c, 1d, 2a, 2b, 2c, 2d, 2e, 2f, 2g, 2h, 2i, 2j, 2k, 2l)일 수 있다.

[0168] 전자 시스템(1200)은 고성능의 MPU/GPU(1210)와 고용량의 메모리 장치(1220)를 가지면서도 내부 발열에 의한 신뢰성 저하를 방지할 수 있다.

[0169] 도 19는 본 발명의 실시 예에 따른 반도체 패키지가 응용된 전자 장치를 개략적으로 보여주는 사시도이다.

[0170] 도 19는 도 18의 전자 시스템(1200)이 모바일 폰(1300)에 적용되는 예를 보여주고 있다. 모바일 폰(1300)은 반도체 패키지(1310)를 포함할 수 있다. 반도체 패키지(1310)는 1 내지 도 16에서 예시한 반도체 패키지(1a, 1b, 1c, 1d, 2a, 2b, 2c, 2d, 2e, 2f, 2g, 2h, 2i, 2j, 2k, 2l)일 수 있다.

[0171] 모바일 폰(1300)은 고성능의 MPU/GPU와 고용량의 메모리 장치를 가지면서도 고신뢰성을 가지는 반도체 패키지(1310)가 포함될 수 있는 바, 소형화가 가능하고 고성능을 가질 수 있다.

[0172] 그밖에 전자시스템(1200)은 휴대용 노트북, MP3 플레이어, 네비게이션(Navigation), 고상 디스크(Solid state disk; SSD), 자동차 또는 가전제품(Household appliances)에 적용될 수 있다.

[0173] 이상, 본 발명을 바람직한 실시예를 들어 상세하게 설명하였으나, 본 발명은 상기 실시예에 한정되지 않고, 본 발명의 기술적 사상 및 범위 내에서 당 분야에서 통상의 지식을 가진 자에 의하여 여러가지 변형 및 변경이 가능하다.

### 부호의 설명

[0174] 1a, 1b, 1c, 1d, 2a, 2b, 2c, 2d, 2e, 2f, 2g, 2h, 2i, 2j, 2k, 2l : 반도체 패키지, 10 : 패키지 베이스 기판, 130, 230, 230-1, 230-2, 230-3, 230-4, : 제1 반도체 칩, 130a, 130b : 서브 반도체 패키지, 100a, 100b, 210, 210a, 210b, 210c, 210d, 210e, 210f, 210g, 210h : 적층 반도체 칩 구조체, 110, 110a, 110b, 110c, 110d, 110e : 제2 반도체 칩, 220, 220-1, 220-2, 220-3, 220-4, 220a, 220b, 220c, 220d, 222a, 222b, 222c, 222d, 224a, 224b, 224c, 224d, 224e, 224f, 224g, 224h, 226a, 226b, 226c, 226d, 227a, 227b, 227c, 227d : 관통 전극 영역, 228 : 관통 전극, 400 : 열 전달 물질층, 500 : 방열 부재

## 도면

## 도면1

## 도면2

도면3

## 도면4

## 도면5

도면6

도면7

## 도면8

## 도면9

2e

## 도면10

## 도면11

## 도면12

## 도면13

2i

## 도면14

2i

도면15

## 도면16

21

## 도면17

## 도면18

## 도면19

## 【심사관 직권보정사항】

## 【직권보정 1】

【보정항목】 청구범위

【보정세부항목】 청구항 17

## 【변경전】

제13 항에 있어서,

상기 열 절단 물질층은,

상기 제1 반도체 칩의 상면 및 상기 복수의 제2 반도체 칩 중 최상단의 제2 반도체 칩의 상면과 접하는 것을 특징으로 하는 반도체 패키지.

## 【변경후】

제13 항에 있어서,

상기 열 전달 물질층은,

상기 제1 반도체 칩의 상면 및 상기 복수의 제2 반도체 칩 중 최상단의 제2 반도체 칩의 상면과 접하는 것을 특징으로 하는 반도체 패키지.