(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5407474号

(P5407474)

(45) 発行日 平成26年2月5日(2014.2.5)

(24) 登録日 平成25年11月15日(2013.11.15)

(51) Int.Cl.

F 1

H01L 23/50 (2006.01)

H01L 23/12 (2006.01)H01L 23/50

H01L 23/50

H01L 23/12A

Y

L

請求項の数 1 (全 10 頁)

(21) 出願番号 特願2009-75139 (P2009-75139)

(22) 出願日 平成21年3月25日 (2009.3.25)

(65) 公開番号 特開2010-232216 (P2010-232216A)

(43) 公開日 平成22年10月14日 (2010.10.14)

審査請求日 平成24年2月20日 (2012.2.20)

(73) 特許権者 000003193

凸版印刷株式会社

東京都台東区台東1丁目5番1号

(74) 代理人 100089875

弁理士 野田 茂

(72) 発明者 戸田 順子

東京都台東区台東1丁目5番1号 凸版印

刷株式会社内

(72) 発明者 馬庭 進

東京都台東区台東1丁目5番1号 凸版印

刷株式会社内

(72) 発明者 塚本 健人

東京都台東区台東1丁目5番1号 凸版印

刷株式会社内

最終頁に続く

(54) 【発明の名称】半導体素子基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

金属板の厚さ方向の一方に位置する第1の面に、半導体素子搭載部と、半導体素子電極が接続される接続端子と、該接続端子から前記第1の面に沿って延在する配線と、前記半導体素子搭載部、前記接続端子および前記配線の周囲を囲むように延在する外枠部の四隅が前記外枠部の周囲を囲むように延在する金属片につながるように前記金属板を前記厚さ方向に貫通するスリットとを形成するための第1のフォトレジストパターンを形成する工程と、

前記金属板の厚さ方向の他方に位置する第2の面に、前記接続端子に接続される外部接続端子と、前記スリットとを形成するための第2のフォトレジストパターンを形成する工程と、

前記第2の面をエッチングして、前記外部接続端子を形成すると共に、前記第2の面に開口し、かつ、その底面の一部が前記配線の部分に対向する複数の凹部を形成する工程と、

前記複数の凹部を保護した状態で前記第2の面をエッチングして前記スリットを形成する工程と、

前記スリットと、前記複数の凹部を除く前記第2の面の部分とに樹脂が入り込まないように前記複数の凹部に樹脂を注入し加熱硬化させて前記第2の面と面一となる樹脂層を形成する工程と、

前記第1の面をエッチングして、前記半導体素子搭載部と、前記接続端子と、前記配線

10

20

とを形成する工程と、

を具備することを特徴とする半導体素子基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子の実装に好適な半導体パッケージ基板の技術に関するもので、特に、半導体素子基板の製造方法に関するものである。

【背景技術】

【0002】

QFP (Quad Flat Package) に代表されるリードフレームを用いた半導体パッケージでは、プリント配線基板との接続のためのアウターリードは、半導体パッケージの側面に配置されている。リードフレームは、金属板の両面に所望のフォトレジストパターンを形成し、両面からエッチングすることにより、半導体素子搭載部と半導体素子電極との接続部であるインナーリード、アウターリード及びこれらを固定している外枠部を得ることができる。

【0003】

また、リードフレームは、エッチング工法以外に、プレスによる打ち抜き加工によっても得ることができる。半導体パッケージの組立工程としては、半導体素子搭載部に半導体素子をダイボンディングしたのち、金ワイヤー等を用いて半導体素子の電極とインナーリードを電気的に接続する。その後、インナーリード部を含む半導体素子の近傍が樹脂封止され、外枠部が断裁され、必要に応じてアウターリードに曲げ加工が施される。

【0004】

このように、側面に設置されたアウターリードは、微細化の加工能力からみて、30mm角程度のパッケージサイズで200から300ピンが限界とされている。

【0005】

近年、半導体素子の電極数が増加するにつれて、アウターリードを側面に有するリードフレームタイプの半導体パッケージでは、端子数が対応しきれなくなり、一部、BGA (Ball Grid Array) やLGA (Land Grid Array) タイプ等プリント配線基板との外部接続端子がパッケージ基板底面でアレイ状に配置された半導体パッケージへ置き換わってきている。これらに用いられている基板は、両面が銅貼りであるガラスエポキシ基板にドリルで穴を開け、穴内をめっきで導通をとり、一方の面は半導体素子の電極と接続するための端子を、他方の面ではアレイ状に並べた外部接続端子を形成するのが一般的である。

【0006】

しかしながら、これらの基板の製造は、工程が複雑になり、コスト高になるとともに、基板内の配線接続にめっきが使用されているため、リードフレームタイプのパッケージに比べ、信頼性が劣るという問題がある。

【0007】

このため、リードフレームを両面からエッチングするという工程を利用して、リードフレームを用いたBGAタイプの半導体パッケージ構造が開示されている（例えば、特許文献1参照）。

【0008】

これは、表裏のフォトレジストのパターンを変えて、同時にエッチングするか、又は、片側をエッチングした後、エッチング面表層に電着ポリイミド樹脂層を形成した後、又は、プリモールド樹脂を塗布した後、他方の面からエッチングを加えることにより、一方の面には半導体素子電極の接続端子を形成し、他方の面にはアレイ状に外部接続端子を形成するものである。

【0009】

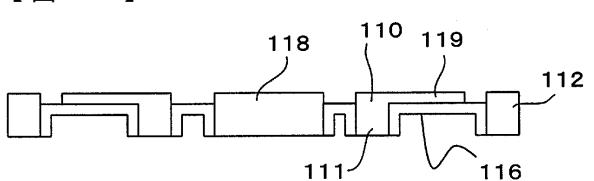

図11及び図12に従来の半導体素子基板を示す。図11及び図12に示すように、BGAタイプのリードフレームでは、外部接続端子111の数が増加すると、半導体素子電

10

20

30

40

50

極の接続端子 119 側の配線 110 長が長くなる。この配線 110 は、金属板をハーフエッティングして作製するもので、その幅も厚さも小さく、エッティング以降の工程で折れや曲がりが発生して収率は非常に悪くなるという問題があった。

#### 【0010】

特許文献 1 では、まず、外部接続端子 111 の側のみハーフエッティングを行い、エッティング面に電着ポリイミド層を形成した後、半導体素子電極接続端子 119 の側をエッティングで形成することを開示している。これにより、微細な配線 110 は、薄膜ではあるがポリイミド樹脂層 116 で担持され、リードフレーム作製時の配線の折れや曲がりは回避される。

#### 【0011】

しかしながら、本構造の半導体素子基板に半導体素子を搭載し、ワイヤーボンディングにより半導体素子電極と接続端子 119 を接続する際、接続端子 119 の下部は中空になっているため、ワイヤー接続の力がかからず、接続不良が発生し、組み立て収率を著しく落とすという問題があった。

#### 【0012】

特許文献 1 では、電着ポリイミド層に代わりプリモールド樹脂を充填することにより、ボンディング不良の問題をある程度回避させることができると推定される。しかし、凹部に充填されたプリモールド樹脂が硬化する際に、樹脂が収縮し、樹脂と外枠部の密着力が樹脂の収縮力に負けてしまうことにより、剥離がおきてしまうという問題が発生した。

#### 【先行技術文献】

#### 【特許文献】

#### 【0013】

【特許文献 1】特許第 3642911 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0014】

本発明の目的は、半導体素子の電極数の増加に対応し、信頼性が高く、作製及び半導体パッケージ組み立てを安定に行うことができる半導体素子基板の製造方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0015】

請求項 1 の発明に係る半導体素子基板の製造方法は、金属板の厚さ方向の一方に位置する第 1 の面に、半導体素子搭載部と、半導体素子電極が接続される接続端子と、該接続端子から前記第 1 の面に沿って延在する配線と、前記半導体素子搭載部、前記接続端子および前記配線の周囲を囲むように延在する外枠部の四隅が前記外枠部の周囲を囲むように延在する金属片につながるように前記金属板を前記厚さ方向に貫通するスリットとを形成するための第 1 のフォトレジストパターンを形成する工程と、前記金属板の厚さ方向の他方に位置する第 2 の面に、前記接続端子に接続される外部接続端子と、前記スリットとを形成するための第 2 のフォトレジストパターンを形成する工程と、前記第 2 の面をエッティングして、前記外部接続端子を形成すると共に、前記第 2 の面に開口し、かつ、その底面の一部が前記配線の部分に対向する複数の凹部を形成する工程と、前記複数の凹部を保護した状態で前記第 2 の面をエッティングして前記スリットを形成する工程と、前記スリットと、前記複数の凹部を除く前記第 2 の面の部分とに樹脂が入り込まないように前記複数の凹部に樹脂を注入し加熱硬化させて前記第 2 の面と面一となる樹脂層を形成する工程と、前記第 1 の面をエッティングして、前記半導体素子搭載部と、前記接続端子と、前記配線とを形成する工程と、を具備することを特徴とする。

#### 【発明の効果】

#### 【0016】

本発明によれば、プリント配線基板と接続するための外部接続端子を半導体素子基板の裏面全面にアレイ状に配置することが可能であり、半導体素子の多端子化に対応できる。

10

20

30

40

50

また、本発明によれば、リードフレームをベースにした基板であり、めっき配線を使用しないため、熱応力に対する信頼性を確保することができる。さらに、本発明によれば、本基板作製時において、配線の折れや曲がり等の不良が発生せず、半導体パッケージ組み立て工程であるワイヤーボンディング時において、スリットが設けられていることによって、プリモールド樹脂が凹部に充填された後、硬化する際に発生するプリモールド樹脂の応力が緩和されることにより、プリモールド樹脂が金属板から剥離してしまうことを防ぐことが可能となる。

【0017】

したがって、本発明によれば、半導体素子の電極数の増加に対応し、信頼性が高く、作製及び半導体パッケージ組み立てを安定に行うことができる。

10

【図面の簡単な説明】

【0018】

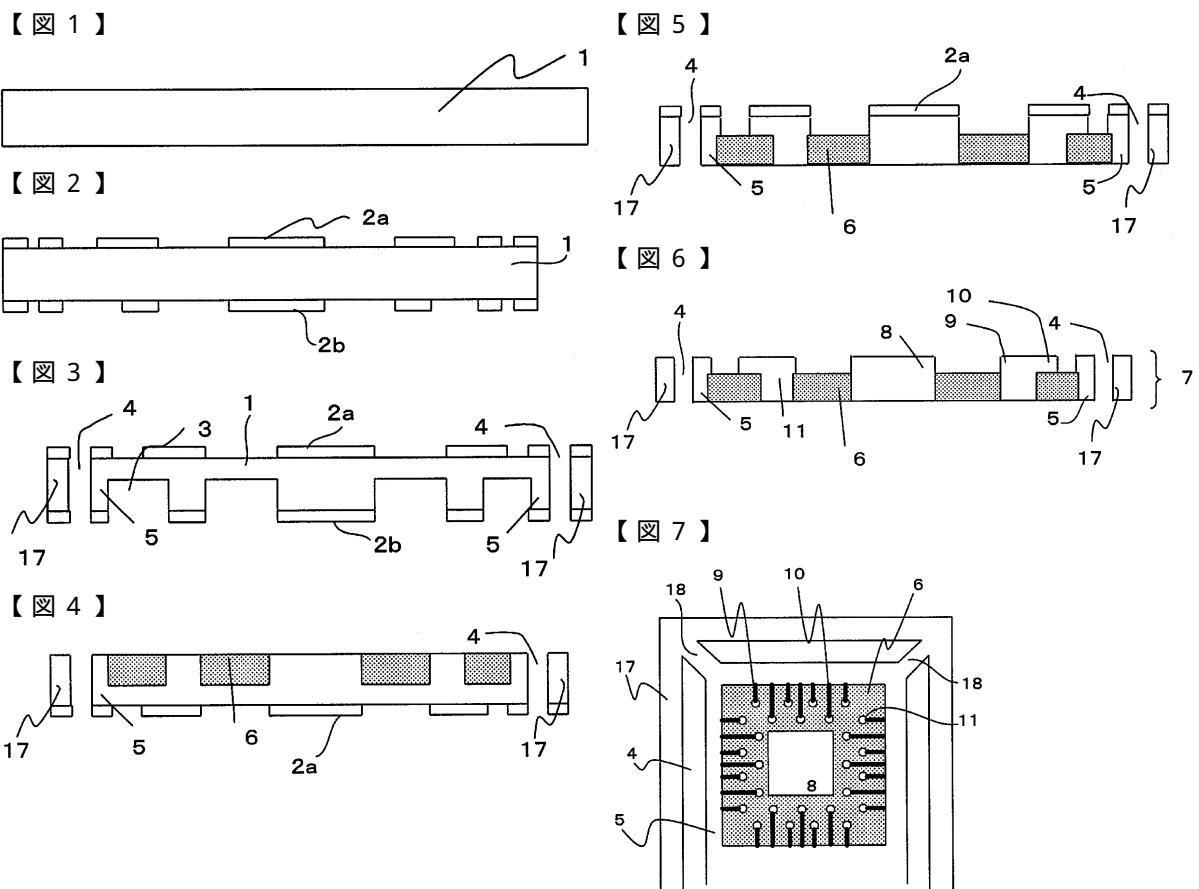

【図1】本発明の実施の形態1に係る半導体素子基板の製造方法の工程を説明するための概略断面である。

【図2】本発明の実施の形態1に係る半導体素子基板の製造方法の他の工程を説明するための概略断面である。

【図3】本発明の実施の形態1に係る半導体素子基板の製造方法の他の工程を説明するための概略断面である。

【図4】本発明の実施の形態1に係る半導体素子基板の製造方法の他の工程を説明するための概略断面である。

20

【図5】本発明の実施の形態1に係る半導体素子基板の製造方法の他の工程を説明するための概略断面である。

【図6】本発明の実施の形態1に係る半導体素子基板の製造方法の他の工程を説明するための概略断面である。

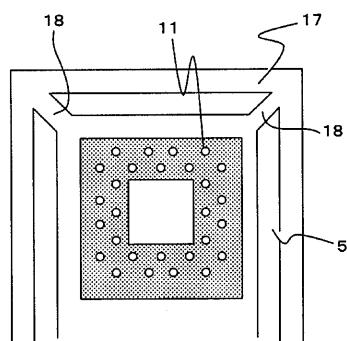

【図7】本発明の実施の形態1に係る半導体素子基板の一部を示す一部切欠平面図である。

【図8】本発明の実施の形態1に係る半導体素子基板の他の部を示す一部切欠平面図である。

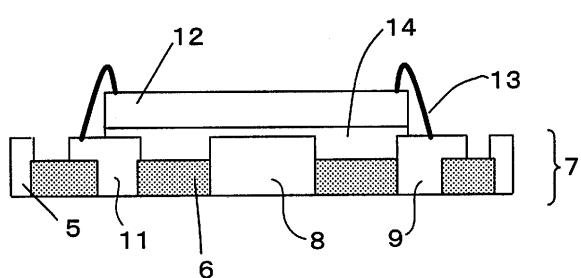

【図9】本発明の実施の形態2に係る半導体装置の製造方法の工程を説明するための略断面図である。

30

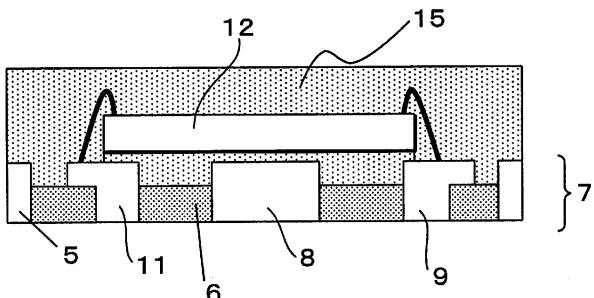

【図10】本発明の実施の形態2に係る半導体装置の製造方法の他の工程を説明するための略断面図である。

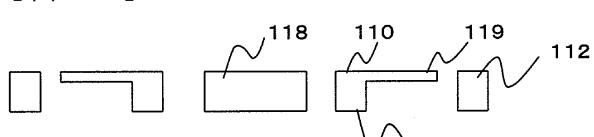

【図11】従来の半導体素子基板の製造方法の工程を説明するための略断面図である。

【図12】従来の半導体素子基板の製造方法の他の工程を説明するための略断面図である。

【発明を実施するための形態】

【0019】

次に、本発明の実施の形態について、図面を参照して詳細に説明する。

(実施の形態1)

図1～図6は、本発明の実施の形態1に係る半導体素子基板の製造方法の工程を説明するための概略断面である。

40

【0020】

図1及び図2に示すように、リードフレームに用いられる金属板1の上下面に、フォトレジストの第1のフォトレジストパターン2a及び第2のフォトレジストパターン2bが形成される。図2に示すように、金属板1の上面の第1のフォトレジストパターン2aは、半導体素子搭載部8、半導体素子電極との接続端子9、配線10、外枠部5及び当該外枠部5に少なくとも当該外枠部5の四隅と金属片17がつながるように金属板1の第2の面に貫通するスリット4を形成するためのものである(図6参照)。

【0021】

金属板1の上面の第2のフォトレジストパターン2bは、金属板1の第2の面に外部接

50

続端子 11、外枠部 5 及び当該外枠部 5 に少なくとも当該外枠部 5 の四隅と金属片 17 がつながるように金属板 1 の上面に貫通するスリット 4 を形成するためのものである（図 6 参照）。

#### 【 0 0 2 2 】

金属板 1 としては、リードフレームとしてのエッチング加工性、機械的強度、熱伝導性、膨張係数等を有していればいずれの材料を用いて良いが、42 合金に代表される鉄 - ニッケル系合金や、機械的強度を向上させるために各種金属元素を添加した銅系合金等が良く用いられる。

#### 【 0 0 2 3 】

次に、塩化第二鉄液等の金属板 1 を溶解するエッチング液を用いて金属板 1 は下面からエッチングが行なわれ、凹部 3 が形成される（図 3 参照）。凹部 3 の深さは、金属板 1 の残存部が最終的に配線になるため、第 2 回目の上面側からのエッチング時に微細の配線が形成できるように約 10 μm から 50 μm までの厚さが残されることが好ましい。 10

#### 【 0 0 2 4 】

次に、凹部 3 が貫通しないように、カバーフィルムで覆ったあと、エッチングが再度行われることによって、外枠部 5 にスリット 4 が形成される（図 3 参照）。この外枠部 5 にスリット 4 が形成されることにより、外枠部 5 に少なくとも当該外枠部 5 の四隅と当該外枠部 5 の金属片 17 とを連結する連結片 18 が形成される。

#### 【 0 0 2 5 】

次に、エッチング加工された金属板 1 の上下面を逆にして、金属板 1 の上面に液状のプリモールド樹脂からなる樹脂層 6 がスリット 4 に入らないように注入される（図 4 参照）。 20

#### 【 0 0 2 6 】

外枠部 5 の周囲にスリット 4 が設けられることによって、凹部 3 に充填されたプリモールド樹脂からなる樹脂層 6 が硬化した際に発生する応力が緩和され、樹脂層 6 が金属板 1 から剥離することを防ぐことが可能となる。

#### 【 0 0 2 7 】

さらに、金属板 1 の反対の面をエッチングして、半導体搭載部 8、半導体素子電極の接続端子 9、配線 10 が形成されて半導体素子基板 7 が作製された（図 5 及び図 6 参照）。 30

#### 【 0 0 2 8 】

図 7 は、本発明の実施の形態 1 に係る半導体素子基板の一部を示す一部切欠平面図である。図 8 は、本発明の実施の形態 1 に係る半導体素子基板の他の部を示す一部切欠平面図である。図 7 及び図 8 に示すように、外部接続端子 11 をアレイ状に配置することができ、半導体素子の多ピン化に対応が可能となった。また、スリット 4 が形成されることにより、外枠部 5 の少なくとも四隅が連結片 18 により金属片 17 とつながっている状態になっている。

#### 【 0 0 2 9 】

##### （実施の形態 2 ）

次に、本発明の実施の形態 2 について、図面を参照して説明する。図 9 は、本発明の実施の形態 2 に係る半導体装置の製造方法の工程を説明するための略断面図である。図 10 は、本発明の実施の形態 2 に係る半導体装置の製造方法の他の工程を説明するための略断面図である。本発明の実施の形態 2 においては、本発明の実施の形態 1 と同じ構成要素には同じ参照符号が付されて、その説明が省略される。 40

#### 【 0 0 3 0 】

図 9 に示すように、半導体素子基板 7 の半導体素子搭載部 8 の上にダイアタッチ材 14 により半導体素子 12 が搭載され、半導体素子 12 は金線 13 で半導体素子電極の接続端子 9 と接続される。必要に応じて、半導体素子電極の接続端子 9 には、ニッケル - 金めっき、錫めっき、銀めっき又はニッケル - パラジウム - 金めっきが施される。ワイヤーボンディングを行う際、本リードフレーム型の半導体素子基板 7 がヒートブロックの上に載せられ、加熱しながら接合が行うが、半導体素子電極の接続端子 9 の下部に樹脂層 6 が面一 50

で存在し、中空構造をとらないため、接合不良を起こさず組み立てることができる。

#### 【0031】

最後に、図10に示すように、半導体素子基板7の側がトランスマルード又はボッティングにより封止され、ダイヤモンドブレード等で外枠部5を分離させて、小片化される。BGAタイプであれば、はんだボールを外部接続端子11に搭載して、半導体素子基板7を用いた半導体装置(半導体パッケージ)が得られる。

#### 【0032】

##### (実施例1)

次に、本発明の実施例1について、図面を参照して詳細に説明する。本発明の実施例1は、LGA(Land Grid Array)タイプの半導体素子基板を製造する例についてのものである。10

#### 【0033】

製造したLGAのパッケージは、サイズが10mm角であり、パッケージの下面には168ピンのアレイ状の外部接続端子11を持つものである。

#### 【0034】

まず、図1に示すように、幅が150mmであり厚みが200μmの長尺帯状の銅合金製の金属板1(古河電工製、EFTEC64T)が用意された。次に、図2に示すように、この金属板1の両面に、ロールコーラーでフォトレジスト(東京応化(株)製、OPR4000)が5μmの厚さになるようにコーティングされた後、90°でプレベークが行われた。20

#### 【0035】

次に、所望のパターンを有するフォトマスクを介して両面からパターン露光が行われ、その後1%炭酸ナトリウム水溶液で現像処理が行われた後に水洗及びポストベークを行い、図2に示すようにフォトレジストパターン2a、2bが得られた。

#### 【0036】

金属板1の上面(第1の面)の第1のフォトレジストパターン2aは、半導体素子搭載部8、半導体素子電極との接続端子9、配線10、外枠部5及び当該外枠部5の周囲に少なくとも当該外枠部5の四隅と金属片17がつながるように金属いた1の第2の面上に貫通するスリット4を形成するためのものである(図6参照)。

#### 【0037】

金属板1の下面(第2の面)の第2のフォトレジストパターン2bは、金属板1の第2の面上に外部接続端子11、外枠部5及び当該外枠部5の周囲に少なくとも当該外枠部5の四隅と金属片17がつながるように金属板1の上面に貫通するスリット4を形成するためのものである(図6参照)。30

#### 【0038】

次に、金属板1の第1の面側をバックシートで覆って保護した後(図示せず)、塩化第二鉄溶液を用いて金属板の第2の面より第1回目のエッチング処理が行われ、第2の面側のフォトレジストパターン2bから露出した金属板1の部位を厚さを30μmまで薄くして凹部3が形成された(図3参照)。塩化第二鉄溶液の比重は液温50°で1.38とした。40

#### 【0039】

次に、凹部3が貫通しないように、カバーフィルムで保護した後(図示せず)、塩化第二鉄溶液を用いて、再びエッチング処理が行われ、第一の面まで貫通しているスリット4が形成された(図3参照)。塩化第二鉄溶液の比重は液温50°で1.38とした。

#### 【0040】

次に、第2面をエッチングした金属板1を、30°C、50g/Lの過硫酸アンモニウム水溶液に5分間浸漬して、第1回目のエッチングで形成されたエッチング面の表面が粗化された(図示せず)。さらに、金属板1が所定の水酸化ナトリウム水溶液系剥離液に浸漬され、第2面のフォトレジストが剥離された(図示せず)。

#### 【0041】

10

20

30

40

50

次に、第1回目のエッティングで形成された金属板1の第1の面に、スリット4の部分に入り込まないように、液状の熱硬化性の樹脂（信越化学工業製SMC-376KF1）が注入され、180°Cで3時間だけ本硬化が行われ、樹脂層6が形成された（図4参照）。熱硬化樹脂である樹脂層6の埋め込み性は良好で、ボイド等の不良は観察されなかった。外部接続端子11、外枠部5のエッティングされなかつた面上には、ほとんど熱硬化樹脂である樹脂層6が残存しなかつたが、その表面洗浄を兼ねて、60の過マンガン酸カリウムのアルカリ水溶液（40g/L過マンガン酸カリウム+20g/L水酸化ナトリウム）に3分ほど浸漬処理が行われた。

#### 【0042】

次に、金属板1の第1の面側のバックシートを除去後、塩化第二鉄溶液により金属板1の第1の面側より第2回目のエッティング処理が施されフォトレジストパターン2aから露出した金属板1の部位が溶解除去され、半導体素子搭載部8、半導体素子電極接続端子9、配線10が形成された（図5参照）。外部接続端子11は半導体素子電極接続端子9から延在している。なお図示していないが、金属板1の第2の面側に不要なエッティングが行われないように、第2回目のエッティング処理時には金属板1の第2の面側にバックシート等が貼り付けられるのが好ましい。

#### 【0043】

次に、金属板1の第1の面のフォトレジストパターン2aの剥離が行われ、所望のリードフレーム型LGA基板である半導体素子基板7が得られた（図6参照）。

#### 【0044】

次に、フォトレジストパターン2a、2bの剥離後、露出した金属板1の面に対し、電解ニッケル-金めっきが施された。ニッケルの厚さは5μmであり、金の厚さは0.1μmであった（図示せず）。

#### 【0045】

次に、リードフレーム型LGA基板である半導体素子基板7にダイアタッチ材14を用いて半導体素子12が搭載され、150°Cで1時間だけダイアタッチ材を14が硬化された。さらに、30μm径の金線を用いて、半導体素子12の電極と半導体素子電極の接続端子9がワイヤーボンディング接続された（図9参照）。ワイヤーボンディングの加熱温度は200°Cで行われ、半導体素子電極の接続端子9の側のワイヤーのブル強度を測定したところ、9g以上あり、良好な接続が得られた。

#### 【0046】

その後、図10に示すように、半導体素子12、半導体素子電極の接続端子9を含むエリアがトランスマーモールド15により封止され、小片に断裁して半導体素子基板7を用いた半導体装置（半導体パッケージ）が得られた。

#### 【0047】

本発明は、製造時の不良及び半導体パッケージ組立時の不良を低減し、熱応力に対する信頼性を高めたリードフレーム型基板を得ることが可能となり、特にリードフレームタイプの半導体パッケージでは対応できない多ピンパッケージ基板に適用される。

#### 【符号の説明】

#### 【0048】

- 1 金属板

- 2a、2b フォトレジストパターン

- 3 凹部

- 4 スリット

- 5 外枠部

- 6 樹脂層

- 7 半導体素子基板

- 8 半導体素子搭載部

- 9 半導体素子電極接続端子

- 10 配線

10

20

30

40

50

- 1 1 外部接続端子

1 2 半導体素子

1 3 金線

1 4 ダイアタッチ材

1 5 トランスマルト樹脂

1 6 電着ポリイミド層

1 7 金属片

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

---

フロントページの続き

審査官 山本 雄一

(56)参考文献 特開平09-307043(JP,A)

特開2002-198482(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/50

H01L 23/12