(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6356214号

(P6356214)

(45) 発行日 平成30年7月11日(2018.7.11)

(24) 登録日 平成30年6月22日(2018.6.22)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

P

請求項の数 6 (全 12 頁)

(21) 出願番号 特願2016-501859 (P2016-501859)

(86) (22) 出願日 平成26年3月13日 (2014.3.13)

(65) 公表番号 特表2016-511629 (P2016-511629A)

(43) 公表日 平成28年4月14日 (2016.4.14)

(86) 國際出願番号 PCT/US2014/025485

(87) 國際公開番号 WO2014/159935

(87) 國際公開日 平成26年10月2日 (2014.10.2)

審査請求日 平成29年2月15日 (2017.2.15)

(31) 優先権主張番号 13/828,044

(32) 優先日 平成25年3月14日 (2013.3.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】スイッチングレギュレータにおける100パーセントデューティサイクルのためのシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項1】

スイッチングレギュレータ回路であって、

入力電圧を受け取るための入力端子と、出力ノードに結合された出力端子とを有する第1のスイッチングトランジスタと、

期間を有するランプ信号を生成するためのランプジェネレータと、

前記ランプ信号および誤差信号を受信するための比較器と、前記比較器の出力は、フリップフロップに結合され、それに従って、変調信号を生成する、

を備え、

ここにおいて、第1の動作モードでは、前記ランプ信号は、前記誤差信号と交差するよう<sup>10</sup>

に増加し、それに従って、前記ランプ信号の各期間中の前記第1のスイッチングトラン

ジスタの状態を変化させ、第2の動作モードでは、前記誤差信号は、前記ランプ信号の最

大値を超えて増加し、それに従って、前記第1のスイッチングトランジスタは、前記ラン

プ信号の1つまたは複数の全期間にわたってオンにされる、

前記ランプジェネレータは、前記スイッチングレギュレータ回路における電流を感知して、前記ランプ信号におけるオフセットを生成するための電流フィードバック回路と、ここにおいて、前記ランプ信号の前記最大値は、前記誤差信号の最大値よりも小さい、

電流源と、

前記電流源に結合された端子を有するキャパシタと、

スイッチと、

10

20

リセット信号を受信するように結合された第1の入力と、前記変調信号を受信するように結合された第2の入力とを有する論理和ゲートと、ここにおいて、前記リセット信号が第1の状態にあるとき、前記ランプ信号は一定値を有し、前記リセット信号が第2の状態にあるとき、前記ランプ信号は前記最大値まで増加する、

ここにおいて、前記オフセットおよび前記電流源の大きさは、前記誤差信号の最大値よりも小さくなるように前記最大値を設定するように構成される、

をさらに備える、

スイッチングレギュレータ回路。

#### 【請求項2】

前記誤差信号は、前記出力ノードからのフィードバック電圧を受け取るように結合された第1の入力と、基準電圧に結合された第2の入力とを有する誤差増幅器によって生成される、請求項1に記載の回路。 10

#### 【請求項3】

クロック信号を受信して、前記リセット信号を生成するための分周器回路をさらに備え、前記クロック信号は、前記ランプ信号の前記期間を設定する、請求項1に記載の回路。

#### 【請求項4】

スイッチングレギュレータ回路において実行される方法であって、

第1のスイッチングトランジスタの入力端子で入力電圧を受け取ることと、前記第1のスイッチングトランジスタは、出力ノードに結合された出力端子を有し、

期間を有するランプ信号を生成することと、 20

前記ランプ信号と誤差信号を比較し、変調信号を生成するために前記比較された信号をフリップフロップにおいて記憶することと、

ここにおいて、第1の動作モードでは、前記ランプ信号は、前記誤差信号と交差するよう<sup>4</sup>に増加し、それに従って、前記ランプ信号の各期間中の前記第1のスイッチングトランジスタの状態を変化させ、第2の動作モードでは、前記誤差信号は、前記ランプ信号の最大値を超えて増加し、それに従って、前記第1のスイッチングトランジスタは、前記ランプ信号の1つまたは複数の全期間にわたってオンにされる、

前記スイッチングレギュレータ回路における電流を感知することと、

前記感知された電流に基づいて、前記ランプ信号におけるオフセットを生成することと、ここにおいて、前記ランプ信号の前記最大値は、前記誤差信号の最大値よりも小さい、

を備え、 30

ここにおいて、前記ランプ信号を生成することは、

キャパシタへの電流を生成することと、

前記変調信号およびリセット信号の論理和に応答して、前記キャパシタを放電することと

を備え、

ここにおいて、前記リセット信号が第1の状態にあるとき、前記ランプ信号は一定値を有し、前記リセット信号および変調信号の両方が第2の状態にあるとき、前記ランプ信号は前記最大値まで増加し、

ここにおいて、前記オフセットおよび前記キャパシタへの前記電流の大きさは、前記誤差信号の最大値よりも小さくなるように前記ランプ信号の前記最大値を設定するように構成される、方法。 40

#### 【請求項5】

前記誤差信号は、前記出力ノードからのフィードバック電圧と、基準電圧とに基づいて生成される、請求項4に記載の方法。

#### 【請求項6】

クロック信号を分周して、前記リセット信号を生成することをさらに備え、前記クロック信号は、前記ランプ信号の前記期間を設定する、請求項4に記載の方法。

#### 【発明の詳細な説明】

#### 【関連出願の相互参照】

10

20

30

40

50

**【0001】**

[0001]本開示は、あらゆる目的のために、その内容全体が参照により本明細書に組み込まれている、2013年3月14日に出願された米国非仮特許出願第13/828,044号の優先権を主張する。

**【背景技術】****【0002】**

[0002]本開示は、スイッチングレギュレータに関し、特に、スイッチングレギュレータにおける100%デューティサイクルのためのシステムおよび方法に関する。

**【0003】**

[0003]スイッチングレギュレータは、幅広い種類の電子アプリケーションで使用される。スイッチングレギュレータの1つの一般的なアプリケーションは、1つまたは複数の集積回路（I C）に調整された電圧を供給する電源電圧を生成することである。1つの実例的なスイッチングレギュレータが、バックレギュレータ（buck regulator）である。バックレギュレータでは、電源が入力電圧および入力電流を供給する。電源は、スイッチの1つの端子に結合され、これは、一般にスイッチングトランジスタ（例えば、PMOSトランジスタ）である。スイッチのもう1つの端子は、フィルタを通じて負荷に結合される。バックコンバータでは、出力電圧は、入力電圧よりも小さい。これは、典型的に、以下の式に従うデューティサイクルにおいてスイッチを開閉することによって達成される：

$$\text{デューティサイクル} = V_{\text{out}} / V_{\text{in}}$$

バックスイッチングレギュレータは、典型的に、100%よりも少ない、スイッチに対する最大デューティサイクル制限を有する。この制限は、電流モード（current mode）アーキテクチャにおけるスロープ補償のような、スイッチング期間ごとにリセットされる制御回路からの要求の結果である。バックレギュレータのためのコントローラが最大100%のデューティサイクルの動作をサポートすることができない場合、これは、 $V_{\text{out}} / \text{デューティサイクル}$ の係数（factor）によって、調整された出力をサポートする最小入力電圧に直接影響を及ぼす。

**【発明の概要】****【0004】**

[0004]本開示は、スイッチングレギュレータにおける100%デューティサイクルのためのシステムおよび方法を含む。スイッチングレギュレタ回路が、期間を有するランプ信号を生成するためのランプジェネレータと、ランプ信号および誤差信号を受信し、それに従って、変調信号を生成するための比較器とを含む。第1の動作モードでは、ランプ信号は、誤差信号と交差（intersect）するように増加し、それに従って、ランプ信号の各期間中のスイッチングトランジスタの状態を変化させる。第2の動作モードでは、誤差信号は、ランプ信号の最大値を超えて増加し、それに従って、スイッチングトランジスタは、ランプ信号の1つまたは複数の全期間（full periods）にわたってオンにされる。

**【0005】**

[0005]以下の詳細な説明および添付の図面は、本開示の特性および利点のより良い理解を提供する。

**【図面の簡単な説明】****【0006】**

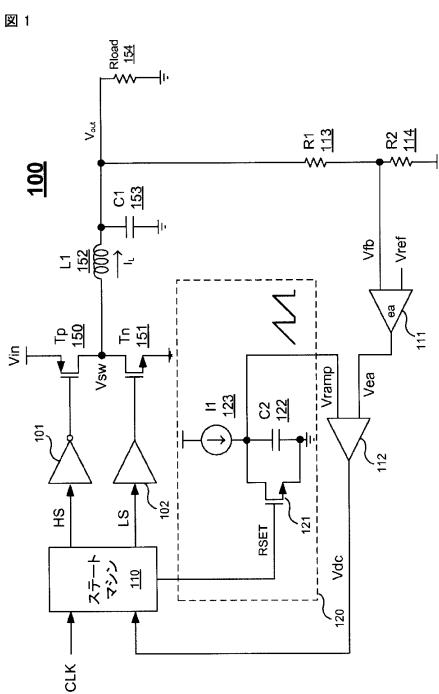

【図1】図1は、一実施形態によるスイッチングレギュレータを例示する。

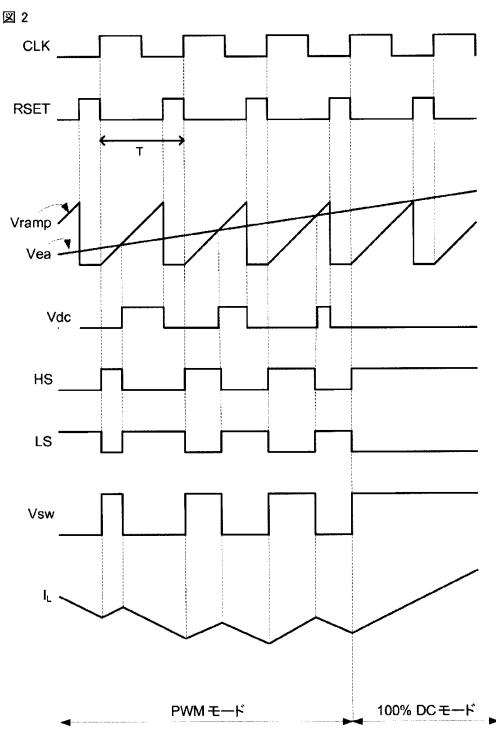

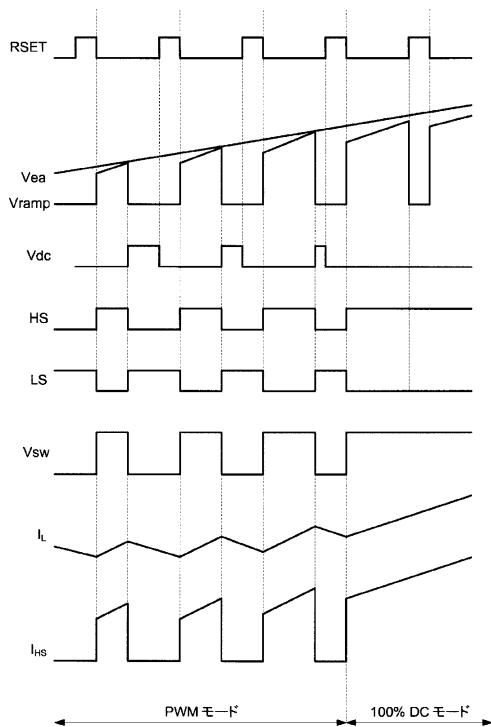

【図2】図2は、図1におけるスイッチングレギュレータに関連付けられる波形を例示する。

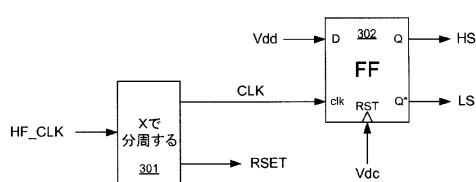

【図3】図3は、一実施形態によるスイッチングレギュレータにおける実例的な制御ロジックを例示する。

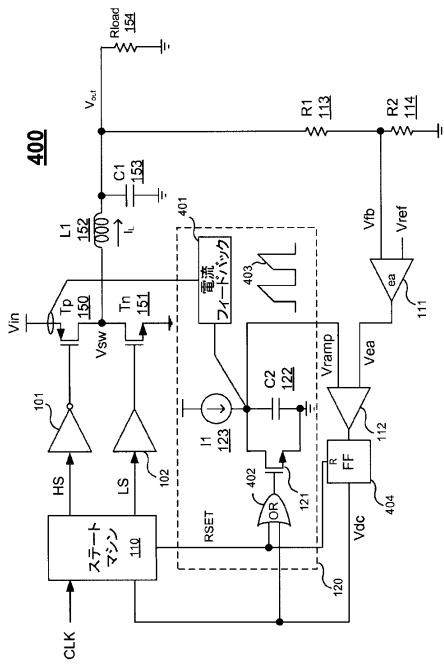

【図4】図4は、一実施形態によるスイッチングレギュレータを例示する。

【図5】図5は、図4におけるスイッチングレギュレータに関連付けられる波形を例示する。

**【発明を実施するための形態】**

10

20

30

40

50

## 【0007】

[0011]本開示は、スイッチングレギュレータに関する。以下の説明では、説明の目的のために、多数の例および特定の詳細が、本開示についての完全な理解を提供するために記載される。しかしながら、特許請求の範囲において表される本開示が、単独であるいは以下に説明される他の特徴との組み合わせにおいて、これらの例における特徴の一部またはすべてを含むことができ、また、ここに説明される特徴および概念の修正および同等物をさらに含むことができることは、当業者にとって明らかであろう。

## 【0008】

[0012]図1は、本開示の実施形態による実例的なスイッチングレギュレータ回路を例示する。スイッチングレギュレータ100は、PMOSトランジスタTp 150、NMOSトランジスタTn 151、インダクタL1 152、キャパシタC1 153、およびRload 154によって例示される負荷を含む。負荷は、例えば、集積回路のような、1つまたは複数の電子回路でありうる。Tpの一方の端子は、入力電圧Vinを受け取り、Tpの他方の端子は、電圧Vswを有するスイッチングノードに結合される。Tnの一方の端子は、スイッチングノードに結合され、Tnの他方の端子は、基準電圧（例えば、グランド）に結合される。TnおよびTpは、回路におけるノードを共に選択的に結合するスイッチとして機能する。この例では、TpはPMOSトランジスタであり、TnはNMOSトランジスタであるが、他のスイッチ構造および配置が使用されうることを理解されたい。ここで示される実例的なスイッチングレギュレータアーキテクチャは、ここで説明される技法を使用しうる多くのスイッチングトポロジのうちの1つにすぎない。

## 【0009】

[0013]ドライバ101および102は、TpおよびTnをオンおよびオフにする。Tpがオンであるとき、Tnはオフであり、VswはVinに等しい。この状態では、インダクタの両端の交流電圧は、Vin - Voutであり、インダクタ電流ILは増加する。この例で示されるバックコンバータアーキテクチャの場合、Vinは、Voutよりも大きい（ $Vin > Vout$ ）。Tnがオンであるとき、Tpはオフであり、Vswはグランドに等しい。この状態では、インダクタの両端の交流電圧は、-Voutであり、インダクタ電流ILは減少する。出力負荷へのインダクタ電流は、出力電圧Voutを生成する。この例では、フィードバックが、所定の電圧において出力電圧を維持するように動作する。以下に説明される他の実施形態では、電流は、例えば、フィードバックパラメータ（例えば、電流制御モード）として使用されうる。したがって、本開示の実施形態は、出力電圧、出力電流、または両方を感知するスイッチングレギュレータを含みうる。

## 【0010】

[0014]この例では、出力電圧Voutは、フィードバックとして使用される。1つの実例的なフィードバック回路は、抵抗器R1 113およびR2 114を含み、これは、Voutを受け取って、誤差増幅器（ea）111の入力へのフィードバック信号Vfbを生成しうる。誤差増幅器111はまた、誤差信号Ve aを生成するために、基準（例えば、このケースでは、電圧Vref）を受け取ることができる。Ve aは、出力電圧に基づくことができ、または他の実施形態では、出力電流に基づくことができる。この例では、誤差増幅器111の出力は、比較器112の入力に結合される。比較器112の別の入力は、ランプジェネレータ120に結合される。比較器112は、変調信号を生成するためにランプ信号と誤差信号を比較するための1つの実例的な手段である。ランプジェネレータ120は、ランプ信号Vrampを生成する。Vrampは、変調信号Vdcを生成するためにVe aと比較され、これは、TpおよびTnをオンおよびオフにする駆動信号HSおよびLSを生成するために、ステートマシン110に結合されうる。

## 【0011】

[0015]この例では、ランプジェネレータ120は、電流源123、キャパシタ（C2）122、および放電トランジスタ（discharge transistor）121を含む。電流源123、キャパシタ122、および放電トランジスタ121は、ランプ信号を生成するための1つの実例的な手段である。電流源123は、キャパシタ122への電流I1を生成する。

10

20

30

40

50

電流  $I_1$  が  $C_2$  に流れるにつれて、キャパシタ  $C_{22}$  上の電圧は、 $V_{ramp}$  を生成するためにほぼ線形に (approximately linearly) 増加する。ステートマシン  $110$  は、リセット信号  $RSET$  を生成する。この例では、トランジスタ  $121$  は、キャパシタ  $C_2$  を放電するスイッチとして機能する。例えば、 $RSET$  は、トランジスタ  $121$  をオンにし、キャパシタ  $C_{22}$  上に蓄積された電荷は、基準電圧（例えば、グランド）に結合される。 $RSET$  は、クロック信号  $CLK$  に関連する周期信号である。したがって、キャパシタ  $C_{22}$  上の電圧  $V_{ramp}$  は、 $RSET$  と同じ期間で、最大値まで線形に増加し、その後、グランドまで減少しうる。電流  $I_1$ 、キャパシタンス  $C_2$ 、基準電圧（例えば、グランド）、および  $RSET$  の期間とデューティサイクルは、 $V_{ramp}$  の最大値と最小値を決定しうる。以下により詳細に説明されるように、電流  $I_1$  の大きさが  $V_{ramp}$  のスロープを設定するので、例えば、電流源  $123$  からの電流  $I_1$  の大きさは、誤差信号の最大値よりも小さくなるようにランプ信号の最大値を設定するように構成されうる。

#### 【0012】

[0016] 図 2 は、図 1 におけるスイッチングレギュレータに関連付けられる波形を例示する。図 2 は、50% デューティサイクルと期間  $T$  を有するクロック信号  $CLK$  を示す。リセット信号  $RSET$  は、異なるデューティサイクルであるが、 $CLK$  と同じ期間を有しうる。ここで、 $RSET$  は、 $CLK$  の立ち上がりエッジの前に、ハイ (high) 状態に遷移する。 $CLK$  の立ち上がりエッジは、 $RSET$  をロー (low) 状態に遷移させる。上記で説明されたように、 $V_{ramp}$  は、 $RSET$  がローである間に増加する。 $RSET$  がハイ状態にあるとき、 $V_{ramp}$  は、一定値（例えば、グランド）にリセットされる。 $RSET$  がロー状態にあるとき、 $V_{ramp}$  は、最大値まで増加する。したがって、 $RSET$  の期間とデューティサイクルに関連する、 $RSET$  がロー状態にある時間期間は、誤差信号の最大値よりも小さくなるようにランプ信号の最大値を設定するように構成されうる。

#### 【0013】

[0017] 図 2 は、例示を目的として、値の範囲にわたって誤差信号  $V_{ea}$  を示す。 $V_{ramp}$  が増加するにつれて、それは、 $V_{ea}$  と交差しうる。 $V_{ramp}$  が  $V_{ea}$  よりも小さいとき、 $Vdc$ （比較器  $112$  の出力）はローであり、 $V_{ramp}$  が  $V_{ea}$  よりも大きいとき、 $Vdc$  はハイである。ランプがリセットされるとき、 $V_{ramp}$  は、再び  $V_{ea}$  と交差する。したがって、 $V_{ea}$  が、 $V_{ramp}$  の最大値よりも小さく、 $V_{ramp}$  の最小値（ここでは、グランド）よりも大きいとき、 $Vdc$  は、ランプ信号の各期間の間に（例えば、2回）状態の間を遷移する。例えば、 $V_{ramp}$  が増加して  $V_{ea}$  と交差したとき、 $Vdc$  は、ロー状態からハイ状態に遷移し、また、 $V_{ramp}$  がリセットされたとき、 $Vdc$  は、ハイ状態からロー状態に遷移する。

#### 【0014】

[0018] 図 2 に例示されるように、 $Vdc$  がハイである時間期間は、 $V_{ea}$  が増加するにつれて減少する。 $Vdc$  は、順に (in turn)、スイッチングトランジスタ  $Tp$  および  $Tn$  を制御するために使用されうる。この例では、ハイサイド駆動信号  $HS$  は、 $CLK$  の立ち上がりエッジとともにハイになり、ロー サイド駆動信号  $LS$  は、 $CLK$  の立ち上がりエッジとともにローになる。この状態では、 $Tp$  はオンであり、 $Tn$  はオフであり、スイッチノード  $Vsw$  は、 $Vin$  に等しい。この例では、これら駆動信号は、 $Vdc$  の立ち上がりエッジで遷移する。したがって、 $V_{ramp}$  が  $V_{ea}$  と交差すると、 $Vdc$  がハイになり、 $HS$  がローになり、 $LS$  がハイになることを引き起こす。この状態では、 $Tn$  はオンであり、 $Tp$  はオフであり、 $Vsw$  はグランドに等しい。 $V_{ea}$  が増加するにつれて、図 2 は、変調信号  $Vdc$  がハイである時間期間が減少することを例示する。その代わりに、 $HS$  がハイであり、 $LS$  がローである時間が増加し、これは、 $Tp$  についてのより長いオン時間および  $Tn$  についてのより長いオフ時間に対応し、これは、インダクタ電流を増加させる。

#### 【0015】

[0019] 一実施形態では、スイッチングレギュレータは、図 2 に例示されるように 2 つのモードで動作する。第 1 のモードでは、ランプ信号  $V_{ramp}$  は、誤差信号  $V_{ea}$  と交差

10

20

30

40

50

するように増加する。上記で説明されたように、 $V_{ea}$ における変化は、 $V_{dc}$ の変調をもたらし、 $T_p$ および $T_n$ の状態は、ランプ信号の各期間中に（例えば、オンからオフに）変化する。したがって、このモードは、PWMモードと称される。しかしながら、図2に例示されるように、第2の動作モードでは、誤差信号 $V_{ea}$ は、ランプ信号 $V_{ramp}$ の最大値を超えて増加する。したがって、スイッチングトランジスタ $T_p$ は、ランプ信号 $V_{ramp}$ の1つまたは複数の全期間にわたってオンにされる。 $T_p$ が全期間にわたってオンであるとき、デューティサイクルは100%である。しがたって、このモードは、100%デューティサイクルモード（100%D Cモード）と称される。例えば、負荷への電流が増加した場合、 $V_{out}$ および $V_{fb}$ は、降下することがあり得、 $V_{ea}$ を上昇させる。負荷電流 $I_L$ は、 $V_{ea}$ の値の範囲にわたって図2に例示される。示されるように、 $V_{ea}$ が $V_{ramp}$ の最大値を超えて増加したとき、デューティサイクルは100%であり、インダクタ電流は、 $V_{ramp}$ の複数の期間にわたって連続的に増加する。100%D Cモードでは、 $V_{out}$ は、最終的には $V_{in}$ とほぼ等しくなり、インダクタ電流のスロープは、ほぼゼロ（例えば、平坦（flat））になる。

#### 【0016】

[0020]本開示の特徴および利点は、 $V_{ramp}$ の最大値よりも大きい値を達成しうる誤差信号を含む。例えば、誤差増幅器111は、 $V_{ramp}$ の全範囲よりも、 $V_{fb}$ の入力の範囲に応答して、より広い出力電圧範囲を有しうる。特に、誤差増幅器111は、ランプ信号 $V_{ramp}$ の値の範囲よりも大きい値の範囲にわたって $V_{ea}$ を生成するために、 $V_{fb}$ と $V_{ref}$ の間の差を増幅する利得を有しうる。誤差増幅器111のためにインプリメントされる特定の利得は、設計パラメータに依存することができ、これは、例えば、出力電流および電圧、フィードバック抵抗分圧器（feedback resistor divider）（例えば、抵抗器113および114）の減衰、およびランプ信号の最小値、最大値、およびスロープ（例えば、 $I_1$ および $C_2$ ）を含む。

#### 【0017】

[0021]図3は、ステートマシン110における制御ロジックの一部を例示する。一実施形態では、高周波数クロック $H_F\_CLK$ は、スイッチング周波数クロック $CLK$ およびリセット信号 $RSET$ を生成するために分周（divided down）ができる。この例では、 $H_F\_CLK$ は、分周器回路（divider circuit）301によって受信される。分周器回路301は、 $CLK$ および $RSET$ を生成するために $H_F\_CLK$ を分周する。上記に例示されたように、 $CLK$ は、50%デューティサイクルを有することができ、 $RSET$ は、50%よりも少ないデューティサイクルを有する。 $RSET$ は、設定周波数において図1のキャパシタ $C_2$ を放電することによって、ランプ信号の期間を設定する。 $CLK$ は、ハイサイド駆動信号 $HS$ およびローサイド駆動信号 $LS$ を生成するために、フリップフロップ（FF）302によって受信される。この例では、FF302は、高い電圧（例えば、 $V_{dd}$ ）を受け取るための遅延入力（D）と、D入力における論理値を出力Qに転送（transfer）する $CLK$ 入力とを有する遅延タイプフリップフロップ（D-FF）である。変調信号 $V_{dc}$ は、FF302のリセット（RST）入力で受信される。FF302のQ出力は、 $HS$ 信号を生成し、 $Q^*$ （Qの論理反転）出力は、 $LS$ 信号を生成する。 $CLK$ および $RSET$ は、同じ期間を有し、図2の例では、 $HS$ および $LS$ の1つの遷移を制御する、 $CLK$ の立ち上がりエッジは、 $RSET$ の立ち下がりエッジと同時に起こり、これは、 $V_{ramp}$ をオンにする。したがって、 $HS$ および $LS$ の第1の遷移と、 $V_{dc}$ によって生成される第2の遷移との間の時間期間は、 $V_{ea}$ の値に対応する。

#### 【0018】

[0022]図4は、本開示の別の実施形態による実例的なスイッチングレギュレータ回路を例示する。スイッチングレギュレータ400は、スイッチングレギュレータ100と実質的に同じであるが、電流制御のために構成される。この例では、電流制御回路は、トランジスタ $T_p$ 150の端子（例えば、このケースでは、入力端子）に結合された入力を有する電流フィードバック回路401を含む。電流フィードバック回路401は、キャパシタ122の端子に結合された出力を有する。電流フィードバック回路401は、 $T_p$ にお

10

20

30

40

50

ける電流を感知し、これは、 $T_p$ がオンであるときの各期間の部分の間の出力電流に対応する。電流フィードバック回路401は、図4の403において例示されるように、ランプ信号 $V_{ramp}$ におけるオフセットを生成する。オフセットおよび電流源の大きさは、以下に説明されるように、誤差信号の最大値よりも小さくなるように $V_{ramp}$ の最大値を設定するように構成されうる。 $V_{ea}$ は、比較器112を使用して $V_{ramp}$ と比較される。この例では、比較器112の出力は、フリップフロップ404に結合される。フリップフロップ404の出力は、以下により詳細に説明されるように、変調信号 $V_{dc}$ を生成する。フリップフロップ404は、例えば、ステートマシン110の一部として含まれうるが、ここでは、例示を目的として、別個に示される。

## 【0019】

10

[0023]図5は、図4におけるスイッチングレギュレータ400に関連付けられる波形を例示する。図5に例示されるように、 $RSET$ がローになったとき、 $V_{ramp}$ は、出力電流に対応する第1のオフセット電圧まで増加し、その後、線形に増加し始める。最初に、 $T_p$ オンおよび $T_n$ オフ（出力電流の増加）に対応して、各クロック期間の始まりにおいて、 $V_{dc}$ はローであり、 $HS$ はハイであり、 $LS$ はローである。 $V_{ramp}$ が $V_{ea}$ と交差するとき、比較器112は、フリップフロップ404へのパルスを生成する。比較器112の出力は、ローからハイへの $V_{dc}$ における遷移を生成する。 $V_{dc}$ がハイになると、 $HS$ がローになり、 $LS$ がハイになり、 $T_p$ オフおよび $T_n$ オフ（出力電流の減少）に対応する。 $V_{dc}$ は、 $RSET$ の次の立ち上がりエッジまでハイのままである。 $RSET$ がローからハイに遷移するとき、 $V_{dc}$ は、FF404の出力においてローにリセットされる。この例では、キャパシタC2は、2つの状態 -  $V_{dc}$ ハイまたは $RSET$ ハイのいずれかに基づいてリセットされる。したがって、 $V_{ramp}$ が $V_{ea}$ に達した（meets）とき、 $V_{dc}$ はハイになり、 $V_{dc}$ は、 $V_{ramp}$ をグランドに設定するために、論理和ゲート402を通じてトランジスタ121に結合される。しかしながら、 $RSET$ がローからハイに遷移するので、 $V_{ramp}$ はグランドにどまり、これは、FF404をリセットし、 $V_{dc}$ をローにリセットするが、トランジスタ121をオンに維持する。

## 【0020】

20

[0024]図5は、 $V_{ramp}$ の最大値よりも大きい値を達成しうる誤差信号 $V_{ea}$ をさらに例示する。図1および図2における実施形態と同様に、誤差増幅器111は、 $V_{ramp}$ の全範囲よりも、 $V_{fb}$ の入力の範囲に応答して、より広い出力電圧範囲を有しうる。したがって、スイッチングレギュレータ400は、図5に例示されるように2つのモードで動作する。第1のモードでは、 $V_{ramp}$ は、誤差信号 $V_{ea}$ と交差するように増加する。上記で説明されたように、 $V_{ea}$ における変化は、 $V_{dc}$ の変調をもたらし、 $T_p$ および $T_n$ の状態は、ランプ信号の各期間中に（例えば、オンからオフに）変化する。したがって、このモードは、同様にPWMモードと称される。しかしながら、図5に例示されるように、第2の動作モードでは、誤差信号 $V_{ea}$ は、 $V_{ramp}$ の最大値を超えて増加する。したがって、スイッチングトランジスタ $T_p$ は、 $V_{ramp}$ の1つまたは複数の全期間にわたってオンにされる。 $T_p$ が全期間にわたってオンであるとき、デューティサイクルは100%である（100%D Cモード）。図5は、異なる動作モードおよび $V_{dc}$ の異なる状態についてのトランジスタ $T_p$ におけるハイサイド電流、インダクタ電流 $I_L$ 、およびスイッチングノード $V_{sw}$ を例示する。

## 【0021】

40

[0025]100%デューティサイクル動作を有することが有利である例は、スイッチドモードバッテリ充電器についてである。例えば、最大のバックデューティサイクルは、電力経路抵抗とともに、所与の充電電流と充電終止（フロート）電圧（end-of-charge(float) voltage）をサポートしうる最小の充電器入力電圧を決定しうる。100%デューティサイクル動作は、より低い入力電圧および/またはより高い充電電流を可能にするために、バッテリ充電器アプリケーションにおいて使用されうる。

## 【0022】

50

[0026]上記説明は、どのように特定の実施形態の様がインプリメントされうるかの例とともに、本発明の様々な実施形態を例示する。上記例は、唯一の実施形態であるように見なされるべきではなく、以下の特許請求の範囲によって定義される特定の実施形態の柔軟性および利点を例示するために示された。上記開示および以下の特許請求の範囲に基づいて、他の配置、実施形態、インプリメンテーションおよび同等物が、特許請求の範囲によって定義される本開示の範囲から逸脱することなく用いられる。

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

[ C 1 ]

入力電圧を受け取るための入力端子と、出力ノードに結合された出力端子とを有する第1のスイッチングトランジスタと、

10

期間を有するランプ信号を生成するためのランプジェネレータと、

前記ランプ信号および誤差信号を受信し、それに従って、変調信号を生成するための比較器と

を備え、

ここにおいて、第1の動作モードでは、前記ランプ信号は、前記誤差信号と交差するよう

に増加し、それに従って、前記ランプ信号の各期間中の前記第1のスイッチングトラン

ジスタの状態を変化させ、第2の動作モードでは、前記誤差信号は、前記ランプ信号の最

大値を超えて増加し、それに従って、前記スイッチングトランジスタは、前記ランプ信号

の1つまたは複数の全期間にわたってオンにされる、

スイッチングレギュレータ回路。

20

[ C 2 ]

前記誤差信号は、前記出力ノードからのフィードバック電圧を受け取るように結合され

た第1の入力と、基準電圧に結合された第2の入力とを有する誤差増幅器によって生成さ

れる、C 1 に記載の回路。

[ C 3 ]

前記ランプジェネレータは、

電流源と、

前記電流源に結合された端子を有するキャパシタと、

スイッチと

を備え、

ここにおいて、前記電流源の大きさは、前記誤差信号の最大値よりも小さくなるように

前記ランプ信号の前記最大値を設定するように構成される、C 1 に記載の回路。

30

[ C 4 ]

前記ランプジェネレータは、リセット信号を受信し、前記リセット信号が第1の状態に

あるとき、前記ランプ信号は一定値を有し、前記リセット信号が第2の状態にあるとき、

前記ランプ信号は前記最大値まで増加し、前記リセット信号の前記第2の状態の時間期間

は、前記誤差信号の最大値よりも小さくなるように前記ランプ信号の前記最大値を設定す

るように構成される、C 1 に記載の回路。

[ C 5 ]

クロック信号を受信して、前記リセット信号を生成するための分周器回路をさらに備え

、前記クロック信号は、前記ランプ信号の前記期間を設定する、C 4 に記載の回路。

40

[ C 6 ]

前記ランプジェネレータは、前記スイッチングレギュレータにおける電流を感知して、

前記ランプ信号におけるオフセットを生成するための電流フィードバック回路をさらに備

え、ここにおいて、前記ランプ信号の前記最大値は、前記誤差信号の最大値よりも小さい

、C 1 に記載の回路。

[ C 7 ]

前記ランプジェネレータは、

電流源と、

前記電流源に結合された端子を有するキャパシタと、

50

スイッチと、

リセット信号を受信するように結合された第1の入力と、前記変調信号を受信するよう

に結合された第2の入力とを有する論理和ゲートと、ここにおいて、前記リセット信号が

第1の状態にあるとき、前記ランプ信号は一定値を有し、前記リセット信号が第2の状態

にあるとき、前記ランプ信号は前記最大値まで増加する、

を備え、

ここにおいて、前記オフセットおよび前記電流源の大きさは、前記誤差信号の最大値よ

りも小さくなるように前記最大値を設定するように構成される、C 6 に記載の回路。

[ C 8 ]

第1のスイッチングトランジスタの入力端子で入力電圧を受け取ることと、前記スイッ

チングトランジスタは、出力ノードに結合された出力端子を有し、

期間を有するランプ信号を生成することと、

変調信号を生成するために前記ランプ信号と誤差信号を比較することと

を備え、

ここにおいて、第1の動作モードでは、前記ランプ信号は、前記誤差信号と交差するよ

うに増加し、それに従って、前記ランプ信号の各期間中の前記第1のスイッチングトラン

ジスタの状態を変化させ、第2の動作モードでは、前記誤差信号は、前記ランプ信号の最

大値を超えて増加し、それに従って、前記スイッチングトランジスタは、前記ランプ信号

の1つまたは複数の全期間にわたってオンにされる、方法。

[ C 9 ]

前記誤差信号は、前記出力ノードからのフィードバック電圧と、基準電圧とに基づいて

生成される、C 8 に記載の方法。

[ C 10 ]

前記ランプ信号を生成することは、

キャパシタへの電流を生成することと、

第1の信号に応答して、前記キャパシタを放電することと

を備え、

ここにおいて、前記電流の大きさは、前記誤差信号の最大値よりも小さくなるように前

記ランプ信号の前記最大値を設定するように構成される、C 8 に記載の方法。

[ C 11 ]

前記ランプ信号を生成することは、

リセット信号を受信することを備え、ここにおいて、前記リセット信号が第1の状態に

あるとき、前記ランプ信号は一定値を有し、前記リセット信号が第2の状態にあるとき、

前記ランプ信号は前記最大値まで増加し、前記リセット信号の前記第2の状態の時間期間

は、前記誤差信号の最大値よりも小さくなるように前記ランプ信号の前記最大値を設定す

るよう構成される、C 8 に記載の方法。

[ C 12 ]

クロック信号を分周して、前記リセット信号を生成することをさらに備え、前記クロッ

ク信号は、前記ランプ信号の前記期間を設定する、C 11 に記載の方法。

[ C 13 ]

前記スイッチングレギュレータにおける電流を感知することと、

前記感知された電流に基づいて、前記ランプ信号におけるオフセットを生成することと

、ここにおいて、前記ランプ信号の前記最大値は、前記誤差信号の最大値よりも小さい、

をさらに備える、C 8 に記載の方法。

[ C 14 ]

前記ランプ信号を生成することは、

キャパシタへの電流を生成することと、

前記変調信号およびリセット信号の論理和に応答して、前記キャパシタを放電すること

と

を備え、

10

20

30

40

50

ここで、前記リセット信号が第1の状態にあるとき、前記ランプ信号は一定値を有し、前記リセット信号および変調信号の両方が第2の状態にあるとき、前記ランプ信号は前記最大値まで増加し、

ここで、前記オフセットおよび前記電流源の大きさは、前記誤差信号の最大値よりも小さくなるように前記ランプ信号の前記最大値を設定するように構成される、C 1 3に記載の方法。

### [ C 1 5 ]

入力電圧を受け取るための入力端子と、出力ノードに結合された出力端子とを有する第1のスイッチングトランジスタと、

ランプ信号を生成するための手段と、前記ランプ信号は、期間を有し、

10

変調信号を生成するために前記ランプ信号と誤差信号を比較するための手段とを備え、

ここで、第1の動作モードでは、前記ランプ信号は、前記誤差信号と交差するようになりますし、それに従って、前記ランプ信号の各期間中の前記第1のスイッチングトランジスタの状態を変化させ、第2の動作モードでは、前記誤差信号は、前記ランプ信号の最大値を超えて増加し、それに従って、前記スイッチングトランジスタは、前記ランプ信号の1つまたは複数の全期間にわたってオンにされる、

スイッチングレギュレータ回路。

【図1】

【図2】

Fig. 1

Fig. 2

【図3】

図3

Fig. 3

【図4】

図4

Fig. 4

【図5】

図5

Fig. 5

---

フロントページの続き

(72)発明者 ゴンカルベス、リカルド・ティー .

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 シュトックスタッド、トロイ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 ルツコウスキ、ジョセフ・ティー .

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 小林 秀和

(56)参考文献 特開2005-168221(JP, A)

特開2008-236822(JP, A)

特開2009-219179(JP, A)

特開2009-148157(JP, A)

米国特許出願公開第2009/0102440(US, A1)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155