(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5156235号

(P5156235)

(45) 発行日 平成25年3月6日(2013.3.6)

(24) 登録日 平成24年12月14日(2012.12.14)

(51) Int.Cl.

F 1

**H01L 21/338 (2006.01)**

**H01L 29/778 (2006.01)**

**H01L 29/812 (2006.01)**

**H01L 21/306 (2006.01)**

H01L 29/80

H

H01L 21/306

B

請求項の数 23 (全 17 頁)

(21) 出願番号 特願2006-549235 (P2006-549235)

(86) (22) 出願日 平成16年9月28日 (2004.9.28)

(65) 公表番号 特表2007-518265 (P2007-518265A)

(43) 公表日 平成19年7月5日 (2007.7.5)

(86) 國際出願番号 PCT/US2004/031756

(87) 國際公開番号 WO2005/076365

(87) 國際公開日 平成17年8月18日 (2005.8.18)

審査請求日 平成19年8月28日 (2007.8.28)

(31) 優先権主張番号 10/758,871

(32) 優先日 平成16年1月16日 (2004.1.16)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 592054856

クリー インコーポレイテッド

C R E E I N C.

アメリカ合衆国 ノースカロライナ州 2

7703 ダラム シリコン ドライブ

4600

(74) 代理人 110000855

特許業務法人浅村特許事務所

(74) 代理人 100066692

弁理士 浅村 瞥

(74) 代理人 100072040

弁理士 浅村 肇

(74) 代理人 100159525

弁理士 大日方 和幸

最終頁に続く

(54) 【発明の名称】窒化物ベースのトランジスタの製作方法

## (57) 【特許請求の範囲】

## 【請求項 1】

窒化物ベースの半導体チャネル層上に、窒化物ベースの半導体バリア層を形成するステップと、

前記窒化物ベースの半導体バリア層のゲート領域上に、保護層を形成するステップと、

前記バリア層上に、パターニングされた複数のオーム接点金属領域を形成するステップと、

第1および第2のオーム接点を形成するために、前記パターニングされたオーム接点金属を、前記ゲート領域上に前記保護層を載せたままアニールするステップと、

前記保護層全体を除去するステップと、

前記バリア層の前記ゲート領域上に、ゲート接点を形成するステップと

を有することを特徴とするトランジスタを製作する方法。

## 【請求項 2】

前記保護層は、窒化アルミニウム層、窒化ケイ素(SiN)層、および/または二酸化ケイ素(SiO<sub>2</sub>)層を含むことを特徴とする請求項1に記載の方法。

## 【請求項 3】

前記保護層を除去するステップは、低損傷エッチング技術を利用して前記保護層を除去するステップを含むことを特徴とする請求項1に記載の方法。

## 【請求項 4】

前記低損傷エッチング技術は、強塩基を使用する湿式エッチングを含むことを特徴とす

10

20

る請求項 3 に記載の方法。

【請求項 5】

前記保護層を除去し、それに続いて、前記バリア層の複数の露出部分上にパッシベーション層を形成するステップを特徴とする請求項 1 に記載の方法。

【請求項 6】

前記ゲート接点を形成するステップは、

前記バリア層の前記ゲート領域の一部分を露出させるために、低損傷エッチング技術を利用して、前記パッシベーション層に陥凹部をエッチングするステップと、

前記パッシベーション層の前記陥凹部中に、前記ゲート接点を形成するステップとを含むことを特徴とする請求項 5 に記載の方法。 10

【請求項 7】

前記ゲート接点を形成するステップは、前記パッシベーション層を貫通して前記バリア層に接触するゲート接点を形成するステップを含むことを特徴とする請求項 5 に記載の方法。

【請求項 8】

前記保護層を形成するステップは、前記バリア層上に、パターニングされた保護層を形成するステップを含み、前記パターニングされた保護層は、前記ゲート領域に対応する前記バリア層の第 1 の部分を覆い、それに隣接すると共に前記第 1 および第 2 のオーム接点に対応する、前記バリア層の第 2 の部分を露出させ、パターニングされた複数のオーム接点金属領域を形成するステップは、前記バリア層の前記第 2 の部分上に、パターニングされた複数のオーム接点金属領域を形成するステップを含み、前記パターニングされた複数のオーム接点金属領域は、前記パターニングされた保護層に隣接すると共にそれから離隔されることを特徴とする請求項 1 に記載の方法。 20

【請求項 9】

前記パターニングされた保護層を形成するステップは、

前記バリア層上に、保護層材料をプランケット堆積させるステップと、

前記プランケット堆積させた保護層材料上に、前記第 1 および第 2 のオーム接点の位置に対応するウインドウを有するマスクを形成するステップと、

低損傷エッチング技術を利用して、前記ウインドウを通して、前記プランケット堆積させた保護層をエッチングするステップと、 30

前記マスクを除去するステップと

を含むことを特徴とする請求項 8 に記載の方法。

【請求項 10】

前記第 1 および第 2 のオーム接点の位置に対応する前記ウインドウは、前記第 1 および第 2 のオーム接点の面積よりも大きいことを特徴とする請求項 9 に記載の方法。

【請求項 11】

前記バリア層の前記第 2 の部分上に、前記パターニングされた保護層に隣接すると共にそれから離隔される、パターニングされた複数のオーム接点金属領域を形成するステップは、前記マスクを除去する前に実施されることを特徴とする請求項 9 に記載の方法。

【請求項 12】

前記パッシベーション層は、窒化ケイ素を含むことを特徴とする請求項 5 に記載の方法。 40

。

【請求項 13】

前記窒化物ベースのチャネル層を設けるために、III族窒化物層を形成するステップをさらに含み、窒化物ベースの半導体バリア層を形成するステップは、III族窒化物層を形成するステップを含むことを特徴とする請求項 1 に記載の方法。

【請求項 14】

前記チャネル層は、 $A_1 \times G_a 1 - x N$  (ただし  $0 < x < 1$ ) の組成を有し、前記チャネル層の前記バンドギャップは、前記バリア層の前記バンドギャップよりも小さいことを特徴とする請求項 13 に記載の方法。 50

**【請求項 15】**

前記チャネル層は、窒化アルミニウムガリウム (AlGaN)、窒化ガリウム (GaN)、窒化インジウムガリウム (InGaN)、および / または窒化アルミニウムインジウムガリウム (AlInGaN) を含み、前記バリア層は、窒化アルミニウム (AlN)、窒化アルミニウムインジウム (AlInN)、AlGaN、GaN、InGaN、および / または AlInGaN を含むことを特徴とする請求項 14 に記載の方法。

**【請求項 16】**

前記バリア層は、複数の層を含むことを特徴とする請求項 1 に記載の方法。

**【請求項 17】**

基板上にバッファ層を形成するステップと、

10

前記窒化物ベースのチャネル層を設けるために、前記バッファ層上に III 族窒化物チャネル層を形成するステップと

をさらに有することを特徴とする請求項 1 に記載の方法。

**【請求項 18】**

前記チャネル層および前記バリア層は、高電子移動度トランジスタ (HEMT) をなすように構成されることを特徴とする請求項 1 に記載の方法。

**【請求項 19】**

前記窒化物ベースのチャネル層は、SiC 基板上に形成されることを特徴とする請求項 1 に記載の方法。

**【請求項 20】**

20

前記保護層は、前記オーム接点材料の厚さと少なくとも同じ厚さに形成されることを特徴とする請求項 1 に記載の方法。

**【請求項 21】**

前記保護層は、5.0 nmから500 nmの厚さを有することを特徴とする請求項 1 に記載の方法。

**【請求項 22】**

前記パッシベーション層を形成するステップは、in-situ で実施されることを特徴とする請求項 5 に記載の方法。

**【請求項 23】**

前記パッシベーション層を形成するステップは、MOCVD 成長を使用して前記パッシベーション層を成長させることを含むことを特徴とする請求項 22 に記載の方法。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体デバイスに関し、より詳細には、窒化物ベースの活性層を組み込んだトランジスタに関する。

**【背景技術】****【0002】**

シリコン (Si) やガリウムヒ素 (GaAs) などの材料は、より低電力および (Si の場合には) より低周波用途向けの半導体デバイスに幅広く応用されてきている。しかし、よく知られているように、これらの半導体材料は、比較的小さなバンドギャップ (例えば、室温で、Si の場合には 1.12 eV、GaAs の場合には 1.42 eV) および / または比較的小さな破壊電圧のため、より高電力および / またはより高周波用途向けには適していない。

40

**【0003】**

Si および GaAs が示す難点に照らして、高電力、高温および / または高周波の用途ならびにデバイスにおける関心は、炭化ケイ素 (-SiC の場合には、室温で 2.996 eV) や III 族窒化物 (例えば、GaN の場合には、室温で 3.36 eV) などの広バンドギャップの半導体材料に移ってきた。これらの材料は一般に、ガリウムヒ素およびシリコンと比べて、より高い電界破壊強度およびより高い電子飽和速度を有する。

50

## 【0004】

高電力および／または高周波用途向けの、特に关心が寄せられているデバイスは、高電子移動度トランジスタ（HEMT）であり、これは変調ドープ電界効果トランジスタ（MODFET）としても知られる。これらのデバイスでは、異なるバンドギャップエネルギーを有し、かつバンドギャップが小さい方の材料がより高い電子親和力を有する2種類の半導体材料のヘテロ接合部で、2次元電子ガス（2DEG）が形成されるので、いくつかの状況のもとで、動作上の利点をもたらすことができる。2DEGは、非ドープの（「意図的でなくドープされた」）、バンドギャップが小さい方の材料中の蓄積層であり、例えば $10^{13}$ キャリア/ $\text{cm}^2$ を上回る、非常に高いシート電子濃度を有することができる。さらに、バンドギャップが広い方の半導体中からの電子が2DEGに移動し、そこではイオン化不純物散乱が低減されているため、高い電子移動度を持つことが可能になる。10

## 【0005】

高キャリア濃度と高キャリア移動度がこのように組み合わさることにより、非常に大きな相互コンダクタンスをHEMTに与えることができ、また高周波用途向けの金属半導体電界効果トランジスタ（MESFET）に勝る、大きな性能上の利点をもたらすことができる。

## 【0006】

【特許文献1】米国特許第5192987号明細書

【特許文献2】米国特許第5296395号明細書

【特許文献3】米国特許第6316793号明細書20

【特許文献4】米国特許出願公開第2002/0066908号明細書

【特許文献5】米国特許仮出願第60/290195号明細書

【特許文献6】米国特許出願公開第2002/0167023号明細書

【特許文献7】米国特許出願第10617843号明細書

【特許文献8】米国特許出願公開第2003/0102482号明細書

【特許文献9】米国特許仮出願第60/337687号明細書

【特許文献10】米国再発行特許第34861号明細書

【特許文献11】米国特許第4946547号明細書

【特許文献12】米国特許第5200022号明細書

【特許文献13】米国特許第6218680号明細書30

【特許文献14】米国特許第5210051号明細書

【特許文献15】米国特許第5393993号明細書

【特許文献16】米国特許第5523589号明細書

【特許文献17】米国特許第5292501号明細書

【非特許文献1】Yuet al., “Schottky barrier engineering in III-V nitrides via the piezoelectric effect”, Applied Physics Letters, Vol. 73, No. 13, 1998

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0007】

窒化ガリウム／窒化アルミニウムガリウム（GaN／AlGaN）材料系で製作される高電子移動度トランジスタは、前述の高破壊電界、それらの材料の広いバンドギャップ、大きな伝導帯オフセット、および／または高飽和電子ドリフト速度を含めた材料特性を併せもつたため、大きな高周波電力を発生する可能性を有する。2DEG中の電子の大部分は、AlGaN中の分極によるものとされている。GaN／AlGaN系によるHEMTは、これまでに示されている。AlGaN／GaN HEMT構造および製造方法は、文献に記載されている（特許文献1、特許文献2参照）。半絶縁性炭化ケイ素基板、基板上に窒化アルミニウムバッファ層、バッファ層上に絶縁性窒化ガリウム層、窒化ガリウム層上に窒化アルミニウムガリウムバリア層、窒化アルミニウムガリウムの活性構造上にパッシベーション層を有するHEMTデバイスが、文献に記載されている（特許文献3参照）。

【0008】4050

窒化物ベースのトランジスタの製作における1つの段階は、そうしたトランジスタ用のオーム性接触の形成である。オーム性接触の形成には一般に、高アニール温度（例えば900）が必要とされてきた。そうした高アニール温度は、材料および／またはデバイスに損傷を与えることがある。

#### 【0009】

例えば、オーム性接触を形成する際に高アニール温度を利用する従来型のデバイスでは、AlGaN層および／またはGaN層のゲート領域（2つの接点間の活性デバイス領域と定義される）のシート抵抗は一般に、成長させたままのAlGaN層および／またはGaN層のシート抵抗に比べて増大する。シート抵抗のこうした増大は、デバイスに悪影響を及ぼすと考えられている。10

#### 【課題を解決するための手段】

#### 【0010】

本発明の諸実施形態は、窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成し、窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによる、トランジスタの製作を提供する。バリア層上に、パターニングされたオーム性接触金属領域を形成し、それをアニールして、第1および第2のオーム性接触を形成する。アニールは、ゲート領域上に保護層を載せたままで実施される。ゲート接点も、バリア層のゲート領域（例えば、第1と第2のオーム性接触間の活性デバイス領域）上に形成される。20

#### 【0011】

本発明の別の諸実施形態では、パターニングされたオーム性接触金属をアニールした後に、保護層が除去される。保護層は窒化アルミニウム層でよい。保護層は、低損傷エッチング技術を利用して除去することができる。例えば、低損傷エッチング技術には、KOHなどの強塩基を用いた湿式除去が含まれ得る。保護層を除去した後に、バリア層の露出部分上に、パッシベーション層を形成することができる。これらの実施形態では、バリア層のゲート領域の一部分を露出させるために、低損傷エッチング技術を利用してパッシベーション層に陥凹部をエッチングし、パッシベーション層の陥凹部中にゲート接点を形成することによって、ゲート接点を形成することができる。20

#### 【0012】

本発明の別の諸実施形態では、バリア層および保護層の露出部分上に、パッシベーション層が形成される。これらの諸実施形態では、パッシベーション層および保護層を貫通して延びてバリア層に接触するゲート接点を形成することによって、ゲート接点を設けることができる。30

#### 【0013】

本発明の別の諸実施形態では、保護層を形成することは、バリア層上にパターニングされた保護層を形成することを含む。パターニングされた保護層は、ゲート領域に対応するバリア層の第1の部分を覆い、それに隣接すると共に第1および第2のオーム性接触に対応する、バリア層の第2の部分を露出させる。パターニングされたオーム性接触金属領域は、バリア層の第2の部分上に、パターニングされたオーム性接触金属領域を形成することによって設けられる。パターニングされたオーム性接触金属領域は、パターニングされた保護層に隣接すると共にそれから離隔される。40

#### 【0014】

本発明の別の諸実施形態では、パターニングされた保護層を形成することは、バリア層上に保護層材料をプランケット堆積させること、プランケット堆積された保護層材料上に、第1および第2のオーム性接触の位置に対応するウインドウを有する、一般にはフォトレジストであるマスクを形成すること、プランケット堆積された保護層を、低損傷エッチング技術を利用して、ウインドウを通してエッチングすること、およびマスクを除去することを含む。第1および第2のオーム性接触の位置に対応するウインドウは、第1および第2のオーム性接触の面積よりも大きくてよい。低損傷エッチング技術は、CF<sub>4</sub> / O<sub>2</sub>、NF<sub>3</sub> / O<sub>2</sub>および／または他のフッ素化種を使用する、RIE、ECR、ダウンスト50

リームプラズマ、ならびに／あるいはICPのうちの1つまたは複数でよい。

**【0015】**

ゲート接点を形成することは、パターニングされた保護層に陥凹部をエッチングして、バリア層の第1の部分の一部分を露出させること、およびゲート接点をその陥凹部中に堆積させることを含むことができる。陥凹部を形成することは、パターニングされた保護層上に、陥凹部の位置に対応するウインドウを有するマスクを形成すること、パターニングされた保護層を、低損傷エッチング技術を利用して、ウインドウを通してエッチングすること、およびマスクを除去することを含むことができる。パターニングされた保護層をエッチングするのに利用される低損傷エッチング技術は、 $\text{CF}_4/\text{O}_2$ 、 $\text{NF}_3/\text{O}_2$ および／または他のフッ素化種を使用する、RIE、ECR、ダウンストリームプラズマ、ならびに／あるいはICPを含むことができる。10

**【0016】**

本発明の特別な諸実施形態では、保護層はSiN、AlN、および／またはSiO<sub>2</sub>を含む。SiN、AlN、および／またはSiO<sub>2</sub>は、非化学量論的でよく、圧縮歪みまたは引っ張り歪みを有することができる。保護層は、物理気相成長(PVD)および／または化学気相成長(CVD)を使用して堆積させることができる。

**【0017】**

本発明の別の諸実施形態では、パターニングされた保護層と第1および第2のオーム性接触との間の隙間を実質的に埋めるように、パターニングされた保護層上にパッシベーション層が形成される。パターニングされた保護層およびパッシベーション層の材料は、同じでも異なっていてもよい。例えば、パターニングされた保護層は、窒化アルミニウムでよく、パッシベーション層は窒化ケイ素でよい。あるいは、パターニングされた保護層およびパッシベーション層が窒化ケイ素でもよい。20

**【0018】**

本発明の別の諸実施形態では、バリア層の第1の部分を露出させるために、パターニングされた保護層が除去される。パターニングされた保護層を除去し、それに続いて、バリア層の露出部分上にパッシベーション層を形成することができる。こうした諸実施形態では、パターニングされた保護層は、窒化アルミニウムでよく、パッシベーション層は窒化ケイ素でよい。

**【0019】**

本発明の別の諸実施形態では、ゲート接点の形成の前に、パッシベーション層の形成が実施される。ゲート接点は、パッシベーション層に陥凹部を形成して、バリア層の第1の部分の一部分を露出させ、陥凹部中にゲート接点を形成することによって、設けられる。陥凹部を形成することは、パッシベーション層上にマスクを形成することを含むことができる。マスクは、陥凹部の位置に対応するウインドウを有する。パッシベーション層は、低損傷エッチング技術を利用して、ウインドウを通してエッチングされ、次いでマスクが除去される。30

**【0020】**

本発明の特定の諸実施形態では、窒化物ベースのチャネル層および窒化物ベースの半導体バリア層は、II族窒化物層である。例えば、チャネル層のバンドギャップがバリア層のバンドギャップよりも小さい場合、チャネル層は、 $\text{Al}_{x}\text{Ga}_{1-x}\text{N}$ (ただし $0 < x < 1$ )の組成を有することができる。チャネル層は窒化アルミニウムガリウム( $\text{AlGaN}$ )、窒化ガリウム( $\text{GaN}$ )、窒化インジウムガリウム( $\text{InGaN}$ )および／または窒化アルミニウムインジウムガリウム( $\text{AlInGaN}$ )でもよく、バリア層は窒化アルミニウム( $\text{AlN}$ )、窒化アルミニウムインジウム( $\text{AlInN}$ )、 $\text{AlGaN}$ 、 $\text{GaN}$ 、 $\text{InGaN}$ 、および／または $\text{AlInGaN}$ でよい。バリア層および／またはチャネル層は、複数の層でもよい。窒化物ベースのチャネル層を形成するために、バッファ層を基板上に形成し、チャネル層をそのバッファ層上に形成してもよい。チャネル層およびバリア層は、高電子移動度トランジスタ(HEMT)となるように構成することができる。窒化物ベースのチャネル層は、SiC基板上に形成することができる。4050

## 【0021】

本発明の別の諸実施形態では、ゲート接点の形成の前に、パッシベーション層の形成が実施される。ゲート接点の形成は、パッシベーション層およびパターニングされた保護層に陥凹部を形成して、バリア層の第1の部分の一部分を露出させること、および陥凹部中にゲート接点を形成することを含む。

## 【0022】

本発明の特定の諸実施形態では、保護層はオーム性接触材料の厚さと少なくともほぼ同じ厚さに形成される。保護層は、少なくとも単層約2枚分の厚さを有してもよい。具体的には、保護層は約1nmから約500nmの厚さを有することができる。

## 【0023】

10

本発明の別の諸実施形態では、高電子移動度トランジスタは、基板上に窒化物ベースのチャネル層を、および窒化物ベースのチャネル層上に窒化物ベースの半導体バリア層を有する。チャネル層とバリア層の間の境界面での電子のチャネルは、窒化物ベースのHEMTチャネルの成長させたままのシート抵抗と実質的に同じシート抵抗を有する。バリア層上にオーム性接触およびゲート接点が形成される。

## 【0024】

20

高電子移動度トランジスタはさらに、オーム性接触に隣接すると共にそれから離隔され、またゲート接点が中を貫通して延びる、バリア層上に配設された保護層を含むことができる。保護層上にパッシベーション層を形成することもでき、これはオーム性接触と保護層の間の隙間を実質的に埋める。パッシベーション層は、保護層上にあってもよく、ゲート接点は保護層およびパッシベーション層を貫通して延びることができる。ゲート接点を、保護層上に直接形成してもよい。バリア層上のパッシベーション層は、オーム性接触とゲート接点の間の隙間を実質的に埋めることができる。

## 【0025】

本発明の特定の諸実施形態では、窒化物ベースのチャネル層および窒化物ベースの半導体バリア層はそれぞれII族窒化物層を含む。チャネル層は、バリア層よりも低いバンドギャップを有することができる。チャネル層は約2.0eVを超える厚さを有する非ドープ層を含むことができる。チャネル層は、超格子および/またはII族窒化物層の組合せを含んでもよい。チャネル層は、窒化アルミニウムガリウム(AlGaN)、窒化ガリウム(GaN)、窒化インジウムガリウム(InGaN)、および/または窒化アルミニウムインジウムガリウム(AlInGaN)を含むことができる。バリア層は、窒化アルミニウム(AlN)、窒化アルミニウムインジウム(AlInN)、AlGaN、GaN、InGaN、および/またはAlInGaNを含むことができる。例えば、バリア層は $Al_xG_{1-x}N$ (ただし $0 < x < 1$ )を含むことができる。バリア層は、複数の層を含んでもよい。バッファ層を基板上に形成することもでき、その場合には、バッファ層上に窒化物ベースのチャネル層が配設される。

30

## 【0026】

本発明の別の諸実施形態では、保護層は、オーム性接触の厚さと少なくともほぼ同じ厚さを有する。オーム性接触は、約1~1mm未満の接点抵抗を有してもよい。

## 【0027】

40

本発明の別の諸実施形態では、高電子移動度トランジスタは、基板上に窒化物ベースのチャネル層を、窒化物ベースのチャネル層上に窒化物ベースの半導体バリア層を、バリア層上に保護層を、バリア層上に、保護層に隣接すると共にオーム性接触と保護層の間に隙間を設けるようにそれから離隔されたオーム性接触を、およびバリア層上に保護層を貫通して延びるゲート接点を含む。保護層上にパッシベーション層を形成することもでき、これはオーム性接触と保護層の間の隙間を実質的に埋める。

## 【0028】

本発明の別の諸実施形態では、トランジスタの製作は、窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することを含む。バリア層上に、パターニングされた

50

オーム性接触金属領域が形成される。パターニングされたオーム性接触金属は、第1および第2のオーム性接触、例えばソース接点およびドレイン接点を形成するために、アニールされる。バリア層のゲート領域の一部分を露出させるために、低損傷エッチング技術を利用して、バリア層のゲート領域内の保護層に陥凹部がエッチングされる。ゲート接点は、パッシベーション層の陥凹部中に形成される。

#### 【0029】

本発明の特定の諸実施形態では、保護層はパッシベーション層を含む。保護層は、例えば、窒化アルミニウム層、窒化ケイ素層、ならびに／あるいは1層または複数層の二酸化ケイ素層でよい。低損傷エッチング技術は、強塩基を使用する湿式エッチングでよい。本発明のいくつかの実施形態では、第1および第2のオーム性接触を形成するために、10 パターニングされたオーム性接触金属のアニールは、保護層を形成する前に実施される。本発明の他の諸実施形態では、第1および第2のオーム性接触を形成するために、パターニングされたオーム性接触金属のアニールは、保護層を形成した後に実施される。

#### 【発明を実施するための最良の形態】

#### 【0030】

次に本発明を、本発明の諸実施形態が示された添付の図面を参照して、以下により完全に説明する。ただし本発明は、多くの異なる形態で実施することができ、本明細書に記載の実施形態だけに限定されるものと解釈すべきではない。そうではなく、これらの実施形態は、本開示が網羅的で完全なものとなるように、また本発明の範囲を当分野の技術者に十分に伝えるために、提供するものである。同じ数字は、全体を通じて同じ要素を表す。さらに、図面に示す様々な層および領域は、概略的に示されている。したがって、本発明は、添付の図面に示された相対寸法、間隔および配列に限定されるものではない。やはり当分野の技術者には理解されるように、本明細書において、基板または他の層「上」に形成された層という言及は、基板または他の層上に直接形成された層を指すことも、基板または他の層上に形成された1層または複数層の介在する層上に形成された層を指することもある。別の構成に「隣接」して配設される構造または構成という言及は、隣接する構成と重畠する、またはその下にある部分を有することもあること、当分野の技術者には理解されるであろう。

#### 【0031】

本発明の諸実施形態では、トランジスタなどの半導体デバイス中で、ゲート漏れ電流を低減させ、かつ／または高品質のショットキー接点を形成するために、保護層および／または低損傷陥凹部の製作技術を利用する。保護層を使用することにより、デバイスのオーム性接触のアニール中に、トランジスタのゲート領域内で半導体が受ける損傷を低減することができる。したがって、オーム性接触の形成に起因するゲート領域の品質低下が低減された、高品質のゲート接点およびオーム性接触を形成することができる。

#### 【0032】

本発明の諸実施形態は、IIII族窒化物ベースのデバイスなど、窒化物ベースのHEMTで使用するのに特に十分に適切となり得る。本明細書では、「IIII族窒化物」という用語は、窒素と、周期表のIIII族の元素、一般にアルミニウム(A1)、ガリウム(Ga)、および／またはインジウム(In)との間で形成された半導体化合物を指す。この用語は、Al<sub>x</sub>G<sub>y</sub>NやAl<sub>1-x</sub>G<sub>y</sub>Nなど三元化合物および四元化合物も指す。当分野の技術者には十分に理解されるように、IIII族元素は窒素と結合して、二元化合物(例えばGaN)、三元化合物(例えばAl<sub>x</sub>G<sub>y</sub>N、Al<sub>1-x</sub>In<sub>y</sub>N)、および四元化合物(例えばAl<sub>1-x</sub>In<sub>y</sub>G<sub>z</sub>N)を形成することができる。これらの化合物はすべて、1モルの窒素が合計1モルのIIII族元素と組み合わされた実験式を有する。したがって、それらを記述するために、Al<sub>x</sub>G<sub>y</sub>N(ただし0≤x≤1)などの式がしばしば使用される。

#### 【0033】

本発明の諸実施形態を利用することのできるGaNベースのHEMTのための適切な構造は、文献に記載されている(例えば、本願の譲受人に譲渡された特許文献3および2001年7月12日出願、2002年6月6日公開の、「ALUMINUM GALLIUM NITRIDE/GALLI

10

20

30

40

50

UM NITRIDE HIGH ELECTRON MOBILITY TRANSISTORS HAVING A GATE CONTACT ON A GALLIUM NITRIDE BASED CAP SEGMENT AND METHODS OF FABRICATING SAME」という名称の特許文献4、2001年5月11日出願の、「GROUP III NITRIDE BASED HIGH ELECTRON MOBILITY TRANSISTOR (HEMT) WITH BARRIER/SPACER LAYER」という名称の特許文献5、2002年11月14日公開の、Smorchkova等の、「GROUP-III NITRIDE BASED HIGH ELECTRON MOBILITY TRANSISTOR (HEMT) WITH BARRIER/SPACER LAYER」という名称の特許文献6、ならびに2003年7月11日出願の、「NITRIDE-BASED TRANSISTORS AND METHODS OF FABRICATION THEREOF USING NON-ETCHED CONTACT RECESSES」という名称の特許文献7参照)。

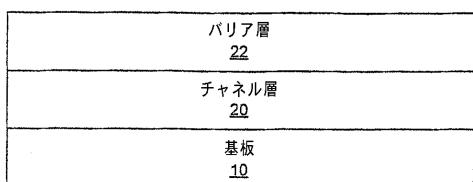

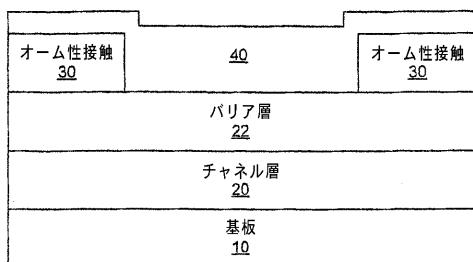

#### 【0034】

本発明の諸実施形態の製作を、図1A～1Eに概略的に示す。図1Aから分かるように、その上に窒化物ベースのデバイスを形成することのできる基板10が提供される。本発明の特定の諸実施形態では、基板10は、半絶縁性炭化ケイ素(SiC)の基板でよく、炭化ケイ素は、例えば4Hポリタイプの炭化ケイ素でよい。炭化ケイ素ポリタイプの他の候補には、3C、6Hおよび15Rポリタイプが含まれる。「半絶縁性」という用語は、絶対的な意味ではなく、説明的なものとして使用される。本発明の特定の諸実施形態では、炭化ケイ素のバルク結晶は、室温で約 $1 \times 10^5$  - cm以上の抵抗率を有する。

10

#### 【0035】

基板10上に、バッファ層、核形成層、および/または遷移層(図示せず)を任意選択で形成することができる。例えば、炭化ケイ素基板とデバイスの残りの部分の間で適当な結晶構造の遷移をもたらすために、AINバッファ層を形成することができる。さらに、文献に記載されているように、1層または複数層の歪み平衡遷移層(strain balanced straining transition layer)を形成することもできる(例えば、本願の譲受人に譲渡された、2002年7月19日出願、2003年6月5日公開の、「STRAIN BALANCED NITRIDE HETEROJUNCTION TRANSISTORS AND METHODS OF FABRICATING STRAIN BALANCED NITRIDE HETEROJUNCTION TRANSISTORS」という名称の特許文献8、および2001年12月3日出願の、「STRAIN BALANCED NITRIDE HETEROJUNCTION TRANSISTORS」という名称の特許文献9参照)。

20

#### 【0036】

炭化ケイ素の方が、IIII族窒化物デバイス用の非常に一般的な基板材料であるサファイア(A<sub>2</sub>O<sub>3</sub>)よりも、IIII族窒化物にずっと近い結晶格子整合を有する。格子整合がより近いことから、サファイア上で一般に得られるものよりも高品質のIIII族窒化物被膜を得ることができる。炭化ケイ素は、非常に高い熱伝導性も有し、その結果、炭化ケイ素上のIIII族窒化物デバイスの全出力電力は一般に、サファイア上に形成された同じデバイスの場合ほどは、基板の放熱による制限を受けない。また、半絶縁性炭化ケイ素基板が利用できるので、デバイスの分離および寄生容量の低減をもたらすことができる。適当なSiC基板は例えば、本発明の譲受人であるノースカロライナ州ダラムのCree社により製造されており、製造方法は文献に記載されている(例えば、特許文献10、特許文献11、特許文献12、特許文献13参照)。同様に、IIII族窒化物のエピタキシャル成長技術も、これまでに文献に記載されている(例えば、特許文献14、特許文献15、特許文献16、特許文献17参照)。

30

#### 【0037】

基板材料として炭化ケイ素を使用することができるが、本発明の諸実施形態では、サファイア、窒化アルミニウム、窒化アルミニウムガリウム、窒化ガリウム、シリコン、GaAs、LGO、ZnO、LAO、InPなど、どんな適切な基板も利用することができる。いくつかの実施形態では、適当なバッファ層を形成することもできる。

40

#### 【0038】

図1Aに戻ると、基板10上にチャネル層20が形成される。チャネル層20は、上述のようにバッファ層、遷移層、および/または核形成層を使用して、基板10上に堆積させることができる。チャネル層20は、圧縮歪みを受けていてよい。さらに、チャネル層および/またはバッファ核形成層(buffer nucleation layer)

50

および／または遷移層は、MOCVDによって、またはMBEやHYPEなど、当分野の技術者には公知の他の技術によって、堆積させることができる。

#### 【0039】

本発明のいくつかの実施形態では、チャネル層とバリア層の間の境界面で、チャネル層20の伝導帯端のエネルギーの方がバリア層22の伝導帯端のエネルギーよりも小さいという条件のもとで、チャネル層20は、 $\text{Al}_x\text{Ga}_{1-x}\text{N}$ （ただし $0 < x < 1$ ）などのIII族窒化物である。本発明のいくつかの実施形態では $x = 0$ であり、チャネル層20がGaNであることを意味する。チャネル層20は、InGaN、AlInGaNなど、他のIII族窒化物でもよい。チャネル層20は、ドープされていない（「意図的でなくドープされていて」）よく、約20nmを超える厚さにまで成長させることができる。チャネル層20は、超格子またはGaN、AlGaNなどの組合せなどの多層構造でもよい。

10

#### 【0040】

チャネル層20上にバリア層22が設けられる。チャネル層20は、バリア層22のバンドギャップよりも小さなバンドギャップを有することができ、またチャネル層20は、バリア層22よりも大きな電子親和力を有することもできる。バリア層22は、チャネル層20上に堆積させることができる。本発明のいくつかの実施形態では、バリア層22は、約0.1nmから約10nmの間の厚さの、AlN、AlInN、AlGaNまたはAlInGaNである。本発明のいくつかの実施形態による層の例は、文献に記載されている（その開示を、本明細書に完全に記載されているのと同様に、Smorchkova等の、「GROUP-III NITRIDE BASED HIGH ELECTRON MOBILITY TRANSISTOR (HEMT) WITH BARRIER/SPACER LAYER」という名称の、特許文献6参照。）。本発明の特定の諸実施形態では、バリア層22は、オーム接触金属の下に埋め込まれたときに、分極効果によって、チャネル層20とバリア層22の間の境界面で、十分なキャリア濃度を誘起させるのに十分なほど厚く、十分なほど高いAlの組成およびドーピングを有する。またバリア層22は、バリア層22と第2のキャップ層24（図1B）の間の境界面に堆積されたイオン化不純物による、チャネル内での電子の散乱を低減し、または最小限に抑えるのに十分なほど厚くあるべきである。

20

#### 【0041】

バリア層22は、III族窒化物でよく、チャネル層20のバンドギャップよりも大きなバンドギャップ、およびチャネル層20よりも小さな電子親和力を有する。したがって、本発明のいくつかの実施形態では、バリア層22は、AlGaN、AlInGaN、および／またはAlNまたはそれらの層の組合せである。バリア層22は、例えば、約0.1nmから約10nmの厚さでよいが、亀裂または重大な欠陥の形成をその中で引き起こすほど厚くはない。本発明のいくつかの実施形態では、バリア層22はドープされず、あるいはn型ドーパントで約 $10^{19} \text{ cm}^{-3}$ 未満の濃度までドープされる。本発明のいくつかの実施形態では、バリア層22は、 $\text{Al}_x\text{Ga}_{1-x}\text{N}$ （ただし $0 < x < 1$ ）である。特定の諸実施形態では、アルミニウム濃度は約25%である。しかし、本発明の他の諸実施形態では、バリア層22は、アルミニウム濃度が約5%から約100%の間のAlGaNを含む。本発明の特定の諸実施形態では、アルミニウム濃度は約10%を超える。

30

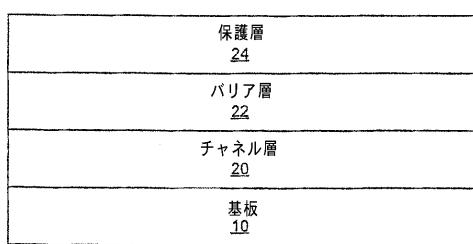

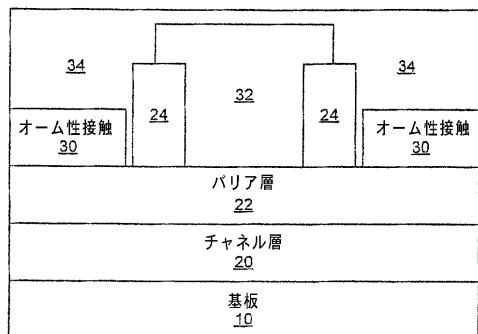

#### 【0042】

図1Bは、バリア層22上での保護層24の形成を示す。保護層24は、窒化ケイ素（ $\text{Si}_x\text{N}_y$ ）、窒化アルミニウム（AlN）、ならびに／あるいは、二酸化ケイ素（ $\text{SiO}_2$ ）および／または酸窒化物など、他の適切な保護材料でよい。下にあるバリア層22に損傷を与えるに材料を除去することができる限り、保護層24に他の材料を利用してよい。例えば、保護層24は、酸化マグネシウム、酸化スカンジウム、酸化アルミニウム、および／または酸窒化アルミニウムを含むこともできる。さらに、保護層24は、組成が一様および／または非一様な、単一の層あるいは複数の層とすることができる。

40

#### 【0043】

本発明の特定の諸実施形態では、保護層24はSiNである。SiNはPVDおよび／

50

またはCVDで形成することができ、圧縮歪みまたは引っ張り歪みにおいて非化学量論的でよい。例えば、保護層は、約-100 MPaから約100 MPaの間の応力を有することができる。本発明のいくつかの実施形態では、SiN保護層は、633 nmの波長で約1.6から約2.2の屈折率を有する。特定の諸実施形態では、SiN保護層の屈折率は、 $1.98 \pm 0.05$ である。

#### 【0044】

いくつかの実施形態では、保護層24はAlNでよい。AlNは、PVDおよび/またはCVDで形成することができ、圧縮歪みまたは引っ張り歪みにおいて非化学量論的でよい。例えば、保護層は、約-100 MPaから約100 MPaの間の応力を有することができる。本発明のいくつかの実施形態では、AlN保護層は、633 nmの波長で約1.8から約2.1の屈折率を有する。特定の諸実施形態では、AlN保護層の屈折率は、 $1.85 \pm 0.05$ である。

10

#### 【0045】

保護層24はSiO<sub>2</sub>でもよい。SiO<sub>2</sub>はPVDおよび/またはCVDで形成することができ、圧縮歪みまたは引っ張り歪みにおいて非化学量論的でよい。例えば、保護層は、約-100 MPaから約100 MPaの間の応力を有することができる。本発明のいくつかの実施形態では、SiO<sub>2</sub>保護層は、633 nmの波長で約1.36から約1.56の屈折率を有する。特定の諸実施形態では、SiO<sub>2</sub>保護層の屈折率は、 $1.46 \pm 0.03$ である。

20

#### 【0046】

保護層24は、バリア層22上にブランケット形成され、堆積によって形成することができる。例えば、窒化ケイ素層は、高品質なスパッタリングおよび/またはPECVDで形成することができる。一般に、保護層24は、約30 nmの厚さを有することができるが、他の厚さの層を利用することもできる。例えば、保護層は、後続のオーム性接触のアーナー中に、下にある層を保護するために、十分に厚くなければならない。単層2枚または3枚分ほどの薄い層で、そうした目的に十分となり得る。しかし、一般には、保護層24は約10 nmから約500 nmの厚さを有することができる。また、III族窒化物層のMOCVD成長を用いて、高品質なSiN保護層をin-situで成長させることもできる。

30

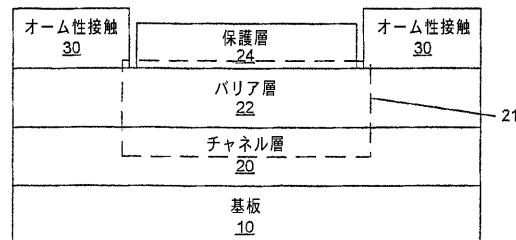

#### 【0047】

図1Cに示すように、オーム性接触30を形成するために、保護層24にウインドウを開口する。これらのウインドウを、パターニングされたマスクおよびバリア層22に対する低損傷エッチングを利用して形成して、下にあるバリア層22を露出させることができる。低損傷エッチング技術の例には、プラズマに直流成分のない、誘導結合プラズマエッチングまたは電子サイクロトロン共鳴( ECR )エッチングまたはダウンストリームプラズマエッチングなど、反応性イオンエッチング以外のエッチング技術が含まれる。SiO<sub>2</sub>の場合には、低損傷エッチングは、緩衝フッ化水素酸を用いた湿式エッチングとすることができます。ITO、SCO、MgOなどのエッチングストップ層まで、SiNおよび/またはSiO<sub>2</sub>を選択的にエッチングし、それに続いて、エッチングストップ層の低損傷除去を実施することもできる。SiNの場合には、エッティングストップ層としてSiO<sub>2</sub>を使用することができる。こうした諸実施形態では、保護層24は、SiN層、AlN層および/またはSiO<sub>2</sub>層ならびにエッティングストップ層を含むことができる。したがって、本発明のいくつかの実施形態では、保護層24は複数の層を含むことができる。

40

#### 【0048】

図1Cにさらに示すように、後続のフォトリソグラフィ段階および蒸着でオーム金属をパターニングして、オーム性接触30を形成する。オーム性接触30は、保護層24内のウインドウよりも小さくなり、その結果、オーム性接触30の縁部が保護層24から離隔されるようにパターニングされる。例えば、オーム性接触30の縁部は、保護層24から約0.1 μmから約0.2 μmの距離だけ離隔することができる。オーム性接触30は、オーム性接触金属の形成およびパターニング時にずれ公差を許容できるほど十分に大きな

50

距離だけ、保護層 24 から離隔されるべきである。オーム性接触金属が保護層 24 に接触すると、後続の加熱段階中に、金属が保護層 24 内に拡散することがあり、その結果ゲート接点と 1つまたは複数のオーム性接触 30との間で短絡を生じる恐れがある。ただし、オーム性接触 30 と保護層 24 の間の隙間は、保護層 24 の保護目的を無効にし、それによってデバイスの性能を実質的に低下させるほど大きくあるべきではないが、オーム性材料の、保護層に対する無作為な接触を危うくするほど小さくあるべきでもない。したがって、例えば、本発明のいくつかの実施形態では、隙間は約 0.1 μm から約 0.5 μm でよい。

#### 【 0049 】

オーム性接触材料をアニールして、オーム性接触 30 を形成する。アニールは、高温アニールでよい。例えば、アニールは、約 900 °C を超える温度でのアニールでよい。オーム性接触のアニールを使用することによって、オーム性接触の抵抗を、高抵抗から約 1 - mm 未満まで低減させることができる。したがって、本明細書では、「オーム性接触」という用語は、約 1 - mm 未満の接点抵抗を有する、非整流性接点を指す。高温工程段階中に保護層があるため、そうした段階によって引き起こされる恐れのある、バリア層 22 への損傷を抑制することができる。したがって、例えば、オーム性接触を高温アニールした後のゲート領域 21 のシート抵抗は、成長させたまま（すなわち、接点をアニールする前）のゲート領域 21 のシート抵抗と実質的に同じになることができる。

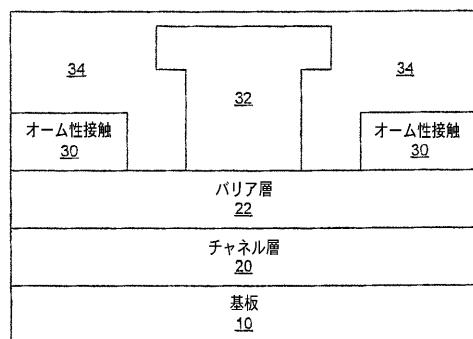

#### 【 0050 】

図 1D は、ゲートウインドウの形成を示す。図 1D から分かるように、オーム性接触および保護層 24 上にマスク 26 を形成し、パターニングして、保護層 24 の一部分を露出するウインドウを形成する。次いで、バリア層 22 の一部分を露出するために、保護層 24 を貫通して陥凹部を形成する。陥凹部は、上述のように、マスク 26 および低損傷エッチング法を使用して形成する。オーム性接触 30 によってソース接点およびドレイン接点が形成される特定の諸実施形態では、陥凹部が、後にはゲート接点 32 が、ドレイン接点よりもソース接点の方に近くなるように、陥凹部を、ソース接点とドレイン接点の間で位置決めすることができる。

#### 【 0051 】

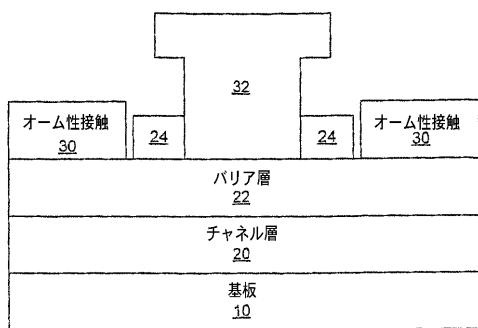

図 1E から分かるように、ゲート接点 32 は、陥凹部中に形成され、バリア層 22 の露出部分に接触する。ゲート接点は、図 1E に示すような「T」ゲートでよく、従来の製作技術を使用して製作することができる。適切なゲート材料は、バリア層の組成によって変わることがあるが、いくつかの実施形態では、Ni、Pt、NiSi<sub>x</sub>、Cu、Pd、Cr、W および / または WSiN など、窒化物ベースの半導体材料に対してショットキー接点を形成することのできる従来型の材料を使用することができる。望ましくないことかもしれないが、保護層 24 とゲート接点 32 の間の小さな隙間が、例えば、低損傷エッチングの異方性の結果として生じることがあり、それによって保護層 24 とゲート接点 32 の間にバリア層 22 の露出した表面がもたらされる。

#### 【 0052 】

図 1F は、パッシベーション層 34 の形成を示す。パッシベーション層は、図 1E の構造上にプランケット堆積させることができる。特定の諸実施形態では、パッシベーション層 34 は、保護層 24 とオーム接触 30 の間の隙間を、また保護層 24 とゲート接点 32 の間の隙間があればそれも、実質的に埋めるように堆積させる。本発明のいくつかの実施形態では、パッシベーション層 34 は、窒化ケイ素、窒化アルミニウム、二酸化ケイ素、および / または酸窒化物でよい。さらに、パッシベーション層 34 は、組成が一様および / または非一様な、単一の層あるいは複数の層とすることができる。

#### 【 0053 】

以上、本発明の諸実施形態を、開口したゲート接点ウインドウを形成するための、また保護層 24 に対する隙間をもつゲート接点を形成するための、2つのマスクによる方法に即して説明してきたが、図 2A および図 2B は、オーム性接触ウインドウおよびオーム性接触を单一のマスクで形成するための操作を示す。図 2A から分かるように、保護層 24

10

20

30

40

50

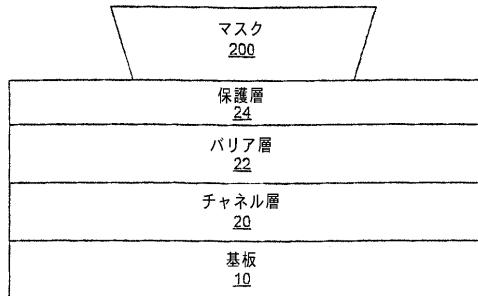

上に、負の斜角をもつ、フォトレジストなどのマスク 200 を形成することができる。マスク 200 の負の斜角は、その後形成されるオーム性接触 30 とパターニングされた保護層 24 との間の隙間の距離に対応する。保護層 24 を、上述の低損傷エッチング法を使用して等方的にエッチングして、接点ウインドウを形成する。したがって、接点ウインドウは、マスク 200 の底辺寸法によって画定される。エッチングが等方性であり、低損傷エッチングにより実質的にオーバーエッチングされて、横方向のアンダカットを所望の間隔にすることができる場合には、負の斜角をもたないマスク層を使用することもできる。

#### 【 0 0 5 4 】

図 2 B から分かるように、オーム接触金属 300 を、得られた構造上に蒸着させる。マスク 200 のオーバーハング部が、露出したバリア層 22 上に金属が堆積される場所を画定する。したがって、接触金属 300 は、パターニングされた保護層 24 から離隔される。マスク 200 およびマスク 200 上の金属 300 を除去すると、図 1 C の構造がもたらされる。

#### 【 0 0 5 5 】

図 2 A に示す斜角付きのマスクを提供する技術は、当分野の技術者には公知である。さらに、マスク 200 は斜角を有するように示してあるが、本発明の他の諸実施形態では、マスクは、段を有することもでき、保護層 24 のエッチングおよび接点材料の堆積用の、2 つの異なる見かけのウインドウサイズを有するマスクを形成するような他の構成を有することもできる。したがって、例えば、1 回の露光で、保護層 24 に隣接するフォトレジストの層によって形成されるウインドウの方が、保護層 24 から離隔されたフォトレジストの層によって形成されるウインドウよりも大きくなるような、オーバーハングまたは段を有するマスクを形成することのできる、異なる露光感度を有する多層フォトレジストを利用することができます。

#### 【 0 0 5 6 】

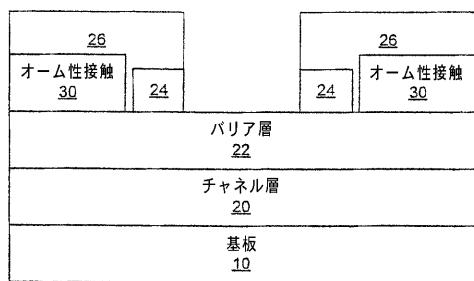

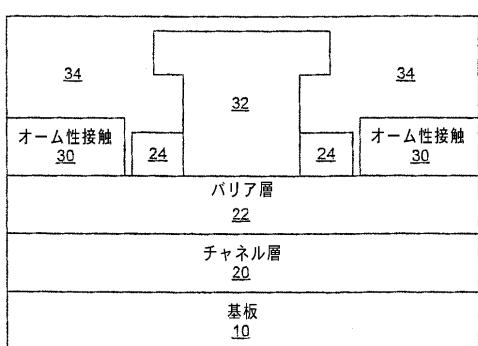

図 3 は、本発明の別の諸実施形態による、トランジスタの製作を示す。図 3 から分かるように、オーム金属堆積前の保護層 24 の形成は省略することができ、バリア層 22 上にオーム金属を堆積させ、パターニングして、バリア層 22 上にオーム性接触材料領域 30 を形成することができる。次いで、バリア層 22 のゲート領域およびオーム性接触材料上に、保護層 40 を形成する。本発明の特定の諸実施形態では、保護層 40 は、窒化アルミニウムをスパッタリングによってプランケット堆積させたものでよい。保護層 40 は、保護層 24 に関して上記で述べたものなどの材料でもよい。

#### 【 0 0 5 7 】

オーム性接触材料領域 30 のアニールは、保護層 40 を適切な位置に配置したままで実施する。次いで保護層 40 を、例えば、上述のような低損傷エッチング技術を使用して除去することができる。次いで、パッシベーション層 34 の形成前または形成後に、ゲート接点 32 を形成することができる。例えば、窒化ケイ素層を、スパッタリングによって堆積させることができる。次いで、例えば上述の低損傷エッチング法を使用して、パッシベーション層にゲート陥凹部をエッチングし、陥凹部中にゲートを形成することができる。そのような方法によって、「T」ゲートの縁部に達する十分な厚さを維持する窒化ケイ素パッシベーション層を形成することができる。したがって、図 4 に示すような構造を有するトランジスタを形成することができる。

#### 【 0 0 5 8 】

あるいは、図 4 に示す構造は、図 1 A ~ 1 F に示す製作段階を利用して形成することができ、ただし保護層 24 は、ゲート接点 32 の形成前または後に除去することができる。そうした場合には、保護層 24 は、上述のような低損傷エッチング技術を使用して除去すべきである。

#### 【 0 0 5 9 】

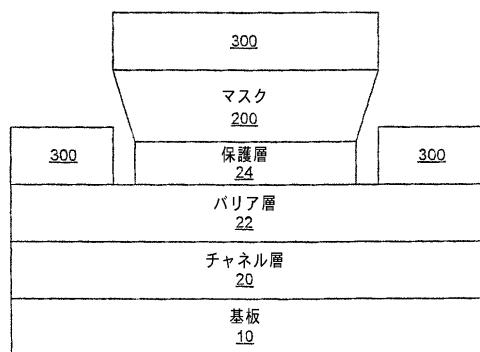

図 5 は、保護層 24 が少なくともオーム性接触 30 とほぼ同程度の厚さに形成される、本発明の別の諸実施形態を示す。図 5 から分かるように、こうした諸実施形態では、ゲート接点 34 の袖部 (wing) は、直接保護層 24 上に形成することができる。例えば、

10

20

30

40

50

保護層 24 は、約 500 から約 5000 の厚さに形成することができる。保護層 24 を通して低損傷エッチングが実施され、「T」ゲート 32 が、直接保護層 24 上に載り、またそれを貫通して形成される。例えば、デバイスの環境からの保護を向上させるために、その後にオーバーレイヤ (overlayer) パッシベーション 34 を形成することもできる。

#### 【0060】

以上、本発明の諸実施形態を、本明細書において特定の HEMT 構造に関して説明してきたが、本発明は、そうした構造に限定されるものと解釈すべきではない。例えば、追加の層を HEMT デバイス内に含めても、本発明の教示の恩恵を受けることができる。こうした追加の層は、文献に記載の GaN キャップ層を含むことができる（例えば、非特許文献 1 または 2001 年 7 月 12 日出願、2002 年 6 月 6 日公開の、「ALUMINUM GALLIUM NITRIDE/GALLIUM NITRIDE HIGH ELECTRON MOBILITY TRANSISTORS HAVING A GATE CONTACT ON A GALLIUM NITRIDE BASED CAP SEGMENT AND METHODS OF FABRICATING SAME」という名称の特許文献 4 参照）。いくつかの実施形態では、MISHEMT を製作するために、かつ / または表面を不活性化するために、SiNx や比較的高品質の AlN などの絶縁層を堆積させることができる。追加の層は、組成が傾斜した 1 層または複数層の遷移層を含むこともできる。

#### 【0061】

さらに、文献に記載されているように、バリア層 22 が複数の層を備えることもできる（その開示を、本明細書に完全に記載されているのと同様に、参照により本明細書に組み込む、Smorchkova 等の、「GROUP-III NITRIDE BASED HIGH ELECTRON MOBILITY TRANSISTOR (HEMT) WITH BARRIER/SPACER LAYER」という名称の特許文献 6 参照。）。したがって、本発明の諸実施形態では、バリア層は単一の層に限定されるものと解釈すべきではなく、例えば GaN、AlGaN および / または AlN 層の組合せを有するバリア層を含むことができる。例えば、GaN、AlN 構造を、合金散乱を低減または回避するために利用することができる。したがって、本発明の諸実施形態は、窒化物ベースのバリア層を含むことができ、こうした窒化物ベースのバリア層は、AlGaN ベースのバリア層、AlN ベースのバリア層、およびそれらの組合せを含むことができる。

#### 【0062】

以上、図面および明細書で、本発明の一般的な諸実施形態が開示されてきた。特定の用語が用いられてきたが、それらは限定するためではなく、一般的および説明的な意味において使用されたにすぎない。

#### 【図面の簡単な説明】

#### 【0063】

【図 1A】本発明の諸実施形態による、トランジスタの製作を示す概略図である。

【図 1B】本発明の前記諸実施形態による、トランジスタの製作を示す別の概略図である。

【図 1C】本発明の前記諸実施形態による、トランジスタの製作を示す別の概略図である。

【図 1D】本発明の前記諸実施形態による、トランジスタの製作を示す別の概略図である。

【図 1E】本発明の前記諸実施形態による、トランジスタの製作を示す別の概略図である。

【図 1F】本発明の前記諸実施形態による、トランジスタの製作を示す別の概略図である。

【図 2A】本発明の別の諸実施形態による、トランジスタの製作における一操作を示す概略図である。

【図 2B】本発明の前記別の諸実施形態による、トランジスタの製作における一操作を示す概略図である。

#### 【図 3】本発明の諸実施形態による、一代替製作段階の概略図である。

10

20

30

40

50

【図4】本発明の別の諸実施形態による、トランジスタの概略図である。

【図5】本発明の別の諸実施形態による、トランジスタの概略図である。

【図1A】

【図1C】

【図1B】

【図1D】

【図 1 E】

【図 2 A】

【図 1 F】

【図 2 B】

【図 3】

【図 5】

【図 4】

---

フロントページの続き

(74)代理人 100138346

弁理士 畑中 孝之

(72)発明者 スコット ティー . シェパード

アメリカ合衆国 27516 ノースカロライナ州 チャペル ヒル オータム レーン 101

(72)発明者 リチャード ピーター スミス

アメリカ合衆国 27510 ノースカロライナ州 カルボロ スウィート ベイ ブレイス 2

42

(72)発明者 ゾルタン リング

アメリカ合衆国 27713 ノースカロライナ州 ダラム オールド フォックス トレイル

327

審査官 村岡 一磨

(56)参考文献 特開2003-086608 (JP, A)

特開平09-186175 (JP, A)

特表2002-502557 (JP, A)

特開2003-257999 (JP, A)

特開2003-197646 (JP, A)

特開2002-124663 (JP, A)

特開2001-210658 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/338

H01L 21/306

H01L 29/778

H01L 29/812