| DOMANDA DI INVENZIONE NUMERO | 102021000014306 |

|------------------------------|-----------------|

| Data Deposito                | 01/06/2021      |

| Data Pubblicazione           | 01/12/2022      |

# Classifiche IPC

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 01     | L           | 21     | 56          |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

| Н       | 01     | L           | 23     | 31          |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

| Н       | 01     | L           | 23     | 36          |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

| П       | 01     | Ţ           | 23     | 495         |

#### Titolo

Procedimento per fabbricare dispositivi a semiconduttore e dispositivo a semiconduttore corrispondente

DESCRIZIONE dell'invenzione industriale dal titolo:

"Procedimento per fabbricare dispositivi a semiconduttore e dispositivo a semiconduttore corrispondente"

di: STMicroelectronics S.r.l., nazionalità italiana, via C. Olivetti, 2 - 20864 Agrate Brianza (MB)

Inventori Designati: Roberto TIZIANI, Antonio BELLIZZI

Depositata il: 1° Giugno 2021

\* \* \* \*

#### TESTO DELLA DESCRIZIONE

# Campo tecnico

La descrizione si riferisce ai dispositivi a semiconduttore.

Una o più forme di attuazione possono essere applicate, per esempio, a dispositivi a semiconduttore Quad-Flat No-lead (QFN) e ad altri dispositivi a semiconduttore utilizzanti la tecnologia Direct Copper Interconnection (DCI, Interconnessione in Rame Diretta).

#### Sfondo

I dispositivi a semiconduttore fabbricati utilizzando la tecnologia Direct Copper Interconnection (DCI) - spesso indicata anche come tecnologia Laser Direct Structuring (LDS, Strutturazione Laser Diretta) - possono comprendere un package "slug-up" o "die-pad-up", in cui pattern conduttivi strutturati mediante attivazione laser sono successivamente placcati con materiali conduttivi (per esempio, rame) per fornire formazioni elettricamente conduttive come piste e pad.

I relativi processi di placcatura sono facilitati linee di placcatura che vengono infine rimosse durante una fase di singolazione che separa i singoli dispositivi.

In tal modo si rimuovono le linee di placcatura che si

estendono nei siti in cui viene eseguito il taglio per scopi di singolazione, mentre porzioni rimanenti delle linee di placcatura vengono lasciate esposte in corrispondenza delle pareti laterali del package del dispositivo a semiconduttore.

Soprattutto nelle applicazioni ad alta tensione, queste porzioni esposte delle linee di placcatura possono causare violazioni indesiderate della distanza di creepage; "creepage" è una definizione corrente del fenomeno che porta a una dispersione indesiderata di corrente sulla superficie di un materiale (dielettrico) isolante.

# Oggetto e sintesi

Uno scopo di una o più forme di attuazione è affrontare i problemi discussi in precedenza.

Secondo una o più forme di attuazione, tale scopo può essere raggiunto mediante un procedimento avente le caratteristiche riportate nelle rivendicazioni che seguono.

Una o più forme di attuazione possono riguardare un dispositivo a semiconduttore corrispondente.

Le rivendicazioni sono parte integrante dell'insegnamento tecnico qui fornito rispetto alle forme di attuazione.

In breve, una o più forme di attuazione forniscono un procedimento applicabile, per esempio, a package QFN slugup utilizzanti la tecnologia DCI in cui vengono affrontati efficacemente problemi di creepage relativi a porzioni di linee di placcatura che rimangono esposte in corrispondenza delle pareti laterali del package.

In una o più forme di attuazione, le linee di placcatura che si estendono nei siti in cui viene eseguito il taglio di singolazione vengono rimosse mediante taglio

parziale. Le scanalature/trincee risultanti da tale taglio parziale sono riempite con materiale isolante come materiale resist che incapsula le porzioni di linee di placcatura altrimenti esposte. L'incapsulamento così realizzato supera i problemi di distanza di creepage ricorrendo ad una soluzione che è semplice da attuare e a basso costo.

Ad una semplice ispezione visiva, i dispositivi a semiconduttore fabbricati secondo forme di attuazione della presente descrizione presentano, per esempio, pad elettroplaccati con inserti angolari formati da (mezze) trincee riempite con materiale isolante visibili in corrispondenza dei fianchi del package.

# Breve descrizione delle figure allegate

Una o più forme di attuazione saranno ora descritte, a titolo puramente esemplificativo, con riferimento alle figure allegate, in cui:

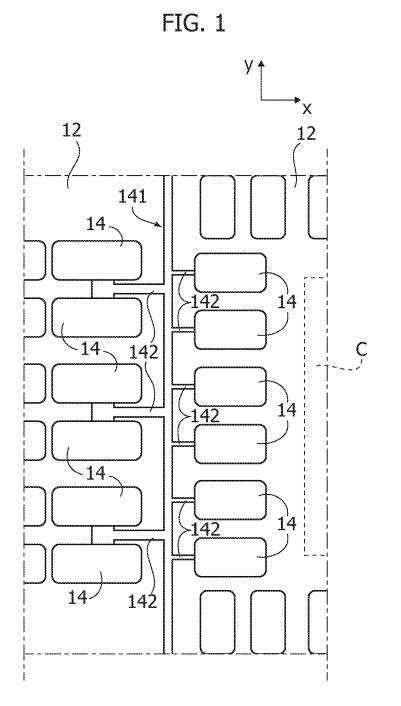

la Figura 1 è una vista in pianta dei fianchi mutuamente affacciati di due dispositivi a semiconduttore durante una fase di fabbricazione prima di una fase di singolazione per produrre singoli dispositivi a semiconduttore,

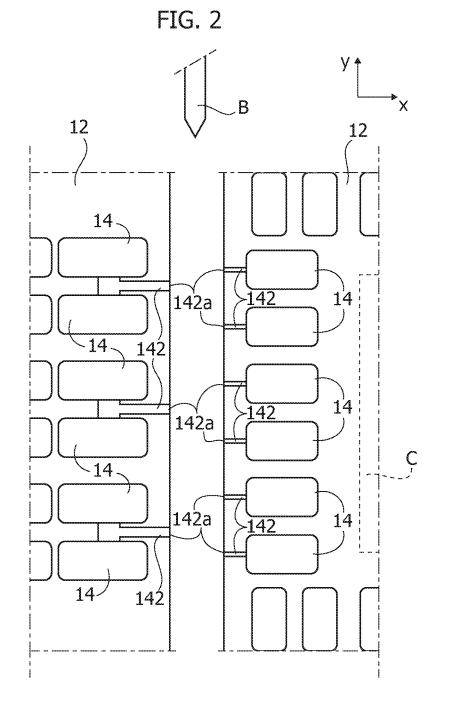

la Figura 2 è una vista in pianta dei fianchi mutuamente affacciati di due dispositivi a semiconduttore durante una fase di fabbricazione dopo una fase di singolazione per produrre singoli dispositivi a semiconduttore,

la Figura 3 è una vista in pianta illustrativa di una fase compresa in forme di attuazione della presente descrizione,

la Figura 4 è una vista in sezione lungo la linea IV-

IV di Figura 3,

la Figura 5 è una vista in pianta illustrativa di una fase compresa in forme di attuazione della presente descrizione,

la Figura 6 è una vista in sezione lungo la linea VI-VI di Figura 5,

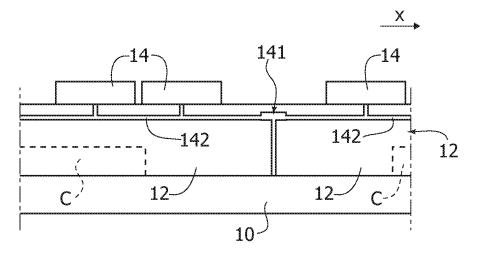

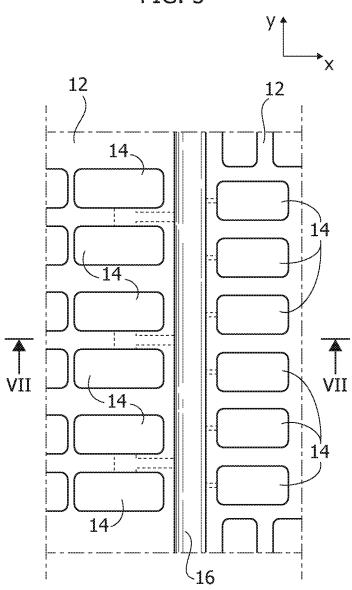

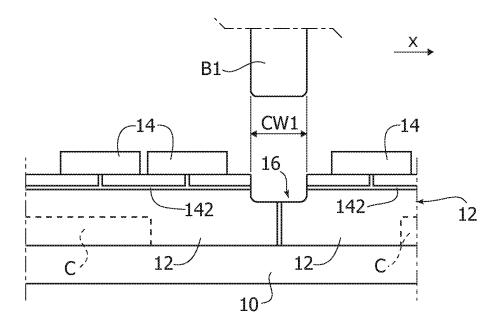

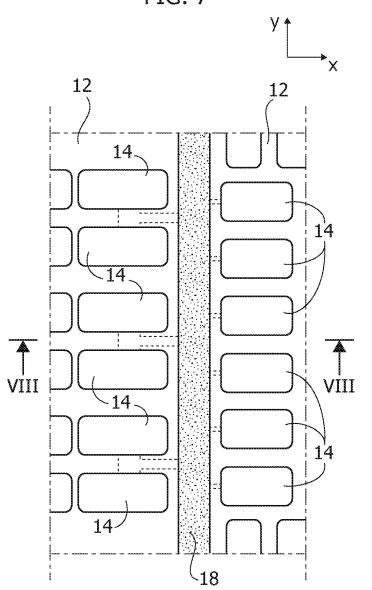

la Figura 7 è una vista in pianta illustrativa di una fase compresa in forme di attuazione della presente descrizione,

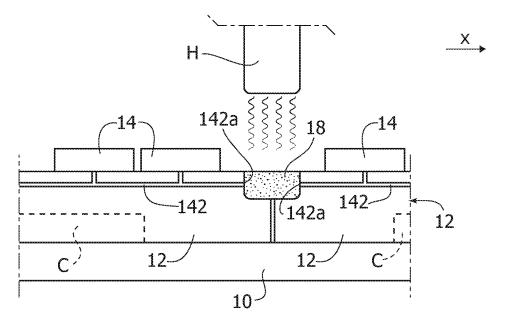

la Figura 8 è una vista in sezione lungo la linea VIII-VIII di Figura 7,

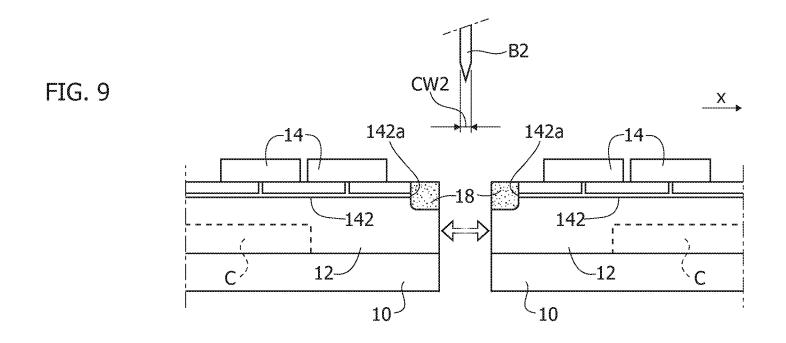

la Figura 9 è una vista in sezione sostanzialmente corrispondente alla Figura 8 dopo una fase di singolazione secondo forme di attuazione della presente descrizione, e

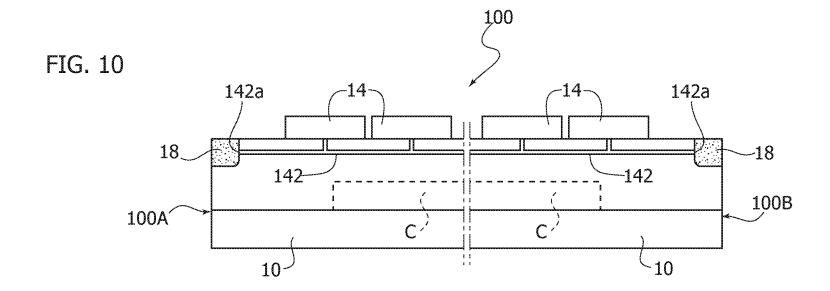

la Figura 10 è una vista in sezione trasversale parzialmente spaccata di un dispositivo a semiconduttore fabbricato secondo forme di attuazione della presente descrizione.

#### Descrizione dettagliata

Nella descrizione che segue vengono illustrati uno o più dettagli specifici, volti a permettere una comprensione approfondita di esempi di forme di attuazione della presente descrizione. Le forme di attuazione possono essere ottenute senza uno o più dei dettagli specifici, o con altri procedimenti, componenti, materiali, ecc. In altri casi, strutture, materiali od operazioni noti non sono illustrati o descritti in dettaglio in modo da non confondere certi aspetti di forme di attuazione.

Il riferimento a "una forma di attuazione" o "una sola forma di attuazione" nel contesto della presente descrizione intende indicare che una particolare

configurazione, struttura o caratteristica descritta in relazione alla forma di attuazione è compresa in almeno una forma di attuazione. Pertanto, espressioni come "in una forma di attuazione" o "in una sola forma di attuazione" che possono essere presenti in uno o più punti della presente descrizione non si riferiscono necessariamente a una sola e alla stessa forma di attuazione. Inoltre, configurazioni, strutture o caratteristiche particolari possono essere combinate in qualsiasi modo adeguato in una o più forme di attuazione.

I riferimenti qui utilizzati sono forniti solo per comodità e quindi non definiscono l'ambito di protezione o il campo delle forme di attuazione.

La tecnologia Direct Copper Interconnect (DCI), spesso indicata anche come tecnologia Laser Direct Structuring, (LDS), è stata proposta come modo per sostituire il wire bonding nei dispositivi a semiconduttore come, per esempio, i dispositivi a semiconduttore Quad-Flat No-leads (QFN).

Documenti come US 2018/342453 A1, US 2020/203264 A1, US 2020/321274 A1, US 2021/050226 A1 e US 2021/050299 A1 (tutti di titolarità della titolare della presente domanda) sono esemplificativi di sviluppi in tale settore.

La tecnologia DCI/LDS facilita la sostituzione del wire bonding fornendo piste e vias in rame che collegano chip a semiconduttore e leadframe associati.

La tecnologia DCI/LDS facilita anche la produzione di configurazioni "die-pad-up" (ovvero con un chip o die a semiconduttore disposto "a faccia in giù" all'interno di un package di dispositivo) con interconnessioni e contatti disposti sul lato inferiore del package, con la possibilità di fare a meno di un leadframe convenzionale.

Una configurazione "die-pad-up" facilita la

dissipazione termica con la possibilità di superare i limiti di gestione termica che si manifestano in dispositivi come i dispositivi QFN che adottano una configurazione "die-pad-down" convenzionale. Per esempio, si riscontra che un dissipatore di calore esterno applicato su una disposizione "die-pad-up" mostra prestazioni termiche significativamente migliorate.

Quali che siano i dettagli specifici, nella tecnologia DCI/LDS formazioni elettricamente conduttive (per esempio le interconnessioni in rame) sono prodotte mediante attivazione a raggio laser di un composto di stampaggio 12 attivabile mediante laser che incapsula die o chip a semiconduttore C disposti su un substrato 10 come visibile nelle figure come le Figure 4, 6, 8, 9 e 10.

Così come discusso, per esempio, nei documenti brevetto di titolarità comune citati in precedenza, l'attivazione laser facilita la crescita di materiale elettricamente conduttivo (come il rame) in un processo di placcatura che può comportare la placcatura electroless seguita da una fase elettrolitica per produrre formazioni "più spesse" che hanno una migliore conducibilità elettrica.

Contatti elettricamente conduttivi così formati sono mostrati a titolo di esempio e indicati con 14 nelle figure.

Il processo di placcatura è facilitato dalla previsione di linee di placcatura che collegano i vari siti in cui sono fornite formazioni elettricamente conduttive per fungere da anodo nei processi di (elettro)placcatura.

Come peraltro convenzionale nel settore, i dispositivi a semiconduttore sono solitamente fabbricati disponendo una pluralità di chip a semiconduttore C su un substrato, a

striscia, allungato (destinato a fornire un cosiddetto "slug", per esempio, nei singoli dispositivi finali) che si estende in una (prima) direzione x longitudinale, con i chip a semiconduttore distribuiti lungo la lunghezza del substrato allungato 10.

Un incapsulamento isolante come 12 di un materiale attivabile mediante laser viene quindi provvisto (stampato) sui chip a semiconduttore C distribuiti lungo la lunghezza del substrato 10.

Di conseguenza, come discusso in precedenza, si prevedono linee di placcatura che attraversano tutti i siti in cui si intendono produrre singoli dispositivi a semiconduttore.

La Figura 1 è una vista in pianta di fianchi mutualmente affacciati di due dispositivi a semiconduttore durante una fase di fabbricazione prima di una fase di singolazione per produrre singoli dispositivi a semiconduttore.

Come è esemplificato nella Figura 1, queste linee di placcatura possono comprendere:

prime linee di placcatura (primarie) 141 che si estendono attraverso il substrato a striscia 10 in una (seconda) direzione y trasversale alla (prima) direzione x longitudinale, e

seconde linee di placcatura (secondarie) 142 che si diramano dalle prime linee di placcatura 141 verso le formazioni elettricamente conduttive 14.

La Figura 2 è una vista in pianta di fianchi mutualmente affacciati di due dispositivi a semiconduttore durante una fase di fabbricazione dopo una fase di singolazione per produrre singoli dispositivi a semiconduttore.

La Figura 2 è esemplificativa di una fase di singolazione convenzionale in cui un substrato a striscia avente chip a semiconduttore C distribuiti su di esso e incapsulati in un incapsulamento isolante 12 (in cui sono state fornite formazioni elettricamente conduttive 14) viene reciso (tagliato) per produrre singoli dispositivi a semiconduttore.

Come esemplificato in Figura 2, tale fase di taglio può essere eseguita (nella direzione y trasversale alla direzione x longitudinale del substrato) con una singola lama B controllata (in modo di per sé noto agli esperti del settore) in modo da agire in corrispondenza dei siti in cui sono provviste le prime linee di placcatura 141.

In tal modo, le prime linee di placcatura 141 possono essere rimosse.

Come è esemplificato in Figura 2, dopo la singolazione del package, le porzioni rimanenti 142a delle seconde linee placcatura (cioè le porzioni di accoppiamento "prossimali" delle seconde linee di placcatura 142 alle prime linee di placcatura 141 situate in prossimità delle prime linee di placcatura 141) rimangono esposte corrispondenza dei fianchi dei singoli dispositivi a semiconduttore risultanti dall'azione di taglio della lama В.

Queste porzioni di accoppiamento esposte 142a sono collegate elettricamente alle formazioni elettricamente conduttive 14: nel caso di applicazioni ad alta tensione (HV), le porzioni di accoppiamento esposte 142a possono avere applicate tensioni elevate con il rischio di creare problemi di creepage e/o possibili cortocircuiti verso circuiti a circuiti e componenti vicini. Una scheda a circuito stampato o PCB "popolata" e/o un dissipatore di

calore (elettricamente conduttivo) esterno possono essere esempi di questi circuiti e componenti.

Si può cercare di affrontare il problema illustrato in relazione alle Figure 1 e 2 applicando sui singoli dispositivi singolati uno rivestimento conforme spesso di materiale elettricamente isolante in modo da rivestire le porzioni di accoppiamento 142a delle seconde linee di placcatura 142.

Materiali a base di silicone applicati dopo il montaggio della PCB possono essere esemplificativi di tale rivestimento conforme.

Un rivestimento conforme può essere applicato spruzzando un rivestimento su tutta la superficie del dispositivo. Questo può comportare uno spesso strato elettricamente (e anche termicamente) isolante applicato come rivestimento sull'intero package.

Soprattutto nel caso di una disposizione "die-pad-up", rivestimento può influire negativamente di prestazioni scambio termico del dispositivo (per esempio, trasferimento del calore verso un dissipatore di calore): i materiali adatti all'uso per fornire un tale rivestimento conforme di solito mostrano bassa conduttività termica (inferiore a 0,1 W/mC°).

Come è esemplificato nella Figura 3 e nelle figure successive, un approccio come qui illustrato contempla un processo di taglio in due fasi con una fase intermedia di incapsulamento delle porzioni di accoppiamento esposte 142a delle (seconde) linee di placcatura 142.

In tutte le Figure 3 a 10, parti o elementi uguali a parti o elementi già discussi in relazione alle Figure 1 e 2 sono indicati con gli stessi simboli di riferimento. Per brevità non si ripeterà una descrizione dettagliata di

queste parti o di questi elementi.

Le Figure 3 e 4 sono rappresentative di una situazione sostanzialmente simile alla situazione illustrata in Figura 1, ovvero:

una pluralità di chip a semiconduttore C (per semplicità ne sono illustrati solo due) distribuiti lungo la lunghezza di un substrato allungato a striscia 10 che si estende in una prima direzione x (longitudinale),

un incapsulamento isolante 12 della pluralità di chip a semiconduttore C sul substrato 10, e

formazioni elettricamente conduttive 14 provviste sull'incapsulamento isolante 12 mediante placcatura (per esempio, dopo attivazione o strutturazione laser dell'incapsulamento attivabile mediante laser 12).

Di nuovo, come illustrato nelle Figure 3 e 4, la placcatura delle formazioni elettricamente conduttive 14 comprende la formazione di linee di placcatura elettricamente conduttive che comprendono:

prime linee di placcatura 141 che si estendono in una direzione y trasversale alla direzione x longitudinale del substrato 10, e

seconde linee di placcatura 142 che si diramano dalle prime linee di placcatura 141 verso le formazioni elettricamente conduttive 14, le seconde linee di placcatura 142 avendo porzioni di accoppiamento (prossimali) 142a alle prime linee di placcatura 141.

Come discusso in precedenza, una o più forme di attuazione possono essere vantaggiosamente (ma, non esclusivamente) applicate alla fabbricazione di dispositivi a semiconduttore utilizzanti la tecnologia CDI/LDS in cui (in modo di per sé noto agli esperti del settore):

un incapsulamento isolante attivabile mediante laser

12 è provvisto per una pluralità di chip a semiconduttore C su un substrato allungato 10,

energia di raggio laser viene applicata per strutturare formazioni elettricamente conduttive 14 e linee di placcatura 141, 142 nell'incapsulamento isolante attivabile mediante laser 12, e

materiale elettricamente conduttivo (per esempio, rame) viene fatto crescere sulle formazioni elettricamente conduttive 14 e sulle linee di placcatura 141, 142 strutturate nell'incapsulamento isolante attivato mediante laser 12.

Le Figure 4, 6 e 8 a 10 illustrano soluzioni in cui le linee di placcatura 141 e 142 si trovano tutte su un singolo livello, il che peraltro non rappresenta una caratteristica imperativa.

Inoltre, le Figure 4, 6 e 8 a 10 illustrano in dettaglio soluzioni in cui, come peraltro convenzionale nel settore, al disopra delle linee di placcatura 141, 142 viene provvisto un sottile strato di incapsulamento aggiuntivo (mostrato e non espressamente indicato con un riferimento) allo scopo di coprire le linee di placcatura.

Come illustrato nelle Figure 5 e 6, un procedimento come qui illustrato comprende una prima fase di taglio -- parziale -- del substrato allungato 10 avente la pluralità di chip a semiconduttore C disposti su di esso nonché l'incapsulamento isolante 12.

Contrariamente alla fase di singolazione convenzionale esemplificata in Figura 2 (una singola fase di taglio completa eseguita utilizzando una lama B avente una larghezza di taglio, per esempio, di 325 micron) la prima fase di taglio esemplificata nelle Figure 3 e 4 è una fase di taglio parziale che rimuove le prime linee di placcatura

141 che si estendono nella direzione y trasversale alla direzione x longitudinale del substrato 10.

Per effetto di tale fase di taglio parziale, in corrispondenza della superficie dell'incapsulamento 12 si formano trincee o scanalature 16 che si estendono nella direzione y trasversale alla direzione x del substrato a striscia allungato 10 su cui sono distribuiti i die a semiconduttore C.

Le trincee o scanalature 16 così formate hanno le porzioni di accoppiamento 142a di seconde linee di placcatura 142 esposte in corrispondenza delle loro pareti laterali (interne).

Quali che siano le specifiche opzioni di implementazione, la fase di taglio parziale delle Figure 5 e 6 può essere eseguita utilizzando una lama di taglio B1 "larga", cioè una lama avente una larghezza di taglio CW1, per esempio, di 450 micron.

Le Figure 7 e 8 sono esemplificative della possibilità di erogare materiale elettricamente isolante 18 nelle trincee o scanalature 16 (a seguito della rimozione delle prime linee di placcatura 141).

Il materiale isolante 18 può comprendere, per esempio, resina termoindurente (di qualsiasi tipo convenzionale noto nel settore, per esempio materiale resist o materiale per stampaggio di package non LDS come resina epossidica) erogata nelle trincee o scanalature 16 allo stato scorrevole (fuso), per esempio, mediante un'apparecchiatura di erogazione convenzionale, non visibile per semplicità.

Dopo la solidificazione del materiale 18 (per esempio, mediante indurimento a caldo o UV, come rappresentato da H in Figura 8 per il resto convenzionale nel settore) si può quindi completare la singolazione dei singoli dispositivi a

semiconduttore come esemplificato in Figura 9 utilizzando una lama B2 avente una larghezza di taglio CW2, per esempio, di 325 micron.

Questo può essere lo stesso tipo di lama da taglio esemplificato con B nella Figura 2.

La lama B2 può essere controllata (in modo di per sé noto agli esperti del settore) per agire in corrispondenza di un piano intermedio - teoricamente un piano mediano - delle trincee o scanalature 16 in cui il materiale isolante 18 è caricato e solidificato.

Occorre osservare che la prima fase di taglio parziale delle Figure 5 e 6 (eseguita vantaggiosamente con una lama "larga" come B1) ha l'effetto di rimuovere le prime linee di placcatura 141 lasciando sostanzialmente intatto il resto del package.

Dopo tale taglio parziale (teoricamente "mezzo taglio"), le trincee o scanalature 16 vengono riempite con materiale isolante (resina) 18 che crea (dopo la solidificazione e il taglio di singolazione finale in corrispondenza di un piano intermedio delle trincee o scanalature 16) un incapsulamento isolante delle porzioni di accoppiamento 142a delle seconde linee di placcatura 142.

incapsulamento isola le di Questo porzioni accoppiamento 142a dai fianchi laterali dei dispositivi 100 che vengono separati dopo la singolazione (finale) come esemplificato in Figura 9, contrastando così efficacemente i problemi di creepage discussi in precedenza.

Come illustrato in Figura 10, questo effetto di incapsulamento può essere ottenuto in corrispondenza di uno qualsiasi dei fianchi 100A, 100B del singolo dispositivo a

semiconduttore 100 risultante dalla fase di singolazione (finale) di Figura 9.

Un dispositivo a semiconduttore 100 come illustrato in Figura 10 comprende quindi uno (o più) chip a semiconduttore C disposti su un substrato di supporto ("slug" 10) e incapsulati da un incapsulamento isolante 12 avente una superficie opposta al substrato di supporto 10 con tale superficie (rivolta verso l'alto in Figura 10) avente formazioni 14 elettricamente conduttive placcate su di essa.

Come illustrato in Figura 10, il dispositivo 100 si estende in una prima direzione x tra fianchi opposti 100A, 100B del dispositivo 100.

Questi fianchi opposti 100A, 100B risultano dalla singolazione come illustrato in Figura 9 e si estendono quindi in una seconda direzione, cioè y, trasversale alla prima direzione x.

Come è illustrato in Figura 10, i fianchi opposti 100A, 100B del dispositivo 100 hanno spigoli (d'angolo) terminali in corrispondenza della superficie - rivolta verso l'alto in Figura 10 - con le formazioni elettricamente conduttive 14 placcate su di essa.

Come visibile in Figura 10, le formazioni elettricamente conduttive 14 hanno ad esse accoppiate linee elettricamente conduttive 142 che si estendono verso i bordi delle porzioni di accoppiamento dei fianchi opposti 100A, 100B del dispositivo 100.

Come risultato delle fasi illustrate nelle Figure 5 a 9, in corrispondenza degli spigoli terminali dei fianchi opposti 100A, 100B del dispositivo 100 sono provvisti inserti elettricamente isolanti formati dal materiale isolante (solidificato) 18.

Come visibile in Figura 10, le linee elettricamente conduttive 142 terminano a distanza dai fianchi opposti 100A, 100B del dispositivo 100, con le rispettive porzioni di accoppiamento 142a incapsulate dagli inserti elettricamente isolanti formati dal materiale 18.

Come visibile nella Figura 10, il/i chip a semiconduttore C può/possono essere disposto/disposti sul substrato di supporto (o slug, 10) in relazione di trasferimento del calore con il substrato di supporto 10 (per esempio, stando direttamente contro il substrato di supporto 10).

Pur con una rappresentazione "capovolta" per semplicità, la disposizione illustrata in Figura 10 può corrispondere alla configurazione attualmente denominata configurazione "die-pad-up", con il dispositivo infine montato su una PCB, per esempio, con lo slug 10 rivolto verso l'alto e le formazioni 14 rivolte verso il basso.

In tal modo, le formazioni elettricamente conduttive e/o (contatti pad) 14 placcate sulla superficie dell'incapsulamento 12 opposta al substrato di supporto 10 possono essere configurate per fornire una connessione elettrica per il/i chip а semiconduttore disposto/disposti sul substrato di supporto 10.

Il substrato di supporto 10 può essere (e effettivamente è) scelto per essere termicamente conduttivo (per esempio, un metallo) al fine di facilitare la dissipazione del calore generato durante il funzionamento del dispositivo 100.

Gli inserti elettricamente isolanti 18 previsti in corrispondenza degli spigoli terminali o d'angolo dei fianchi opposti 100A, 100B del dispositivo 100 isolano elettricamente le rispettive porzioni di accoppiamento 142a

delle (seconde) linee elettricamente conduttive 142 rispetto ai fianchi opposti 100A, 100B del dispositivo 100.

Fermi restando i principi di base, i dettagli e le forme di attuazione potranno variare, anche in modo significativo, rispetto a quanto descritto solo a titolo di esempio, senza per questo discostarsi dall'ambito di protezione.

L'ambito di protezione è determinato dalle rivendicazioni allegate.

#### RIVENDICAZIONI

# 1. Procedimento, comprendente:

disporre una pluralità di chip a semiconduttore (C) su un substrato allungato (10) che si estende in una direzione longitudinale (x), i chip a semiconduttore (C) essendo distribuiti lungo la lunghezza del substrato allungato (10),

fornire un incapsulamento isolante (12) della pluralità di chip a semiconduttore (C) su detto substrato (10),

placcare formazioni elettricamente conduttive (14) sull'incapsulamento isolante (12), in cui placcare formazioni elettricamente conduttive (14) comprende formare di linee di placcatura elettricamente conduttive, le linee di placcatura comprendendo prime linee di placcatura (141) che si estendono in una direzione (y) trasversale a detta direzione longitudinale (x) nonché seconde linee di placcatura (142) che si diramano dalle prime linee placcatura (141) verso dette formazioni elettricamente conduttive (14), le seconde linee di placcatura avendo porzioni di accoppiamento (142a) alle prime linee di placcatura (141), e

produrre dispositivi a semiconduttore singolati tagliando in detta direzione (y) trasversale a detta direzione longitudinale (x) il substrato allungato (10) avente la pluralità di chip a semiconduttore (C) disposti su di esso nonché l'incapsulamento isolante (12),

in cui il procedimento comprende:

una prima fase di taglio parziale (B1) in detta direzione (y) trasversale a detta direzione longitudinale (x) per rimuovere dette prime linee di placcatura (141) che si estendono in detta direzione (y) trasversale a detta

direzione longitudinale (x), formando scanalature (16) che si estendono in detta direzione (y) trasversale a detta direzione longitudinale (x) con le porzioni di accoppiamento (142a) delle seconde linee di placcatura (142) esposte in corrispondenza delle pareti laterali di dette scanalature (16),

erogare materiale isolante (18) in dette scanalature (16), in cui il materiale isolante (18) incapsula le porzioni di accoppiamento (142a) delle seconde linee di placcatura (142), e

una seconda fase di taglio (B2) in detta direzione (y) trasversale a detta direzione longitudinale (x) attraverso il substrato allungato (10) avente la pluralità di chip a (C) disposti di semiconduttore su esso l'incapsulamento isolante (12), la seconda fase di taglio eseguita in corrispondenza di essendo un intermedio di dette scanalature (16) in cui è contenuto detto materiale isolante (18) per produrre dispositivi a semiconduttore singolati in cui le porzioni accoppiamento (142a) delle seconde linee di placcatura (142) sono incapsulate da detto materiale isolante (18).

- 2. Procedimento secondo la rivendicazione 1, comprendente la solidificazione del materiale isolante (18) erogato in dette scanalature (16) prima di detta seconda fase di taglio (B2).

- 3. Procedimento secondo la rivendicazione 2, comprendente:

erogare materiale isolante termoindurente (18) in dette scanalature (16), e

solidificare il materiale isolante termoindurente (18) erogato in dette scanalature (16) mediante esposizione ad

una fonte di calore (H).

4. Procedimento secondo una qualsiasi delle rivendicazioni precedenti, comprendente:

eseguire la prima fase di taglio parziale con un primo strumento di taglio (B1) avente una prima larghezza di taglio (CW1), e

eseguire la seconda fase di taglio con un secondo strumento di taglio (B2) avente una seconda larghezza di taglio (CW2), in cui la prima larghezza di taglio (CW1) è maggiore della seconda larghezza di taglio (CW2).

5. Procedimento secondo una qualsiasi delle rivendicazioni precedenti, comprendente:

fornire un incapsulamento isolante attivabile mediante laser (12) della pluralità di chip a semiconduttore (C) su detto substrato (10),

applicare energia di raggio laser per strutturare dette formazioni elettricamente conduttive (14) e dette linee di placcatura (141, 142) in detto incapsulamento isolante attivabile mediante laser, e

crescere materiale elettricamente conduttivo sulle formazioni elettricamente conduttive (14) e sulle linee di placcatura (141, 142) strutturate nell'incapsulamento isolante attivato mediante laser (12).

#### 6. Dispositivo (100), comprendente:

almeno un chip a semiconduttore (C) disposto su un substrato di supporto (10), l'almeno un chip a semiconduttore (C) essendo incapsulato da un incapsulamento isolante (12) avente una superficie opposta al substrato di supporto (10) con formazioni elettricamente conduttive (14) placcate su detta superficie, in cui:

il dispositivo si estende in una prima direzione (x) tra fianchi opposti (100A, 100B) del dispositivo (100), detti fianchi opposti del dispositivo (100) estendendosi in una seconda direzione (y) trasversale alla prima direzione (x) e aventi spigoli terminali in corrispondenza di detta superficie opposta al substrato di supporto (10),

le formazioni elettricamente conduttive (14) hanno ad esse accoppiate linee di placcatura elettricamente conduttive (142) che si estendono verso detti spigoli terminali dei fianchi opposti (100A, 100B) del dispositivo (100), e

in corrispondenza di detti spigoli terminali dei fianchi opposti (100A, 100B) del dispositivo (100) sono provvisti inserti elettricamente isolanti (18), in cui dette linee di placcatura elettricamente conduttive (142) terminano a distanza dai fianchi opposti (100A, 100B) del dispositivo (100) e hanno rispettive porzioni finali (142a) incapsulate da detti inserti (18) elettricamente isolanti.

- 7. Dispositivo secondo la rivendicazione 6, in cui detti inserti (18) comprendono materiale isolante termoindurente.

- 8. Dispositivo secondo la rivendicazione 6 o la rivendicazione 7, in cui:

l'almeno un chip a semiconduttore (C) è disposto sul substrato di supporto (10) in rapporto di trasferimento del calore con il substrato di supporto (10), il substrato di supporto (10) essendo termicamente conduttivo,

le formazioni elettricamente conduttive (14) placcate su detta superficie opposta al substrato di supporto (10) sono configurate per fornire connessione elettrica per almeno un chip a semiconduttore (C) disposto su detto

substrato di supporto (10), e

detti inserti elettricamente isolanti (18) forniti in corrispondenza di detti spigoli terminali dei fianchi opposti (100A, 100B) del dispositivo (100) isolano elettricamente le rispettive porzioni finali (142a) di dette linee di placcatura (142) elettricamente conduttive rispetto ai fianchi opposti (100A, 100B) del dispositivo (100).

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8