(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-243049

(P2007-243049A)

(43) 公開日 平成19年9月20日(2007.9.20)

| (51) Int.C1.                  | F 1         | テーマコード (参考) |

|-------------------------------|-------------|-------------|

| <b>HO1L 29/78</b> (2006.01)   | HO1L 29/78  | 301G 5FO48  |

| <b>HO1L 21/8238</b> (2006.01) | HO1L 27/08  | 321D 5FO58  |

| <b>HO1L 27/092</b> (2006.01)  | HO1L 21/316 | M 5F140     |

| <b>HO1L 21/316</b> (2006.01)  | HO1L 21/316 | X           |

審査請求 未請求 請求項の数 9 O L (全 16 頁)

|           |                            |          |                                                  |

|-----------|----------------------------|----------|--------------------------------------------------|

| (21) 出願番号 | 特願2006-66300 (P2006-66300) | (71) 出願人 | 000219967<br>東京エレクトロン株式会社<br>東京都港区赤坂五丁目3番6号      |

| (22) 出願日  | 平成18年3月10日 (2006.3.10)     | (74) 代理人 | 100070150<br>弁理士 伊東 忠彦                           |

|           |                            | (72) 発明者 | 秋山 浩二<br>東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内  |

|           |                            | (72) 発明者 | 青山 真太郎<br>東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内 |

|           |                            | (72) 発明者 | 高橋 毅<br>東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内   |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】h i g h - K ゲート絶縁膜を使った半導体装置において、ゲート絶縁膜への電荷のトラップを抑制する。

【解決手段】ゲート電極を、その下の界面酸化膜に接して形成され、小さな電子親和力と大きなバンドギャップを有する第1の絶縁膜と、ゲート電極に接して形成され、より大きな電子親和力とより小さなバンドギャップを有する第2の絶縁膜の積層により形成する。

【選択図】図12

**【特許請求の範囲】****【請求項 1】**

シリコン基板上に、界面酸化膜を介して形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、

前記シリコン基板中、前記ゲート電極の第1および第2の側にそれぞれ形成された第1

および第2の拡散領域と、

よりなる半導体装置であって、

前記ゲート絶縁膜は、前記界面酸化膜上に接して形成された第1の絶縁膜と、前記ゲー

ト電極に接して形成された第2の絶縁膜を含み、

前記第2の絶縁膜は、前記第1の絶縁膜よりも大きな電子親和力を有し、前記ゲート電

極は、前記第2の絶縁膜よりも大きな電子親和力を有することを特徴とする半導体装置。 10

**【請求項 2】**

前記第1の絶縁膜は、前記第2の絶縁膜よりも大きなバンドギャップを有することを特徴

とする請求項1記載の半導体装置。

**【請求項 3】**

前記第2の絶縁膜は、前記第1の絶縁膜に接して形成されていることを特徴とする請求

項1または2記載の半導体装置。

**【請求項 4】**

前記第1の絶縁膜の伝導帯と前記第2の伝導帯との間には、段差が存在することを特徴

とする請求項1～3記載の半導体装置。 20

**【請求項 5】**

前記第1および第2の絶縁膜はHfSiON膜であり、前記第1の絶縁膜は前記第2の

絶縁膜よりも高いSi濃度を有することを特徴とする請求項1記載の半導体装置。

**【請求項 6】**

前記第1の絶縁膜と前記第2の絶縁膜の間で、Si濃度が不連続に変化することを特徴

とする請求項5記載の半導体装置。

**【請求項 7】**

前記第1の伝導帯は前記第2の伝導帯に、連続的に遷移することを特徴とする請求項1

～3のうち、いずれか一項記載の半導体装置。

**【請求項 8】**

前記第1および第2の絶縁膜はHfSiON膜であり、前記第1の絶縁膜は前記第2の

絶縁膜よりも高いSi濃度を有し、前記Si濃度は、前記第1の絶縁膜から前記第2の絶

縁膜に、連続的に遷移することを特徴とする請求項7記載の半導体装置。 30

**【請求項 9】**

前記ゲート電極は、金属よりなることを特徴とする請求項1～8のうち、いずれか一項

記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は一般に半導体装置に係り、特に高誘電体ゲート絶縁膜を有する半導体装置の関

する。 40

**【背景技術】****【0002】**

今日の超高速半導体装置では、微細化プロセスの進歩とともに、30nm以下のゲート

長が可能になりつつある。一般に微細化とともに半導体装置の動作速度は向上するが、こ

のよう非常に微細化された半導体装置では、ゲート絶縁膜の膜厚を、微細化によるゲー

ト長の短縮に伴って、スケーリング則に従って減少させる必要がある。

**【0003】**

しかしゲート長が30nm以下になると、ゲート絶縁膜の厚さも、従来の熱酸化膜を使

った場合、1nm、あるいはそれ以下に設定する必要があるが、このように非常に薄いゲ

ート絶縁膜を有する半導体装置では、ゲート電極の電荷注入によってゲート電極と

半導体基板との間の界面酸化膜が破壊され、ゲート電極と半導体基板との間の

界面が露出する。この露出した界面は、ゲート電極の電荷注入によって酸化され

て、ゲート絶縁膜の膜厚を増加する。この現象は、ゲート電極の電荷注入によって

ゲート絶縁膜の膜厚を増加する現象を「ゲート絶縁膜の膜厚の増加」または

「ゲート絶縁膜の膜厚の増加現象」と呼ぶ。 50

ート絶縁膜ではトンネル電流が増大し、その結果ゲートリーク電流が増大する問題を回避することができない。

【0004】

このような事情で従来、比誘電率が熱酸化膜のものよりもはるかに大きく、このため実際の膜厚が大きくても  $\text{SiO}_2$  膜に換算した場合の膜厚が小さい  $\text{Ta}_2\text{O}_5$  や  $\text{Al}_2\text{O}_3$  ,  $\text{ZrO}_2$  ,  $\text{HfO}_2$  、さらには  $\text{ZrSiO}_4$  あるいは  $\text{HfSiO}_4$  のような高誘電体材料（いわゆる high-K 材料）をゲート絶縁膜に対して適用することが提案されている。このような高誘電体材料を使うことにより、ゲート長が 30 nm 以下と、非常に短い超高速半導体装置においても 1 ~ 2 nm 程度の物理的膜厚のゲート絶縁膜を使うことができ、トンネル効果によるゲートリーク電流を抑制することができる。特に  $\text{HfSiON}$  膜を使ったゲート絶縁膜が、このような超微細化半導体装置のゲート絶縁膜として有望視されている。

【0005】

チャネル領域中のキャリアモビリティを向上させる観点からは、高誘電体ゲート酸化膜とシリコン基板との間に、1 nm 以下、好ましくは 0.8 nm 以下の厚さのきわめて薄いベース酸化膜を介在させるのが好ましい。ベース酸化膜は非常に薄い必要があり、厚さが厚いと高誘電体膜をゲート絶縁膜に使った効果が相殺される。一方、かかる非常に薄いベース酸化膜は、シリコン基板表面を一様に覆う必要があり、また界面準位等の欠陥を形成しないことが要求される。従来、このように非常に薄い界面酸化膜を、紫外光励起酸素ラジカルにより形成する技術が確立している。

【特許文献 1】特開 2005-45166 号公報

【特許文献 2】特開 2003-204061 号公報

【特許文献 3】特開 2004-31760 号公報

【特許文献 4】特開 2004-186567 号公報

【特許文献 5】特開 2004-000614 号公報

【非特許文献 1】Jpn. J. Appl. Phys. vol. 43, No. 12, 2004, pp. 8199-8202

【発明の開示】

【発明が解決しようとする課題】

【0006】

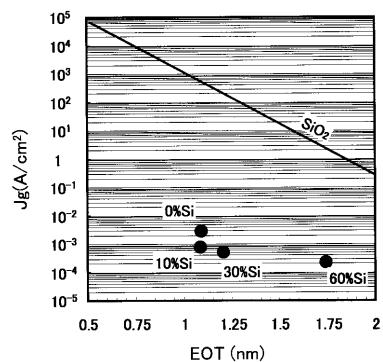

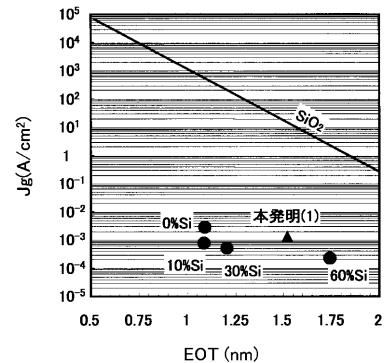

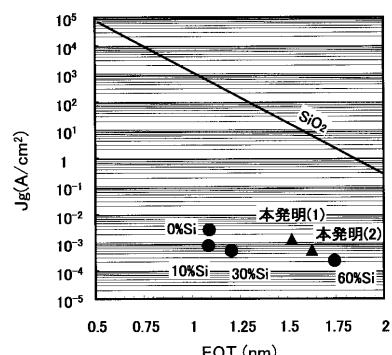

図 1 は、このような  $\text{HfSiON}$  膜のリーク電流  $J_g$  と酸化膜換算膜厚の関係を示す。ただし図 1 は、本発明者が本発明の基礎となる研究において得たものであり、本発明の一部を構成するものである。

【0007】

図 1 中、連続線はシリコン基板上に形成された熱酸化膜のリーク電流特性を示しており、図 1 中にはさらに、 $\text{Si}$  濃度を 0 %、10 %、30 %、60 %とした場合の、前記  $\text{HfSiON}$  膜のリーク電流特性が示されている。ただし図 1 において酸化膜換算膜厚  $EOT$  およびリーク電流  $J_g$  は、シリコン基板上に、熱酸化膜あるいは  $\text{HfSiON}$  膜を介して  $n+$  型の電極を有する  $\text{MOS}$  キャパシタを形成し、かかる  $\text{MOS}$  キャパシタに対して測定を行っている。その際、前記  $\text{HfSiON}$  膜は、シリコン基板表面に、厚さが 0.4 nm の界面酸化膜を介して形成している。

【0008】

図 1 を参照するに、同一のリーク電流値で比較した場合、 $\text{HfSiON}$  膜の酸化膜換算膜厚  $EOT$  は、熱酸化膜に比べて大きく減少しているのがわかる。

【0009】

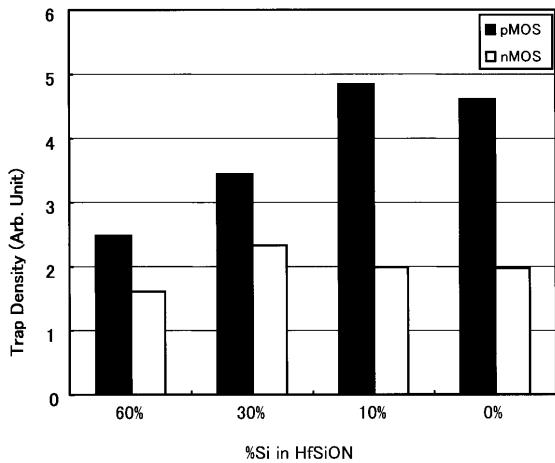

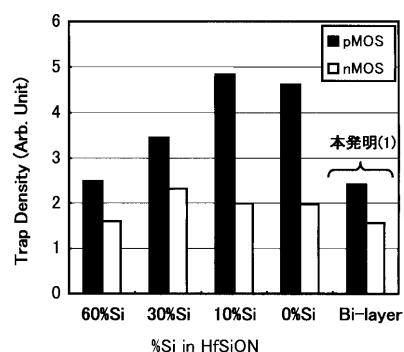

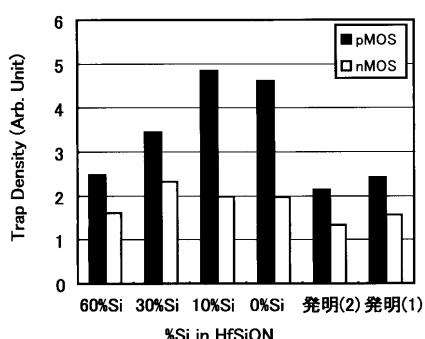

このように、 $\text{HfSiON}$  膜を使うことによりゲート絶縁膜の酸化膜換算膜厚  $EOT$  は大きく減少させることができるが、このような  $\text{HfSiON}$  膜中には、図 2 に示すように、特に  $p\text{MOS}$  構造の場合に多量の電荷トラップが形成されることが見いだされた。ただし図 2 は、 $\text{HfSiON}$  膜をゲート絶縁膜とした  $p\text{MOS}$  構造および  $n\text{MOS}$  構造における電荷トラップ密度と  $\text{HfSiON}$  膜中の  $\text{Si}$  濃度の関係を示す。このようにゲート絶縁膜中に多量の電荷トラップが形成されると、半導体装置のしきい値特性が変動してしまい、また移動度も低下し、半導体装置の安定な高速動作が不可能になる。

10

20

30

40

50

## 【課題を解決するための手段】

## 【0010】

一の側面によれば本発明は、シリコン基板上に、界面酸化膜を介して形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記シリコン基板中、前記ゲート電極の第1および第2の側にそれぞれ形成された第1および第2の拡散領域と、よりなる半導体装置であって、

前記ゲート絶縁膜は、前記界面酸化膜よりもバンドギャップの小さい第1および第2の絶縁膜を、前記界面酸化膜上に順次積層した構造を有し、

前記第1の絶縁膜は、前記第2の絶縁膜よりも大きなバンドギャップを有することを特半導体装置を提供する。

## 【発明の効果】

## 【0011】

本発明によれば、前記ゲート絶縁膜を、界面酸化膜に接する部分においては大きな電子親和力を有しゲート電極に接する部分では小さな電子親和力を有するように構成することにより、nチャネルMOSトランジスタにおいては前記ゲート絶縁膜中にチャネル中の電子に対する高い障壁が形成され、前記チャネル領域から前記ゲート絶縁膜への電子の侵入が抑制されると同時に、仮に電子が侵入した場合でも、侵入した電子を、ゲート絶縁膜中に蓄積することなく、速やかにゲート電極へと排出することができ、ゲート電極中への電荷のトラップによるしきい値特性の変動を抑制することができる。またpチャネルMOSトランジスタにおいても、チャネル領域中のホールに対し、ゲート絶縁膜中に高い障壁を形成できると同時に、ゲート電極側から効率よくゲート絶縁膜中に電子を注入でき、仮にゲート絶縁膜中にホールが侵入しても、これを速やかに中和することが可能となる。

## 【発明を実施するための最良の形態】

## 【0012】

## [原理]

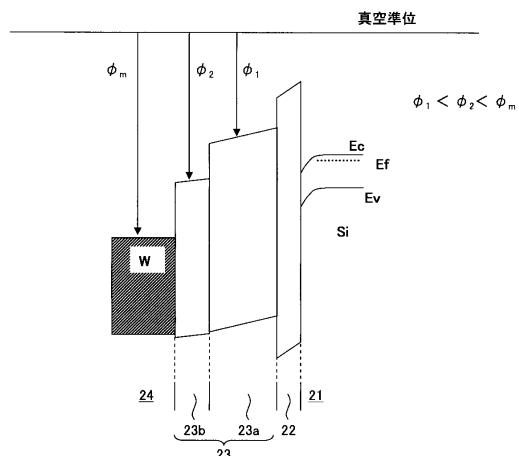

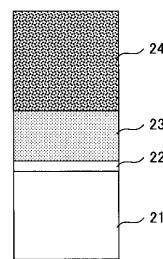

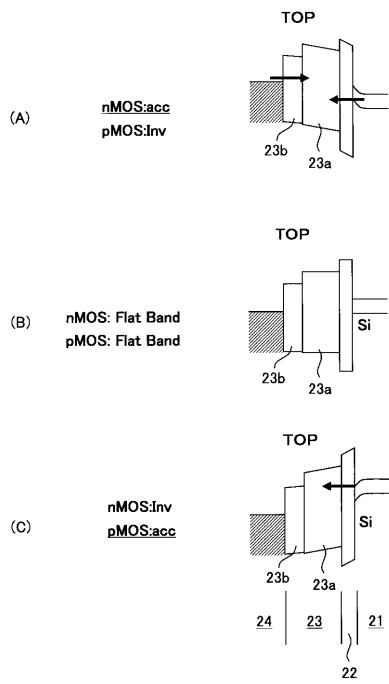

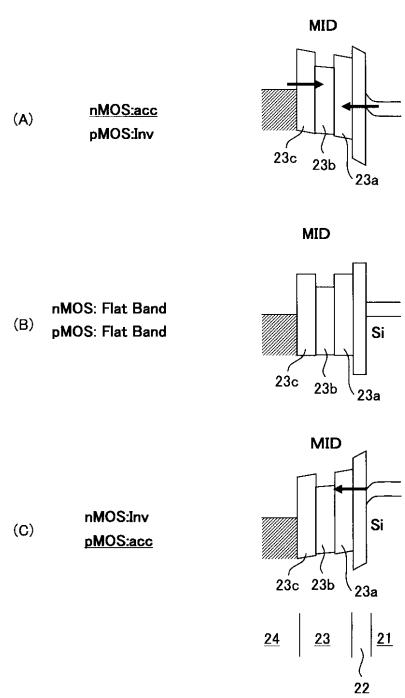

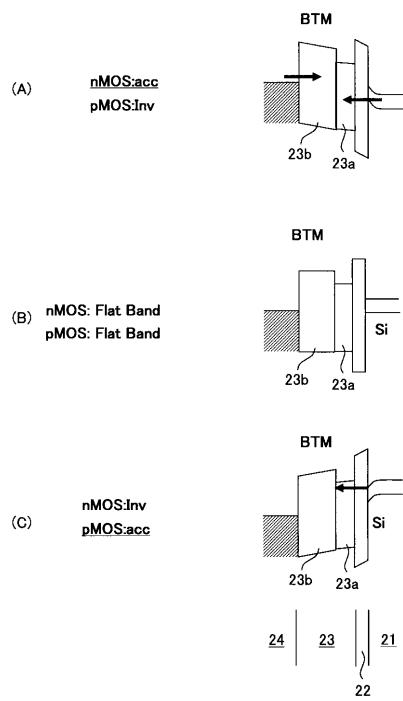

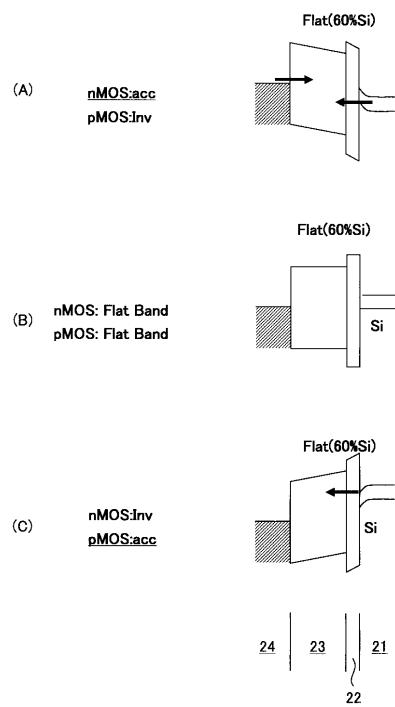

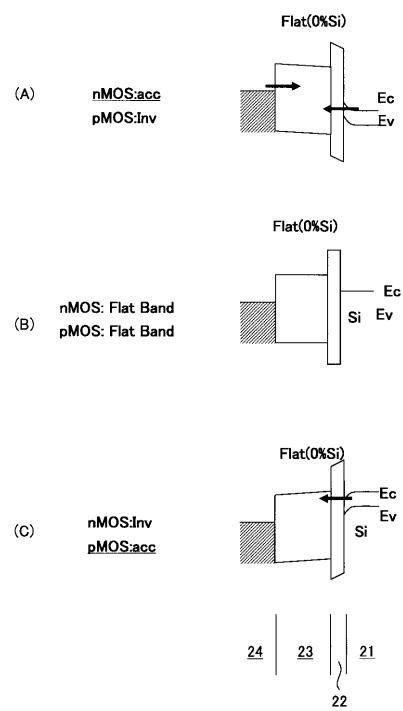

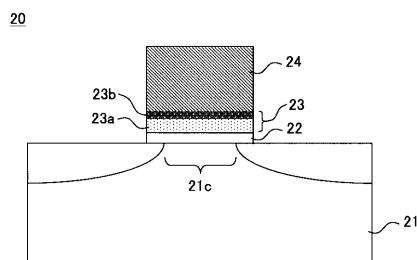

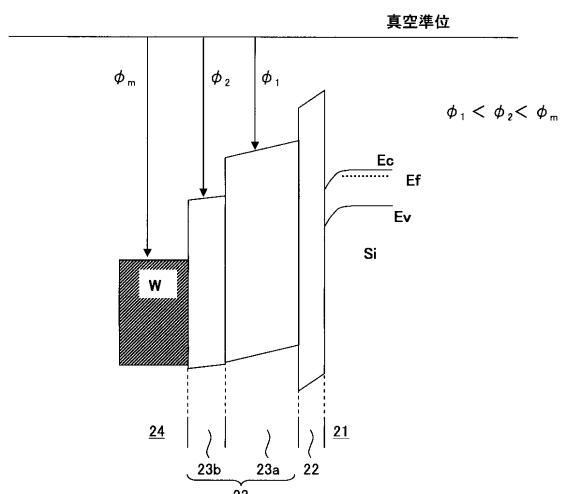

図4(A)～(C)～図8(A)～(C)は、図3の基本構造を示すMOS構造において、ゲート絶縁膜の構成を様々に変化させた場合のバンド構造を示す。

## 【0013】

図3を参照するに、シリコン基板21上には界面酸化膜22を介してゲート絶縁膜23が形成されており、前記ゲート絶縁膜23上には金属ゲート電極24が形成されている。

## 【0014】

図4(A)～(C)は、前記ゲート絶縁膜23が、前記界面酸化膜22に接して形成された、バンドギャップが大きい第1の絶縁膜23aと、前記ゲート電極24に接して形成された、バンドギャップが前記第1の絶縁膜よりは小さい第2の絶縁膜23bよりなる場合(以下、「TOP構成」と称する)を示しており、図4(A)は、前記図3の構成を有するnチャネルMOSトランジスタにおいて蓄積状態が、pチャネルMOSトランジスタにおいて反転状態が生じている場合を、図4(B)は、前記nチャネルMOSトランジスタおよびpチャネルMOSトランジスタとも、フラットバンド状態となっている場合を、さらに図4(C)は、前記nチャネルMOSトランジスタにおいて反転状態が、pチャネルMOSトランジスタにおいて蓄積状態が生じている場合を示す。

## 【0015】

図4(A)の状態では、pチャネルMOSトランジスタにおいて、シリコン基板21表面に形成されたチャネル領域中のホールに対して、前記第1の絶縁膜23aが高い障壁を形成し、ホールのゲート絶縁膜23への侵入を抑制する。また前記第2の絶縁膜23bはバンドギャップが小さいため、ゲート電極24から電子がゲート絶縁膜23に注入されやすく、このようにして注入された電子は、前記第1の絶縁膜23aにチャネル領域から侵入したホールを中和するように作用し、前記ゲート絶縁膜23における電荷トラップに起因するMOSトランジスタのしきい値の変動が抑制できる。

## 【0016】

図4(B)のフラットバンド状態では電荷注入は生じないが、図4(C)に示す、nチャネルMOSトランジスタの反転状態では、前記シリコン基板21の表面に誘起されたチャネル領域より電子がゲート絶縁膜23に侵入しようとする。しかし、この場合にも、界面酸化膜22に接して大きなバンドギャップを有する第1の絶縁膜23aが高い障壁を形成し、電子の侵入を抑制する。また、仮に界面準位などを介して電子が侵入しても、第2の絶縁膜23bが高いバリアを形成しないため、ゲート絶縁膜23に侵入した電子は速やかにゲート電極24へと逃がされ、膜中にトラップされたり、MOSトランジスタのしきい値特性が変調されたりするなどの問題が抑制される。すなわち、図4(A)～(C)のバンド構造は、nチャネルMOSトランジスタ、pチャネルMOSトランジスタのいずれにおいても、ゲート絶縁膜中へのキャリアのトラップを最小化できることがわかる。10

## 【0017】

図5(A)～(C)は、図4(A)～(C)のモデルにおいて、ゲート電極24と第2の絶縁膜の間に、バンドギャップの大きい第3の絶縁膜23cが形成された場合(以下、「MID構成」と称する)を示す。この場合にも図5(A)はpチャネルMOSトランジスタの反転状態を、図5(B)はフラットバンド状態を、図5(C)はnチャネルMOSトランジスタの反転状態を示す。

## 【0018】

図5(A)を参照するに、この場合にも、前記界面酸化膜22に接して形成された第1絶縁膜23aは、チャネル領域中のホールに対して高いバリアを形成するが、ゲート電極24に接して、第3の絶縁膜23cが高いバリアを形成し、ゲート電極24からの前記絶縁膜23への電子の注入が抑制される。このため、pチャネルMOSトランジスタの場合、図4(A)の場合のように効率的に、ゲート絶縁膜23中に注入されたホールを中和することはできない。20

## 【0019】

また図5(C)に示すnチャネルMOSトランジスタにおいては、ゲート絶縁膜23に侵入した電子は、前記ゲート電極24に接して、バンドギャップの大きい第3の絶縁膜23cが形成されているため、バンドギャップの大きな第1の絶縁膜23aと第3の絶縁膜23cの間でトラップされてしまう。

## 【0020】

図6(A)～(C)は、図3のモデルにおいて、前記界面酸化膜22に接してバンドギャップの小さい第1の絶縁膜23aが形成され、前記ゲート電極24に接して、バンドギャップの大きな第2の絶縁膜23bが形成された場合(以下、「BTM構成」と称する)を示す。この場合にも図6(A)はpチャネルMOSトランジスタの反転状態を、図6(B)はフラットバンド状態を、図6(C)はnチャネルMOSトランジスタの反転状態を示す(以下、「BTM構成」と称する)。30

## 【0021】

図6(A)を参照するに、この場合にも、前記界面酸化膜22に接して形成された第1絶縁膜は、チャネル領域中のホールに対して高いバリアを形成するが、ゲート電極24に接して、第2の絶縁膜23bが高いバリアを形成し、ゲート電極24からの前記絶縁膜24への電子の注入が抑制される。このため、pチャネルMOSトランジスタの場合、図4(A)の場合のように効率的に、ゲート絶縁膜23中に注入されたホールを中和することはできない。40

## 【0022】

また図6(C)に示すnチャネルMOSトランジスタにおいては、ゲート絶縁膜23に侵入した電子は、前記ゲート電極24に接して、バンドギャップの大きい第2の絶縁膜23bが形成されているため、バンドギャップの大きな界面酸化膜22と前記第2の絶縁膜23bの間でトラップされてしまう。

## 【0023】

図7(A)～(C)は、図3のモデルにおいて、前記ゲート絶縁膜23として、組成が

一様なHfSiON膜(Si原子濃度60%)を使った場合(以下、Flat(60%Si)構成と称する)を示す。この場合にも図7(A)はpチャネルMOSトランジスタの反転状態を、図7(B)はフラットバンド状態を、図7(C)はnチャネルMOSトランジスタの反転状態を示す。

【0024】

図7(A)を参照するに、HfSiON膜は、チャネル領域中のホールに対して高いバリアを形成するが、ゲート電極24中の電子に対しても高いバリアを形成し、ゲート電極24からの前記絶縁膜23への電子の注入が抑制される。このため、pチャネルMOSトランジスタの場合、図4(A)の場合のように効率的に、ゲート絶縁膜23中に注入されたホールを中和することはできない。

10

【0025】

また図7(C)に示すnチャネルMOSトランジスタにおいては、ゲート絶縁膜23に侵入した電子は、前記ゲート絶縁膜23のバンドギャップが大きいため、ゲート絶縁膜23への侵入が抑制される。ただし、ゲート絶縁膜23のバンドギャップは膜厚方向に一定であるため、侵入した電子のゲート電極24への排出が加速されるわけではない。

【0026】

図8(A)～(C)は、図3のモデルにおいて、前記ゲート絶縁膜23として、組成が一様なHfSiON膜(Si原子濃度0%)を使った場合(Flat(0%Si)構成)を示す。この場合にも図8(A)はpチャネルMOSトランジスタの反転状態を、図8(B)はフラットバンド状態を、図8(C)はnチャネルMOSトランジスタの反転状態を示す。

20

【0027】

図8(A)を参照するに、HfSiON膜(実際にはHfO<sub>2</sub>膜)は、チャネル領域中のホールに対して高いバリアを形成するが、ゲート電極24中の電子に対しては低いバリアを形成し、ゲート電極24からの前記絶縁膜23への電子の注入が生じる。このため、pチャネルMOSトランジスタの場合に、図4(A)の場合のように効率的に、ゲート絶縁膜23中に注入されたホールを中和することが可能である。

【0028】

また図8(C)に示すnチャネルMOSトランジスタにおいては、チャネル領域の電子は、前記ゲート絶縁膜23のバンドギャップが小さいため、ゲート絶縁膜23に容易に侵入してしまう。また、ゲート絶縁膜23のバンドギャップは膜厚方向に一定であるため、侵入した電子のゲート電極24への排出が加速されるわけではない。

30

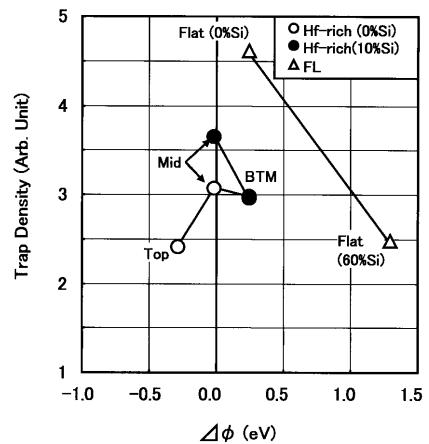

【0029】

図9は、このような様々なバンド構造のゲート絶縁膜について求めた、トラップ準位密度の見積もりを示す。ただし図9中、縦軸はトラップ準位密度を、横軸は、図10に定義するように、界面酸化膜22とゲート絶縁膜23の界面における伝導帯下端とチャネル領域21におけるフェルミレベルE<sub>f</sub>のエネルギー差を示す。が負の場合、ゲート絶縁膜23、特に界面酸化膜22と接している絶縁膜23aの伝導帯下端が、チャネル領域のフェルミレベルよりも高いエネルギー位置を有することを意味する。

40

【0030】

図9を参照するに、「Top」と記したデータ点は、図4(A)～(C)の「TOP構成」において、絶縁膜23aを、Siを60%の原子濃度(Si/(Hf+Si))と定義)で含むHfSiON膜とし、絶縁膜23bをHfO<sub>2</sub>膜(Si原子濃度=0%)とした場合を示し、一方、「Mid」と記した二点のうち、白丸で示したデータ点は、図5(A)～(C)の「MID構成」において、絶縁膜23a, 23cを、Siを60%の原子濃度で含むHfSiON膜とし、絶縁膜23bをHfO<sub>2</sub>膜(Si原子濃度=0%)とした場合を示す。また図9中、「Mid」と記した二点のうち、黒丸で示したデータ点は、図5(A)～(C)の「MID構成」において、絶縁膜23a, 23cを、Siを60%の原子濃度で含むHfSiON膜とし、絶縁膜23bをHfSiON膜(Si原子濃度=10%)とした場合を示す。

50

## 【0031】

さらに図9中、「BTM」と記したデータ点は、図6(A)～(C)の「BTM」構成において、絶縁膜23aをSi原子濃度が10%のHfSiON膜とし、絶縁膜23bを、Si原子濃度が60%のHfSiON膜とした場合を示し、「Flat(60%Si)」と記した点は、図7(A)～(C)の「Flat(60%Si)」構成に対応する。さらに図9中、「Flat(0%Si)」と記したデータ点は、図8(A)～(C)の「Flat(0%Si)」構成に対応する。

## 【0032】

図9よりわかるように、トラップ準位密度が最も低いのは、図4(A)～(C)の「TOP構成」であり、それに次ぐのが図7(A)～(C)の「Flat(60%Si)」構成であることがわかる。

## [第1の実施形態]

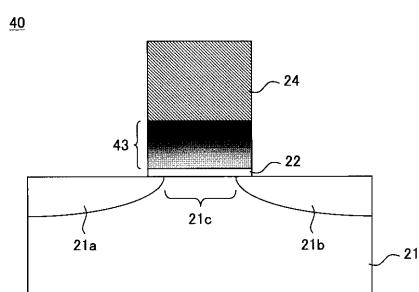

図11は、本発明の第1の実施形態による半導体装置20の構成を示す。前記半導体装置20は、pチャネルMOSトランジスタあるいはnチャネルMOSトランジスタを構成する。

## 【0033】

図11を参照するに、半導体装置20はシリコン基板21上に形成されており、前記シリコン基板21上にはチャネル領域21cに対応して、厚さが約0.4nmの界面酸化膜22が形成されており、前記界面酸化膜22上に、Siに富んだ組成のHfSiON膜よりなる第1のゲート絶縁膜23aが、0.7～2.5nm、例えば2nmの膜厚に形成され、さらに前記第1のゲート絶縁膜23a上に、HfO<sub>2</sub>膜あるいはHfに富んだ組成のHfSiON膜よりなる第2のゲート絶縁膜23bが、0.7～1.5nm、例えば1nmの膜厚に形成されている。前記第1および第2のゲート絶縁膜23a, 23bは、全体としてゲート絶縁膜23を構成し、前記ゲート絶縁膜23上には、Wなどよりなる金属ゲート電極24が、前記第2のゲート絶縁膜23bに接して形成されている。

## 【0034】

さらに、前記シリコン基板21中には、前記ゲート電極24直下のチャネル領域21cを画成するように、ソースおよびドレイン領域21a, 21bが形成されている。前記半導体装置20がnチャネルMOSトランジスタの場合には、前記ソースおよびドレイン領域21a, 21bはAsあるいはPによりn型にドープされ、一方、前記半導体装置20がpチャネルMOSトランジスタの場合には、前記ソースおよびドレイン領域21a, 21bはBによりp型にドープされる。

## 【0035】

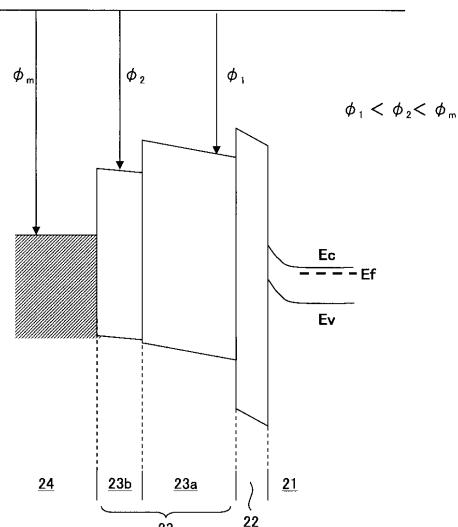

図12は、図11の半導体装置20がnチャネルMOSトランジスタである場合の、ゲート絶縁膜23周辺のバンド構造を示す。ただしEcは伝導帯を、Evは価電子帯を、Efはフェルミ準位を示す。

## 【0036】

図12を参照するに、前記第1の絶縁膜23aは、Siを例えば60%の原子濃度で含むHfSiON膜よりなり、一方、前記第2の絶縁膜23bは、HfO<sub>2</sub>膜あるいはSiを原子濃度で10%以下の濃度で含むHfSiON膜より構成する。

## 【0037】

前記第1および第2の絶縁膜23a, 23bをこのように形成した場合、前記第1の絶縁膜23aの電子親和力1、前記第2の絶縁膜23bの電子親和力2、前記ゲート電極24の電子親和力1(すなわち仕事関数)の間には、

$$1 < 2 < m$$

の関係が成立し、前記界面酸化膜22と第1の絶縁膜23aの間には、チャネル領域中の電子に対し、高い障壁が形成される。また、界面準位や絶縁膜23a, 23b中の欠陥などを伝って侵入した電子は、第2の絶縁膜23bの伝導帯上端が低い位置にあるため、容易にゲート電極24へと排出され、ゲート絶縁膜23中における電荷のトラップが最小限

10

20

30

40

50

に抑制される。

【0038】

図13は、図11の半導体装置20がpチャネルMOSトランジスタである場合の、ゲート絶縁膜23周辺のバンド構造を示す。図12同様にEcは伝導帯を、Evは価電子帯を、Efはフェルミ準位を示す。

【0039】

図13の構成においても、前記第1の絶縁膜23aは、Siを原子濃度で例えば60%含むHfSiON膜よりなり、一方、前記第2の絶縁膜23bは、HfO<sub>2</sub>膜あるいはSiを原子濃度で10%以下の濃度で含むHfSiON膜より構成する。

【0040】

そこで、前記第1および第2の絶縁膜23a, 23bをこのように形成した場合、前記第1の絶縁膜23aの電子親和力1, 前記第2の絶縁膜23bの電子親和力2, 前記ゲート電極24の電子親和力1(すなわち仕事関数)の間には、

$$1 < 2 < m$$

の関係が成立する。

【0041】

この場合、チャネル領域21cのホールに対し、前記第1の絶縁膜23aは大きなバンドギャップを有するため効果的なバリアを形成し、ホールのゲート絶縁膜23への侵入を抑制する。

【0042】

また、ホールが界面準位や前記絶縁膜23a, 23bの欠陥を介して侵入しても、前記第2の絶縁膜23bの電子親和力2が大きな値をとるため、前記ゲート電極24中の電子に対するゲート絶縁膜23の障壁高さが減少しており、ゲート電極24からゲート電極23への電子の注入が促進される。このようにして注入された電子は、前記ゲート絶縁膜23中に侵入したホールを中和し、これにより、前記ゲート絶縁膜23における電荷のトラップを抑制することが可能となる。

【0043】

なお、図12の半導体装置において、前記ゲート電極23としては、Wなど金属を使うことにより、フェルミレベルピニングの問題を軽減することが可能である。また、前記界面酸化膜22としては、例えば紫外光励起酸素ラジカルによりシリコン基板表面を酸化する際に膜厚が0.4nmで生じるセルフリミット効果を使って形成した酸化膜を使うのが好ましい。特許文献5を参照。

【0044】

図14中、「発明1」で示した点は、図11の構造について、ゲート絶縁膜23のリーク電流と酸化膜換算膜厚の関係を示す。ただし図14には、先に図1で示したデータも、比較のため示している。図1と同様に、実線は熱酸化膜についての基準データを示す。

【0045】

図14を参照するに、本発明による二層構造のゲート絶縁膜23のリーク電流値は、データ点「60%Si」で示したSi原子濃度が60%のHfSiON膜のリーク電流値の延長線上に位置しており、このことから、本発明のゲート絶縁膜23は、Siの原子濃度が60%のHfSiON膜とほぼ同等のリーク電流特性および酸化膜換算膜厚を示すことがわかる。

【0046】

図15中「発明1」で示した点、は、図11のゲート絶縁膜23の電荷トラップ密度の測定結果を示す。

【0047】

図15を参照するに、本発明のゲート絶縁膜23により、pチャネルMOSトランジスタの場合もnチャネルMOSトランジスタの場合も、電荷トラップ密度が従来のものに比べて改善されていることがわかる。

【0048】

10

20

30

40

50

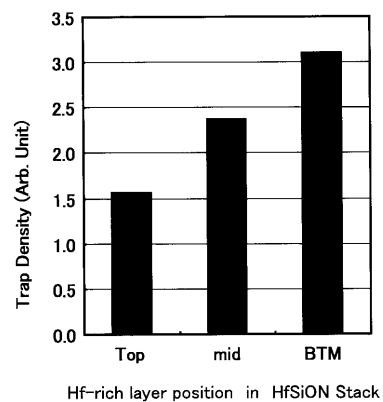

図16は、同じ $HfO_2$ 膜および $Si$ の原子濃度が60%の $HfSiON$ 膜を使って、前記図4(A)～(C)の「TOP構造」、図5(A)～(C)の「MID構造」、さらに図6(A)～(C)の「BTM構造」を形成した場合の、ゲート絶縁膜中のトラップ準位密度を示す。

## 【0049】

図16を参照するに、図4(A)～(C)の「TOP構造」において電荷トラップ密度が最も低く、図6(A)～(C)の「BTM構造」において電荷トラップ密度が最も大きいが、これは先に予測された通りである。

## 【0050】

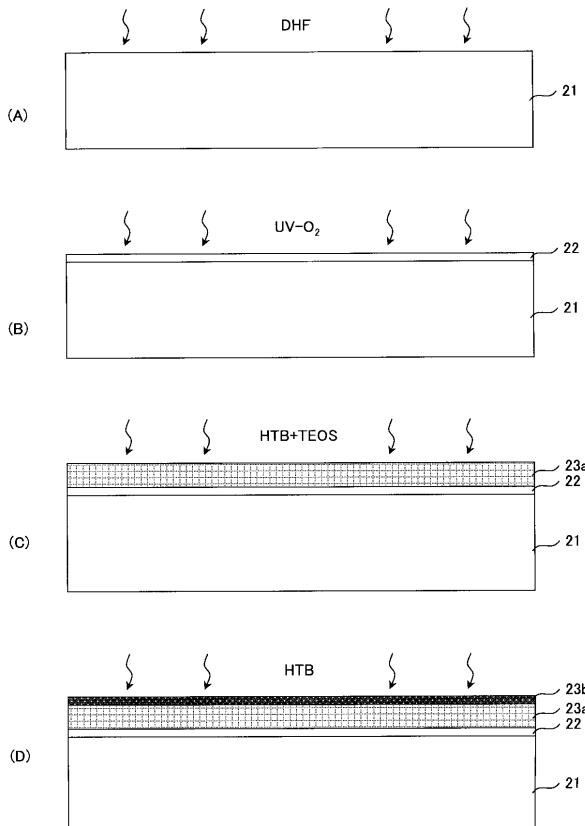

次に、図17(A)～(D)を参照しながら、図11の半導体装置の製造工程を簡単に説明する。 10

## 【0051】

図17(A)を参照するに、シリコン基板21の表面に希フッ酸(DHF)処理が施され、自然酸化膜が除去されると同時に、露出された新鮮なシリコン表面が水素終端される。

## 【0052】

次に図17(B)の工程において、このようにDHF処理されたシリコン基板21の表面に、典型的には400～500 nmの紫外光励起ラジカル酸化処理により、膜厚が約0.4 nmのシリコン酸化膜22が、前記界面酸化膜として形成され、さらに図17(C)の工程において、かかる界面酸化膜上に、ターシャリーブトキシハフニウム(HTB)およびテトラエトキシシラン(TEOS)を原料としたCVD法により、Siを原子濃度で例えば60%含んだ $HfSiO_4$ 膜23aが、典型的には480 nmの基板温度で、0.7～2.5 nm、例えば約2 nmの膜厚に形成される。 20

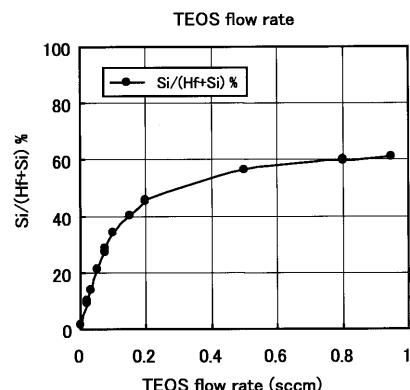

## 【0053】

図18は、図17(C)の工程においてArキャリアガスの流量を1500 sccm、HTBガスの流量を0.397 sccmに設定し、40 Paのプロセス圧下、TEOSガス流量を0～1 sccmの範囲で変化させた場合に、形成される $HfSiO_4$ 膜23a中に取り込まれるSiの原子濃度を示している。

## 【0054】

図18を参照するに、図17(C)の工程ではバンドギャップの大きい $HfSiON$ 膜を形成する必要があるため、前記TEOS流量が、0.5 sccm以上の値に設定される。 30

## 【0055】

さらに図17(D)の工程において、同じCVD装置内において、TEOSガスを例えば0.02 sccm、あるいはそれ以下の流量で供給し、Siの原子濃度が10%以下の $HfSiO_4$ 膜23bを、0.7～1.5 nm、例えば1 nmの厚さに形成する。前記 $HfSiO_4$ 膜23bは、Siを含まない $HfO_2$ 膜であってもよい。

## 【0056】

さらに図示はしないが、前記図17(D)の工程の後、前記CVD装置内に例えばリモートプラズマ源を使い、窒素ラジカルを導入することにより、前記 $HfSiO_4$ 膜23a, 23bを、 $HfSiON$ 膜に変換する。 40

## 【0057】

さらに、図示は省略するが、図17(D)の工程の後、前記 $HfSiON$ 膜23b上にWなどの金属膜を堆積し、これをパターニングして金属ゲート電極24を形成した後、前記金属ゲート電極24をマスクに、前記シリコン基板21中にn型あるいはp型の不純物元素を導入し、図11の半導体装置が得られる。

## [第2の実施形態]

図19は、本発明の第2の実施形態による半導体装置40の構成を示す。ただし図19中、先に説明した部分には同一の参照符号を付し、説明を省略する。 50

## 【0058】

図19を参照するに、本実施形態では前記図11の二層構造のゲート絶縁膜23の代わりに、組成勾配を有し、下面側においてSi濃度が高く、上面側に向かってSi濃度が徐々に減少するHfSiON膜43が使われる。図19の例では、前記HfSiON膜43は0.7~4nm、例えば3nmの膜厚を有し、界面酸化膜22に接する下面側ではSi原子濃度が60%、ゲート電極24に接する上面側では10~0%の組成を有する。

## 【0059】

本実施形態においても、半導体装置40はpチャネルMOSトランジスタあるいはnチャネルMOSトランジスタであるが、同一構成のゲート絶縁膜が、pチャネルMOSトランジスタでもnチャネルMOSトランジスタでも使われる。

10

## 【0060】

図20は、図19の半導体装置40におけるリーク電流Jgと酸化膜換算膜厚EOTの関係を示す。

## 【0061】

図20を参照するに、「発明2」として示すゲート絶縁膜43のリーク電流値は、同じく図20中、「60%Si」として示すSi原子濃度が60%のHfSiON膜のリーク電流値と、「発明1」で示す先の第1の実施形態のゲート絶縁膜23のリーク電流値の中間に位置しているのがわかる。なお、図20中には、図1の本発明の関連技術によるゲート絶縁膜のリーク電流値も併せて示してある。

## 【0062】

図21は、前記HfSiON膜43の電荷トラップ密度を、前記HfSiON膜43をゲート電極に使ってpチャネルMOSトランジスタを形成した場合およびnチャネルMOSトランジスタを形成した場合について示す。ただし図21中、前記HfSiON膜43についての結果を、「発明2」として、図11のHfSiON膜23についての結果8「発明1」)および図2の本発明の関連技術についての結果と併せて示している。

20

## 【0063】

図21を参照するに、本実施形態によるHfSiON膜を使うことにより、pチャネルMOSトランジスタであってもnチャネルMOSトランジスタであっても、電荷トラップ密度を、先の第1の実施形態の場合よりもさらに減少させることができるのがわかる。

## 【0064】

なお、以上の説明では、界面酸化膜22に接するHfSiON膜23aが、Siを原子濃度で60%の濃度で含み、ゲート電極23に接するHfSiON膜23b膜が、Siを原子濃度で10%以下の濃度で含む例を説明したが、本発明はこのような特定の組成に限定されることはなく、図12あるいは13のバンド構造を実現できるものであれば、他の組成を使うことも可能である。

30

## 【0065】

また前記ゲート絶縁膜23a, 23bあるいは43として、HfSiON膜の代わりにZrSiON膜や、HfAlN膜、La<sub>2</sub>O<sub>3</sub>膜、LaAlON膜、LaSiON膜、Y<sub>2</sub>O<sub>3</sub>膜、YAlON膜、YSiON膜、Ta<sub>2</sub>O<sub>5</sub>膜、SrO膜およびこれらの複合膜等、いわゆるhigh-K膜を使うことが可能である。

40

## 【0066】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

## 【図面の簡単な説明】

## 【0067】

【図1】本発明の関連技術によるHfSiON膜のリーク電流と酸化膜換算膜厚の関係を示す図である。

【図2】本発明の関連技術によるHfSiON膜の電荷トラップ密度を示す図である。

【図3】本発明の原理を説明する図である。

50

【図4】本発明の原理を説明する別の図である。

【図5】本発明の原理を説明する別の図である。

【図6】本発明の原理を説明する別の図である。

【図7】本発明の原理を説明する別の図である。

【図8】本発明の原理を説明する別の図である。

【図9】本発明の原理を説明する別の図である。

【図10】本発明の原理を説明する別の図である。

【図11】本発明の第1の実施形態による半導体装置の構成を示す図である。

【図12】図11の半導体装置がnチャネルMOSトランジスタである場合のバンド構造図である。

10

【図13】図11の半導体装置がpチャネルMOSトランジスタである場合のバンド構造図である。

【図14】図11の半導体装置で使われるゲート絶縁膜についての、リーク電流と酸化膜換算膜厚の関係を示す図である。

【図15】図11の半導体装置におけるゲート絶縁膜中への電荷トラップ密度を、本発明の関連技術の場合と比較して示す図である。

【図16】様々なゲート絶縁膜構造について、電荷トラップ密度を比較する図である。

【図17】図11の半導体装置の製造工程を示す図である。

【図18】図17のゲート絶縁膜成膜工程におけるTEOS原料ガスの流量と得られるHfSiON膜のSi濃度の関係を示す図である。

20

【図19】本発明の第2の実施形態による半導体装置の構成を示す図である。

【図20】図20の半導体装置で使われるゲート絶縁膜についての、リーク電流と酸化膜換算膜厚の関係を示す図である。

【図21】図11の半導体装置におけるゲート絶縁膜中への電荷トラップ密度を、本発明の関連技術の場合と比較して示す図である。

【符号の説明】

【0068】

21 シリコン基板

21a, 21b 拡散領域

21c チャネル領域

22 界面酸化膜

23, 23a, 23b ゲート絶縁膜

24 ゲート電極

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図13】

【図12】

【図14】

【図15】

【図16】

【図17】

【図18】

【図20】

【図19】

【図21】

---

フロントページの続き

F ターム(参考) 5F048 AA07 AC03 BA01 BB09 BB11 BB17 BB18

5F058 BA01 BC02 BC03 BC08 BC11 BC20 BD04 BD05 BD10 BD15

BD18 BF04 BF06 BF25 BF27 BF54 BF74 BF78 BH16 BJ01

5F140 AA05 AA06 AB01 BA01 BD01 BD02 BD04 BD05 BD11 BD12

BD15 BE07 BE08 BE10 BF01 BF07