(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 601 05 393 T2 2005.02.17

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 253 781 B1

(21) Deutsches Aktenzeichen: 601 05 393.1

(96) Europäisches Aktenzeichen: 01 310 898.0

(96) Europäischer Anmeldetag: 27.12.2001

(97) Erstveröffentlichung durch das EPA: 30.10.2002

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 08.09.2004

(47) Veröffentlichungstag im Patentblatt: 17.02.2005

(51) Int Cl.<sup>7</sup>: H04N 5/217

H04N 5/335

(30) Unionspriorität:

2001130148 26.04.2001 JP

(84) Benannte Vertragsstaaten:

DE, FR, GB

(73) Patentinhaber:

Fujitsu Ltd., Kawasaki, Kanagawa, JP

(72) Erfinder:

Udo, Shinya, Kawasaki-shi, Kanagawa 211-8588,

JP; Kokubun, Masatoshi, Kawasaki-shi,

Kanagawa 211-8588, JP; Tsuchiya, Chikara,

Kawasaki-shi, Kanagawa 211-8588, JP;

Yamamoto, Katsuyosi, Kawasaki-shi, Kanagawa

211-8588, JP

(74) Vertreter:

W. Seeger und Kollegen, 81369 München

(54) Bezeichnung: X-Y-Adressen-Festkörperbildaufnehmer

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung bezieht sich auf eine Halbleiterbildaufnahmeverrichtung, die von Halbleiterelementen gebildet wird, und insbesondere auf eine Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp, die durch einen CMOS-Prozess hergestellt wird.

**[0002]** In den letzten Jahren werden Halbleiterbildaufnahmeverrichtungen in verschiedenen Produkten wie z.B. Digitalbildkameras, Digitalvideokameras oder tragbaren Telefonen eingebaut und in großen Mengen verwendet. Die Halbleiterbildaufnahmeverrichtung wird grob unterteilt in eine CCD-Halbleiterbildaufnahmeverrichtung (Charge Coupled Device), die durch einen Ladungstransfer-Bildsensor gebildet wird, und eine Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp, in der ein Bildsensor durch z.B. CMOS-Transistoren (Complementary Metal Oxide Semiconductor) gebildet wird. Die Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp, die einen CMOS-Bildsensor nutzt (im folgenden einfach als CMOS-Bildsensor abgekürzt), kann durch die gleiche Technik wie eine Fertigungstechnik eines MOSFET hergestellt werden, sie wird durch eine einzige Leistungsquelle angesteuert, und die verbrauchte elektrische Leistung ist ebenfalls gering, und ferner können verschiedene Signalverarbeitungsschaltungen auf dem gleichen Chip montiert werden. Folglich wird der CMOS-Bildsensor als Ersatz für die CCD-Halbleiterbildaufnahmeverrichtung als vielversprechend betrachtet.

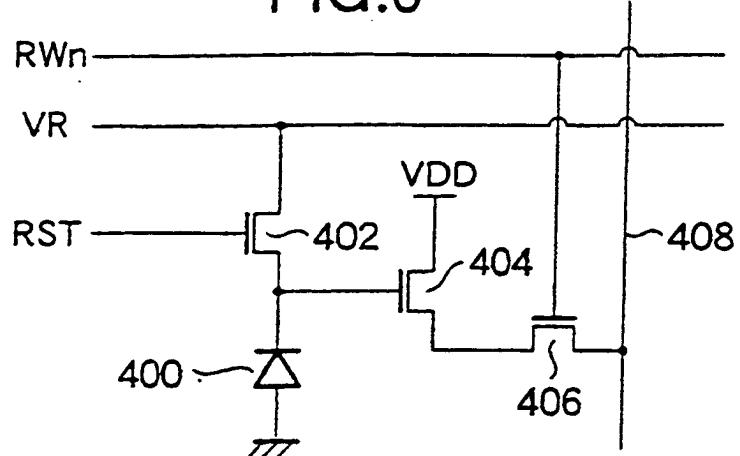

**[0003]** Eine früher vorgeschlagene Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp, die diesen CMOS-Bildsensor nutzt, wird mit Verweis auf **Fig. 6** beschrieben. **Fig. 6** zeigt ein Schaltungsbeispiel eines Pixel des früher vorgeschlagenen Bildsensors vom X-Y-Adressstyps. Der in **Fig. 6** gezeigte früher vorgeschlagene CMOS-Bildsensor hat z.B. eine APS-(aktive Pixelsensor)-Struktur, in der ein Source-Folgeverstärker **404** in jedem Pixel montiert ist. Eine Kathodenseite einer Photodiode **400** ist mit einer Gate-Elektrode des Source-Folge-verstärkers **404** und einem Rücksetz-Transistor **402** vom MOS-Typ verbunden. Daneben ist der Source-Folgeverstärker **404** über einen horizontalen Auswahltransistor **406** mit einer vertikalen Auswahlleitung **408** verbunden.

**[0004]** Die Operation dieses früher vorgeschlagenen CMOS-Bildsensors wird kurz beschrieben. Zunächst wird an eine Gate-Elektrode des Rücksetz-Transistors **402** zu einer vorbestimmten Zeitlage ein Rücksetzsignal RST angelegt, so dass der Rücksetz-Transistor **402** eingeschaltet wird. Dadurch wird die Photodiode **400** auf ein Rücksetzpotential VR geladen. Als nächstes beginnt mit dem Einfall von Licht, die Photodiode **400** sich zu entladen, und das Poten-

tial wird vom Rücksetzpotential VR abgesenkt. Ein einfallendes Photon während einer Integrationsperiode wird einer photoelektrischen Umwandlung unterworfen, um ein Paar aus einem Elektron und einem Loch zu erzeugen. Das Elektron wird in der Photodiode in einem schwebenden Zustand gespeichert, und das Loch wird von einem auf die Erdung vorgespannten Halbleitersubstrat absorbiert. Wenn eine elektrische Ladung eines Signals Qsig ist, ist eine Potentialänderung  $\Delta VPD$  der Photodiode **400** durch ein Signalelektron gegeben durch  $\Delta VPD = Qsig/Cs$ . Wenn ein horizontales Auswahlsignal RWn in eine Gate-Elektrode des horizontalen Auswahltransistors **406** eingespeist wird, nachdem eine vorbestimmte Zeit verstrichen ist, und der horizontale Auswahltransistor **406** eingeschaltet ist, wird eine Spannung des Source-Folgeverstärkers **404** über die vertikale Auswahlleitung **408** extrahiert.

**[0005]** In der früher vorgeschlagenen APS-Struktur, in der die Photodiode **400** mit Ladungsspeicherkapazität und der Source-Folgeverstärker **404** montiert sind, besteht jedoch ein Problem, dass ein Rauschen mit festem Muster (FPN) (engl. fixed pattern noise), bei dem ein Gleichspannungspegel einer Signalspannung durch Fluktuation einer Schwellenspannung VT oder dergleichen geändert wird, erzeugt und die Bildqualität verschlechtert wird. Um dies zu reduzieren, wird eine Schaltung für eine korrelierte Doppelabtastung (CDS) (engl. correlated double sampling) verwendet. Nachdem eine Signalspannung durch die Schaltung für eine korrelierte Doppelabtastung abgetastet ist, wird zunächst die Photodiode **400** auf das Rücksetzpotential VR zurückgesetzt. Als nächstes wird das Rücksetzpotential durch die Schaltung für eine korrelierte Doppelabtastung abgetastet, und eine Differenz zwischen der Signalspannung und der Rücksetzspannung wird erhalten. Dadurch wird der Einfluss der Fluktuation der Schwellenspannung VT kompensiert, und das FPN kann reduziert werden.

**[0006]** Da in diesem Verfahren die Rücksetzspannung nach einer Signalspeicherung, nicht die Rücksetzspannung vor der Signalspeicherung (Integration) abgetastet wird, um die Differenz zwischen der Rücksetzspannung und der Signalspannung zu erhalten, gibt es jedoch keine Korrelation zwischen einem kTC-Rauschen (thermischen Rauschen), das der Signalspannung überlagert ist, und einem kTC-Rauschen, das der abgetasteten Rücksetzspannung überlagert ist. Folglich bleibt ein Problem bestehen, dass das von der Photodiode **400** in einer Rücksetzperiode zufällig erzeugte kTC-Rauschen durch die CDS-Schaltung nicht entfernt werden kann und das S/N-Verhältnis verglichen mit der CCD-Halbleiterbildaufnahmeverrichtung verschlechtert wird.

**[0007]** Das kTC-Rauschen wird erzeugt, wenn der Rücksetz-Transistor **402** in einen Ein-Zustand ver-

setzt und die Photodiode **400** auf das Anfangspotential zurückgesetzt wird, und ist ein Zufallsrauschen, das ausgedrückt wird durch  $\text{vkTC} = (kT/C)/2$ , wobei  $k$  die Boltzmann-Konstante,  $T$  die absolute Temperatur und  $C$  die gesamte Kapazität ist, die in der Photodiode **400** gespeichert ist.

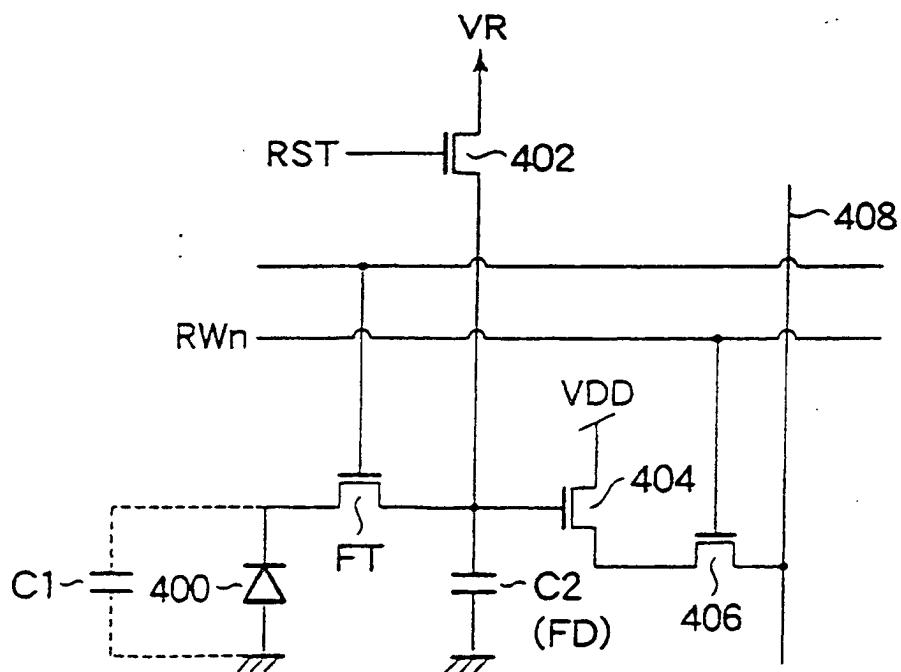

**[0008]** Als nächstes wird mit Verweis auf **Fig. 7** ein CMOS-Bildsensor beschrieben, der imstande ist, das kTC-Rauschen zu reduzieren. In **Fig. 7** ist zwischen einer ersten Kapazität  $C_1$  einer Photodiode **400** und einer zweiten Kapazität  $C_2$  eines Floating-Diffusion-(FD)-Bereichs ein Transfer-Gate **FT** zum Ausbilden einer Energiebarriere vorgesehen, und ein Source-Folgeverstärker **404** ist zwischen das Transfer-Gate **FT** und einen horizontalen Auswahltransistor **406** geschaltet, der von einem MOSFET gebildet wird. Der Rücksetz-Transistor **402** vom MOS-Typ zum Entfernen einer in der zweiten Kapazität  $C_2$  gespeicherten elektrischen Ladung ist mit der zweiten Kapazität  $C_2$  verbunden. Eine Drain-Elektrode des Source-Folgeverstärkers **404** ist mit einer Leistungsquelle  $VDD$  verbunden, und dessen Source-Elektrode ist mit dem horizontalen Auswahltransistor **406** verbunden. Eine Gate-Elektrode des Source-Folgeverstärkers **404** ist mit der zweiten Kapazität  $C_2$  verbunden. Ein Rücksetzpotential  $VR$  wird an eine Drain-Elektrode des Rücksetz-Transistors **402** angelegt. Eine Source-Elektrode des Rücksetz-Transistors **402** ist mit der zweiten Kapazität  $C_2$  verbunden, und ein Rücksetzsignal  $RST$  wird in dessen Gate-Elektrode eingespeist.

**[0009]** Wenn durch Einschalten des Transfer-Gates **FT** eine elektrische Ladung zur zweiten Kapazität  $C_2$  des FD-Bereichs übertragen wird, nachdem die elektrische Ladung in der ersten Kapazität  $C_1$  gespeichert ist, wird das Potential des Gates des Source-Folgeverstärkers **404** allmählich hoch. Wenn der horizontale Auswahltransistor **406** eingeschaltet wird, nachdem eine vorbestimmte Zeit verstrichen ist, wird die Source-Spannung des Source-Folgeverstärkers **404** über eine vertikale Auswahlleitung **408** abgegeben, und eine elektrische Ladungsmenge  $Q$ , die in der zweiten Kapazität  $C_2$  gespeichert ist, kann detektiert werden. Wenn der Rücksetztransistor **402** nur einmal eingeschaltet wird, bevor das Transfer-Gate **FT** eingeschaltet wird, kann die gesamte, in der zweiten Kapazität  $C_2$  gespeicherte elektrische Ladung entfernt werden, und eine Verschlechterung der Bildqualität aufgrund einer restlichen elektrischen Ladung kann unterdrückt werden.

**[0010]** Da die Signalspannung nach einem Zurücksetzen abgetastet werden kann, nachdem die Rücksetzspannung vor der Signalspeicherung abgetastet ist, weisen gemäß dieser Struktur die kTC-Rauschereignisse, die der Rücksetzspannung und der Signalspannung überlagert sind, eine hohe Korrelation auf. Wenn die Signalspannung abgetastet wird, nachdem

die Rücksetzspannung abgetastet ist, und die Differenz zwischen der Rücksetzspannung und der Signalspannung unter Verwendung der Schaltung für eine korrelierte Doppelabtastung erhalten wird, kann folglich das kTC-Rauschen der Signalspannung reduziert werden.

**[0011]** In der Struktur des in **Fig. 7** gezeigten, früher vorgeschlagenen CMOS-Bildsensors, wie er oben beschrieben wurde, gibt es jedoch, obwohl das FPN und das kTC-Rauschen reduziert werden können, ein Problem, dass die Elementstruktur kompliziert wird. Die Elementstruktur des in **Fig. 7** gezeigten Pixel hat ein Problem, dass verglichen mit der Elementstruktur des in **Fig. 6** gezeigten Pixel die Anzahl der Transistoren erhöht ist, der Pixelteil kompliziert wird und das Öffnungsverhältnis (Füllfaktor) des lichtempfangenden Teils verringert wird.

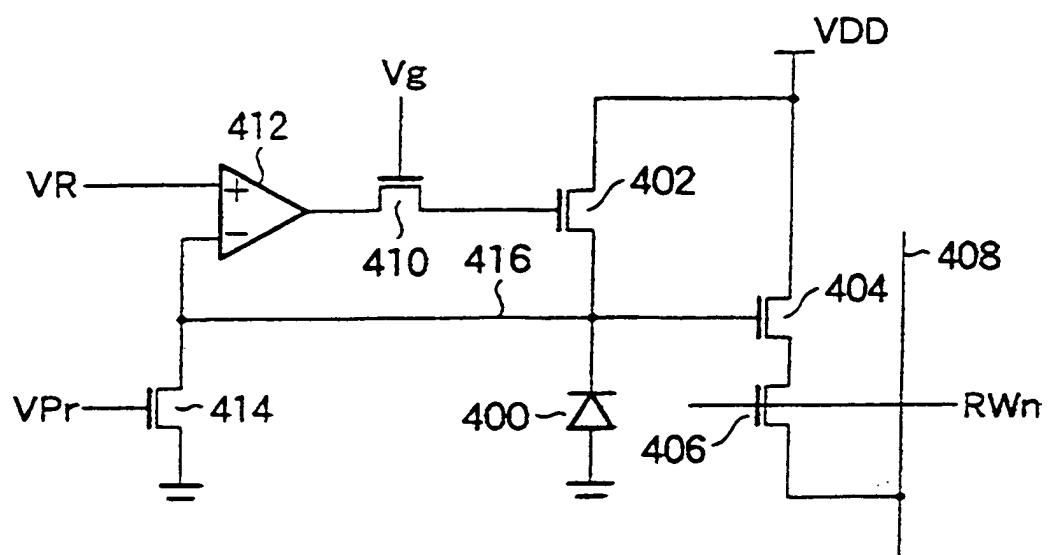

**[0012]** Ein anderes Beispiel eines CMOS-Bildsensors, der das kTC-Rauschen reduzieren kann, wird als nächstes mit Verweis auf **Fig. 8** beschrieben. Der in **Fig. 8** gezeigte CMOS-Bildsensor enthält zusätzlich zur in **Fig. 6** gezeigten Elementstruktur eine Steuerschaltung zum Steuern einer an eine Gate-Elektrode eines Rücksetz-Transistors **402** angelegten Rücksetzspannung, um das kTC-Rauschen zu reduzieren.

**[0013]** Ein Referenz-Rücksetzsignal  $VR$  wird in einen nicht invertierenden Eingangsanschluss eines Operationsverstärkers **412** der Steuerschaltung eingespeist. Ein Signal an einem Verbindungspunkt zwischen einem Kathodenanschluss der Photodiode **400** und dem Rücksetz-Transistor **402** wird über eine Verdrahtungsleitung **416** in einen invertierenden Eingangsanschluss des Operationsverstärkers **412** eingespeist. Die Verdrahtungsleitung **416** ist in einem Pixelbereich angeordnet. Daneben ist eine Konstantstromquelle **414** mit dem invertierenden Eingangsanschluss des Operationsverstärkers **412** verbunden. Ein Ausgangsanschluss des Operationsverstärkers **412** ist über einen Schalterstromkreis **410** mit der Gate-Elektrode des Rücksetz-Transistors **402** verbunden.

**[0014]** Eine Steuerschaltung mit einer solchen Struktur wird, wenn ein Signal  $Vg$  in eine Gate-Elektrode des Schalterstromkreises **410** zu einer vorbestimmten Rücksetzzeitlage eingespeist und der Schalterstromkreis **410** eingeschaltet wird, eine Gate-Spannung des Rücksetz-Transistors **402** so gesteuert, dass ein Potential an der Kathodenseite der Photodiode **400** immer die Rücksetzspannung  $VR$  wird. Indem man so verfährt, kann man die kTC-Rauschereignisse, die der Signalspannung bzw. dem nachfolgenden Rücksetzsignal nach einer Signalspeicherung überlagert sind, einen nahezu konstanten Pegel annehmen lassen. Wenn das Rücksetzsignal nach der Signalspeicherung abgetastet wird und

eine Differenz zwischen der abgetasteten Spannung und der Signalspannung durch eine CDS-Schaltung erhalten wird, kann somit das kTC-Rauschen reduziert werden. Da es notwendig wird, die Verdrahtungsleitung **416** im Pixelbereich anzutragen, ergibt sich jedoch in dieser Struktur ein Problem, dass ein Öffnungsverhältnis nicht weit ausgebildet wird.

**[0015]** Wie oben beschrieben wurde, hat der in **Fig. 6** gezeigte CMOS-Bildsensor das Problem, dass das kTC-Rauschen nicht reduziert werden kann. Auf der anderen Seite weisen die in **Fig. 7** und **8** dargestellten CMOS-Bildsensoren das Problem auf, dass bei einem Austausch zur Reduzierung des kTC-Rauschens der Elementumfang groß wird und kein weites Öffnungsverhältnis erhalten werden kann.

**[0016]** Bildsensoren mit einer Schaltung zur Reduzierung von kTC-Rauschen und einer Rücksetzoperation ähnlich den oben beschriebenen Schaltungen sind aus z.B. WO-A-99 53 683 oder EP-A-0 796 000 bekannt.

**[0017]** Es ist wünschenswert, eine Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp zu schaffen, die einen kleinen Elementumfang und ein weites Öffnungsverhältnis aufweist und das kTC-Rauschen reduzieren kann.

**[0018]** Dies wird erreicht durch einen Bildsensor gemäß Anspruch 1. Die abhängigen Ansprüche beziehen sich auf dessen Ausführungsformen.

**[0019]** Gemäß einer Ausführungsform der vorliegenden Erfindung wird eine Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp geschaffen, die gekennzeichnet ist durch einen Pixelbereich, der einen photoelektrischen Transducer zum Durchführen einer photoelektrischen Umwandlung von einfallendem Licht, einen Rücksetz-Transistor zum Zurücksetzen des photoelektrischen Transducers, einen Verstärkungstransistor zum Umwandeln einer im photoelektrischen Transducer gespeicherten elektrischen Ladung in eine Spannung und einen horizontalen Auswahltransistor umfasst, um die Spannung als Bilddaten an eine vertikale Auswahlleitung auf der Basis eines horizontalen Auswahlsignals abzugeben, das an eine horizontale Leitung abgegeben wird, und eine Schaltung zur Reduzierung von kTC-Rauschen, um ein zur Zeit des Zurücksetzens erzeugtes kTC-Rauschen zu reduzieren.

**[0020]** Nun wird beispielhaft auf die beiliegenden Zeichnungen verwiesen, in denen:

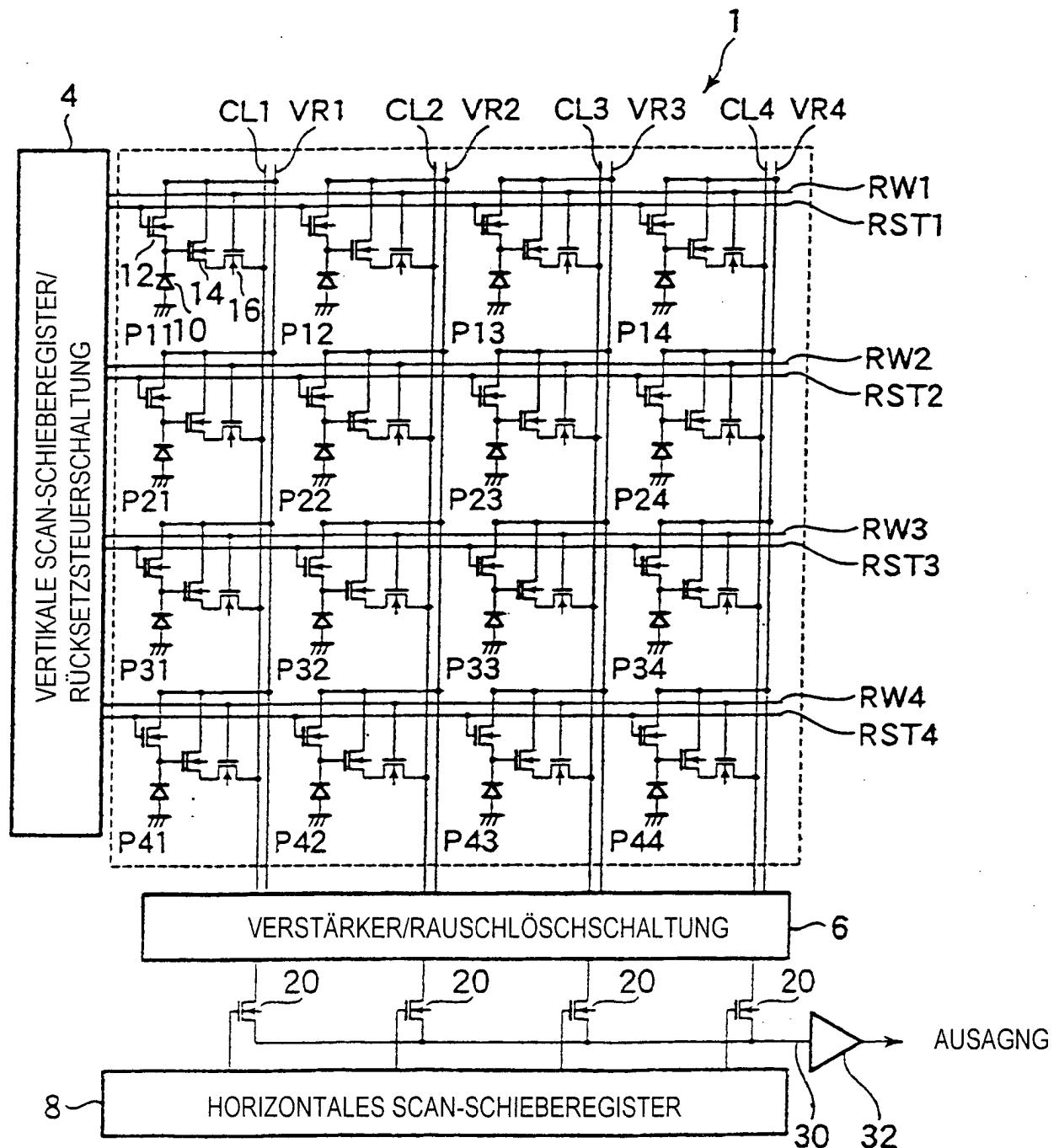

**[0021]** **Fig. 1** eine Ansicht ist, die ein Schaltungsbeispiel von  $4 \times 4$  Pixel eines CMOS-Bildsensors **1** gemäß einer Ausführungsform der vorliegenden Erfindung zeigt;

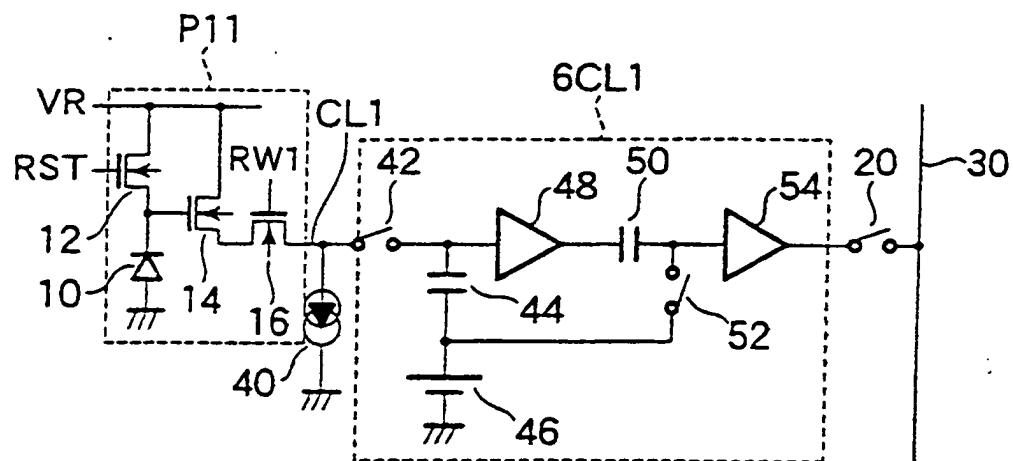

**[0022]** **Fig. 2** eine Ansicht ist, die ein Schaltungsbeispiel einer Abtast- und Halteschaltung und einer Schaltung für eine korrelierte Doppelabtastung des CMOS-Bildsensors **1** gemäß der Ausführungsform der vorliegenden Erfindung zeigt;

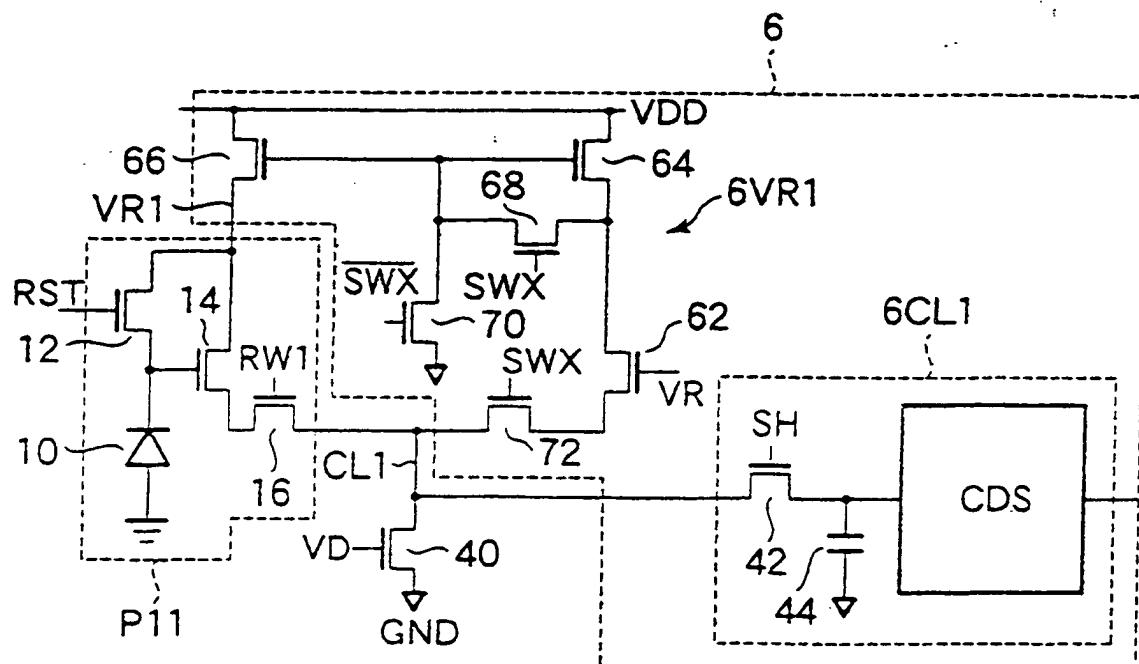

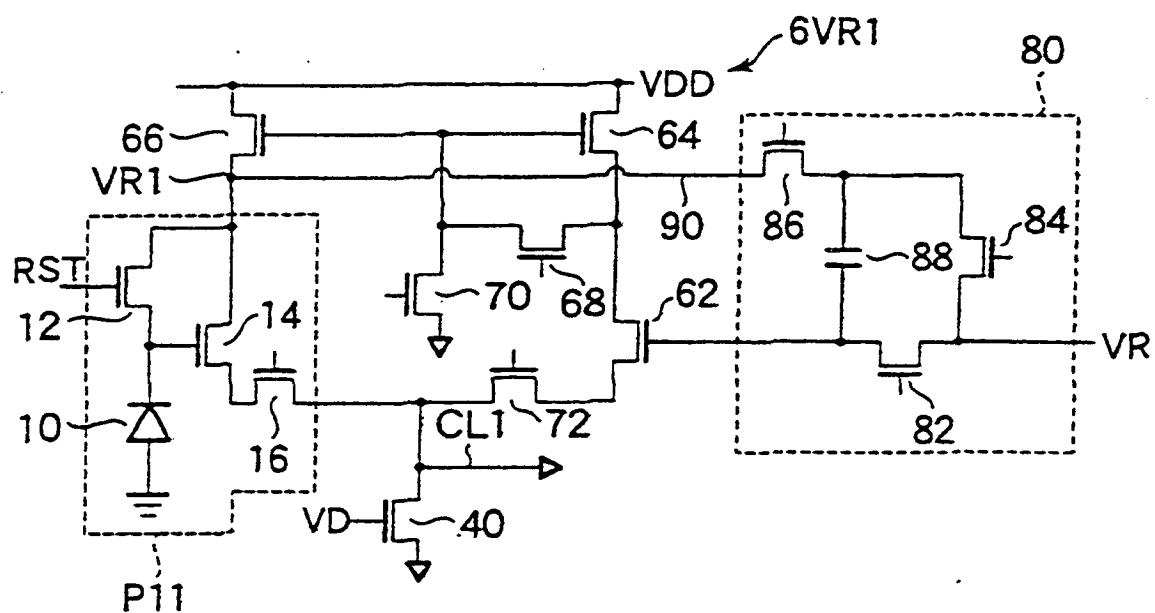

**[0023]** **Fig. 3** eine Ansicht ist, die ein Schaltungsbeispiel einer Schaltung zur Reduzierung von kTC-Rauschen des CMOS-Bildsensors **1** gemäß der Ausführungsform der vorliegenden Erfindung zeigt;

**[0024]** **Fig. 4** eine Ansicht ist, die ein Schaltungsbeispiel einer Schaltung zur Korrektur einer Offset-Spannung des CMOS-Bildsensors **1** gemäß der Ausführungsform der vorliegenden Erfindung ist;

**[0025]** **Fig. 5** eine Ansicht ist, die einen Effekt des CMOS-Bildsensors gemäß der Ausführungsform der vorliegenden Erfindung zeigt;

**[0026]** **Fig. 6** eine Ansicht ist, die eine früher vorgeschlagene Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp zeigt, die einen CMOS-Bildsensor nutzt;

**[0027]** **Fig. 7** eine Ansicht ist, die ein anderes Beispiel einer früher vorgeschlagenen Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp zeigt, die einen CMOS-Bildsensor nutzt; und

**[0028]** **Fig. 8** eine Ansicht ist, die noch ein weiteres Beispiel einer früher vorgeschlagenen Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp zeigt, die einen CMOS-Bildsensor nutzt.

**[0029]** Mit Verweis auf **Fig. 1** bis **5** wird eine Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp gemäß einer Ausführungsform der vorliegenden Erfindung beschrieben. Zunächst wird mit Verweis auf **Fig. 1** eine Grobstruktur eines CMOS-Bildsensors als die Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp gemäß der Ausführungsform beschrieben. **Fig. 1** zeigt ein Schaltungsbeispiel von  $4 \times 4$  Pixel eines CMOS-Bildsensors **1**, der ein Pixel-Array mit  $m$  Reihen und  $n$  Spalten enthält. Mehrere Pixelbereiche P11 bis P44 sind in einer Matrixform angeordnet, und mehrere vertikale Auswahlleitungen CL1 bis CL4 und mehrere horizontale Auswahlleitungen RW1 bis RW4 sind vertikal und horizontal angeordnet. Eine Photodiode **10** als ein photoelektrischer Transducer ist in jedem der Pixelbereiche P11 bis P44 ausgebildet. Als der photoelektrische Transducer kann anstelle der Photodiode **10** z.B. ein Photo-Gate verwendet werden.

**[0030]** Der CMOS-Bildsensor **1** hat eine APS-Struktur, in der ein Source-Folgeverstärker **14**, der durch z.B. einen MOSFET (in dieser Ausführungsform ist ein n-ch(n-Kanal) MOSFET beispielhaft veranschaulicht) gebildet wird, ein horizontaler Auswahltransistor

**16** und dergleichen in jedem der Pixelbereiche P11 bis P44 angeordnet sind.

**[0031]** Im folgenden wird eine Reihennummer m gesetzt, wird eine Spaltennummer n gesetzt, und eine Schaltungsstruktur eines Pixelbereichs Pmn ist beschrieben. Eine Kathodenseite der Photodiode **10** im Pixelbereich Pmn wird mit einer Source-Elektrode einer Rücksetz-Transistors **12** eines z.B. n-ch-MOSFET und einer Gate-Elektrode des Source-Folgeverstärkers **14** verbunden.

**[0032]** Eine Drain-Elektrode des Rücksetz-Transistors **12** und eine Drain-Elektrode des Source-Folgeverstärkers **14** sind mit einer Versorgungsleitung VRn für eine Rücksetzspannung verbunden, an die eine Rücksetzspannung VR angelegt wird. Eine Gate-Elektrode des Rücksetz-Transistors **12** ist mit einer Leitung RSTm für ein Rücksetzsignal verbunden. Eine Source-Elektrode des Source-Folgeverstärkers **14** ist mit einer Drain-Elektrode des horizontalen Auswahltransistors **16** eines z.B. n-ch-MOSFET verbunden. Eine Gate-Elektrode des horizontalen Auswahltransistors **16** ist mit der horizontalen Auswahlleitung RWm verbunden, an die ein horizontales Auswahlsignal RW geliefert wird. Eine Source-Elektrode des horizontalen Auswahltransistors **16** ist mit der vertikalen Auswahlleitung CLn verbunden.

**[0033]** Die horizontale Auswahlleitung RWm ist mit einer vertikalen Scan-Schieberegister/Rücksetzsteuerschaltung **4** verbunden. Das horizontale Auswahlsignal RW wird zu einer vorbestimmten Zeitlage durch ein nicht dargestelltes Schieberegister, das in der vertikalen Scan-Schieberegister/Rücksetzsteuerschaltung **4** vorgesehen ist, sukzessiv an die horizontale Auswahlleitung RWm abgegeben. Die Leitung RSTm für ein Rücksetzsignal ist ebenfalls mit der vertikalen Scan-Schieberegister/Rücksetzsteuerschaltung **4** verbunden, und das Rücksetzsignal RST wird zu einer vorbestimmten Zeitlage für jede horizontale Auswahlleitung RWm an den Rücksetz-Transistor **12** des Pixelbereichs Pmn angelegt.

**[0034]** Die Versorgungsleitung VRn für die Rücksetzspannung ist nahezu parallel zur vertikalen Auswahlleitung CLn angeordnet und ist zusammen mit der vertikalen Auswahlleitung CLn mit einer Verstärker/Rauschlöschschaltung **6** verbunden.

**[0035]** Die vertikale Auswahlleitung CLn ist mit einer gemeinsamen Signalaustrittsleitung **30** durch eine CDS-Schaltung **6CLn**, die in der Verstärker/Rauschlöschschaltung **6** angeordnet ist, und einem Spaltenauswahltransistor **20** verbunden, der durch z.B. einen n-ch-MOSFET gebildet wird. Eine Struktur der CDS-Schaltung **6CLn** in der Verstärker/Rauschlöschschaltung **6** wird später mit Verweis auf **Fig. 2** beschrieben.

**[0036]** Die Versorgungsleitung VRn für die Rücksetzspannung ist mit einer Schaltung **6VRn** zur Reduzierung von kCT-Rauschen verbunden, dessen Hauptschaltungsteil in der Verstärker/Rauschlöschschaltung **6** vorgesehen ist. Eine Struktur der Schaltung **6VRn** zur Reduzierung von kCT-Rauschen wird später mit Verweis auf **Fig. 3** beschrieben.

**[0037]** Ein Spaltenauswahlsignal wird sukzessiv in Gate-Elektroden der mehreren Spaltenauswahltransistoren **20** von einem horizontalen Scan-Schieberegister **8** zu einer vorbestimmten Zeitlage eingespeist, und Bilddaten, in denen ein Rauschen mit festem Muster und ein kTC-Rauschen durch die Verstärker/Rauschlöschschaltung **6** entfernt sind, werden sukzessiv an die gemeinsame Signalaustrittsleitung **30** abgegeben und über einen Verstärker **32** zu einem externen System übertragen.

**[0038]** Als nächstes wird kurz die Operation des CMOS-Bildsensors **1** beschrieben. Wenn der Rücksetz-Transistor **12** durch das Rücksetzsignal RST zu der vorbestimmten Zeitlage eingeschaltet wird, wird zunächst die Photodiode auf das Rücksetzpotential VR geladen. Mit dem Einfall von Licht beginnt als nächstes die Photodiode **10** sich zu entladen, und das Potential wird vom Rücksetzpotential VR abgesenkt. Wenn das horizontale Auswahlsignal RW an die horizontale Auswahlleitung RWm abgegeben wird, nachdem eine vorbestimmte Zeit verstrichen ist, wird das horizontale Auswahlsignal RW in die Gate-Elektrode des horizontalen Auswahltransistors **16** eingespeist, der mit der horizontalen Auswahlleitung RWm verbunden ist, und der horizontale Auswahltransistor **16** wird eingeschaltet. Dadurch wird die Ausgangsspannung von dem Source-Folgeverstärker **14** als die Bilddaten des Pixelbereichs Pmn an die vertikale Auswahlleitung CLn abgegeben.

**[0039]** Als nächstes wird die Struktur der Verstärker/Rauschlöschschaltung **6** beschrieben. Die Verstärker/Rauschlöschschaltung **6** enthält, wie in **Fig. 2** dargestellt ist, eine mit der vertikalen Auswahlleitung CL1 verbundene Abtast- und Halteschaltung und eine Schaltung für eine korrelierte Doppelabtastung. In **Fig. 2** zeigt ein Block, der durch eine gestrichelte Linie auf der linken Seite der Zeichnung angegeben ist, der Pixelbereich P11 auf der oberen linken Seite von **Fig. 1** als ein Beispiel der mehreren Pixel, die mit der vertikalen Auswahlleitung CL1 verbunden sind. Ein durch eine gestrichelte Linie auf der rechten Seite der Zeichnung angegebener Block zeigt die Abtast- und Halteschaltung und die Schaltung für eine korrelierte Doppelabtastung.

**[0040]** Die Abtast- und Halteschaltung ist mit einem Abtast-Halteschalter **42** versehen, um die Einspeisung eines an die vertikale Auswahlleitung CL1 abgegebenen Signals zu steuern. Eine Konstantstromquelle **40** ist mit einem Verbindungspunkt zwischen

einer Eingangsseite des Abtast-Halteschalters **42** und der vertikalen Auswahlleitung CL1 verbunden. Eine Elektrodenseite oder eine Seite mit einer Elektrode (im folgenden bezüglich zweier Elektroden, die eine Kapazität bilden, und zweier Elektroden eines Transistors mit Ausnahme einer Gate-Elektrode, falls notwendig, wobei eine von ihnen als eine Elektrode bezeichnet wird und die andere als die andere Elektrode bezeichnet wird) einer Abtast-Haltekapazität **44** zum Halten des an die vertikale Auswahlleitung CL1 abgegebenen Signals ist mit einer Ausgangsseite des Abtast-Halteschalters **42** verbunden. Eine Referenzspannungsquelle **46** ist mit der Seite mit der anderen Elektrode der Abtast-Haltekapazität **44** verbunden.

**[0041]** Ein Eingangsanschluss eines Verstärkers **48**, der die Schaltung für eine korrelierte Doppelabtastung bildet, ist mit einem Verbindungspunkt zwischen dem Abtast-Halteschalter **42** und der Seite mit einer Elektrode der Abtast-Haltekapazität **44** verbunden. Ein Ausgangsanschluss des Verstärkers **48** ist mit der Seite mit einer Elektrode einer CDS-Kapazität **50** der Schaltung für eine korrelierte Doppelabtastung verbunden, und die Seite mit der anderer, Elektrode der CDS-Kapazität **50** ist mit einem Eingangsanschluss eines Verstärkers **54** verbunden.

**[0042]** Die Seite mit der anderen Elektrode der CDS-Kapazität **50** ist durch einen Klemmschalter **52** mit der Seite mit der anderen Elektrode der Abtast-Haltekapazität **44** verbunden. Durch Schalten des Klemmschalters **52** kann die Seite mit der anderen Elektrode der CDS-Kapazität **50** von der Referenzspannung der Referenzspannungsquelle **46** abgetrennt oder auf die Referenzspannung fixiert werden. Ein Ausgangsanschluss des Verstärkers **54** ist durch den Spaltenauswahltransistor **20** mit der gemeinsamen Signalausgangsleitung **30** verbunden.

**[0043]** Als nächstes wird mit Verweis auf **Fig. 2** die Operation der Abtast- und Halteschaltung und der Schaltung für eine korrelierte Doppelabtastung beschrieben. Zunächst wird kurz ein Fluss eines vom Pixelbereich P11 abgegebenen Signals beschrieben. Wenn das horizontale Auswahlsignal RW1 in die Gate-Elektrode des horizontalen Auswahltransistors **16** eingespeist wird, wird eine Spannungsvariation des Source-Folgeverstärkers **14** entsprechend der Menge an elektrischer Ladung, die in der Photodiode **10** des Pixelbereichs **11** gespeichert ist, als eine Signalspannung VS, die die Bilddaten enthält, an die vertikale Auswahlleitung CL1 abgegeben. Als nächstes wird das Rücksetzsignal RST in die Gate-Elektrode des Rücksetz-Transistors **12** eingespeist, während der horizontale Auswahltransistor **16** den Ein-Zustand hält, so dass der Rücksetztransistor **12** in einen Ein-Zustand versetzt wird, um die Photodiode **10** auf das Rücksetzpotential zurückzusetzen, und die Rücksetzspannung VR wird an die vertikale

Auswahlleitung CL1 abgegeben. Die obige Operation wird in einer horizontalen Austastperiode ausgeführt.

**[0044]** Im obigen Fluss des Signals werden z.B. zu dem Zeitpunkt, zu dem das horizontale Auswahlsignal RW1 eingespeist und der horizontale Auswahltransistor **16** eingeschaltet wird, der Abtast-Halteschalter **42** und der Klemmschalter **52** in den Ein-Zustand versetzt. Dadurch wird die Signalspannung VS an den Eingangsanschluss der Abtast- und Halteschaltung angelegt. Da der Klemmschalter **52** im Ein-Zustand ist, lädt die Signalspannung VS die Abtast-Haltekapazität **44** der Abtast- und Halteschaltung und lädt auch die CDS-Kapazität **50**.

**[0045]** Nachdem der Klemmschalter **52** ausgeschaltet ist, wird als nächstes das Rücksetzsignal RST eingespeist, um den Rücksetz-Transistor **12** in den Ein-Zustand zu versetzen. Dadurch wird die Photodiode **10** auf das Rücksetzpotential VR zurückgesetzt; und die Rücksetzspannung VR wird an die vertikale Auswahlleitung CL1 abgegeben. Die Rücksetzspannung VR wird in den Eingangsanschluss der Abtast- und Halteschaltung eingespeist und durch die Abtast-Haltekapazität **44** gehalten.

**[0046]** Als Folge wird ein Differenzsignal (VS-VR), das einer Differenz zwischen der Signalspannung VS und der Rücksetzspannung VR entspricht, an der Ausgangsseite der CDS-Kapazität **50** erzeugt. Dieses Signal wird von der CDS-Kapazität **50** gehalten. Indem man so verfährt, ist es möglich, die analogen Bilddaten zu erhalten, in denen die sowohl der Signalspannung VS als auch der Rücksetzspannung VR überlagerten Komponenten des Rauschens mit festem Muster entfernt sind. Die analogen Bilddaten werden vom Ausgangsanschluss des Verstärkers **54** über den Spaltenauswahltransistor **20** an die gemeinsame Ausgangsleistung **30** abgegeben.

**[0047]** In der Verstärker/Rauschlöschschaltung **6** sind für die vertikale Auswahlleitung CLn die Abtast- und Halteschaltung und die Schaltung für eine korrelierte Doppelabtastung (im folgenden wird eine Kombination beider Schaltungen eine CDS-Schaltung genannt) vorgesehen.

**[0048]** In der Verstärker/Rauschlöschschaltung **6** der Ausführungsform ist ferner für jede CDS-Schaltung **6CLn** die Schaltung zur Reduzierung von kTC-Rauschen vorgesehen, um im Zusammenwirken mit der CDS-Schaltung **6CLn** das kTC-Rauschen zu reduzieren.

**[0049]** Im folgenden wird mit Verweis auf **Fig. 3** die Schaltung **6VRn** zur Reduzierung von kTC-Rauschen der Ausführungsform beschrieben. Die Schaltung **6VRn** zur Reduzierung von kTC-Rauschen ist dadurch gekennzeichnet, dass ein Hauptteil des Schaltungsteils in der Verstärker/Rauschlöschschal-

tung **6** ausgebildet ist und ein Teil der Schaltungsstruktur ein Element im Pixelbereich Pmn nutzt. In **Fig. 3** zeigt ein Block, der durch eine gestrichelte Linie an der linken Seite in der Zeichnung angegeben ist, als ein Beispiel den mit der vertikalen Auswahlleitung CL1 verbundenen Pixelbereich P11. Ein Block, der durch eine gestrichelte Linie an der rechten Seite der Zeichnung angegeben ist, zeigt die CDS-Schaltung **6CL1** und einen Hauptteil der Schaltung **6VR1** zur Reduzierung von kTC-Rauschen in der Verstärker/Rauschlöschschaltung **6**. Übrigens ist die Schaltung für eine korrelierte Doppelabtastung von **Fig. 3** nicht ausführlich dargestellt, sondern ist als ein Schaltungsblock dargestellt.

**[0050]** In **Fig. 3** ist in der Verstärker/Rauschlöschschaltung **6** ein Schalttransistor **72** mit nahezu der gleichen Charakteristik wie der im Pixelbereich P11 gebildete horizontale Auswahltransistor **16** vorgesehen, und dessen Source-Elektrode ist mit der vertikalen Auswahlleitung CL1 verbunden. Ein Schaltsignal SWX wird in einer Gate-Elektrode des Schalttransistors **72** eingespeist. Das Schaltsignal SWX wird synchron mit dem Rücksetzsignal RST abgegeben.

**[0051]** Eine Drain-Elektrode des Schalttransistors **72** ist mit einer Source-Elektrode eines ersten differentiellen Transistors **62** mit nahezu der gleichen Charakteristik wie der Source-Folgeverstärker **14** verbunden. Eine Drain-Elektrode des ersten differentiellen Transistors **62** ist mit der Seite mit einer Elektrode eines Transistors **64** z.B. eines MOS-Typs verbunden, und eine Spannung VDD wird an die Seite mit der anderen Elektrode des Transistors **64** angelegt. Eine Rücksetzspannung VR wird in eine Gate-Elektrode des ersten differentiellen Transistors **63** eingespeist.

**[0052]** Auf der anderen Seite sind Drain-Elektroden des Rücksetz-Transistors **12** und des Source-Folgeverstärkers **14** im Pixelbereich P11 durch eine Versorgungsleitung VR1 für die Rücksetzspannung, an die die Rücksetzspannung VR angelegt wird, mit einer Seite mit einer Elektrode eines Transistors **66** z.B. eines MOS-Typs verbunden. Die Spannung VDD wird an die Seite mit der anderen Elektrode des Transistors **66** angelegt. Die Versorgungsleitung VR1 für die Rücksetzspannung ist entlang der vertikalen Auswahlleitung CL1 außerhalb der mehreren Pixelbereiche P11, P21, P31... ausgebildet und liefert die Rücksetzspannung VR an die mehreren Rücksetztransistoren, die jeweils in den Pixelbereichen P11, P21, P31,... ausgebildet sind.

**[0053]** Eine Gate-Elektrode des Transistors **66** und eine Gate-Elektrode des Transistors **64** sind miteinander verbunden. Ein Schalttransistor **68** ist auf solch eine Weise ausgebildet, dass seine Seite mit einer Elektrode mit einem Verbindungspunkt zwischen dem ersten differentiellen Transistor **72** und dem

Transistor **64** verbunden ist und die Seite mit der anderen Elektrode mit dem Gate-Elektroden des Transistors **64** und des Transistors **66** verbunden ist. Ein Schaltsignal SWX wird in eine Gate-Elektrode des Schalttransistors **68** eingespeist. Daneben ist ein Schalttransistor **70** auf solch eine Weise ausgebildet, dass seine Seite mit einer Elektrode mit den Gate-Elektroden des Transistors **64** und des Transistors **66** verbunden ist und die Seite mit der anderen Elektrode geerdet ist. Ein Schaltsignal /SWX mit einer umgekehrten Polarität zum Schaltsignal SWX wird in eine Gate-Elektrode des Schalttransistors **70** eingespeist.

**[0054]** Der horizontale Auswahltransistor **16** des Pixelbereichs P11 und die Schalttransistoren **68** und **72** in der Verstärker/Rauschlöschschaltung **6** werden hier eingeschaltet, und der Schalttransistor **70** wird ausgeschaltet, und wenn der Source-Folgeverstärker **14** des Pixelbereichs P11 als ein zweiter differentieller Transistor betrachtet wird, der das Differenzpaar zum ersten differentiellen Transistor **62** bildet, wird die obige Struktur von **Fig. 3** ein Differenzverstärker, der mit einer Stromspiegelschaltung anstelle eines zusätzlichen Widerstands versehen ist. Die Stromspiegelschaltung wird gebildet durch den Transistor **64**, in welchem die Gate-Elektrode direkt mit Seite mit einer Elektrode verbunden ist, und den Transistor **66** mit der Seite mit der anderen Elektrode, an die die Spannung VDD zusätzlich zur Seite mit der anderen Elektrode des Transistors **64** angelegt wird, und der Gate-Elektrode, die mit der Gate-Elektrode des Transistors **64** wechselseitig verbunden ist.

**[0055]** Die mit Verweis auf **Fig. 3** beschriebene Schaltung ist die Schaltungsstruktur der Schaltung **6VR1** zur Reduzierung von kTC-Rauschen der Ausführungsform, und obwohl nicht dargestellt hat eine anderen Schaltung **6VRn** zur Reduzierung von kTC-Rauschen auch eine ähnliche Struktur. In der Schaltung **6VRn** zur Reduzierung von kTC-Rauschen ist gleichfalls der Großteil der Schaltungsstruktur in der Verstärker/Rauschlöschschaltung **6** ausgebildet, und ein Teil der Schaltungsstruktur nutzt das Element im Pixelbereich Pmn.

**[0056]** Als nächstes wird die Operation zum Reduzieren des kTC-Rauschens unter Verwendung der Schaltung **6VR1** zur Reduzierung von kTC-Rauschen beschrieben, die in **Fig. 3** als ein Beispiel dargestellt ist. Bis zur Zeit unmittelbar vor dem Ende der Rücksetzperiode sind zunächst der horizontale Auswahltransistor **16** und die Schalttransistoren **68** und **72** im Ein-Zustand, und der Schalttransistor **70** ist im Aus-Zustand. Dementsprechend ist der Hauptteil der Schaltung **6VR1** zur Reduzierung von kTC-Rauschen mit dem Element im Bildbereich P11 elektrisch verbunden, und die Schaltung **6VR1** zur Reduzierung von kTC-Rauschen dient als Differenzverstärker und ist in dem Zustand, in welchem die Operation zur

Reduzierung von kTC-Rauschen ausgeführt wird.

**[0057]** Wenn das Rücksetzsignal RST in einen inaktiven Pegel fällt, werden der horizontale Transistor **16** und die Schalttransistoren **68** und **72** in den Aus-Zustand versetzt, und der Schalttransistor **70** wird in den Ein-Zustand versetzt. Dadurch wird der Hauptteil der Schaltung **6VR1** zur Reduzierung von kTC-Rauschen vom Element im Bildbereich P11 elektrisch getrennt, und die Schaltung **6VR1** zur Reduzierung von kTC-Rauschen dient nicht als der Differenzverstärker und wird in den Zustand versetzt, in welchem die Operation zur Reduzierung von kTC-Rauschen nicht ausgeführt wird. Auf der anderen Seite führen die jeweiligen Elemente im Pixelbereich P11 die ursprüngliche Signalspeicherungsoperation aus.

**[0058]** Zu dem Zeitpunkt, zu dem das horizontale Auswahlsignal RW1 eingespeist wird, nachdem eine vorbestimmte Zeit verstrichen und der horizontale Transistor **16** in den Ein-Zustand versetzt ist, werden als nächstes der Abtast-Halteschalter **42** und der Klemmschalter **52** der CDS-Schaltung **6CL1** geschlossen, und die Signalspannung VS, die vom Source-Folgeverstärker **14** des Pixelbereichs P11 an die vertikale Auswahlleitung CL1 abgegeben wird, wird in die Abtast-Haltekapazität **44** und die CDS-Kapazität **50** geladen.

**[0059]** Als nächstes wird der Klemmschalter **52** ausgeschaltet, wird der Schalttransistor **70** in den Aus-Zustand versetzt, und werden die Schalttransistoren **68** und **72** in den Ein-Zustand versetzt. Dadurch dient die Schaltung **6VR1** zur Reduzierung von kTC-Rauschen wieder als der Differenzverstärker und wird in den Betriebszustand der Reduzierung von kTC-Rauschen versetzt. In diesem Zustand wird zu dem Zeitpunkt, zu dem das Rücksetzsignal RST an die Gate-Elektrode des Rücksetztransistors **12** des Pixelbereichs P11 angelegt wird, die Rücksetzspannung VR an die Gate-Elektrode des ersten Differenzverstärkers **72** geliefert.

**[0060]** Dadurch wird die Ausgangsspannung (=Rücksetzspannung VR) des ausgangsseitigen Transistors **66** der Stromspiegelschaltung der Schaltung **6VR1** zur Reduzierung von kTC-Rauschen so gesteuert, dass das Potential der Photodiode **10** an der Kathodenseite immer die Rücksetzspannung VR in der Periode wird, in der der Rücksetztransistor **12** im Ein-Zustand ist. Desgleichen dient die Schaltung **6VR1** zur Reduzierung von kTC-Rauschen zu der Zeit der Rücksetzoperation als Operationsverstärker mit einem Verstärkungsfaktor **1**.

**[0061]** In diesem Fall ist das kTC-Rauschen, das jedes Mal erzeugt wird, wenn die Photodiode **10** zurückgesetzt wird, nahezu konstant gemacht, und es ist möglich, eine Korrelation zwischen der Signalspannung VS einschließlich des kTC-Rauschens vor

der Signalspeicherung und dem kTC-Rauschen zu erzeugen, das nach der Signalspeicherung der Rücksetzspannung VR überlagert ist. Wenn die Photodiode **10** unter Verwendung der Schaltung **6VR1** zur Reduzierung von kTC-Rauschen auf der Rücksetzspannung VR zurückgesetzt wird, wird die Rücksetzspannung VR an die vertikale Auswahlleitung CL1 abgegeben. Die Rücksetzspannung VR wird in den Eingangsanschluss der Abtast- und Halteschaltung eingespeist und von der Abtast-Haltekapazität **44** gehalten.

**[0062]** Als Folge wird an der Ausgangsseite der CDS-Kapazität **50** der CDS-Schaltung **6CL1** ein Differenzsignal (VS-VR) erzeugt, das einer Differenz der Signalspannung VS und der Rücksetzspannung VR entspricht. Dieses Signal wird von der CDS-Kapazität **50** gehalten. Indem man so verfährt, ist es möglich, analoge Bilddaten zu erhalten, in denen nicht nur die sowohl der Signalspannung VS als auch der Rücksetzspannung VR überlagerten Komponenten eines Rauschens mit festem Muster, sondern auch das kTC-Rauschen entfernt ist. Diese analogen Bilddaten werden über den Spaltenauswahltransistor **20** vom Ausgangsanschluss des Verstärkers **54** an die gemeinsame Signalausgangsleitung **30** ausgegeben.

**[0063]** Gemäß der Schaltung **6VRn** zur Reduzierung von kTC-Rauschen der Ausführungsform ist der Hauptteil der Schaltung außerhalb des Pixelbereichs angeordnet, und das Element im Pixelbereich wird als der Teil der Schaltungsstruktur zur Zeit der Operation zur Reduzierung von kTC-Rauschen genutzt, um die Schaltung zu bilden, so dass das kTC-Rauschen ohne Verringern des Öffnungsverhältnisses des Pixel reduziert werden kann.

**[0064]** Selbst wenn die Größe und dergleichen des ersten differentiellen Transistors **62** und des Source-Folgeverstärkers **14**, die das Differenzpaar bilden, so einheitlich ausgebildet ist, dass sie nahezu die gleichen Charakteristiken aufweisen, gibt es übrigens einen Fall, in welchem eine sich gemäß einer Verdrahtungsdistanz zwischen beiden ändernde Offset-Spannung erzeugt wird. Da der Transistor des Source-Folgeverstärkers **14** klein ist, wird ferner die Offsetspannung mehrere zehn mV. Dies ist nicht vorzuziehen, da die Rücksetzspannung VR, die an die Kathodenseite der Photodiode **10** angelegt wird, in jedem der mehreren Pixelbereiche verschieden wird. Falls die Offset-Spannung verhältnismäßig niedrig ist, kann sie durch die CDS-Schaltung **6CLn** entfernt werden, die bei einer späteren Stufe eingerichtet ist. Um die Offset-Spannung sicher zu entfernen, ist es jedoch wünschenswert, eine Offset-Korrekturschaltung einzusetzen, die durch eine gestrichelte Linie von Fig. 4 umgeben ist.

**[0065]** Fig. 4 zeigt eine Skizze einer Offset-Korrekturschaltung **80**. Ein Hauptteil der Offset-Korrektur-

schaltung **80** ist in der Verstärker/Rauschlöschschaltung **6** vorgesehen. Die Offset-Korrekturschaltung **80** enthält einen einen Offset korrigierenden Transistor **82**, der in einer Eingangsstufe einer Rücksetzspannung VR eingesetzt ist, die an eine Gate-Elektrode des ersten differentiellen Transistors **62** angelegt wird. Eine Seite mit einer Elektrode des einen Offset korrigierenden Transistors **82** ist mit der Gate-Elektrode des ersten differentiellen Transistors **62** verbunden. Daneben enthält die Offset-Korrekturschaltung **80** einen einen Offset korrigierenden Transistor **86** mit einer Seite mit einer Elektrode, die mit der Versorgungsleitung VR1 für die Rücksetzspannung verbunden ist, an die die gesteuerte Rücksetzspannung VR abgegeben wird, wenn die Schaltung **6VR1** zur Reduzierung von kTC-Rauschen als der Differenzverstärker dient. Eine Seite mit einer Elektrode eines einen Offset korrigierenden Transistors **84** und eine Seite mit einer Elektrode einer einen Offset korrigierenden Kapazität **88** sind mit der Seite mit der anderen Elektrode des einen Offset korrigierenden Transistors **86** verbunden. Die Seite mit der anderen Elektrode des einen Offset korrigierenden Transistors **84** ist mit der Seite mit der anderen Elektrode des einen Offset korrigierenden Transistors **82** verbunden, und die Seite mit der anderen Elektrode der einen Offset korrigierenden Kapazität **88** ist mit einer Seite mit einer Elektrode des einen Offset korrigierenden Transistors **82** verbunden d.h. der Gate-Elektrode des ersten differentiellen Transistors **62**.

**[0066]** Es wird eine eine Offset-Spannung entfernende Operation durch die Offset-Korrekturschaltung **80** mit der obigen Struktur beschrieben. Zunächst arbeiten zu dem Zeitpunkt, zu dem das Rücksetzsignal RST an die Gate-Elektrode des Rücksetz-Transistors **12** angelegt wird, die Schalttransistoren **68**, **70** und **72**, und die Schaltung **6VR1** zur Reduzierung von kTC-Rauschen dient als Differenzverstärker. Bei einer Anfangsphase der Rücksetzperiode sind die einen Offset korrigierenden Transistoren **82** und **86** im Ein-Zustand, und der einen Offset korrigierende Transistor **84** ist im Aus-Zustand. Die Rücksetzspannung VR wird somit an die Gate-Elektrode des ersten differentiellen Transistors angelegt, und eine Spannung VR + VO einschließlich der Offset-Spannung VO wird über den Differenzverstärker an die Versorgungsleitung VR1 für die Rücksetzspannung abgegeben. Dementsprechend wird in der einen Offset korrigierenden Kapazität **82** die Offset-Spannung VO gehalten.

**[0067]** Wenn die einen Offset korrigierenden Transistoren **82** und **86** ausgeschaltet werden und der einen Offset korrigierenden Transistor **84** eingeschaltet wird, wird als nächstes ein Spannungswert VR – VO als die Rücksetzspannung an die Gate-Elektrode des ersten differentiellen Transistors **62** angelegt. Dadurch wird die gewünschte Rücksetzspannung VR über den Differenzverstärker an die Versorgungslei-

tung VR1 für die Rücksetzspannung abgegeben. Diese Operation wird in der Anfangsphase der Rücksetzperiode ausgeführt. Indem man so verfährt, wird es möglich, an jeden der Pixelbereiche Pmn die einheitliche Rücksetzspannung VR zu liefern.

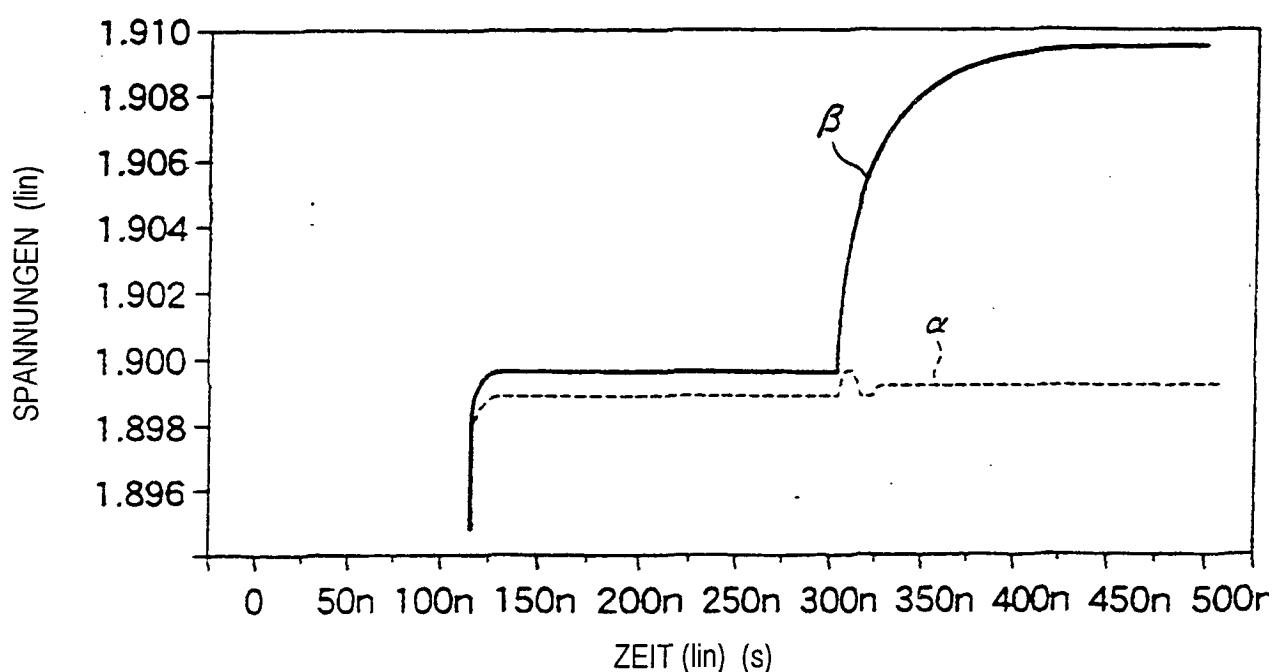

**[0068]** **Fig. 5** ist eine Simulationsdarstellung, die einen Effekt einer Reduzierung von kTC-Rauschen durch die Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp der Ausführungsform zusammen mit einem Vergleichsbeispiel zeigt. In der Zeichnung gibt die horizontale Achse eine Zeit an, und die vertikale Achse gibt einen Spannungswert an. Eine gestrichelte Linie  $\alpha$  in der Zeichnung ist eine Kurve, die den Effekt der Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp der Ausführungsform zeigt, und eine durchgezogene Linie  $\beta$  ist eine Kurve, die eine früher vorgeschlagene Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp zeigt. **Fig. 5** zeigt einen Ausgangsspannungswert von der CDS-Schaltung in dem Fall, in dem das Rücksetzsignal RST zu der Zeit 120 ns in den Rücksetz-Transistor eingespeist wird, und das kTC-Rauschen mit einer Gleichstromkomponente 10 mV ist nach etwa 200 ns von der Zeit an überlagert, zu der das Potential der Photodiode an der Kathodenseite etwa 1,9 V wird. Wie in der Zeichnung gezeigt ist, kann in der früher vorgeschlagenen Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp das kTC-Rauschen durch die CDS-Schaltung nicht reduziert werden, und es erscheint eine Rauschkomponente von etwa 10 mV, was nahezu gleich dem Pegel des überlagerten kTC-Rauschens ist. Auf der anderen Seite beträgt in der Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp der Ausführungsform eine Variation des Ausgangsspannungswertes von der CDS-Schaltung nur etwa 0,25 mV, und es kann ein extrem besserer Effekt einer Reduzierung von kTC-Rauschen erzielt werden.

**[0069]** Wie oben beschrieben wurde, ist es gemäß der vorliegenden Erfindung möglich, die Halbleiterbildaufnahmeverrichtung vom X-Y-Adressstyp zu realisieren, die eine geringe Elementgröße und ein weites Öffnungsverhältnis aufweist und das kTC-Rauschen reduzieren kann.

### Patentansprüche

1. Bildsensor, in welchem ein Gate eines Source-Folgetransistors (**14**) mit einem Ende eines photoelektrischen Transducers (**10**) verbunden ist und ein Potential an dem einen Ende des photoelektrischen Transducers über den Source-Folgetransistor als Bilddaten ausgelesen wird, welcher Bildsensor **durch gekennzeichnet** ist, daß zur Zeit der Rücksetzung des photoelektrischen Transducers ein Differenzverstärker (**14**, **16**, **40**, **62**, **64**, **66**, **72**) eingerichtet wird, in welchem ein invertierender Eingangsanschluß das Gate des Source-Folgetransistors ist und ein nicht invertierender Eingangsanschluß das Gate

eines ersten differentiellen Transistors (**62**) ist, an den eine konstante Spannung (VR) angelegt wird, und das eine Ende des photoelektrischen Transducers bei der konstanten Spannung gehalten wird, indem eine Ausgabe des Differenzverstärkers zum invertierenden Eingangsanschluß rückgekoppelt wird.

2. Bildsensor nach Anspruch 1, dadurch gekennzeichnet, daß die Ausgabe des Differenzverstärkers über einen Rücksetz-Transistor (**12**) zum Zurücksetzen des photoelektrischen Transducers zum invertierenden Eingangsanschluß rückgekoppelt wird.

3. Bildsensor nach Anspruch 2, dadurch gekennzeichnet, daß der photoelektrische Transducer, der Source-Folgetransistor und der Rücksetz-Transistor ein Pixel (P) bilden und mehrere solche Pixel in einer Matrixform angeordnet sind.

4. Bildsensor nach Anspruch 3, dadurch gekennzeichnet, daß Ausgänge der mehreren Pixel gemeinsam mit einer vertikalen Auswahlleitung (CL) verbunden sind und die Bilddaten der jeweiligen Pixel über die vertikale Auswahlleitung ausgelesen werden.

5. Bildsensor nach Anspruch 4, dadurch gekennzeichnet, daß der erste differentielle Transistor (**62**) des Differenzverstärkers für jede der vertikalen Auswahlleitungen (CL1–CL4) vorgesehen ist.

6. Bildsensor nach Anspruch 5, dadurch gekennzeichnet, daß der erste differentielle Transistor (**62**) über einen Schalttransistor (**72**), der synchron mit einer Operation des Rücksetz-Transistors (**12**) eingeschaltet wird, mit der vertikalen Auswahlleitung (CL) verbunden ist.

7. Bildsensor nach Anspruch 3, 4, 5 oder 6, dadurch gekennzeichnet, daß Rücksetz-Transistoren (**12**) der mehreren Pixel gemeinsam mit einer Versorgungsleitung (VR1–VR4) für die Rücksetzspannung verbunden sind.

8. Bildsensor nach Anspruch 7, dadurch gekennzeichnet, daß der Differenzverstärker eine Stromspiegelschaltung (**64, 66**) enthält und die Stromspiegelschaltung für jede der mehreren derartigen Versorgungsleitungen (VR1–VR4) für die Rücksetzspannung vorgesehen und betreibbar ist, um die Ausgabe des Differenzverstärkers an jeden der mehreren Rücksetz-Transistoren (**12**) zu liefern, die gemeinsam mit der Versorgungsleitung für die Rücksetzspannung verbunden sind.

9. Bildsensor nach Anspruch 8, dadurch gekennzeichnet, daß die vertikale Auswahlleitung (CL) und die Versorgungsleitung (VR) für die Rücksetzspannung ein Paar bilden und parallel zueinander angeordnet sind.

Es folgen 5 Blatt Zeichnungen

FIG.1

FIG.2

FIG.3

FIG.4

FIG.5

FIG.6

FIG.7

FIG.8