(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4294778号

(P4294778)

(45) 発行日 平成21年7月15日(2009.7.15)

(24) 登録日 平成21年4月17日(2009.4.17)

(51) Int.Cl.

F 1

G06F 11/34 (2006.01)

G06F 9/38 (2006.01)G06F 11/34 S

G06F 11/34 L

G06F 9/38 380C

請求項の数 34 外国語出願 (全 38 頁)

(21) 出願番号 特願平10-375360

(22) 出願日 平成10年11月26日(1998.11.26)

(65) 公開番号 特開平11-272517

(43) 公開日 平成11年10月8日(1999.10.8)

審査請求日 平成17年11月9日(2005.11.9)

(31) 優先権主張番号 08/980164

(32) 優先日 平成9年11月26日(1997.11.26)

(33) 優先権主張国 米国(US)

(73) 特許権者 398038580

ヒューレット・パッカード・カンパニー

HEWLETT-PACKARD COMPANY

アメリカ合衆国カリフォルニア州パロアルト ハノーバー・ストリート 3000

(74) 代理人 100059959

弁理士 中村 梓

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100065189

弁理士 宍戸 嘉一

(74) 代理人 100096194

弁理士 竹内 英人

最終頁に続く

(54) 【発明の名称】プロセッサパイプラインにより処理される相互作用の特性の統計値を推定する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の処理段を有するコンピュータシステムのパイプラインで処理される命令間の相互作用の特性の統計値を推定するためにコンピュータが実行する方法であって、

パイプラインの第1段へ命令をフェッチし；

フェッチした命令から命令のセットをランダムに選択し、その選択された命令のセットのサブセットは互いに同時に実行され；

前記の選択された命令のサブセット間の距離を特定し；

前記の選択された命令のセットがパイプラインで処理されている間にコンピュータシステムの状態情報を記録し；

記録された状態情報をソフトウェアへ通信し；そして

前記の選択された命令の複数のセットからの前記の記録された状態情報を統計学的に分析して、前記の選択された命令のセット間の相互作用の統計値を推定する段階を備えたことを特徴とする方法。

## 【請求項 2】

ランダムに選択されたそれぞれのセットは少なくとも2つの命令を有する請求項1に記載の方法。

## 【請求項 3】

前記の分析は更に、前記の記録された状態情報のファンクションに基づいて前記の複数のセットの中の一つのサブセットを選択する段階を含む請求項1に記載の方法。

**【請求項 4】**

前記のファンクションは、選択された命令の識別情報に基づいて選択を行い、この識別情報は、選択された命令のアドレス、選択された命令を実行するプロセス、選択された命令がその中で実行するアドレススペース番号、そして選択された命令がその中で実行するハードウェアコンテクスト又はスレッド番号を含む請求項 3 に記載の方法。

**【請求項 5】**

前記のファンクションは、選択された命令に関連した経路識別情報に基づいて選択を行う請求項 3 に記載の方法。

**【請求項 6】**

前記のファンクションは、選択された命令の演算コードに基づいて選択を行う請求項 3 10 に記載の方法。

**【請求項 7】**

前記のファンクションは、選択された命令に対して記録された待ち時間情報に基づいて選択を行う請求項 3 に記載の方法。

**【請求項 8】**

前記のファンクションは、選択された命令に対して記録された事象情報に基づいて選択を行う請求項 3 に記載の方法。

**【請求項 9】**

前記のファンクションは、選択された命令のオペランドの値に基づいて選択を行う請求項 3 20 に記載の方法。

**【請求項 10】**

前記のファンクションは、選択された命令のデータ依存関係に基づいて選択を行う請求項 3 に記載の方法。

**【請求項 11】**

前記のファンクションは、選択された命令が経験する事象カウントに基づいて選択を行う請求項 3 に記載の方法。

**【請求項 12】**

フェッチのレートはクロックにより決定され、そして前記の事象カウントは、選択された命令のいずれか 2 つのフェッチ間のサイクル数と、選択された命令のいずれか 2 つの間でリタイアする命令の数と、選択された命令のいずれか 2 つの間でパイプラインの特定の段に入る命令の数と、プロセッサ、メモリシステム、ネットワーク又は I / O サブシステム事象の所定の測定値を含む請求項 1 1 に記載の方法。

**【請求項 13】**

前記の距離は、選択された命令のセットのいずれか 2 つのメンバー間のクロックサイクル数として特定される請求項 1 に記載の方法。

**【請求項 14】**

前記の距離は、選択された命令の最初から最後までのフェッチ間にフェッチされた命令の数として特定される請求項 1 に記載の方法。

**【請求項 15】**

前記の距離は、フェッチされた命令の最初から最後のフェッチまでのサイクルの細分化の数として特定される請求項 1 2 に記載の方法。

**【請求項 16】**

前記の距離は、一定の間隔にわたって変化する請求項 1 に記載の方法。

**【請求項 17】**

前記の距離は、一定の間隔にわたりランダムにそして均一に変化する請求項 1 6 に記載の方法。

**【請求項 18】**

前記の統計学的分析は、選択された命令の特定のセットにおける選択された命令の記録された状態情報のファンクションを計算する請求項 1 7 に記載の方法。

**【請求項 19】**

50

20

30

40

50

前記のファンクションは、特定命令の複数の実行中の平均同時性レベルを計算する請求項18に記載の方法。

【請求項20】

前記のファンクションは、特定の命令の複数回実行中のパイプラインの特定段の平均利用を計算する請求項18に記載の方法。

【請求項21】

前記のファンクションは、特定の命令の複数回実行中に浪費されるイッシュースロットの数を計算する請求項18に記載の方法。

【請求項22】

前記の統計学的分析は、選択された命令の特定のセットに対する記録された状態情報のファンクションを計算する請求項3に記載の方法。 10

【請求項23】

前記のファンクションは、同一の選択された命令を含むセットに基づいてループ反復待ち時間を推定する請求項22に記載の方法。

【請求項24】

前記のファンクションは、同時発生のループ反復の数を推定する請求項22に記載の方法。

【請求項25】

前記のファンクションは、実行コンテクスト間の遷移の頻度を推定する請求項22に記載の方法。 20

【請求項26】

実行コンテクストはスレッド又はプロセスである請求項25に記載の方法。

【請求項27】

前記のファンクションはロードから使用までの待ち時間を計算する請求項18に記載の方法。

【請求項28】

前記のファンクションは、選択された命令の実行間の重なる量を計算する請求項18に記載の方法。

【請求項29】

重なりはクロックサイクルで測定される請求項28に記載の方法。 30

【請求項30】

前記の重なりはフェッチされた命令で測定される請求項28に記載の方法。

【請求項31】

前記の実行コンテクストはプログラムの部分である請求項25に記載の方法。

【請求項32】

前記の遷移は割り込み又はトラップハンドラーへの、そしてそこからのものである請求項25に記載の方法。

【請求項33】

前記のファンクションは、データを発生する第1の選択された命令と、発生されたデータを消費する第2の選択された命令との間の待ち時間を推定する請求項22に記載の方法。 40

【請求項34】

前記の第1の命令はロードオペレーションを実行し、そして第2の命令はそのロードオペレーションの結果を使用する請求項29に記載の方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、一般に、コンピュータシステムの性能測定に係り、より詳細には、プロセッサパイプラインによって処理される命令間の相互作用の特性の統計値を推定することに係る。 50

## 【0002】

## 【従来の技術】

コンピュータプロセッサは、益々高速になっているが、ソフトウェアアプリケーションの性能は、それに歩調が合っていない。大型の商業用途の場合に、命令当たりの平均プロセッササイクル( C P I )値が 2 . 5ないし 3 という大きさである。4 ウェイ命令イッシュープロセッサでは、C P I が 3 であることは、12ごとに1つのイッシュースロットしか良好に使用されないことになる。ソフトウェアスループットがハードウェアの改良となぜ歩調が合わないかを理解することが重要である。

このような問題をメモリの待ち時間に転嫁するのが一般的であり、実際に、多くのソフトウェアアプリケーションは、データ転送が完了するのを待機して多数のサイクルを費やす。しかしながら、分岐予想ミスのような他の問題も、プロセッササイクルを浪費する。一般的な原因とは独立して、システムアーキテクチャー並びにハードウェア及びソフトウェアエンジニアは、複雑なプロセッサを組み込んだ近代的なコンピュータシステムの性能を改善するために、どの命令がストールしているかそしてなぜかを知る必要がある。10

## 【0003】

通常、これは、システムが動作している間にその振る舞いの「プロファイル」を発生することにより行われる。プロファイルとは、性能データの記録である。しばしば、プロファイルは、性能のボトルネックを容易に識別できるようにグラフ的に発生される。

プロファイル形成は、計装及び模擬により行うことができる。計装では、プログラムの実行中に特定事象を監視するためにプログラムに付加的なコードが追加される。模擬は、実際のシステムでプログラムを実行するのではなく、人為的な環境においてプログラム全体の振る舞いをエミュレートするように試みる。20

これら2つの方法は、各々、欠点を有する。計装は、追加命令及び余計なデータ参照のためにプログラム真の振る舞いを擾乱させる。模擬は、実際のシステムにおいてプログラムを実行する場合に比して実質的な性能オーバーヘッドを犠牲にして擾乱を回避する。更に、計装又は模擬では、大規模なソフトウェアシステム全体、即ちアプリケーション、オペレーティングシステム及びデバイスドライバコードをプロファイリングすることが通常困難である。

## 【0004】

プロセッサのプロファイル情報を与えるために、ハードウェア実施の事象サンプリングを使用することもできる。ハードウェアサンプリングは、模擬及び計装に勝る多数の効果を有し、即ち性能を測定するためにソフトウェアプログラムを変更する必要がない。サンプリングは、比較的低いオーバーヘッドで全システムに作用する。実際に、最近では、低いオーバーヘッドのサンプリングをベースとするプロファイリングを使用して、パイプラインストール及びそれらの原因に関する詳細な命令レベル情報を収集することができる。しかしながら、多くのハードウェアサンプリング技術は、特定の事象を測定するように設計されているので融通性に欠ける。30

デジタル社の A l p h a A X P 2 1 1 6 4 、インテル社のペンティウム・プロ及び M I P S 1 0 0 0 0 は、データキャッシュ( D キャッシュ )ミス、命令キャッシュ( I キャッシュ )ミス及び分岐予想ミスのような種々の事象をカウントすることのできる事象カウンタを形成する。これらの事象カウンタは、カウンタがオーバーフローするときに割り込みを発生し、従って、カウンタの性能データを高レベルのソフトウェアでサンプリングすることができる。40

## 【0005】

事象カウンタは、特定のプログラム又はその一部分を実行する間にシステムが招いた分岐予想ミスの数のような集合情報を捕獲するのに有用である。しかしながら、既知の事象カウンタは、どの分岐命令が頻繁に予想ミスを生じるかのように状態情報を個々の命令に帰属させる点で有用性が低い。これは、事象カウンタがオーバーフローしそして割り込みを生じるときには、その事象を生じた命令のプログラムカウンタ( P C )がもはや使用できないためである。50

命令をアウトオブオーダー（順序ずれして）でイッシュすることができるプロセッサの動的なオペレーションを推測することが特に問題である。実際に、アウトオブオーダープロセッサで実行されるソフトウェアプログラムの振る舞いは極めて不可解で且つ理解が困難である。その具体的な例としてアウトオブオーダーの A l p h a 2 1 2 6 4 プロセッサでの命令の流れについて考える。

#### 【0006】

##### スーパースカラープロセッサーアーキテクチャー

###### 実行順序

アウトオブオーダープロセッサは、命令を正しい順序でフェッチしそしてリタイアするが、命令をそれらのデータ依存性に基づいて処理する。命令の処理は、レジスタのマッピング、命令の発生及び実行を含む。命令は、それがフェッチされたときから、それがリタイア又はアボートするときまで、「フライト中」であると言える。10

各プロセッササイクル中に、プロセッサパイプラインの第1段は、命令キヤッシュ（Iキヤッシュ）から命令のセットをフェッチする。命令のセットはデコードされる。命令デコーダは、フェッチされたセットのどの命令が命令流の一部分であるかを識別する。

#### 【0007】

フェッチすべき次の命令のPCを分析するには多数のサイクルを要するので、PCは、通常、分岐又はジャンプブレディクタ（予想子）により前もって予想される。予想を誤ったときには、プロセッサは、「不良」実行経路を占有する予想ミス命令をアボート（中止）し、そして「良好」経路において命令のフェッチを再スタートする。20

命令を順序ずれ状態で実行できるようにするために、命令のオペランドに指定されたレジスタは、「読み取り後の書き込み」と「書き込み後の書き込み」競合を防止するように動的に名前を付け直される。この名前の付け直しは、アーキテクチャー即ち「仮想」レジスタを物理的レジスタへとマッピングすることにより達成される。従って、同じ仮想レジスタに書き込む2つの命令は、それらが異なる物理的レジスタに書き込みそして仮想レジスタの消費者が適切な値を得るので、順序ずれ状態で安全に実行することができる。

#### 【0008】

レジスタマップ型命令は、そのオペランドが計算されそして適當な形式の機能的「実行」ユニットが得られるまで、イッシュ待ち行列に存在する。命令によって使用される物理的なレジスタは、命令がイッシュされるサイクルで読み取られる。命令は、それらが実行された後に、リタイアの準備ができたとマークされ、そしてプログラム順序における全ての手前のリタイア準備命令がリタイアしたときに、即ち命令が正しいプログラム順序でリタイアするときに、プロセッサによりリタイアされる。リタイアの際に、プロセッサは、命令によりなされる変更をシステムのアーキテクチャー「状態」へコミットし、そして命令により消費されたリソースを解除する。30

#### 【0009】

###### 予想ミス

分岐が誤って予想されるようなある場合には、命令をトラップし又は破棄しなければならない。これが生じたときには、現在の推測的な構造状態が、予想ミスが生じた実行点へと戻され、正しい命令においてフェッチが続けられる。40

#### 【0010】

###### 遅延

多数の事象が命令の実行を遅らせる。パイプラインの前方において、フェッチユニットは、Iキヤッシュミスのためにストールするか、又はフェッチユニットは、予想ミスのために不良経路に沿って命令をフェッチすることがある。マップ手段は、空いた物理的レジスタが欠乏するか、又はイッシュ待ち行列に空きスロットが欠乏するためにストールすることがある。イッシュ待ち行列の命令はそれらのレジスタ依存性が満足されるか又は機能的実行ユニットが使用できるようになるのを待機する。

命令は、データキャッシュミスによりストールがある。命令は、それらが不良経路を下るように推測的に発生されるか、又はプロセッサが割り込みを行ったためにとラッ50

プされることがある。これら事象の多くは、例えば、コードの検査により静的に予想することが困難であり、それらは全てシステムの性能を低下させる。この形式の状態情報を捕獲するのに単純な事象カウンタでは不充分である。加えて、遅延の長さを厳密に測定して、どの遅延に特に注目すべきかを決定することは困難である。

#### 【0011】

プログラマー又は最適化ツールが、スーパースカラー及びアウトオブオーダープロセッサ、又はこの点については任意のアーキテクチャー設計のプロセッサのような複雑なコンピュータシステムのソフトウェア及びハードウェア要素の性能を改善できるように、事象を特定の命令及びマシン状態に直接的に帰属させることが強く望まれる。

#### 【0012】

##### 【発明が解決しようとする課題】

##### 公知の事象カウンタに伴う問題

既知の事象カウンタに伴う主な問題は、カウンタをオーバーフローさせた事象を生じさせた命令が、通常は、例外的PCよりも前にフェッチされることであり、即ち、このPCは、オーバーフローを生じさせた命令のものではない。フェッチと割り込みとの間の遅延の長さは、一般に、予想できない量である。この予想できない事象分布は、事象を特定の命令に適切に帰属させることを困難にする。順序ずれ及び予測的実行は、この問題を増幅するが、これは、Alpha21164プロセッサのようなインオーダー（順序正しい）マシンにも存在する。例えば、Alpha21164（インオーダー）プロセッサ対ベンチウム・プロ（アウトオブオーダー）プロセッサに対してDキャッシュ基準事象カウントを監視しながら、性能カウンタ割り込みハンドラーに与えられるプログラムカウンタ値を比較する。例示的プログラムは、ランダムメモリアクセス命令、例えば、ロード命令と、それに続く、ナルオペレーション命令（nop）のハンドラーとを含むループより成る。

#### 【0013】

インオーダー型のAlphaプロセッサでは、全ての性能カウンタ事象（例えば、キャッシュミス）は、事象の6サイクル後に実行される命令に帰属され、ロードアクセス後の7番目の命令においてサンプルの大きなピークを生じる。このスキーした事象分布は、理想的なものではない。しかしながら、单一の大きなピークがあるために、静的な分析は、時々、このピークから後方に作用し、その事象を生じさせた実際の命令を識別することができるが、これは、非常に単純なプログラムに対する最良の推測以上のものは何もない。アウトオブオーダー型のベンチウム・プロで実行される同一のプログラムの場合に、事象サンプルは、次の25個の命令にわたって広く分布され、スキーを示すだけでなく、著しい不鮮明さも示す。サンプルの広い分布は、特定の事象を、その事象を生じた特定の命令に帰属させるのをほぼ不可能にする。他のハードウェア事象をカウントするときにも同様の振る舞いが生じる。

#### 【0014】

スキー又は不鮮明さのある事象サンプル分布に加えて、従来の事象カウンタは、付加的な問題で悩まされている。通常、事象カウンタより多くの当該事象があり、全ての当該事象を同時に監視することは、不可能でないまでも、困難である。プロセッサの複雑さが増すと、この問題が一層悪化する。

加えて、事象カウンタは、事象が発生したという事実しか記録せず、その事象に関する付加的な状態情報を与えない。多数の種類の事象に対し、キャッシュミス事象にサービスする待ち時間のような付加的な情報が極めて有用である。

更に、公知のカウンタは、一般に、事象をコードの「ブラインドスポット」に帰属させることができない。ブラインドスポットとは、割り込み権が与えられるまで事象が確認されないために、高優先順位システムルーチン及びPALコードのような割り込み不能コードである。その今までに、プロセッサの状態は著しく変化し、おそらく偽の情報を与える。

#### 【0015】

10

20

30

40

50

### ストール対ボトルネック

パイプライン式のインオーダープロセッサにおいて、パイプライン段で1つの命令がストールすると、その後の命令がそのパイプライン段に通過することが妨げられる。それ故、インオーダープロセッサでは「ボトルネック」命令を識別することが比較的容易であり、即ちボトルネック命令は、パイプラインのどこかでストールする傾向がある。インオーダープロセッサの場合、命令が各パイプライン段を通るときにその待ち時間を測定し、そしてその測定された待ち時間を、各パイプライン段におけるその命令の理想的な待ち時間と比較することにより、ストールを識別することができる。命令は、ある段を通過する最小待ち時間より長い時間を必要とするときに、その段においてストールしたと仮定することができる。

10

#### 【0016】

しかしながら、アウトオブオーダープロセッサでは、あるパイプライン段でストールした命令に対して他の命令がそのパイプライン段を通過することがある。実際に、ストールした命令の付加的な待ち時間は、他の命令の処理によって完全にマスクされ、実際に、ストールした命令は、観察されるプログラム完了を遅延しないことがある。

インオーダーシステムにおいても、あるパイプライン段のストールは、別のパイプライン段がボトルネックであるときにはプログラムの全実行時間に影響しない。例えば、メモリ集中のプログラムの実行中には、Dキャッシュミスにより遅延される実行ユニットからの「バックプレッシャー」のために、命令パイプラインのフェッチ手段及びマップ手段がしばしばストールすることができる。

20

#### 【0017】

理想的には、キャッシングミスを生じるメモリオペレーションを一次ボトルネックとして分類する。フェッチ手段及びマップ手段のストールは、実際には、キャッシングミスによる遅延の非兆候状態であり、即ち二次ボトルネックである。

ストールが他の命令によりマスクされない命令を識別し、そしてそれらを真のボトルネックとして識別することが望ましい。更に、プログラムの振る舞いを改善するためには、非兆候（二次）ボトルネックよりもカジュアル（一次）のボトルネックに焦点を合わせることが必要である。このようにパイプライン段のボトルネックをカジュアル及び非兆候と分類することは、パイプラインの状態並びにフライト中命令のデータ及びリソース依存性を詳細に知ることが必要であるが、これらは、良く知られたように、単純な事象カウンタから得ることができない。

30

#### 【0018】

1992年9月29日付のウェスコット氏等の「命令サンプリング手段(Instruction Sampling Instrumentation)」と題する米国特許第5,151,981号は、アウトオブオーダーの実行マシンにおいて命令ベースのサンプリングを行うハードウェアメカニズムを提案している。ウェスコット氏等の解決策には多数の欠点がある。第1に、この解決策は、サンプリングされるコードの長さ及びサンプリングレートに基づいて命令サンプルの流れをバイアスし得る。第2に、このシステムは、リタイアした命令のみをサンプリングし、フェッチした全ての命令をサンプリングするのではなく、その幾つかがアポートされる。第3に、ウェスコット氏等のメカニズムにより収集される情報は、例えば、キャッシングミスのような個々の事象属性に集中するが、命令間の関係を決定するための有用な情報を与えるものではない。

40

#### 【0019】

最近、「ロード通知(informing loads)」と称するハードウェアメカニズムが提案されている。これについては、1996年5月22日のプロシーディングズ第23アニュアルインターナショナルシンポジウム・オン・コンピューターアーキテクチャー、第260-270ページに掲載されたホロイツ氏等の「インフォームドメモリオペレーション：近代的なプロセッサにおけるメモリ性能フィードバックの供給(Informed memory operations: Providing memory performance feedback in modern processors)」を参照されたい。この場合は、メモリオペレーションに続いて、そのメモリオペレーションがキャッシングにおい

50

てミスした場合及びその場合にのみ条件分岐オペレーションを行うことができる。プロファイリングについては特に設計されていないが、このメカニズムは、特にDキャッシュミスの事象情報を収集するのに使用できる。

#### 【0020】

キャッシュミスルックアサイド(CML)バッファと称する他の特殊なハードウェアにおいては、高いレベル2のキャッシュミスレートに悩まされる仮想メモリページが識別される。この詳細な説明については、1994年10月4日のプロシーディングズ・オブ・ザ・シックスス・インターナショナルコンファレンス・オン・アーキテクチャルサポート・フォア・プログラミングランゲッジ・アンド・オペレーティングシステム、第158-170ページに掲載されたバーシャド氏等の「大型の直接マップ式キャッシュにおける競合ミスの動的な回避(Avoiding conflict misses dynamically in large direct-mapped caches)」を参照されたい。10

#### 【0021】

インテル社のペンティウムのようなプロセッサは、分岐ブレディクタの分岐ターゲットバッファ(BTB)の内容をソフトウェアで読み取ることができる。ソフトウェアでBTBを周期的に読み取ることにより、コンテ氏等は、プログラムの限界実行頻度を推定するための非常にオーバーヘッドの低い技術を開発した。これについては、1994年11月30日のプロシーディングズ・オブ・第27アニュアルインターナショナルシンポジウム・オン・マイクロアーキテクチャ、第12-21ページに掲載された「プロファイル駆動の最適化をサポートするための分岐ハンドリングハードウェアの使用(Using branch handling hardware to support profile-driven optimization)」を参照されたい。20

#### 【0022】

この解決策は、関連サンプリング情報を記憶する「プロファイル記録」に含まれた分岐方向情報を追跡することにより得られるものと同様の情報を形成する。最近、コンテ氏等は、分岐が実行される回数及び実行されない回数をカウントするプロファイルバッファと称する付加的なハードウェアの断片を提案している。これについては、1996年12月2日のプロシーディングズ・オブ・第29アニュアルインターナショナルシンポジウム・オン・マイクロアーキテクチャ、第36-45ページに掲載された「プロファイルバッファを使用する正確且つ実際的なプロファイル駆動の編集(Accurate and practical profile-driven compilation using the profile buffer)」を参照されたい。30

#### 【0023】

##### 【課題を解決するための手段】

本発明によれば、プロセッサのオペレーションを測定するための装置及び方法であって、従来のメカニズムとは異なる装置及び方法が提供される。事象をカウントし、そして事象カウンタがオーバーフローしたときにプログラムカウンタをサンプリングするのではなく、本発明の装置及び方法は、命令をランダムに選択し、そしてその選択された命令に対して詳細な状態情報をサンプリングすることに依存する。

周期的に、プロセッサの動作中に、プロファイリングされるべき命令がランダムに選択され、そして命令の実行中に何が起きたかのプロファイル記録がプロセッサの内部プロファイルレジスタのセットに累積される。選択された命令の処理が終了し、例えば、命令がリタイアし、アボートし又はトランプした後に、割り込みが発生される。パイプラインにおいて命令がいかに処理されたかの詳細を特徴付ける記録情報を内部プロファイルレジスタからソフトウェアによりサンプリングすることができる。40

#### 【0024】

プロファイルレジスタは、命令の実行に関する多数の有用な事実を記録することができる。性能情報は、例えば、選択された命令が実行パイプラインの各段において費やしたサイクルの数、即ち段の待ち時間、命令がIキャッシュ又はDキャッシュミスを受けたかどうか、メモリオペランドの有効アドレス又は分岐/ジャンプターゲット、そして命令がリタイア又はアボートされたかどうかを含むことができる。

順序正しく実行する(インオーダー型)プロセッサにおいては、サンプルされた命令のフ50

エッチ - リタイア待ち時間が与えられたときに各命令に起因する全ストールサイクル数を推定することができる。これは、1つのストールした命令が別のストールした命令とオーバーラップする事がないので、ボトルネックを識別するのに充分である。

#### 【0025】

順序ずれして実行する（アウトオブオーダー型）プロセッサにおいては、ほとんどのストールがおそらくオーバーラップし、そしてそのストールした命令の周りで順序ずれして発生される他の命令によりマスクされる。これは、ストールした命令の識別を困難なものにする。更に、ボトルネックを識別するためには、各命令が実行される間に同時性の平均レベルに関する情報を収集することが必要となる。

特殊目的のハードウェアは、プロファイリングされた命令が実行される間に発生する命令の数をカウント及び記録して、同時実行のレベルを測定することができる。しかしながら、これは、発生するがアボートされ、従って、リタイアしない命令を考慮に入れるものではない。そこで、有用な同時性の量の測定値が与えられる。有用な同時性は、並列に発生しそして所与の命令で首尾良くなりタイアする命令の平均数である。発生するがその後にアボートされる命令は、有用ではない。従って、ストールが有用な同時性によりマスクされない命令をボトルネックとして分類することができる。この別の方法を説明するために、アウトオブオーダープロセッサにおいて性能ボトルネックの位置を正確に示すための重要なメトリックは、所与の命令が実行される間に費やされた発生スロットの数である。

#### 【0026】

従って、有用な同時性を測定するために、「対ごとのサンプリング(pair-wise sampling)」と称する技術が提供される。基本的な考え方は、ネスト形態のサンプリングを実行することである。ここでは、第1のプロファイリングされた命令と同時に実行できる命令のウインドウが動的に定義される。命令のウインドウからプロファイリングするために第2の命令がランダムに選択される。プロファイリングされた及び第2の命令は、プロファイル情報を収集できるところのサンプル対を形成する。

対ごとのサンプリングは、各命令に起因する費やされた発生スロットの数を容易に決定すると共に、ボトルネックの位置を既知の技術よりもかなり正確に指示する。一般に、対ごとのサンプリングは、非常に融通性があり、種々様々な当該同時性及び利用メトリックを決定することのできる分析の基礎を形成する。

#### 【0027】

より詳細には、プロセッサのパイプラインにより処理される1つ以上の命令を周期的に且つランダムに選択し、そして実行パイプラインの段を経て命令が進行する間にプロファイル情報を収集するための装置及び方法が提供される。高レベルのソフトウェアは、次いで、この情報を種々の仕方で後処理することができ、例えば、同じ命令の多数の実行から情報を収集することにより後処理することができる。

捕獲することのできる情報は、例えば、命令のアドレス（プログラムカウンタ即ちPC）、命令が命令キャッシュミスを受けたかどうか、及びミスにサービスするために被る待ち時間を含む。命令がメモリオペレーションを実行する場合には、命令がデータキャッシュミスを受けたかどうか決定し、そしてメモリ要求を満足するための待ち時間を測定する。更に、命令が各パイプライン段において費やす時間の長さを測定することができる。又、プロファイル情報は、命令がリタイアしたかアボートしたかを指示すると共に、後者の場合には、どんな種類のトラップが命令の実行をアボートしたかも指示することができる。

#### 【0028】

命令が実行パイプラインを経て進行するときにプロファイリングレジスタのセットに情報が収集される。命令の実行が終了すると、それがリタイアするか又はアボートするためには、上位レベルのソフトウェアに割り込みが与えられる。次いで、ソフトウェアは、プロファイリングレジスタに存在する情報を種々の方法で処理することができる。

サンプリングされる性能情報は、プロファイルで指示される最適化にとって非常に有用であるが、事象の発生を集合的にカウントするようなハードウェア事象カウンタとしても多数の使い方がある。

10

20

30

40

50

ここに開示する技術は、既存の性能監視ハードウェアに対する改良であり、そして命令を順序ずれして発生できる近代的なマイクロプロセッサにおいて比較的低いハードウェアコストで効率的に実施することができる。

#### 【0029】

より詳細には、複数の処理段を有するコンピュータシステムのパイプラインで処理される命令間の相互作用の特性の統計値を推定する方法が提供される。

パイプラインの第1段へと命令がフェッチされる。フェッチされた命令から命令のセットがランダムに選択され、その選択された命令のセットのサブセットが互いに同時に実行される。選択された命令のセット間の距離が特定され、そして選択された命令のセットがパイプラインにより処理される間にコンピュータシステムの状態情報が記録される。

10

記録された状態情報は、ソフトウェアへ通信され、そこで、選択された命令の複数のセットに対して統計学的に分析されて、選択された命令のセット間の相互作用の統計値を推定する。

#### 【0030】

##### 【発明の実施の形態】

###### システムの概要

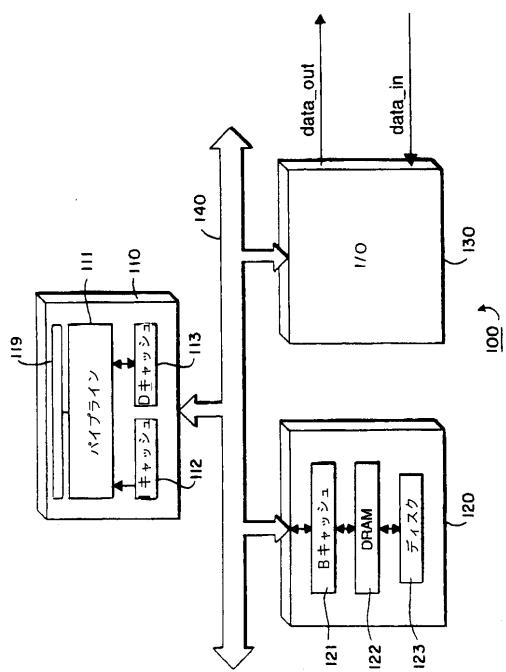

図1は、ここに開示するサンプリング方法及び装置を使用することのできるコンピュータシステム100を示す。このシステム100は、バスライン140で接続された1つ以上のプロセッサ110、オフチップメモリ120及び入力/出力インターフェイス(I/O)130を備えている。プロセッサ110は、例えば、デジタルイクリップメント社のA1pha21264プロセッサのように、集積半導体チップにおいて、機能的実行ユニットを含む多数の実行パイプライン111、命令キャッシュ(Iキャッシュ)112及びオンチップデータキャッシュ(Dキャッシュ)113として実施することができる。又、プロセッサチップ110は、以下に詳細に述べるように、選択された命令に対してプロセッサ状態をサンプリングするためのハードウェア119も備えている。

20

#### 【0031】

オフチップメモリ120は、汎用キャッシュ(Bキャッシュ又はSRAM)121と、揮発性メモリ(DRAM)122と、永続的メモリ(ディスク)123とを含むハイアラーキー構成をとることができる。I/O130は、システム100に対してデータを入力及び出力するのに使用できる。

30

#### 【0032】

###### オペレーション

システム100のオペレーション中に、ソフトウェアプログラムの命令及びデータがメモリ120に記憶される。命令及びデータは、既知のコンパイラ、リンカー及びローダー技術を使用して従来のやり方で発生される。命令及びデータは、キャッシュ112-113を経て1つのプロセッサ110の実行パイプライン111に転送される。パイプラインにおいて、命令が実行のためにデコードされる。ある命令は、データに作用する。他の命令は、プログラムの実行流を制御する。

命令を実行しながら詳細な性能データを収集することが所望される。性能データは、メモリオペレーション及び実行流に関連付けることができる。

40

#### 【0033】

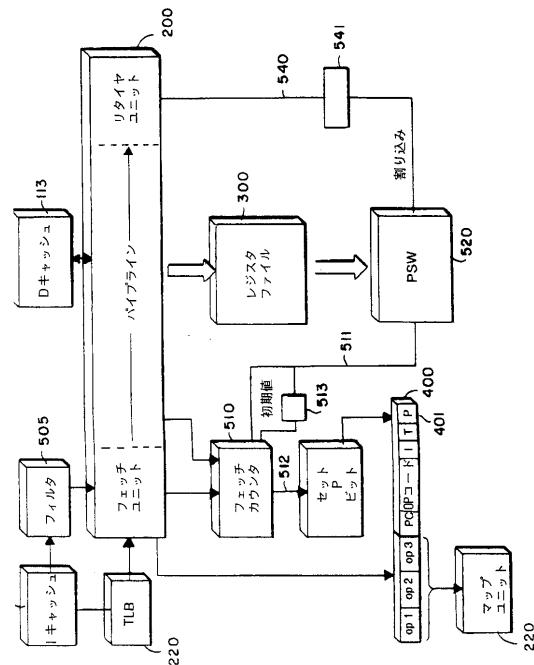

###### プロセッサパイプライン

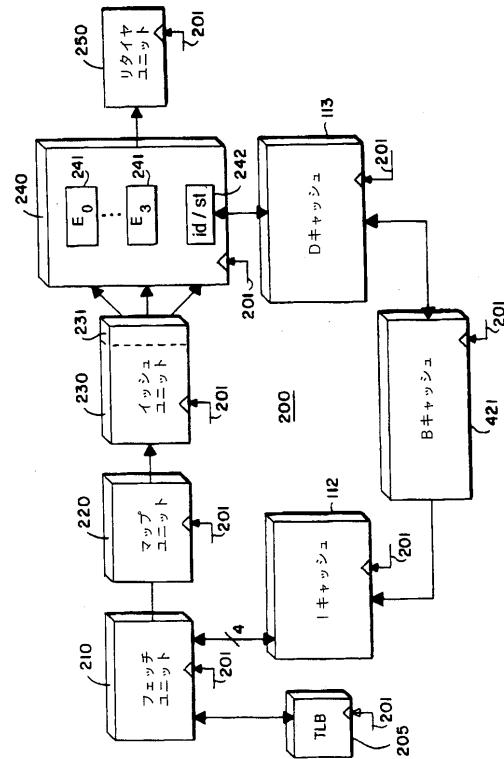

図2aは、図1の1つのプロセッサ110の実行パイプライン200を示すもので、これは、例えば、フェッチ、マップ、イッシュ、実行及びリタイアユニット、各々、210、220、230、240及び250としてシリアルに構成された複数の段を有する。パイプライン200が情報(データ及び命令)を処理するレートは、ライン201上のシステムクロック信号、即ちいわゆるクロック「サイクル」により制御される。

各クロックサイクルは、パイプライン200の段が個々の量の処理を実行できるときの「スロット」即ち時間間隔を定義する。処理スロットは、通常、順方向命令を搬送し、そして以下に述べる実行ユニットの場合は、以下一般に「データ項目」と称するデータを搬送

50

する。例えば、分岐予想ミス又はキャッシュミス或いはパイプラインストールのような場合には、クロックはサイクルを続けるが、有意義な命令は順方向に送られない。

#### 【0034】

1つの効果として、本発明の装置及び方法は、「廃物(garbage)」即ち非有効データを搬送するプロセッサスロットに関する状態情報をサンプリングすることができる。これらは、「浪費(wasted)」スロットとして知られている。浪費スロットを識別しそしてサンプリングすることは、タスクを最適化するための重要な先駆手段である。というのは、浪費スロットは、有効に機能せず、従って、システム性能を低下するからである。それ故、一般に、ここでサンプリングされるものは、公知技術のように単なる「事象」又は「命令」ではなく、プロセッサスロットが有効な命令に関連したものであるか無効の命令に関連したものであるかに関わりなくパイプライン200を経てプロセッサスロットをプッシュすることに関連した状態情報をである。10

#### 【0035】

##### フェッчуニット

Bキャッシュ121は、データ項目を各々Iキャッシュ112及びDキャッシュ113に転送する。フェッчуニット210は、仮想アドレスを物理的アドレスへと解析するためのある形式の変換ルックアサイドバッファ(TLB)205を使用して、実行されるべき次の命令をIキャッシュ112からフェッチする。Iキャッシュ112からフェッチされる項目は、一般的に、実行可能な命令である。しかしながら、これらは、Iキャッシュが「廃物」データ即ち非命令をミスする場合のように、無効命令でもよい。20

単一のプロセッササイクル中に「命令」のセットがフェッチされるのが好ましい。このセットは、例えば、4つの命令を含むことができる。換言すれば、パイプライン200は、4スロット巾である。スロットの数は、使用可能な実行ユニットの数に基づく。他の形式のプロセッサは、單一プロセッササイクル中により少數の又はより多数の命令をフェッチすることができる。一般に、これは、各サイクルがキャッシュから4つの処理スロットを満たすことを意味する。あるスロットは、Iキャッシュ112が使用可能なデータをもたないときに浪費される。全ての処理を休止、停止するのではなく、スロットはいかなる場合にも順方向に搬送されて、サンプリングの目的で使用できるようにされるが、スロットの廃物「命令」は、実行のために発生されることがない。

フェッチ中に、選択された命令は、サンプリング又はシステムプロファイリングを許すために付加的な情報で増強することができる。増強命令は、図4を参照して以下に説明する。他の実施においては、選択された命令の増強が、イッシュユーニット230を含むプロセッサのいかなる段でも実行できることに注意されたい。30

#### 【0036】

##### マップユニット

システム100では、パイプライン200の次の段のマップユニット220を用いて命令のオペランドが物理的レジスタに動的に指定又は「マップ」される。マップユニットは、物理的レジスタをアーキテクチャー即ち「仮想」レジスタに指定する。換言すれば、仮想レジスタと物理的レジスタとの間には1対1の対応がなくてもよい。

#### 【0037】

##### イッシュユーニット

次の段において、フェッチされた命令は、イッシュユーニット230によって順序付けされる。イッシュユーニット230は、実行されるべき次の命令のための待ち行列ヘッド(a head-of-the-queue)エントリ231を有するイッシュー待ち行列を備えている。命令に必要なリソースが使用できないために、イッシュユーニット230の1つ以上の命令がストールされ得ることに注意されたい。それ故、ストールされた命令の「周り」で待ち行列230から他の保留中命令が順序ずれして発生される。正しい実行順序は、以下に述べるリタイアユニット250で確認される。

#### 【0038】

##### 実行ユニット

10

20

30

40

50

命令は、機能的実行ユニット( E 0 . . . E 3 ) 2 4 1 及び l d / s t ユニット 2 4 2 へ発生される。実行ユニット 2 4 1 の各々は、特定形式のオペレータコード( o p コード)、例えば、整数及び浮動小数点演算、分岐及びジャンプ命令等で命令を取り扱うように設計される。l d / s t ユニット 2 4 2 は、メモリアクセス命令を実行し、例えば、D キャッシュ 1 1 3 に対してデータをロード及び記憶する。l d / s t ユニット 2 4 2 は、長い遅延を経験するために特別に識別される。又、長い待ち時間を伴うメモリアクセス命令は、スループットを改善するために、データがプロセッサに送り込まれるかなり前に「完了」となる。

#### 【 0 0 3 9 】

##### リタイアユニット

10

命令の実行の終了は、リタイアユニット 2 5 0 により処理される。リタイアユニット 2 5 0 は、処理状態をコミットする。ある命令は、アボートするか、又はトランプされることに注意されたい。例えば、実行流は、命令がフェッチされた後に変化するか、又は命令は、例外トランプを被ることがある。このような場合に、パイプラインに既にある命令及び全ての後続命令は破棄され、そして推測的処理状態がロールバックされる。ここでの 1 つの効果として、破棄又は「アボート」された命令も、浪費プロセッサスロットと同様にプロファイリングされる。換言すれば、終了とは、完全に実行された有効命令をリタイアし、部分的に実行された有効命令を後処理し、或いは無効命令又は浪費スロットを破棄することを意味する。

#### 【 0 0 4 0 】

20

本発明の技術の根底にある基本的な考え方は、パイプライン 2 0 0 の段を経て進むときには、選択された「スロット」、主として命令において「データ項目」の処理を行うものである。プロファイリングハードウェアは、詳細な状態情報を動的に収集する。状態情報は、いずれのパイプライン段からでも又はシステム 1 0 0 のどこからでも到来することができる、例えば、第 1 及び第 2 レベルキャッシュ又は他のサブシステムから到来することができる。状態情報は、特定事象に直接起因し得る。

ここでの設計戦略は、プロファイル記録において静的に決定することが困難な情報を収集することである。これは、プロファイル記録を性能ツールとして又はプロファイルで指令される最適化として有用なものにするか、或いはサンプリング及び分析に直接応答する動的な調整を含むオペレーティングシステム及びアプリケーションレベルソフトウェアにおけるリソース割り当てポリシー判断を行う上で有用なものにする。本発明の方法及び装置は、実際の機能的システムにおいて作用するよう設計されることを想起されたい。

30

#### 【 0 0 4 1 】

プロファイル記録の一部分としてセーブするのにどんな状態情報に关心があるかを決定するために、図 2 b に示すように、近代的なアウトオブオーダーマイクロプロセッサのパイプライン 2 0 0 の種々の段に理論的に得られる情報を検査することが有用である。

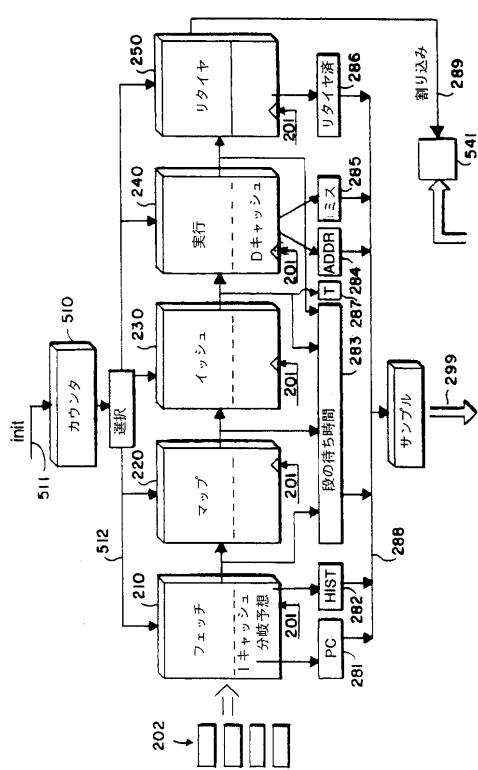

図 2 b に示すように、パイプラインの段は、フェッチ 2 1 0 、マップ 2 2 0 、イッシュ 2 3 0 、実行 2 4 0 及びリタイア 2 5 0 である。これらの段のいずれかの間に、特定の実施形態に基づき、パイプライン 2 0 0 で処理されるいずれかの「フライト中」命令 2 0 2 をライン 5 1 2 によりサンプリングのために選択することができる。この選択は、カウンタ 5 1 0 の値により制御される。カウンタの値は、ライン( i n i t )により初期化することができる。

40

#### 【 0 0 4 2 】

命令アドレス( P C ) 2 8 1 、分岐経過ビット( H I S T ) 2 8 2 、段の待ち時間 2 8 3 、分岐実行指示( T ) 2 8 7 、データアドレス( A D D R ) 2 8 4 、データミス( M I S S ) 2 8 5 及びリタイア状態 2 8 6 のような状態情報は、ライン 2 8 8 においてサンプリングすることができる。選択された命令の処理が終了すると、ライン 2 8 9 に割り込み信号を発生することができる。割り込み信号 2 8 9 は、ソフトウェアでライン 2 9 9 を経て状態情報 2 8 1 - 2 8 6 をサンプリングすることができるようになる。或いは又、ソフトウェアは、内部プロセッサレジスタ 5 4 1 を経てライン 2 8 9 をポーリングすることもで

50

きる。

#### 【0043】

##### スーパースカラーのアウトオブオーダープロセッサーキテクチャー

アウトオブオーダー実行プロセッサは、正しい順序で命令をフェッチ及びリタイアするが、それらのデータ依存性に基づいて命令を実行する。命令は、それがフェッチされたときから、それが終了するまで、例えば、リタイア又はアボートするまで、「フライト中」であると言える。命令は、マッピングの後、イッシュユニット230に入れられ、そして入力オペランドを保持するレジスタが更新されるまでそこで待機する。

#### 【0044】

各プロセッササイクルごとに、フェッチユニット210は、命令キャッシュ112から命令のセットをフェッチしてデコードする。フェッチユニット210の一部分である命令デコーダは、フェッチされたセットの中のどの命令が命令流の一部分であるかを識別する。フェッチすべき次の命令のプログラムカウンタ（PC）を分析するには多数のサイクルを必要とするので、次のPCは、フェッチユニット210の一部分である分岐又はジャンブルディクタにより予想される。予想が間違っている場合には、プロセッサは、その予想ミスした命令、即ち「不良」経路においてフェッチされた命令をアボートし、そして「良好」経路においてフェッチ命令を再スタートする。

命令を順序ずれして実行できるようにするために、レジスタはマップユニット220により動的に名前が付け直され、「読み取り後の書き込み」及び「書き込み後の書き込み」競合を防止する。同じ仮想レジスタに書き込む2つの命令は、順序ずれ状態で安全に実行することができる。というのは、それらは、異なる物理的レジスタに書き込みするのであり、そして仮想レジスタの消費者が適切な値を得るからである。命令は、正しい順序でフェッチされ、マップされそしてリタイアされるが、順序ずれ状態で実行することができる。

#### 【0045】

レジスタマップユニット220は、フェッチされた命令のオペランドを有効な物理的レジスタに指定する。即ち、レジスタオペランドの仮想名は、プロセッサの物理的なレジスタスペースに対して名前付けし直される。次いで、命令は命令待ち行列230へ送られ、そこで、実行の前に2つの事象を待機する。第1に、それらのレジスタ依存性を分析しなければならない。第2に、命令に必要なリソース、例えば、実行ユニット、レジスタ、キャッシュポート、メモリ待ち行列等が使用できねばならない。これは、現在マップされたいとなる命令に対しても、必要なリソースを再割り当てできないことを意味する。

ある命令に対してこれら2つの条件が満たされると、命令オペランドが物理的レジスタファイルにおいて探索される。次いで、オペランドレジスタの内容及び命令に関するある情報が適当な実行ユニット240へ送られて実行される。命令が実行を終了し、そして命令がプロセッサにおいて最も古い「非リタイア」命令であるときに、命令がリタイアする。これは、命令により使用されるリソース、例えば、物理的レジスタ及びキャッシュポートを解放する。

#### 【0046】

多数の事象が命令の実行を遅延せることがある。パイプラインの前方では、フェッチユニット210がIキャッシュ112のミスによりストールするか又はフェッチユニット210が予想ミス経路の命令をフェッチすることがある。マップユニット220は、空きの物理的レジスタの欠乏、又はイッシュユニット230における空きスロットの欠乏によりストールすることがある。

イッシュユニット230における命令は、それらのレジスタ依存性が満足されるのを待機するか、又は実行ユニット240が使用できるのを待機する。命令は、Dキャッシュにおけるミスによりストールすることがある。命令は、それらが不良経路に沿って推測的に発生されるか、又はプロセッサが不法なオペレーション又はメモリアドレスのような割り込みを行ったためにトラップされることがある。これら条件の多くは、コンパイル時に予想することが困難であり、それらは全てシステム100の性能を低下させる。これにより、ライン288に得られる情報をサンプリングすることが重要となる。

10

20

30

40

50

## 【0047】

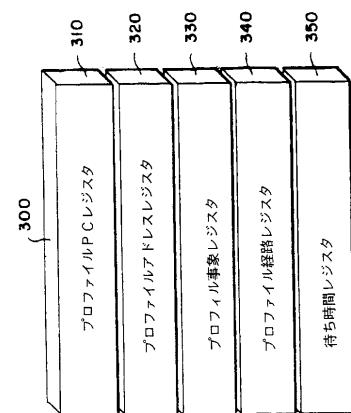

プロファイル情報レジスタ

それ故、図3に示すように、サンプリングされる各命令ごとにプロファイル情報を記憶するためのメモリ300が設けられる。メモリ300は、レジスタファイル又はバッファの形態でよい。換言すれば、サンプリングされる選択済み命令は、レジスタファイル300で直接識別される。レジスタファイル300は、複数のレジスタを含むことができる。或いは又、ファイル300は、多数のフィールドをもつ単一のインデックス可能なレジスタとして実施することができる。

ファイル300は、図2bのライン288によりパイプライン200の要素に接続され、従って、選択された命令に関連した性能情報をパイプライン200の各段に対して捕獲することができる。プロファイルレジスタ300は、公知技術で見られる単純な「事象」カウンタ以上のものであり、ここでは、これらレジスタは、特定の既知の命令及び事象に起因する性能情報を収集することに注意されたい。10

## 【0048】

図3において、各レジスタに対して割り当てられるビットの数は、そこに記憶される情報の形式、例えば、命令アドレス(64ビット)、サイクルカウント、即ち待ち時間(8又は10ビット)、個別事象(1ビット/事象)等々に依存している。これらの数は単なる指針に過ぎない。他の実施形態は、種々のレジスタ300に対して異なるビット数を使用することができ、これは設計上の選択肢である。

好ましい実施形態では、プロファイルPCレジスタ310は、選択された命令のPCを記憶する。以下に述べるように、プロファイリングされている命令は、アサートされた「プロファイル」ビットを有する。又、PCレジスタ310は、選択された命令のopコードを含むこともできる。更に、マルチスレッド式実行を許すプロセッサについては、レジスタ310の付加的なビットがスレッドの識別子を記憶することができる。レジスタ310の他のフィールドは、プロセス識別子、アドレススペース番号、CPU番号、及び実行されている命令の命令番号(inum)を記憶することができる。更に、多数の論理レジスタセット、即ちハードウェアコンテクスト及び同時実行スレッドを有するプロセッサでは、レジスタ310がハードウェアコンテクスト及びスレッド識別子である。この情報を記憶することにより、プロファイル情報を特定の命令に直接起因させることができる。更に、サンプリングされた情報は、アドレスの範囲、opコード、実行スレッド、アドレススペース、等々に基づいてフィルタすることができます。20

## 【0049】

プロファイル有効アドレスレジスタ320には、選択された命令に関連したアドレスがロードされる。命令がロード又は記憶のようなメモリアクセス命令である場合には、有効な64ビット仮想メモリアドレスが捕獲される。命令がジャンプ又は分岐である場合には、ターゲットPCが記録される。

本発明のサンプリング技術の1つの効果として、パイプライン200によって処理される全ての「命令」は、サンプリングレートに関わりなく、サンプリングのために選択される確率が等しい。命令は、有効な命令、無効の命令、非割り込み命令、又は「廃物」命令である。従って、捕獲された有効アドレスは、プログラムの全体的な振る舞いを統計学的に表す。サンプリングされた命令の有効アドレスを捕獲することにより、メモリアクセス及び実行流を、実際の動的な実行に正確に関連付けることができる。40

## 【0050】

プロファイル事象カウンタ330は、例えば、1ビットフィールドに区画化される。1ビットフィールドは、選択された命令に対する事象を記録する。命令が最初に選択されるときに、レジスタがクリアされる。事象は、キャッシュミス、分岐予想ミス、リソース競合、トラップ及び例外条件、リタイア/アボート/無効、TLBミス、実行/非実行、データ依存性ストール、リソース依存性ストール、等々を含む。この実施形態では、多数の事象を单一の命令に起因させることができる。リタイア及びアボートの両命令に対して事象情報が収集されることに注意されたい。事象レジスタ330のサイズを減少するために、50

あるビットフィールドを使用して、命令の op コードに基づき異なる形式の相互に排他的な事象を記録することができる。

#### 【 0 0 5 1 】

プロファイル経路レジスタ 340 は、分岐経過テーブルから最近の分岐実行 / 非実行情報を捕獲するのに使用される。分岐経過テーブルは、他の用途に対して良く知られている。グローバルな分岐実行経過は、選択された命令をフェッチした実行経路を指示するのに使用できる。命令は、この情報を有効なものにするために分岐命令である必要はないことに注意されたい。経路情報の使用は、以下で詳細に説明する。

待ち時間レジスタ 350 は、選択された命令が、例えば、パイプライン 200 の種々の段間をフライト中である間に、チェックポイントにおいて得られたタイミング情報を記憶する。チェックポイントは、命令がストールされて、ある事象又はリソースを待機する場所に基づいて、プロセッサごとに異なる。各待ち時間レジスタ 350 は、2つのチェックポイント間で命令が費やすサイクル数をカウントする。

#### 【 0 0 5 2 】

選択された命令がチェックポイントを通過し、即ちパイプライン 200 の次の段に入るとときに、それに対応する待ち時間レジスタ 350 が最初にクリアされ、そして 1 サイクル当たり 1 回増加され、やがて、命令が次のチェックポイントを通過し、次の待ち時間レジスタが初期化されそしてカウントを開始する。待ち時間レジスタ 350 の数は、特定の実施形態におけるパイプライン 200 の段数に基づく。命令がアボート又はリタイアするときには、待ち時間レジスタ 350 に完全な待ち時間プロファイルが記憶される。

収集すべき潜在的に有用な待ち時間のリストは、フェッチ対マップ、マップ対データレディ、データレディ対実行、実行対リタイアレディ、リタイアレディ対リタイア遅延を含む。メモリ命令（ロード及び記憶）の場合、待ち時間は、イッシュ対完了である。この最後の待ち時間は、あるメモリオペレーションは、それらが作用するデータが実際にプロセッサに送られる前にリタイアの準備ができるという点で、他の待ち時間とは異なる。これらの待ち時間は、レジスタ 350 で直接カウントすることもできるし、或いはレジスタが生のサイクルカウントを収集することもでき、この場合に、プロファイルリングソフトウェアは、次々の段に対する生のカウント間の差を計算して、実際の待ち時間を決定する。例えば、パイプライン待ち時間クロックサイクルをカウントする回路は、図 6 を参照して以下に詳細に説明する。

#### 【 0 0 5 3 】

レジスタ 300 における情報の更新は、遅延が受け入れられた直後に行う必要はない。必要とされるのは、選択された命令が完了した（リタイア又はアボートした）ことを知らせる割り込みを、レジスタファイル 300 の全ての情報が更新されるまで遅延するか、或いは割り込みハンドラーを、プロファイルファイル 300 が更新されるまでストールできることだけである。

プロファイルレジスタファイル 300 を複写できることに注意されたい。プロファイルレジスタファイルの多数のコピーがある場合には、シリアルに又は同時にプロファイルリングするために多数の命令を選択することができる。この場合には、各選択された命令が、以下に述べるように、特定のレジスタファイルで明確に識別される。オーバーヘッドの量を減少するために单一の割り込み信号に応答して多数のレジスタファイルをサンプリングすることができる。

#### 【 0 0 5 4 】

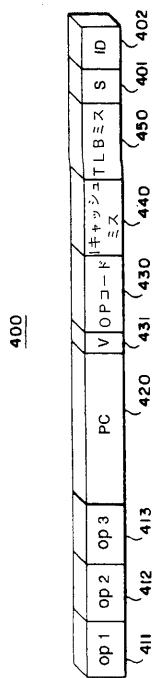

##### 増強命令

図 4 に示すように、各命令 400 はサンプルフィールドを含む。例えば、このサンプルフィールドは、「サンプル」ビット (S) 401 と称する 1 ビットタグである。サンプルビット 401 がアサートされると、サンプリングのために命令が選択される。ビット 401 をアサートすると、プロファイル情報を収集するサンプリングハードウェアが作動されると共に、選択された命令が完了した（リタイア又はアボートされた）ときに割り込みを生じさせる。或いは又、フェッチされた各「命令」を「ignum」値で連続的に番号付けす

10

20

30

40

50

ることもできる。この場合には、特定の *inum* 値をもつ命令を選択することができる。命令を選択するメカニズムについては、以下に述べる。

#### 【0055】

プロファイルレジスタファイル 300 は、フィールドが更新されそして割り込み信号が発生されたときに読み取ることができる。割り込み信号は、特権付きのプロファイリングソフトウェア (PSW) がプロファイルレジスタ 300 の内容を処理できるようにする。多数のサンプルが記録される場合には、単一の割り込みで、多数の選択された命令に対して性能データをサンプリングできることに注意されたい。

実施形態に基づき、増強命令 400 は、次の付加的なフィールド、即ち 3 つまでの命令オペランド (op1, op2 及び op3) 411 - 413 と、プログラムカウンタ (PC) 420 と、オペレータコード (op コード) 430 とを含むことができる。有効フィールド (V) 431 は、1 ビットフィールドを真又は偽にセットすることにより、選択されたスロットにおける「命令」が有効であるかどうか指示することができる。フィールド 440 及び 450 は、命令に関連したキャッシュ及び TLB ミスを各々指示するために指定することができる。単一の命令が多数のオペランドを含み得るので、その命令に対して多数のミスが考えられることに注意されたい。

#### 【0056】

##### プロファイルレジスタファイル ID

若干複雑な設計では、多数の命令を同時にプロファイルすることができる。この実施形態では、複数のレジスタファイル 300、或いはサブフィールドを伴う単一の大きなレジスタがあり、ファイル 300 の数は、同時にプロファイルすることのできるフライト中命令の数に対応する。このケースを取り扱うために、命令 400 は、サンプルレジスタファイル識別子 (ID) フィールド 402 も含むように増強される。これは、多数のレジスタファイル 300 の 1 つにプロファイル情報を直接リンクできるようになる。上記したように、ここでは、選択された命令とプロファイルレジスタとの間に直接的な関連がある。それ故、レジスタに収集されるプロファイル情報は、特定の命令に直接起因し得る。

一度に 1 つのフライト中命令しかプロファイリングされないときでも、ファイル即ちレジスタ 300 を ID フィールド 402 でインデックスして、プロファイリングソフトの割り込みハンドラーのコストを多数の命令サンプルにわたり償還できるようになるのが有用である。命令セット内の命令が選択された命令であるかどうかを決定することは、「ワイヤド OR」オペレーションを用いて行うことができる。

#### 【0057】

##### ランダムサンプリング

本発明のプロファイリングのオーバーヘッドは、同時にプロファイリングすることのできる命令の数を制限することにより減少され、例えば、ビット 401 がセットされる。プログラム又はプログラムの一部分において各命令をプロファイリングするのではなく、ここでは、プロファイリングされるべき命令が、プロセッサバイオペラント 200 の特定の段階中に、例えば、フェッチの間に選択され、そしてその選択された命令がサンプルビット 401 のアサートによりタグ付けされる。サンプルビット 401 がアサートされた場合には、バイオペラント 200 の要素がプロファイル情報をプロファイルレジスタファイル 300 へ送る。

ここに記載する命令レベルプロファイリングをサポートする詳細について以下に述べる。

#### 【0058】

##### フライト中状態

第 1 に、プロセッサバイオペラント 200 を通過する各デコードされた命令状態は、上記のように、付加的な情報で増強される。命令は、それがフェッチされたときから、それがリタイア又はアボートするときまで、フライト中であるとみなされる。上述したように、命令は、少なくとも 1 つのサンプルビット 401 で増強される。サンプルビット 401 は、各フライト中命令及びキャッシュ / メモリ要求の状態の一部分である。ビット 401 がアサートされると、このビットは、この命令に対してプロファイリング情報が記録されるこ

10

20

30

40

50

とを示し、さもなくば、記録されないことを示す。

#### 【0059】

簡単な設計においては、一度に1つのフライト中命令のみが、そのサンプルビット401をアサートすることが許される。サンプルビット401は、選択された命令に対し、その命令がリタイアするか又はアボートされるまで、アサートされたままとなる。多数のレジスタファイル300をもつ更に複雑な設計では、多数のフライト中命令を個々にプロファイリングすることができ、そして付加的なビットをアサートすることができる。

#### プロファイルされた命令の選択及びサンプリング

フェッチ段の実施について図5に示したように、プロファイリングされるべき命令の選択及びプロファイル情報のサンプリングは、次のように行われる。フェッチカウンタ510は、例えば、特権付きプロファイリングソフトウェア(PSW)520によりライン511を経て初期化される。PSW520は、所定サイズを有する値の間隔からランダムに選択された値でカウンタ510を初期化することができる。従って、サンプリングされた命令は、命令の実行における特定のパターンと相關しない。間隔のサイズは、サンプリングの平均頻度を決定する。カウンタ510の値を初期化するための他のランダム化技術(ハードウェアを含む)も使用できる。

#### 【0060】

例えば、公知技術の場合のように命令が固定頻度でサンプリングされるときのように、ランダムサンプリングが行われないと、例えば、システム100の収集オペレーションのように、フェッチされた全ての命令の統計学的に正しいプロファイルを発生することができない。これは、サンプリングレートに対して比較的重要でない多数の命令を含む実行ループを有する実行スレッド、例えば、命令を有しそしてサンプリング間隔が65536個の命令であるループに対して、特に言えることである。他の通常のサンプリングも同じ問題を有する。そこで、2つの命令の一方のみからのサンプルが常に収集される。1つの効果として、ランダムに選択された命令は、サンプリング間隔の長さとは独立した相関を発生する。各命令400がフェッチされるたびに、カウンタ510がパイプライン200のフェッチユニット210によりその初期値から増加されるか、或いは別の実施形態では、減少される。カウンタ510が、その実施形態に基づいて、オーバーフローするか又はアンダーフローしたときに、現在フェッチされた命令がそのサンプルビット401をアサートし、そしてIDフィールド402は、多数の命令がサンプリングのために選択されたときにも初期化することができる。

#### 【0061】

別の実施形態では、カウンタ510は、各命令がフェッチされるたびではなく各サイクルごとに増加され、例えば、カウンタ510は、フェッチの機会をカウントし、実際にフェッチされる命令をカウントするのではない。例えば、フェッチユニット210が各クロックサイクル中にIキャッシュ112から4つの項目をフェッチできる場合には、4つのフェッチ機会がある。Iキャッシュからの1つ以上のフェッチがミスとなるか又は「不良」命令をフェッチすることがある。ミスの場合には、ミスした命令に対して使用できるスロットが「廃物」を含み、命令を無効とマークすることが必要になる。不良命令は、不良の実行経路に存在するものであるか、又はさもなくば、アボートされる。

フェッチされた命令ではなくサイクルをカウントする場合には、設計を効果的に簡略化する。フェッチされた有効な命令のみをカウントする場合には、かなり複雑なものとなる。というのは、制御流が、フェッチされた命令のグループに向かって又はそこから分岐することができ、従って、全ての命令をデコードしてどれが有効であるかを決定することが必要となり、もはや、カウンタを4だけ増加するだけの簡単なことではなくなるからである。

#### 【0062】

1つの効果として、サイクル中にIキャッシュからフェッチされた全てのもの(良好な命令、不良の命令、廃物命令)をサンプリングのために選択し、Iキャッシュ112及びパイプライン200の真の性能を決定することができる。ここでは、バイアスはなく、従つ

10

20

30

40

50

て、システム性能の統計学的に正しい推定値が得られる。

これは、短い固定の時間周期中に又は離間された固定の間隔で各有効な命令のみを選択する既知の技術とは区別されるものである。何れの場合にも、オーバーヘッドを最小にすることが戦略である。システム全体の性能データを捕獲することのできる技術はない。

#### 【0063】

##### 命令のフィルタ動作

選択されたものは、フィルタ505によりフィルタすることができる。フィルタ動作は、命令opコード、オペランド、或いは例えば、ある時間周期内で第1形式の命令の後に別の形式の命令が続くといったより複雑なフィルタ基準に基づいて行うことができる。パイプライン200への入力においてフィルタ動作を行う場合には、カウンタ510をリセットすることができる。これを行う方法は、多数ある。1つの方法では、カウンタ510の現在初期値が初期値(init)レジスタ513に記憶される。命令がフィルタされるときには、初期値レジスタ513に記憶された値がカウンタ510に再ロードされ、初期のランダム化選択が想起される。

10

#### 【0064】

命令が増強された後に、パイプライン200は、図2bのプロファイル情報281-286をレジスタファイル300(1つ又は複数)に供給する。リタイアユニット250は、命令の完了又はアボートに応答して、プロファイル情報をファイリングを完了し、そしてライン540に割り込み信号を発生して、PSW520がプロファイル情報をサンプリングできるようにする。

20

或いは、PSW520は、内部プロセッサレジスタ又はメモリ位置(541)を経てライン540をポーリングすることもできる。本発明の技術の1つの特徴として、公知のあるプロファイル技術とは対照的に、たとえ本発明の技術がプロセッサにわたる状態に関する正確な情報を与えるものであっても、プロセッサのサイクルタイムに何ら影響を与えない。唯一の時間制約は、プロファイルレジスタ300がサンプリングされる前に全てのプロファイル情報を記録しなければならないことである。

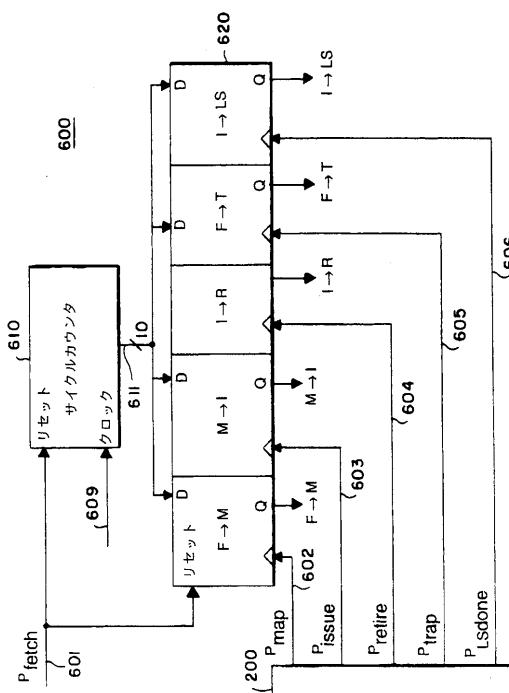

#### 【0065】

##### 待ち時間カウンタ

図6は、例示的な待ち時間、フェッチ対マップ(FM)、マップ対イッシュ(MI)、イッシュ対リタイア(IR)、フェッチ対トラップ(FT)、及びイッシュ対1dst(ILS)をカウントするための回路600を示す。この回路600は、ライン611によりラッチ620に接続されたサイクルカウンタ610を備えている。

30

サイクルカウンタ610及びラッチ620は、ライン601上の信号Pfetchnにより初期化される。この信号は、プロファイルリングされるべき命令がフェッチされるときに発生され、例えば、サンプルビット401から導出される信号である。カウンタ610は、ライン609のクロック信号により増加される。各クロック信号は、1つのプロセッササイクルに対応する。

#### 【0066】

命令400がパイプライン200の段を経て進行するときに、パイプライン200の段遷移がライン602-606の信号、各々、Pmap、Pissue、Pretire、Ptrap及びPLSdoneをトリガーする。対応するラッチ620は、図3のプロファイル待ち時間レジスタ(又はフィールド)350に記憶するためにライン612-616において読み取ることができる。

40

#### 【0067】

##### プロファイルリングアプリケーション

上記のプロファイルリングハードウェアは、種々の異なる方法で使用することができる。本発明の技術は、個々の命令の実行に関する非常に詳細な情報を与えるので、1つのアプリケーションで非常に多数の命令をプロファイルリングすることができる。サンプル情報はメモリバッファに記憶され、プロファイルリングツールにより後で処理されて、詳細な命令レベル情報を形成することができる。

50

この情報は、例えば、各ロード命令に対するロード待ち時間のヒストグラム、命令実行時間のヒストグラム、及びおそらくは各命令に対するパイプライン状態の適度に包括的な分析を発生するのに使用できる。この解決策により与えられる情報の量は、おそらく、かなり多くなるので、本発明の技術の全メモリオーバーヘッドも、相当の量のメモリトラフィックが含まれるために、かなり大きなものとなる。例えば、1秒当たり10億の命令がフェッチされ、そして各1万のフェッチされる命令ごとにサンプリングが実行される場合には、プロファイル情報のデータレートが1秒当たり約2.4MBとなる。

以下、プロファイル情報を収集することにより帯域幅を減少するためのソフトウェア実施方法について説明する。

#### 【0068】

10

##### 出力プロファイル情報をフィルタすることによるデータの減少

サンプリングされるデータの量は、プロファイル記録のあるフィールド、例えば、プロファイルレジスタ300のデータを、それらが明確に要求されるときを除いて、無視することにより、減少することができる。システム100のユーザは、異なるレベルのプロファイリングを望むことがある。最低のオーバーヘッドモードでは、プロファイリングアプリケーションソフトウェアは、PC及びリタイア-遅延フィールドのみを用いてプログラムの全部又は一部分に対してプロファイルレポートを発生することができる。実行されるべき最適化に基づき、平均化又は他の統計学的メトリック、例えば、最小、最大又は標準偏差の計算により他のPCごとの(per-PC)値を要約することができる。データを処理するための更なる時間が与えられると、プロファイリングアプリケーションは、種々の命令待ち時間のヒストグラムを形成することができる。

20

#### 【0069】

有効なメモリアドレス、分岐ターゲットアドレス及び分岐経過サンプルは、おそらく、他のフィールドよりも経費のかかる処理を必要とする。これらのフィールドは、おそらく、特定の最適化タスクを実行するためにデータを収集するとき以外は無視することができる。命令と命令との間の命令間フェッチ距離がサイクルで与えられると、プロファイリングアプリケーションは、同時性のレベルに関する情報も収集することができる。

又、プロファイリング情報のフィルタ動作は、例えば、マスクレジスタ又はプログラマブルロジックのようなハードウェア手段により行うこともできる。例えば、キャッシュミスがあったとき又は命令がリタイアしたときにのみサンプリングするか、或いはopコード、オペランド、アドレス、事象及び待ち時間の他のブール組合せのみをサンプリングする。

30

#### 【0070】

##### ハードウェアオペレーションの決定

本発明のプロファイリング技術は、Alphab1264プロセッサのようなアウトオブオーダーイッシュユニットプロセッサの内部動作の正確な理解を得るために使用することができる。この形式のマシン編成に関して注目すべき第1の事柄の1つは、パイプライン200において命令がストールする場所が多数ありそしてストールする理由が非常に多数あることである。

例えば、ある命令は、イッシュユニット230においてストールすることがある。というのは、そのオペランドの幾つかがデータレディでなく、選択された命令の実行に必要なリソースの幾つかが使用できず、又はその命令に先立って他の命令が実行されるべく選択されるからである。

40

#### 【0071】

ある命令は、仮想-物理的レジスタマッピングを行うマップ段においてストールすることがある。というのは、マシンが物理的レジスタからのものであり、フライト中の命令が非常に多数あり、或いはイッシュユニット230がいっぱいである(実行されようとしている命令を入れる場所がないことを意味する)ためである。或いは又、ある命令は、リタイアユニットにおいてストールすることがある。というのは、プログラム順に既にイッシュされた命令がまだ完了していないからである。

50

命令がどこでストールされたか、なぜストールされたかそしてどれほどの時間ストールされたかを正確に決定することは、主に、その命令が実行されるときのマシンの正確な状態によって左右される。プロセッサがこのように動的であるために、ソフトウェア性能ツールでこの状態を静的に決定することは困難である。

#### 【0072】

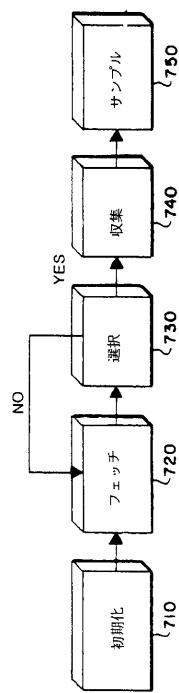

##### オペレーションの概要

図7aに示すように、プロファイリング方法700は、次のステップを含むことができる。プロファイリング状態は、ステップ710において初期化される。ここで、レジスタがクリアされ、そしてカウンタに初期値が指定される。ステップ720において、命令がフェッチされそしてカウントされる。ステップ730において、初期化以来フェッチされた命令の数が所定のランダム数に等しいときに命令が選択される。選択された命令は、その選択を指示するよう増強される。10

選択された命令が実行パイプライン200を経て進むときに、ステップ740においてプロファイル情報が収集される。完了（リタイア又はアボート）時に、収集された情報がステップ740においてサンプリングされる。サンプリングされた情報は、その後の処理のためにバッファすることができる。又、特定のプロファイリング状態をサンプリングし、より詳細な情報を抽出することもできる。

#### 【0073】

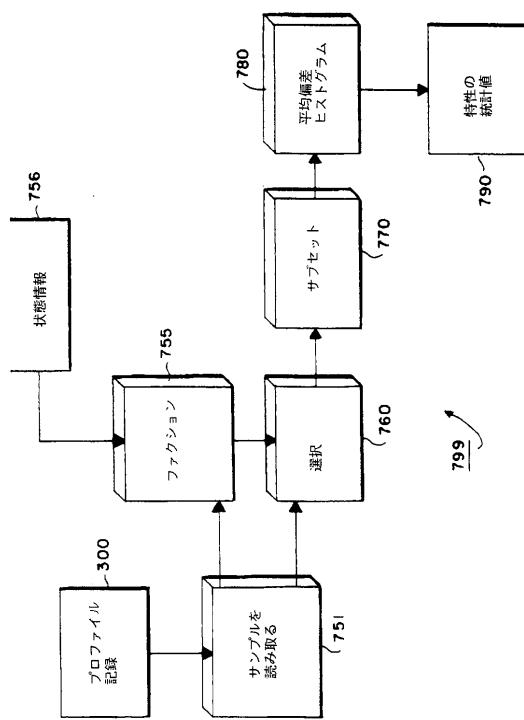

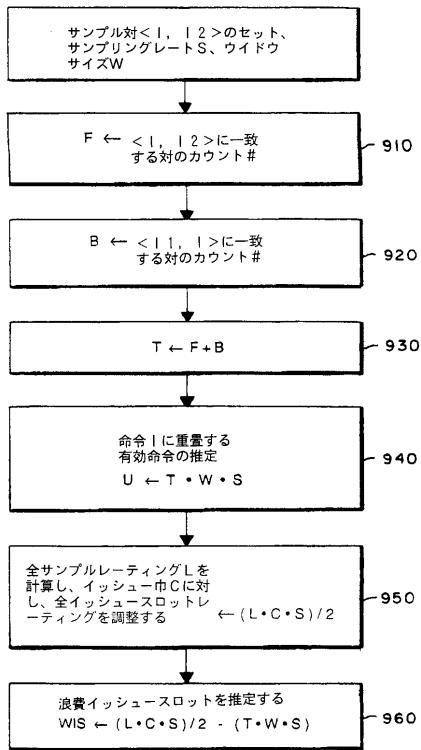

##### 処理された命令の特性の統計値の推定

図7bに示されたように、プロセス799は、パイpline200により処理される命令の特性の統計値を推定する。プロセス799は、次のステップを含むことができる。ステップ751は、ステップ750において上記したようにサンプリングされたプロファイル記録300を読み取る。記録は、選択された命令が完了したときに読み取られる。ステップ760において、サンプルは、システムの状態情報を考慮するファンクション755に基づいて選択又は破棄される。20

例えば、ファンクション755は、選択された命令のアドレス、プロセス識別子、アドレススペース番号、ハードウェアコンテクスト識別子、又はスレッド識別子のような状態情報756を入力として得る。又、ファンクション755は、経路識別情報、opコード、オペランド、待ち時間、又は選択された命令により経験する事象のような状態情報も使用することができる。事象情報は、リタイア／アボート／無効状態、キャッシュヒット／ミス、分岐予想ミス、トラップ状態TLBヒット／ミス、及びデータリソース依存性状態、等々である。30

#### 【0074】

ステップ760は、ファンクション755に基づいてサンプルのサブセットを発生する。ステップ780において、統計値790が決定される。これら統計値は、サンプリングされた命令の特性の平均値、標準偏差、ヒストグラム（分布）及びエラー限界を含むことができる。例えば、特定の事象が発生する平均レートや、命令実行の平均待ち時間や、メモリアクセスがある。又、プロセス、スレッド又はハードウェアコンテクストの実行レートの平均値も決定できる。ヒストグラムは、命令実行、メモリアクセスレート又は待ち時間のような分布を示すことができる。40

エラーの限界は、サンプリングされている特定の特性に対してサンプルの数の平方根の逆数で近似することができる。

#### 【0075】

##### N個ごとのサンプリング

ここに開示するプロファイリング技術は、N個ごとの(N-wise)サンプリングを実行するのにも使用できる。ここで、多数の同時実行命令間の相互作用の動的な状態を捕獲することができる。単一のフライト中命令をプロファイリングするのではなく、2つ以上の個別の命令が同時にプロファイリングされる。選択された命令間の動的な「距離」は、フェッチされた命令の数、又はフライト中の命令を「分離」するプロセッササイクルの数として測定することができる。カウンタ510によりカウントされる事象のいずれかを用いて、選50

択された命令間の距離、例えば、クロックサイクル、フェッチされた命令等を測定することができる。

N個ごとのサンプリングされた命令に対するプロファイル情報は、多数の考えられる用途を有する。第1に、情報を分析して、有用な同時性レベルを測定することができる。これは、真のボトルネックを探索できるようにする。真のボトルネックは、長いストールが低い同時性で結合されることを特徴とする。又、N個ごとのサンプルは、経路のプロファイリングを容易にすると共に、経路に沿った少なくとも2つのポイントを含むように経路を制限することにより実行経路候補を明確化することができる。更に、N個ごとのサンプリングから、詳細なプロセッサパイプライン状態を統計学的に再構成することもできる。ここで、命令のグループの選択は、命令間のある類似性の尺度、例えば、最近の分岐経過、ストール、命令形式、又は他の最近の状態経過をベースとすることができます。10

#### 【0076】

##### 有効な同時性の測定

アウトオブオーダープロセッサにおいて性能のボトルネックを正確に位置決めするには、ストール時間及び同時性レベルの両方に関する詳細な情報を必要とする。インオーダープロセッサとは対照的に、長い待ち時間の命令がストールされる間にプロセッサを効率的に利用するに充分な同時性があるときには、長い待ち時間の命令が問題とならない。

同時性情報を得るための1つの解決策は、全パイプライン状態のスナップショットを得ることである。これは、同時実行命令のセットが所与の時点でパイプラインの段のどこにあるかを直接的に露呈する。しかしながら、全パイプラインの状態をサンプリングレジスタ及びバッファに「ダンプ」することは、時間及びスペースの両面で非常に経費がかかる。更に、発生される多量のデータは、おそらく、サンプリングのコストを償還するように効率的に収集することができない。更に悪いことに、この解決策は、リタイアする命令しか「有効」としてカウントされず、そしてフェッチされた命令がアボートするところの情報がまだ分からないので、実際上不充分である。20

#### 【0077】

##### ネスト状の対ごとのサンプリング

N個ごとのサンプリングの1つの形式は、単一命令プロファイリングと全パイプラインスナップショットとの間の妥協を最小にする。ここで、統計学的な対ごとの(pair-wise)サンプリングがネスト状に行われ、所与の選択された命令に対して、同時に実行し得る別の命令が直接サンプリングされる。30

##### ネスト状のN個ごとのサンプリングに対するハードウェアサポート

N個ごとのサンプリングは、次のハードウェア特徴を含む。第1に、ハードウェアは、少なくとも2つの同時フライト中命令に対しプロファイル情報を捕獲できねばならない。プロファイルレジスタのセットは、プロファイル記録の多数の個別のセットをサポートするために複写されねばならず、そして單一サンプルビット401は、より一般的なIDフィールド402へと増強されねばならない。第2に、ハードウェアは、サンプリングレートの変更により、選択された命令間の距離を動的に変更できねばならない。これは、ハードウェア又はソフトウェアによって行うことができる。同時サンプリング命令(N個ごと、但しN>1)のセットのサイズは、カウンタ及びレジスタの付加的な複写でより大きくすることができる。40

#### 【0078】

例えば、特権付きプロファイリングソフトウェア520は、対ごとのケースでは2つのフェッチカウンタ510の初期値がランダムに選択されるところの間隔のサイズを動的に変更することができる。これは、一対の命令に対するサンプル間フェッチ距離を同時に特定できるようにする。ハードウェアは、ソフトウェアレベルでの最大の融通性を得るために比較的大きなサンプル間フェッチ距離をサポートすることができる。

第2のフェッチカウンタがコアフェッチ命令カウンタ510と同じサイズであって、充分な距離に離れた2つの独立した命令を選択できるのが理想的である。Alpha21264プロセッサの場合には10ビットカウンタで充分である。フェッチ命令をカウントする50

ときに同時性を測定するには、それより小さなカウンタで充分であり、サイクルがカウントされる場合には、それより大きなカウンタが必要とされる。ネスト状のN個ごとのサンプリングについては、ハードウェアは、サンプル間フェッチ・対・フェッチ待ち時間もサイクルで測定して、多数の待ち時間レジスタ350を時間的に相関させねばならない。

#### 【0079】

##### ネスト状のN個ごとのサンプリングアプリケーション

高レベルアプリケーションソフトウェアは、ネスト状のN個ごとのサンプリングを用いて、有効な同時性を測定することができる。ここでの重要な考え方は、潜在的に同時に実行し得る命令セットのサンプリングを許すことである。ネスト状のサンプリングは、通常のサンプリングを正当化する同じ統計学的引数に基づくもので、即ちサンプリングが繰り返し適用される。N個ごとのサンプリングは2つのサンプリングレベルを含むので、著しく実行されるコードについては最も効果的である。明らかに、これは、最も重要なところもある。

10

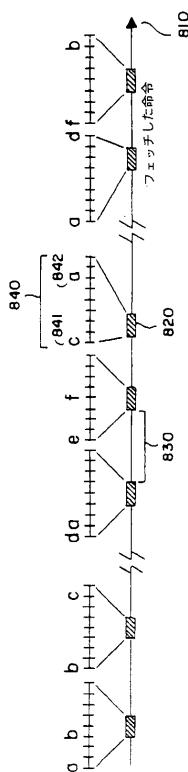

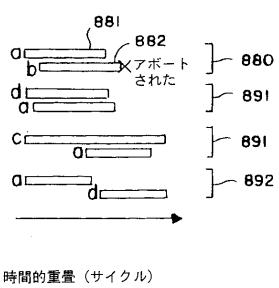

##### 定義された同時性

図8に示すように、4巾のパイプラインにおける所与の選択された命令I(810)に対し、潜在的に同時の命令とは、ある動的な実行中に命令Iと共にプロセッサパイプライン200に共存する命令である。これは、命令Iがフェッチされる前に種々の実行段に存在する命令と、命令Iがリタイア又はアボートされる前にフェッチされる命令とを含む。

#### 【0080】

20

例えば、Alphab21264プロセッサは、80個のライト中命令を許すものである。しかしながら、実際には、同時即ちライト中命令の実数は、おそらく、ハードウェアでサポートされるピーク値より相当に小さい。他方、予想ミス又は不良経路に沿った推測的実行は、潜在的同時性のウインドウを増加することができる。

Alphab21264プロセッサにおいて同時性を検討するために、命令I(810)の周りのウインドウW820の適度なサイズが約100個の命令を含まねばならないことが提案された。他の実施形態については、ウインドウの適当なサイズを実験で決定することができる。

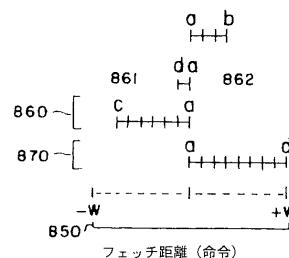

例えば、約100個の潜在的な同時命令であるサイズWのウインドウが与えられると、選択される命令間のフェッチ距離をランダム化することにより非バイアスのサンプリングを行うことができる。例えば、対ごとの各サンプル<I1, I2>(831及び832)に対し、サンプル間フェッチ距離は、1とWとの間に均一に分布した擬似ランダム数にセットされる。このように、第1の選択された命令I1と第2の選択された命令I2との間でサンプル間距離をランダムに変更すると、命令が実際に時間的に重畳するところの多量の統計学的情報が捕獲される。

30

#### 【0081】

##### 同時重畠の分析

種々のサンプル間フェッチ距離をもつ同時選択される命令のセットに対するプロファイル情報は、有効な同時性統計値を直接的に表す。対応するサンプル情報の各セットを使用し、第1命令I1から時間的に前方にそして第2命令I2から時間的に後方に見ることにより同時性情報を決定することができる。

40

各N個ごとの選択された命令に対して記録されるプロファイル情報は、両命令<I1, I2>が所与の時間にプロセッサパイプライン200に存在するようなインスタンスを正確に考慮する待ち時間を含まねばならない。更に、待ち時間レジスタのセットを相関させるためには、サンプル間フェッチ待ち行列が記録されねばならない。又、ネスト状のプロファイリングは、放棄した実行経路において命令<I1, I2>が完了したときを指示することもできる。この詳細な情報を統計学的に収集して、有効な同時性レベルを反映する種々のメトリックを形成することができる。

#### 【0082】

##### 浪費イッシュースロットの測定

50

種々のサンプル間フェッチ距離をもつ対ごとの命令サンプル< I 1、 I 2 >の収集は、有効な同時性統計値を直接的に表す。対ごとの各サンプルを使用して、第1命令から時間的に前方にそして第2命令から時間的に後方に見ることにより同時性情報を計算する。命令Iの後にフェッチされた命令に対する性能情報を測定するために、< I 1、 I 2 >の形態の対を考える。命令Iの前にフェッチされた命令に対する性能を測定するために、< I 1、 I >の形態のサンプルされた対を考える。

対ごとの各サンプル< I 1、 I 2 >に対して記録されるプロファイルデータは、待ち時間レジスタ350に記憶される値であって、各時点にプロセッサバイオライン200のどこにI 1及びI 2があるかを指示する値と、2セットの待ち時間レジスタ350を相関させることのできるサンプル間フェッチ待ち時間とを含む。又、プロファイル記録は、対< I 1、 I 2 >がリタイアするかどうかも指示する。

10

#### 【0083】

この詳細な情報を統計学的に収集して、有効な同時性レベルを反映する種々のメトリックを形成することができる。例えば、命令Iに対する1つの関心のある同時性の尺度は、Iがフライト中である間に浪費したイッシュースロットの平均数である。

浪費したイッシュースロットの数は、図9に示すように決定できる。I及びI 2がリタイアするような形式< I 1、 I 2 >のサンプルの数をF 1とし、サンプルと共に記録される待ち時間は、I及びI 2の実行が重畠することを指示する(ステップ910)。それ故、有効な順方向重畠を伴うサンプル対の全数をカウントし、これはF 1で表される。同様に、ステップ920において、I及びI 2の両方がリタイアしそしてそれらの実行が重畠するような形式< I 1、 I >のサンプルの数をB 1とする。即ち、第2の命令が第1の命令に対してサンプリングされる場合には順方向に、そして第1の命令が第2の命令に対してサンプリングされる場合には逆方向に、各対が2回考慮される。

20

#### 【0084】

次いで、ステップ930において、一致するサンプルの数F 1 + B 1に潜在的な同時性のサンプルウインドウのサイズWを乗算することにより、命令Iがフライト中である間にイッシューされる有効命令の数を統計学的に推定し、即ち形成されるイッシュースロットの数は、 $W \times (F 1 + B 1)$ となる。

イッシュースロットで測定される命令Iの累積的待ち時間L 1、例えば、A1pha21264プロセッサで持続できる4/サイクルを付加的に決定することにより、ステップ940において、命令Iの実行中に浪費したイッシュースロット(WIS)の全数を次のように要約することができる。

30

$$WIS = L 1 - (W \times (F 1 + B 1))$$

値WISは、命令Iの実行当たりの浪費イッシュースロットの割合又は平均数を表すよう容易に拡張することができる。好都合にも、この平均に寄与する値を増分的に収集し、データ収集中にコンパクトな記憶を行うことができる。又、これは、1997年3月3日に出願されたウエイル氏等の「プロセッサ性能カウンタの高頻度サンプリング(High Frequency Sampling of Processor Performance Counters)」と題する米国特許出願第08/812,899号に開示されたような効率的なデータ減少技術を可能にする。

40

#### 【0085】

命令Iがフライト中である間にリタイアした命令の数、又は命令Iの周りでイッシューされた命令の数のような他の同時性メトリックも同様に決定することができる。

最終的に、命令Iが特定のバイオライン段にある間の特定の実行ユニット240の平均的な利用のような更に詳細な情報も抽出又は収集することができる。

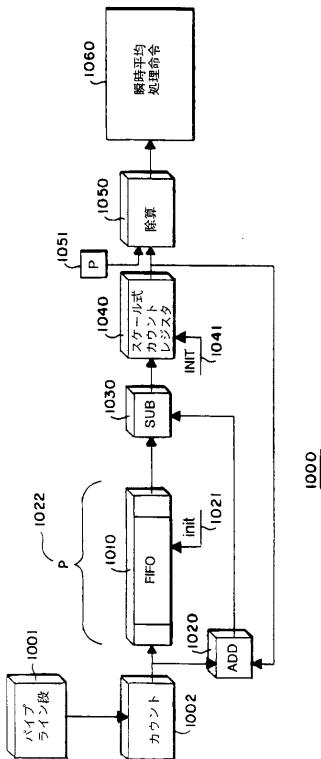

#### 单一プロセッササイクル中にバイオライン段により処理される

#### 命令の瞬時平均数の決定

図10に示すように、異なる形式の多路サンプリングを使用して、固定サイズのプロセッササイクル数にわたりバイオラインにより処理される命令の平均数を決定することができる。図10は、例えば、リタイアされる命令の瞬時平均数を決定するための回路を示す。プロセッササイクル中に、バイオライン220のいずれの段1001についても、同様の

50

回路を使用して、フェッチ、マップ、イッシュ又は実行される命令の平均数を決定することができる。

#### 【0086】

装置1000において、先入れ先出し(FIFO)待ち行列1010及びN容量の加算器1020の各々は、単一のプロセッササイクル中にパイプラインの特定の段1001により処理される命令の数(カウント1002)を受け取り、例えば、フェッチ、マップ、イッシュ又は実行される命令の数を受け取る。FIFO待ち行列1010におけるエントリの数(P)1022は、平均値が決定されるところのサイクルの数を決定する。Pは、ハードウェアで設定されてもよいし、ソフトウェアで設定されてもよい。値Pは、平均値が決定されるところのサイクルのウインドウを制御する。

加算器1010はスケール型カウントレジスタ1040に接続され、従って、このレジスタ1040は、N個のサイクル中にリタイアした命令の全数を累積することができる。FIFO待ち行列1020及びレジスタ1040は、ライン1021及び1041を経て初期化することができる。減算器1030は、それまでのN-1サイクルにリタイアした命令の数をレジスタ1040から減算し、例えば、FIFO待ち行列1010のヘッドエントリに記憶されたカウントを減算する。レジスタ1040の出力は追跡されたサイクルの数(P)で除算され(1050)、段1001で処理された実際の命令の動特性即ち瞬時平均数1060を形成する。瞬時平均値は、プロファイルレジスタ300に捕獲されるか、或いはソフトウェアで読み取り可能なプロセッサレジスタ又はメモリ位置に記憶される。

10

サンプルされた命令がリタイアした命令であるときには、コンピュータにより行われた実際の「真」の有効作業を計算することができる。これは、相対的なプロセッサ性能を指示するためにしばしば引用される「生」の命令フェッチレートよりも良好な指示である。例えば、特定のアーキテクチャーは、大きなフェッチレートをもつことができるが、パイプラインにおけるストールが性能を低下することがある。

20

#### 【0087】

##### 命令のクラスター化

又、サンプルされた状態情報を使用し、同時性情報を収集しながら当該ケースを識別することもできる。例えば、命令Iがキャッシュの1つにおいて「ヒット」するときに平均同時性レベルを計算し、次いで、平均同時性レベルを、命令Iがキャッシュミスを招く場合と比較することが有用である。変化する同時性レベルと相關するために検討すべき他の当該特徴は、レジスタ依存性ストール、キャッシュミスストール、分岐予想ミスストール、及び最近の分岐経過を含む。

30

#### 【0088】

一般に、N個ごとのサンプリングは、W個の命令のウインドウにわたりF(I1, I2)と表すことのできるファンクションの値をサンプリングすることにより種々の異なるメトリックを統計学的に計算できるようにする著しい融通性を与える。対応する公知のハードウェアメカニズムとは対照的に、ここに与えられる融通性は、N個ごとのサンプリングを、複雑なプロセッサに関する同時性情報を捕獲するための非常に優れた選択肢にする。これは、新規なメトリック及び分析技術の設計を可能にするためである。

40

標準的なSPECベンチマークソフトウェアを実行するプロセッサでの実験では、統計学的に収集されたサンプルをベースとするメトリックは、低いオーバーヘッドの完全な情報で得られた値に収斂することが示されている。

#### 【0089】

##### 経路プロファイル

命令のクラスターをプロファイリングする付加的な効果は、経路プロファイルが得られることである。経路プロファイルは、多数のコンパイラ最適化及びトレーススケジューリングに有用である。

更に、最近の分岐実行経過と共にプログラムの実行経路に沿った多数のポイントを制限することにより、経路プロファイルが明確化される。この明確化は、N個ごとのサンプリン

50

グとで改善され、即ちNが増加するにつれて、明確化が改善される。著しく実行されるコードの場合には、同時プログラムが、全ての実行命令に対しパイプライン200の各段において命令の相対的な実行順序を示すことができる。従って、ここでは、オペレーティングシステムにおける実行パイプライン200の実際のオペレーションを統計学的に再構成することができる。

#### 【0090】

##### ランダムにサンプルされるプロファイル情報の他のアプリケーション

マイクロプロセッサの最新の世代は、考えられる最高の性能を与るためにコンピューターアーキテクチャーが許す全ての策略を利用する。これらのマイクロプロセッサは、サイクル当たり多数の命令をフェッチし、イッシュしてコミットする。更に、これらのプロセッサは、命令を順序ずれして実行する。それらのあるものは、メモリオペレーションも順序ずれして実行する。

10

不都合なことに、プロセッサにより使用される多数の発見的メカニズムが命令及びメモリオペレーションを順序ずれしてイッシュするので、性能特性がかなり変化し得る。1つの効果として、ここに述べるプロファイリング技術は、システム100の性能を自動的に改善できるように、システムがプログラムの性能を充分詳細に測定できるようにすることである。

#### 【0091】

##### 最適化

又、本発明のプロファイリング技術は、システム100の最適化を実行するのにも使用できる。以下の説明は、プログラマー及びコンパイラで指令されるソフトウェアプログラムの最適化を手引きするよう意図されたものである。

20

#### 【0092】

##### ハードウェアの最適化

アウトオブオーダーのスーパースカラーマイクロプロセッサは、データ及びリソースの利用状態に基づいて命令をスケジューリングし直すので、コンパイル-時間命令スケジューリングは、構造的に簡単なプロセッサの場合よりも重要性がかなり低い。ここでは、主なボトルネックは、命令フェッチ及びメモリオペレーションによるものである。

より詳細には、分岐又はジャンプ予想ミス、オンチップキャッシュミス、及びTLB欠陥によりプロセッサパイプライン200においてサイクルが失われる。これらは、静的に推測することが不可能でないまでも困難な状態である。又、高レベルオフチップオペレーションにおける遅延に対しても、キャッシュミス、リソーストラップ及び順序づけトラップのために、サイクルが失われる。失われたサイクルは、時間を浪費する。

30

従来の事象カウンタでは、これらの性能低下事象の合計数を測定することはできるが、失われたサイクルをプログラムの特定の命令に起因させることは不可能ではないまでも非常に困難である。ここに述べるプロファイリング技術は、ユーザが主な性能問題を測定して、それら問題を特定の命令に相關させることができるようとする。

#### 【0093】

##### フロントエンド最適化

性能の助けとなる1つのフロントエンド最適化は、基本的ブロックにおいて命令をそして手順において基本的ブロックを順序付けし直すことである。基本的ブロックとは、1つの単位として直線的に実行されるか又は全く実行されない命令のセットとして定義される。手順とは、一般に、コール命令を経て到達する基本的ブロックの凝集セットである。手順は、多数の基本的ブロックを含むことができる。基本的ブロックにおいて命令をそして手順において基本的ブロックを順序付けし直すことは、ページ及びキャッシュの一時的な位置を最適化すると共に、分岐の数を減少するように実行流及びデータアクセスを変更できるようになる。分岐は、実行流しか再指令せずそしてデータにおいて有効に作用しないので、サイクルを浪費する。この最適化は、入力として、制御流グラフエッジ周波数を知る必要がある。

#### 【0094】

40

50

### トレースの形成

同様に、命令のスケジューリングを追跡するために、コンパイラーは、制御流グラフのエッジ又は経路周波数を必要とする。トレーススケジューラは、各基本的ブロック又はより大きな実行経路を実行するのにどれほどの時間を要するかの推定値を有するときは非常な良好なジョブを行うことができる。アルタ・ビ斯塔サーチエンジンのような大規模な動作システムの場合には、これを従来のツールでリアルタイムに測定することが困難である。

【0095】

### ホット / コールド最適化及び経路情報

トレーススケジューリング及びホット / コールド最適化のような多数のコンパイラー最適化は、プログラムによりどの実行経路が頻繁にとられるかを知ることに依存している。これらは「ホット」経路と称する。最近まで、計装又は模擬のいずれかによりプログラムをプロファイリングすることにより、頻繁に実行される経路が推測されて、基本的なプロック又はエッジカウントが収集され、そしてこれらのカウントを用いて、ホット及びコールド経路が間接的に推測される。

最近、経路情報を直接収集するための技術が使用されている。これらの技術は正確な経路情報を与えるが、非常に高いオーバーヘッドをもつ傾向があり、アクティブな大規模コンピュータシステムを測定するには不適当である。本発明のプロファイリングでは、経路情報を最小のオーバーヘッドでランダムに捕獲することができ、そして実際の実行流の統計学的に正しい概観を依然として表すことができる。

【0096】

### 分岐経過レジスタ

ほとんどの近代的なマイクロプロセッサは、グローバルな分岐経過レジスタにおいて最後のN個の分岐の方向を追跡する。分岐経過レジスタは、移動ウインドウとして、最近の分岐予想を観察し、そしてそれに応じて将来の命令フェッチに作用を及ぼすことができる。命令のPCがサンプリングされると共に、このレジスタの内容を命令フェッチ時間に捕獲することにより、時には、制御流グラフの静的な分析を使用して、プロセッサがとらねばならない最後のN個の分岐により厳密な経路を仮定することができる。

【0097】

しかしながら、従来の経過レジスタは、通常、分岐の方向しか含まず、実際のターゲット行先を含まないので、情報が不正確なものとなる。特に、制御流の合流は、実際にとられた経路を識別する上であいまいさを招く。

又、分岐コードの実行を生じさせる非同期事象、例えば、割り込み又はコンテクストスイッチは、分岐経過ビットを汚染することがある。しかしながら、これらの事象は、比較的稀であり、そしてオペレーティングシステムにおけるそれらの発生は、コードにわたってランダムに分布されねばならない。頻度の高い経路を識別するのが目的であるから、予想不能な非同期事象により発生される「ノイズ性」の分岐経過ビットにより生じるものと含む頻度の低い経路を無視することができる。

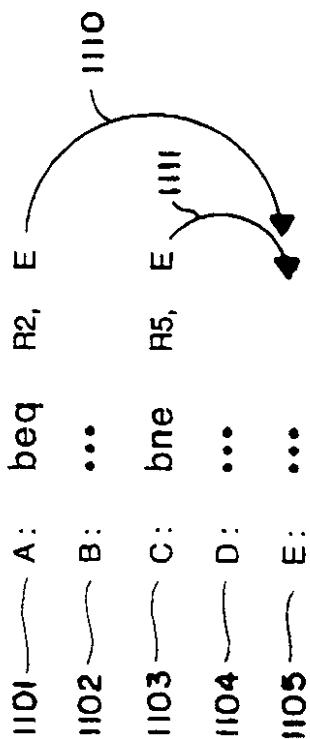

【0098】

図11に示す命令シーケンスについて考える。PCアドレスA-E(1101-1105)に命令がある。アドレスA及びCにおける命令1101及び1103は、分岐型の命令である。EのPCをもつ命令1105があつて、グローバルな分岐経過における最後のビットが1である場合には、CDEで終わるいかなる経路も除外することができる。というのは、このような経路の最後の分岐が失敗に終わり、それ故、グローバルな分岐経過に対応しないからである。しかしながら、ポイントEにおける異なる制御経路の合体により、実行された真の経路がAE(1110)又はABCDE(1111)であったときを決定することができない。

【0099】

### 制御流グラフの合流によるあいまいさ

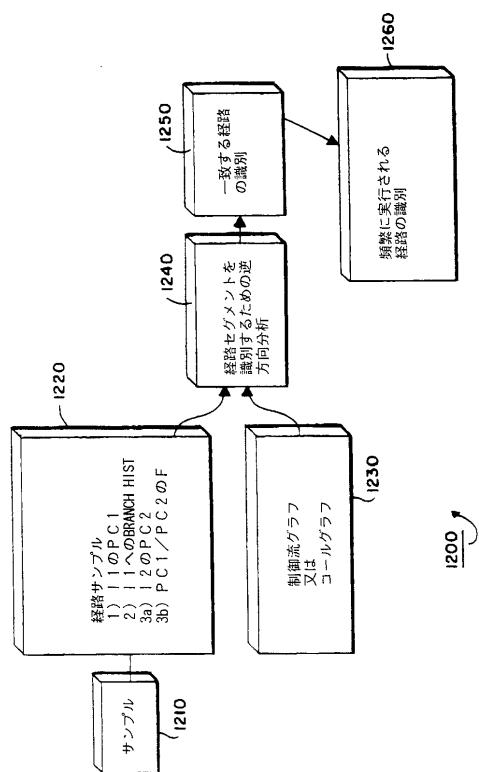

図12は、サンプリングされたPC値を入力として使用して、プログラム流の静的な分析を実行することのできるプロセス1200を示す。選択された命令の経路サンプルがステ

10

20

30

40

50

ツップ1210において上記のように捕獲される。マシンへの影響を最小にするために、サンプリングされた命令はランダムに選択されるのが好ましい。各「経路」サンプル1220は、サンプリングされた第1命令I1のPC1と、命令I1までの最後のN個の条件付き分岐によりとられる方向(BRANCH HIST)とを含む。

#### 【0100】

任意であるが、サンプリングされた情報は、第1命令の直前に実行される第2命令(I2)のPC2で増強することもできるし、或いは最後のM個の分岐のPC値に適用されるあるファンクション、例えば、ある数の下位ビット又はハッシュ関数を用いて決定されたビットを選択するファンクションに基づいて選択された情報で増強することもできる。

ステップ1240において、経路サンプルを使用して、プログラムの制御流グラフの逆方向分析を実行する。この分析は、サンプリングされたデータに一致する実行経路を識別することができ(1250)、そしてこの情報を収集して、最適化から更に効果が得られる頻繁に実行される経路を識別することができる(1260)。

10

#### 【0101】

例えば、図11を参照すれば、命令Eにおいて、1の分岐経過長さが与えられると、経過ビット「1」により、ソフトウェアツールは、経路セグメントAE1110及びABCE(1101-1105)を考えられる経路として識別することができる。分岐経過ビットの値が与えられたときに、静的な分析が、可能性として、単一経路セグメントしか識別できないときに、考えられる最良の成果が得られる。

又、プロセスの最近の実行経過に関する他の情報も、特定の命令に到達するためにとられた実行経路を識別する上で助けとなる。有効な情報の1つの断片は、最近実行された命令の第2のPC値の知識である。おそらくN個ごとのサンプリングと共に多数のPC値を使用することにより、1つのPCしか含まない経路を除外することができる。

20

#### 【0102】

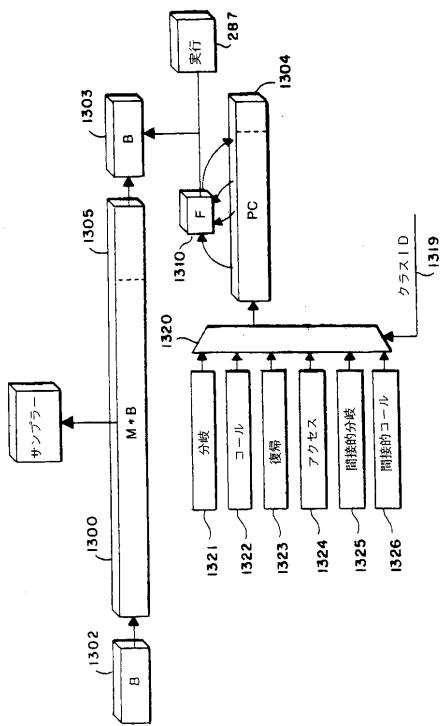

##### 所与のクラスの最後のM個の命令のサンプリング

図13に示す別の技術においては、ハードウェアは、パイプラインの任意の選択された段、例えばリタイアユニットで処理された最後のM個の命令の各々から少数のビット(B)を捕獲することができる。Bビット1303は、PCの下位のBビットでもよいし、或いはBビットは、PC1304に適用されるハードウェア実施ファンクションF1310を使用して選択することもでき、即ちB-F(PC)である。ファンクション1310がハッシュ関数である場合には、分岐アドレスの非均一な分布が回避される。

30

命令のクラスは、例えば、条件分岐、コール、リターン、アクセス(ロード又は記憶)命令、間接的分岐、及び間接的コール1321-1326として識別することができる。クラスは、比較器又はマルチブレクサのような選択メカニズム1320によりライン1321を経て選択することができる。又、クラスは、パイプラインの段、例えば、フェッチ、マップ又はリタイア等により識別することもできる。クラスID1319は、ソフトウェアにより制御される。

#### 【0103】

選択されたビットは、M×Bビット巾のシフトレジスタ1300に記憶することができる。このレジスタは、ソフトウェアの内部レジスタとして或いはメモリ位置として図5のPSW520へアクセスすることができる。識別されたクラスの命令1321-3124が処理されるときには、シフトレジスタ1300は、その上位のBビット1302を破棄するようにシフトされる。命令のPC1304の選択されたBビット1303は、空きビット1305へとシフトされる。従って、レジスタ1300は、これら形式の命令に対し指紋即ち「経路符号」として働く。レジスタ1300は、例えば、実行された最新のM個の分岐を制限する助けをする。というのは、現在経路符号に一致しない経路は、考慮対象から排除できるからである。分岐命令1321に対し、図2の分岐実行指示287を使用して、サンプリングをトリガーすることができる。

40

#### 【0104】

経路符号により得られる精度の改善は、相当のものとなり、例えば、B=4、M=6のよ

50

うに、最後の 6 個の分岐から 4 つのビットを節約するだけでも、標準的な SpecInt 95 ベンチマークプログラムに対する実行経路を決定する精度が 2 倍になる。経路符号及びグローバルな分岐経過を使用すると、トレースを次のように分析することができる。

トレースにおいて実行される各命令に対し、次のいずれかに達するまで経路セグメントを決定するように逆方向に進行する。

- a ) グローバルな分岐経過ビットが尽きる、又は

- b ) 命令を含むルーチンの開始点に到達する。

制御流グラフの逆方向進行中に手順のコール命令に遭遇したときには、コールされた手順を通して逆方向に進行し、そして最終的に、そのコールされた全ルーチンを通して逆方向に作用するに充分な分岐経過があるときに、コール側手順に復帰する。従って、実行流のより正確な概観が与えられる。

#### 【 0105 】

##### キャッシュ及びTLBヒットレートの増強

キャッシュ又は変換ルックアサイドバッファ (TLB) における高いミスレートは、システムの性能を著しく低下する。公知の解決策は、一般に、キャッシュミスマッチを収集する特殊なハードウェア又は特殊なソフトウェア機構、例えば、TLB を周期的にフラッシュするものに依存している。観察されたミスパターンは、頻繁にアクセスされるページ即ち「ホット」ページのおおよその理解を与え、これは、仮想 / 物理ページマッピングポリシーに影響するように使用することができる。しかしながら、完全な分析を行うのに必要なアドレス情報は、事象が検出されるときまでに得られない。

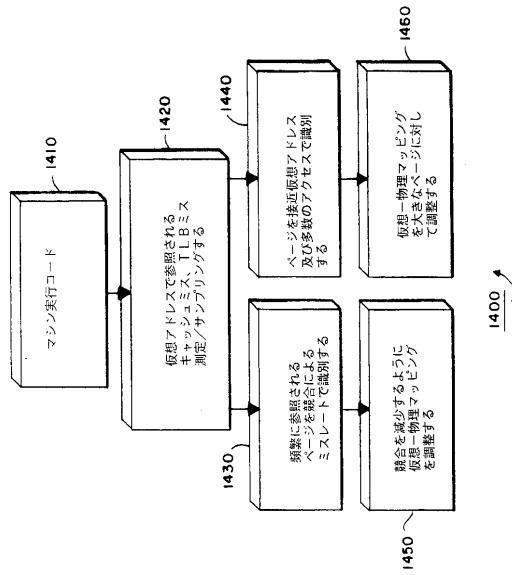

#### 【 0106 】

図 14 は、より正確な仮想 / 物理ページマッピングを実行するのに使用できるプロセス 1400 を示す。ステップ 1410 では、マッピングされるべきコードがシステムにおいて実行される。ステップ 1420 では、メモリをアクセスするオペレーション (ロード及び記憶) がサンプリングのために選択される。オーバーヘッドを最小にするためにサンプリングはランダムであるのが好ましい。

命令が実行される間に、有効な仮想メモリアドレスが、ステップ 1430 において、キャッシュ及び TLB ミスと共に識別され、従って、1 つの効果として、事象及びアドレスを特定の命令に直接的に起因させることができる。同様に、ステップ 1440 において、高いアクセスレートで隣接ページを識別することができる。ステップ 1450 では、キャッシュ及び TLB におけるアクセス競合を減少するために、仮想 / 物理ページマッピングを調整することができる。ステップ 1460 では、隣接ページを大きな「スーパーページ」へと合成し、ページングオーバーヘッドを減少することができる。

キャッシュ又は TLB において捕獲され損なったメモリ参照の仮想アドレスは特定の命令に直接的に起因させて、ページマッピングポリシーを誘導するに必要な情報の形式を厳密に与えることができる。アプリケーションのメモリ参照流に関する情報を使用して、オペレーティングシステムの仮想 / 物理マッピングポリシーを動的に制御すると、大きな直接マップ式キャッシュにおける競合ミスを首尾良く回避し、スーパーページの形成による TLB ミスレートを低減し、そしてページの複写及び移動による非均一メモリアクセス時間 (NUMA) マルチプロセッサにおける遠隔メモリ参照の数を減少することができる。

#### 【 0107 】

##### 改良された命令スケジューリング

コード最適化の間に行われる 1 つの重要なタスクは、理想的な命令スケジューリングである。理想的な命令スケジューリングは、メモリ待ち時間による遅延を最小にするようにコードを順序付けし直す。基本的なブロックにおける隣接命令の静的な順序付けは、前世代のインオーダー型 RISC プロセッサの場合よりも重要性が低いが、巨視的な命令スケジューリングは、アウトオブオーダー型プロセッサにおいて非常に重要である。

命令スケジューリングについての 1 つの非常に困難なものは、ロード及び記憶のスケジューリングである。これは、静的なスケジューラが、メモリアクセス命令を最適にスケジュ

10

20

30

40

50

ールできるようにする厳密な依存性情報を常に有していないからである。加えて、メモリアクセス命令の待ち時間を厳密に予想することが困難である。命令スケジューラは、通常、メモリアクセスに関する正確な情報が不充分であるから、一般に、Dキャッシュヒットを仮定してロード及び記憶をスケジュールする。或いは又、バランス型スケジューリングは、ロード当たり等しい量の待ち時間を含むスケジュールを発生するよう試みる。これは、ロード/記憶オペレーションがキャッシュにおいて常にヒットすると常時仮定することに勝る改良である。

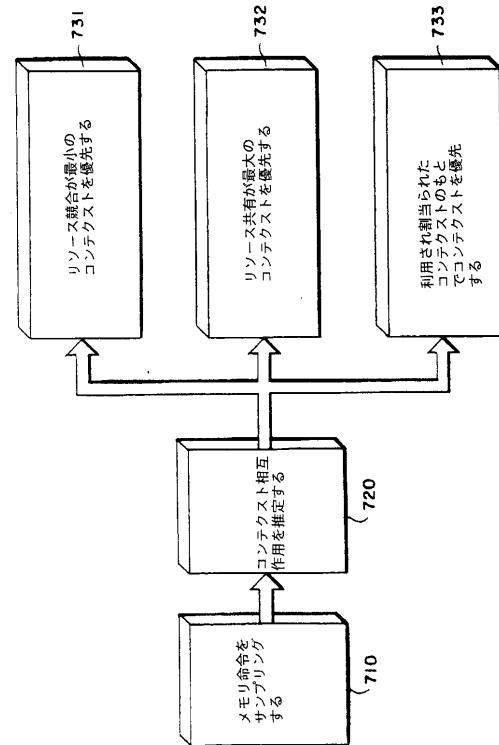

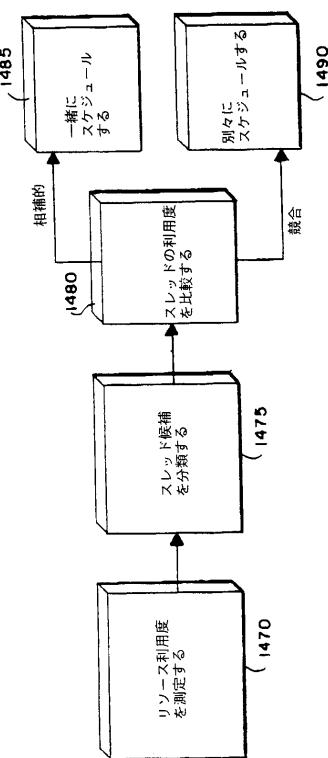

## 【0108】

マルチスレッド型プロセッサにおけるスレッドのスケジューリング

マルチスレッド型プロセッサにおいては、上記プロファイリング方法を用いて得たスレッドのリソース利用に関する情報を使用して、全体的なリソース利用度及びスループットを最大にするようにスレッドをスケジューリングすることができる。10

2つのスレッドがリソースの相補的な使い方を有し、例えば、一方のスレッドが主として整数演算ユニットを使用するが、他方のユニットは主として浮動小数点演算ユニットを使用する場合には、2つのスレッドが異なる機能的実行ユニットを使用するので、2つのスレッドを同時に動作するようにスケジューリングすることができる。同様に、2つのスレッドが競合するリソース使用を有し、例えば、両スレッドが浮動小数点演算ユニットを頻繁に使用する場合には、それらを異なる時間に動作するようにスケジューリングすることができる。

## 【0109】

図14bは、プロセッサの利用度によりスレッドをスケジューリングするためのプロセスを示す。オペレーティングシステムにおいて実行されるスレッドのリソース利用度がステップ1470において測定される。ステップ1475では、リソースの利用度が収集され、そしてそのリソース利用度に基づいてスレッドがセットへと分類される。本発明のサンプリングでは、各スレッドが、プロセッサにおける各クラスのリソース、例えば、整数演算ユニット、浮動小数点演算ユニット、メモリユニット、分岐ユニット、イッシュユニット等々をいかに使用するかを決定することができる。20

ステップ1480では、スレッドのリソース利用度を比較して、非競合実行スケジュールを決定する。所与のクラスのリソースに対する1組のスレッドの合成利用度により、そのクラスのリソースが完全利用状態より著しく多く利用されている場合には、その組のスレッドと一緒にスケジューリングしてはならず(ステップ1490)、逆に、合成利用度により、そのクラスのリソースが完全利用状態以下で利用されるか或いは完全利用状態より若干多めに利用される場合には、それらと一緒にスケジューリングするのが有益である(ステップ1485)。30

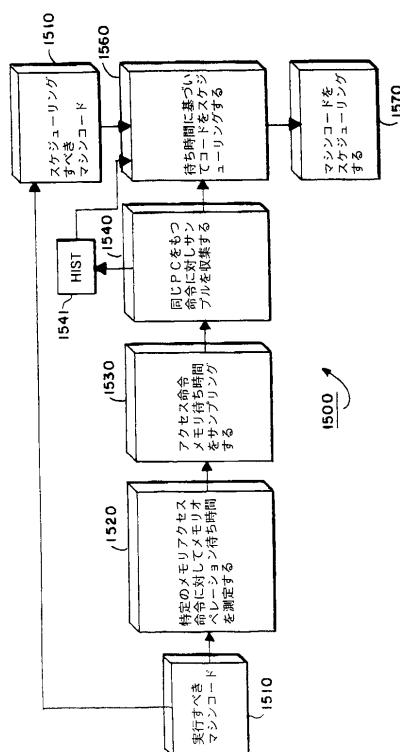

## 【0110】

図15は、命令のスケジューリングを実行するのに使用できるプロセス1500を示す。マシンコード1510は、図1のシステム100で実行される。コードが実行される間に、メモリオペレーション命令の待ち時間がステップ1520において上記のように測定される。多数の命令、例えば、命令対に対する測定値をステップ1530においてサンプリングすることができる。サンプリングは、オーバーヘッドを減少するためにランダムに行うことができる。同じPCをもつ命令に対してサンプリングされたデータは、ステップ1540において収集されて、例えば、待ち時間のヒストグラム(HIST)1541が形成される。ステップ1560では、マシンコードが順序付けし直される。この再順序付けは、収集されたヒストグラム情報1541に基づく。例えば、長い待ち時間をもつメモリオペレーションは、それらに依存するオペレーションからできるだけ離れるように進められる。ステップ1560は、リストスケジューリング或いはトレーススケジューリングのようなスケジューリングアルゴリズムを使用することができる。

ランダムサンプリングによりロード及び記憶待ち時間を収集する場合には、各命令を待ち時間のヒストグラムに基づいてスケジューリングすることができる。本発明の技術は、全キャッシュシミュレーションの経費を被ることなく待ち時間情報を収集することにより最40

適化を導出するように使用できる。

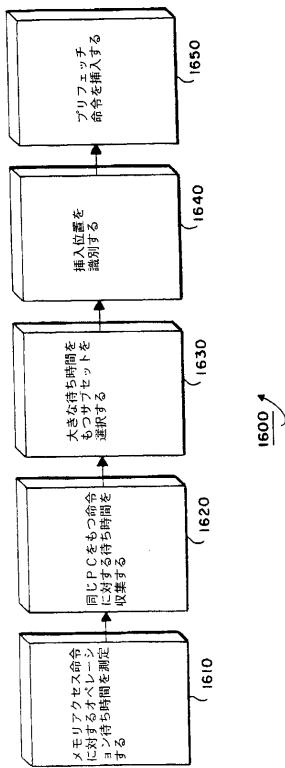

#### 【0111】

##### プリフェッヂ命令の挿入

図16は、測定された待ち時間に基づいてプリフェッヂ命令を挿入するためのプロセスを示す。プリフェッヂ命令の挿入は、メモリから返送されるべきデータを待機することにより生じるプロセッサストールを隠す上で助けとなる技術である。データが実際に必要とされる充分前にメモリシステムに要求を発生し、そして時々はデータが必要になると決定される直前にデータを要求することにより、コンパイラー及びオプチマイザーは、メモリからデータをフェッチするための待ち時間のほとんど又は全部をしばしば隠すことができる。

10

しかしながら、性能を実際に改善するためには、著しい待ち時間を実際に経験するメモリオペレーションに対してのみプリフェッヂ命令を挿入することが望ましく、即ち長い待ち時間を実際に被らないメモリオペレーションにプリフェッヂ命令を挿入すると、付加的なプリフェッヂ命令を実行しなければならないためにプログラムが实际上低速化されてしまう。メモリオペレーション、特に、プリフェッヂから利益を得るロードオペレーションを識別するために、プログラム内の種々のメモリオペレーションにより経験する平均待ち時間に関する統計学的データを収集することが所望される。

その一般的な構成が図16に示されている。ステップ1610では、プログラム内のメモリオペレーションに対するメモリオペレーション待ち時間が測定される。ステップ1620では、同じプログラムカウンタ(PC)値をもつ命令に対しサンプリングされたメモリオペレーション情報が収集される。ステップ1630では、プリフェッヂを挿入すべき大きなメモリ待ち時間をもつメモリオペレーションのサブセットが識別される。

20

#### 【0112】

ステップ1640では、実行頻度情報及び測定された待ち時間情報に基づき、これらのメモリオペレーションに対してプリフェッヂ命令を挿入するのに有益な位置が識別される。ステップ1650では、その適当な位置にプリフェッヂ命令が挿入される。

待ち時間は、上記のように測定することができる。1つの方法は、サンプリングハードウェアでメモリオペレーションの待ち時間を直接測定することである。別の方法は、ロード命令が対の第1サンプルでありそしてロードからのデータの使用が対の第2サンプルである場合に、対構成でサンプリングを行いそして対を探索することによるものである。2つのサンプルにおいて待ち時間情報を探し、そして特に2つのサンプルのイッシュ時間の差を探すことにより、ロードオペレーションに対するメモリシステム待ち時間を推定することができる。

30

#### 【0113】

以上、特定の実施形態について詳細に説明した。当業者であれば、上記実施形態を変更しても、幾つかの又は全ての効果が達成されることが明らかであろう。それ故、本発明の精神及び範囲内に包含されるこののような修正や変更は全て請求の範囲内に含まれるものとする。

##### 【図面の簡単な説明】

【図1】命令駆動状態サンプリングを伴うコンピュータシステムのブロック図である。

40

【図2a】サンプリングされた命令を処理するためのマイクロプロセッサ実行パイプラインのブロック図である。

【図2b】サンプリングすることのできる状態情報を示すパイプラインのブロック図である。

【図3】プロファイル情報を記憶するためのレジスタファイルのブロック図である。

【図4】増強された命令のブロック図である。

【図5】選択された命令をプロファイリングするための流れ線図である。

【図6】パイプライン待ち時間を測定するための回路を示す回路図である。

【図7】プロセスの流れ線図である。

【図7a】命令をサンプリングするプロセスの流れ線図である。

50

【図 7 b】プロセッサパイプラインにより処理される命令の特性の統計値を推定するためのプロセスを示す流れ線図である。

【図 8 a】命令の同時実行を示す図である。

【図 8 b】命令の同時実行を示す図である。

【図 8 c】命令の同時実行を示す図である。

【図 9】費やされる発生スロットを決定するプロセスを示す流れ線図である。

【図 10】プロセッササイクル中に処理される命令の平均数を決定するための装置のプロック図である。

【図 11】命令シーケンスの制御の流れを示すグラフである。

【図 12】制御流を識別するプロセスのデータの流れを示す図である。 10

【図 13】分岐経過を収集する装置のブロック図である。

【図 14 a】ページマッピングプロセスの流れ線図である。

【図 14 b】スレッドスケジューリングプロセスの流れ線図である。

【図 15】メモリ待ち時間の影響を受ける命令スケジューラの流れ線図である。

【図 16】プリフェッチ命令を挿入するためのプロセッサ 1600 の流れ線図である。

#### 【符号の説明】

100 コンピュータシステム

110 プロセッサ

111 パイプライン

112 データキャッシュ (Dキャッシュ) 20

113 命令キャッシュ (Iキャッシュ)

119 プロセッサ状態をサンプリングするハードウェア

120 オフチップメモリ

121 汎用キャッシュ

122 揮発性メモリ

123 永続的メモリ

130 入力 / 出力インターフェイス (I/O)

140 バスライン

200 実行パイプライン

205 変換ルックアサイドバッファ (TLB) 30

210 フェッチユニット

220 マップユニット

230 イッシュユニット

240 実行ユニット

250 リタイアユニット

【 四 1 】

【図2a】

【図2b】

【 図 3 】

【 四 4 】

【 四 5 】

【 义 6 】

【図7】

【図 7 a】

【図 7 b】

【図 8 a】

【図 8 b】

【図 8 c】

【図 9】

【図 10】

【図 11】

【図 12】

【図13】

【図14 a】

【図14 b】

【図15】

【図16】

---

フロントページの続き

(74)代理人 100074228

弁理士 今城 俊夫

(74)代理人 100084009

弁理士 小川 信夫

(74)代理人 100082821

弁理士 村社 厚夫

(72)発明者 ジェフリー エイ ディーン

アメリカ合衆国 カリフォルニア州 94025 メンロ パーク フィフティーンス アベニュー

- 884

(72)発明者 ジェームズ イー ヒックス

アメリカ合衆国 マサチューセッツ州 02159 ニュートン ボウ ロード 63

(72)発明者 スティーヴン シー ルート

アメリカ合衆国 マサチューセッツ州 01581 ウエストボロー ウエスト メイン ストリ

ート 201

(72)発明者 カール エイ ウォールドスパージャー

アメリカ合衆国 カリフォルニア州 94027 アサートン パーク ドライヴ 27

(72)発明者 ウィリアム イー ウィール

アメリカ合衆国 カリフォルニア州 94114 サン フランシスコ クリッパー ストリート

280

審査官 坂庭 剛史

(56)参考文献 特開平08-171505 (JP, A)

特開平08-030494 (JP, A)

特開平07-064799 (JP, A)

特開平03-263136 (JP, A)

特開平03-175533 (JP, A)

特開平03-099342 (JP, A)

特開平02-158847 (JP, A)

特開平02-083751 (JP, A)

特開平01-220042 (JP, A)

特開昭63-046552 (JP, A)

特開昭63-025742 (JP, A)

特開昭62-243035 (JP, A)

特開昭62-214450 (JP, A)

特開昭59-069853 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 11/34

G06F 9/38