(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-187864

(P2015-187864A)

(43) 公開日 平成27年10月29日(2015.10.29)

(51) Int.Cl.

G06F 12/02 (2006.01)

G06F 12/00 (2006.01)

G06F 12/16 (2006.01)

F 1

G06F 12/02

G06F 12/00

G06F 12/16530E

597U

310A

テーマコード(参考)

5B018

5B060

審査請求 未請求 請求項の数 20 O L (全 27 頁)

(21) 出願番号 特願2015-64985 (P2015-64985)

(22) 出願日 平成27年3月26日 (2015.3.26)

(31) 優先権主張番号 10-2014-0035142

(32) 優先日 平成26年3月26日 (2014.3.26)

(33) 優先権主張国 韓国 (KR)

(特許庁注: 以下のものは登録商標)

1. FIREWIRE

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100086368

弁理士 萩原 誠

(72) 発明者 崔 仁 奥

大韓民国京畿道華城市盤松洞 シビヨムダ

イウンマウル サムスンライミアンアパー

ト309棟1402号

最終頁に続く

(54) 【発明の名称】不揮発性メモリ及びメモリコントローラを含むメモリシステムの動作方法

## (57) 【要約】

【課題】向上された速度及び信頼性を有する不揮発性メモリ及びメモリコントローラを含むメモリシステムの動作方法を提供する。

【解決手段】本発明の動作方法は、複数のメモリブロックの中で自由ブロックの割当間隔を計算する段階及び割当間隔にしたがって複数のメモリブロックの中で消去ブロックの数を調節する段階で構成される。自由ブロックは、複数のメモリブロックの中で、データを格納しない状態であり、データを格納するデータブロックに選択されるメモリブロックを示す。消去ブロックは、複数のメモリブロックの中で、消去された状態であり、自由ブロックに割当されるメモリブロックを示す。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

複数のメモリブロックを含む不揮発性メモリ及び前記不揮発性メモリを制御するメモリコントローラを含むメモリシステムの動作方法において、

前記複数のメモリブロックの中で自由ブロックの割当間隔を計算する段階と、

前記割当間隔にしたがって前記複数のメモリブロックの中で消去ブロックの数を調節する段階と、を含み、

前記消去ブロックは、前記複数のメモリブロックの中で消去された状態のメモリブロックを示し、

前記自由ブロックは、前記消去ブロックの中でデータを書き込むように選択されたメモリブロックを示す動作方法。 10

**【請求項 2】**

前記割当間隔は、最も最近に前記自由ブロックに割当された予め定めた個数のメモリブロックの割当間隔である請求項 1 に記載の動作方法。

**【請求項 3】**

前記消去ブロックの数を調節する段階で、前記割当間隔が増加すれば、前記消去ブロックの数が減少される請求項 1 に記載の動作方法。

**【請求項 4】**

前記消去ブロックの数を調節する段階で、前記割当間隔が減少すれば、前記消去ブロックの数が増加される請求項 1 に記載の動作方法。 20

**【請求項 5】**

無効ブロックを消去して消去ブロックを生成する時、タイムスタンプ ( time stamp ) を格納する段階をさらに含み、

前記無効ブロックは、前記複数のメモリブロックの中で無効データを格納し、前記データブロックが無効化されて生成されるメモリブロックであり、

前記タイムスタンプは、前記無効ブロックが消去されて前記消去ブロックが生成された時間を示す請求項 1 に記載の動作方法。

**【請求項 6】**

前記タイムスタンプにしたがって、前記消去ブロックを再び消去する段階をさらに含む請求項 5 に記載の動作方法。 30

**【請求項 7】**

前記タイムスタンプが示す時間及び現在時間の差が閾値より大きい時、前記消去ブロックが再び消去される請求項 6 に記載の動作方法。

**【請求項 8】**

前記現在時間は、前記消去ブロックが前記自由ブロックに割当することを要請する要請が生成された時間を示す請求項 7 に記載の動作方法。

**【請求項 9】**

前記要請にしたがって、前記再び消去された消去ブロックが前記自由ブロックに割当される請求項 8 に記載の動作方法。

**【請求項 10】**

前記要請にしたがって、前記再び消去された消去ブロックではない他の消去ブロックが前記自由ブロックに割当される請求項 8 に記載の動作方法。 40

**【請求項 11】**

複数のメモリブロックを含む不揮発性メモリ及び前記不揮発性メモリを制御するメモリコントローラを含むメモリシステムの動作方法において、

無効ブロックを消去して消去ブロックを生成する時、タイムスタンプ ( time stamp ) を格納する段階と、

前記タイムスタンプにしたがって、前記消去ブロックを再び消去する段階と、を含み、

前記タイムスタンプは、前記無効ブロックが消去されて前記消去ブロックが生成された時間を示し、 50

前記無効ブロックは、前記複数のメモリブロックの中で無効データを格納するメモリブロックであり、

前記消去ブロックは、前記複数のメモリブロックの中で消去された状態であるメモリブロックを示す動作方法。

【請求項 1 2】

前記タイムスタンプが示す時間及び現在時間の差が閾値より大きい時、前記消去ブロックが再び消去される請求項 1 1 に記載の動作方法。

【請求項 1 3】

前記現在時間は、前記消去ブロックが前記自由ブロックに割当することを要請する要請が生成された時間を示し、

前記自由ブロックは、前記複数のメモリブロックの中でデータを格納しない状態であり、データを格納するデータブロックに選択されるメモリブロックを示す請求項 1 2 に記載の動作方法。

【請求項 1 4】

前記要請にしたがって、前記再び消去された消去ブロックが前記自由ブロックに割当される請求項 1 3 に記載の動作方法。

【請求項 1 5】

前記要請にしたがって、前記再び消去された消去ブロックではない他の消去ブロックが前記自由ブロックに割当される請求項 1 3 に記載の動作方法。

【請求項 1 6】

前記タイムスタンプは、前記消去ブロックのアドレスとマッピングされて共に格納される請求項 1 1 に記載の動作方法。

【請求項 1 7】

不揮発性メモリの動作方法において、

メモリコントローラが自由ブロックの要請に応答して複数の消去ブロックの中で 1 つの消去ブロックを選択する段階と、

前記メモリコントローラが前記選択された消去ブロックと連関されたタイムスタンプに基づいて経過時間を計算する段階と、

前記経過時間が閾値時間に到達しなかった時、前記メモリコントローラが前記選択された消去ブロックを前記自由ブロックに割当する段階と、を含み、

前記消去ブロックは、前記不揮発性メモリの複数のメモリブロックの中で消去状態を有するメモリブロックであり、

前記自由ブロックは、前記消去ブロックの中でデータが書き込まれるように選択されたメモリブロックである動作方法。

【請求項 1 8】

前記経過時間が前記閾値時間に到達した時に、前記消去ブロックの中で他の 1 つの消去ブロックを選択する段階と、

請求項 1 7 の段階を再び遂行する段階と、を含む請求項 1 7 に記載の動作方法。

【請求項 1 9】

前記経過時間が前記閾値時間に到達した時に、前記選択された消去ブロックを無効データを格納する無効ブロックに設定する段階をさらに含む請求項 1 7 に記載の動作方法。

【請求項 2 0】

前記タイムスタンプは、無効データを格納する無効ブロックが消去された時間を示す請求項 1 7 に記載の動作方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は半導体メモリに係り、より詳細には不揮発性メモリ及びメモリコントローラを含むメモリシステムの動作方法に関する。

【背景技術】

10

20

30

40

50

## 【0002】

半導体メモリ (semiconductor memory) はシリコン (Si、silicon)、ゲルマニウム (Ge、Germanium)、砒素ガリウム (GaAs、gallium arsenide)、リン化インジウム (InP、indium phosphide) 等のような半導体を利用して具現される記憶装置である。半導体メモリは大きく揮発性メモリ (Volatile memory) と不揮発性メモリ (Nonvolatile memory) とに区分される。

## 【0003】

揮発性メモリは電源供給が遮断されれば、格納しているデータを消失するメモリ装置である。揮発性メモリはSRAM (Static RAM)、DRAM (Dynamic RAM)、SDRAM (Synchronous DRAM) 等を含む。不揮発性メモリは電源供給が遮断されても格納しているデータを維持するメモリ装置である。不揮発性メモリにはROM (Read Only Memory)、PROM (Programmable ROM)、EPROM (Electrically Programmable ROM)、EEPROM (Electrically Erasable and Programmable ROM)、フラッシュメモリ、PRAM (Phase-change RAM)、MRAM (Magnetic RAM)、RRAM (登録商標) (Resistive RAM)、FRAM (登録商標) (Ferroelectric RAM) 等がある。

10

## 【0004】

不揮発性メモリの中の一部は書き込み前消去 (erase-before-write) 特性を有する。例えば、フラッシュメモリは書き込み前消去特性を有する。書き込み前消去特性を有する不揮発性メモリで、データが書き込まれる前に消去が先に遂行されなければならず、上書きは支援されていない。書き込み前消去特性を有する不揮発性メモリでの消去時間は動作性能を低下させる原因になる。

20

## 【先行技術文献】

## 【特許文献】

## 【0005】

【特許文献1】米国特許第7,975,119号公報

30

【特許文献2】米国特許第7,564,721号公報

【特許文献3】米国特許公開第2010/0023677号明細書

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

本発明の目的は向上された速度及び信頼性を有する不揮発性メモリ及びメモリコントローラを含むメモリシステムの動作方法を提供することにある。

## 【課題を解決するための手段】

## 【0007】

複数のメモリブロックを含む不揮発性メモリ及び前記不揮発性メモリを制御するメモリコントローラを含む本発明の実施形態によるメモリシステムの動作方法は、前記複数のメモリブロックの中で自由ブロックの割当間隔を計算する段階と、前記割当間隔にしたがって前記複数のメモリブロックの中で消去ブロックの数を調節する段階と、を含み、前記消去ブロックは、前記複数のメモリブロックの中で消去された状態のメモリブロックを示し、前記自由ブロックは、前記消去ブロックの中でデータを書き込むように選択されたメモリブロックを示す。

40

## 【0008】

実施形態として、前記割当間隔は、最も最近に前記自由ブロックに割当された予め定まれた個数のメモリブロックの割当間隔である。

実施形態として、前記消去ブロックの数を調節する段階で、前記割当間隔が増加すれば、前記消去ブロックの数が減少する。

50

実施形態として、前記消去ブロックの数を調節する段階で、前記割当間隔が減少すれば前記消去ブロックの数が増加する。

#### 【0009】

実施形態として、無効ブロックを消去して消去ブロックを生成する時、タイムスタンプ (time stamp) を格納する段階をさらに含み、前記無効ブロックは、前記複数のメモリブロックの中で無効データを格納し、前記データブロックが無効化されて生成されるメモリブロックであり、前記タイムスタンプは、前記無効ブロックが消去されて前記消去ブロックが生成された時間を示す。

#### 【0010】

実施形態として、前記タイムスタンプにしたがって、前記消去ブロックを再び消去する段階をさらに含む。

実施形態として、前記タイムスタンプが示す時間及び現在時間の差が閾値より大きい時、前記消去ブロックが再び消去される。

実施形態として、前記現在時間は、前記消去ブロックが前記自由ブロックに割当することを要請する要請が生成された時間を示す。

#### 【0011】

実施形態として、前記要請にしたがって、前記再び消去された消去ブロックが前記自由ブロックに割当される。

実施形態として、前記要請にしたがって、前記再び消去された消去ブロックではない他の消去ブロックが前記自由ブロックに割当される。

複数のメモリブロックを含む不揮発性メモリ及び前記不揮発性メモリを制御するメモリコントローラを含む本発明の他の実施形態によるメモリシステムの動作方法は、

#### 【0012】

無効ブロックを消去して消去ブロックを生成する時、タイムスタンプ (time stamp) を格納する段階と、前記タイムスタンプにしたがって、前記消去ブロックを再び消去する段階と、を含み、前記タイムスタンプは、前記無効ブロックが消去されて前記消去ブロックが生成された時間を示し、前記無効ブロックは、前記複数のメモリブロックの中で無効データを格納するメモリブロックであり、前記消去ブロックは、前記複数のメモリブロックの中で消去された状態であるメモリブロックを示す。

#### 【0013】

実施形態として、前記タイムスタンプが示す時間及び現在時間の差が閾値より大きい時、前記消去ブロックが再び消去される。

実施形態として、前記現在時間は、前記消去ブロックが前記自由ブロックに割当することを要請する要請が生成された時間を示し、前記自由ブロックは、前記複数のメモリブロックの中でデータを格納しない状態であり、データを格納するデータブロックに選択されるメモリブロックを示す。

#### 【0014】

実施形態として、前記要請にしたがって、前記再び消去された消去ブロックが前記自由ブロックに割当される。

実施形態として、前記要請にしたがって、前記再び消去された消去ブロックではない他の消去ブロックが前記自由ブロックに割当される。

#### 【発明の効果】

#### 【0015】

本発明によれば、自由ブロックが要請される前に予め消去ブロックが生成される。したがって、自由ブロックが要請される時、消去が遂行されず、自由ブロックが直ちに割当されるので、向上された速度を有するメモリシステムの動作方法が提供される。

また、本発明によれば、消去ブロックのうち、消去された後、経過した経過時間が閾値時間より大きい消去ブロックが再消去される。したがって、消去の後、長い時間が経過することによって消去ブロックで発生するエラーが防止されるので、向上された信頼性を有するメモリシステムの動作方法が提供される。

10

20

30

40

50

## 【図面の簡単な説明】

## 【0016】

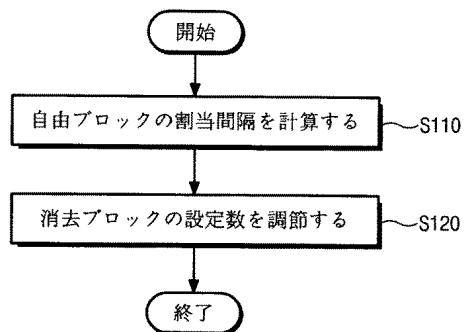

【図1】本発明の第1実施形態によるメモリシステムを示すブロック図。

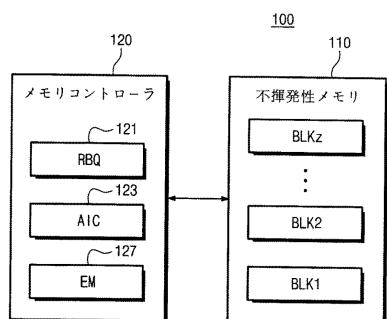

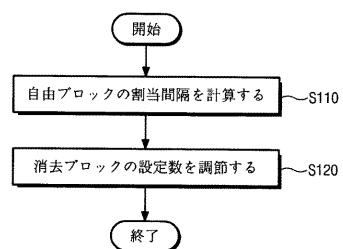

【図2】本発明の第1実施形態によるメモリシステムの動作方法を示す順序図。

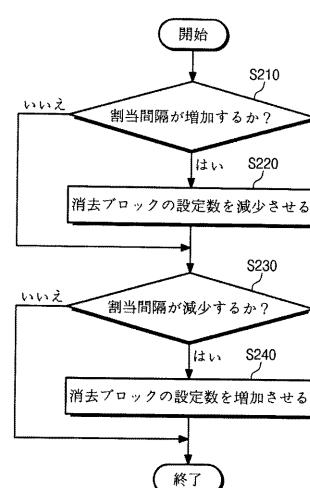

【図3】本発明の実施形態による設定数を調整する方法を示す順序図。

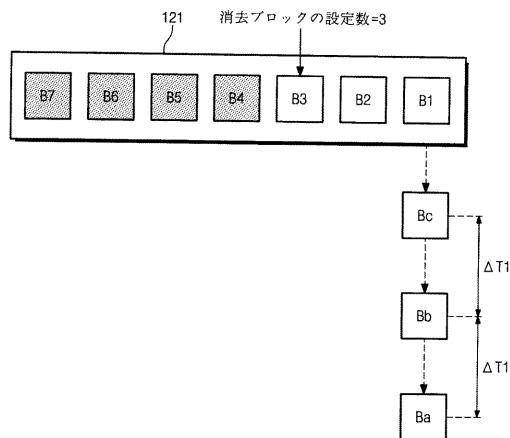

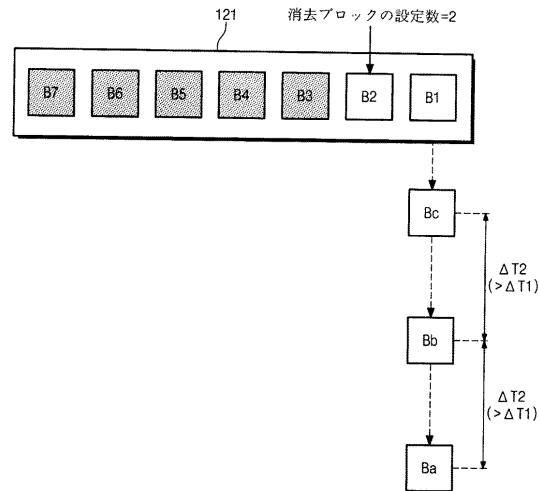

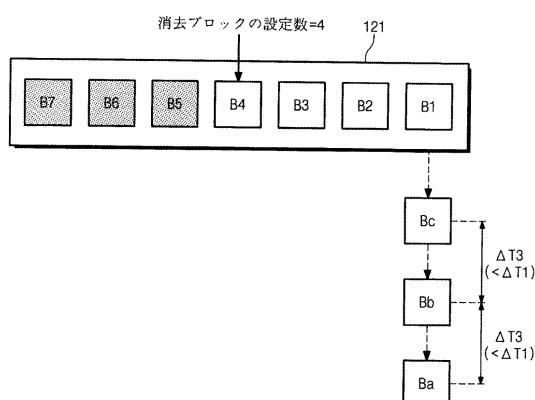

【図4】消去ブロックの設定数が調節される例を示す図。

【図5】消去ブロックの設定数が調節される例を示す図。

【図6】消去ブロックの設定数が調節される例を示す図。

【図7】本発明の第2実施形態によるメモリシステムを示すブロック図。

10

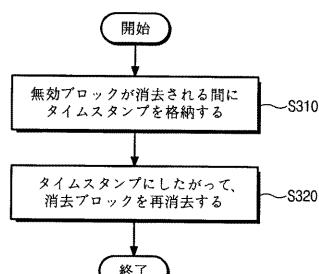

【図8】本発明の第2実施形態によるメモリシステムの動作方法を示す順序図。

【図9】本発明の実施形態によって、消去ブロックの再消去遂行する方法の第1例を示す順序図。

【図10】消去ブロックが再消去される例を示す図。

【図11】本発明の実施形態によって、消去ブロックの再消去を遂行する方法の第2例を示す順序図。

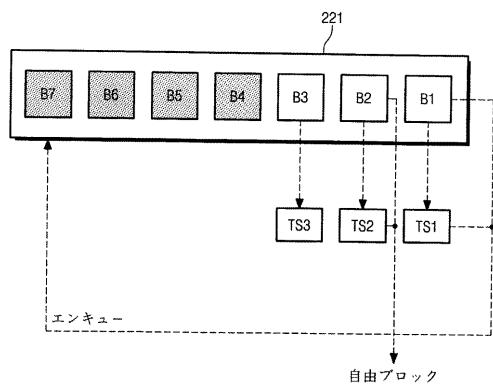

【図12】消去ブロックがエンキューされる例を示す図。

【図13】本発明の第3実施形態によるメモリシステムを示すブロック図。

【図14】本発明の第3実施形態によるメモリシステムの動作方法を示す順序図。

【図15】本発明の実施形態による不揮発性メモリを示すブロック図。

20

【図16】本発明の実施形態によるメモリブロックを示す回路図。

【図17】本発明の他の実施形態によるメモリブロックを示す回路図。

【図18】本発明の実施形態によるメモリコントローラを示すブロック図。

【図19】本発明の第4実施形態によるメモリシステムを示すブロック図。

【図20】本発明の第5実施形態によるメモリシステムを示すブロック図。

【図21】本発明の実施形態によるコンピューティング装置を示すブロック図。

## 【発明を実施するための形態】

## 【0017】

以下で、本発明が属する技術分野で通常の知識を有する者が本発明の技術的思想を容易に実施できるようにするために、本発明の実施形態を添付された図面を参照して説明する。

30

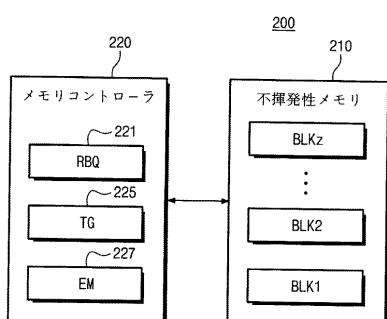

図1は本発明の第1実施形態によるメモリシステム100を示すブロック図である。図1を参照すれば、メモリシステム100は不揮発性メモリ110及びメモリコントローラ120を含む。

## 【0018】

不揮発性メモリ110はメモリコントローラ120の制御にしたがって、書き込み、読み出し、及び消去を遂行するように構成される。不揮発性メモリ110は複数のメモリブロックB1K1～B1Kzを含む。各メモリブロックはデータを格納できる複数のメモリセルを含む。各メモリブロックは不揮発性メモリ110の消去の単位である。例えば、不揮発性メモリ110の消去はメモリブロックの単位で遂行される。同一なメモリブロックのメモリセルは同時に消去される。

40

## 【0019】

各メモリブロックはデータブロック、無効ブロック、消去ブロック、又は自由ブロックである。データブロックはデータを格納するメモリブロックである。データブロックは有効データ又は無効データを格納する。無効ブロックは無効なデータのみを格納するメモリブロックである。無効ブロックはデータブロックが無効化されて生成される。消去ブロックは、データを格納せず、消去された状態のメモリブロックである。無効ブロックが消去されて消去ブロックが生成される。自由ブロックはデータを格納しない状態であり、データブロックとして選択されるメモリブロックである。自由ブロックは、消去ブロックから割当される。無効ブロック及び消去ブロックは予備ブロックと称される。

## 【0020】

50

メモリコントローラ 120 は不揮発性メモリ 110 を制御するように構成される。メモリコントローラ 120 は外部装置（例えば、メモリシステム 100 のホスト）の要請にしたがって、又は内部的に定められたスケジュールにしたがって、不揮発性メモリ 110 の書き込み、読み出し、又は消去を制御する。メモリコントローラ 120 は予備ブロックキューライ 121、割当間隔計算機 123、及び消去管理者 127 を含む。

予備ブロックキューライ 121 は複数のメモリブロック  $B_{LK1} \sim B_{LKz}$  の中で予備ブロックを管理する。データブロックが無効化されて無効ブロックが生成されれば、生成された無効ブロックは予備ブロックキューライ 121 に登録される。消去ブロックが自由ブロックに割当されれば、自由ブロックに割当された消去ブロックは予備ブロックキューライ 121 から削除される。

10

#### 【0021】

割当間隔計算機 123 は予備ブロックキューライ 121 の消去ブロックから自由ブロックが割当される間隔（以下で、割当間隔）を計算するように構成される。例示的に、割当間隔計算機 123 は最も最近に 2 以上の消去ブロックが自由ブロックに割当された間隔を計算する。割当間隔計算機 123 は、最も最近に、予め定まれた数の自由ブロックが割当された間隔（例えば、平均間隔）を計算する。割当間隔計算機 123 によって計算される割当間隔は時間情報を含む。

#### 【0022】

消去管理者 127 は予備ブロックキューライ 121 に登録された無効ブロックを消去して消去ブロックを生成する。消去管理者 127 は割当間隔計算機 123 によって計算される割当間隔に基づいて消去を遂行する。消去管理者 127 は消去ブロックの設定数を管理する。消去ブロックの設定数は予備ブロックキューライ 121 に登録されたメモリブロックの中で消去ブロックの数が到達しなければならない設定値を示す。予備ブロックキューライ 121 の消去ブロックが自由ブロックに割当されれば、消去ブロックの数が減少する。予備ブロックキューライ 121 の無効ブロックが消去されれば、消去ブロックの数が増加する。予備ブロックキューライ 121 の消去ブロックの数が設定数より少ない場合、消去管理者 127 は無効ブロックを消去することによって、消去ブロックの数を増加させる。予備ブロックキューライ 121 の消去ブロックの数が設定数より大きい場合、消去管理者 127 は自由ブロックが割当される間に無効ブロックを消去しないことによって、消去ブロックの数を減少させる。例示的に、消去ブロックの設定数は外部装置又は外部から受信される信号にしたがって調節される。例えば、消去ブロックの設定数の基本値が外部制御にしたがって設定され、以下に説明された方法によって消去ブロックの設定数が調節される。

20

#### 【0023】

図 2 は本発明の第 1 実施形態によるメモリシステム 100 の動作方法を示す順序図である。図 1 及び図 2 を参照すれば、S110 段階で、自由ブロックの割当間隔が計算される。割当間隔計算機 123 は、予め定まれた数の自由ブロックが最も最近に割当された割当間隔（例えば、平均割当間隔）を計算する。

S120 段階で、消去ブロックの設定数が調節される。例えば、消去管理者 127 は割当間隔にしたがって、設定数を調節する。即ち、消去管理者 127 は予備ブロックキューライ 121 で消去ブロックに維持されるメモリブロックの数を調節する。

30

#### 【0024】

図 3 は本発明の実施形態による設定数を調整する方法（S120 段階）を示す順序図である。図 1 及び図 3 を参照すれば、S210 段階で、割当間隔が増加するか否かが判別される。割当間隔が増加すれば、S220 段階で消去ブロックの設定数が減少する。即ち、予備ブロックキューライ 123 で消去ブロックに維持されるメモリブロックの数が減少する。

40

S230 段階で、割当間隔が減少するか否かが判別される。割当間隔が減少すれば、S240 段階で消去ブロックの設定数が増加する。即ち、予備ブロックキューライ 123 で消去ブロックに維持されるメモリブロックの数が増加する。

#### 【0025】

図 4 乃至図 6 は消去ブロックの設定数が調節される例を示す。先ず、図 1 及び図 4 を参

50

照すれば、予備ブロックキュー 121 に 7 つのメモリブロック B1 ~ B7 が登録される。メモリブロック Ba、Bb、Bc は最も最近に自由ブロックに割当されたメモリブロックである。メモリブロック Ba、Bb、Bc の割当間隔は第 1 割当間隔 T1 である。この時、予備メモリキュー 121 で維持される消去ブロックの設定数は 3 である。即ち、予備メモリキュー 121 に登録された 7 つのメモリブロック B1 ~ B7 の中で最も先に登録された 3 つのメモリブロック B1 ~ B3 が消去ブロックに維持される。残る 4 つのメモリブロック B4 ~ B7 は無効ブロックに維持される。予備ブロックキュー 121 の消去ブロックが自由ブロックに割当されれば、無効ブロックが消去されて消去ブロックの数が設定数に維持される。例えば、無効ブロックはメモリシステム 100 の遊休時間 (idle time) に、又はメモリシステム 100 が背景動作 (background operation) を遂行する時に消去される。10

#### 【0026】

図 4 で、自由ブロック Ba、Bb、Bc が割当される割当間隔は第 1 割当間隔 T1 で一定なものとして図示されている。しかし、自由ブロックの割当間隔は一定ではなくともよい。第 1 割当間隔 T1 は最も最近に割当された自由ブロック Ba、Bb、Bc の平均割当間隔である。例えば、第 1 割当間隔 T1 は最も最近に割当された自由ブロック Ba、Bb、Bc の加重された平均割当間隔である。加重値は、最も最近に割当された自由ブロックであるほど、増加する。

#### 【0027】

図 1、図 4、及び図 5 を参照すれば、メモリブロック Ba、Bb、Bc の割当間隔は第 2 割当間隔 T2 である。第 2 割当間隔 T2 は第 1 割当間隔 T1 より大きい。割当間隔が増加すれば、消去ブロックの設定数が減少する。例示的に、消去ブロックの設定数は 2 に減少する。即ち、予備ブロックキュー 121 に登録された 7 つのメモリブロック B1 ~ B7 の中で最も先に登録された 2 つのメモリブロック B1、B2 が消去ブロックとして維持される。残る 5 つのメモリブロック B3 ~ B7 は無効ブロックとして維持される。20

#### 【0028】

消去ブロックの数が設定数より大きい場合、自由ブロックが割当される間は無効ブロックは消去されない。即ち、消去ブロックの生成を中止することによって、消去ブロックの数が減少される。消去ブロックの数が設定数に到達すれば、消去ブロックの数が設定数に維持される。例えば、予備ブロックキュー 121 の消去ブロックが自由ブロックに割当されれば、無効ブロックが消去されて消去ブロックの数が設定数に維持される。例えば、無効ブロックはメモリシステム 100 の遊休時間に、又はメモリシステム 100 が背景動作 (background operation) を遂行する時に消去される。消去ブロックの数が設定数に到達するまで、メモリシステム 100 の遊休時間に又は背景動作の時に無効ブロックが順次的に消去される。30

#### 【0029】

図 5 で、自由ブロック Ba、Bb、Bc が割当される割当間隔は第 2 割当間隔 T2 で一定なものとして図示されている。しかし、自由ブロックの割当間隔は一定ではなくともよい。第 2 割当間隔 T2 は最も最近に割当された自由ブロック Ba、Bb、Bc の平均割当間隔である。例えば、第 2 割当間隔 T2 は最も最近に割当された自由ブロック Ba、Bb、Bc の加重された平均割当間隔である。加重値は、最も最近に割当された自由ブロックであるほど、増加する。40

#### 【0030】

図 1、図 4、及び図 6 を参照すれば、メモリブロック Ba、Bb、Bc の割当間隔は第 3 割当間隔 T3 である。第 3 割当間隔 T3 は第 1 割当間隔 T1 より小さい。割当間隔が減少すれば、消去ブロックの設定数が増加する。例示的に、消去ブロックの設定数は 4 に増加する。即ち、予備ブロックキュー 121 に登録された 7 つのメモリブロック B1 ~ B7 の中で最も先に登録された 4 つのメモリブロック B1 ~ B4 が消去ブロックとして維持される。残る 3 つのメモリブロック B5 ~ B7 は無効ブロックとして維持される。

#### 【0031】

10

20

30

40

50

消去ブロックの数が設定数より小さい場合、自由ブロックが割当されなくとも無効ブロックが消去される。即ち、消去ブロックの生成を増加させることによって、消去ブロックの数が増加される。消去ブロックの数が設定数に到達すれば、消去ブロックの数が設定数に維持される。例えば、予備ブロックキューワン・ツー・ワンの消去ブロックが自由ブロックに割当されれば、無効ブロックが消去されて消去ブロックの数が設定数に維持される。

【0032】

図6で、自由ブロックB a、B b、B cが割当される割当間隔は第3割当間隔T3で一定なものとして図示されている。しかし、自由ブロックの割当間隔は一定ではなくともよい。第3割当間隔T3は最も最近に割当された自由ブロックB a、B b、B cの平均割当間隔である。例えば、第3割当間隔T3は最も最近に割当された自由ブロックB a、B b、B cの加重された平均割当間隔である。加重値は、最も最近に割当された自由ブロックであるほど、増加する。

【0033】

上述したように、設定数に該当する消去ブロックが予備ブロックキューワン・ツー・ワンで維持される。自由ブロックを必要とする時、無効ブロックを消去する必要が無く、予備ブロックキューワン・ツー・ワンで維持される消去ブロックから自由ブロックが割当される。したがって、自由ブロックを割当する間に消去が遂行されないので、メモリシステムワン・ゼロ・ゼロの速度が向上する。

【0034】

消去ブロックのメモリセルの状態は時間が経過することによって、変化することができる。例えば、データリテンション(reten tion)特性によって、メモリセルの状態(例えば、閾値電圧)が変化することができる。また、消去ブロックと隣接するブロックで遂行されるプログラム又は読み出しの影響によって、消去ブロックで攪乱が発生し得る。メモリセルの状態が臨界値から大きく変化すれば、消去ブロックが自由ブロックに割当された後にデータが書き込まれるか、或いは書き込まれたデータが読み出される時、エラーが発生することがある。

【0035】

本発明の実施形態によれば、自由ブロックが割当される割当間隔にしたがって、予備メモリキューワン・ツー・ワンで維持される消去ブロックの数(即ち、設定数)が調節される。したがって、消去ブロックが臨界時間以上に放置されることによって発生するエラーが防止されるので、メモリシステムワン・ゼロ・ゼロの信頼性が向上する。

例示的に、設定数の基本値又は初期値は、メモリコントローラワン・ツー・ゼロ又は不揮発性メモリワン・ツー・ゼロに格納される。例えば、メモリコントローラワン・ツー・ゼロはROMのような不揮発性格納媒体に設定数の基本値又は初期値を格納することができる。設定数の基本値又は初期値が不揮発性メモリワン・ツー・ゼロに格納される場合、メモリコントローラワン・ツー・ゼロは電源が供給される時、不揮発性メモリワン・ツー・ゼロから設定数の初期値又は基本値を読み出すことができる。他の例として、設定数の初期値又は基本値は外部装置又は外部から受信される信号によって決定される。

【0036】

図7は本発明の第2実施形態によるメモリシステムツー・ゼロ・ゼロを示すブロック図である。図7を参照すれば、メモリシステムツー・ゼロ・ゼロは不揮発性メモリツー・ツー・ゼロ及びメモリコントローラツー・ツー・ゼロを含む。

不揮発性メモリツー・ツー・ゼロは複数のメモリブロックB L K 1 ~ B L K zを含む。複数のメモリブロックB L K 1 ~ B L K zは自由ブロック、データブロック、無効ブロック、又は消去ブロックを含む。不揮発性メモリツー・ツー・ゼロは図1乃至図7を参照して説明された不揮発性メモリワン・ツー・ゼロと同一の構造を有し、同一の方法で動作する。

【0037】

メモリコントローラツー・ツー・ゼロは予備ブロックキューワン・ツー・ツー・ゼロ、時間生成器ツー・ツー・ゼロ、及び消去管理者ツー・ツー・ゼロを含む。

予備ブロックキューワン・ツー・ツー・ゼロは複数のメモリブロックB L K 1 ~ B L K zの中で予備ブロ

10

20

30

40

50

ックを管理する。データブロックが無効化されて無効ブロックが生成されれば、生成された無効ブロックは予備ブロックキュー 221 に登録される。消去ブロックが自由ブロックに割当されれば、自由ブロックに割当された消去ブロックは予備ブロックキュー 221 から削除される。

時間生成器 225 は現在時間を示す情報を生成する。例えば、時間生成器 225 は自身で時間情報を生成する装置又は外部装置（例えば、メモリシステム 200 のホスト）から時間情報を受信して出力する装置である。

#### 【0038】

消去管理者 227 は予備ブロックキュー 221 に登録された無効ブロックを消去して消去ブロックを生成する。無効ブロックが消去されて消去ブロックが生成される時、消去管理者 227 は時間生成器 225 から出力される時間情報を獲得する。消去の時の時間情報は消去ブロックのタイムスタンプ（time stamp）として管理される。消去ブロックを自由ブロックに割当することを要請する要請が生成（又は受信）される時、消去管理者 227 は時間生成器 225 から時間情報を獲得する。要請の時の時間情報は現在時間である。消去管理者 227 は消去ブロックのタイムスタンプ及び現在時間に基づいて、消去ブロックを再消去自由ブロックに割当する。

10

#### 【0039】

図 8 は本発明の第 2 実施形態によるメモリシステム 200 の動作方法を示す順序図である。図 7 及び図 8 を参照すれば、S310 段階で、無効ブロックが消去される間にタイムスタンプが格納される。例えば、消去管理者 227 は予備ブロックキュー 221 に登録された無効ブロックを消去して消去ブロックを生成する。無効ブロックを消去する時、消去管理者 227 は時間生成器 225 から時間情報を受信し、受信された時間情報を消去ブロックのタイムスタンプとして格納する。例えば、タイムスタンプはメモリコントローラ 220 内に格納されるか、或いは又は不揮発性メモリ 210 に格納される。タイムスタンプは消去ブロックを管理するためのメタデータとして管理される。

20

#### 【0040】

S320 段階で、タイムスタンプにしたがって、消去ブロックが再消去される。例えば、消去管理者 227 は時間生成器 225 から時間情報を現在時間として受信できる。消去管理者 227 は選択された消去ブロックと連関されたタイムスタンプを現在時間と比較する。比較結果にしたがって、消去管理者 227 は選択された消去ブロックを再消去するか、或いは再消去遂行しない。

30

#### 【0041】

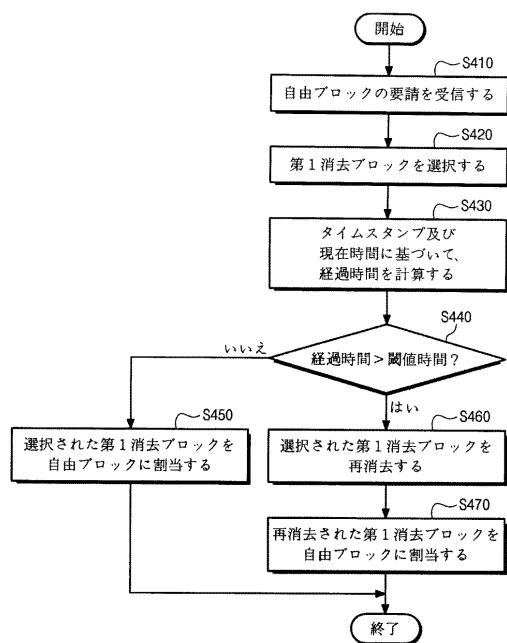

図 9 は本発明の実施形態によって、消去ブロックの再消去遂行する方法（S320 段階）の第 1 例を示す順序図である。図 7 乃至図 9 を参照すれば、S410 段階で、自由ブロックの要請が受信される。例えば、メモリコントローラ 220 は外部装置（例えば、メモリシステム 200 のホスト）の要請にしたがって、又は内部的に生成される要請にしたがって、自由ブロックの要請を生成する。例えば、内部的に生成される要請は、併合（merge）の要請である。併合要請は、1 つ又はそれ以上のデータブロックに書き込まれたデータを自由ブロックにコピーし、1 つ又はそれ以上のデータブロックを無効ブロックに設定する動作である。生成された要請は消去管理者 227 で受信される。

40

#### 【0042】

S420 段階で、第 1 消去ブロックが選択される。例えば、予備ブロックキュー 221 の消去ブロックの中で最も先に消去された消去ブロックが選択される。消去管理者 227 は最も先に消去された消去ブロックを第 1 消去ブロックとして選択する。

S430 段階で、タイムスタンプ及び現在時間に基づいて、経過時間が計算される。消去管理者 227 は第 1 消去ブロックと連関されたタイムスタンプを獲得する。

例えば、第 1 消去ブロックのタイムスタンプがメモリコントローラ 220 の内部メモリに格納されている場合、消去管理者 227 は内部メモリからタイムスタンプを読み出す。第 1 消去ブロックのタイムスタンプが不揮発性メモリ 210 に格納されている場合、消去管理者 227 は不揮発性メモリ 210 からタイムスタンプを読み出す。

50

例えば、消去ブロックのタイムスタンプは、表1のようなテーブル（以下で、消去テーブルであると称する）の形態で管理される。

【0043】

【表1】

| 消去ブロックのアドレス | タイムスタンプ |

|-------------|---------|

| ADDR_BLK1   | T1      |

| ADDR_BKL2   | T2      |

| ADDR_BLK3   | T3      |

10

【0044】

表1の消去テーブルに記載されたように、タイムスタンプは消去ブロックのアドレスとマッピング関係で管理される。第1消去ブロックのアドレスが識別されれば、消去テーブルに基づいて、第1消去ブロックのタイムスタンプが獲得される。消去テーブルはパワーオフの時に不揮発性メモリ210に格納され、パワーオンの時に、又は消去テーブルが最初に要求される時点で、メモリコントローラ220にローディングされる。

消去管理者227は時間生成器225から現在時間を獲得する。消去管理者227はタイムスタンプ及び現在時間を比較して経過時間を計算する。経過時間は、第1消去ブロックが消去された後、現在に到達する時までに経過した時間を示す。経過時間は、現在時間とタイムスタンプとが示す時間の差に該当する。

20

【0045】

S440段階で、経過時間が閾値時間より大きいか否かが判別される。閾値時間は、メモリコントローラ220が製造される時、メモリコントローラ220に入力される値である。閾値時間は、メモリコントローラ220が製造された後、メモリコントローラ220に格納される値であってもよい。閾値時間は、不揮発性メモリ210が製造される時、不揮発性メモリ210に入力される値である。閾値時間は不揮発性メモリ210が製造された後、不揮発性メモリ210に格納される値であってもよい。閾値時間は不揮発性メモリ210のメモリブロックBLK1～BLKzの特性によって決定される値である。閾値時間は、不揮発性メモリ210のメモリブロックBLK1～BLKzが消去された後、書き込み又は読み出しエラーを引き起こさない最大経過時間を示す。閾値時間は外部装置によって又は外部から受信される信号にしたがって決定される。

30

消去管理者227はメモリコントローラ220内で閾値時間を獲得するか、或いは不揮発性メモリ210から閾値時間を獲得する。消去管理者227は獲得された閾値時間を経過時間と比較する。

【0046】

経過時間が閾値時間より大きくない場合、第1消去ブロックは書き込み又は読み出しエラーを引き起こさない。したがって、S450段階で、第1消去ブロックは自由ブロックに割当される。例えば、第1消去ブロックは再消去のような別の処理無しで、自由ブロックに割当される。

40

経過時間が閾値時間より大きい場合、第1消去ブロックは書き込み又は読み出しエラーを引き起こし得る。この時、S460段階で、第1消去ブロックが再消去される。消去管理者227は第1消去ブロックを再消去する。以後に、S470段階で、再消去された第1消去ブロックが自由ブロックに割当される。

【0047】

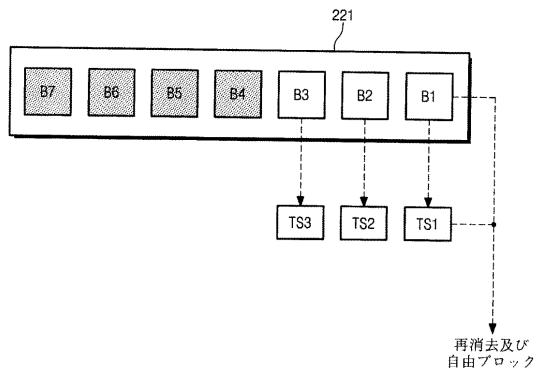

図10は消去ブロックが再消去される例を示す。図7乃至図10を参照すれば、予備ブロックキュー221に7つのメモリブロックB1～B7が登録される。予備ブロックキュー221で、消去ブロックの設定数は3である。即ち、予備ブロックキュー221に登録された7つのメモリブロックB1～B7の中で最も先に登録された3つのメモリブロック

50

B 1 ~ B 3 が消去ブロックとして維持される。残る 4 つのメモリブロック B 4 ~ B 7 は無効ブロックとして維持される。設定数は固定された値である。

【 0 0 4 8 】

第 1 メモリブロック B 1 が消去される時、第 1 タイムスタンプ T S 1 が生成される。第 2 メモリブロック B 2 が消去される時、第 2 タイムスタンプ T S 2 が生成される。第 3 メモリブロック B 3 が消去される時、第 3 タイムスタンプ T S 3 が生成される。生成されたタイムスタンプは消去タイムテーブルに格納されて管理される。

自由ブロックが要請される時、第 1 番目の消去ブロックである第 1 メモリブロック B 1 の第 1 タイムスタンプ T S 1 が現在時間と比較される。現在時間と第 1 タイムスタンプ T S 1 との差である経過時間が閾値時間より大きい時、第 1 メモリブロック B 1 は消去された後に自由ブロックに割当される。

10

【 0 0 4 9 】

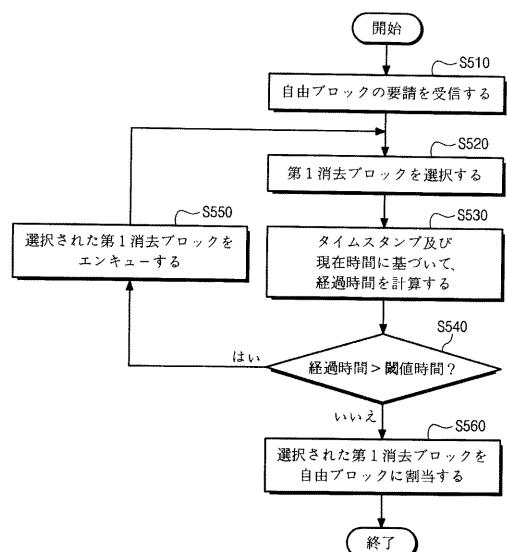

図 1 1 は本発明の実施形態によって、消去ブロックの再消去遂行する方法 ( S 3 2 0 段階 ) の第 2 例を示す順序図である。図 7 、図 8 、及び図 1 1 を参照すれば、S 5 1 0 段階で、自由ブロックの要請が受信される。S 5 2 0 段階で、第 1 消去ブロックが選択される。S 5 3 0 段階で、タイムスタンプ及び現在時間に基づいて、経過時間が計算される。S 5 4 0 段階で、経過時間が閾値時間より大きいか否かが判別される。S 5 1 0 段階乃至 S 5 4 0 段階は、図 9 の S 4 1 0 段階乃至 S 4 4 0 段階と同一の方法で遂行される。したがって、重複する説明は省略する。

20

【 0 0 5 0 】

経過時間が閾値時間より大きい場合、第 1 消去ブロックは書込み又は読出しエラーを引き起こし得る。したがって、S 5 5 0 段階で、第 1 消去ブロックは予備ブロックキュー 2 2 1 にエンキュー ( enqueue ) される。即ち、第 1 消去ブロックは無効ブロックに設定され、予備ブロックキュー 2 2 1 にエンキューされる。予備ブロックキュー 2 2 1 にエンキューされれば、消去管理者 2 2 7 の制御スケジュールにしたがって、消去が遂行され、消去ブロックに再び設定される。以後に、S 5 2 0 段階で、次の消去ブロックが選択され、S 5 3 0 段階及び S 5 4 0 段階が再び遂行される。

経過時間が閾値時間より大きければ、第 1 消去ブロックは書込み又は読出しエラーを引き起こさない。したがって、S 5 6 0 段階で、第 1 消去ブロックが自由ブロックに割当される。

30

【 0 0 5 1 】

図 1 2 は消去ブロックがエンキューされる例を示す。図 7 、図 8 、図 1 1 、及び図 1 2 を参照すれば、予備ブロックキュー 2 2 1 に 7 つのメモリブロック B 1 ~ B 7 が登録される。予備ブロックキュー 2 2 1 で、消去ブロックの設定数は 3 である。即ち、予備ブロックキュー 2 2 1 に登録された 7 つのメモリブロック B 1 ~ B 7 の中で最も先に登録された 3 つのメモリブロック B 1 ~ B 3 が消去ブロックとして維持される。残る 4 つのメモリブロック B 4 ~ B 7 は無効ブロックとして維持される。設定数は固定された値である。

【 0 0 5 2 】

第 1 メモリブロック B 1 が消去される時、第 1 タイムスタンプ T S 1 が生成される。第 2 メモリブロック B 2 が消去される時、第 2 タイムスタンプ T S 2 が生成される。第 3 メモリブロック B 3 が消去される時、第 3 タイムスタンプ T S 3 が生成される。生成されたタイムスタンプは消去タイムテーブルに格納されて管理される。

40

自由ブロックが要請される時、第 1 番目の消去ブロックである第 1 メモリブロック B 1 の第 1 タイムスタンプ T S 1 が現在時間と比較される。現在時間と第 1 タイムスタンプ T S 1 との差である経過時間が閾値時間より大きい時、第 1 メモリブロック B 1 は予備ブロックキュー 2 2 1 に再びエンキュー ( enqueue ) される。

以後に、第 2 メモリブロック B 2 が選択される。第 2 メモリブロック B 2 の第 2 タイムスタンプ T S 2 が現在時間と比較される。現在時間と第 2 タイムスタンプ T S 2 との差である経過時間が閾値時間より大きくない時、第 2 メモリブロック B 2 は自由ブロックに割当される。

50

## 【0053】

上述したように、消去管理者 227 は予備ブロックキュー 221 に登録されたメモリブロックの中で設定数に該当するメモリブロックを消去ブロックとして維持する。自由ブロックが要請される時、選択された消去ブロックのタイムスタンプと現在時間とが比較される。即ち、選択された消去ブロックが消去された後、閾値時間が経過したか否かが判別される。消去された後、閾値時間が経過した場合、選択された消去ブロックは再消去される。したがって、消去ブロックが臨界時間以上に放置されることによって発生するエラーが防止されるので、メモリシステム 200 の信頼性が向上する。

## 【0054】

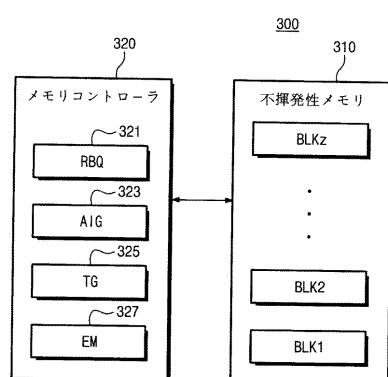

図 13 は本発明の第 3 実施形態によるメモリシステム 300 を示すブロック図である。

図 13 を参照すれば、メモリシステム 300 は不揮発性メモリ 310 及びメモリコントローラ 320 を含む。

不揮発性メモリ 310 はメモリコントローラ 320 の制御にしたがって、書き込み、読み出し、及び消去を遂行するように構成される。不揮発性メモリ 310 は複数のメモリブロック BLK1 ~ BLKz を含む。

## 【0055】

メモリコントローラ 320 は不揮発性メモリ 310 を制御するように構成される。メモリコントローラ 320 は予備ブロックキュー 321、割当間隔計算機 323、時間生成器 325、及び消去管理者 127 を含む。

第 3 実施形態によるメモリシステム 300 は、図 1 を参照して説明されたメモリシステム 100 及び図 7 を参照して説明されたメモリシステム 200 が組合された形態である。即ち、メモリシステム 300 は予備ブロックキュー 321 で維持される消去ブロックの数である設定数を調節することができ、消去ブロックのタイムスタンプ及び現在時間によって再消去遂行することができる。

## 【0056】

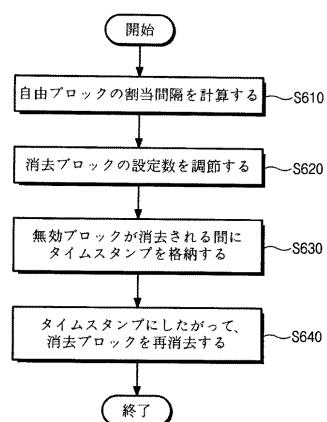

図 14 は本発明の第 3 実施形態によるメモリシステム 300 の動作方法を示す順序図である。図 13 及び図 14 を参照すれば、S610 段階で、自由ブロックの割当間隔が計算される。割当間隔計算機 323 は、予め定まれた数の自由ブロックが最も最近に割当された割当間隔（例えば、平均割当間隔）を計算する。

S620 段階で、消去ブロックの設定数が調節される。例えば、消去管理者 327 は割当間隔にしたがって、設定数を調節する。即ち、消去管理者 327 は予備ブロックキュー 321 で消去ブロックに維持されるメモリブロックの数を調節する。設定数は、図 3 乃至図 6 を参照して説明された方法によって調節される。

S630 段階で、無効ブロックが消去される間にタイムスタンプが格納される。無効ブロックを消去する時、消去管理者 327 は時間生成器 325 から時間情報を受信し、受信された時間情報を消去ブロックのタイムスタンプとして格納する。

## 【0057】

S640 段階で、タイムスタンプにしたがって、消去ブロックが再消去される。例えば、消去管理者 327 は時間生成器 325 から時間情報を現在時間として受信する。消去管理者 327 は選択された消去ブロックと連関されたタイムスタンプを現在時間と比較する。比較結果にしたがって、消去管理者 327 は選択された消去ブロックを再消去遂行するが再消去遂行しないこともあります。再消去は図 9 乃至図 12 を参照して説明された方法によって遂行される。

即ち、メモリシステム 300 は自由ブロックが割当される割当間隔にしたがって、予備ブロックキュー 321 の設定数を調節する。また、自由ブロックが要請される時、選択された消去ブロックが消去された後、閾値時間より長い経過時間が経過したことによって、消去ブロックが再消去される。

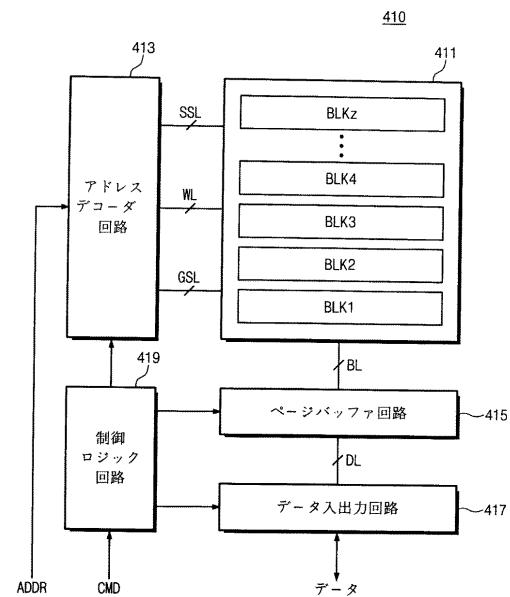

## 【0058】

図 15 は本発明の実施形態による不揮発性メモリ 410 を示すブロック図である。図 15 を参照すれば、不揮発性メモリ 410 はメモリセルアレイ 411、アドレスデコーダ回

10

20

30

40

50

路 4 1 3、ページバッファ回路 4 1 5、データ入出力回路 4 1 7、及び制御ロジック回路 4 1 9 を含む。

メモリセルアレイ 4 1 1 は、図 1、図 7、及び図 13 を参照して説明されたように、複数のメモリブロック B L K 1 ~ B L K z を含む。各メモリブロックは複数のメモリセルを含む。各メモリブロックは少なくとも 1 つの接地選択ライン G S L、複数のワードライン W L、及び少なくとも 1 つのストリング選択ライン S S L を通じてアドレスデコーダ回路 4 1 3 に連結される。各メモリブロックは複数のビットライン B L を通じてページバッファ回路 4 1 5 に連結される。複数のメモリブロック B L K 1 ~ B L K z は複数のビットライン B L に共通に連結される。複数のメモリブロック B L K 1 ~ B L K z のメモリセルは同一な構造を有する。

10

#### 【 0 0 5 9 】

アドレスデコーダ回路 4 1 3 は複数の接地選択ライン G S L、複数のワードライン W L、及び複数のストリング選択ライン S S L を通じてメモリセルアレイ 4 1 1 に連結される。アドレスデコーダ回路 4 1 3 は制御ロジック回路 4 1 9 の制御にしたがって動作する。アドレスデコーダ回路 4 1 3 はメモリコントローラ 1 2 0 からアドレスを受信する。アドレスデコーダ回路 4 1 3 は受信されたアドレス A D D R をデコーディングし、デコーディングされたアドレスにしたがってワードライン W L に印加される電圧を制御する。

#### 【 0 0 6 0 】

ページバッファ回路 4 1 5 は複数のビットライン B L を通じてメモリセルアレイ 4 1 1 に連結される。ページバッファ回路 4 1 5 は複数のデータライン D L を通じてデータ入出力回路 4 1 7 と連結される。ページバッファ回路 4 1 5 は制御ロジック回路 4 1 9 の制御にしたがって動作する。

20

ページバッファ回路 4 1 5 はメモリセルアレイ 4 1 1 のメモリセルにプログラムされるデータ又はメモリセルから読み出されるデータを格納する。プログラムの時に、ページバッファ回路 4 1 5 はメモリセルにプログラムされるデータを格納する。格納されたデータに基づいて、ページバッファ回路 4 1 5 は複数のビットライン B L をバイアスできる。プログラムの時に、ページバッファ回路 4 1 5 は書き込みドライバとして機能する。読み出しの時に、ページバッファ回路 4 1 5 はビットライン B L の電圧をセンシングし、センシング結果を格納する。読み出しの時に、ページバッファ回路 4 1 5 は感知増幅器として機能する。

30

#### 【 0 0 6 1 】

データ入出力回路 4 1 7 は複数のデータライン D L を通じてページバッファ回路 4 1 5 と連結される。データ入出力回路 4 1 7 はメモリコントローラ 1 2 0、2 2 0、又は 3 2 0（図 1、図 7、又は図 13 参照）とデータ D A T A を交換する。

データ入出力回路 4 1 7 は受信されるデータ D A T A を臨時に格納する。データ入出力回路 4 1 7 は格納されたデータをページバッファ回路 4 1 5 に伝達する。データ入出力回路 4 1 7 はページバッファ回路 4 1 5 から伝達されるデータ D A T A を臨時に格納する。データ入出力回路 4 1 7 は格納されたデータ D A T A を外部へ伝送する。データ入出力回路 4 1 7 はバッファメモリとして機能する。

#### 【 0 0 6 2 】

制御ロジック回路 4 1 9 はメモリコントローラ 4 2 0 からコマンド C M D を受信する。制御ロジック回路 4 1 9 は受信されたコマンド C M D をデコーディングし、デコーディングされたコマンドにしたがって不揮発性メモリ 4 1 0 の諸般動作を制御する。制御ロジック回路 4 1 9 はメモリコントローラ 4 2 0 から多様な制御信号及び電圧をさらに受信する。

40

設定数は不揮発性メモリ 4 1 0 に格納される。例えば、設定数は複数のメモリブロック B L K 1 ~ B L K z の中でメタデータを格納するように設定されたメモリブロックに格納される。設定数は不揮発性メモリ 4 1 0 のヒューズ回路（図示せず）に格納される。ヒューズ回路（図示せず）は制御ロジック回路 4 1 9 内に提供される。

#### 【 0 0 6 3 】

50

各メモリブロックのタイムスタンプは不揮発性メモリ410に格納される。例えば、タイムスタンプは複数のメモリブロックB L K 1～B L K zの中でメタデータを格納するように設定されたメモリブロックに格納される。タイムスタンプは対応するメモリブロックに格納される。例えば、第1メモリブロックB L K 1のタイムスタンプは、第1メモリブロックB L K 1のメモリセルの中でメタデータを格納するように設定されたメモリセルに格納される。

#### 【0064】

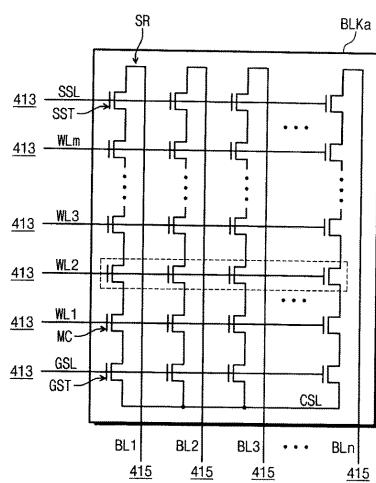

図16は本発明の実施形態によるメモリブロックB L K aを示す回路図である。例示的に、図15に図示されたメモリセルアレイ411の複数のメモリブロックB L K 1～B L K zの中で1つのメモリブロックB L K aが図16に図示される。

図15及び図16を参照すれば、メモリブロックB L K aは複数のストリングS Rを含む。複数のストリングS Rは複数のビットラインB L 1～B L nに各々連結される。各ストリングS Rは接地選択トランジスタG S T、メモリセルM C、及びストリング選択トランジスタS S Tを含む。

#### 【0065】

各ストリングS Rの接地選択トランジスタG S TはメモリセルM C及び共通ソースラインC S Lの間に連結される。複数のストリングS Rの接地選択トランジスタG S Tは共通ソースラインC S Lに共通に連結される。

各ストリングS Rのストリング選択トランジスタS S TはメモリセルM C及びビットラインB Lの間に連結される。複数のストリングS Rのストリング選択トランジスタS S Tは複数のビットラインB L 1～B L nに各々連結される。複数のビットラインB L 1～B L nはページバッファ回路415に連結される。

#### 【0066】

各ストリングS Rで、接地選択トランジスタG S T及びストリング選択トランジスタS S Tの間に複数のメモリセルM Cが提供される。各ストリングS Rで、複数のメモリセルM Cは直列連結される。

複数のストリングS Rで、共通ソースラインC S Lから同一の順序に位置したメモリセルM Cは1つのワードラインに共通に連結される。複数のストリングS RのメモリセルM Cは複数のワードラインW L 1～W L mに連結される。複数のワードラインW L 1～W L mはアドレスデコーダ回路413に連結される。

1つのメモリセルM Cは1つ又は2つ以上のビットを格納することができる。

#### 【0067】

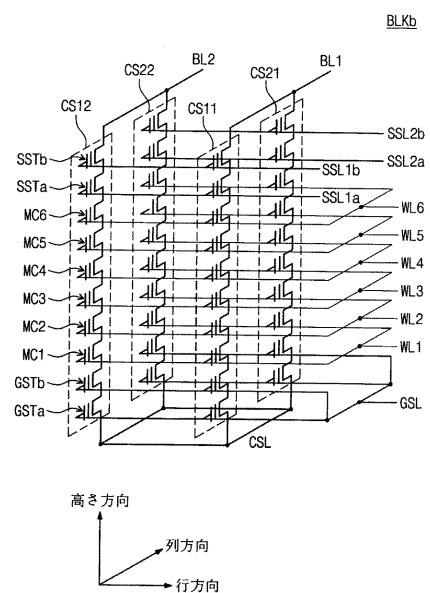

図17は本発明の他の実施形態によるメモリブロックB L K bを示す回路図である。図17を参照すれば、メモリブロックB L K bは複数のセルストリングC S 1 1～C S 2 1、C S 1 2～C S 2 2を含む。複数のセルストリングC S 1 1～C S 2 1、C S 1 2～C S 2 2は行方向(row direction)及び列方向(column direction)に沿って配列されて、行及び列を形成する。

例えば、行方向(row direction)に沿って配列されたセルストリングC S 1 1、C S 1 2は第1行を形成し、行方向(row direction)に沿って配列されたセルストリングC S 2 1、C S 2 2は第2行を形成する。列方向(column direction)に沿って配列されたセルストリングC S 1 1、C S 2 1は第1列を形成し、列方向(column direction)に沿って配列されたセルストリングC S 1 2、C S 2 2は第2列を形成する。

#### 【0068】

各セルストリングは複数のセルトランジスタを含む。複数のセルトランジスタは電荷捕獲型(charge trap type)セルトランジスタである。即ち、複数のセルトランジスタは絶縁膜に電荷を捕獲することによって、プログラムされ、絶縁膜に捕獲された電荷を流出することによって、消去される。

複数のセルトランジスタは接地選択トランジスタG S T a、G S T b、メモリセルM C 1～M C 6、及びストリング選択トランジスタS S T a、S S T bを含む。各セルストリ

10

20

30

40

50

ングの接地選択トランジスタ G S T a、 G S T b、 メモリセル M C 1 ~ M C 6、 及びストリング選択トランジスタ S S T a、 G S T b はセルストリング C S 1 1 ~ C S 2 1、 C S 1 2 ~ C S 2 2 が行及び列に沿って配列される平面（例えば、メモリブロック B L K b の基板の上の平面）と垂直になる高さ方向に積層される。

最下端の接地選択トランジスタ G S T a は共通ソースライン C S L に共通に連結される。

#### 【 0 0 6 9 】

複数のセルストリング C S 1 1 ~ C S 2 1、 C S 1 2 ~ C S 2 2 の接地選択トランジスタ G S T a、 G S T b は接地選択ライン G S L に共通に連結される。

例示的に、同一の高さ（又は順序）の接地選択トランジスタは同一の接地選択ラインに連結され、互に異なる高さ（又は順序）を有する接地選択トランジスタは互に異なる接地選択ラインに連結される。例えば、第1高さの接地選択トランジスタ G S T a は第1接地選択ラインに共通に連結され、第2高さの接地選択トランジスタ G S T b は第2接地選択ラインに共通に連結される。

#### 【 0 0 7 0 】

例示的に、同一の行の接地選択トランジスタは同一の接地選択ラインに連結され、互に異なる行の接地選択トランジスタは互に異なる接地選択ラインに連結される。例えば、第1行のセルストリング C S 1 1、 C S 1 2 の接地選択トランジスタ G S T a、 G S T b は第1接地選択ラインに連結され、第2行のセルストリング C S 2 1、 C S 2 2 の接地選択トランジスタ G S T a、 G S T b は第2接地選択ラインに連結される。

#### 【 0 0 7 1 】

基板（又は接地選択トランジスタ G S T ）から同一の高さ（又は順序）に位置したメモリセルは1つのワードラインに共通に連結され、互に異なる高さ（又は順序）に位置したメモリセルは互に異なるワードライン W L 1 ~ W L 6 に各々連結される。例えば、メモリセル M C 1 はワードライン W L 1 に共通に連結される。メモリセル M C 2 はワードライン W L 2 に共通に連結される。メモリセル M C 3 はワードライン W L 3 に共通に連結される。メモリセル M C 4 はワードライン W L 4 に共通に連結される。メモリセル M C 5 はワードライン W L 5 に共通に連結される。メモリセル M C 6 はワードライン W L 6 に共通に連結される。

#### 【 0 0 7 2 】

複数のセルストリング C S 1 1 ~ C S 2 1、 C S 1 2 ~ C S 2 2 の同一の高さ（又は順序）の第1ストリング選択トランジスタ S S T a で、互に異なる行の第1ストリング選択トランジスタ S S T a は互に異なるストリング選択ライン S S L 1 a ~ S S L 2 a に各々連結される。例えば、セルストリング C S 1 1、 C S 1 2 の第1ストリング選択トランジスタ S S T a はストリング選択ライン S S L 1 a に共通に連結される。セルストリング C S 2 1、 C S 2 2 の第1ストリング選択トランジスタ S S T a はストリング選択ライン S S L 2 a に共通に連結される。

#### 【 0 0 7 3 】

複数のセルストリング C S 1 1 ~ C S 2 1、 C S 1 2 ~ C S 2 2 の同一の高さ（又は順序）の第2ストリング選択トランジスタ S S T b で、互に異なる行の第2ストリング選択トランジスタ S S T b は互に異なるストリング選択ライン S S L 1 b ~ S S L 2 b に各々連結される。例えば、セルストリング C S 1 1、 C S 1 2 の第2ストリング選択トランジスタ S S T b はストリング選択ライン S S L 1 b に共通に連結される。セルストリング C S 2 1、 C S 2 2 の第2ストリング選択トランジスタ S S T b はストリング選択ライン S S L 2 b に共通に連結される。

#### 【 0 0 7 4 】

即ち、互に異なる行のセルストリングは互に異なるストリング選択ラインに連結される。同一の行のセルストリングの同一の高さ（又は順序）のストリング選択トランジスタは同一のストリング選択ラインに連結される。同一の行のセルストリングの互に異なる高さ（又は順序）のストリング選択トランジスタは互に異なるストリング選択ラインに連結さ

10

20

30

40

50

れる。

例示的に、同一の行のセルストリングのストリング選択トランジスタは1つのストリング選択ラインに共通に連結される。例えば、第1行のセルストリングCS11、CS12のストリング選択トランジスタSSTa、SSTbは1つのストリング選択ラインに共通に連結される。第2行のセルストリングCS21、CS22のストリング選択トランジスタSSTa、SSTbは1つのストリング選択ラインに共通に連結される。

【0075】

複数のセルストリングCS11～CS21、CS12～CS22の列は互に異なるビットラインBL1、BL2に各々連結される。例えば、第1列のセルストリングCS11～CS21のストリング選択トランジスタSSTbはビットラインBL1に共通に連結される。第2列のセルストリングCS12～CS22のストリング選択トランジスタSSTはビットラインBL2に共通に連結される。

【0076】

図17に図示されたメモリブロックBLKbは例示的なものである。本発明の技術的的思想は図17に図示されたメモリブロックBLKbに限定されない。例えば、セルストリングの行の数は増加又は減少してもよい。セルストリングの行の数を変更することによって、セルストリングの行に連結されるストリング選択ライン又は接地選択ラインの数及び1つのビットラインに連結されるセルストリングの数もまた変更することができる。

セルストリングの列の数は増加又は減少してもよい。セルストリングの列の数を変更することによって、セルストリングの列に連結されるビットラインの数及び1つのストリング選択ラインに連結されるセルストリングの数もまた変更することができる。

セルストリングの高さは増加又は減少してもよい。例えば、セルストリングの各々に積層される接地選択トランジスタ、メモリセル又はストリング選択トランジスタの数は増加又は減少することができる。

【0077】

例示的に、書き込み及び読み出しはセルストリングCS11～CS21、CS12～CS22の行の単位に遂行することができる。ストリング選択ラインSSL1a、SSL1b、SSL2a、SSL2bによって、セルストリングCS11～CS21、CS12～CS22は1つの行単位で選択されることができる。

セルストリングCS11～CS21、CS12～CS22の選択された行で、書き込み及び読み出しはワードラインの単位で遂行されることができる。セルストリングCS11～CS21、CS12～CS22の選択された行で、選択されたワードラインに連結されたメモリセルがプログラムされる。

【0078】

図16に図示されたメモリブロックBLKaと比較すれば、メモリブロックBLKbは高さ方向に積層された構造を有する。メモリブロックBLKbに提供されるメモリセルの数は、メモリブロックBLKaに提供されるメモリセルの数より多いことがある。したがって、メモリブロックBLKbを消去するのに必要とする時間はメモリブロックBLKaを消去するのに必要とする時間より長い。また、メモリブロックBLKの消去を検証するのに必要とする時間は、メモリブロックBLKaの消去を検証するのに必要とする時間よりさらに長い。即ち、設定数に該当する消去ブロックが予め準備される本発明の技術的的思想は、図17に図示されたような積層構造のメモリブロックでさらに大きい効用を有することができる。

【0079】

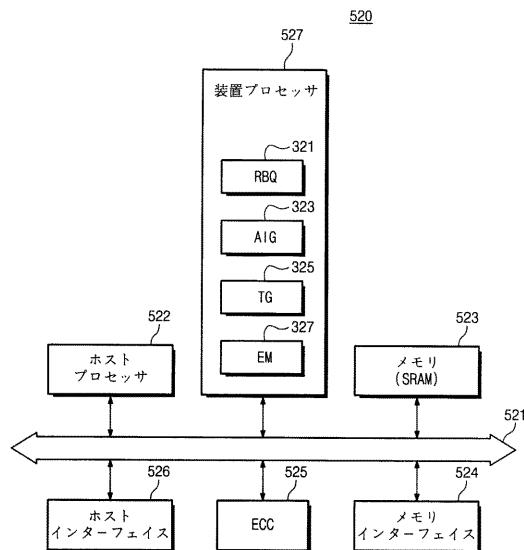

図18は本発明の実施形態によるメモリコントローラ520を示すブロック図である。図18を参照すれば、メモリコントローラ520はバス521、ホストプロセッサ522、メモリ523、メモリインターフェイス524、エラー訂正ブロック525、ホストインターフェイス526、及び装置プロセッサ527を含む。

バス521はメモリコントローラ520の構成要素の間にチャンネルを提供するように構成される。

10

20

30

40

50

## 【0080】

ホストプロセッサ522は外部ホストとの通信を制御する。ホストプロセッサ522は外部ホストから受信されるコマンド又はデータを処理する。ホストプロセッサ522は外部ホストからホストインターフェイス526を通じて受信されるコマンド又はデータをメモリ523に格納し、格納されたコマンド又はデータの制御を装置プロセッサ527に伝達する。ホストプロセッサ522はメモリ523に格納されたデータをホストインターフェイス526を通じて外部ホストへ出力する。ホストプロセッサ522は外部ホストと連関された諸般動作を制御する。

## 【0081】

メモリ523はプロセッサ522の動作メモリ、キャッシュメモリ、又はバッファメモリとして使用される。メモリ523はプロセッサ522が実行するコード及び命令を格納する。メモリ523はプロセッサ522によって処理されるデータを格納する。メモリ223はSRAMを含む。

メモリインターフェイス524はプロセッサ522の制御にしたがって、不揮発性メモリ410との通信を遂行する。

## 【0082】

エラー訂正ブロック525はエラー訂正を遂行する。エラー訂正ブロック525は不揮発性メモリ410に書き込まれるデータに基づいて、エラー訂正を遂行するためのパリティを生成する。データ及びパリティはメモリインターフェイス524を通じて不揮発性メモリ510に伝送され、不揮発性メモリ410に書き込まれる。エラー訂正ブロック525はメモリインターフェイスを通じて不揮発性メモリ510から読み出されるデータ及びパリティを利用して、データのエラー訂正を遂行する。

## 【0083】

ホストインターフェイス526はプロセッサ522の制御によって、外部のホストと通信する。ホストインターフェイス526はSATA(Serial AT Attachment)、eSATA、PCI(Peripheral Component Interconnect)、PCI-e、SCSI(Small Computer System Interface)、USB(Universal Serial Bus)、Mini USB、Micro USB、Firewire、NVMe等のような多様な通信方式の中で少なくとも1つに基づいて通信を遂行することができる。

## 【0084】

装置プロセッサ527は不揮発性メモリ410(図15参照)との通信を制御する。装置プロセッサ527はメモリ523に格納されたコマンドに基づいて、メモリインターフェイス524を通じて不揮発性メモリ410へ内部コマンドを伝送する。装置プロセッサ527はメモリ523に格納されたデータをメモリインターフェイス524を通じて不揮発性メモリ410へ伝送する。装置プロセッサ527は不揮発性メモリ410からメモリインターフェイス524を通じて受信されるデータをメモリ523に格納する。装置プロセッサ527はメモリ523に格納されたデータに対する制御をホストプロセッサ522に伝達する。装置プロセッサ523は不揮発性メモリ410と連関された諸般動作を制御する。

## 【0085】

装置プロセッサ527は不揮発性メモリ410のメモリブロックBLK1～BLKzの消去を管理する。装置プロセッサ527は予備ブロックキューリー321、割当間隔計算機323、時間生成器325、及び消去管理者327を含む。予備ブロックキューリー321、割当間隔計算機323、時間生成器325、及び消去管理者327の動作及び機能は図1乃至図14を参照して詳細に説明したので、それ以上の説明は省略する。

## 【0086】

例示的に、図1乃至図6を参照して説明したように、装置プロセッサ527の構成要素の中で時間生成器325は提供されなくともよい。即ち、装置プロセッサ527は設定数を調節する機能を支援するが、タイムスタンプにしたがって消去ブロックの再消去遂行す

10

20

30

40

50

る機能は支援しなくともよい。他の例として、図7乃至図12を参照して説明したように、装置プロセッサ527に割当間隔計算機323が提供されなくともよい。即ち、装置プロセッサ527はタイムスタンプにしたがって消去ブロックを再消去する機能を支援するが、設定数を調節する機能は支援しなくともよい。

#### 【0087】

例示的に、予備ブロックキュー321、割当間隔計算機323、時間生成器325、及び消去管理者327は全て装置プロセッサ527によって駆動されるソフトウェアで具現されることができる。予備ブロックキュー321、割当間隔計算機323、時間生成器325、及び消去管理者327は全てハードウェアで具現されることができる。予備ブロックキュー321、割当間隔計算機323、時間生成器325、及び消去管理者327の中で少なくとも1つはハードウェアで具現され、少なくともその他の1つは装置プロセッサ527によって駆動されるソフトウェアで具現することができる。

#### 【0088】

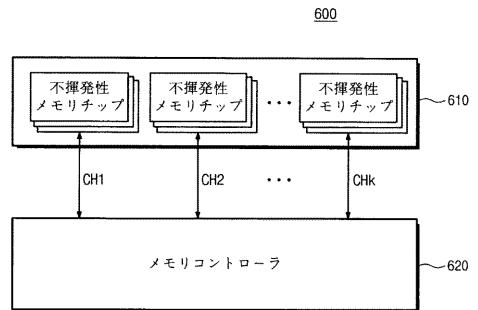

図19は本発明の第4実施形態によるメモリシステム600を示すブロック図である。図19を参照すれば、メモリシステム600は不揮発性メモリ610及びメモリコントローラ620を含む。不揮発性メモリ610は複数の不揮発性メモリチップを含む。複数の不揮発性メモリチップは複数のグループに分割される。複数の不揮発性メモリチップの各グループは1つの共通チャネルを通じてメモリコントローラ620と通信するように構成される。例示的に、複数の不揮発性メモリチップは第1乃至第kチャネルCH1～CHkを通じてメモリコントローラ620と通信するように図示されている。

図19では、1つのチャネルに複数の不揮発性メモリチップが連結されると説明された。しかし、1つのチャネルに1つの不揮発性メモリチップが連結されるようにメモリシステム600が変更されてもよい。

#### 【0089】

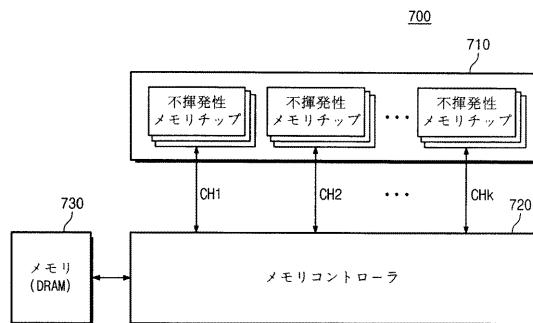

図20は本発明の第5実施形態によるメモリシステム700を示すブロック図である。図20を参照すれば、メモリシステム700は不揮発性メモリ710、メモリコントローラ720、及びメモリ730を含む。図19を参照して説明されたメモリシステム600と比較すれば、メモリシステム700はメモリ730をさらに含む。

メモリ730はメモリシステム700のバッファメモリである。例えば、メモリコントローラ720は外部ホストから受信されるデータをメモリ730に臨時に格納することができる。メモリ730に格納されたデータは不揮発性メモリ710に書き込まれる。メモリコントローラ720は不揮発性メモリ710から読み出したデータをメモリ730に臨時に格納することができる。メモリ730に格納されたデータは外部ホストへ出力されるか、或いは不揮発性メモリ710に再書き込まれる。メモリ730はDRAMを含む。

例示的に、本発明の実施形態によるメモリシステムはSSD(Solid State Drive)を形成する。

#### 【0090】

本発明の実施形態によるメモリシステムはメモリカード又は埋め込み型メモリのようなストレージモジュールを形成することができる。例えば、本発明の実施形態によるメモリシステムは、PCカード(PCMCIA、personal Computer Memory Card international association)、コンパクトフラッシュ(登録商標)カード(CF)、スマートメディアカード(SM、SMC)、メモリスティック、マルチメディアカード(MMC、RS-MMC、MMC micro)、SDカード(SD、miniSD、microSD、SDHC)、ユニバーサルフラッシュストレージ(UFS)モジュール、eMMC(embedded MMC)モジュール等のような多様なストレージモジュールを形成することができる。

#### 【0091】

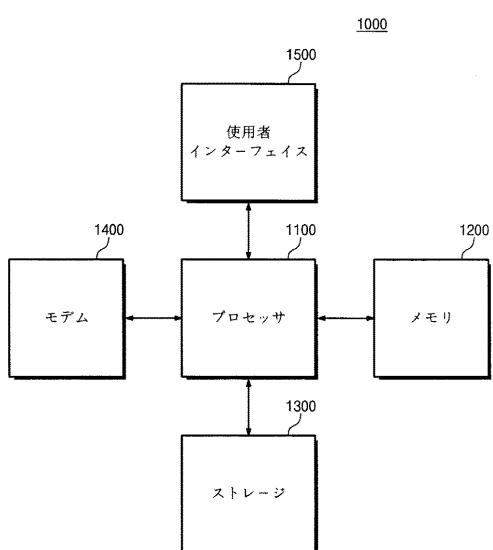

図21は本発明の実施形態によるコンピューティング装置1000を示すブロック図である。図21を参照すれば、コンピューティング装置1000はプロセッサ1100、メ

10

20

30

40

50

モリ1200、ストレージ1300、モデム1400、及び使用者インターフェイス1500を含む。

プロセッサ1100はコンピューティング装置1000の諸般動作を制御し、論理演算を遂行することができる。例えば、プロセッサ1100はシステムオンチップ(SoC、System-on-Chip)で構成することができる。プロセッサ1100は汎用コンピュータに使用される汎用プロセッサ、特殊目的コンピュータに使用される特殊目的プロセッサ、又はモバイルコンピューティング装置に使用されるアプリケーションプロセッサであってもよい。

#### 【0092】

メモリ1200はプロセッサ1100と通信できる。メモリ1200はプロセッサ1100又はコンピューティング装置1000のメインメモリである。プロセッサ1100はメモリ1200にコード又はデータを臨時に格納することができる。プロセッサ1100はメモリ1200を利用してコードを実行し、データを処理できる。プロセッサ1100はメモリ1200を利用して運営体系、アプリケーションのような多様なソフトウェアを実行することができる。プロセッサ1100はメモリ1200を利用してコンピューティング装置1000の諸般動作を制御することができる。メモリ1200はSRAM(Static RAM)、DRAM(Dynamic RAM)、SDRAM(Synchronous DRAM)等のような揮発性メモリ、又はフラッシュメモリ、PRAM(Phase-change RAM)、MRAM(Magnetic RAM)、RRAM(Resistive RAM)、FRAM(Ferroelectric RAM)等のような不揮発性メモリを含むことができる。メモリ1200はランダムアクセスメモリで構成されることができる。

#### 【0093】

ストレージ1300はプロセッサ1100と通信できる。ストレージ1300は長期的に保存されなければならないデータを格納することができる。即ち、プロセッサ1100は長期的に保存されなければならないデータをストレージ1300に格納することができる。ストレージ1300はコンピューティング装置1000を駆動するためのブートイメージを格納することができる。ストレージ1300は運営体系、アプリケーションのような多様なソフトウェアのソースコードを格納することができる。ストレージ1300は運営体系、アプリケーションのような多様なソフトウェアによって処理されたデータを格納することができる。

#### 【0094】

例示的に、プロセッサ1100はストレージ1300に格納されたソースコードをメモリ1200にロードし、メモリ1200にロードされたコードを実行することによって、運営体系、アプリケーションのような多様なソフトウェアを駆動することができる。プロセッサ1100はストレージ1300に格納されたデータをメモリ1200にロードし、メモリ1200にロードされたデータを処理できる。プロセッサ1100はメモリ1200に格納されたデータの中で長期的に保存しようとするデータをストレージ1300に格納することができる。

#### 【0095】

ストレージ1300はフラッシュメモリ、PRAM(Phase-change RAM)、MRAM(Magnetic RAM)、RRAM(Resistive RAM)、FRAM(Ferroelectric RAM)等のような不揮発性メモリを含むことができる。

ストレージ1300は本発明の実施形態によるメモリシステムを含むことができる。例えば、ストレージ1300は自由ブロックの割当間隔にしたがって、消去ブロックに維持されるメモリブロックの数である設定数を調節することができる。ストレージ1300は消去ブロックのタイムスタンプに基づいて、消去ブロックを再消去することができる。

#### 【0096】

モデム1400はプロセッサ1100の制御にしたがって外部装置と通信を遂行するこ

10

20

30

30

40

50

とができる。例えば、モデム1400は外部装置と有線又は無線通信を遂行することができる。モデム1400はLTE( Long Term Evolution)、WiMax、GSM(登録商標)(Global System for Mobile Communication)、CDMA(Code Division Multiple Access)、Bluetooth(登録商標)、NFC(Near Field Communication)、WiFi、RFID(Radio Frequency Identification)等のような多様な無線通信方式、又はUSB(Universal Serial Bus)、SATA(Serial ATA Attachment)、SCSI(Small Computer System Interface)、Firewire、PCI(Peripheral Component Interconnection)等のような多様な有線通信方式少なくとも1つに基づいて通信を遂行することができる。10

#### 【0097】

使用者インターフェイス1500はプロセッサ1100の制御にしたがって使用者と通信できる。例えば、使用者インターフェイス1500はキーボード、キーパッド、ボタン、タッチパネル、タッチスクリーン、タッチパッド、タッチボール、カメラ、マイク、ジャイロスコープセンサ、振動センサ、等のような使用者入力インターフェイスを含むことができる。使用者インターフェイス1500はLCD(Liquid Crystal Display)、OLED(Organic Light Emitting Diode)表示装置、AMOLED(Active Matrix OLED)表示装置、LED、スピーカ、モータ等のような使用者出力インターフェイスを含むことができる。20

コンピューティング装置1000はスマートフォン、スマートパッド、スマートカメラ等のようなモバイルコンピューティング装置を形成することができる。コンピューティング装置1000は個人用コンピュータ、ノートブック型コンピュータ、スマートテレビジョン等のような多様な装置を形成することができる。

#### 【0098】

本発明の詳細な説明では具体的な実施形態について説明したが、本発明の範囲と技術的思想から逸脱しない限度内で様々な変形が可能である。したがって、本発明の範囲は上述した実施形態に限定して定めてはならないし、後述する特許請求の範囲のみでなく、この発明の特許請求の範囲と均等なものによって定められる。30

#### 【符号の説明】

#### 【0099】

|                 |             |

|-----------------|-------------|

| 100、200、300     | メモリシステム     |

| 110、210、310、410 | 不揮発性メモリ     |

| BLK1～BLKz       | メモリブロック     |

| 411             | メモリセルアレイ    |

| 413             | アドレスデコーダ回路  |

| 415             | ページバッファ回路   |

| 417             | データ入出力回路    |

| 419             | 制御ロジック回路    |

| 120、220、320、520 | メモリコントローラ   |

| 521             | バス          |

| 522             | ホストプロセッサ    |

| 523             | メモリ         |

| 524             | メモリインターフェイス |

| 525             | エラー訂正ブロック   |

| 526             | ホストインターフェイス |

| 527             | 装置プロセッサ     |

| 121、221、321     | 予備ブロックキュー   |

| 123、323         | 割当間隔計算機     |

10

20

30

40

50

2 2 5、3 2 5 時間生成器

1 2 7、2 2 7、3 2 7 消去管理者

1 0 0 0 コンピューティング装置

1 1 0 0 プロセッサ

1 2 0 0 メモリ

1 3 0 0 ストレージ

1 4 0 0 モデム

1 5 0 0 使用者インターフェイス

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図8】

【図7】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【 図 1 4 】

【 図 15 】

【図 1 6】

【 図 17 】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 宋 秉 俊

大韓民国京畿道水原市靈通区梅灘3洞 シンマイタン ウェベハンエルチャイアパート130棟1

202号

F ターム(参考) 5B018 GA04 HA31 KA23 MA23 NA01 NA06 QA02

5B060 AA14 CA02