# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

#### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

| (51) International Patent Classification <sup>5</sup> : |                                      | (11) International Publication Number: | WO 91/06910 |

|---------------------------------------------------------|--------------------------------------|----------------------------------------|-------------|

| G06F 13/00 A1                                           | (43) International Publication Date: | 16 May 1991 (16.05.91)                 |             |

(21) International Application Number:

PCT/US90/05910

(22) International Filing Date:

16 October 1990 (16.10.90)

(30) Priority data:

422,489

17 October 1989 (17.10.89) U

(71)(72) Applicant and Inventor: MITCHELL, Maurice, E. [US/US]; 601 Terra California Blvd. #4, Walnut Creek, CA 94595 (US).

(74) Agent: ZITO, Joseph, J.; Suite 300, 1919 Pennsylvania Avenue, N.W., Washington, DC 20006 (US).

(81) Designated States: AT (European patent), AU, BE (European patent), BR, CH (European patent), DE (European patent), DK (European patent), ES (European patent), FR (European patent), GB (European patent), GR (European patent), IT (European patent), JP, KR, LK, LU (European patent), MC, NL, NL (European patent), SE, SE (European patent), SU, US.

#### **Published**

With international search report.

Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.

(54) Title: A MICROCOMPUTER WITH DISCONNECTED, OPEN, INDEPENDENT, BIMEMORY ARCHITECTURE

### (57) Abstract

A Bimemory Independent CPU (BICPU) microcomputer (101) which is comprised of a known CPU chip provided with additional circuitry to enable CPU to interact in a multi BICPU microcomputer system. Each BICPU microcomputer in a system is supplied with an assigned standard memory (120) mechanically and logically connected to its BICPU's "A" bus circuits (124). The BICPU microcomputer is also provided with connectors (100) enabling the CPU to be connected to system buses. Any number of BICPU microcomputers can be logically chained, linked and treed in a sample logical bimemory indepenent pattern infinitely in as many dimensions as is reasonably desired, using one standard set of dedicated, simple, single line conductors (system buses) to mechanically interconnect any "B" (128) or "C" (132) bus circuits of two different BICPU microcomputers.

1

### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT | Austria                  | ES | Spain                        | MG | Madagascar               |

|----|--------------------------|----|------------------------------|----|--------------------------|

| ΑU | Australia                | FI | Finland                      | ML | Mali                     |

| BB | Barbados                 | FR | France                       | MR | Mauritania               |

| BE | Belgium                  | GA | Gabon                        | MW | Malawi                   |

| BF | Burkina Faso             | GB | United Kingdom               | NL | Netherlands              |

| BG | Bulgaria                 | GR | Greece                       | NO | Norway                   |

| BJ | Benin                    | ዘሆ | Hungary                      | PL | Poland                   |

| BR | Brazil                   | IT | Italy                        | RO | Romania                  |

| CA | Canada                   | JР | Japan                        | SD | Sudan                    |

| CF | Central African Republic | KP | Democratic People's Republic | SE | Sweden                   |

| CG | Congo                    |    | of Korea                     | SN | Senegal                  |

| CH | Switzerland              | KR | Republic of Korea            | SU | Soviet Union             |

| CI | Côte d'Ivoire            | LI | Liechtenstein                | TD | Chad                     |

| CM | Cameroon                 | LK | Sri Lanka                    | TG | Togo                     |

| DE | Germany                  | LU | Luxembourg .                 | us | United States of America |

| DK | Denmark                  | MC | Monaco                       |    |                          |

# A MICROCOMPUTER WITH DISCONNECTED, OPEN, INDEPENDENT, BIMEMORY ARCHITECTURE

5

# CROSS REFERENCE TO RELATED APPLICATION

This is a continuation in part application of Serial Number 061,338 filed June 12, 1987 and now issued as Patent Number 4,875,154; which is a continuation in part of application Serial Number 541,453, filed October 13, 1983, now abandoned.

10

# TECHNOLOGICAL CONTEXT OF THE INVENTION

The advent of the Eniac computer and later computers has signalled a period of technology in which numerous problems that were previously insolvable could be solved. However, even with the increased data processing power achieved by the computer, the magnitude and complexity of some problems still defies the computer age.

15

One of the most evident unsolved problems is climate and weather forecasting. In the May Issue of Science 82, Jim Hansen, the Director of NASA's Goddard Institute for Space Studies, stressed that the ability to forecast the future climate of the world with a relatively high degree of accuracy is of very great importance to all the people of the world. Hansen and his colleagues have, accordingly, been engaged in formulating mathematical models which might explain and predict world climate. However, the models generated have been greatly simplified so that existing computer systems can process the data. As a result of the simplifications, such climate models have been less than optimal.

20

7

To a great extent, the problem with predicting weather and climate relates to the vast number of atmospheric volumes which interact to form an overall pattern. That is, the atmosphere can be viewed as a multitude of cells encircling the earth, each cell containing sundry forms of information which changes over

10

15

20

25

30

35

4

٠

time, and affects the characteristics of other adjoining cells.

If the cells were configured as interacting, almost spherical ellipsoids of influence, with each ellipsoidal cell enclosing essentially 25 cubic miles and with only a 25 mile layer of contiguous ellipsoidal cells being formed about the earth, approximately 200 million cells would be required. A smaller cell size or increasing the volume to be considered would, of course, increase the number of ellipsoidal cells required. In any case, let each cell contain information requiring, say 1,000 floating point calculations per second. A computer system designed to handle information for the various cells would thus be required to perform 200 billion interacting floating point calculations per second.

If a computer system based on existing technology were capable of performing such calculations, the cost would be exorbitant.

Moreover, adaptability of such a system based on known art, would be limited.

Relying on prior technology, the solution to modeling weather and the climate thus appears arduous if achievable.

Other problems which are similarly difficult to solve at reasonable costs include large oil field geological surveys, econometric models, air traffic control systems, and other large scale complex three-dimensional space prediction problems. For example, econometric models which evaluate myriad possibilities based on "what if" assumptions and calculations require complex, costly systems.

The more recent Strategic Defense Initiative Organization (SDIO) computer problem is substantially more complex than any of the other applications mentioned above.

Moreover, language applications — such as implementing the new Defense Department ADA language — and corporate decision—making applications often require high—volume, high—speed calculations based on information received from numerous sources. The cost and adaptability of data processing systems which handle such highly parallel tasks are notably less than optimal.

For many years computer scientists have known one basic object of the Ideal Computer System is to, "Be capable of mimicking human thinking". The problems noted above would be solvable, if a computer which could mimic human thinking at computer speed were applied to the task.

This object is quite straight forward. Manufacturing computer system designers have spent the past 20 years attempting to accomplish this objective. The speed of a single computer is limited by the speed of electric signals in the computer circuits. Single, high speed computers, made with shorter and colder circuits, are approaching their maximum circuit speed limits.

Therefore, the manufacturing computer system designers have for some time, attempted to combine more than one processor in a computer system. There are hundreds of different systems for linking, treeing and chaining processors together in a computer system. None of these systems have been capable of mimicking human thinking to the desired degree.

A computer system must be capable of mimicking human thinking to a degree, for the problems above

and others.

5

10

15

20

25

30

35

In the Ideal Computer System, the individual, independent microcomputer should be able to individually "decide" to work with the other microcomputers, or not to work with the other microcomputers in the system, when the logic in it's standard memory circuits, written by human programmers and human field application system designers, instruct the microcomputer to work, or not to work, with the other microcomputers.

Individuals "working together" and "learning together" do so in what might be referred to as parallel thinking. For example, the individual people who designed and built the long range tracking cameras that obtained some of the key pictures of the Space Shuttle booster rocket seal failure, needed to know little or nothing of the science that was required to develop the booster rockets and the seals that failed. This kind of parallel human thinking and action is referred to as "parallel programs" or "parallel architecture" by the computer scientists. Think of the hundreds of billions of human "parallel" thinking patterns that had to go on from the start of the Moon Rocket program to the Shuttle.

Therefore, in the Ideal Computer System, the thousands of individual, independent microcomputers "working together" must be able to be working on tens of thousands of different "parallel" computer programs at the same time, where one individual, independent microcomputer is not interrupted or slowed down by the needs of those other individual, independent microcomputers working on other parts of the overall problem, until data being processed by that one individual, independent microcomputer is needed.

Therefore, in the Ideal Computer System, with thousands of individual, independent microcomputers "working together" in a running system, one must be able to remove individual, independent microcomputers that fail or are damaged by enemy action, or remove an individual, independent microcomputer and add it to a different part of the system, without causing further failure of the overall program logic of the running system.

The "individual people" who are "learning together", "step by step" do this by talking to each other, usually one on one. Even in larger groups, this "learning together" basically entails one person learning something from another person. When one person is speaking to several hundred, the individual person listening is learning in what could be considered a bimemory fashion from the person doing the talking.

Therefore, in the Ideal Computer System, with thousands of individual, independent microcomputers "learning together" in a running system, an individual, independent microcomputer and it's connected standard memory circuits must be capable of directly communicating with another individual, independent microcomputer and it's connected standard memory circuits in what might be called a logical bimemory manner.

The first basic problem of present multiprocessor systems is that when more than two levels of hierarchy are included or more than about twenty processors are interconnected, the hardware and software overhead requirements become so burdensome that additional levels of hierarchy and additional processors have not increased the overall effectiveness or through put of the multiprocessor system. Many of the present multiprocessor systems use one interconnecting circuit to carry data information some of the time and use the same interconnecting circuit to carry address information at other times. This dual use of one circuit to carry

10

15

20

25

30

35

\*

both data information and address information, in present multiprocessor systems, requires many additional timing circuits, additional switching circuits, additional arbitration logic circuits and additional error checking logic circuits, and a very large number of additional interrupts when circulating Pierce loops are also used, between the various interconnected processors. This additional complexity, in the interconnecting circuits, is a very large part of the reason that more than two levels of hierarchy and more than about twenty processors being interconnected have not increased the overall effectiveness or through put of the multiprocessor system.

The second basic problem of present multiprocessor systems is most multiprocessor systems are designed with essentially permanent connections between the various clusters of processors, creating one basic system of mechanical connections between the processors. To mimic human thinking to the desired degree requires the ability to use the human thinking of the field application system designers and the programmers to decide which sets of billions of different optional mechanical and logical combinations of interconnections between the individual processors in a multiprocessor system are most effective for a given problem at a given moment in time, based on the actual data flow in the problem, at computer speeds. None of the present multiprocessor systems permit the field application system designers and the programmers to arbitrarily change the mechanical interconnections between the various processors in the billions of different ways the human field application system designers and programmers think the processors should be interconnected.

The human programmers and field application system designers think the processors should be interconnected this way today and change their mind and think they should be interconnected in a different way tomorrow. Sometimes the human programmers think the individual processors should be interconnected one way and the human field application system designers think the individual processors should be interconnected in a different way. Only actual, real time, testing in the field of the various sets of billions of mechanical and logical interconnections will make the multicomputer system "be capable of mimicking human thinking" to the required degree.

The third basic problem of present multiprocessor systems is the inability to make existing multiprocessor systems work as truly "parallel processors". The Strategic Defense Initiative Organization problem and the World Climate Prediction problem probably both require very highly parallel architectures to be effective. Over 200 billion interacting floating point calculations are required per second on the World Climate Prediction problem as a minimum, and the SDIO requirement is very much larger. The SDIO problem could probably use 20 trillion interacting floating point calculations per second.

The fourth basic problem of present multiprocessor systems is removing individual processors that have failed or have been damaged by enemy action from a running system without causing further failure of the overall program logic of the balance of the remaining running system.

The fifth basic problem of present multiprocessor systems is adding individual processors to a running system without causing failure of the overall program logic of the balance of the running system.

The sixth basic problem of present multiprocessor systems is some of the switching circuits and some of

the arbitration logic circuits and some of the error checking logic circuits needed to effectively interconnect several thousand processors, are being placed outside of the individual processors. These different external logic circuits and BLOCK/SHORT circuits in circulating Pierce loop circuits, preclude using one standard group of circuits made up of simple, dedicated purpose, single line conductors, where the standard group of circuits can be of various random lengths — less than a maximum length — to interconnect any two processors.

The seventh basic problem of present multiprocessor systems is that more than one standard group of circuits are used in the multiprocessor system to interconnect processors on different hierarchy levels. For example, some present multiprocessor systems, like the "Restructurable Integrated Circuit For Implementing Digital Systems" as described by Rob Budzinski, John Linn, and Satish Thatte, COMPUTER, March 1982, pages 43 through 54, use the concept of external coordination of microprocessors as developed by R. G. Arnold and E. W. Page, Proc. 3rd Ann. Symp. Computer architecture 1976, pages 40–45, where both time–shared busses referred to above, and "circulating" Pierce Loop busses are used on each level of hierarchy. The highest hierarchy level of busses (Master Control Group) use "circulating" busses without special "BLOCK/SHORT" logic circuit modules. Each additional level of hierarchy (Control Group), below the Master Control Group, requires an additional set of busses with special "BLOCK/SHORT" logic circuit modules.

This requirement of an additional set of busses (Control Group) for each level of hierarchy caused Arnold and Page to state in their OBSERVATIONS AND CONCLUSIONS, "As is evident from the examples, only a limited number of Control Groups are likely to be used". When one thinks of one hundred levels of hierarchy requiring one hundred separate sets of (Control Group) busses interconnecting each of several thousand processors, it is easy to understand Arnold and Page's above stated conclusions.

The Bimemory Independent Central Processing Unit microcomputer (BICPU microcomputer) invention, as herein taught, solves all seven of these basic problems. The BICPU microcomputer is actually capable of mimicking the human thinking of the field application system designers and the human programmers involved in the system. If the human programmer can think of a solution, or the human field application system designer can think of a solution, several thousand BICPU microcomputers, mechanically interconnected in one of several billion different unique systems, where the programmers, at computer speeds, can logically connect and logically disconnect the thousands of BICPU microcomputers in several billion additional unique ways, using logical bimemory "S" hookups and logical bimemory "Y" hookups, probably will "be capable of mimicking human thinking" to the required degree.

To demonstrate that none of the hundreds of presently known multiprocessor systems are "capable of mimicking human thinking" to the required degree, one only has to read what Digital Equipment Corporation executives said about their newest multiprocessor systems in the January 20, 1987 edition of the New York Times;

Digital to Offer Mainframes

System links VAX Units

15

10

5

20

25

30

35

Moving into the mainframe computer arena, the Digital Equipment

Corporation will announce today a \$2.5 million system that links four of its

most powerful VAX computers into one, giving it the speed of some of I.B.M.'s

largest systems. \* \* \* \*

"This is an alternative style of computing when compared to I.B.M.," said Rose Ann Giodan, vice president of information system marketing for Digital. "It is an integrated whole, all the way from a desktop, \$5,000 computer to a mainframe."

The announcement today, at a news conference in New York, is expected to involve two new machines, the VAX 8974 and 8978. Both link VAX 8700 computers, the 8974 in a cluster of four processors, the 8978 in a cluster of eight.

Digital said the 8974 would be able to process about 27 million instructions a second, putting it in direct competition with the low end of I.B.M.'s System 3090 computers. The 8978 would run at about twice the rate.

#### **Questions on Power**

At the same time, some experts question whether the multiprocessing solution that Digital and other manufacturers have settled on will actually provide heavy-duty users with the power they need.

Four VAX's that are tied together do not process data more quickly than a single VAX — indeed, to solve most tasks only one of the four processors is at work. But because the four processors can work simultaneously, sharing mass storage devices and other expensive peripherals, they can reduce the waiting time that any individual user or program spends waiting for a single processor to become free.

The clustered VAX computers accelerate an industry trend toward the combination of several processors in a single computer. But strictly speaking, the new VAX's are not "parallel processors" because their ability to divide a single problem and parcel it out to different processors is severely limited.

"That's a software problem that still requires some additional work," said F. Grant Saviers, Digital's vice president of storage systems. "Obviously, it's something we are working on intensely." \* \* \*.

This article confirms several of the seven basic problems of present multiprocessor systems mentioned above.

5

10

15

20

25

30

10

15

20

25

30

First Problem - Note the two levels of hierarchy used with the five or nine interconnected processors involved. The VAX 8974 or the VAX 8978 are on one hierarchy level, and the clusters of four or eight VAX 8700 are on the second hierarchy level.

Second Problem - Note there is no indication that the four or eight VAX 8700 are flexibly connected to the VAX 8974 or VAX 8978 in the clusters. In other words, there is no indication that the field application system designers can arbitrarily change the mechanical interconnection arrangement of the four VAX 8700 computers or the eight VAX 8700 computers.

Third Problem - Note "strictly speaking, the new VAX's are not "parallel processors" because their ability to divide a single problem and parcel it out to different processors is severely limited."

Fourth Problem - Note there is no indication that one VAX 8700 processor can be individually powered off and removed from the other three or seven VAX 8700s in a system, without causing a failure of the logic of the other running programs in the system.

Fifth Problem - Note there is no indication that programmers and field application system designers have the ability to add a fifth or ninth VAX 8700 to the system, without causing a failure of the logic of the other running programs in the system.

Sixth Problem - Note to make a four processor multiprocessor system and an eight processor multiprocessor system, three different processors are needed. The VAX 8700, the VAX 8974 and the VAX 8978, instead of only one multiprocessor that can be interconnected into multiprocessor systems of two to over a thousand processors.

Seventh Problem - If the VAX 8974 and VAX 8978 are considered interconnecting circuits for interconnecting four and eight computers, then two different interconnecting circuits are required to interconnect four computers or eight computers.

Especially note that "some experts question whether the multiprocessing solution that Digital and other manufacturers have settled on will actually provide heavy-duty users with the power they need".

# SUMMARY OF THE INVENTION

The invention is a Bimemory Independent CPU (BICPU) microcomputer which is comprised of a known CPU chip provided with additional circuitry to enable the CPU to interact in a multi BICPU microcomputer system. Each BICPU microcomputer in a system is supplied with an assigned standard memory mechanically and logically connected to it's BICPU's "A" bus circuits. The BICPU microcomputer is also provided with connectors enabling the CPU to be connected to system buses. Any number of BICPU microcomputers can be logically chained, linked and treed in a simple logical bimemory independent pattern infinitely in as many dimensions as is reasonably desired, using one standard set of dedicated, simple, single line conductors (system buses) to mechanically interconnect any "B" or "C" bus circuits of two different BICPU microcomputers. Packaging considerations will tend to be the limiting factor in the number of BICPU

10

15

20

25

30

35

Ž.

microcomputers that can be mechanically interconnected in large multi-BICPU microcomputer systems.

For example, the BICPU microcomputer system might be as small as a single stand alone application of one Bimemory Independent CPU microcomputer utilizing its given memory, to a system with thousands of Bimemory Independent CPU microcomputers (BICPU microcomputers) in a world weather prediction system, or in an oil field geological survey, or in the Strategic Defense Initiative Organization computer system.

The invention can be retrofitted on certain types of highly successful microcomputers with dedicated pinout circuits being built today so that most, if not all, of the present software of these highly successful microcomputers can be run on the new Bimemory Independent CPU microcomputer invention with very little, if any, modifications. The memory access circuits (address, data, control) of the CPU are connected to a switching unit. Three buses, "A", "B" and "C" are connected to the switching unit. The internal structure of the switching unit is configured solely by the CPU to create a signal path connecting the memory access circuits of the CPU to the desired bus or buses or any selected portion thereof.

The CPU is further provided with circuitry, including two dedicated function processors (ILUs), to enable the CPU to communicate and interact with other CPUs on either of the system buses "B" or "C". The CPU is also provided with additional registers to store switching unit configurations, system addresses etc.

This specification describes how the invention can be retrofitted on the MCS6502 microcomputer of the MCS650X chip family made by MOS Technology Inc. of Norristown, Pennsylvania, and described in detail in a HARDWARE MANUAL and a SOFTWARE MANUAL published in 1976, MOS Technology Inc. of Norristown, Pennsylvania, and incorporated herein by reference.

The CPU of the BICPU microcomputer invention has dedicated circuits similar to the MCS6502 type microcomputer as described in the MOS microcomputer HARDWARE MANUAL above. For example the MCS6502 and the MCS650X family of microcomputers are packaged in 40 pin DIPs (Dual In-Line Packages). According to Figure 1.15, page 42, of the above MOS microcomputer HARDWARE MANUAL, there are 8 dedicated pins connected to the 8 Data Bus circuits, 8 dedicated pins connected to the 8 Address Bus Low circuits, 8 dedicated pins connected to the 8 Address Bus High circuits, 10 dedicated pins connected to computer and memory control circuits, 3 dedicated pins connected to Power circuits and 3 pins are not connected.

On Page 5 of the above MOS microcomputer HARDWARE MANUAL, in Figure 1.1, the basic organization of a microcomputer system is shown based on the MCS6502 type microcomputer. Especially note that the \*\*\* MCS6502 \*\*\* microcomputer in the lower right in Figure 1.1, is <u>directly</u> and independently connected to the dedicated standard memory circuits, (address bus, data bus, write enable, interrupts and other control signals).

On Page 41, in lines 9 through 11, of the above MOS microcomputer HARDWARE MANUAL, the MCS6502 has the oscillator and clock driver on-chip, thus eliminating the need of an external high-level two-phase clock generator.

Therefore with the MCS6502, in Figure 1.1 of the MOS microcomputer HARDWARE MANUAL

10

15

20

25

30

35

above, the microcomputer independently, directly, logically controls all of the Program Memory (ROM), the Data Memory (RAM), and the Peripheral Interface Device shown, by independently, directly, logically reading and independently, directly, logically writing to the dedicated standard memory circuits mechanically and logically connected to the 40 pins of the MCS6502 Pinout Designation as shown in Figure 1.15 on page 42 of the above MOS microcomputer HARDWARE MANUAL.

The MCS6502 is a CPU that can independently, directly, logically read or write, in a logical manner, 256 pages of 256 characters each, where each character can be any of 256 different characters. The phrase, in a logical manner, is meant to include all of the CPU's present and potential set of microinstructions, which in the case of the MCS6502 consists of 256 different microinstructions of which essentially 156 have been implemented. The MCS6502 independently, directly, logically controls everything that is read or written on these 256 pages of memory space.

Examples of fantastic implementations of the MCS6502 include the Commodore, Apple, Atari, and many other personal computers. The MCS6502 essentially is an 8-bit microcomputer addressing a 16-bit address space. (With essentially 16-bit MCS650X type microcomputers addressing a 32-bit address space, the numbers 256 above can be changed to 65,536. In the World Climate and SDIO problems above, 16-bit BICPU microcomputers addressing 32-bit address space can be used).

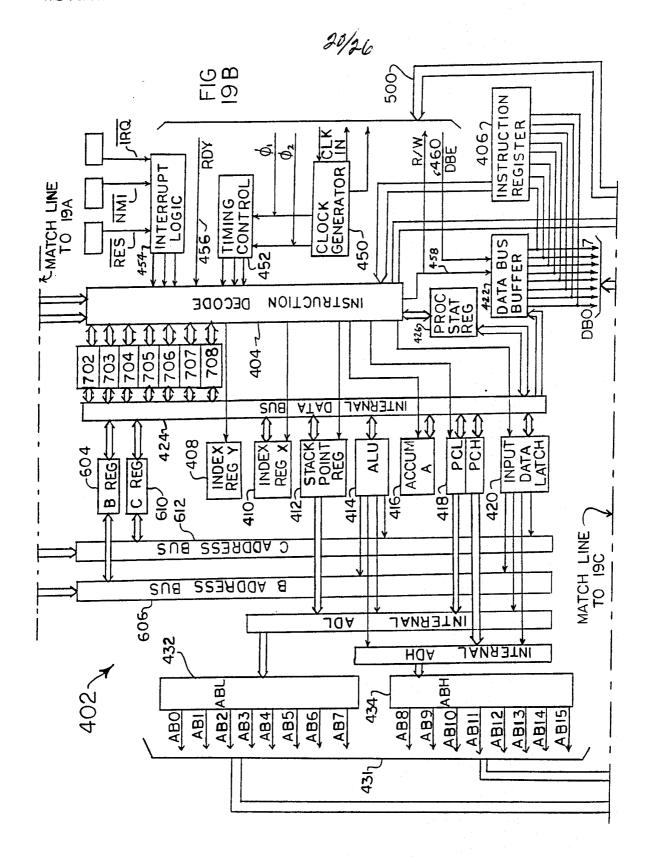

The BICPU microcomputer invention takes the MCS6502 and the dedicated address, data and control circuits presently connected to the 40 pins in Figure 1.15 on page 42 of the MOS microcomputer HARDWARE MANUAL (or some other similar type highly successful microcomputer), and defines these circuits the "A" bus circuits 520 of Figure 19 (the power circuits are not changed by the invention and for clarity are not shown in Figure 19). The new bimemory switching circuits 502, 504, 506, and 508, of Figure 19 are inserted in these "A" bus circuits between the CPU and the pins of Figure 1.15 on page 42 above, (but are not inserted in the BICPU microcomputer power circuits). These bimemory switching circuits are also connected to the "B" bus circuits 522, and the "C" bus circuits 524 in a bimemory manner where at any one time the individual address circuits, data circuits and the read/write circuit from the microcomputer of Figure 1.1 page 5, is logically directly connected to only one of the dedicated off chip pins in the "A" bus circuits 520, "B" bus circuits 522 or "C" bus circuits 524. The remainder of the circuits utilized for memory control, eg. clock timing circuits, ready circuit, sync circuit, interrupt circuits etc., remain connected between the CPU and its memory during bimemory operations.

At any one moment in time, a first Bimemory Independent CPU (like in Figure 1.1 on page 5, MOS microcomputer HARDWARE MANUAL), (a) can be independently, directly, logically connected to the "A" bus circuits 520 in Figure 19, and a first set of standard memory circuits mechanically connected to the "A" bus circuits of this first BICPU microcomputer or,

(b) can be directly, logically connected in a bimemory manner, to the "B" bus circuits 522 in Figure

ŧ

Î

19, which are mechanically connected to a set of dedicated standard Bimemory Interconnecting Control-BUS (BIC-BUS) circuits which are mechanically connected to "B" or "C" bus circuits of a consenting second BICPU microcomputer which has logically, directly, connected it's "B" or "C" bus circuits to it's "A" bus circuits and a second set of standard memory circuits mechanically connected thereto or,

5

(c) can be <u>directly</u>, logically connected in a bimemory manner, to the "C" bus circuits 524 in Figure 19, which are mechanically connected to a set of dedicated standard Bimemory Interconnecting Control-BUS (BIC-BUS) circuits which are mechanically connected to "B" or "C" bus circuits of a consenting third BICPU microcomputer which has logically, <u>directly</u>, connected it's "B" or "C" bus circuits to it's "A" bus circuits and a third set of standard memory circuits mechanically connected thereto.

10

Human programmers and human field application system designers can mechanically interconnect two or more BICPU microcomputers with dedicated standard memory circuits mechanically and logically directly connected to their "A" bus circuits, by mechanically connecting sets of dedicated BIC-BUS circuits between the "B" or "C" bus circuits of one BICPU microcomputer and the "B" or "C" bus circuits of a second BICPU microcomputer. In this simple manner, programmers and field application system designers can mechanically interconnect thousands of BICPU microcomputers in billions of different systems with hundreds of logical levels of hierarchy.

15

The meaning of the new mnemonics used in this specification are as follows:

20

BICPU - Bimemory Independent Central Processing Unit - This is the mnemonic for the invention. It comprises the basic CPU being implemented on the invention, plus the seven new switch means, the nine additional new registers, the two new ILUs, the new BIC-CTRB control lines, the new Interconnect Switch and the new "B" and "C" bus circuits.

BIM mode - <u>BIM</u>emory mode - This is one of eight different logical bimemory modes a BICPU can assume. In these eight BIM modes, a first BICPU microcomputer is in a logical bimemory hookup, controlling part or all of two standard memory circuits in a bimemory manner.

25

FLT mode - FLoaTing mode - This is one of four different logical bimemory modes a "consenting" BICPU microcomputer can assume. In these four FLT modes, a "consenting" BICPU microcomputer has logically connected some or all of its "A" bus circuits and the standard memory circuits connected thereto, to the BICPU microcomputer in the BIM mode in a logical bimemory hookup, and gone into a "floating" state waiting for the BICPU microcomputer in the BIM mode to complete the logical bimemory hookup.

30

PRM mode – PRimary Mode – This is one of three different logical modes a BICPU microcomputer can assume. In these three PRM modes, the BICPU microcomputer is logically connected to its "A" bus circuits and the standard memory circuits connected thereto, in exactly the same logical manner as the CPU was connected to its standard memory circuits before being retrofit with the BICPU invention. These three PRM modes logically bridge the gap between microprocessors and the BIM and FLT modes of the BICPU microcomputer.

35

WO 91/06910 PCT/US90/05910

11

BIC-BUS - Bimemory Interconnecting Control-BUS - These standard groups of simple, single line, circuits are used to interconnect the "B" or "C" bus circuits of any two different BICPU microcomputers.

ILU - Interrupt Logic Unit - The two new "B" and "C" ILUs monitor and control the BIC-CTRB circuits for the CPU of the BICPU in an asynchronous manner. They enable the CPU of the BICPU invention to go about its data processing tasks, without being interrupted or slowed down, except when the exact BICPU microcomputer needs to be involved in a logical bimemory manner. The ILUs make and complete all logical bimemory hookups, under the control of the CPU of the BICPU microcomputer.

5

10

15

20

25

30

35

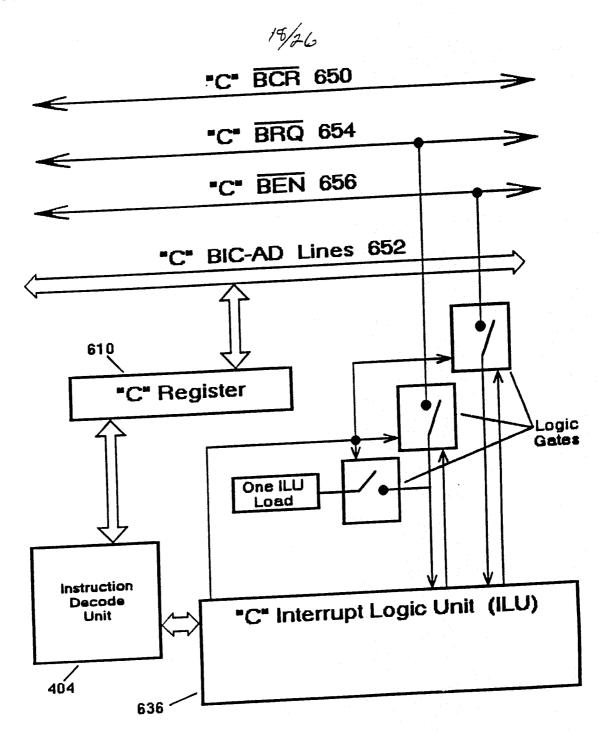

BIC-CTRB - BIC-BUS ConTRol Bus - These circuits comprise the BIC-AD circuits and the "BCR", "BEN" and "BRQ" lines. They are connected to the new buffers and Interconnect Switch on one end and connected to the "B" and "C" bus circuits on the other end. They join and run parallel with the other circuits in the BIC-BUS circuits. They are monitored and controlled by the ILUs, under the control of the CPU of the BICPU microcomputer. Essentially these circuits are new interrupt circuits between two CPUs of two different BICPU microcomputers. These BIC-CTRB circuits are always unique to one set of BIC-BUS circuits. The BIC-CTRB circuits of two different sets of BIC-BUS circuits are never interconnected, and remain unique to just the one set of BIC-BUS circuits they are in. The BICPU microcomputers never directly interconnect the BIC-CTRB circuits. The "B" BIC-CTRB circuits are monitored and controlled by the "B" ILU, and the "C" BIC-CTRB circuits are monitored and controlled by the "C" ILU.

"BCR" line – Bus ControlleR line – This line is set TRUE by the "calling" ILU of a BICPU microcomputer and determines which ILU has control of a set of BIC–CTRB circuits. The "BCR" line is set FALSE by the ILU of the BICPU microcomputer in the BIM mode in a logical bimemory hookup, to initiate logical hang up. The "BCR" line always being set FALSE by the ILU of the BICPU microcomputer in the BIM mode assures that all logical bimemory hookups can be interrupted in a logical manner where the program logic of the bimemory hookup is saved in a logical manner, as desired by the programmer, before the logical bimemory hookup is hung up.

"BEN" line - Bus ENable line - This line enables the logical bimemory hookup to proceed when it is set TRUE by the ILU of the "consenting" BICPU microcomputer. When the "BEN" line is set FALSE by an ILU of a BICPU microcomputer, the logical bimemory hookup is logically hung up, saving the program logic in a logical hang up procedure.

"BRQ" line - Bus ReQuest line - This line is used by the ILUs to generate the "Not Active", "Active BICPU" or "Two or More" signals without requiring external logic circuits outside of the BICPU microcomputers involved in the logical bimemory hookup. This enables simple, single line circuits, without logic, to be used in the BIC-BUS circuits.

BIC-AD lines - Bimemory Interconnecting Control Bus-ADdress lines - These BIC-AD lines are part of the BIC-CTRB circuits. These BIC-AD lines are not to be confused with the standard address circuits of the CPU of the BICPU microcomputer. These BIC-AD lines are unique to one set of BIC-BUS circuits, and

10

15

20

25

30

35

ŧ

'n,

carry the assigned "B" or "C" register number of a BICPU microcomputer being "called" to participate in a logical bimemory hookup. The standard address circuits of the CPU of the BICPU microcomputer can be interconnected between two sets of BIC-BUS circuits by the ILUs of the BICPU microcomputers involved in the logical bimemory hookup. The BIC-AD circuits of two different sets of BIC-BUS circuits are never interconnected. The ILUs monitor these BIC-AD circuits to determine when the address on these circuits match the valid assigned bus number stored in the correct "B" or "C" register, so that the ILUs can determine when they are being "called" by another ILU on this set of BIC-BUS circuits.

DHU - Directed Hang Up - New bimemory instruction causing an ILU to place a special code on the BIC-AD line, subsequently causing both "BEN" lines of each BICPU microcomputer in a given set of BIC-BUS circuits to go FALSE, thereby causing all logical bimemory hookups utilizing all involved BIC-BUS circuits to terminate logically.

NHU - Normal Hang Up - New bimemory instruction causing a normal logical hang up of the various sets of BIC-BUS circuits involved in a logical bimemory hookup. This is used by the programmer to hang up a logical bimemory hookup and return to a PRM mode. It can be compared to the RTN (return) instruction after a subroutine has been completed and the programmer directs the program logic to return to the instruction after the gosubroutine instruction.

GBH - Go Bimemory Hookup - New bimemory instruction causing the BICPU microcomputer to attempt to create a logical bimemory hookup between this BICPU microcomputer and another BICPU microcomputer. This instruction can be compared to a gosubroutine instruction, where the subroutine includes many conditional tests.

To make the following descriptions of the amazing flexibility of both the mechanical and logical interconnection of several thousand BICPU microcomputers more clear and concise, the phrase "standard memory circuits" will be used to refer to "standard dedicated memory circuits" and the phrase "BIC-BUS circuits" will be used to refer to "dedicated BIC-BUS circuits" as all standard memory circuits and all BIC-BUS circuits are dedicated circuits in the BICPU microcomputer invention. Since all standard memory circuits are always mechanically connected to "A" bus circuits, and all BIC-BUS circuits are always mechanically connected to "B" or "C" bus circuits, the phrases "connected standard memory circuits" and "connected "B" or "C" bus circuits" always means "mechanically connected".

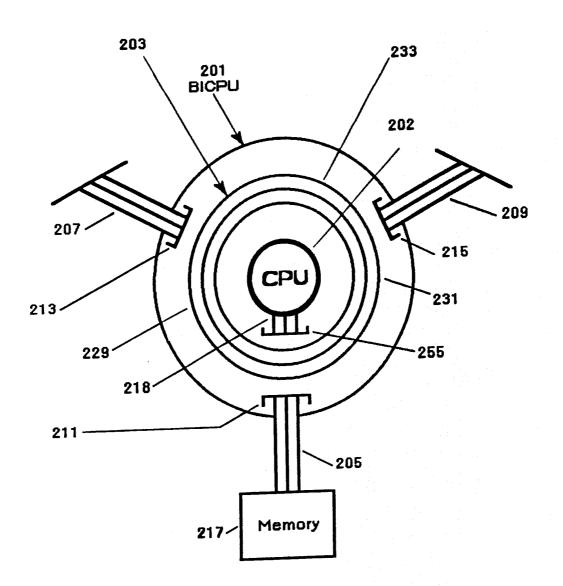

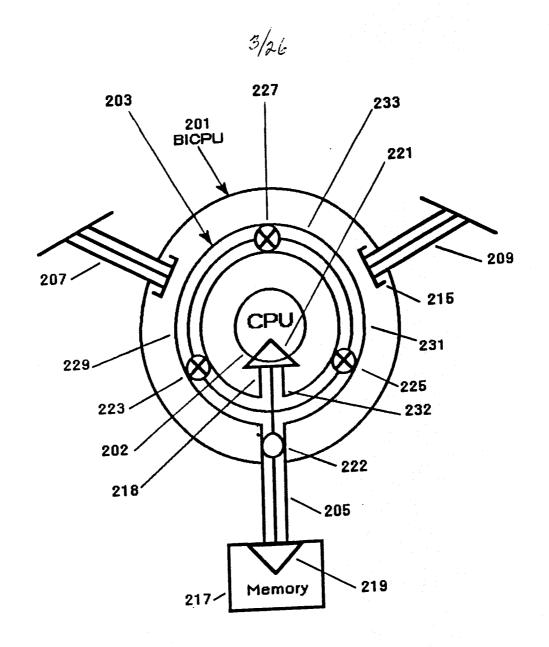

The phrase "first BICPU microcomputer" will generally be used to refer to a BICPU microcomputer as depicted in the various bimemory modes in Figure 3 through Figure 13 and Figure 15 through Figure 17 that has standard memory circuits 217 connected to it's "A" bus circuits.

The phrase "second BICPU microcomputer" will generally be used to refer to a BICPU microcomputer connected to BIC-BUS circuits connected to the "B" bus circuits of a first BICPU microcomputer, that is in the process of being logically <u>directly</u> connected to, or is logically <u>directly</u> connected to the "B" bus circuits of a first BICPU microcomputer.

The phrase "third BICPU microcomputer" will generally be used to refer to a BICPU microcomputer connected to BIC-BUS circuits connected to the "C" bus circuits of a first BICPU microcomputer, that is in the process of being logically directly connected to, or is logically directly connected to the "C" bus circuits of a first BICPU microcomputer.

5

The phrase "consenting" BICPU microcomputer refers to a BICPU microcomputer that has "consented" to assume one of the FLT modes and directly logically connects some or all of it's "A" bus circuits and the standard memory circuits connected thereto, to it's "B" or "C" bus circuits thus directly logically connecting these "A" bus circuits and the standard memory circuits connected thereto, to the BICPU microcomputer in the BIM mode in either a logical bimemory "S" hookup or a logical bimemory "Y" hookup.

10

The phrase "original calling" BICPU microcomputer refers to a BICPU microcomputer that initially reads the first microcode of either a logical bimemory "S" hookup or a logical bimemory "Y" hookup. The mode of the "original calling" BICPU microcomputer must be either a BIM mode or a FLT mode or a bimemory programming error has occurred.

15

The phrase "interconnecting" BICPU microcomputer refers to a BICPU microcomputer in either a PRM-1 mode or a PRM-2 mode, interconnecting two different sets of BIC-BUS circuits.

The following parts are added to the existing CPU to enable the CPU to function interactively in a system of any number of BICPU microcomputers.

20

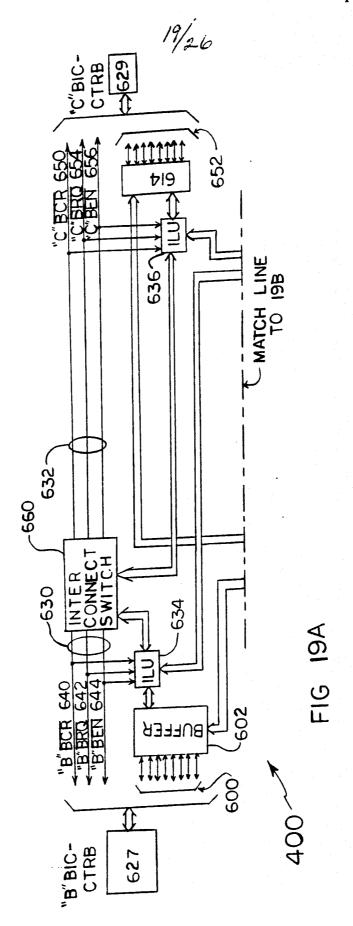

The new "B" BIC-CTRB circuits 627 in Figure 19, join and run parallel to the "B" bus circuits 522 in Figure 19, and new "C" BIC-CTRB circuits 629 in Figure 19, join and run parallel to the "C" bus circuits 524 in Figure 19.

The new "B" Interrupt Logic Unit 634 in Figure 19, monitors and controls the "B" BIC-CTRB circuits 627 in Figure 19, and the new "C" Interrupt Logic Unit 636 in Figure 19, monitors and controls the "C" BIC-CTRB circuits 629 in Figure 19.

25

The new "B" register 604 in Figure 19 and the new "C" register 610 in Figure 19 hold assigned bus address numbers of this BICPU microcomputer, when this BICPU microcomputer is logically connected to the dedicated BIC-BUS circuits mechanically connected to it's "B" or "C" bus circuits.

The new "B" BIC-BUS Status Register #1 and #2, 702 and 703 in Figure 19, and the new "C" BIC-BUS Status Registers #1 and #2, 704 and 705 in Figure 19, hold the status of the nearest linking second and third BICPU microcomputers logically connected to the sets of new BIC-BUS circuits mechanically connected to "B" and "C" bus circuits 522 and 524 in Figure 19.

30

The new BICPU Bus Status Registers #1, #2 and #3, 706, 707 and 708 in Figure 19, hold the bimemory status of BICPU microcomputer 400 in Figure 19.

35

The new Inter Connect Switch 660 in Figure 19, latches the status of the "BCR", and "BEN" circuits in a special bimemory way under control of the new Interrupt Logic Units (ILUs) 634 and 636.

The new Buffers 602 and 614 in Figure 19, latch, drive and read the BIC-AD circuits 600 and 652 in

Figure 19, under the control of the new ILUs 634 and 636.

5

10

15

20

25

30

35

The new Bimemory Switching units ABL Switch 504, ABH Switch 506, DATA Switch 508, CONTROL Switch 502 and DECODE Switch 530 in Figure 19 configure the path of the memory address, data and control lines, under the control of the Instruction Decode unit 404.

3

ð

New additional logical bimemory microinstructions are programmed into the existing Instruction Decode unit 404.

When the invention is implemented on a MCS6502 type microcomputer, the standard address circuits, the standard data circuits and the standard control circuits connecting the BICPU of the BICPU microcomputer invention and the standard memory circuits are dedicated circuits such as are used in the MCS6502. For example, on page 42, Figure 1.15 of the above MOS microcomputer HARDWARE MANUAL gives the MCS6502 Pinout Designation. There is a pin numbered 33, marked DB0, for the lowest order bit of the data bus circuits. There is a pin numbered 9, marked AB0, for the lowest order bit of the Address Bus Low circuits. Pin numbered 33 is used only for the lowest order bit of the data bus circuits. Pin number 9 is used only for the lowest order bit of the address bus low circuits. These two pins and their data and address circuits and the logical information they carry are NEVER interconnected or interchanged on these pins. The same is true for all of the data circuits and all of the address circuits and the R/W circuit on pin 34. Notice in the legend of Figure 1.12 on page 33, of the above MOS microcomputer HARDWARE MANUAL, the MCS6501 "always puts out known addresses on the address bus". The MCS6502 always does the same.

Page 32, lines 28 through 34, and page 34, lines 1 and 2, of the MOS microcomputer HARDWARE MANUAL;

#### 1.4.1.2.2 AB00-AB15--Address BUS

The address bus buffers on the MCS650X family of microprocessors are push/pull type drivers capable of driving at least 130 pf and 1 standard TTL load.

The address bus will always contain known data as detailed in Appendix A. The addressing technique involves putting an address on the address bus which is known to be either in program sequence, on the same page in program memory or at a known point in RAM. A brief study of Appendix A will acquaint the designer with the detailed operation of this bus."

On page 34, lines 10 through 23;

"The specific timing of the address bus is exactly the same for all the processors. The address is valid 300 ns (at 1 MHz clock rate) into the 01 clock pulse and stays stable until the next 01 pulse. This specification will only change for the processors which are specified to operate at a higher clock rate. Figure 1.13 details the relation of address bus to other critical signals.

Because of the reduced number of address lines on the 28-pin processors, it is possible to write a program which attempts to access non-existent memory address space, i.e., the address bits 13, 14, or 15 set to logic "1." These upper address bits in the program will be ignored and the

10

15

20

25

30

35

program will drop into existing address space. This assumes proper memory management when using devices of large addressing capability such that the addressed memory space will fit within the constraints of a device with smaller available memory addressing capability."

Especially notice the above paragraph explains in detail how and why the BICPU invention can do a partly connected Address Bus High mode in the BIM-1, BIM-3, BIM-5, BIM-7, FLT-1 and FLT-3 modes.

On page 34 of the MOS microcomputer HARDWARE MANUAL, lines 24 through 35, and page 35, lines 1 through 5;

#### 1.4.1.2.3 DB0-DB7--Data Bus

The processor data bus is exactly the same for the processors currently available and for the software-compatible processors which will be introduced in the near future. All instructions and data transfers between the processor and memory take place on these lines. The buffers driving the data bus lines have full "three-state" capability. This is necessitated by the fact that the lines are bidirectional.

Each data bus pin is connected to an input and an output buffer, with the output buffer remaining in the "floating" condition except when the processor is transferring data into or out of one of the support chips. All inter-chip data transfers take place during the Phase Two clock pulse.

During Phase One the entire data bus is "floating."

The data bus buffer is a push/pull driver capable of driving 130 pf and 1 standard TTL load at the rated speed. At a 1 MHz clock rate, the data on the data bus must be stable 100 ns before the end of Phase Two. This is true for transfers in either direction. Figure 1.13 details the relationship of the data bus to other signals."

On page 36 of the above MOS microcomputer HARDWARE MANUAL, lines 6 through 16; 1.4.1.2.4 R/W--Read/Write

The Read/Write line allows the processor to control the direction of data transfers between the processor and the support chips. This line is high except when the processor is writing to memory or to a peripheral interface device.

All transitions on this line occur during the Phase One clock pulse (concurrent with the address lines). This allows complete control of the data transition which takes place during the Phase Two clock pulse.

The R/W buffer is similar to the address buffers. They are capable of driving 130 pf and one standard TTL load at the rated speed. Again, Figure 1.13 details the relative timing of the R/W line."

On page 41 of the above MOS microcomputer HARDWARE MANUAL, lines 1 through 19;

# 1.4.2.1 Product Characteristics

1.4.2 The MCS6502

The MCS6502 is very similar to the MCS6501 described in detail in the previous section. It provides a full 16-pin address bus and therefore addresses a full 65,536 words in memory. It also has the same data bus, R/W and RDY available on the MCS6501.

Ŧ

Figure 1.15 illustrates the pin configuration of the MCS6502.

The differences between the two devices are as follows:

5

10

15

20

25

30

35

- The MCS6502 has the oscillator and clock driver on-chip, thus eliminating the need for an external high-level two-phase clock generator.

- 2. The MCS6502 generates a SYNC signal instead of the bus available (BA) signal. The SYNC signal is described in detail below.

- 3. Pin 5, corresponding to the MC6800 VMA signal, is not connected.

- 4. The internal data bus enable function is connected directly to the phase two clock on the chip. Therefore pin 36 on the MCS6502 is not connected.

Some multiprocessors use the same pin and the same circuit to carry data information part of the time and to carry address information at different times. These types of multiprocessors are completely different and do not relate to the BICPU microcomputer invention, as implemented on the MCS6502 type of microcomputer. The BICPU microcomputer invention achieves it's fantastic ability to be chained, linked and treed in a simple bimemory independent pattern infinitely in as many dimensions as is reasonably desired by directly logically switching, in a bimemory manner, dedicated circuits that carry standard memory address information, standard memory data information and standard memory control information. This is what enables over a thousand BICPU microcomputers to be mechanically and logically interconnected in billions of different ways, using one dedicated standard set of BIC-BUS circuits.

The implementation of the BICPU microcomputer invention, as described in this specification, requires that the standard address circuits, the standard data circuits and the standard control circuits and the standard memory circuits be of the dedicated type described in the MOS microcomputer HARDWARE MANUAL above. In this specification, when the word "standard" is used in connection with address circuits, data circuits, control circuits and memory circuits, standard means the standard address circuits, standard data circuits, standard control circuits and standard memory circuits as described in the MOS microcomputer HARDWARE MANUAL above for the MCS6502.

On page 50 of the MOS microcomputer HARDWARE MANUAL, lines 1 through 15, and page 51, lines 1 through 5;

- 1.5 Peripheral Interface Device MCS6520

- 1.5.1 Introduction

The MCS6520 is a direct pin for pin replacement for the Motorola MC6820 Peripheral Interface Adapter, the "PIA". As such, it meets all of the "PIA" electrical specifications and is totally

10

15

20

25

30

35

hardware compatible with the MC6820.

The MCS6520 is an I/O device which acts as an interface between the microprocessor and the peripherals such as printers, displays, keyboards, etc. The prime function of the MCS6520 is to respond to stimulus from each of the two worlds it is serving. On the one side, the MCS6520 is interfacing with the peripherals via two eight-bit bi-directional peripheral data ports. On the other side, the device interfaces with the microprocessor through an eight-bit data bus; this is the same data bus discussed at length in Section 1.3.1. It is, therefore, simplest to view the basic function of the MCS6520 as in the block diagram of Figure 1.23. In addition to the lines described above, the MCS6520 provides four interrupt input/peripheral control lines and the logic necessary for simple, effective control of peripheral interrupts. No external logic is required for interfacing the MCS650X microprocessor to most peripheral devices."

Especially notice the last sentence, above, "No external logic is required for interfacing the MCS650X microprocessor to most peripheral devices." This is another key to the multi-microcomputer system using BICPU microcomputers. All of the present MCS6502 microcode routines to do keyboard, CRT display, printer, disk and other usual data processing functions can be used either without change, or at most, very little change in the BICPU microcomputer invention.

It seems impossible, but with the BICPU microcomputer, only two basic logical bimemory hookups are required to logically interconnect several thousands of BICPU microcomputers in logical interacting parallel programs in a running multi-microcomputer system, with tens of thousands of parallel programs.

The logical bimemory "S" hookup (Straight Line) with a BIM mode on one end and a FLT mode on the other, with any number of interconnecting PRM-1 and PRM-2 modes in between, and the logical bimemory "Y" hookup with a BIM mode at the base of an imaginary "Y" and a FLT mode at the end of each branch of the imaginary "Y", with any number of interconnecting PRM-1 and PRM-2 modes in between the BIM mode and the FLT modes.

When programmers perfect the use of these two bimemory hookups, truly fantastic "bimemory logic structures" can be created that "mimic the thinking" of the human programmers and human field application design engineers involved.

In a climate forecasting context as outlined above, each ellipsoidal cell contains information pertaining to a specific volume of atmosphere. For processing this information, one or more BICPU microcomputers can be used for each cell. In accordance with the invention, information written by a first BICPU microcomputer to it's "A" bus circuits and stored in the standard memory connected thereto, can be logically directly read from these same "A" bus circuits by other mechanically and logically connected BICPU microcomputers. The consenting first BICPU microcomputer in a FLT mode, directly logically connects some or all of it's "A" bus circuits, to the other BICPU microcomputer in the BIM mode.

The other BICPU microcomputers individually take direct logical bimemory control of some or all of

10

15

20

25

30

35

the "A" bus circuits of the consenting first BICPU microcomputer, and the standard memory circuits connected thereto, using either a logical bimemory "S" hookup or a logical bimemory "Y" hookup, with the consent of the first BICPU microcomputer. Data from contiguous cells can thereby be evaluated very rapidly.

It is not necessarily intuitively obvious, but the BICPU microcomputer invention requires the human programmers to cause each and every logical interconnection of BIC-BUS circuits between any two BICPU microcomputers to be made by execution of appropriate program steps. This is an object of the invention.

The human field application system designers mechanically interconnect thousands of BICPU microcomputers in billions of different unique systems. Each and every one of the individual, independent BICPU microcomputers can run all of their individual parallel programs, and each and every one of the individual, independent BICPU microcomputers can communicate in their old fashion way, using the standard memory circuits connected to their "A" bus circuits, just the same as they do now. However, no logical bimemory "S" hookup between two BICPU microcomputers occurs on BIC-BUS circuits until the human programmers write new microcodes logically storing valid bus numbers in the new "B" and "C" registers and write logical bimemory hookup microcodes to logically interconnect two BICPU microcomputers, one in a BIM mode, and one or two in a consenting FLT mode.

The BICPU microcomputer invention, puts the human programmer — with the help of the human field application system designers — in complete control of the logical bimemory interconnection of BICPU microcomputers. The BICPU microcomputer causes human programmers to create truly highly parallel logic programs that fit the data flow of the problem, and best employ the data processing power and standard memory circuits connected to the "A" bus circuits of individual Bimemory Independent CPU microcomputers in a multi-BICPU microcomputer system, to enhance the data processing therein.

Specifically, if the state of a first cell changes, the first BICPU microcomputer modeling the first cell, can write data relating to these changes in the first cell, <u>directly</u> logically to the "A" bus circuits of a consenting second BICPU microcomputer modeling a second cell, and the standard memory circuits connected thereto.

Moreover, the first BICPU microcomputer modeling the first cell, can read data directly logically from the "A" bus circuits, and the standard memory circuits connected thereto, of the consenting second BICPU microcomputer modeling the second cell. With such direct logical bimemory hookup capabilities for each BICPU microcomputer, a system can be formed where BICPU microcomputers — and the standard memory circuits connected to their "A" bus circuits — can be linked, treed and chained to closely model the interactive data flow of the modeled cells that make up the atmosphere or some other complex system.

In accordance with the invention, the BICPU microcomputers contain all of the necessary switching circuits, arbitration logic circuits and error detecting circuits needed to effectively logically interconnect BICPU microcomputers in either the logical bimemory "S" hookup or the logical bimemory "Y" hookup, within the individual BICPU microcomputers. Since all logic switching circuits, all arbitration logic circuits and error detecting circuits are contained within the BICPU microcomputers, only simple, single circuit, BIC-BUS circuits

10

15

20

25

30

are needed to mechanically interconnect the "B" and "C" bus circuits of two BICPU microcomputers.

Therefore, in a large multi-BICPU microcomputer system of several thousand BICPU microcomputers mechanically interconnected with several thousand BIC-BUS circuits, the only logic circuits needed on the CPU side of the "A" bus circuits is the BICPU of the BICPU microcomputer invention itself. The fabrication costs of multi-BICPU microcomputer systems are, therefore, notably reduced. The BICPU microcomputers are also, preferably, adapted from existing highly successful microprocessor or microcomputer chips.

Multi-BICPU microcomputers systems require only BICPU microcomputers, standard BIC-BUS circuits, and standard memory circuits containing present standard peripherals.

The cost of adding the BICPU microcomputer bimemory switching circuits to present microprocessors is relatively small, and the total costs will be fairly low, compared to present multiprocessor systems. The billions of man hours, that have gone into developing standard microcode routines, to handle such mundane computer tasks as monitoring the keyboard, displays, disks and other peripheral equipment, over the past twenty years, will continue to be used fully. The object of practicality is thus achieved.

# BRIEF DESCRIPTION OF THE DRAWINGS

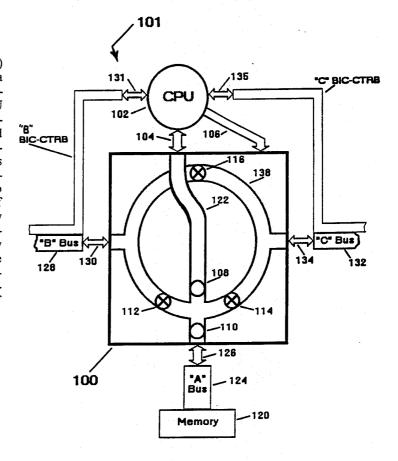

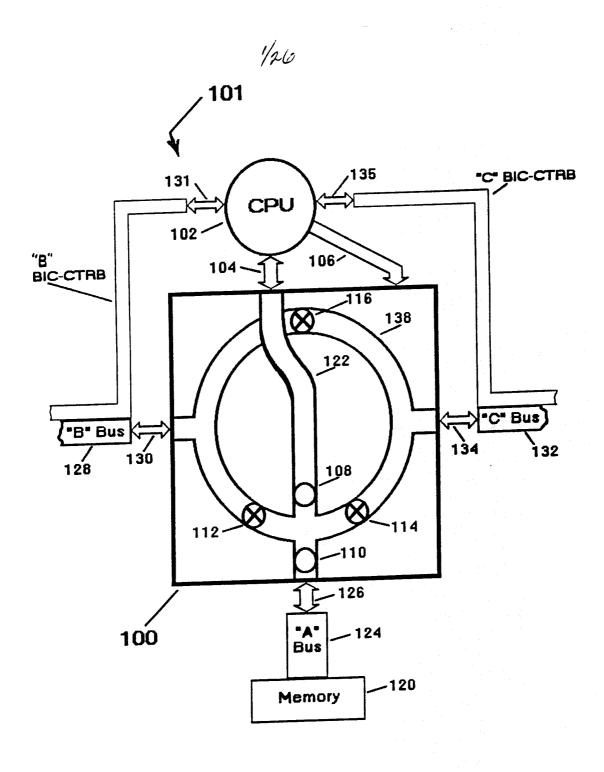

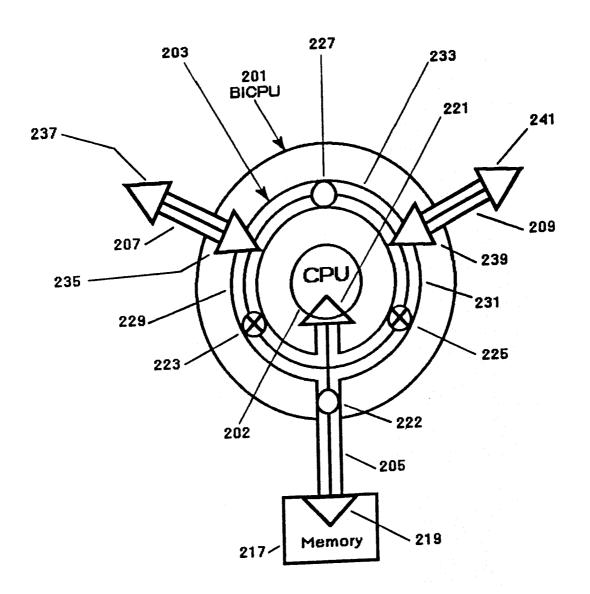

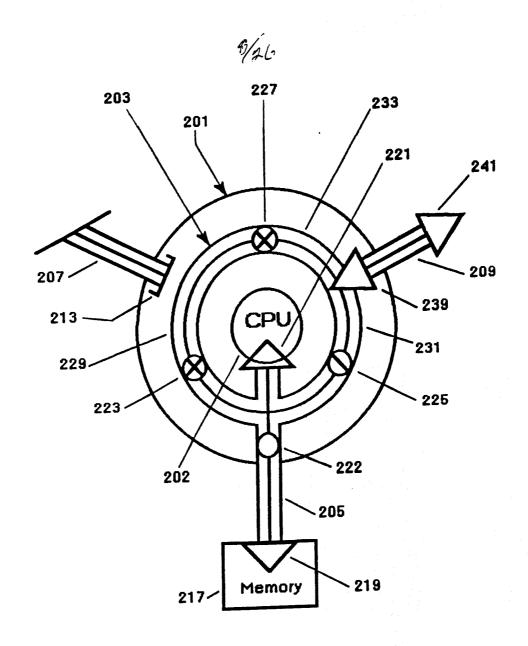

Figure 1 is a general diagram of one simple bimemory switching circuit according to the invention, in one of the dedicated standard memory circuits between the CPU and the "A" bus circuits, the "B" bus circuits and the "C" bus circuits.

There is one such bimemory switching circuit connected in each BICPU microcomputer dedicated standard memory address circuit, standard memory data circuit and standard memory control circuit.

Figure 2 illustrates the logically disconnected and latched positions of the five major switch means in the bimemory switching circuits and the logically disconnected and latched, floating circuits of the first and second switch means in the automatic power off deactivated mode.

This logically disconnected and latched, power off deactivated mode is an object of the invention.

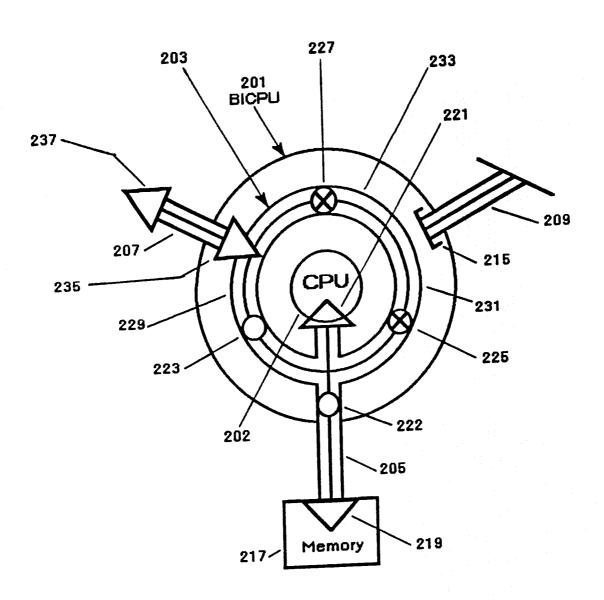

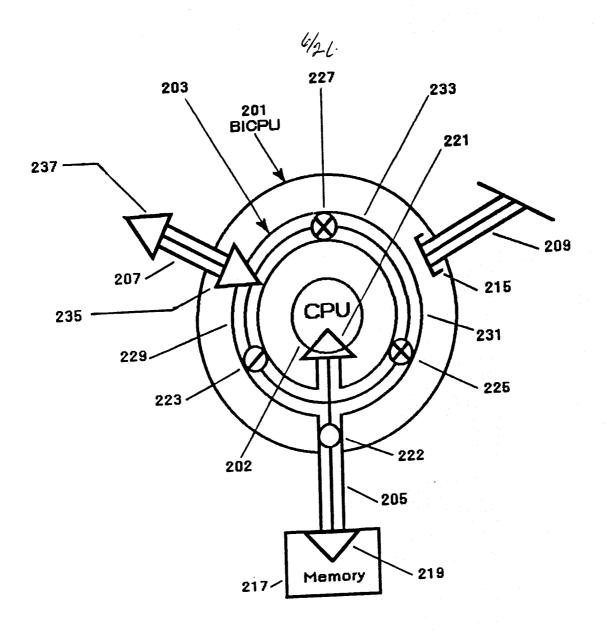

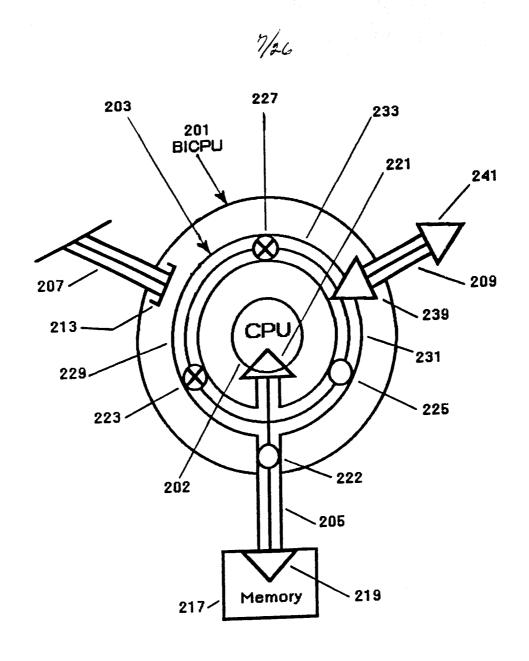

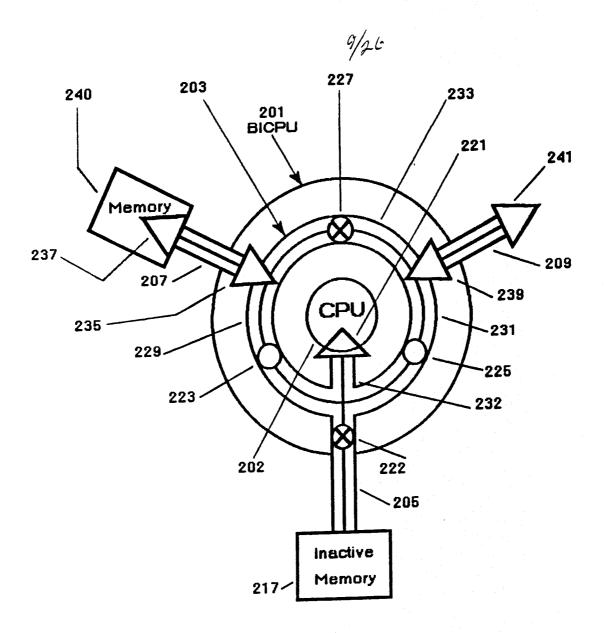

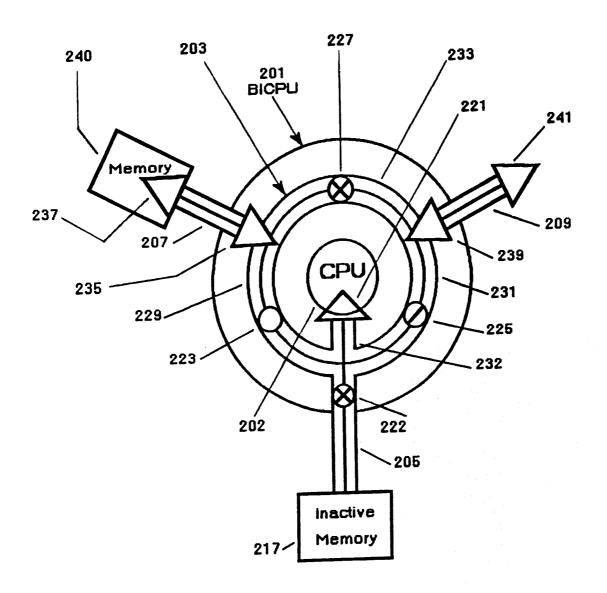

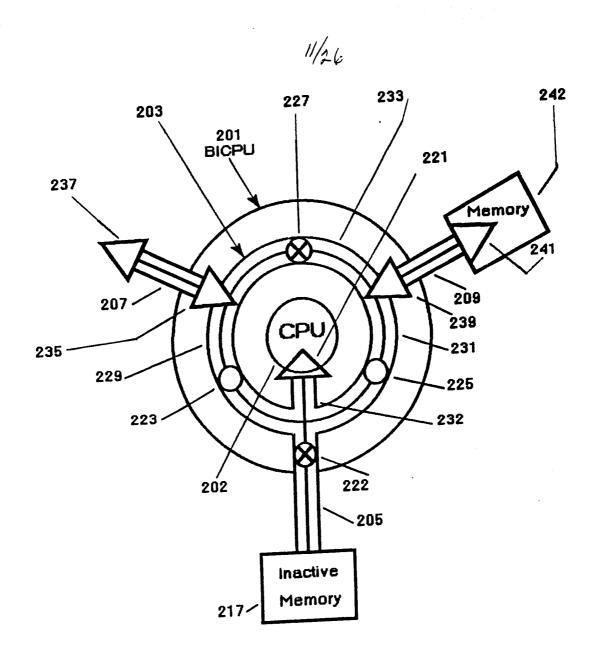

Each of Figures 3 through 13 and 15 through 17 illustrate the logically disconnected and latched positions or the logically connected and unlatched logical bimemory hookup positions of the third through seventh switch means in the bimemory switching circuits, controlled by the CPU 202 to place the BICPU microcomputer in fifteen different logical bimemory modes, when power is being supplied to the power circuits.

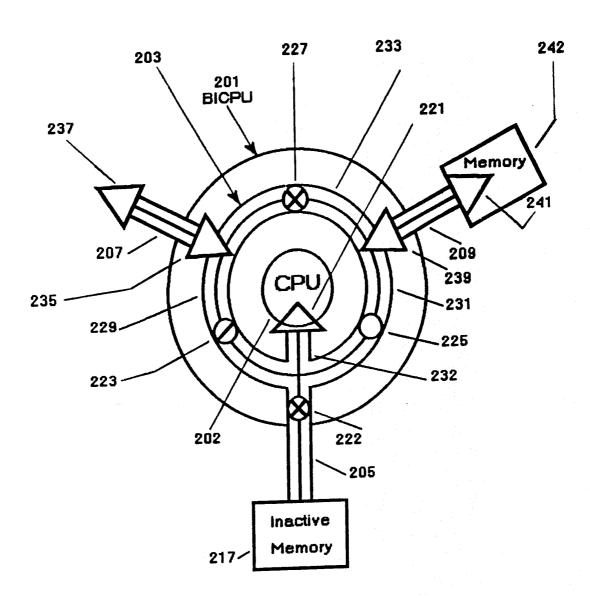

Figure 3 represents the PRM-0 mode.

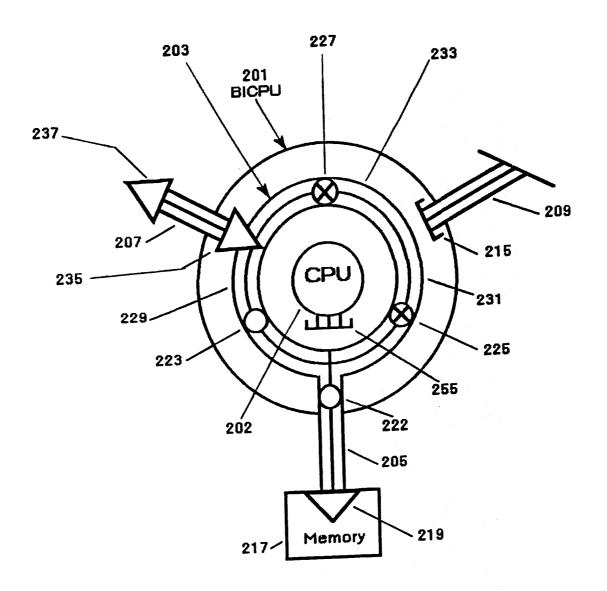

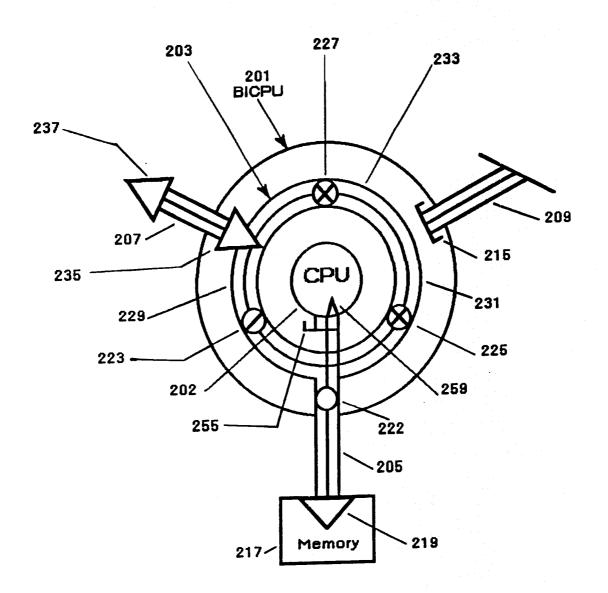

Figure 4 represents the PRM-1 and PRM-2 modes.

Figure 5 represents the BIM-0 mode.

Figure 6 represents the BIM-1 mode.

Figure 7 represents the BIM-2 mode.

Figure 8 represents the BIM-3 mode.

Figure 9 represents the BIM-4 mode.

Figure 10 represents the BIM-5 mode.

Figure 11 represents the BIM-6 mode.

Figure 12 represents the BIM-7 mode.

Figure 13 represents the FLT-0 mode.

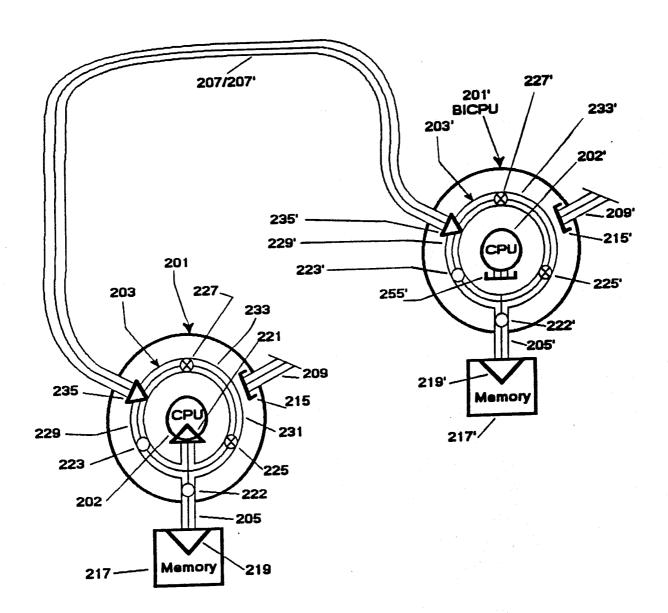

Figure 14 is an illustration of the logically disconnected and latched switch means, the logically connected and latched switch means and the logically connected and unlatched switch means of two BICPU microcomputers in a logical bimemory "S" hookup.

Figure 15 represents the FLT-1 mode.

Figure 16 represents the FLT-2 mode.

Figure 17 represents the FLT-3 mode.

Figure 18 is a diagram depicting one way one ILU load can be logically connected to, and logically disconnected from, the "BRQ" circuit, and how the "BEN" and "BRQ" circuits of one ILU, can be logically connected to the "BEN" and "BRQ" circuits of the "B" and "C" bus circuits.

Figure 19 is a detailed diagram of a BICPU microcomputer.

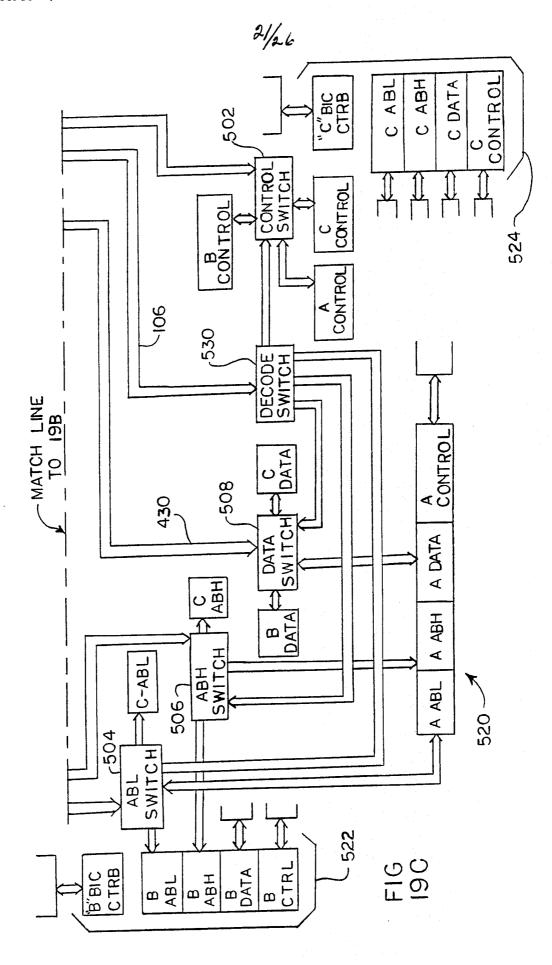

Figure 20 is an illustration of BICPU microcomputers connected along dedicated standard Bimemory Interconnecting Control-BUS (BIC-BUS) circuits connected to "B" and "C" bus circuits, 522 and 524 of Figure 19.

Figure 21 is another illustration of BICPU microcomputers connected along dedicated BIC-BUS circuits connected to "B" and "C" bus circuits.

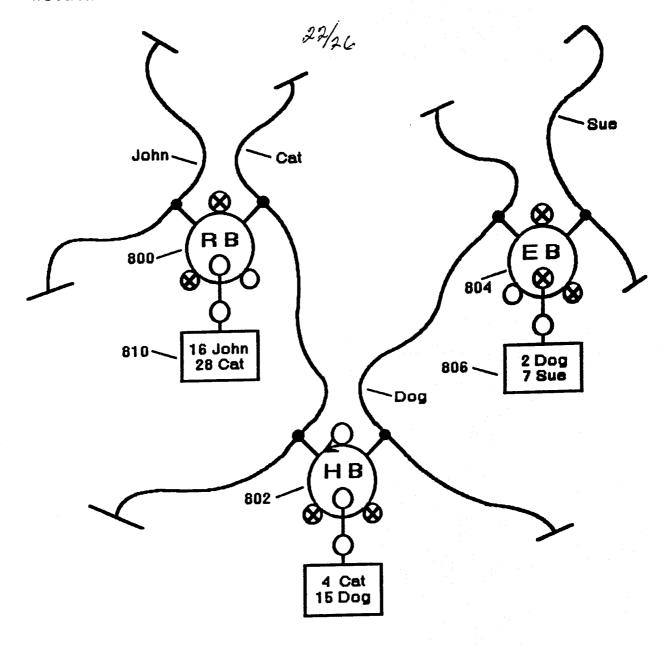

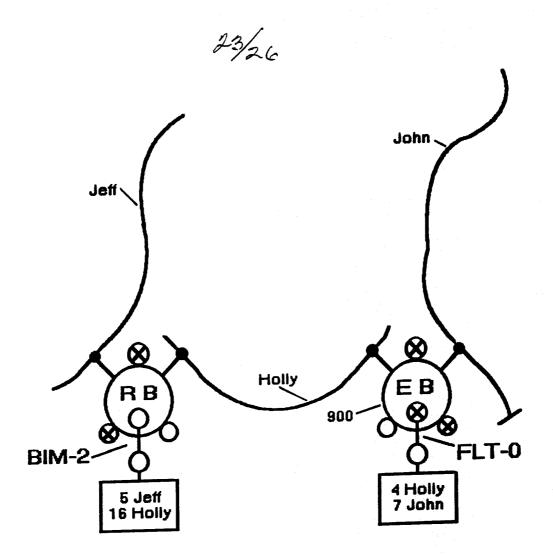

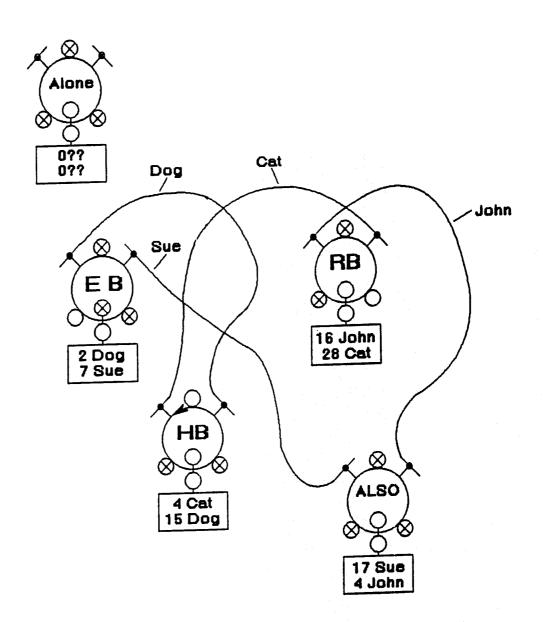

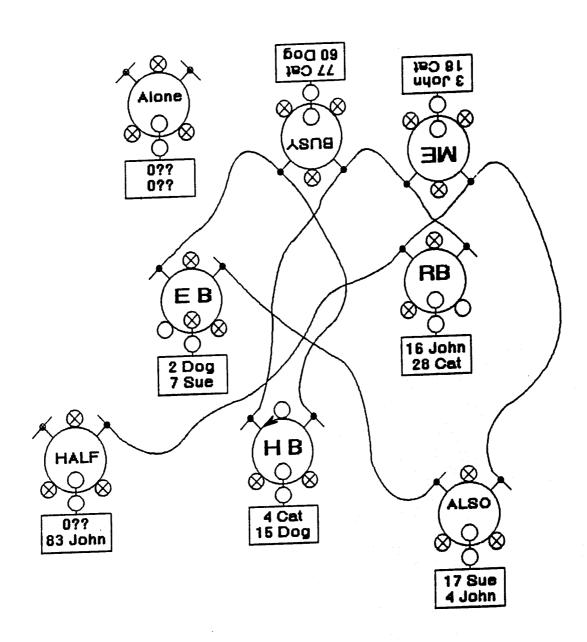

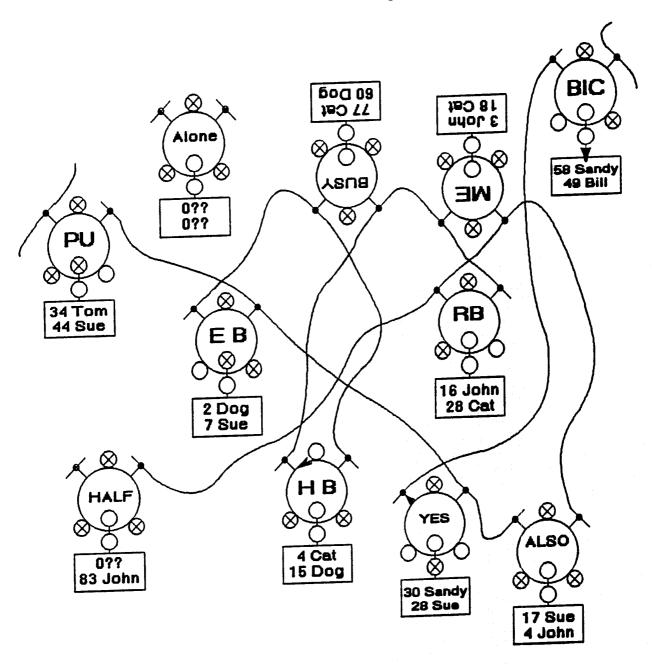

Figures 22 through 24 illustrate how a given multi-microcomputer system of BICPU microcomputers interconnected on sets of dedicated BIC-BUS circuits can be easily changed and modified, where both BICPU microcomputers and sets of dedicated BIC-BUS circuits can be added, that can contain additional "parallel" programs, without changing the program logic of the original system.

# DETAILED DESCRIPTION OF A PREFERRED EXEMPLARY EMBODIMENT OF THE INVENTION

# I. GENERAL DESCRIPTION OF THE BIMEMORY SWITCHING CIRCUITS OF A BICPU MICROCOMPUTER

30

5

10

15

20

25

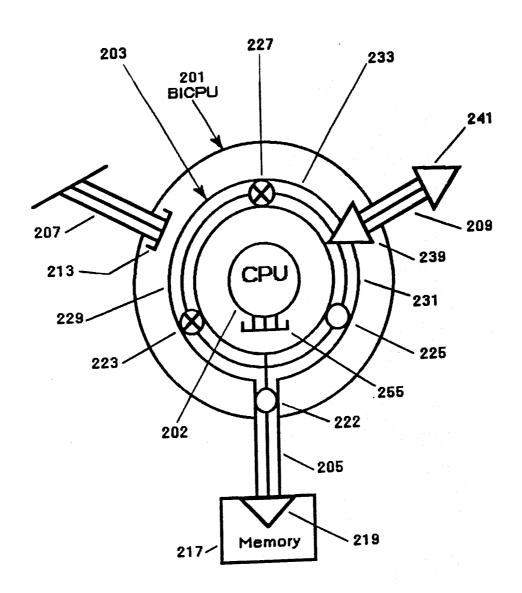

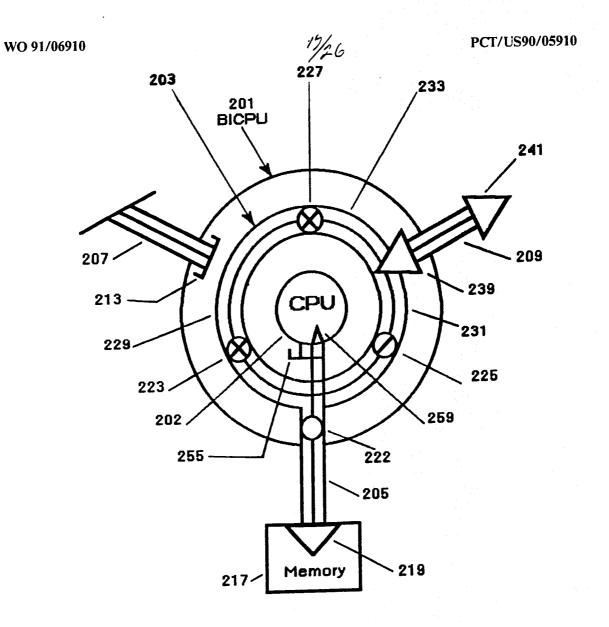

In Figure 1, a basic diagram of a bimemory switching unit 100 of a bimemory microcomputer (BICPU microcomputer) 101 — in accordance with the invention — is illustrated. The bimemory switching unit 100 is attached to a conventional central processor unit (CPU) 102 — (such as a MCS6502 or some other similar microcomputer) — being implemented on the BICPU microcomputer invention. The bimemory switching unit

WO 91/06910 PCT/US90/05910

21

100 is inserted and connected into each input and output circuit 104 presently connected to the microprocessor being implemented on the BICPU microcomputer invention, (excepting only the power circuits of the microprocessor which are connected directly to the power circuits of the BICPU microcomputer). The input and output circuits of the CPU prior to being implemented on the invention are directly logically connected to standard memory circuits 124 and such input and output circuits are herein referred to as the "A" bus circuits and the standard memory 120 connected thereto, of a BICPU microcomputer.

5

10

15

20

25

30

35

The switching unit 100 is connected to buses "A", "B" and "C" through the first, second and fourth parts of a first switching mechanism divided into five parts 126, 130, 131, 134, and 135, and is connected to the CPU 102 through a second switch mechanism 104. These switches are utilized to connect the address, data and control lines necessary for the proper memory access between the buses, the switching unit 100 and the CPU, 102. The third 131 and fifth 135 parts of the first switch are utilized to connect the CPU, 102 to the system address and status lines of the "B" and "C" buses.

Control lines, 106, enable the CPU, 102 to logically connect and disconnect the desired switches including the above described first and second as well as the third 108, fourth 110, fifth 112, sixth 114, and seventh 116. The third through seventh switches are utilized to create a data flow path through the switching unit 100 for transfer of data between the CPU 102 and the memory 120 and the "B" and "C" buses.

Based on signals from the CPU of the BICPU microcomputer on the control circuits 106, the first switch means (in 126, 130 and 134 circuits in Figure 1), the second switch means (in 104 circuits in Figure 1), the third switch means 108, the fourth switch means 110, the fifth switch means 112, the sixth switch means 114 and the seventh switch means 116 are logically disconnected and logically connected to (a) permit logical data flow, (b) to inhibit logical data flow, or (c) permit logical data flow to or from the "A" bus circuits 124 and the standard memory circuits connected thereto, of a BICPU microcomputer. Each first switch means, second switch means, third switch means 108, fourth switch means 110, fifth switch means 112, sixth switch means 114 and seventh switch means 116, it is noted, actually represents a plurality of logical elements, each of which can logically connect or logically disconnect an address, data, or control circuit that is mechanically connected to the switch means, under the control of the CPU 102 when power is being supplied to the BICPU microcomputer power circuits.

By appropriately logically connecting and logically disconnecting the first switch means (in 126, 130 and 134 circuits in Figure 1), the second switch means (in 104 circuits in Figure 1), the third switch means 108, the fourth switch means 110, the fifth switch means 112, the sixth switch means 114 and the seventh switch means 116, data can be logically transferred along any of various paths. Specifically, it is noted that the CPU 102 in Figure 1 has logically connected and latched it's second, third and fourth switch means 108 and 110, and it's first switch means connected to it's fourth switch means, and has logically disconnected and latched it's fifth, sixth and seventh switch means 112, 114 and 116, and it's first switch means connected to it's fifth and sixth switch means, thus logically connecting CPU 102 to the "A" bus circuits 124 and the standard memory circuits

10

15

20

25

30

35

120 connected thereto, via a path used by conventional CPUs. In the invention, the logical transfer of data between CPU 102 and the "A" bus circuits and the standard memory circuits 120 connected thereto, is over the first internal bus circuits 122 (via I/O circuits 104 each with second switch means, via the third switch means 108 to a common junction point), and the second internal bus circuits to it's "A" bus circuits 124 (from the common junction point, via the fourth switch means 110, via I/O circuits 126 each with first switch means). As depicted in Figure 1, the third switch means 108 and fourth switch means 110 are logically connected and latched (i.e. there is no "X" in the two small circles representing the switch means) permitting logical data transfer between CPU 102 and the "A" bus circuits 124 and the standard memory circuits 120 connected thereto. CPU 102 is directly logically connected to and directly logically controls the dedicated standard address circuits, standard data circuits, and standard control circuits, connected to the "A" bus circuits 124 and the standard memory circuits 120 connected thereto.

The fifth switch means 112 is a switching device, under the control of the BICPU microcomputer, that can logically connect and logically disconnect the circuit between the common junction point and the "B" bus circuits 128 (via I/O circuits 130 each with first switch means). The "B" bus circuits 128 can be mechanically connected to BIC-BUS circuits and logically connected to the "A" bus circuits and the standard memory circuits connected thereto, of a consenting second BICPU microcomputer. By logically disconnecting the sixth switch means 114, and logically disconnecting the fourth switch means 110, and logically connecting the fifth switch means 112 in a bimemory manner, CPU 102 directly logically connects the first BICPU microcomputer to the "A" bus circuits and the standard memory circuits connected thereto, of a consenting second BICPU microcomputer on the "B" bus circuits 128, can directly logically connect the first BICPU microcomputer 101, to some or all of the consenting second BICPU microcomputer's "A" bus circuits and the standard memory circuits connected thereto, for a logical bimemory hookup.

In this way, the first BICPU microcomputer 101 can be <u>directly</u> logically connected to, and <u>directly</u> logically control some or all of the "A" bus circuits and the standard memory circuits connected thereto, of a consenting second BICPU microcomputer.

The first BICPU microcomputer 101 can be directly logically connected to, and thus directly logically control it's own "A" bus circuits and the standard memory circuits 120 connected thereto, or can be directly logically connected to, and thus directly logically control some or all of the "A" bus circuits and the standard memory circuits connected thereto, of a consenting second BICPU microcomputer in a bimemory manner. This logical bimemory hookup is called a logical bimemory "S" hookup.

The "Bimemory" characterization of the invention, comes from the fact that at the same time, one BICPU microcomputer in a BIM mode can be <u>directly</u> logically connected to, and <u>directly</u> logically control some or all of two "A" bus circuits and the standard memory circuits connected thereto, in a logical bimemory manner.

The "Independent" characterization of the invention, comes from the fact that every BICPU

10

15

20

25

30

35

microcomputer can be logically disconnected from BIC-BUS circuits connected to it's "B" and "C" bus circuits and operate completely in a stand alone independent manner, at any time, without causing a failure of the program logic of other running BICPU microcomputers logically connected to the same BIC-BUS circuits, and without causing a failure of it's own program logic.

The sixth switch means 114 is a switching device, under the control of the BICPU microcomputer, that can logically connect and logically disconnect the circuit between common junction point and the "C" bus circuits 132 (via I/O circuits 134 each with first switch means). The "C" bus circuits 132 can be mechanically connected to BIC-BUS circuits and logically connected to a consenting third BICPU microcomputer. By logically disconnecting the fifth switch means 112, and logically disconnecting the fourth switch means 110, and logically connecting the sixth switch means 114 in a bimemory manner, CPU 102 directly logically connects the first BICPU microcomputer to some or all of the "A" bus circuits and the standard memory circuits connected thereto, of a consenting third BICPU microcomputer logically connected to the "C" bus circuits 132.

The consenting third BICPU microcomputer on the "C" bus circuits 132, can directly logically connect the first BICPU microcomputer 101, to some or all of the consenting third BICPU microcomputer's "A" bus circuits and the standard memory circuits connected thereto, for a logical bimemory hookup.

Referring now to the seventh switch means 116, a particularly significant aspect of the invention is achieved. The seventh switch means 116 is a switching device, under the control of the BICPU microcomputer. Specifically, logically disconnecting and latching the fifth and sixth switch means and logically connecting and latching the seventh switch means 116, directly logically interconnects the standard address, data, and control circuits between the "B" bus circuits 128 and the "C" bus circuits 132 over the fifth internal bus circuits 138. That is, a second BICPU microcomputer on the "B" bus circuits 128 can be directly logically connected to and directly logically control the "A" bus circuits and the standard memory circuits connected thereto, of a third BICPU microcomputer on the "C" bus circuits 132 via the fifth internal bus circuits 138. Conversely, a third BICPU microcomputer on the "C" bus circuits 132 can be directly logically connected to and directly logically control the "A" bus circuits and the standard memory circuits connected thereto, of a second BICPU microcomputer on the "B" bus circuits 128 via the fifth internal bus circuits 138. The first BICPU microcomputer 101 thereby directly logically interconnecting the two sets of BIC-BUS circuits connected to it's "B" bus circuits 128 and "C" bus circuits 132.

The logically disconnecting and logically connecting of the first switch means, the second switch means, the third switch means 108, the fourth switch means 110, the fifth switch means 112, the sixth switch means 114 and the seventh switch means 116 results in the BICPU microcomputer 101 assuming the various bimemory modes depicted in Figures 2 through 17.

Particularly notice that the standard BIC-BUS circuits mechanically directly logically interconnect "A" bus circuits and CPUs of the BICPU microcomputer invention on the CPU side of the "A" bus circuits, 520 of Figure 19.

Intuitively, it can seem the standard BIC-BUS circuits are mechanically interconnecting the standard memory circuits of two BICPU microcomputers.

#### This is not the case.

5

10

15

20

25

30

35

Standard memory circuits are connected only to "A" bus circuits of BICPU microcomputers. Standard BIC-BUS circuits are never connected to "A" bus circuits or to standard memory circuits. In a BICPU microcomputer, the standard address circuits in the "A" bus circuits always send the address information to the standard memory circuits connected thereto.

The standard address circuits of the "B" and "C" bus circuits are bi-directional standard address circuits, similar to the bi-directional standard data circuits. The "B" and "C" bus circuits are connected to BIC-BUS circuits, which are connected to other "B" or "C" bus circuits.

When the "B" or "C" bus circuits are used to <u>directly</u> logically connect the CPU of this BICPU microcomputer in a BIM mode, through BIC-BUS circuits to "A" bus circuits of a consenting BICPU microcomputer in a FLT mode, standard address information is always sent from this BICPU microcomputer in a BIM mode, to the "A" bus circuits of the consenting BICPU microcomputer in the FLT mode.

When the "B" or "C" bus circuits are used to <u>directly</u> logically connect a BICPU microcomputer in a BIM mode to the "A" bus circuits of this consenting BICPU microcomputer in a FLT mode, standard address information is always sent from the BICPU microcomputer in the BIM mode to the "A" bus circuits of this consenting BICPU microcomputer in a FLT mode.

When the "B" and "C" bus circuits of this interconnecting BICPU microcomputer in a PRM-1 or PRM-2 mode, are used to <u>directly</u> logically interconnect a BICPU microcomputer in a BIM mode, on either the "B" or "C" bus circuits, with a BICPU microcomputer in a consenting FLT mode, on the other "C" or "B" bus circuits, standard address information is always sent from the BICPU in the BIM mode to the BICPU in the FLT mode.