(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5393965号

(P5393965)

(45) 発行日 平成26年1月22日(2014.1.22)

(24) 登録日 平成25年10月25日(2013.10.25)

(51) Int.Cl.

H01L 21/66 (2006.01)

GO1R 31/28 (2006.01)

F 1

H01L 21/66

GO1R 31/28

GO1R 31/28Z

H

B

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2007-242656 (P2007-242656)

(22) 出願日 平成19年9月19日 (2007.9.19)

(65) 公開番号 特開2008-91902 (P2008-91902A)

(43) 公開日 平成20年4月17日 (2008.4.17)

審査請求日 平成22年9月16日 (2010.9.16)

(31) 優先権主張番号 10-2006-0096065

(32) 優先日 平成18年9月29日 (2006.9.29)

(33) 優先権主張国 韓国 (KR)

前置審査

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100086368

弁理士 萩原 誠

(72) 発明者 季 鍾 弦

大韓民国京畿道水原市靈通區靈通洞 サル

グゴル7 地アパート711棟1102号

最終頁に続く

(54) 【発明の名称】半導体集積回路装置の不良分析方法及びシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

第2ウエハ内の欠陥のある不良ピットを探し出し、前記欠陥の位置と前記不良ピットの位置とが互いにマッチする前記不良ピットのアナログ特性を測定し、前記欠陥と前記アナログ特性との間に相関関係があるかを検証し、前記相関関係があると検証された前記欠陥と前記アナログ特性とを対応付けてデータベースに保存し、

電気的テストにより第1ウエハ内の欠陥のある不良ピットを探し出し、

前記第1ウエハ内の欠陥のある不良ピットのアナログ特性を測定し、

前記測定されたアナログ特性と前記データベースに保存されたアナログ特性とを比較して、前記データベースに保存された複数のアナログ特性の中から、前記測定されたアナログ特性に類似する1つ以上のアナログ特性とそれらと相関関係にある1つ以上の欠陥と共に提供することにより、不良の原因となった欠陥を判別することを特徴とする不良分析方法。

## 【請求項 2】

前記第2ウエハ内の前記欠陥は、前記第2ウエハの製造工程中に前記第2ウエハに対して欠陥検査を実施して前記第2ウエハの外観に形成された欠陥の位置及び写真を求めるこことにより探し出すことを特徴とする請求項1に記載の不良分析方法。

## 【請求項 3】

前記第2ウエハ内の前記不良ピットは、前記第2ウエハの製造工程が完了した後、前記第2ウエハに対して電気的テストを実施して前記不良ピットの位置を求ることにより探

し出すことを特徴とする請求項 1 に記載の不良分析方法。

【請求項 4】

前記検証は、前記欠陥を反映した回路をモデリングし、前記モデリングした回路をシミュレーションして得たアナログ特性と前記不良ビットを測定して得たアナログ特性とを比較することにより行うことを特徴とする請求項 1 に記載の不良分析方法。

【請求項 5】

第 1 ウエハの製造工程中に、前記第 1 ウエハに対して欠陥検査を実施して前記第 1 ウエハ内の欠陥を探し出し、前記第 1 ウエハの製造工程が完了した後、前記第 1 ウエハに対して電気的テストを実施して前記第 1 ウエハ内の不良 S R A M セルを探し出し、前記欠陥の位置と前記不良 S R A M セルの位置とが互いにマッチされる不良 S R A M セルのアナログ特性を測定し、前記第 1 ウエハ内の欠陥と、前記第 1 ウエハ内の不良 S R A M セルの前記アナログ特性との間に相関関係があるか否かを検証し、前記相関関係があると検証された前記欠陥と前記アナログ特性とを対応付けてデータベースに保存し、第 2 ウエハの製造工程が完了した後で、前記第 2 ウエハに対して電気的テストを実施して前記第 2 ウエハ内の不良 S R A M セルを探し出し、前記第 2 ウエハ内の不良 S R A M セルのアナログ特性を測定し、前記第 2 ウエハ内の不良 S R A M セルの測定されたアナログ特性と前記データベースに保存されたアナログ特性とを比較して、前記データベースに保存された複数のアナログ特性の中から、前記測定されたアナログ特性に類似する 1 つ以上のアナログ特性とそれらと相関関係にある 1 つ以上の欠陥とを共に提供することにより、不良の原因となった欠陥を判別することを含む不良分析方法。

10

20

【請求項 6】

第 2 ウエハの製造工程には、第 2 ウエハに対して欠陥検査を実施しない請求項 5 に記載の不良分析方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置の不良分析方法及びシステムに関する。

【背景技術】

【0002】

従来の静的ランダムアクセスメモリ ( S R A M : S t a t i c R a n d o m A c c e s s M e m o r y ) の不良分析技術は、多様にあり、欠陥検査法、物理的分析法、電気的特性測定法などが例として挙げられる。特許文献 1 にも不良分析技術が開示されている。欠陥検査法は、ウエハの多数の製造工程を各々進行させる度にウエハの外観 ( e x t e r n a l a p p e a r a n c e ) を検査して、欠陥の位置、大きさなどを検査する方法である。物理的分析法は、ウエハの製造工程が完成された後、物理的にデプロセッシング ( d e p r o c e s s i n g ) しつつ、欠陥を直接的に探し出す方法であり、電気的特性測定法は、ウエハの製造工程が完成された後、 S R A M セルの電気的特性を測定することによって、不良ビットの位置を探し、収率 ( y i e l d ) ( すなわち、全体チップ ( またはダイ ( d i e ) ) のうち、グッドチップ ( g o o d c h i p ) の比率 ) を探し出す方法である。

30

40

【0003】

ところで、これら方法は、大規模 ( m a s s i v e ) に進行することは難しく、何より不良分析をするのに長時間を要する。のみならず、欠陥検査法は、多数の製造工程を進行する度に検査を実施するので、製造工程時間及び人件費を増加させて、結局、半導体チップのコストを増加させる。また、デザインルールが徐々に小さくなり、半導体工程がさらに複雑になることによって、電気的特性検査のみを実施しては、不良を完全に分析するには難点があった。

【特許文献 1】大韓民国特許公開 2003 - 083563 号

【発明の開示】

【発明が解決しようとする課題】

50

**【0004】**

本発明が解決しようとする技術的課題は、さらに迅速で正確な不良分析方法を提供することにある。

**【0005】**

本発明が解決しようとする他の技術的課題は、さらに迅速で正確な不良分析システムを提供することにある。

**【0006】**

本発明の技術的課題は、以上で言及した 技術的課題に制限されず、言及されていない他の 技術的課題は下記の記載から当業者に明確に理解されうる。

**【課題を解決するための手段】**

10

**【0007】**

前記技術的課題を達成するための本発明の一態様による半導体集積回路装置の不良分析方法は、互いに相関関係のある欠陥とアナログ特性とをデータベースに保存し、第1ウエハ内の不良ビットを探し出し、第1ウエハ内の不良ビットのアナログ特性を測定し、該測定されたアナログ特性とデータベースに保存されたアナログ特性とを比較して、不良の原因となった欠陥を判別することを含む。

**【0008】**

前記技術的課題を達成するための本発明の他の態様による半導体集積回路装置の不良分析方法は、第1ウエハの製造工程中に、第1ウエハに対して欠陥検査を実施して第1ウエハ内の欠陥を探し出し、第1ウエハの製造工程が完了した後で、第1ウエハに対して電気的テストを実施して第1ウエハ内の不良S R A Mセルを探し出し、欠陥の位置と不良S R A Mセルの位置とが互いにマッチされる不良S R A Mセルのアナログ特性を測定し、第1ウエハ内の欠陥と、第1ウエハ内の不良S R A Mセルのアナログ特性との間に相関関係があるかを検証し、相関関係があると検証された欠陥とアナログ特性とをデータベースに保存し、第2ウエハの製造工程が完了した後で、第2ウエハに対して電気的テストを実施して第2ウエハ内の不良S R A Mセルを探し出し、第2ウエハ内の不良S R A Mセルのアナログ特性を測定し、第2ウエハ内の不良S R A Mセルの測定されたアナログ特性とデータベースに保存されたアナログ特性とを比較して、不良の原因となった欠陥を判別することを含む。

20

**【0009】**

30

前記技術的課題を達成するための本発明の一態様による半導体集積回路装置の不良分析システムは、相関関係のある欠陥とアナログ特性とを保存しているデータベース、第1ウエハ内の不良ビットを探し出す電気的テスタ、第1ウエハ内の不良ビットのアナログ特性を測定するアナログ特性テスタ、及び測定されたアナログ特性と、データベースに保存されたアナログ特性とを比較して不良の原因となった欠陥を判別する分析器を備える。

**【0010】**

その他の実施例の具体的な事項は詳細な説明及び図面に含まれている。

**【発明の効果】****【0011】**

半導体集積回路装置の不良分析方法及びシステムによれば、欠陥とアナログ特性とをデータベース化して不良分析を行うために、製造工程中には、欠陥検査を行わなくてもよく、測定されたアナログ特性と最も高い相関関係のある欠陥を容易に探し出すことができる。したがって、本発明は、従来に比べてさらに迅速で正確に不良分析を行える。

40

**【発明を実施するための最良の形態】****【0012】**

以下、添付された図面を参照して本発明の実施形態を詳細に説明する。本発明の利点及び特徴、そしてこれを達成する方法は添付された図面に基づいて詳細に後述されている実施例を参照すれば明確になる。しかし、本発明は以下で開示される実施例に限定されるものではなく、この実施例から外れて多様な形に具現でき、本明細書で説明する実施例は本発明の開示を完全にし、本発明が属する技術分野で当業者に発明の範ちゅうを完全に報せ

50

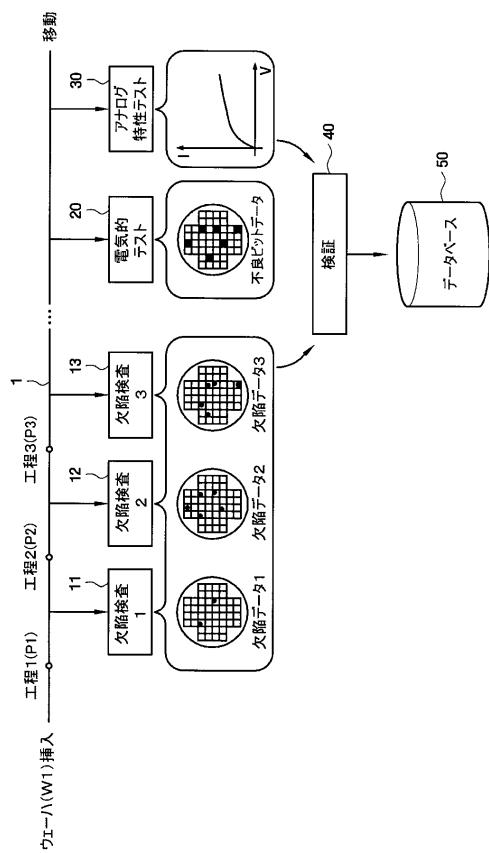

るために提供されるものであり、本発明は請求項及び発明の詳細な説明により定義されるだけである。明細書全体に亘って同一の参照符号は同一の構成要素を示す。図1及び図2は本発明の一実施形態による半導体集積回路装置の不良分析方法を説明するための図である。具体的に、図1は、相関関係のある欠陥と、不良ビットのアナログ特性を保存するデータベースを作る方法を説明するための図であり、図2は、図1で作ったデータベースを用いて不良の原因となった欠陥を探し出す方法を説明するための図である。

#### 【0013】

まず、図1を参照すれば、製造ライン1は、工程1 P1、工程2 P2、工程3 P3などを含み、各工程 P1、P2、P3に対応して製造装置が配されている。製造ライン1にウエハW1が挿入されれば、工程1 P1、工程2 P2、工程3 P3などの順番で順次に進行し、このような工程 P1、P2、P3を通じてウエハW1内には、半導体集積回路装置のチップが多数個同時に形成される。本発明の一実施形態において、半導体集積回路装置は、例えば、2次元的に配列された多数のメモリセルを含むメモリ領域を含み、メモリセルは、例えば、S R A M セルであり得る。

#### 【0014】

欠陥検査11、12、13は、各工程1 P1、工程2 P2、工程3 P3が進行する度に、詳しくは、ウエハW1上に一層のレイヤを形成する度に実施しうる。欠陥検査11、12、13は、光学的方法、スキャニングなどを通じてウエハW1の外観に形成された欠陥を探し出す。具体的に、欠陥は、外来物質、欠陥パターンなどであり得るが、これは例示的なものに過ぎず、これに限定されるものではない。外来物質は、製造工程中に製造装置内で形成された物質であることもあり、製造工程後に残された物質であることもあり、エッティング残留物 (e t c h i n g r e s i d u e)、ホコリなどでもあり、そのサイズは、約0.1 μmないし数百μm程度であり得る。また、欠陥パターンは、例えば、フォトリソグラフィ、エッティングなどの工程進行中に、所望しないパターン、ヒルロック、色の変化などを意味しうる。

#### 【0015】

欠陥検査を行う装置としては、例えば、K L A I n c . の K L A 2 1 、 T E N C O N I n c . の S U R F S C A N 7 、日立社のW I 8 8 0などがあり得るが、これに限定されるものではない。

#### 【0016】

欠陥検査11、12、13により得られる欠陥データは、例えば、欠陥の位置（例えば、x、yアドレスで表示される）、欠陥写真、サイズ、形態、個数などであり、このような欠陥データは、欠陥検査器によって多少の差はあり得る。図1に例示的に図示された欠陥データにおいて、大きな円 (l a r g e c i r c l e)は、ウエハを意味し、ウエハ内の四角形は、チップ（またはダイ (d i e)）を意味し、黒いマークは、探し出した欠陥を意味する。図1に示された欠陥データは、便宜上、ウエハ内に欠陥の位置を表示したものであり、実際に欠陥検査器から出るデータはこれと異なることがある。

#### 【0017】

次いで、電気的テスト20が実行されるが、電気的テスト20は、製造ライン1を経て製造された（すなわち、製造工程が完了した後）チップ内のメモリセルの電気的特性を測定して不良ビットを探し出す。例えば、電気的テスト20は、メモリセル内にデータを書き込み、メモリセルからデータを再び読み出し、読み出しデータと書き込みデータとが異なる場合には、このようなメモリセルを不良ビットと定義する方式を使用しうる。

#### 【0018】

電気的テスト20を行う電気的テスタとしては、例えば、T e r a d y n e I n c . の J 9 3 7 、 A d v a n t e s t I n c . の T 5 3 6 5 Pなどがあり得るが、これに限定されるものではない。

#### 【0019】

電気的テスト20により得られる不良ビットデータは、例えば、不良ビットの位置（例えば、x、yアドレスで表示される）、不良モード（例えば、1ビット不良、2ビット不

10

20

30

40

50

良、ブロック不良)、収率(yield)などであり得る。ここで、収率は、全体チップのうち、グッドチップの比率を意味し、グッドチップは、不良ビットを含まないチップであり、バッドチップ(bad chip)は不良ビットを含むチップを意味する。図1に示された不良ビットデータは、大きな円がウエハを意味し、ウエハ内の黒い四角形がバッドチップを意味し、白い四角形がグッドチップを意味する。

#### 【0020】

次いで、ウエハW1内の不良ビットのアナログ特性を測定するアナログ特性テスト30を実施する。

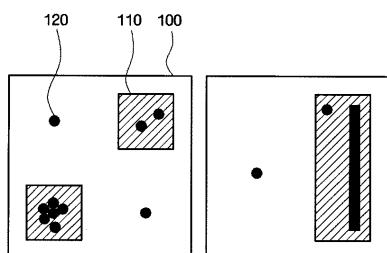

#### 【0021】

特に、不良ビットのアナログ特性を測定することは、欠陥検査11、12、13を通じて得られた欠陥の位置と、電気的テストを通じて得られた不良ビットの位置とが互いにマッチされる不良ビットに対してのみアナログ特性を探し出すことができる。但し、このような欠陥の位置と不良ビットの位置とをマッチさせる方法は、多様にあり得る。例えば、欠陥のアドレスと不良ビットのアドレスとが十分に近いか(near enough)、同一である場合、欠陥の位置と不良ビットの位置とがマッチされると判断しうる。図3を参照すれば、大きな四角形(squares)100はチップを意味し、ハッチングされた小さな四角形110は、不良ビットを意味し、黒いマーク120は、欠陥を意味する。ハッチングされた小さな四角形110内に黒いマーク120が位置すれば、互いにマッチされると判断しうる。

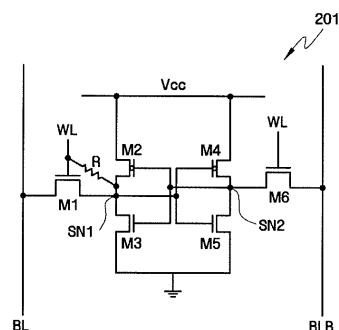

#### 【0022】

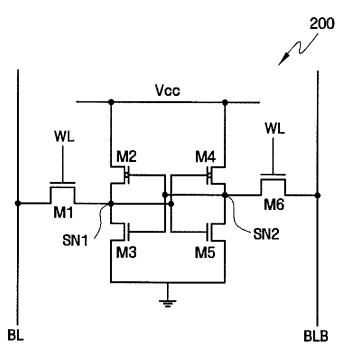

アナログ特性テスト30は、不良ビットの不良原因を探すために実施するテストであり、ビットがSRAMセルである場合を例示すれば、次の通りである。図4のように、6個のトランジスタで構成されたSRAMセル200は、ワードラインWLとビットライン対BL、BLBとが交差する領域と定義される。また、プルアップトランジスタM2、M4、プルダウントランジスタM3、M5が交差連結された(cross-coupled)インバータを構成し、アクセストランジスタM1、M6は、ストレージノードSN1、SN2に各々連結されている。もし、SRAMセル200の出力と相補出力(output bar)に対称性があれば、SRAMセル200のアナログ特性の分析に相当有利である。理想的に、SRAMセル200の両側が完全に均衡的であれば、SRAMセル200の出力と相補出力にスキュー(skew)が発生しないためである。但し、SRAMセルではないDRAMセル、フラッシュセル、PRAMセル、RRAMセル、MRAMセルなどである場合にも、本発明を適用できるということは当業者にとって自明である。

#### 【0023】

アナログ特性テスト30は、ビットラインBL、相補ビットラインBLB、ワードラインWLに特定電圧を印加し、6個のトランジスタM1～M6のうち少なくとも1つのトランジスタに流れる電流をビットラインBLまたは相補ビットラインBLBで測定する。SRAMセル200に対するバイアシング条件は、次の表1のようである。表1から提示されたバイアシング条件は、例示的なものに過ぎず、本発明の権利範囲がこのようなバイアシング条件に制限されるものではない。

#### 【0024】

10

20

30

40

【表1】

| バイアシング条件 | ビットライン<br>(BL) | 相補ビットライン<br>(BLB) | ワードライン<br>(WL) |

|----------|----------------|-------------------|----------------|

| A        | スイップ&測定        | Vcc               | Vcc            |

| B        | スイップ           | Vcc & 測定          | Vcc            |

| C        | Vcc            | スイップ&測定           | Vcc            |

| D        | Vcc & 測定       | スイップ              | Vcc            |

10

## 【0025】

バイアシング条件Aでは、ビットラインBLを0Vから所定電圧(例えば、1V)までスイープしつつ、ビットラインBLでの電流変化を測定し、バイアシング条件Bでは、ビットラインBLをスイープしつつ相補ビットラインBLBでの電流変化を測定し、バイアシング条件Cでは相補ビットラインBLBをスイープしつつ、相補ビットラインBLBでの電流変化を測定し、バイアシング条件Dでは相補ビットラインBLBをスイープしつつ、ビットラインBLでの電流変化を測定する。このような4種のバイアシング条件で各々アクセストランジスタM1またはM6、プルアップトランジスタM2またはM4、プルダウントランジスタM3またはM5のうち、少なくとも1つに流れる電流の大きさを測定する。

20

## 【0026】

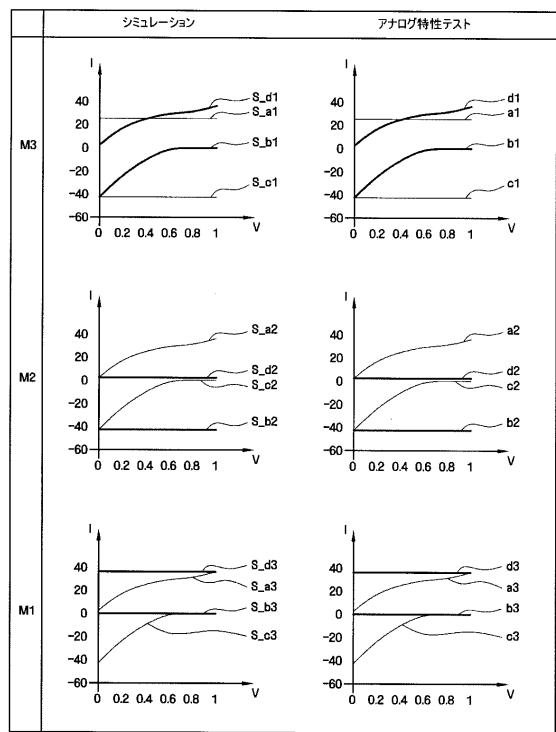

次いで、ウエハW1内の欠陥と測定されたアナログ特性との間に相関関係があるかを検証する(40)。図5及び図6を参照して検証方法を詳細に説明する。図5は、欠陥が発生したSRAMセルをモデリングした回路図であり、図6は、欠陥が発生したSRAMセルをシミュレーションして得たアナログ特性と、アナログ特性テストを通じて得たアナログ特性とを同時に示す図である。

30

## 【0027】

具体的に、不良ビットとマッチされる欠陥の欠陥写真を検討し、このような欠陥を反映した回路201をモデリングする。例えば、図5では、ストレージノードSN1とワードラインWLとの間にブリッジRが発生した場合をモデリングしたものである。

## 【0028】

次いで、モデリングした回路201をシミュレーションしてアナログ特性を探し出す。具体的に、図6でシミュレーションカーブs\_a1、s\_b1、s\_c1、s\_d1は、各々前述したバイアシング条件A、B、C、Dでモデリングした回路201のプルダウントランジスタM3に流れる電流の波形を示し、シミュレーションカーブs\_a2、s\_b2、s\_c2、s\_d2は、各々前述したバイアシング条件A、B、C、Dでモデリングした回路201のプルアップトランジスタM2に流れる電流の波形を示し、シミュレーションカーブs\_a3、s\_b3、s\_c3、s\_d3は、各々前述したバイアシング条件A、B、C、Dでモデリングした回路201のアクセストランジスタM1に流れる電流の波形を示す。

40

## 【0029】

このようにシミュレーションして得たアナログ特性と、アナログ特性テストを通じて得たアナログ特性とを比較する。具体的に、図6に示したアナログ特性カーブa1、b1、c1、d1は、各々前述したバイアシング条件A、B、C、DでウエハW1の不良SRAMセルのプルダウントランジスタM3に流れる電流の波形を示し、アナログ特性カーブa2、b2、c2、d2は、各々前述したバイアシング条件A、B、C、DでウエハW1の不良SRAMセルのプルアップトランジスタM2に流れる電流の波形を示し、アナログ特性カーブa3、b3、c3、d3は、各々前述したバイアシング条件A、B、C、DでウエハW1の不良SRAMセルのアクセストランジスタM1に流れる電流の波形を示す。

50

**【0030】**

同じバイアシング条件でのシミュレーションカーブとアナログ特性カーブ（例えば、 $s\_a_1$ と $a_1$ 、 $s\_b_1$ と $b_1$ ）とが相当類似している場合、ウエハW1内の欠陥と測定されたアナログ特性との間に相関関係があると判断されうる。ここで、類似如何を判断することは多様な方法があり得る。例えば、シミュレーションカーブとアナログ特性カーブとの相関係数を求め、相関係数が所定の基準値（例えば、0.9）以上になれば、シミュレーションカーブとアナログ特性カーブは、相当類似していると判断しうる。図6に示されたシミュレーションカーブとアナログ特性カーブは、ほぼ類似しているので、相関関係があると判断しうる。

**【0031】**

10

次いで、このように相関関係があると検証された欠陥と不良ビットのアナログ特性をデータベース50に保存する。

**【0032】**

データベース50を作るために、多数のウエハに対して前述した欠陥検査11、12、13、電気的テスト20、アナログ特性テスト30、検証30を反復して実施しうる。多数のウエハに対して繰り返して多くのデータを蓄積するほど、データベース50に保存されたデータの信頼性が高まりうる。

**【0033】**

20

ところで、多数のウエハに対して繰り返して実施すれば、不良ビットのアナログ特性と相関関係にある欠陥の種類は、1つ以上あり得る。すなわち、不良ビットのアナログ特性と欠陥の種類は、必ずしも一対一に対応するものではない。なぜならば、欠陥の種類は異なっても（すなわち、欠陥検査11、12、13を通じて得られた欠陥写真は互いに異なっても）、このような欠陥により現れるアナログ特性は同一であるからである。例えば、1つのノードと他の1つのノードとの間にブリッジが発生しようとすれば、基板レベルでブリッジが発生するか、配線レベルでブリッジが発生しうる。ところで、基板レベル及び配線レベルのうち、どちらのレベルでブリッジが発生しても、このようなブリッジを反映した回路は、同一であり、ブリッジによるアナログ特性カーブも同一であり得る。

**【0034】**

30

構築されたデータベースを例として示せば、表2のようである。不良ビットのアナログ特性と相関関係のある欠陥の種類が様々である場合には、相関関係のある全ての欠陥を保存するが、保存する各欠陥の発生頻度も同時に保存できる。例えば、ケースA（ストレージノードとワードラインとの間のリーケージ）の場合、アナログ特性と相関関係のある欠陥が3種（A1、A2、A3）であり、各欠陥の発生頻度は、100回、25回、10回であるということを保存して置くことができる。

**【0035】**

表2で不良モードはケースA（ストレージノードとワードラインとの間のリーケージ）、ケースB（電源電圧（Vcc）とストレージノードとの間のリーケージ）、ケースC（ストレージノードと接地電圧（Vss）との間のリーケージ）のみを記述しているが、これは例示的なものであり、本発明はこれに限定されるものではない。また、表2で、“-”表示は、イメージが開示されていることを表す。

40

**【0036】**

【表2】

| ケース | 不良モード                       | アナログ特性 | 欠陥種類 | 欠陥写真 | 欠陥頻度 |

|-----|-----------------------------|--------|------|------|------|

| A   | ストレージノードとワードラインとの間のリーケージ    | —      | A 1  | —    | 100  |

|     |                             |        | A 2  | —    | 25   |

|     |                             |        | A 3  | —    | 10   |

| B   | 電源電圧(Vcc)とストレージノードとの間のリーケージ | —      | B 1  | —    | 200  |

|     |                             |        | B 2  | —    | 150  |

| C   | ストレージノードと接地電圧(Vss)との間のリーケージ | —      | C 1  | —    | 20   |

|     |                             |        | C 2  | —    | 15   |

10

## 【0037】

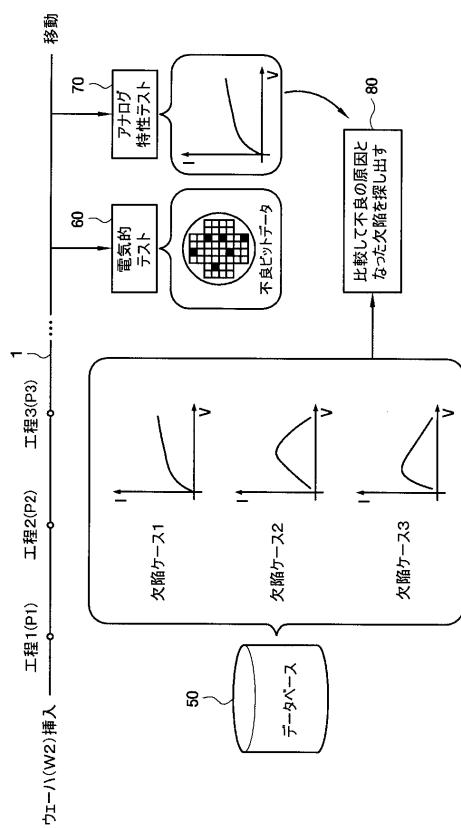

図2に基づき、図1の過程を通じて作られたデータベースを用いて不良の原因となった欠陥を探し出す方法を説明する。

20

## 【0038】

製造ライン1にウエハW2が挿入されれば、工程1 P1、工程2 P2、工程3 P3などの順番で順次に進行し、このような工程を通じてウエハW2内には、半導体集積回路装置のチップが多数個同時に形成される。ところで、図2のように不良の原因となった欠陥を探し出す方法では、各工程1 P1、工程2 P2、工程3 P3が進行する度には、欠陥検査11、12、13は実施しない。

## 【0039】

次いで、製造工程が完了した後で、電気的テストを実施してウエハW2内の不良ビットを探し出す(60)。

30

## 【0040】

次いで、ウエハW2内の不良ビットに対してアナログ特性を測定する(70)。ここで、アナログ特性は、表1のバイアシング条件下で測定された電流カーブである。

## 【0041】

次いで、測定されたアナログ特性とデータベースに保存されたアナログ特性とを比較して不良の原因となった欠陥が何かを判断する(80)。すなわち、データベース50に保存された多数のアナログ特性のうち、測定されたアナログ特性と類似した1つ以上のアナログ特性を分類して提供しうる。具体的に、測定されたアナログ特性カーブとデータベースに保存されたアナログ特性カーブとの間の相関係数を算出し、相関係数の大きさが基準値(例えば、0.9)以上となるデータベースに保存されたアナログ特性カーブを探し出す。このように類似した1つ以上のアナログ特性カーブを分類して提供するが、各アナログ特性カーブと共に保存されている1つ以上の欠陥と共に提供する。この際、1つ以上の欠陥それぞれと共に保存されている発生頻度も共に提供しうる。

40

## 【0042】

測定されたアナログ特性と類似した1つ以上のアナログ特性と欠陥が提供される形態は、例えば、表3のようである。また、表3で、“-”表示は、イメージが開示されていることを示す。

## 【0043】

表3で、測定されたアナログ特性と類似したアナログ特性が類似性の高い順に提供されている。すなわち、測定されたアナログ特性と最も類似したアナログ特性を有するケース

50

は、ケース A であり、それより類似していないアナログ特性を有するケースは、ケース G 、ケース K である。各ケースに対して欠陥種類及び欠陥頻度も共に提供するために、測定されたアナログ特性は、欠陥 A 1 から誘発される可能性が最も高いということを容易に類推しうる。

**【 0 0 4 4 】**

【表 3】

| 測定された<br>アナログ特性 | 順<br>序 | 類似した<br>アナログ特性 | ケース | 欠陥種類 | 欠陥写真 | 欠陥頻度  |

|-----------------|--------|----------------|-----|------|------|-------|

| —               | 1      | —              | A   | A 1  | —    | 1 0 0 |

|                 |        |                |     | A 2  | —    | 2 5   |

|                 |        |                |     | A 3  | —    | 1 0   |

|                 | 2      | —              | G   | G 1  | —    | 1 0   |

|                 |        |                |     | G 2  | —    | 8     |

|                 | 3      | —              | K   | K 1  | —    | 7 0   |

|                 |        |                |     | K 2  | —    | 1 5   |

|                 |        |                |     | K 3  | —    | 1 4   |

10

20

30

**【 0 0 4 5 】**

本発明の一実施形態では、欠陥とアナログ特性とをデータベース化して不良分析を行うために、製造工程中には、欠陥検査を行わなくても良く、測定されたアナログ特性と最も高い相関関係のある欠陥を容易に探し出せる。したがって、本発明は、従来に比べてさらに迅速で正確に不良分析を行うことができる。

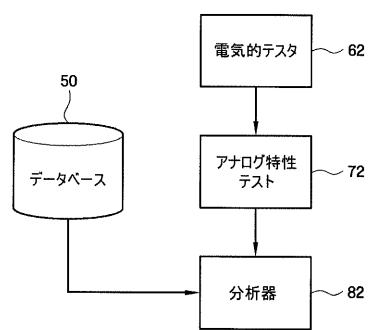

**【 0 0 4 6 】**

図 7 は、本発明の一実施形態による半導体集積回路装置の不良分析システムを説明するためのブロック図である。図 7 は、図 2 の不良分析方法を具現するための一例として提示されるものであり、本発明の権利範囲はこれに限定されるものではない。

**【 0 0 4 7 】**

図 7 を参照すれば、本発明の一実施形態による半導体集積回路装置の不良分析システムは、データベース 5 0 、電気的テスタ 6 2 、アナログ特性テスタ 7 2 、分析器 8 2 を備える。

40

**【 0 0 4 8 】**

データベース 5 0 は、相関関係のある欠陥と、不良ビットのアナログ特性とを保存する。不良ビットのアナログ特性と相関関係のある欠陥の種類が様々である場合には、データベース 5 0 には、相関関係のあるあらゆる欠陥を保存するが、保存する各欠陥の発生頻度も同時に保存して置くことができる。データベース 5 0 に保存されるデータは、前述した表 2 と同じであり得る。

**【 0 0 4 9 】**

電気的テスタ 6 2 は、製造ラインを経て製造されたチップ内のメモリセルの電気的特性を測定して不良ビットを探し出す。電気的テスタ 6 2 は、メモリセル内にデータを書き込み、メモリセルからデータを再び読み出し、読み出しデータと書き込みデータとが異なる場合には

50

、このようなメモリセルを不良ビットと定義する方式を使用しうる。

#### 【0050】

アナログ特性テスタ72は、ウエハ内の不良ビットのアナログ特性を測定する。アナログ特性テスタ72は、ビットがSRAMセルである場合には、前述した表1のバイアシング条件下で流れる電流の大きさを測定しうる。

#### 【0051】

分析器82は、測定されたアナログ特性と、データベース50に保存されたアナログ特性とを比較して不良の原因となる欠陥を探し出す。分析器82は、データベース50に保存された多数のアナログ特性のうち、電気的テスタ62により測定されたアナログ特性と類似した1つ以上のアナログ特性を分類して提供しうる。類似した1つ以上のアナログ特性を分類して提供するが、各アナログ特性と共に保存されている1つ以上の欠陥を共に提供する。この際、1つ以上の欠陥のそれぞれと共に保存されている発生頻度も共に提供しうる。測定されたアナログ特性と類似した1つ以上のアナログ特性と欠陥とが提供される形態は、例えば、表3のようであり得る。10

#### 【0052】

一方、図面では、別途に表示していないが、データベース50を作る過程では、ウエハ(図1のW1参照)内の欠陥を探し出す欠陥検査器がさらに必要である。データベース50を作る過程のうち、電気的テスタ62は、ウエハW1内の不良ビットを探し出し、アナログ特性テスタ72は、探し出した不良ビットのアナログ特性を測定し、分析器82は、ウエハW1内の欠陥とアナログ特性との間に相関関係があるかを検証し、相関関係があると検証された欠陥と、不良ビットのアナログ特性とをデータベースに保存させる。20

#### 【0053】

以上、添付図を参照して本発明の実施例を説明したが、本発明が属する技術分野で当業者ならば本発明がその技術的思想や必須特徴を変更せずとも他の具体的な形に実施されうるということが理解できるであろう。したがって、前述した実施例は全ての面で例示的なものであって、限定的なものではないと理解しなければならない。

#### 【産業上の利用可能性】

#### 【0054】

本発明は、半導体集積回路装置の不良分析関連の技術分野に好適に適用されうる。

#### 【図面の簡単な説明】

#### 【0055】

【図1】本発明の一実施形態による半導体集積回路装置の不良分析方法を説明するための図である。

【図2】本発明の一実施形態による半導体集積回路装置の不良分析方法を説明するための図である。

【図3】欠陥の位置と不良ビットの位置とをマッチさせる方法を説明するための図である。

#### 【図4】SRAMセルの回路図である。

#### 【図5】欠陥が発生したSRAMセルをモデリングした回路図である。

【図6】欠陥が発生したSRAMセルをシミュレーションして得たアナログ特性と、アナログ特性テストを通じて得たアナログ特性とを同時に示す図である。40

【図7】本発明の一実施形態による半導体集積回路装置の不良分析システムを説明するためのプロック図である。

#### 【符号の説明】

#### 【0056】

11、12、13 欠陥検査

20 電気的テスト

30 アナログ特性テスト

40 検証

50 データベース

10

20

30

40

50

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

---

フロントページの続き

審査官 堀江 義隆

(56)参考文献 特開平09-033604(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/66

G01R 31/28