(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7149164号**

**(P7149164)**

(45)発行日 令和4年10月6日(2022.10.6)

(24)登録日 令和4年9月28日(2022.9.28)

(51)国際特許分類

|        |                 |     |        |       |         |

|--------|-----------------|-----|--------|-------|---------|

| G 09 F | 9/302 (2006.01) | F I | G 09 F | 9/302 | C       |

| G 09 F | 9/33 (2006.01)  |     | G 09 F | 9/33  |         |

| G 09 G | 3/30 (2006.01)  |     | G 09 G | 3/30  | J       |

| G 09 G | 3/32 (2016.01)  |     | G 09 G | 3/32  | A       |

| G 09 G | 3/20 (2006.01)  |     | G 09 G | 3/20  | 6 4 2 L |

請求項の数 12 (全33頁) 最終頁に続く

(21)出願番号 特願2018-207672(P2018-207672)

(22)出願日 平成30年11月2日(2018.11.2)

(65)公開番号 特開2020-71456(P2020-71456A)

(43)公開日 令和2年5月7日(2020.5.7)

審査請求日 令和3年11月1日(2021.11.1)

(73)特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74)代理人 110002147弁理士法人酒井国際特許事務所

池田 雅延

東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

前出 優次

(72)発明者 東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

金谷 康弘

東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内

審査官 新井 重雄

最終頁に続く

(54)【発明の名称】 表示装置

**(57)【特許請求の範囲】****【請求項1】**

基板と、

前記基板に設けられた複数の画素と、を有し、

複数の前記画素の各々は、赤色発光素子と第1緑色発光素子とを含み、

赤色を表示させる入力信号に基づいて前記第1緑色発光素子が前記赤色発光素子と同時に点灯する時、前記第1緑色発光素子の発光強度は、前記赤色発光素子の発光強度よりも小さく、かつ、前記第1緑色発光素子の光のスペクトルの半値幅は、前記赤色発光素子の光のスペクトルの半値幅よりも大きい

表示装置。

10

**【請求項2】**

複数の前記画素の各々は、さらに、第2緑色発光素子を有し、

前記第2緑色発光素子の発光強度は、前記第1緑色発光素子の発光強度よりも大きい

請求項1に記載の表示装置。

**【請求項3】**

前記第1緑色発光素子の光のスペクトルの極大発光波長は、前記第2緑色発光素子の光のスペクトルの極大発光波長よりも長く、前記赤色発光素子の光のスペクトルの極大発光波長よりも短い

請求項2に記載の表示装置。

**【請求項4】**

20

複数の前記画素の各々は、さらに、青色発光素子を有し、

前記赤色発光素子と前記第1緑色発光素子とは、第1方向に並び、

前記赤色発光素子と、前記第2緑色発光素子又は前記青色発光素子の一方とは、前記第1方向と交差する第2方向に並ぶ

請求項2に記載の表示装置。

**【請求項5】**

複数の前記画素の各々は、さらに、青色発光素子を有し、

前記赤色発光素子と、前記第2緑色発光素子又は前記青色発光素子の一方とは、第1方向に並び、

前記赤色発光素子と、前記第2緑色発光素子又は前記青色発光素子の他方とは、前記第1方向と交差する第2方向に並ぶ

請求項2に記載の表示装置。

**【請求項6】**

前記画素の入力階調値が第1しきい値以下の場合に前記赤色発光素子が点灯し、前記第1緑色発光素子が点灯せず、

前記画素の入力階調値が前記第1しきい値よりも大きく、且つ、前記第1しきい値よりも大きい第2しきい値よりも小さい場合に前記赤色発光素子及び前記第1緑色発光素子が点灯する

請求項1に記載の表示装置。

**【請求項7】**

前記画素の入力階調値が前記第2しきい値以上の場合に前記赤色発光素子が点灯し、前記第1緑色発光素子が点灯しない、

請求項6に記載の表示装置。

**【請求項8】**

複数の前記画素の各々は、第1画素と、前記第1画素に隣接する第2画素を含み、

前記第1画素の入力階調値に基づいて、前記第1画素の前記第1緑色発光素子の第1階調値と、前記第2画素の前記第1緑色発光素子の第2階調値とを演算し、前記第1画素の前記第1緑色発光素子と前記第2画素の前記第1緑色発光素子とが点灯され、

前記第1画素の前記入力階調値に基づいて点灯される前記第1画素の前記第1緑色発光素子に供給される駆動電流がしきい値電流よりも大きい場合に、前記第1画素の前記第1緑色発光素子が前記第1階調値より低い第1出力階調値で点灯し、前記第2画素の前記第1緑色発光素子が前記第2階調値より高い第2出力階調値で点灯する、

請求項1に記載の表示装置。

**【請求項9】**

前記第2出力階調値は、前記第2階調値と第3階調値との和であり、

前記第3階調値は、前記第1階調値と前記第1出力階調値との差である、

請求項8に記載の表示装置。

**【請求項10】**

前記赤色発光素子の発光層は、ユウロピウム(Eu)が添加された窒化ガリウム(GaN)を含む

請求項1に記載の表示装置。

**【請求項11】**

赤色を表示させる第1入力信号に基づいて発光する第1赤色発光素子及び第1緑色発光素子を含む第1画素と、

前記第1画素に隣接し、赤色を表示させる第2入力信号に基づいて発光する第2赤色発光素子及び第2緑色発光素子を含む第2画素と、

信号処理回路と

を有し、

前記第1入力信号は、赤色の入力階調値を含み、

前記第2緑色発光素子は、前記第1入力信号に基づいて発光することが可能であり、

10

20

30

40

50

前記第1入力信号に基づいて前記第2緑色発光素子が発光する時、

前記信号処理回路は、前記入力階調値に基づいて、前記第1緑色発光素子の第1階調値と、前記第2緑色発光素子の第2階調値とを出力し、

前記第1緑色発光素子に供給される、前記第1階調値に基づく駆動電流が、しきい値電流よりも大きい時、

前記第1階調値より低い第3階調値で、前記第1緑色発光素子が点灯し、

前記第2階調値より高い第4階調値で、前記第2緑色発光素子が点灯する、表示装置。

### 【請求項12】

前記第4階調値は、前記第2階調値と第5階調値との和であり、

10

前記第5階調値は、前記第1階調値と前記第3階調値との差である、

請求項11に記載の表示装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、表示装置に関する。

#### 【背景技術】

#### 【0002】

表示素子として無機発光ダイオード（マイクロLED（micro LED））を用いた表示装置が知られている。このような表示装置では、表示する色ごとに異なる種類のLEDが用いられる。特許文献1に記載されている赤色LEDは、発光層として窒化ガリウム（GaN）の多重量子井戸構造が適用されている。また、特許文献2に記載されている赤色LEDには、発光層として窒化ガリウム（GaN）にヨウロピウム（Eu）が添加された材料が用いられている。

20

#### 【先行技術文献】

#### 【特許文献】

#### 【0003】

【文献】米国特許出願公開第2018/0097033号明細書

特許第5388041号公報

30

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

特許文献1の赤色LEDは、青色LEDや緑色LEDに比べて発光効率が低い。このため、赤色LEDの駆動電流を大きくする必要があり、消費電力が増大する可能性がある。また、特許文献2の赤色LEDでは、光のスペクトルの半値幅が、青色LEDや緑色LEDの光のスペクトルの半値幅に比べて小さい。このため、赤色のみが鮮やかに表示され、良好に画像を表示することが困難となる可能性がある。

#### 【0005】

本発明は、良好に画像を表示することができる表示装置を提供することを目的とする。

#### 【課題を解決するための手段】

40

#### 【0006】

本発明の一態様の表示装置は、基板と、前記基板に設けられた複数の画素と、複数の前記画素の各々に設けられる複数の赤色発光素子と複数の第1緑色発光素子と、を有し、前記第1緑色発光素子は、前記赤色発光素子と同時に点灯し、前記第1緑色発光素子の発光強度は、前記赤色発光素子の発光強度よりも小さく、かつ、前記第1緑色発光素子の光のスペクトルの半値幅は、前記赤色発光素子の光のスペクトルの半値幅よりも大きい。

#### 【図面の簡単な説明】

#### 【0007】

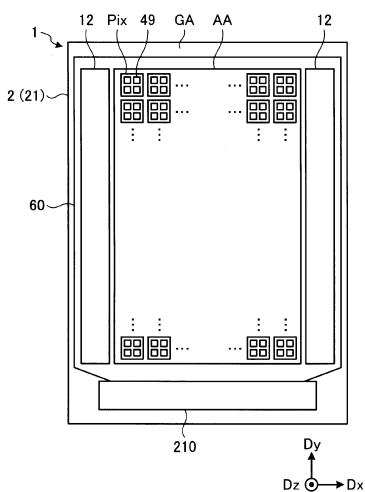

【図1】図1は、実施形態に係る表示装置を模式的に示す平面図である。

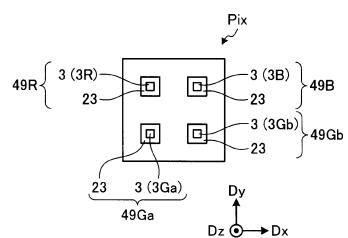

【図2】図2は、複数の画素を示す平面図である。

50

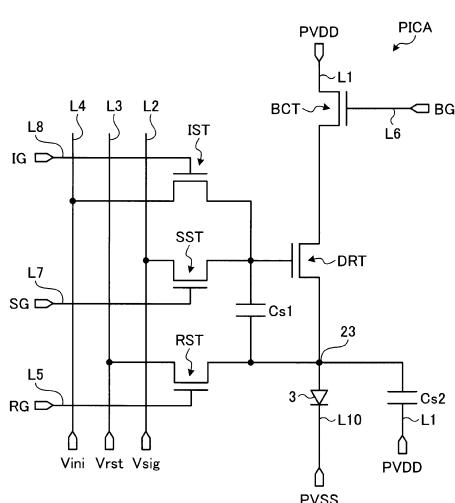

【図 3】図 3 は、画素回路を示す回路図である。

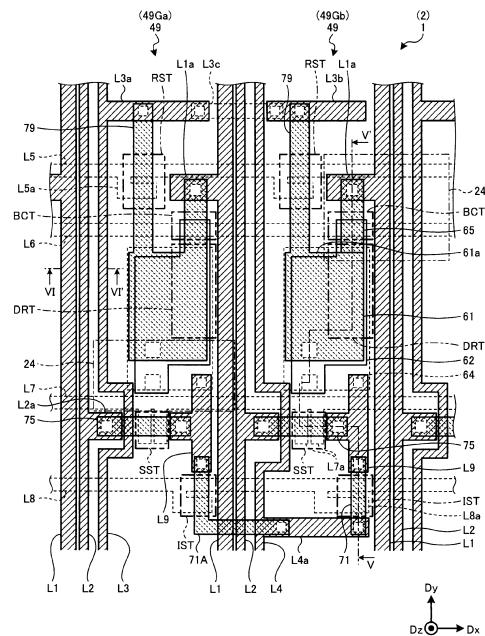

【図 4】図 4 は、実施形態に係る表示装置の、2つの画素を拡大して示す平面図である。

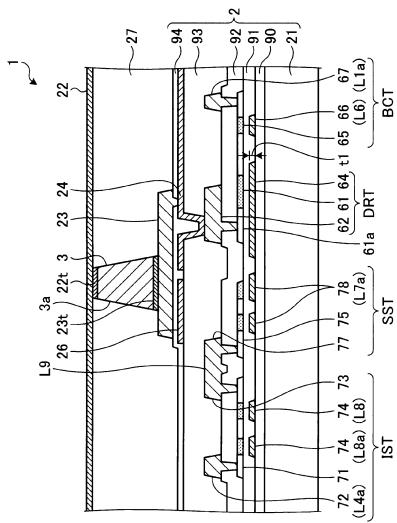

【図 5】図 5 は、図 4 の V - V' 線に沿う断面図である。

【図 6】図 6 は、図 4 の VI - VI' 線に沿う断面図である。

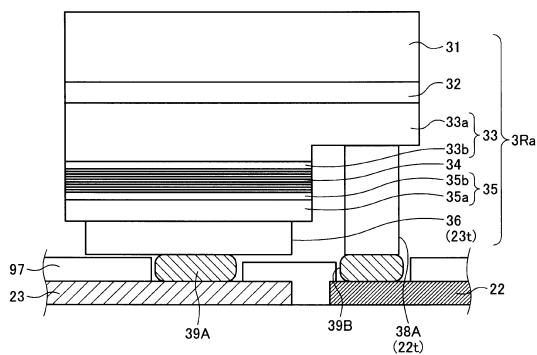

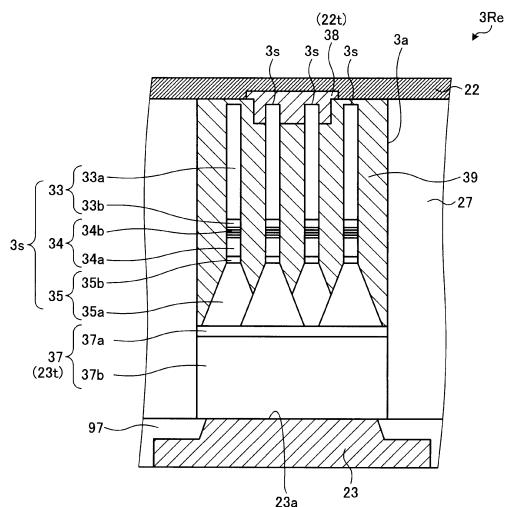

【図 7】図 7 は、実施形態に係る赤色発光素子を示す断面図である。

【図 8】図 8 は、赤色発光素子及び第 1 緑色発光素子の発光強度と波長との関係を模式的に示すグラフである。

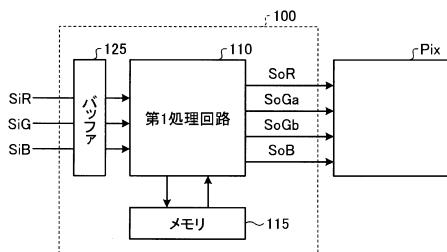

【図 9】図 9 は、信号処理回路の構成を模式的に示すブロック図である。

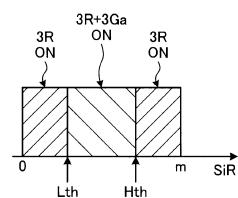

【図 10】図 10 は、入力階調値と、駆動される発光素子との関係を説明するための説明図である。 10

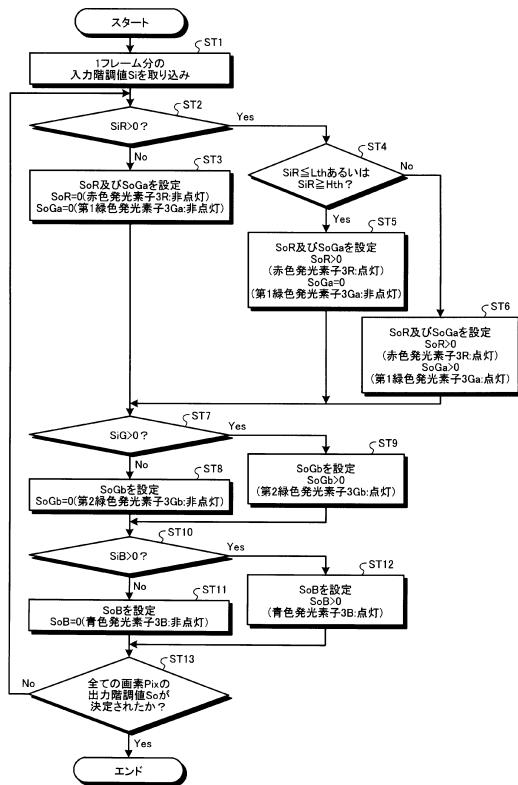

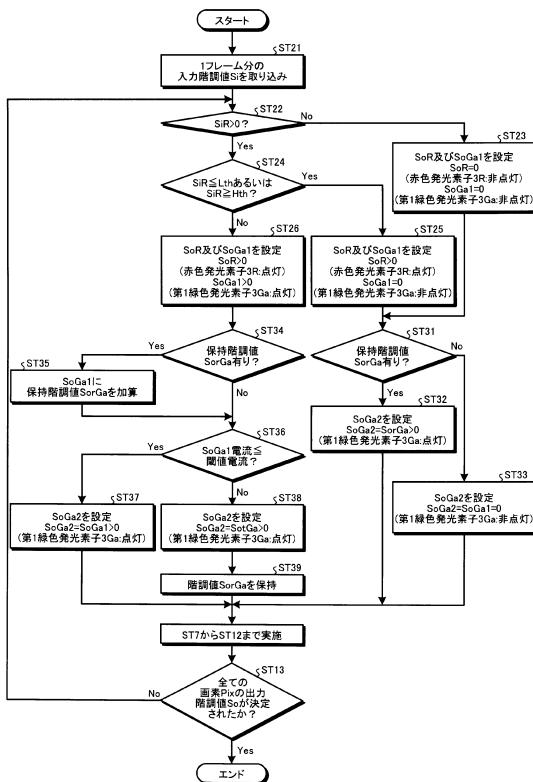

【図 11】図 11 は、第 1 変形例に係る各発光素子の出力階調値の設定方法を説明するためのフローチャートである。

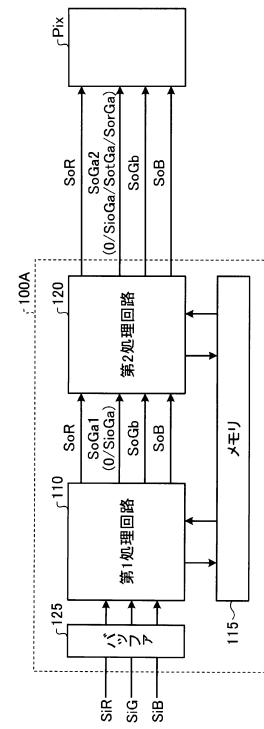

【図 12】図 12 は、第 2 変形例に係る信号処理回路の構成を模式的に示すブロック図である。 20

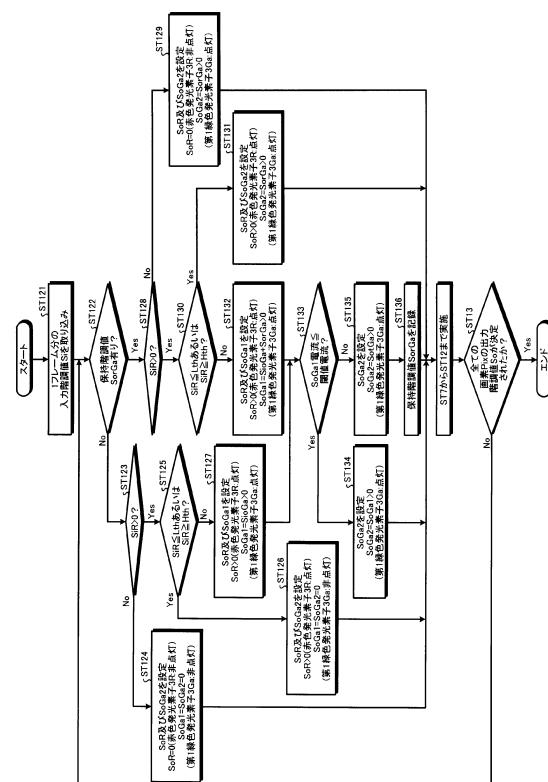

【図 13】図 13 は、第 2 変形例に係る各発光素子の出力階調値の設定方法を説明するためのフローチャートである。

【図 14】図 14 は、第 3 変形例に係る各発光素子の出力階調値の設定方法を説明するためのフローチャートである。

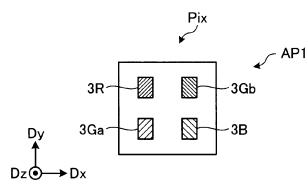

【図 15 A】図 15 A は、第 4 変形例に係る 1 つの画素群における各発光素子の第 1 配置パターンを示す平面図である。 20

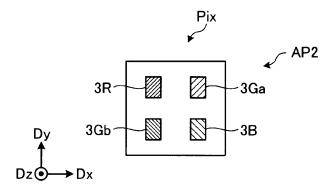

【図 15 B】図 15 B は、1 つの画素群における各発光素子の第 2 配置パターンを示す平面図である。

【図 15 C】図 15 C は、1 つの画素群における各発光素子の第 3 配置パターンを示す平面図である。

【図 16 A】図 16 A は、第 5 変形例に係る 2 つの画素群における各発光素子の第 4 配置パターンを示す平面図である。 30

【図 16 B】図 16 B は、2 つの画素群における各発光素子の第 5 配置パターンを示す平面図である。

【図 16 C】図 16 C は、2 つの画素群における各発光素子の第 6 配置パターンを示す平面図である。

【図 17】図 17 は、第 6 変形例に係る赤色発光素子を示す断面図である。

【図 18】図 18 は、第 7 変形例に係る赤色発光素子を示す断面図である。

【図 19】図 19 は、第 8 変形例に係る赤色発光素子を示す断面図である。

【図 20】図 20 は、第 9 変形例に係る赤色発光素子を示す断面図である。

【図 21】図 21 は、第 10 変形例に係る赤色発光素子を示す断面図である。

#### 【発明を実施するための形態】

##### 【0008】

本発明を実施するための形態（実施形態）につき、図面を参照しつつ詳細に説明する。以下の実施形態に記載した内容により本発明が限定されるものではない。また、以下に記載した構成要素には、当業者が容易に想定できるもの、実質的に同一のものが含まれる。さらに、以下に記載した構成要素は適宜組み合わせることが可能である。なお、開示はあくまで一例にすぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は説明をより明確にするため、実際の態様に比べ、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同様の要素には、同一の符号を付して、詳細な説明を適宜省略することがある。 40

##### 【0009】

##### (実施形態)

図 1 は、実施形態に係る表示装置を模式的に示す平面図である。図 1 に示すように、表

示装置 1 は、アレイ基板 2 と、画素  $P_{i \times}$  (画素群) と、駆動回路 1 2 と、駆動 I C (Integrated Circuit) 2 1 0 と、カソード配線 6 0 と、を含む。アレイ基板 2 は、各画素  $P_{i \times}$  を駆動するための駆動回路基板であり、バックプレーン又はアクティブマトリクス基板とも呼ばれる。アレイ基板 2 は、基板 2 1 、複数のトランジスタ、複数の容量及び各種配線等を有する。

#### 【 0 0 1 0 】

図 1 に示すように、表示装置 1 は、表示領域 A A と、周辺領域 G A とを有する。表示領域 A A は、複数の画素  $P_{i \times}$  と重なって配置され、画像を表示する領域である。周辺領域 G A は、複数の画素  $P_{i \times}$  と重ならない領域であり、表示領域 A A の外側に配置される。

#### 【 0 0 1 1 】

複数の画素  $P_{i \times}$  は、表示領域 A A において、第 1 方向 D x 及び第 2 方向 D y に配列される。なお、第 1 方向 D x 及び第 2 方向 D y は、基板 2 1 の表面に対して平行な方向である。第 1 方向 D x は、第 2 方向 D y と直交する。ただし、第 1 方向 D x は、第 2 方向 D y と直交しないで交差してもよい。第 3 方向 D z は、第 1 方向 D x 及び第 2 方向 D y と直交する方向である。第 3 方向 D z は、例えば、基板 2 1 の法線方向に対応する。なお、以下、平面視とは、第 3 方向 D z から見た場合の位置関係を示す。

#### 【 0 0 1 2 】

駆動回路 1 2 は、駆動 I C 2 1 0 からの各種制御信号に基づいて複数のゲート線 (例えば、リセット制御信号線 L 5 、出力制御信号線 L 6 、画素制御信号線 L 7 、初期化制御信号線 L 8 (図 3 参照)) を駆動する回路である。駆動回路 1 2 は、複数のゲート線を順次又は同時に選択し、選択されたゲート線にゲート駆動信号 (例えば、画素制御信号 S G ) を供給する。これにより、駆動回路 1 2 は、ゲート線に接続された複数の画素  $P_{i \times}$  を選択する。

#### 【 0 0 1 3 】

駆動 I C 2 1 0 は、表示装置 1 の表示を制御する回路である。駆動 I C 2 1 0 は、基板 2 1 の周辺領域 G A に C O G (Chip On Glass) として実装される。これに限定されず、駆動 I C 2 1 0 は、基板 2 1 の周辺領域 G A に接続された配線基板の上に C O F (Chip On Film) として実装されてもよい。配線基板は、例えば、フレキシブルプリント基板やリジット基板である。

#### 【 0 0 1 4 】

カソード配線 6 0 は、基板 2 1 の周辺領域 G A に設けられる。カソード配線 6 0 は、表示領域 A A の複数の画素  $P_{i \times}$  及び周辺領域 G A の駆動回路 1 2 を囲んで設けられる。言い換えると、カソード配線 6 0 は、基板 1 0 上に形成された周辺回路と基板 2 1 の外縁との間に配置される。複数の発光素子 3 のカソード (カソード端子 2 2 t (図 5 参照)) は、共通のカソード配線 6 0 に接続され、固定電位 (例えば、グランド電位) が供給される。より具体的には、発光素子 3 のカソード端子 2 2 t (図 5 参照) は、カソード電極 2 2 を介して、カソード配線 6 0 に接続される。なお、カソード配線 6 0 は、基板 1 0 の 3 辺に沿って連続して形成される 1 つの配線に限らず、基板 2 1 上において、いずれかの辺においてスリットを有する 2 つの部分配線からなってもよく、基板 2 1 の少なくとも 1 つの辺に沿って配置される配線であれば良い。

#### 【 0 0 1 5 】

図 2 は、複数の画素を示す平面図である。図 2 に示すように、1 つの画素  $P_{i \times}$  は、複数の画素 4 9 を含む。例えば、画素  $P_{i \times}$  は、第 1 画素 4 9 R と、第 2 画素 4 9 G a と、第 3 画素 4 9 G b と、第 4 画素 4 9 B とを有する。第 1 画素 4 9 R は、第 1 色としての原色の赤色を表示する。第 2 画素 4 9 G a は、第 2 色としての原色の第 1 緑色を表示する。第 3 画素 4 9 G b は、第 2 色としての原色の第 2 緑色を表示する。第 4 画素 4 9 B は、第 3 色としての原色の青色を表示する。第 1 緑色と第 2 緑色は、いずれも緑色の光であるが、発光強度及び光のスペクトルの極大発光波長の少なくともいずれかが異なる。

#### 【 0 0 1 6 】

図 2 に示すように、1 つの画素  $P_{i \times}$  において、第 1 画素 4 9 R と第 2 画素 4 9 G a は

10

20

30

40

50

第2方向Dyで並ぶ。第1画素49Rと第4画素49Bは第1方向Dxで並ぶ。第2画素49Gaと第3画素49Gbは第1方向Dxで並ぶ。また、第3画素49Gbと第4画素49Bは第2方向Dyで並ぶ。なお、第1色、第2色、第3色は、それぞれ赤色、緑色、青色に限られず、補色などの任意の色を選択することができる。以下において、第1画素49R、第2画素49Ga、第3画素49Gb及び第4画素49Bをそれぞれ区別する必要がない場合、画素49という。

#### 【0017】

画素49は、それぞれ発光素子3と、アノード電極23とを有する。具体的には、第1画素49R、第2画素49Ga、第3画素49Gb及び第4画素49Bは、それぞれ、赤色発光素子3R、第1緑色発光素子3Ga、第2緑色発光素子3Gb及び青色発光素子3Bを有する。つまり、赤色発光素子3Rと第1緑色発光素子3Gaは第2方向Dyで並ぶ。赤色発光素子3Rと青色発光素子3Bは第1方向Dxで並ぶ。第1緑色発光素子3Gaと第2緑色発光素子3Gbは第1方向Dxで並ぶ。また、第2緑色発光素子3Gbと青色発光素子3Bは第2方向Dyで並ぶ。赤色発光素子3Rは赤色の光を出射する。第1緑色発光素子3Gaは第1緑色の光を出射する。第2緑色発光素子3Gbは、第2緑色の光を出射する。青色発光素子3Bは、青色の光を出射する。なお、以下において、赤色発光素子3R、第1緑色発光素子3Ga、第2緑色発光素子3Gb及び青色発光素子3Bをそれぞれ区別する必要がない場合、発光素子3という。

10

#### 【0018】

発光素子3は、平面視で、3μm以上、300μm以下程度の大きさを有する無機発光ダイオード(LED:Light Emitting Diode)チップであり、マイクロLED(micro LED)又はミニLED(mini LED)と呼ばれる。各画素にマイクロLEDを備える表示装置1は、マイクロLED表示装置とも呼ばれる。なお、マイクロLEDのマイクロは、発光素子3の大きさを限定するものではない。

20

#### 【0019】

なお、複数の発光素子3は、4色以上の異なる光を出射してもよい。なお、第1色、第2色、第3色は、それぞれ赤色、緑色、青色に限られず、補色などの任意の色を選択することができる。また、1つの画素Pi xに配置される画素49の数は4に限らず、5以上であってもよく、5以上の画素49には、それぞれ異なる色が対応づけられていてよい。さらに、画素49の配列は、これに限らず、第1画素49R、第2画素49Ga、第3画素49Gb及び第4画素49Bが第1方向Dx及び第2方向Dyのいずれか一方で並ぶように配列されていてよい。

30

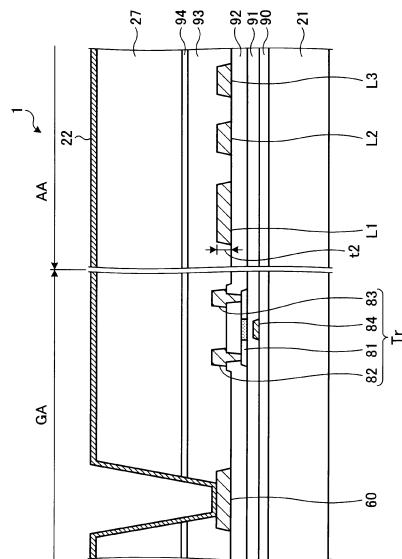

#### 【0020】

図3は、画素回路を示す回路図である。図3は、1つの画素49に設けられた画素回路PICAを示しており、画素回路PICAは複数の画素49のそれぞれに設けられている。図3に示すように、画素回路PICAは、発光素子3と、5つのトランジスタと、2つの容量とを含む。具体的には、画素回路PICAは、駆動トランジスタDRT、出力トランジスタBCT、初期化トランジスタIST、画素選択トランジスタSST及びリセットトランジスタRSTを含む。駆動トランジスタDRT、出力トランジスタBCT、初期化トランジスタIST、画素選択トランジスタSST及びリセットトランジスタRSTは、それぞれn型TFT(Thin Film Transistor)で構成される。また、画素回路PICAは、第1容量Cs1及び第2容量Cs2を含む。

40

#### 【0021】

発光素子3のカソード(カソード端子22t)は、カソード電源線L10に接続される。また、発光素子3のアノード(アノード端子23t)は、駆動トランジスタDRT及び出力トランジスタBCTを介してアノード電源線L1に接続される。アノード電源線L1には、アノード電源電位PVDDが供給される。カソード電源線L10には、カソード配線60及びカソード電極22に対応しカソード電源電位PVSSが供給される。アノード電源電位PVDDは、カソード電源電位PVSSよりも高い電位である。

#### 【0022】

50

アノード電源線 L 1 は、画素 4 9 に、駆動電位であるアノード電源電位 P V D D を供給する。具体的には、発光素子 3 には、理想的にはアノード電源電位 P V D D とカソード電源電位 P V S S との電位差 ( P V D D - P V S S ) により順方向電流 ( 駆動電流 ) が供給され発光する。つまり、アノード電源電位 P V D D は、カソード電源電位 P V S S に対し、発光素子 3 を発光させる電位差を有している。発光素子 3 のアノード端子 2 3 t はアノード電極 2 3 に接続され、アノード電極 2 3 とアノード電源線 L 1 との間に第 2 容量 C s 2 が接続される。

#### 【 0 0 2 3 】

駆動トランジスタ D R T のソース電極は、アノード電極 2 3 を介して発光素子 3 のアノード端子 2 3 t に接続され、ドレイン電極は、出力トランジスタ B C T のソース電極に接続される。駆動トランジスタ D R T のゲート電極は、第 1 容量 C s 1 、画素選択トランジスタ S S T のドレイン電極及び初期化トランジスタ I S T のドレイン電極に接続される。

10

#### 【 0 0 2 4 】

出力トランジスタ B C T のゲート電極は、出力制御信号線 L 6 に接続される。出力制御信号線 L 6 には、出力制御信号 B G が供給される。出力トランジスタ B C T のドレイン電極は、アノード電源線 L 1 に接続される。

#### 【 0 0 2 5 】

初期化トランジスタ I S T のソース電極は、初期化電源線 L 4 に接続される。初期化電源線 L 4 には、初期化電位 V i n i が供給される。初期化トランジスタ I S T のゲート電極は、初期化制御信号線 L 8 に接続される。初期化制御信号線 L 8 には、初期化制御信号 I G が供給される。すなわち、駆動トランジスタ D R T のゲート電極には、初期化トランジスタ I S T を介して初期化電源線 L 4 が接続される。

20

#### 【 0 0 2 6 】

画素選択トランジスタ S S T のソース電極は、映像信号線 L 2 に接続される。映像信号線 L 2 には、映像信号 V s i g が供給される。画素選択トランジスタ S S T のゲート電極には、画素制御信号線 L 7 が接続されている。画素制御信号線 L 7 には、画素制御信号 S G が供給される。

#### 【 0 0 2 7 】

リセットトランジスタ R S T のソース電極は、リセット電源線 L 3 に接続される。リセット電源線 L 3 には、リセット電源電位 V r s t が供給される。リセットトランジスタ R S T のゲート電極は、リセット制御信号線 L 5 が接続される。リセット制御信号線 L 5 には、リセット制御信号 R G が供給される。リセットトランジスタ R S T のドレイン電極は、アノード電極 2 3 ( 発光素子 3 のアノード端子 2 3 t ) 及び駆動トランジスタ D R T のソース電極に接続される。リセットトランジスタ R S T のリセット動作により、第 1 容量 C s 1 及び第 2 容量 C s 2 に保持された電圧がリセットされる。

30

#### 【 0 0 2 8 】

リセットトランジスタ R S T のドレイン電極と、駆動トランジスタ D R T のゲート電極との間に、第 1 容量 C s 1 が設けられる。画素回路 P I C A は、第 1 容量 C s 1 及び第 2 容量 C s 2 により、駆動トランジスタ D R T の寄生容量とリーク電流とによるゲート電圧の変動を抑制することができる。

40

#### 【 0 0 2 9 】

なお、以下の説明において、アノード電源線 L 1 及びカソード電源線 L 1 0 を単に電源線と表す場合がある。映像信号線 L 2 、リセット電源線 L 3 及び初期化電源線 L 4 を信号線と表す場合がある。リセット制御信号線 L 5 、出力制御信号線 L 6 、画素制御信号線 L 7 及び初期化制御信号線 L 8 をゲート線と表す場合がある。

#### 【 0 0 3 0 】

駆動トランジスタ D R T のゲート電極には、映像信号 V s i g ( または、階調信号 ) に応じた電位が供給される。つまり、駆動トランジスタ D R T は、出力トランジスタ B C T を介して供給されたアノード電源電位 P V D D に基づいて、映像信号 V s i g に応じた電流を発光素子 3 に供給する。このように、アノード電源線 L 1 に供給されたアノード電源

50

電位 P V D D は、駆動トランジスタ D R T 及び出力トランジスタ B C T によって降下するため、発光素子 3 のアノード端子 2 3 t には、アノード電源電位 P V D D よりも低い電位が供給される。

#### 【 0 0 3 1 】

第 2 容量 C s 2 の一方の電極には、アノード電源線 L 1 を介してアノード電源電位 P V D D が供給され、第 2 容量 C s 2 の他方の電極には、アノード電源電位 P V D D よりも低い電位が供給される。つまり、第 2 容量 C s 2 の一方の電極には、第 2 容量 C s 2 の他方の電極よりも高い電位が供給される。第 2 容量 C s 2 の一方の電極は、例えば、アノード電源線 L 1 であり、第 2 容量 C s 2 の他方の電極は、駆動トランジスタ D R T のソースに接続されたアノード電極 2 3 及びこれに接続されたアノード接続電極 2 4 である。

10

#### 【 0 0 3 2 】

表示装置 1 において、駆動回路 1 2 ( 図 1 参照 ) は、複数の画素行を、先頭行 ( 例えば、図 1 中の表示領域 A A において、最上部に位置する画素行 ) から順番に選択する。駆動 I C 2 1 0 は、選択された画素行の画素 4 9 に映像信号 V s i g ( 映像書き込み電位 ) を書き込み、発光素子 3 を発光させる。駆動 I C 2 1 0 は、1 水平走査期間ごとに、映像信号線 L 2 に映像信号 V s i g を供給し、リセット電源線 L 3 にリセット電源電位 V r s t を供給し、初期化電源線 L 4 に初期化電位 V i n i を供給する。表示装置 1 は、これらの動作が 1 フレームの画像ごとに繰り返される。

#### 【 0 0 3 3 】

次に、図 4 から図 6 を参照しつつ、各トランジスタ及び各配線の具体的な構成例について説明する。図 4 は、実施形態に係る表示装置の、2 つの画素を拡大して示す平面図である。

20

#### 【 0 0 3 4 】

図 4 は、第 1 方向 D x に隣り合う 2 つの画素 4 9 ( 例えば、第 2 画素 4 9 G a と第 3 画素 4 9 G b ) について示す。図 4 に示すように、アノード電源線 L 1 、映像信号線 L 2 、リセット電源線 L 3 及び初期化電源線 L 4 は、第 2 方向 D y に延出する。リセット制御信号線 L 5 、出力制御信号線 L 6 、画素制御信号線 L 7 、初期化制御信号線 L 8 は、第 1 方向 D x に延出し、平面視で、アノード電源線 L 1 、映像信号線 L 2 、リセット電源線 L 3 及び初期化電源線 L 4 とそれぞれ交差する。また、第 1 方向 D x に隣り合う 2 つのアノード電源線 L 1 の間に接続配線 L 9 が設けられている。接続配線 L 9 は、駆動トランジスタ D R T 、画素選択トランジスタ S S T 及び初期化トランジスタ I S T を接続する。

30

#### 【 0 0 3 5 】

図 4 では、各配線及び半導体層を区別するために、アノード電源線 L 1 、映像信号線 L 2 、リセット電源線 L 3 及び初期化電源線 L 4 に斜線を付している。リセット制御信号線 L 5 、出力制御信号線 L 6 、画素制御信号線 L 7 及び初期化制御信号線 L 8 を点線で示している。また、各半導体層 6 1 、6 5 、7 1 、7 5 、7 9 にも斜線を付している。アノード接続電極 2 4 は、2 点鎖線で示している。

#### 【 0 0 3 6 】

アノード電源線 L 1 、映像信号線 L 2 、リセット電源線 L 3 、初期化電源線 L 4 及び接続配線 L 9 は、各ゲート線 ( リセット制御信号線 L 5 、出力制御信号線 L 6 、画素制御信号線 L 7 、初期化制御信号線 L 8 ) と異なる層に設けられた金属層で形成されている。

40

#### 【 0 0 3 7 】

各種配線の材料として、チタン ( T i ) 、モリブデン ( M o ) 、タングステン ( W ) 、タンタル ( T a ) 、ニオブ ( N b ) 、インジウムスズ酸化物 ( I T O ) 、アルミニウム ( A l ) 、銀 ( A g ) 、A g 合金、銅 ( C u ) 、カーボンナノチューブ、グラファイト、グラフェン又はカーボンナノバッドが用いられる。ここで、アノード電源線 L 1 、映像信号線 L 2 、リセット電源線 L 3 、初期化電源線 L 4 及び接続配線 L 9 のシート抵抗値は、各ゲート線のシート抵抗値以下である。また、アノード電源線 L 1 のシート抵抗値は、各信号線 ( 映像信号線 L 2 、リセット電源線 L 3 、初期化電源線 L 4 ) 及び接続配線 L 9 のシート抵抗値以下である。例えば、アノード電源線 L 1 のシート抵抗値は、3 0 m / 以

50

上 1 2 0 m / 以下である。各信号線及び接続配線 L 9 のシート抵抗値は、1 2 0 m / 以上 3 0 0 m / 以下である。また、各ゲート線のシート抵抗値は、3 0 0 m / 以上 3 0 0 0 m / 以下である。これにより、表示装置 1 は、アノード電源線 L 1 に印加される駆動電圧の電圧降下を抑制し、表示性能の低下を抑制できる。

#### 【 0 0 3 8 】

なお、各種配線は、それぞれ、単層に限定されず、積層膜で構成されていてもよい。例えば、各電源線及び信号線は Ti / Al / Ti あるいは Mo / Al / Mo の積層構造であってもよく、Al の単層膜であってもよい。また、Ti、Al、Mo は合金でもよい。

#### 【 0 0 3 9 】

半導体層 6 1、6 5、7 1、7 5、7 9 は、例えば、アモルファスシリコン、微結晶酸化物半導体、アモルファス酸化物半導体、ポリシリコン、低温ポリシリコン（L T P S : Low Temperature Polycrystalline Silicon）又は窒化ガリウム（GaN）で構成される。酸化物半導体としては、IGZO、酸化亜鉛（ZnO）、ITZO が例示される。IGZO は、インジウムガリウム亜鉛酸化物である。ITZO は、インジウムスズ亜鉛酸化物である。半導体層 6 1、6 5、7 1、7 5、7 9 は、いずれも同じ材料、例えば、ポリシリコンで構成されていてもよい。

10

#### 【 0 0 4 0 】

図 4 に示すように、リセット電源線 L 3 及び初期化電源線 L 4 は、第 1 方向 D x に隣り合う 2 つの画素 4 9 で共有される。つまり、図 4 の左側に示す第 2 画素 4 9 G a では、初期化電源線 L 4 は設けられず、映像信号線 L 2 に沿ってリセット電源線 L 3 が設けられている。図 4 の右側に示す第 3 画素 4 9 G b では、リセット電源線 L 3 は設けられず、映像信号線 L 2 に沿って初期化電源線 L 4 が設けられている。これにより、各画素 4 9 にリセット電源線 L 3 及び初期化電源線 L 4 を設けた場合に比べて、配線の数を少なくして効率よく配線を配置することができる。

20

#### 【 0 0 4 1 】

駆動トランジスタ D R T は、半導体層 6 1、ソース電極 6 2 及びゲート電極 6 4 を有する。半導体層 6 1、ソース電極 6 2 及びゲート電極 6 4 は、平面視で、少なくとも一部が重なって配置され、第 1 方向 D x に隣り合う 2 つのアノード電源線 L 1 と、出力制御信号線 L 6 と、画素制御信号線 L 7 とで囲まれた領域に設けられる。半導体層 6 1 のうち、ゲート電極 6 4 と重なる領域の一部にチャネル領域が形成される。駆動トランジスタ D R T は、半導体層 6 1 と重なって 1 つのゲート電極 6 4 が設けられたシングルゲート構造である。

30

#### 【 0 0 4 2 】

半導体層 6 1 は、第 1 部分半導体層 6 1 a を有する。第 1 部分半導体層 6 1 a は、半導体層 6 1 と同層で、同じ半導体材料が用いられる。第 1 部分半導体層 6 1 a は、半導体層 6 1 から第 1 方向 D x に突出した部分である。第 1 部分半導体層 6 1 a の第 1 方向 D x の幅は、半導体層 6 1 のうち、出力トランジスタ B C T の半導体層 6 5 と接続される部分での第 1 方向 D x の幅よりも大きい。半導体層 6 1 は、第 1 部分半導体層 6 1 a を介してソース電極 6 2 と接続される。半導体層 6 1 及び第 1 部分半導体層 6 1 a は、第 1 絶縁膜 9 1（図 5 参照）及びゲート電極 6 4 と重なって設けられており、第 1 部分半導体層 6 1 a とゲート電極 6 4 との間に第 1 容量 C s 1 が形成される。なお、半導体層 6 1 と第 1 部分半導体層 6 1 a とは、それぞれ矩形状に形成されて接続部を介して電気的に接続されている。

40

#### 【 0 0 4 3 】

出力トランジスタ B C T は、半導体層 6 5 を有する。半導体層 6 5 は駆動トランジスタ D R T の半導体層 6 1 と接続されており、出力制御信号線 L 6 と平面視で交差する。半導体層 6 5 のうち、出力制御信号線 L 6 と重なる領域にチャネル領域が形成される。出力制御信号線 L 6 のうち半導体層 6 5 と重なる部分が、出力トランジスタ B C T のゲート電極 6 6 として機能する。半導体層 6 5 の一端側は、アノード電源線接続部 L 1 a と電気的に接続される。アノード電源線接続部 L 1 a は、アノード電源線 L 1 から第 1 方向 D x に分

50

岐された部分である。これにより、駆動トランジスタD R T及び出力トランジスタB C Tには、アノード電源線L 1からアノード電源電位P V D Dが供給される。

#### 【0044】

図4の右側に示す第3画素49G bでは、初期化トランジスタI S Tは、半導体層71を有する。図4の左側に示す第2画素49G aでは、初期化トランジスタI S Tは、半導体層71Aを有する。半導体層71、71Aは、それぞれ、初期化制御信号線L8及び分岐信号線L8aと平面視で交差する。半導体層71、71Aのうち、初期化制御信号線L8及び分岐信号線L8aと重なる領域にチャネル領域が形成される。分岐信号線L8aは、初期化制御信号線L8から分岐され、第1方向D xに延出する。初期化制御信号線L8及び分岐信号線L8aのうち半導体層71、71Aと重なる部分が、それぞれ初期化トランジスタI S Tのゲート電極74として機能する。つまり、初期化トランジスタI S Tは、半導体層71、71Aのそれぞれに重なって2つのゲート電極74が設けられたダブルゲート構造である。10

#### 【0045】

図4の右側に示す第3画素49G bでは、半導体層71は、第2方向D yに延出し、一端が接続配線L9に電気的に接続され、他端が初期化電源線接続部L4aに接続される。初期化電源線接続部L4aは、初期化電源線L4から第1方向D xに分岐された部分である。また、図4の左側に示す第2画素49G aでは、半導体層71Aは、第2方向D yに延出する部分と、第1方向D xに延出する部分とを有する。半導体層71Aのうち、第2方向D yに延出する部分の一端が接続配線L9に電気的に接続される。半導体層71Aのうち、第1方向D xに延出する部分は、平面視でアノード電源線L1及び映像信号線L2と交差して第3画素49G bまで延出し、初期化電源線接続部L4aに電気的に接続される。以上のような構成により、1つの初期化電源線L4は、2つの初期化トランジスタI S Tに電気的に接続されて、第1方向D xに隣り合う2つの画素49で共有される。20

#### 【0046】

画素選択トランジスタS S Tは、半導体層75を有する。半導体層75は、第1方向D xに延出し、2つの分岐信号線L7aと平面視で交差する。半導体層75のうち、2つの分岐信号線L7aと重なる領域にチャネル領域が形成される。2つの分岐信号線L7aは、画素制御信号線L7から第2方向D yに分岐された部分である。2つの分岐信号線L7aのうち半導体層75と重なる部分が、それぞれ画素選択トランジスタS S Tのゲート電極78として機能する。つまり、画素選択トランジスタS S Tは、半導体層75に重なって2つのゲート電極78が設けられたダブルゲート構造である。半導体層75の一端は、映像信号線接続部L2aに接続され、他端は接続配線L9に接続される。映像信号線接続部L2aは、映像信号線L2から第1方向D xに分岐された部分である。30

#### 【0047】

リセットトランジスタR S Tは、半導体層79を有する。半導体層79は、第2方向D yに延出し、リセット制御信号線L5及び分岐信号線L5aと平面視で交差する。半導体層79のうち、リセット制御信号線L5及び分岐信号線L5aと重なる領域にチャネル領域が形成される。分岐信号線L5aは、リセット制御信号線L5から分岐され、第1方向D xに延出する。リセット制御信号線L5及び分岐信号線L5aのうち、半導体層79と重なる部分が、それぞれリセットトランジスタR S Tのゲート電極として機能する。つまり、リセットトランジスタR S Tは、ダブルゲート構造である。40

#### 【0048】

リセット電源線L3には、第1方向D xに延出するリセット電源線接続部L3a、L3b及びブリッジ部L3cが接続されている。リセット電源線接続部L3a、L3bはリセット電源線L3と同層の金属層で形成され、ブリッジ部L3cは、リセット電源線接続部L3a、L3bと異なる層、例えば各種ゲート線と同層の金属層で形成される。リセット電源線接続部L3aは第2画素49G aに設けられ、リセット電源線接続部L3bは、第3画素49G bに設けられる。リセット電源線接続部L3aとリセット電源線接続部L3bとの間に、アノード電源線L1、映像信号線L2及び初期化電源線L4が設けられる。50

プリッジ部 L 3 c は、平面視でアノード電源線 L 1、映像信号線 L 2 及び初期化電源線 L 4 と交差して、リセット電源線接続部 L 3 a とリセット電源線接続部 L 3 b とを接続する。

#### 【 0 0 4 9 】

第 2 画素 4 9 G a において、半導体層 7 9 の一端はリセット電源線接続部 L 3 a に接続される。また、第 3 画素 4 9 G b において、半導体層 7 9 の一端はリセット電源線接続部 L 3 b に接続される。また、半導体層 7 9 の他端は、それぞれ駆動トランジスタ D R T の半導体層 6 1 に電気的に接続される。つまり、リセットトランジスタ R S T の半導体層 7 9 の他端は、半導体層 6 1、ソース電極 6 2 を介して発光素子 3 のアノード端子 2 3 t に電気的に接続される。以上のような構成により、1 つのリセット電源線 L 3 は、2 つのリセットトランジスタ R S T に電気的に接続されて、第 1 方向 D x に隣り合う 2 つの画素 4 9 で共有される。

#### 【 0 0 5 0 】

第 1 容量 C s 1 ( 図 3 参照 ) は、半導体層 6 1 ( 第 1 部分半導体層 6 1 a ) とゲート電極 6 4 との間に形成される。アノード接続電極 2 4 は、駆動トランジスタ D R T と電気的に接続され、少なくともアノード電源線 L 1 と重なって配置される。アノード接続電極 2 4 と、アノード電源線 L 1 及びアノード電源線 L 1 に接続された各種配線との間に第 2 容量 C s 2 ( 図 3 参照 ) が形成される。第 2 画素 4 9 G a で形成される第 2 容量 C s 2 は、第 3 画素 4 9 G b で形成される第 2 容量 C s 2 よりも小さい容量値である。すなわち、第 2 画素 4 9 G a に設けられたアノード接続電極 2 4 の面積は、第 3 画素 4 9 G b に設けられたアノード接続電極 2 4 の面積よりも小さい。第 2 画素 4 9 G a において、第 2 容量 C s 2 は例えれば 1 5 0 f F 程度である。また、第 3 画素 4 9 G b において、第 2 容量 C s 2 は例えれば 2 5 0 f F 程度である。

#### 【 0 0 5 1 】

また、本実施形態において、発光素子 3 に駆動電流を供給するための駆動トランジスタ D R T 及び出力トランジスタ B C T は、シングルゲート構造である。初期化トランジスタ I S T 、画素選択トランジスタ S S T 及びリセットトランジスタ R S T はダブルゲート構造である。これにより、初期化トランジスタ I S T 、画素選択トランジスタ S S T 及びリセットトランジスタ R S T のリーク電流を抑制することができる。

#### 【 0 0 5 2 】

次に、表示装置 1 の断面構成について説明する。図 5 は、図 4 の V - V' 線に沿う断面図である。図 6 は、図 4 の V I - V I' 線に沿う断面図である。なお、図 6 では、周辺領域 G A に設けられたカソード配線 6 0 及びトランジスタ T r を模式的に示している。

#### 【 0 0 5 3 】

図 5 に示すように、発光素子 3 は、アレイ基板 2 の上に設けられる。アレイ基板 2 は、基板 2 1 、各種トランジスタ、各種配線及び各種絶縁膜を有する。基板 2 1 は絶縁基板であり、例えば、ガラス基板、樹脂基板又は樹脂フィルム等が用いられる。

#### 【 0 0 5 4 】

本明細書において、基板 2 1 の表面に垂直な方向において、基板 2 1 から平坦化膜 2 7 に向かう方向を「上側」とする。また、平坦化膜 2 7 から基板 2 1 に向かう方向を「下側」とする。

#### 【 0 0 5 5 】

駆動トランジスタ D R T 、出力トランジスタ B C T 、初期化トランジスタ I S T 、画素選択トランジスタ S S T 及びリセットトランジスタ R S T は、基板 2 1 の一方の面側に設けられる。基板 2 1 の一方の面に、アンダーコート膜 9 0 、各ゲート線、第 1 絶縁膜 9 1 、半導体層 6 1 、6 5 、7 1 、7 5 、第 2 絶縁膜 9 2 、各信号線及び電源線、第 3 絶縁膜 9 3 、アノード接続電極 2 4 及びシールド電極 2 6 、第 4 絶縁膜 9 4 の順に積層される。

#### 【 0 0 5 6 】

アノード接続電極 2 4 及びシールド電極 2 6 の上に、第 4 絶縁膜 9 4 を介して、アノード電極 2 3 及び発光素子 3 が設けられる。

#### 【 0 0 5 7 】

10

20

30

40

50

表示装置 1において、アレイ基板 2は、基板 21からアノード電極 23までの各層を含む。アレイ基板 2には、平坦化膜 27、カソード電極 22及び発光素子 3は含まれない。

#### 【0058】

アンダーコート膜 90、第1絶縁膜 91、第2絶縁膜 92及び第4絶縁膜 94は、シリコン酸化膜(SiO)、シリコン窒化膜(SiN)又はシリコン酸化窒化膜(SiON)等の無機絶縁材料が用いられる。また、各無機絶縁膜は、単層に限定されず積層膜であつてもよい。また、アンダーコート膜 90は設けられていなくてもよい。第3絶縁膜 93及び平坦化膜 27は、有機絶縁膜あるいは無機有機ハイブリッド絶縁膜(Si-O主鎖に、例えば有機基(メチル基あるいはフェニル基)が結合した材料)である。

#### 【0059】

ゲート電極 64、66、74、78は、アンダーコート膜 90を介して基板 21の上に設けられる。第1絶縁膜 91は、ゲート電極 64、66、74、78を覆ってアンダーコート膜 90の上に設けられる。半導体層 61、65、71、75は、第1絶縁膜 91の上に設けられる。第2絶縁膜 92は、半導体層 61、65、71、75を覆って第1絶縁膜 91の上に設けられる。

#### 【0060】

図5に示す例では、各トランジスタは、いわゆるボトムゲート構造である。ただし、各トランジスタは、半導体層の上側にゲート電極が設けられたトップゲート構造でもよく、半導体層の上側及び下側の両方にゲート電極が設けられたデュアルゲート構造でもよい。

#### 【0061】

接続配線 L9、ソース電極 62、72及びドレイン電極 67は、第2絶縁膜 92の上に設けられる。ソース電極 62は第2絶縁膜 92に設けられたコンタクトホールを介して第1部分半導体層 61a(半導体層 61)と電気的に接続される。

#### 【0062】

ドレイン電極 67は第2絶縁膜 92に設けられたコンタクトホールを介して半導体層 65と電気的に接続される。また、初期化トランジスタ ISTのソース電極 72は、第2絶縁膜 92に設けられたコンタクトホールを介して半導体層 71と電気的に接続される。

#### 【0063】

接続配線 L9の一端側は、第2絶縁膜 92に設けられたコンタクトホールを介して画素選択トランジスタ SSTの半導体層 75と電気的に接続される。接続配線 L9のうち、半導体層 75と重なる部分がドレイン電極 77として機能する。また、接続配線 L9の他端側は、第2絶縁膜 92に設けられたコンタクトホールを介して初期化トランジスタ ISTの半導体層 71と電気的に接続される。接続配線 L9のうち、半導体層 71と重なる部分がドレイン電極 73として機能する。このような構成により、画素選択トランジスタ SSTのドレンと初期化トランジスタ ISTのドレンとが接続配線 L9を介して電気的に接続される。

#### 【0064】

第3絶縁膜 93は、ソース電極 62、72及びドレイン電極 67、73、77を覆って、第2絶縁膜 92の上に設けられる。第3絶縁膜 93の上にアノード接続電極 24及びシールド電極 26が設けられる。アノード接続電極 24は、第3絶縁膜 93に設けられたコンタクトホールを介してソース電極 62と接続される。シールド電極 26は、アノード電極 23及び発光素子 3の下に設けられる。

#### 【0065】

第4絶縁膜 94は、アノード接続電極 24及びシールド電極 26を覆って、第3絶縁膜 93の上に設けられる。アノード電極 23は第4絶縁膜 94の上に設けられる。アノード電極 23は、第4絶縁膜 94に設けられたコンタクトホールを介してアノード接続電極 24と電気的に接続される。

#### 【0066】

発光素子 3は、アノード電極 23の上に設けられ、発光素子 3のアノード端子 23tとアノード電極 23が接続される。これにより、発光素子 3のアノード端子 23tは、駆動

10

20

30

40

50

トランジスタ D R T のソース電極 6 2 と電気的に接続される。

【 0 0 6 7 】

平坦化膜 2 7 は、発光素子 3 の少なくとも側面 3 a を覆って第 4 絶縁膜 9 4 の上に設けられる。カソード電極 2 2 は、平坦化膜 2 7 の上に設けられ、発光素子 3 のカソード端子 2 2 t と接続される。カソード電極 2 2 は、表示領域 A A から周辺領域 G A に亘って設けられており、複数の画素 4 9 の発光素子 3 と電気的に接続される。

【 0 0 6 8 】

図 6 に示すように、基板 2 1 の周辺領域 G A には、複数のトランジスタとして、駆動回路 1 2 (図 1 参照) に含まれるトランジスタ T r 及びカソード配線 6 0 が設けられる。カソード配線 6 0 は、アノード電源線 L 1 と同層に設けられ、周辺領域 G A において第 2 絶縁膜 9 2 の上に設けられる。図 5 に示すカソード電極 2 2 は、第 3 絶縁膜 9 3 、第 4 絶縁膜 9 4 及び平坦化膜 2 7 に設けられたコンタクトホールを介して、カソード配線 6 0 と電気的に接続される。また、図 3 に示すカソード電源線 L 1 0 は、カソード配線 6 0 及びカソード電極 2 2 を含む。

10

【 0 0 6 9 】

トランジスタ T r は、半導体層 8 1 、ソース電極 8 2 、ドレイン電極 8 3 及びゲート電極 8 4 を含む。トランジスタ T r は、画素回路 P I C A に含まれる各トランジスタと同様の層構成を有しており、詳細な説明は省略する。半導体層 8 1 は、第 1 絶縁膜 9 1 の上、すなわち、各半導体層 6 1 、6 5 、7 1 、7 5 、7 9 と同層に設けられている。ただし、トランジスタ T r は、画素 4 9 の各トランジスタと異なる層に設けられていてもよい。

20

【 0 0 7 0 】

図 6 に示すように、アノード電源線 L 1 、映像信号線 L 2 及びリセット電源線 L 3 は、第 2 絶縁膜 9 2 の上に設けられる。アノード電源線 L 1 の幅は、映像信号線 L 2 及びリセット電源線 L 3 のそれぞれの幅よりも大きい。また、アノード電源線 L 1 の厚さ t 2 は、ゲート電極 6 4 の厚さ t 1 (図 5 参照) よりも厚い。また、アノード電源線 L 1 の厚さ t 2 は、映像信号線 L 2 及びリセット電源線 L 3 の厚さと等しい。これにより、アノード電源線 L 1 の抵抗値を小さくすることができる。なお、アノード電源線 L 1 の厚さ t 2 は、映像信号線 L 2 及びリセット電源線 L 3 の厚さと異なっていてもよい。

【 0 0 7 1 】

各配線の層構成は適宜変更できる。例えば、アノード電源線 L 1 と、映像信号線 L 2 及びリセット電源線 L 3 等の各信号線とが、異なる層に設けられていてもよい。

30

【 0 0 7 2 】

アノード電源線 L 1 と各種ゲート線との間に形成される容量は、デカップリングコンデンサとして用いられる。これにより、デカップリングコンデンサは、アノード電源電位 P V D D の変動を吸収して、駆動 I C 2 1 0 を安定して動作させることができる。また、デカップリングコンデンサは、表示装置 1 で発生する電磁ノイズが外部に漏れることを抑制できる。

【 0 0 7 3 】

なお、上述した図 3 に示す画素回路 P I C A の構成は適宜変更することができる。例えば 1 つの画素 4 9 での配線の数及びトランジスタの数は異なっていてもよい。

40

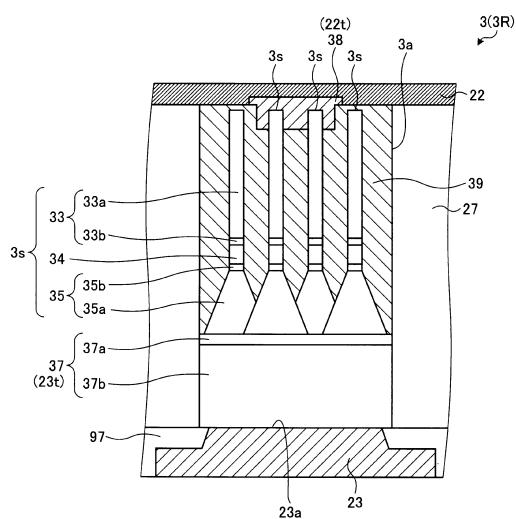

【 0 0 7 4 】

図 7 は、実施形態に係る赤色発光素子を示す断面図である。本実施形態の表示装置 1 において、赤色発光素子 3 R は、アノード端子 2 3 t が下側に設けられカソード端子 2 2 t が上側に設けられた、いわゆるフェースアップ構造である。

【 0 0 7 5 】

図 7 に示すように、赤色発光素子 3 R は、複数の部分発光素子 3 s と、複数の部分発光素子 3 s を覆う保護層 3 9 と、p 型電極 3 7 と、n 型電極 3 8 と、を有する。複数の部分発光素子 3 s は、p 型電極 3 7 と n 型電極 3 8 との間に、それぞれ柱状に形成される。複数の部分発光素子 3 s は、n 型クラッド層 3 3 と、発光層 3 4 と、p 型クラッド層 3 5 と、を有する。n 型電極 3 8 は、n 型クラッド層 3 3 に電気的に接続される。p 型電極 3 7

50

は p 型クラッド層 3 5 に電気的に接続される。p 型電極 3 7 の上に、p 型クラッド層 3 5 、発光層 3 4 、n 型クラッド層 3 3 の順に積層される。

#### 【 0 0 7 6 】

n 型クラッド層 3 3 は、第 1 n 型クラッド層 3 3 a 及び第 2 n 型クラッド層 3 3 b を有する。発光層 3 4 の上に、第 2 n 型クラッド層 3 3 b 、第 1 n 型クラッド層 3 3 a の順に積層される。第 1 n 型クラッド層 3 3 a は、例えば n 型窒化ガリウム ( n - G a N ) であり、第 2 n 型クラッド層 3 3 b は、例えば n 型アルミニウム窒化ガリウム ( n - A 1 G a N ) である。

#### 【 0 0 7 7 】

p 型クラッド層 3 5 は、第 1 p 型クラッド層 3 5 a 及び第 2 p 型クラッド層 3 5 b を有する。p 型電極 3 7 の上に、第 1 p 型クラッド層 3 5 a 、第 2 p 型クラッド層 3 5 b の順に積層される。すなわち、発光層 3 4 は、第 2 p 型クラッド層 3 5 b と第 2 n 型クラッド層 3 3 b との間に設けられる。第 1 p 型クラッド層 3 5 a は、例えば p 型窒化ガリウム ( p - G a N ) であり、第 2 p 型クラッド層 3 5 b は、例えば p 型アルミニウム窒化ガリウム ( p - A 1 G a N ) である。

#### 【 0 0 7 8 】

赤色発光素子 3 R の発光層 3 4 は、ユウロピウム ( E u ) が添加された窒化ガリウム ( G a N ) である。これにより、赤色発光素子 3 R は、赤色の光の発光効率を向上させることができる。

#### 【 0 0 7 9 】

n 型電極 3 8 は、I T O ( Indium Tin Oxide ) 等の透光性の導電性材料である。n 型電極 3 8 は、赤色発光素子 3 R のカソード端子 2 2 t であり、カソード電極 2 2 に接続される。また、p 型電極 3 7 は、赤色発光素子 3 R のアノード端子 2 3 t であり、P t 層 3 7 a と、メッキにより形成された厚膜 A u 層 3 7 b と、を有する。厚膜 A u 層 3 7 b は、アノード電極 2 3 の載置面 2 3 a に接続される。

#### 【 0 0 8 0 】

保護層 3 9 は、例えば S O G ( Spin on Glass ) である。保護層 3 9 の側面が、赤色発光素子 3 R の側面 3 a となる。平坦化膜 2 7 は、保護層 3 9 の側面を囲んで設けられる。

#### 【 0 0 8 1 】

複数の部分発光素子 3 s のそれぞれに発光層 3 4 が設けられており、複数の部分発光素子 3 s ごとに、窒化ガリウム ( G a N ) に添加されたユウロピウム ( E u ) の状態を異なることができる。具体的には、複数の部分発光素子 3 s ごとに、ユウロピウム ( E u ) の添加量が異なる。これにより、赤色発光素子 3 R は、光のスペクトル S P R ( 図 8 参照 ) の半値幅を大きくすることができる。

#### 【 0 0 8 2 】

図 7 では赤色発光素子 3 R について説明したが、第 1 緑色発光素子 3 G a 、第 2 緑色発光素子 3 G b 及び青色発光素子 3 B の断面構造も同様である。第 1 緑色発光素子 3 G a 、第 2 緑色発光素子 3 G b 及び青色発光素子 3 B では、n 型クラッド層 3 3 及び p 型クラッド層 3 5 の材料として、例えば窒化インジウムガリウム ( I n G a N ) が用いられる。また、発光層 3 4 は、インジウム窒化ガリウム ( I n x G a ( 1 - x ) N ) と窒化ガリウム ( G a N ) とが複数層繰り返し積層されて構成される多重量子井戸構造 ( M Q W 構造 ) である。

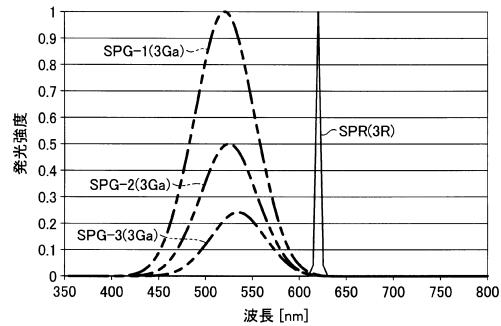

#### 【 0 0 8 3 】

図 8 は、赤色発光素子及び第 1 緑色発光素子の発光強度と波長との関係を模式的に示すグラフである。図 8 には、赤色発光素子 3 R から出射される光のスペクトル S P R と、第 1 緑色発光素子 3 G a から出射される光のスペクトル S P G - 1 、 S P G - 2 、 S P G - 3 を示している。スペクトル S P G - 1 、 S P G - 2 、 S P G - 3 は、第 1 緑色発光素子 3 G a にそれぞれ異なる大きさの駆動電流を供給した場合の光のスペクトルを示す。スペクトル S P G - 1 、 S P G - 2 、 S P G - 3 の順に駆動電流が小さくなる。

#### 【 0 0 8 4 】

10

20

30

40

50

スペクトル S P R 及びスペクトル S P G - 1 の極大発光波長は、それぞれ 6 2 0 n m 、 5 2 0 n m 程度である。本実施形態では、赤色発光素子 3 R の発光層 3 4 として、ユウロピウム ( E u ) が添加された窒化ガリウム ( G a N ) を用いているので、赤色発光素子 3 R の発光効率 ( 発光強度 ) が向上する。また、スペクトル S P R の半値幅は、スペクトル S P G - 1 、 S P G - 2 、 S P G - 3 の半値幅よりも小さい。

#### 【 0 0 8 5 】

また、第 1 緑色発光素子 3 G a に供給される駆動電流が小さくなるにしたがって、すなわち、スペクトル S P G - 1 、 S P G - 2 、 S P G - 3 の順に、発光強度が小さくなり、極大発光波長が長くなる。すなわち、第 1 緑色発光素子 3 G a のスペクトル S P G - 2 、 S P G - 3 の発光強度は、赤色発光素子 3 R の発光強度よりも小さい。また、極大発光波長は、スペクトル S P G - 1 、 S P G - 2 、 S P G - 3 の順にスペクトル S P R の極大発光波長に近づく。赤色の光のスペクトル S P R の波長領域は、第 1 緑色の光のスペクトル S P G - 1 、 S P G - 2 、 S P G - 3 の波長領域の一部と重なる。

#### 【 0 0 8 6 】

図 8 では、第 1 緑色発光素子 3 G a の第 1 緑色の光のスペクトル S P G - 1 、 S P G - 2 、 S P G - 3 を示している。ただし、第 2 緑色発光素子 3 G b についても、第 1 緑色発光素子 3 G a と同一構成とすることができます、第 2 緑色発光素子 3 G b から出射される第 2 緑色の光のスペクトルも、スペクトル S P G - 1 、 S P G - 2 、 S P G - 3 と同様である。

#### 【 0 0 8 7 】

本実施形態では、赤色の表示の際に、第 1 緑色発光素子 3 G a は、赤色発光素子 3 R の補助光として用いられる。すなわち、画素 P i x は、赤色発光素子 3 R 及び第 1 緑色発光素子 3 G a を同時に点灯させて、赤色発光素子 3 R からの光と第 1 緑色発光素子 3 G a からの光を混色させて赤色の光を表示する。第 1 緑色発光素子 3 G a には、第 2 緑色発光素子 3 G b 及び赤色発光素子 3 R よりも小さい駆動電流が供給される。第 1 緑色発光素子 3 G a は、スペクトル S P G - 2 又はスペクトル S P G - 3 に示すような強度分布の光を出射する。また、第 2 緑色発光素子 3 G b は、第 1 緑色発光素子 3 G a とは独立して駆動され、スペクトル S P G - 1 に示すような強度分布の光を出射する。

#### 【 0 0 8 8 】

すなわち、第 1 緑色発光素子 3 G a の発光強度は、赤色発光素子 3 R の発光強度よりも小さく、かつ、第 1 緑色発光素子 3 G a の光のスペクトル ( 例えばスペクトル S P G - 2 又はスペクトル S P G - 3 ) の半値幅は、赤色発光素子 3 R の光のスペクトル S P R の半値幅よりも大きい。また、第 2 緑色発光素子 3 G b の発光強度は、第 1 緑色発光素子 3 G a の発光強度よりも大きい。第 1 緑色発光素子 3 G a の光のスペクトル ( 例えばスペクトル S P G - 2 又はスペクトル S P G - 3 ) の極大発光波長は、第 2 緑色発光素子 3 G b の光のスペクトル ( 例えばスペクトル S P G - 1 ) の極大発光波長よりも長く、赤色発光素子 3 R の光のスペクトル S P R の極大発光波長よりも短い。

#### 【 0 0 8 9 】

これにより、赤色発光素子 3 R のみで赤色を表示する場合に比べて、赤色の光の波長の分布が実質的に拡がる。これにより、赤色発光素子 3 R 及び第 1 緑色発光素子 3 G a からの光が混色して出射される赤色の光の半値幅と、第 2 緑色発光素子 3 G b から出射される緑色の光の半値幅及び青色発光素子 3 B から出射される青色の光の半値幅との差が小さくなる。したがって、表示装置 1 は、画像によっては赤色のみが鮮やかに表示されることを抑制して、良好に画像を表示することができる。

#### 【 0 0 9 0 】

次に、図 9 及び図 1 0 を参照しつつ、各発光素子の駆動方法について説明する。図 9 は、信号処理回路の構成を模式的に示すブロック図である。図 1 0 は、入力階調値と、駆動される発光素子との関係を説明するための説明図である。

#### 【 0 0 9 1 】

図 9 に示すように、信号処理回路 1 0 0 は、第 1 処理回路 1 1 0 と、メモリ 1 1 5 と、バッファ 1 2 5 とを有する。信号処理回路 1 0 0 は、映像信号 V s i g に基づいて 4 つの

10

20

30

40

50

画素 4 9 の各々の出力階調値 S o R、S o G a、S o G b、S o B を演算する。映像信号 V s i g は画素 P i x ごとの入力階調値 S i R、S i G、S i B を含む。入力階調値 S i R、S i G、S i B は、それぞれ赤色、緑色、青色の階調値である。出力階調値 S o R は、第 1 画素 4 9 R に対応する階調値である。出力階調値 S o G a は、第 2 画素 4 9 G a に対応する階調値である。出力階調値 S o G b は、第 3 画素 4 9 G b に対応する階調値である。出力階調値 S o B は、第 4 画素 4 9 B に対応する階調値である。信号処理回路 1 0 0 は、例えば図 1 に示す駆動 I C 2 1 0 に含まれていてもよいし、駆動 I C 2 1 0 と別の回路チップとして基板 2 1 に設けられていてもよい。以下において、出力階調値 S o R、S o G a、S o G b、S o B をそれぞれ区別する必要がない場合、出力階調値 S o という。また、入力階調値 S i R、S i G、S i B をそれぞれ区別する必要がない場合、入力階調値 S i という。

10

#### 【 0 0 9 2 】

バッファ 1 2 5 は、入力階調値 S i を記憶する回路である。なお、バッファ 1 2 5 は、1 フレーム分の映像信号 V s i g に含まれる入力階調値 S i を記憶してもよいし、1 フレーム分の映像信号 V s i g のうち、一部の映像信号 V s i g に含まれる入力階調値 S i を取り込んでもよい。

#### 【 0 0 9 3 】

メモリ 1 1 5 は、入力階調値 S i R、S i G、S i B と、4 つの画素 4 9 の各々の出力階調値 S o R、S o G a、S o G b、S o B との関係を示す情報を示すデータ L U T を含む。データ L U T は、例えば、ルックアップテーブル (Look Up Table) のようなテーブルデータである。

20

#### 【 0 0 9 4 】

データ L U T は、入力階調値 S i R が 0 以上第 1 しきい値 L t h ( 図 1 0 参照 ) 以下の範囲では、赤色発光素子 3 R のみを点灯させる出力階調値 S o R が対応付けられている。すなわち、入力階調値 S i R が 0 以上第 1 しきい値 L t h 以下の範囲では、出力階調値 S o G a は 0 ( 階調値 0 ) である。また、データ L U T は、入力階調値 S i R が第 1 しきい値 L t h よりも大きく、第 2 しきい値 H t h ( 図 1 0 参照 ) よりも小さい範囲では、赤色発光素子 3 R 及び第 1 緑色発光素子 3 G a の両方を点灯させる出力階調値 S o R、S o G a が対応付けられている。第 2 しきい値 H t h は、第 1 しきい値 L t h よりも大きい階調値である。また、データ L U T は、入力階調値 S i R が第 2 しきい値 H t h 以上の範囲では、赤色発光素子 3 R のみを点灯させる出力階調値 S o R、S o G a が対応付けられている。すなわち、入力階調値 S i R が第 2 しきい値 H t h 以上の範囲では、出力階調値 S o G a は 0 ( 階調値 0 ) である。なお、第 2 しきい値 H t h は、入力階調値 S i R の最大階調値 m ( 例えば、m = 2 5 5 ) 以下の所定の数値である。

30

#### 【 0 0 9 5 】

第 1 処理回路 1 1 0 は、メモリ 1 1 5 から読み出したデータ L U T を参照して、入力階調値 S i R、S i G、S i B に対応する出力階調値 S o R、S o G a、S o G b、S o B を特定する。第 1 処理回路 1 1 0 は、出力階調値 S o R、S o G a、S o G b、S o B を画素 P i x に出力する。各画素 4 9 は、出力階調値 S o R、S o G a、S o G b、S o B に基づいて点灯する。

40

#### 【 0 0 9 6 】

図 1 0 に示すように、入力階調値 S i R が 0 以上第 1 しきい値 L t h 以下の範囲では、出力階調値 S o R、S o G a に基づいて、赤色発光素子 3 R が点灯し、第 1 緑色発光素子 3 G a は点灯しない。入力階調値 S i R が第 1 しきい値 L t h よりも大きく、第 2 しきい値 H t h よりも小さい範囲では、出力階調値 S o R、S o G a に基づいて、赤色発光素子 3 R 及び第 1 緑色発光素子 3 G a の両方が点灯する。緑色の表示及び青色の表示がない場合、すなわち、入力階調値 S i G、S i B が 0 の場合であっても、赤色の中間階調において、第 1 緑色発光素子 3 G a は点灯する。また、入力階調値 S i R が第 2 しきい値 H t h 以上の範囲では、赤色発光素子 3 R のみが点灯し、第 1 緑色発光素子 3 G a は点灯しない。

#### 【 0 0 9 7 】

50

このように、本実施形態では、低階調及び高階調の表示では、発光効率が高い赤色発光素子3Rのみを点灯させることで、駆動電流の増大を抑制して良好に表示を行うことができる。また、中間階調の表示では、赤色発光素子3R及び第1緑色発光素子3Gaの両方を点灯させることで、良好に表示を行うことができる。また、第1緑色発光素子3Gaに供給される駆動電流の増大を抑制することができるので、第2画素49Gaで形成される第2容量Cs2は、他の画素49で形成される第2容量Cs2よりも小さくすることができます。

#### 【0098】

##### (第1変形例)

図11は、各発光素子の出力階調値の設定方法を説明するためのフローチャートである。第1実施形態では、信号処理回路100は、あらかじめ定められたデータLUTに基づいて出力階調値SoR、SoGa、SoGb、SoBを演算するが、これに限定されない。図11に示すように、まず、信号処理回路100は、1フレーム画像を取り込む(ステップST1)。具体的には、バッファ125は、1フレーム分の映像信号Vsigを取り込んで、赤色、緑色、青色のそれぞれに対応する入力階調値SiR、SiG、SiBを記憶する。

10

#### 【0099】

第1処理回路110は、画素Pi<sub>x</sub>ごとに、入力階調値SiRが0より大きいか判断する(ステップST2)。言い換えると、画素Pi<sub>x</sub>ごとに、赤色の表示があるかどうかを判断する。入力階調値SiRが0である場合(ステップST2、No)、第1処理回路110は、出力階調値SoR、SoGaとして階調値0を設定する(ステップST3)。なお、階調値0は画素Pi<sub>x</sub>を非点灯状態とする階調値である。設定された出力階調値SoR、SoGaは画素Pi<sub>x</sub>に出力され、赤色発光素子3R及び第1緑色発光素子3Gaは非点灯状態となる。一方で、入力階調値SiRが0より大きい場合(ステップST2、Yes)、すなわち入力階調値SiRが1以上の値である場合、第1処理回路110は、入力階調値SiRと、第1しきい値Lth及び第2しきい値Hthとを比較する(ステップST4)。

20

#### 【0100】

入力階調値SiRが0より大きく第1しきい値Lth以下の場合、あるいは入力階調値SiRが第2しきい値Hth以上の場合(ステップST4、Yes)、第1処理回路110は、赤色発光素子3Rのみを点灯させる出力階調値SoR、SoGaを設定する(ステップST5)。より具体的には、出力階調値SoRとして入力階調値SiRに基づく0より大きい値(階調値SiOR)を設定し、出力階調値SoGaとして階調値0を設定する。設定された出力階調値SoR、SoGaは画素Pi<sub>x</sub>に出力され、赤色発光素子3Rが点灯し、第1緑色発光素子3Gaは非点灯状態となる。

30

#### 【0101】

入力階調値SiRが第1しきい値Lthよりも大きく、第2しきい値Hthよりも小さい場合(ステップST4、No)、第1処理回路110は、赤色発光素子3R及び第1緑色発光素子3Gaを点灯させる出力階調値SoR、SoGaを設定する(ステップST6)。より具体的には、出力階調値SoRとして入力階調値SiRに基づく0より大きい値(階調値SiORa)を設定し、出力階調値SoGaとして入力階調値SiRに基づく階調値Siogaを設定する。階調値Siogaは、0より大きい値を有する。設定された出力階調値SoR、SoGaは、画素Pi<sub>x</sub>に出力され、赤色発光素子3R及び第1緑色発光素子3Gaが点灯する。

40

#### 【0102】

ステップST3、ステップST5、または、ステップST6の処理が完了した場合、第1処理回路110は、入力階調値SiGが0より大きいかを判断する(ステップST7)。言い換えると、第1処理回路110は、緑色の表示があるかどうかを判断する(ステップST6)。入力階調値SiGが0である場合(ステップST7、No)、第1処理回路110は、出力階調値SoGbとして階調値0を設定する(ステップST8)。設定され

50

た出力階調値 S o G b は画素 P i x に出力され、第 2 緑色発光素子 3 G b は非点灯状態となる。入力階調値 S i G が 0 より大きい場合（ステップ ST 7、Yes）、すなわち入力階調値 S i G が 1 以上の値である場合、第 1 処理回路 110 は、入力階調値 S i G に基づく階調値（階調値 S i o G b）を出力階調値 S o G として設定する（ステップ ST 9）。設定された出力階調値 S o G b は、画素 P i x に出力され、第 2 緑色発光素子 3 G b が点灯する。

#### 【0103】

ステップ ST 8 またはステップ ST 9 の処理が完了した場合、第 1 処理回路 110 は、入力階調値 S i B が 0 より大きいかを判断する（ステップ ST 10）。言い換えると第 1 処理回路 110 は、青色の表示があるかどうかを判断する。入力階調値 S i B が 0 である場合（ステップ ST 10、No）、第 1 処理回路 110 は、出力階調値 S o B として階調値 0 を設定する（ステップ ST 11）。設定された出力階調値 S o B は画素 P i x に出力され、青色発光素子 3 B は非点灯状態となる。入力階調値 S i B が 0 より大きい場合（ステップ ST 7、Yes）、すなわち入力階調値 S i B が 1 以上の値である場合、第 1 処理回路 110 は、入力階調値 S i B に基づく階調値（階調値 S i o B）を出力階調値 S o B として設定する。設定された出力階調値 S o B は、画素 P i x に出力され、青色発光素子 3 B が点灯する（ステップ ST 12）。

10

#### 【0104】

ステップ ST 11 又はステップ ST 12 の処理が完了した場合、第 1 処理回路 110 は、1 フレーム分の全ての画素 P i x の出力階調値 S o R、S o G a、S o G b、S o B が設定されたかを判断する（ステップ ST 13）。全ての画素 P i x の出力階調値 S o が設定されていない場合（ステップ ST 13、No）、次の画素 P i x に対して、ステップ ST 2 からの処理を実行する。全ての画素 P i x の出力階調値 S o が設定されている場合（ステップ ST 13、Yes）、出力階調値 S o の設定処理を完了する。なお、設定処理が完了してから出力階調値 S o R、S o G a、S o G b、S o B が画素 P i x に出力され、それぞれの画素 P i x に配置された発光素子 3 は、設定された出力階調値 S o R、S o G a、S o G b、S o B に基づいて、点灯制御される。

20

#### 【0105】

なお、出力階調値 S o が設定されてから画素 P i x に出力されるタイミングは、1 フレームの全ての画素の出力階調値 S o の設定が完了してからでもよいし、共通するゲート線に接続される 1 ラインの画素群の設定が完了した段階で画素 P i x に出力されてもよい。また、画素 P i x 単位で出力階調値 S o が設定された順に、順次、画素 P i x に出力されてもよい。

30

#### 【0106】

##### （第 2 変形例）

図 12 は、第 2 変形例に係る信号処理回路の構成を模式的に示すブロック図である。図 13 は、第 2 変形例に係る各発光素子の出力階調値の設定方法を説明するためのフローチャートである。図 12 に示すように、信号処理回路 100A は、さらに第 2 処理回路 120 を備える。以下の説明では、隣り合う 2 つの画素 P i x を、第 1 画素群 P i x 1、第 2 画素群 P i x 2 と表す。信号処理回路 100A は、第 1 画素群 P i x 1 の入力階調値 S i R、S i G、S i B に基づいて、第 1 画素群 P i x 1 の各画素 4 9 に加え第 2 画素群 P i x 2 の一部の画素 4 9 を点灯させる。

40

#### 【0107】

第 1 処理回路 110 は、図 11 で示す処理と同様の処理を行い、出力階調値 S o R、S o G a 1、S o G b、S o B を第 2 処理回路 120 へ出力する。第 2 処理回路 120 は、第 1 処理回路 110 から受け取った出力階調値 S o G a 1 に対応する駆動電流と、所定のしきい値電流とを比較し、比較結果に基づく出力階調値 S o G a 2 を設定する。信号処理回路 100A は、設定された出力階調値 S o G a 2 を画素 P i x に出力する。具体的には、第 2 処理回路 120 は、出力階調値 S o G a 1 に基づいて、第 1 画素群 P i x 1 の第 1 緑色発光素子 3 G a に供給される駆動電流を演算する。そして、第 2 処理回路 120 は、

50

第1緑色発光素子3G aの駆動電流が所定のしきい値電流を超えないように、出力階調値S o G a 2を設定する。より具体的には、駆動電流が所定のしきい値電流を超える場合、出力階調値S o G a 1を、基準階調値S o t G aと、保持階調値S o r G aに分け、基準階調値S o t G aを出力階調値S o G a 2として設定する。基準階調値S o t G aは、しきい値電流又はしきい値電流以下の駆動電流に対応する階調値であって、出力階調値S o G a 2として設定され、第1画素群P i x 1の第1緑色発光素子3G a 1に出力される。また、保持階調値S o r G aは、メモリ115に入力される。

#### 【0108】

第2処理回路120は、メモリ115に保持階調値S o r G aが保持されている場合、保持階調値S o r G a及び第2画素群P i x 2の入力階調値S i Rに基づく階調値S i o G aに基づいて、出力階調値S o G a 2を設定する。なお、第1画素群P i x 1の入力階調値S i Rに対応する階調値S i o G aを基準階調値S o t G aと保持階調値S o r G aとに分ける場合は、第1緑色発光素子3G a 1を階調値S i o G aで発光させた場合の輝度と、第1緑色発光素子3G a 1と、第2画素群P i x 2の第1緑色発光素子3G a 2とをそれぞれ基準階調値S o t G aと保持階調値S o r G aで発光させた場合の輝度が実質的に等しくなるように設定される。そして、第2画素群P i x 2の入力階調値S i Rに基づく階調値S i o G aと、第1画素群P i x 1の入力階調値S i Rに基づく階調値S i o G aから分けられた保持階調値S o r G aとにに基づいて、第2画素群P i x 2の第1緑色発光素子3G a 2に対する出力階調値S o G a 2が設定される。

#### 【0109】

図13のステップST21からステップST26及びステップST7からステップST13は、図11と同様であるため、詳細な説明は省略する。図13に示すように、ステップST23、ステップST25の処理が完了した後に、第2処理回路120は、第1処理回路110から出力階調値S o G a 1を受け取り、メモリ115に保持階調値S o r G aが保持されているかを判断する(ステップST31)。メモリ115に保持階調値S o r G aが保持されている場合(ステップST31、Yes)、第2処理回路120は、保持階調値S o r G aを出力階調値S o G a 2として設定する(ステップST32)。設定された出力階調値S o G a 2は画素P i xに出力され、画素P i xに含まれる第1緑色発光素子3G aが点灯する。また、メモリ115に保持階調値S o r G aが保持されていない場合(ステップST31、No)、第2処理回路120は、出力階調値S o G a 1(階調値0)を出力階調値S o G a 2として設定する(ステップST33)。設定された出力階調値S o G a 2は画素P i xに出力され、画素P i xに含まれる第1緑色発光素子3G aが非点灯状態となる。

#### 【0110】

ステップST26の処理が完了した後に、第2処理回路120は、第1処理回路110から出力階調値S o G a 1を受け取り、メモリ115に保持階調値S o r G aが保持されているかを判断する(ステップST34)。メモリ115に保持階調値S o r G aが保持されている場合(ステップST34、Yes)、第2処理回路120は、出力階調値S o G a 1(入力階調値S i Rに基づく階調値S i o G a)に保持階調値S o r G aを加算する(ステップST35)。メモリ115に保持階調値S o r G aが保持されていない場合(ステップST34、No)、第2処理回路120は、出力階調値S o G a 1(階調値S i o G a)に対応する駆動電流がしきい値電流以下か判断する(ステップST36)。

#### 【0111】

出力階調値S o G a 1に対応する駆動電流がしきい値電流以下である場合(ステップST36、Yes)、第2処理回路120は、出力階調値S o G a 1を出力階調値S o G a 2として設定する(ステップST37)。設定された出力階調値S o G a 2は画素P i xに出力され、画素P i xに含まれる第1緑色発光素子3G aが点灯する。

#### 【0112】

なお、ステップST35の処理が完了した場合も同様に、第2処理回路120は、保持階調値S o r G aが加算された出力階調値S o G a 1(階調値S i o G a + 保持階調値S

10

20

30

40

50

$o_r G_a$ )に対応する駆動電流がしきい値電流以下であるかを判定する(ステップST36)。出力階調値 $S_o G_a 1$ に対応する駆動電流がしきい値電流以下である場合(ステップST36、Yes)、保持階調値 $S_o r G_a$ が加算された出力階調値 $S_o G_a 1$ を出力階調値 $S_o G_a 2$ として設定する(ステップST37)。設定された出力階調値 $S_o G_a 2$ は画素 $P_i x$ に出力され、保持階調値 $S_o r G_a$ が加算された出力階調値 $S_o G_a 1$ に対応する階調で、画素 $P_i x$ に含まれる第1緑色発光素子 $3 G_a$ が点灯する。

#### 【0113】

出力階調値 $S_o G_a 1$ に対応する駆動電流がしきい値電流より大きい場合(ステップST36、No)、第2処理回路120は、出力階調値 $S_o G_a 1$ (階調値 $S_{io} G_a$ )より小さい基準階調値 $S_{ot} G_a$ を出力階調値 $S_o G_a 2$ として設定する(ステップST38)。より具体的には、第2処理回路120は、出力階調値 $S_o G_a 1$ に基づき、基準階調値 $S_{ot} G_a$ と保持階調値 $S_o r G_a$ を演算し、基準階調値 $S_{ot} G_a$ を出力階調値 $S_o G_a 2$ として設定する。ステップST38の処理が完了した後に、第2処理回路120は、保持階調値 $S_o r G_a$ をメモリ115に記録する(ステップST39)。設定された出力階調値 $S_o G_a 2$ は画素 $P_i x$ に出力され、画素 $P_i x$ に含まれる第1緑色発光素子 $3 G_a$ が点灯する。10

#### 【0114】

なお、ステップST35の処理が完了した場合も同様に、第2処理回路120は、保持階調値 $S_o r G_a$ が加算された出力階調値 $S_o G_a 1$ (階調値 $S_{io} G_a +$ 保持階調値 $S_o r G_a$ )に対応する駆動電流がしきい値電流より大きい場合(ステップST36、No)、第2処理回路120は、保持階調値 $S_o r G_a$ が加算された出力階調値 $S_o G_a 1$ より小さい基準階調値 $S_{ot} G_a$ を出力階調値 $S_o G_a 2$ として設定する(ステップST38)。より具体的には、第2処理回路120は、保持階調値 $S_o r G_a$ が加算された出力階調値 $S_o G_a 1$ に基づき、基準階調値 $S_{ot} G_a$ と保持階調値 $S_o r G_a$ を演算し、基準階調値 $S_{ot} G_a$ を出力階調値 $S_o G_a 2$ として設定する(ステップST38)。ステップST38の処理が完了した後に、第2処理回路120は、保持階調値 $S_o r G_a$ をメモリ115に記録する(ステップST39)。設定された出力階調値 $S_o G_a 2$ は画素 $P_i x$ に出力され、画素 $P_i x$ に含まれる第1緑色発光素子 $3 G_a$ が点灯する。20

#### 【0115】

ステップST32、ステップST33、ステップST37、又はステップST39の処理が完了した後は、図11と同様に、信号処理回路100Aは、ステップST7からステップST13の処理を実施する。なお、各ステップSTの実施順は適宜変更可能であり、例えば、ステップST38及びステップST39は同時に実施してもよいし、ステップST39をステップST38より先に実施してもよい。また、ステップST36において、出力階調値 $S_o G_a 1$ に対応する駆動電流としきい値電流を比較しているが、これに限らず、しきい値電流に対応する基準階調値 $S_{ot} G_a$ を記録し、出力階調値 $S_o G_a 1$ が基準階調値 $S_{ot} G_a$ 以下かを判定してもよい。なお、基準階調値 $S_{ot} G_a$ は、全ての画素 $P_i x$ に共通の値であってもよいし、画素 $P_i x$ 毎に異なる値を有してもよい。30

#### 【0116】

第2変形例では、第1画素群 $P_i x 1$ の入力階調値 $S_i$ に基づいて演算された第1緑色発光素子 $3 G_a$ に供給される駆動電流がしきい値電流よりも大きい場合に、第1画素群 $P_i x 1$ の第1緑色発光素子 $3 G_a$ が入力階調値 $S_i R$ に対応する階調値 $S_{io} G_a 1$ より低い出力階調値(基準階調値 $S_{ot} G_a$ )で点灯し、保持階調値 $S_o r G_a$ が保持され、隣接する第2画素群 $P_i x 2$ の出力階調値 $S_o$ を設定する際に、保持階調値 $S_o r G_a$ が加算されることで、第1緑色発光素子 $3 G_a$ が入力階調値 $S_i R$ に対応する階調値 $S_{io} G_a 2$ より高い出力階調値(階調値 $S_{io} G_a 2 +$ 保持階調値 $S_o r G_a$ )で点灯する。これによって、隣接する第1画素群 $P_i x 1$ 、第2画素群 $P_i x 2$ の2つの第1緑色発光素子 $3 G_a$ により合計の発光強度を維持しつつ、第1画素群 $P_i x 1$ の第1緑色発光素子 $3 G_a$ に流れる駆動電流を抑制することができる。これにより、例えば図8に示す第1緑色発光素子 $3 G_a$ の光のスペクトルSPG-3の極大発光波長が、赤色発光素子 $3 R$ の波40

長領域から離れるようにシフトすることを抑制することができる。

#### 【0117】

##### (第3変形例)

図14は、第3変形例に係る各発光素子の出力階調値の設定方法を説明するためのフローチャートである。第2変形例において、第1処理回路110が、ステップST22からステップST26の処理を行い、第2処理回路120がステップST31からステップST39の処理を行うとしたが、これに限られない。第1処理回路110及び第2処理回路120が行う処理を入れ替えてよい。第3変形例において、第1処理回路110がメモリ115に保持階調値SorGaが保持されているか否かを判定する。なお、各ステップSTにおいて、第2変形例と共に記載は省略する。

10

#### 【0118】

第1処理回路110は、1フレーム分の入力階調値Siを取り込み(ステップST121)、保持階調値SorGaがメモリ115に保持されているか否かを判定する(ステップST122)。保持階調値SorGaが保持されていない場合(ステップST122、No)、第1処理回路110は、図11のステップST2からステップST6までと同様の処理を行う。具体的には、入力階調値SiRが0である場合(ステップST123、No)、及び、入力階調値SiRが第1しきい値Lth以下、若しくは、入力階調値SiRが第2しきい値Hth以上である場合(ステップST125、Yes)は、第1処理回路110は、第2処理回路120を介さずに、出力階調値SoGa2として階調値0を設定する(ステップST124、ステップST126)。また、入力階調値SiRが第1しきい値Lthより大きく、第2しきい値Hthより小さい場合(ステップST125、No)は、第1処理回路110は、入力階調値SiRに基づく階調値Siogaを出力階調値SoGa1として第2処理回路120に出力する(ステップST127)。

20

#### 【0119】

保持階調値SorGaがメモリ115に保持されている場合(ステップST122、Yes)、第1処理回路110は、保持階調値SorGaを加算した上で、ステップST123からステップST127と同様の処理を実施する。具体的には、入力階調値SiRが0である場合(ステップST128、No)、及び、入力階調値SiRが第1しきい値Lth以下、若しくは、入力階調値SiRが第2しきい値Hth以上である場合(ステップST130、Yes)は、第1処理回路110は、第2処理回路120を介さずに、出力階調値SoGa2として保持階調値SorGaを設定する(ステップST129、ステップST131)。また、入力階調値SiRが第1しきい値Lthより大きく、第2しきい値Hthより小さい場合(ステップST130、No)は、第1処理回路110は、入力階調値SiRに基づく階調値Siogaに保持階調値SorGaを加算した値を出力階調値SoGa1として第2処理回路120に出力する(ステップST132)。

30

#### 【0120】

第2処理回路120は、第1処理回路110から出力階調値SoGa1を受け取ると(ステップST132、ステップST127)、図13のステップST36からステップST39と同様の処理を実施する。具体的には、第2処理回路120は、出力階調値SoGa1に対応する駆動電流がしきい値電流以下かを判断する(ステップST133)。出力階調値SoGa1に対応する駆動電流がしきい値電流以下である場合(ステップST133、Yes)、第2処理回路120は、出力階調値SoGa1を出力階調値SoGa2として設定する(ステップST134)。出力階調値SoGa1に対応する駆動電流がしきい値電流より大きい場合(ステップST133、No)、第2処理回路120は、出力階調値SoGa1に基づいて、基準階調値SotGaと保持階調値SorGaに分け、基準階調値SotGaを出力階調値SoGa2として設定し(ステップST135)、保持階調値SorGaをメモリ115に記録する(ステップST136)。

40

#### 【0121】

ステップST124、ステップST126、ステップST129、ステップST131、ステップST134、又は、ステップST136の処理が完了した後は、図11と同様

50

に、信号処理回路 100A は、ステップ ST7 からステップ ST13 の処理を実施する。

#### 【0122】

このように、保持階調値 S or Ga が保持されているか否かを第1処理回路 110 で処理することで、一部のステップ ST (ステップ ST124、ステップ ST126、ステップ ST129、ステップ ST131) で第2処理回路 120 を介さずに処理を完了することができ、処理を簡素化することができる。

#### 【0123】

##### (第4変形例)

図 15A から図 15C は、1つの画素群における各発光素子の配置パターンの変形例を示す平面図である。実施形態では、1画素 Pixにおいて、図 2 に示すように赤色発光素子 3R、第1緑色発光素子 3Ga、第2緑色発光素子 3Gb 及び青色発光素子 3B が配置されたが、各発光素子 3 の配置パターンはこれに限られない。図 15A は、第4変形例に係る1つの画素群における各発光素子の第1配置パターンを示す平面図である。図 15A に示すように、第1配置パターン AP1 では、赤色発光素子 3R と第1緑色発光素子 3Ga は第2方向 Dy で並ぶ。赤色発光素子 3R と第2緑色発光素子 3Gb は第1方向 Dx で並ぶ。第1緑色発光素子 3Ga と青色発光素子 3B は第1方向 Dx で並ぶ。また、第2緑色発光素子 3Gb と青色発光素子 3B は第2方向 Dy で並ぶ。

10

#### 【0124】

赤色発光素子 3R と第1方向 Dx 又は第2方向 Dy に隣り合う位置には、波長が近い第1緑色発光素子 3Ga 又は第2緑色発光素子 3Gb が設けられることが好ましい。なお、第1配置パターン AP1 において、赤色発光素子 3R と第1緑色発光素子 3Ga との配置を入れ替えてよいし、あるいは、第2緑色発光素子 3Gb と青色発光素子 3B との配置を入れ替えてよい。また、赤色発光素子 3R と第1緑色発光素子 3Ga との配置を入れ替えて、且つ、第2緑色発光素子 3Gb と青色発光素子 3B との配置を入れ替えてよい。

20

#### 【0125】

図 15B は、1つの画素群における各発光素子の第2配置パターンを示す平面図である。図 15B に示すように、第2配置パターン AP2 では、赤色発光素子 3R と第1緑色発光素子 3Ga は第1方向 Dx で並ぶ。赤色発光素子 3R と第2緑色発光素子 3Gb は第2方向 Dy で並ぶ。第1緑色発光素子 3Ga と青色発光素子 3B は第2方向 Dy で並ぶ。また、第2緑色発光素子 3Gb と青色発光素子 3B は第1方向 Dx で並ぶ。

30

#### 【0126】

なお、第2配置パターン AP2 において、赤色発光素子 3R と第1緑色発光素子 3Ga との配置を入れ替えてよいし、あるいは、第2緑色発光素子 3Gb と青色発光素子 3B との配置を入れ替えてよい。また、赤色発光素子 3R と第1緑色発光素子 3Ga との配置を入れ替えて、且つ、第2緑色発光素子 3Gb と青色発光素子 3B との配置を入れ替えてよい。赤色発光素子 3R と第1方向 Dx 又は第2方向 Dy に隣り合う位置には、波長が近い第1緑色発光素子 3Ga 又は第2緑色発光素子 3Gb が設けられることが好ましい。

#### 【0127】

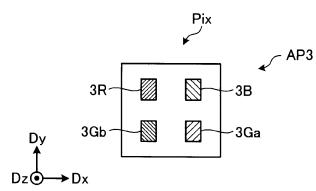

図 15C は、1つの画素群における各発光素子の第3配置パターンを示す平面図である。図 15C に示すように、第3配置パターン AP3 では、赤色発光素子 3R と青色発光素子 3B は第1方向 Dx で並ぶ。赤色発光素子 3R と第2緑色発光素子 3Gb は第2方向 Dy で並ぶ。青色発光素子 3B と第1緑色発光素子 3Ga は第2方向 Dy で並ぶ。また、第2緑色発光素子 3Gb と第1緑色発光素子 3Ga は第1方向 Dx で並ぶ。言い換えると、赤色発光素子 3R と第1緑色発光素子 3Ga が第1方向 Dx 及び第2方向 Dy のいずれとも交差する斜め方向に配列される。

40

#### 【0128】

なお、第3配置パターン AP3 において、赤色発光素子 3R と第1緑色発光素子 3Ga との配置を入れ替えてよいし、あるいは、第2緑色発光素子 3Gb と青色発光素子 3B との配置を入れ替えてよい。また、赤色発光素子 3R と第1緑色発光素子 3Ga との配置を入れ替えて、且つ、第2緑色発光素子 3Gb と青色発光素子 3B との配置を入れ替え

50

てもよい。つまり、赤色発光素子 3 R と、第 2 緑色発光素子 3 G b 又は青色発光素子 3 B の一方とは、第 1 方向 D x に並び、赤色発光素子 3 R と、第 2 緑色発光素子 3 G b 又は青色発光素子 3 B の他方とは、第 2 方向 D y に並ぶ。

#### 【0129】

##### (第 5 変形例)

図 16 A から図 16 C は、2つの画素群における各発光素子 3 の配置パターンの変形例を示す平面図である。実施形態及び第 4 変形例において、各発光素子 3 の配置パターンについて記載したが、マトリクス状に配置された画素 P i x の全てがこの配置である場合、各赤色発光素子 3 R 、第 1 緑色発光素子 3 G a 、第 2 緑色発光素子 3 G b 、青色発光素子 3 B は、それぞれ、一定の方向に配置されることとなる。このような場合、特に第 1 緑色発光素子 3 G a のような非点灯状態となりやすい画素が一方向に配列していると、スジムラとして視認される恐れがある。そこで、第 5 変形例では、各発光素子 3 の配置パターンが異なる 2 種類の画素 P i x を配置する。このようにすることで、スジムラの視認を抑制することができる。10

#### 【0130】

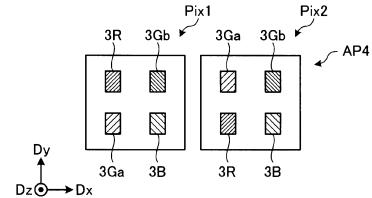

図 16 A は、第 5 変形例に係る 2 つの画素群における各発光素子の第 4 配置パターンを示す平面図である。図 16 A に示すように、第 4 配置パターン A P 4 において、第 1 方向 D x に並ぶ 2 つの第 1 画素群 P i x 1 及び第 2 画素群 P i x 2 は、発光素子 3 の配置が異なる。図 16 A 左側の第 1 画素群 P i x 1 は、図 15 A に示す第 1 配置パターン A P 1 と同じ発光素子 3 の配置であり、図 16 A 右側の第 2 画素群 P i x 2 は、第 1 画素群 P i x 1 の赤色発光素子 3 R と第 1 緑色発光素子 3 G a とを入れ替えた構成である。このように、複数の画素 P i x ごとに発光素子 3 の配置が異なっていてもよい。20

#### 【0131】

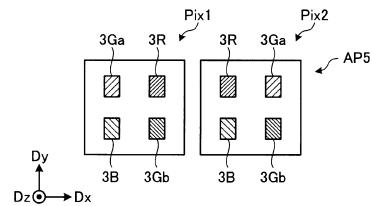

図 16 B は、2つの画素群における各発光素子の第 5 配置パターンを示す平面図である。図 16 B に示すように、第 5 配置パターン A P 5 において、第 1 画素群 P i x 1 及び第 2 画素群 P i x 2 は、図 15 B に示す第 2 配置パターン A P 2 と同様の発光素子 3 の配置である。図 16 B 左側の第 1 画素群 P i x 1 は、図 15 B に示す第 2 配置パターン A P 2 において、赤色発光素子 3 R と第 1 緑色発光素子 3 G a との配置を入れ替えて、且つ、第 2 緑色発光素子 3 G b と青色発光素子 3 B との配置を入れ替えた構成である。図 16 B 右側の第 2 画素群 P i x 2 は、第 1 画素群 P i x 1 の赤色発光素子 3 R と第 1 緑色発光素子 3 G a との配置を入れ替えた構成である。30

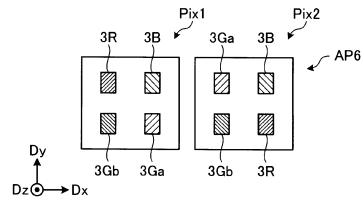

#### 【0132】

図 16 C は、2つの画素群における各発光素子の第 6 配置パターンを示す平面図である。図 16 C に示すように、第 6 配置パターン A P 6 において、左側の第 1 画素群 P i x 1 は、図 15 C に示す第 3 配置パターン A P 3 と同様の発光素子 3 の配置である。図 16 C 右側の第 2 画素群 P i x 2 は、第 1 画素群 P i x 1 の赤色発光素子 3 R と第 1 緑色発光素子 3 G a との配置を入れ替えた構成である。

#### 【0133】

##### (第 6 変形例)

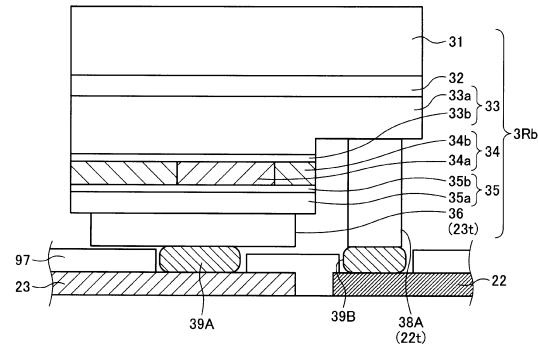

図 17 は、第 6 変形例に係る赤色発光素子を示す断面図である。表示装置 1 において、発光素子 3 はフェースアップ構造に限定されず、発光素子 3 の下部が、アノード電極 2 3 及びカソード電極 2 2 に接続される、いわゆるフェースダウン構造であってもよい。図 17 では、発光素子 3 のうち、赤色発光素子 3 R a の断面構造を示す。40

#### 【0134】

図 17 に示すように、赤色発光素子 3 R a は、透光性基板 3 1 の上に、バッファ層 3 2 、n 型クラッド層 3 3 、発光層 3 4 、p 型クラッド層 3 5 、p 型電極 3 6 の順に積層される。赤色発光素子 3 R a は、透光性基板 3 1 が上側に、p 型電極 3 6 が下側になるように実装される。また、n 型クラッド層 3 3 において、カソード電極 2 2 と対向する面側には、発光層 3 4 から露出した領域が設けられている。この領域に n 型電極 3 8 A が設けられている。50

**【 0 1 3 5 】**

p型電極36は、発光層34からの光を反射する金属光沢のある材料で形成される。p型電極36はバンプ39Aを介してアノード電極23に接続される。n型電極38Aはバンプ39Bを介してカソード電極22に接続される。絶縁膜97はカソード電極22及びアノード電極23を覆っており、絶縁膜97の開口部分でバンプ39A、39Bは、それぞれアノード電極23及びカソード電極22と接続される。

**【 0 1 3 6 】**

赤色発光素子3Raにおいて、p型クラッド層35（第2p型クラッド層35b）とn型クラッド層33（第2n型クラッド層33b）とが直接接合せずに、間に別の層（発光層34）が導入されている。これにより、電子や正孔といったキャリアを発光層34の中に集中させることができ、効率よく再結合（発光）させることができる。本変形例においても、赤色発光素子3Raにおいて、ユウロピウム（Eu）が添加された窒化ガリウム（GaN）が、発光層34として採用される。さらに、赤色発光素子3Raにおいて、数原子層からなる井戸層と障壁層とを周期的に積層させた多重量子井戸構造（MQW構造）が、発光層34として採用される。

10

**【 0 1 3 7 】**

具体的には、発光層34は、第2p型クラッド層35bの上に、ユウロピウム（Eu）が添加された窒化ガリウム（GaN）、MQW構造の順に積層される。MQW構造は、例えばインジウム窒化ガリウム（In<sub>x</sub>Ga<sub>(1-x)</sub>N）と窒化ガリウム（GaN）とが複数層繰り返し積層されて構成される。なお、ユウロピウム（Eu）が添加された窒化ガリウム（GaN）とMQW構造との積層の順番は逆であってもよい。また、ユウロピウム（Eu）が添加された窒化ガリウム（GaN）は、MQW構造に含まれていてもよい。すなわち、MQW構造は、ユウロピウム（Eu）が添加された窒化ガリウム（GaN）と、インジウム窒化ガリウム（In<sub>x</sub>Ga<sub>(1-x)</sub>N）と、窒化ガリウム（GaN）とが複数層繰り返し積層されて構成されてもよい。

20

**【 0 1 3 8 】**

赤色発光素子3Raは、ユウロピウム（Eu）が添加された窒化ガリウム（GaN）を有しているので、発光効率を向上させることができ、且つ、MQW構造により、光のスペクトルSPRの半値幅を大きくすることができます。

**【 0 1 3 9 】**

30

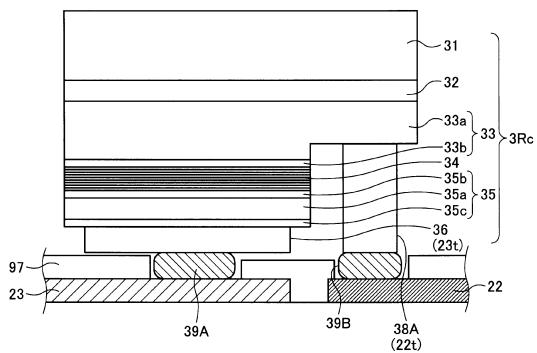

**（第7変形例）**

図18は、第7変形例に係る赤色発光素子を示す断面図である。図18に示すように、第7変形例の赤色発光素子3Rbにおいて、発光層34の第1発光層34a及び第2発光層34bは、同層に設けられる。第1発光層34a及び第2発光層34bは、p型クラッド層35の上において、隣接して設けられる。第1発光層34aの上面及び第2発光層34bの上面は、n型クラッド層33に接し、第1発光層34aの下面及び第2発光層34bの下面是、p型クラッド層35に接する。

**【 0 1 4 0 】**

第1発光層34aは、ユウロピウム（Eu）が添加された窒化ガリウム（GaN）である。また、第2発光層34bは、インジウム窒化ガリウム（In<sub>x</sub>Ga<sub>(1-x)</sub>N）と窒化ガリウム（GaN）とが複数層繰り返し積層されたMQW構造である。

40

**【 0 1 4 1 】****（第8変形例）**

図19は、第8変形例に係る赤色発光素子を示す断面図である。図19に示すように、第8変形例の赤色発光素子3Rcにおいて、p型クラッド層35は、第3p型クラッド層35cを有する。第3p型クラッド層35cは、第1p型クラッド層35aとp型電極36との間に設けられる。第3p型クラッド層35cは、高濃度不純物領域が形成された窒化ガリウム（P<sup>+</sup>GaN）である。

**【 0 1 4 2 】**

発光層34は、第3p型クラッド層35c、第1p型クラッド層35a及び第2p型ク

50

ラッド層 3 5 b と、n 型クラッド層 3 3 との間に設けられる。発光層 3 4 は、第 6 変形例と同様に、ユウロピウム (Eu) が添加された窒化ガリウム (GaN) と、MQW 構造とが積層されている。

#### 【0143】

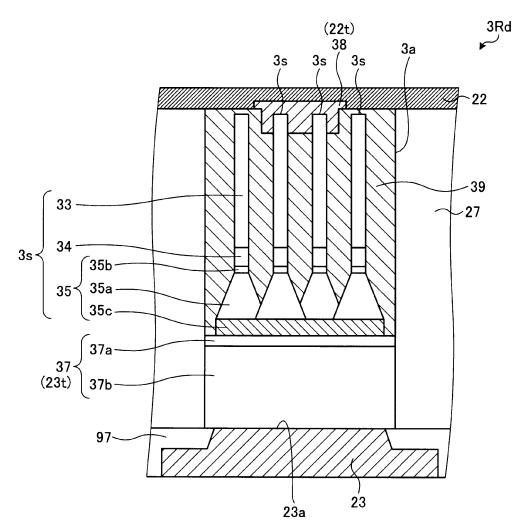

##### (第 9 変形例)

図 20 は、第 9 変形例に係る赤色発光素子を示す断面図である。図 20 に示すように、第 9 変形例の赤色発光素子 3 R d は、図 7 と同様に複数の部分発光素子 3 s を有している。赤色発光素子 3 R d の p 型クラッド層 3 5 は、第 3 p 型クラッド層 3 5 c を有する。第 3 p 型クラッド層 3 5 c は、高濃度不純物領域が形成された窒化ガリウム (P + GaN) である。第 3 p 型クラッド層 3 5 c は、第 1 p 型クラッド層 3 5 a と p 型電極 3 7 との間に設けられる。また、発光層 3 4 は、第 3 p 型クラッド層 3 5 c、第 1 p 型クラッド層 3 5 a 及び第 2 p 型クラッド層 3 5 b と、n 型クラッド層 3 3 との間に設けられる。

10

#### 【0144】

##### (第 10 変形例)

図 21 は、第 10 変形例に係る赤色発光素子を示す断面図である。図 21 に示すように、第 10 変形例の赤色発光素子 3 R e において、発光層 3 4 の第 1 発光層 3 4 a 及び第 2 発光層 3 4 b は、p 型クラッド層 3 5 の上に、この順で積層されている。第 1 発光層 3 4 a 及び第 2 発光層 3 4 b の積層の順番は逆であってもよい。

20

#### 【0145】

第 1 発光層 3 4 a は、ユウロピウム (Eu) が添加された窒化ガリウム (GaN) である。また、第 2 発光層 3 4 b は、インジウム窒化ガリウム (In<sub>x</sub>Ga<sub>(1-x)</sub>N) と窒化ガリウム (GaN) とが複数層繰り返し積層された MQW 構造である。なお、第 1 発光層 3 4 a の上に第 2 発光層 3 4 b が積層された構成に限定されず、例えば、第 6 変形例と同様に、第 2 発光層 3 4 b は、第 1 発光層 3 4 a に含まれて MQW 構造の一部を構成してもよい。

30

#### 【0146】

以上、本発明の好適な実施の形態を説明したが、本発明はこのような実施の形態に限定されるものではない。実施の形態で開示された内容はあくまで一例にすぎず、本発明の趣旨を逸脱しない範囲で種々の変更が可能である。本発明の趣旨を逸脱しない範囲で行われた適宜の変更についても、当然に本発明の技術的範囲に属する。上述した各実施形態及び各変形例の要旨を逸脱しない範囲で、構成要素の種々の省略、置換及び変更のうち少なくとも 1 つを行うことができる。

30

#### 【符号の説明】

##### 【0147】

- 1 表示装置

- 2 アレイ基板

- 3 発光素子

- 3 R、3 R a、3 R b、3 R c、3 R d、3 R e 赤色発光素子

- 3 G a 第 1 緑色発光素子

- 3 G b 第 2 緑色発光素子

- 3 B 青色発光素子

- 1 2 駆動回路

- 2 1 基板

- 4 9 R 第 1 画素

- 4 9 G a 第 2 画素

- 4 9 G b 第 3 画素

- 4 9 B 第 4 画素

- 6 1、6 5、7 1、7 1 A、7 5、7 9 半導体層

- 6 4、6 6、7 4、7 8 ゲート電極

- 6 2、7 2 ソース電極

40

50

67、73、77 ドレイン電極

61a 第1部分半導体層

210 駆動IC

100、100A 信号処理回路

110 第1処理回路

115 メモリ

120 第2処理回路

125 バッファ

DRT 駆動トランジスタ

BCT 出力トランジスタ

IST 初期化トランジスタ

SST 画素選択トランジスタ

RST リセットトランジスタ

PVDD アノード電源電位

PVSS カソード電源電位

L1 アノード電源線

L2 映像信号線

L3 リセット電源線

L4 初期化電源線

L5 リセット制御信号線

L6 出力制御信号線

L7 画素制御信号線

L8 初期化制御信号線

L9 接続配線

10

20

## 【図面】

【図1】

【図2】

30

40

50

【図3】

【 四 4 】

10

20

【 四 5 】

【 四 6 】

30

40

50

【図 7】

【図 8】

10

20

【図 9】

【図 10】

30

40

50

【図 1 1】

【図 1 2】

10

20

【図 1 3】

【図 1 4】

30

40

50

【図 1 5 A】

【図 1 5 B】

【図 1 5 C】

【図 1 6 A】

【図 1 6 B】

【図 1 6 C】

10

20

30

40

50

【図17】

【図18】

10

【図19】

【図20】

20

30

40

50

【図 2 1】

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

|                        | F I    |       |         |

|------------------------|--------|-------|---------|

| H 01 L 33/00 (2010.01) | G 09 G | 3/20  | 6 4 2 K |

| H 01 L 33/32 (2010.01) | G 09 G | 3/20  | 6 4 1 P |

|                        | H 01 L | 33/00 | L       |

|                        | H 01 L | 33/32 |         |

## (56)参考文献

特開2018-040875 (JP, A)

米国特許出願公開第2017/0191786 (US, A1)

米国特許出願公開第2016/0155376 (US, A1)

米国特許出願公開第2013/0175514 (US, A1)

韓国公開特許第10-2008-0002301 (KR, A)

国際公開第2004/072931 (WO, A1)

特開2003-315778 (JP, A)

国際公開第2016/152321 (WO, A1)

米国特許出願公開第2010/0327263 (US, A1)

## (58)調査した分野

(Int.Cl., DB名)

|        |           |

|--------|-----------|

| G 09 F | 9 / 3 0 2 |

| G 09 F | 9 / 3 3   |

| G 09 G | 3 / 3 0   |

| G 09 G | 3 / 3 2   |

| G 09 G | 3 / 2 0   |

| H 01 L | 3 3 / 0 0 |

| H 01 L | 3 3 / 3 2 |