(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5730301号

(P5730301)

(45) 発行日 平成27年6月10日(2015.6.10)

(24) 登録日 平成27年4月17日(2015.4.17)

(51) Int.Cl.

F 1

|        |         |           |

|--------|---------|-----------|

| HO 1 L | 21/8246 | (2006.01) |

| HO 1 L | 27/105  | (2006.01) |

| HO 1 L | 29/82   | (2006.01) |

| HO 1 L | 43/08   | (2006.01) |

|        |       |       |

|--------|-------|-------|

| HO 1 L | 27/10 | 4 4 7 |

| HO 1 L | 29/82 | Z     |

| HO 1 L | 43/08 | Z     |

請求項の数 12 (全 21 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2012-520673 (P2012-520673)  |

| (86) (22) 出願日 | 平成22年7月8日(2010.7.8)           |

| (65) 公表番号     | 特表2012-533190 (P2012-533190A) |

| (43) 公表日      | 平成24年12月20日(2012.12.20)       |

| (86) 國際出願番号   | PCT/US2010/041303             |

| (87) 國際公開番号   | W02011/008616                 |

| (87) 國際公開日    | 平成23年1月20日(2011.1.20)         |

| 審査請求日         | 平成25年3月21日(2013.3.21)         |

| (31) 優先権主張番号  | 12/501,902                    |

| (32) 優先日      | 平成21年7月13日(2009.7.13)         |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                          |

|-----------|------------------------------------------------------------------------------------------|

| (73) 特許権者 | 500373758<br>シーゲイト テクノロジー エルエルシー<br>アメリカ合衆国、95014 カリフォルニア州、クパチーノ、サウス・ディ・アンザ・ブルーバード、10200 |

| (74) 代理人  | 110001195<br>特許業務法人深見特許事務所                                                               |

| (72) 発明者  | チェン、ユアンカイ<br>アメリカ合衆国、94539 カリフォルニア州、フリーモント、スター・ストリート、43162                               |

| (72) 発明者  | ルー、シャオファ<br>アメリカ合衆国、55438 ミネソタ州、ブルーミントン、ブランズウィック・ロード、10650、ナンバー・312                      |

最終頁に続く

(54) 【発明の名称】 静磁場によりアシストされた抵抗性検知素子

## (57) 【特許請求の範囲】

## 【請求項 1】

装置であって、

抵抗性検知素子(RSE)を含み、前記抵抗性検知素子は、

強磁性を示し、第1の面と、前記第1の面と反対側に位置する第2の面とを有する自由層と、

前記自由層の前記第1の面側に配置され、第1の温度において実質的にゼロの正味磁気モーメントを有し、前記第1の温度から上昇した第2の温度において非ゼロの正味磁気モーメントを有するヒートアシスト領域と、

前記自由層と前記ヒートアシスト領域とに挟まれて、前記自由層を前記ヒートアシスト領域から離す第1のバリア層と、

前記自由層の前記第2の面側に配置されて、固定された磁気モーメントを有するピン止め領域と、

前記自由層と前記ピン止め領域とに挟まれて、前記自由層を前記ピン止め領域から離す第2のバリア層とを含み、

前記ヒートアシスト領域は、前記自由層の前記第1および第2の面に沿った磁気異方性を有し、

前記自由層および前記ピン止め領域は、前記ヒートアシスト領域の磁気異方性に対して垂直な磁気異方性を有する、装置。

## 【請求項 2】

10

20

前記ピン止め領域は、逆平行方向に構成された複数の固定磁性層を含む、請求項 1 に記載の装置。

【請求項 3】

読み出し動作の間、前記ピン止め領域および前記ヒートアシスト領域は、各々、実質的にゼロの正味磁気モーメントを有する、請求項 1 に記載の装置。

【請求項 4】

スピン分極された電流は、前記 R S E を单一の方向にのみ通過する、請求項 1 に記載の装置。

【請求項 5】

前記スピン分極された電流は、前記 R S E の後にスイッチングデバイスを通過する、請求項 4 に記載の装置。 10

【請求項 6】

前記ヒートアシスト領域は、少なくとも、各々が合成フェリ磁性素材からなる第 1 の合成フェリ磁性層と第 2 の合成フェリ磁性層とを含む、請求項 1 に記載の装置。

【請求項 7】

前記第 1 の合成フェリ磁性層は、前記 R S E の前記第 2 の合成フェリ磁性層よりも低いキュリー温度を有する、請求項 6 に記載の装置。

【請求項 8】

前記ヒートアシスト領域は、電流によって引き起こされた熱により、正味磁気モーメントが変化するように活性化される、請求項 1 に記載の装置。 20

【請求項 9】

前記ヒートアシスト領域は、希土類遷移金属を含む单一のフェリ磁性層を含む、請求項 1 に記載の装置。

【請求項 10】

抵抗性検知素子 ( R S E ) を含み、前記抵抗性検知素子は、

強磁性を示し、第 1 の面と、前記第 1 の面と反対側に位置する第 2 の面とを有する自由層と、

前記自由層の前記第 1 の面側に配置され、温度に応じて磁気モーメントを変化させるヒートアシスト領域と、

前記自由層と前記ヒートアシスト領域とに挟まれて、前記自由層を前記ヒートアシスト領域から離す第 1 のバリア層と、 30

前記自由層の前記第 2 の面側に配置されて、固定された磁気モーメントを有するピン止め領域と、

前記自由層と前記ピン止め領域とに挟まれて、前記自由層を前記 ピン止め領域 から離す第 2 のバリア層とを含み、

前記ヒートアシスト領域は、合成フェリ磁性素材からなる第 1 の合成フェリ磁性層を含み、

前記自由層および前記ピン止め領域は、前記ヒートアシスト領域の磁気異方性に対して垂直な磁気異方性を有し、

前記抵抗性検知素子は、第 1 の温度において実質的にゼロの正味磁気モーメントを有し、前記第 1 の温度から上昇した第 2 の温度において非ゼロの正味磁気モーメントを有する、装置。 40

【請求項 11】

前記ヒートアシスト領域は、

合成フェリ磁性素材からなる第 2 の合成フェリ磁性層と、

前記第 1 の合成フェリ磁性層と前記第 2 の合成フェリ磁性層との間の第 3 のバリア層とをさらに含み、

前記ピン止め領域は、

第 1 のピン止め層と、

第 2 のピン止め層と、 50

前記第1のピン止め層と前記第2のピン止め層との間の第4のバリア層とをさらに含む、請求項10に記載の装置。

#### 【請求項12】

温度に応じて磁気モーメントを変化させるヒートアシスト領域と、固定された磁気モーメントを有するピン止め領域と、前記ヒートアシスト領域および前記ピン止め領域に挟まれた磁気トンネル接合(MTJ)を有する抵抗性検知素子(RSE)を提供するステップと、

前記ピン止め領域および、第1の温度における前記ヒートアシスト領域が、各々、ゼロの正味磁気モーメントを有している間に、スピン分極された電流を用いて前記MTJに第1の論理状態を書込むステップと、

10

前記ピン止め領域がゼロの正味磁気モーメントを有し、前記第1の温度よりも高い第2の温度における前記ヒートアシスト領域が非ゼロの正味磁気モーメントを生成するよう 20 されている間、静磁場を用いて前記MTJに第2の論理状態を書込むステップとを備える、方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

###### 背景

データ記憶デバイスは、一般的に、速くかつ効率のよい態様でデータを記憶し、取出す 20 20 ように作動する。データの個々のビットを記憶するために、ソリッドステートメモリセルの半導体アレイを利用した記憶デバイスもある。そのようなメモリセルは、揮発性あるいは不揮発性であり得る。揮発性メモリセルは、一般的に、デバイスに作動電力が継続的に供給されている間に限ってメモリに記憶されたデータを保持する。不揮発性メモリセルは、一般的に、作動電力が供給されていなくても、メモリに記憶されたデータを保持する。

##### 【背景技術】

##### 【0002】

抵抗性検知メモリ(RSM)セルは、異なる論理状態を記憶するために異なる電気抵抗を有するように構成され得る。セルの抵抗は、読出電流を与え、セルの電圧降下に関する信号を検知することによって、読出動作の間に後で検出され得る。RSMセルの種類の例は、抵抗性ランダムアクセスメモリ(RRAM)、磁気ランダムアクセスメモリ(MRAM)およびスピン注入ランダムアクセスメモリ(STRAMまたはSTRAM)を含む。 30

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0003】

これらおよび他の種類のデバイスにおいて、電力消費量を減らし、スイッチング電流を下げ、設計を簡素なものにしつつ、能力を向上させることがしばしば望まれる。

##### 【課題を解決するための手段】

##### 【0004】

###### 要約

本発明のさまざまな実施例は、一般的に、スピン注入ランダムアクセスメモリ(STRAM)などの不揮発性メモリセルにデータを書込むための装置および関連する方法に向 40 けられる。

##### 【0005】

いくつかの実施例に従うと、抵抗性検知素子(RSE)は、ヒートアシスト領域、磁気トンネル接合(MTJ)およびピン止め領域を有する。スピン分極された電流を用いてMTJに第1論理状態が書込まれるとき、ピン止め領域およびヒートアシスト領域は、各々、実質的にゼロの正味磁気モーメントを有する。静磁場を用いてMTJに第2論理状態が書込まれるとき、ピン止め領域は実質的にゼロの正味磁気モーメントを有し、ヒートアシスト領域は非ゼロの正味磁気モーメントを有する。 50

## 【0006】

別の実施例に従うと、ヒートアシスト領域、磁気トンネル接合（M T J）およびピン止め領域を有する抵抗性検知素子（R S E）が提供される。そして、ピン止め領域およびヒートアシスト領域が、各々、ゼロの正味磁気モーメントを有している間に、スピン分極された電流を用いてM T Jに第1の論理状態が書き込まれる。そして、ピン止め領域がゼロの正味磁気モーメントを有し、ヒートアシスト領域が非ゼロの正味磁気モーメントを生成するようにされている間、静磁場を用いてM T Jに第2の論理状態が書き込まれる。

## 【0007】

本発明のさまざまな実施例を特徴付けるこれらのおよびさまざまな他の特徴および利点は、添付の図面を考慮した以下の詳細な考察を考慮することにより理解され得る。

10

## 【0008】

図面の簡単な説明

## 【図面の簡単な説明】

## 【0009】

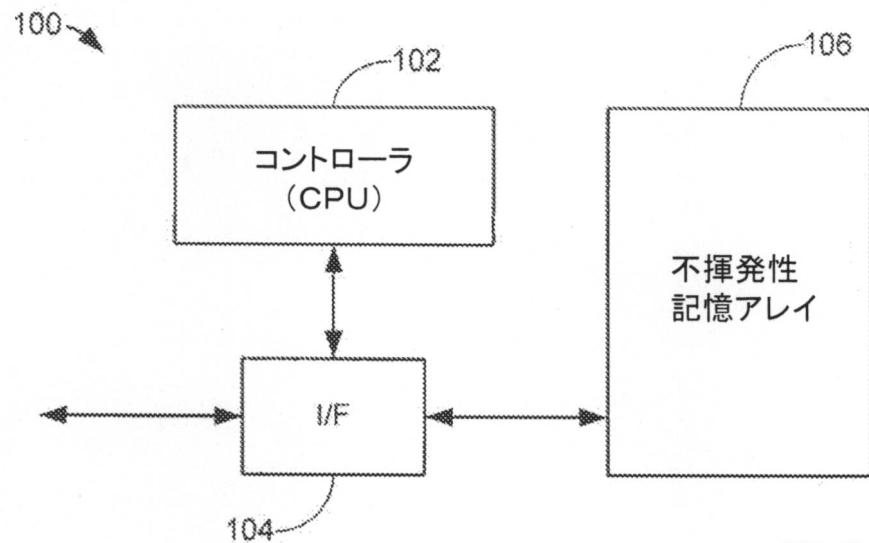

【図1】図1は、一般的に、データ記憶デバイスの機能ブロック図を示す。

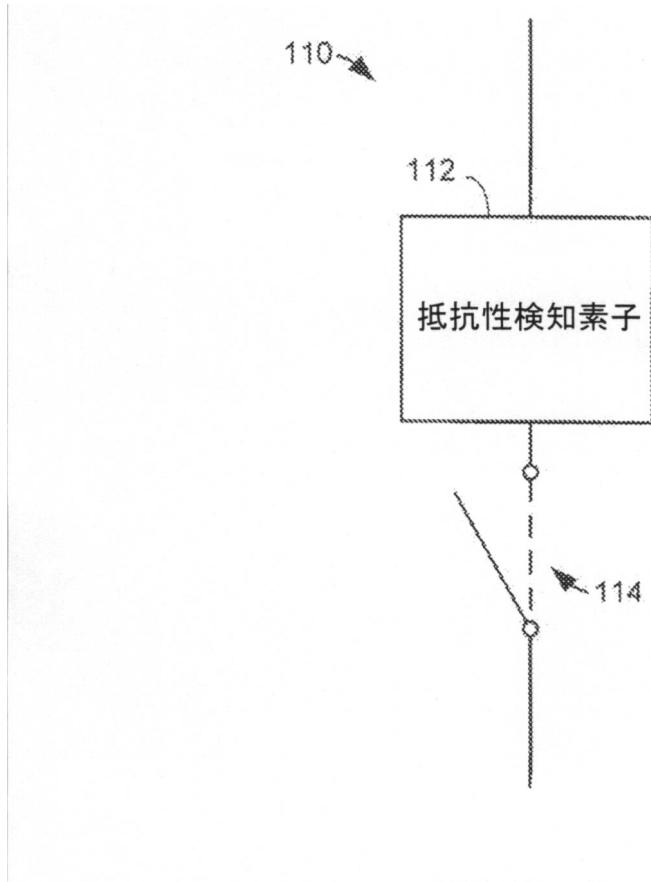

【図2】図2は、一般的に、ユニットセルの機能ブロック図を示す。

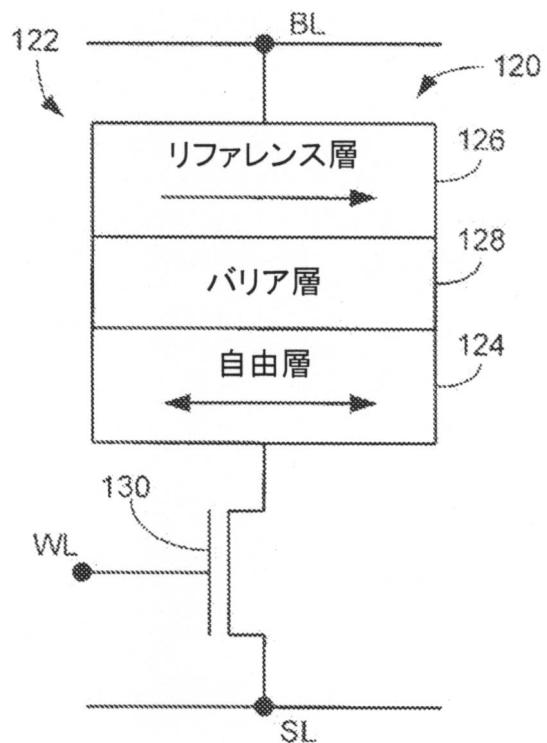

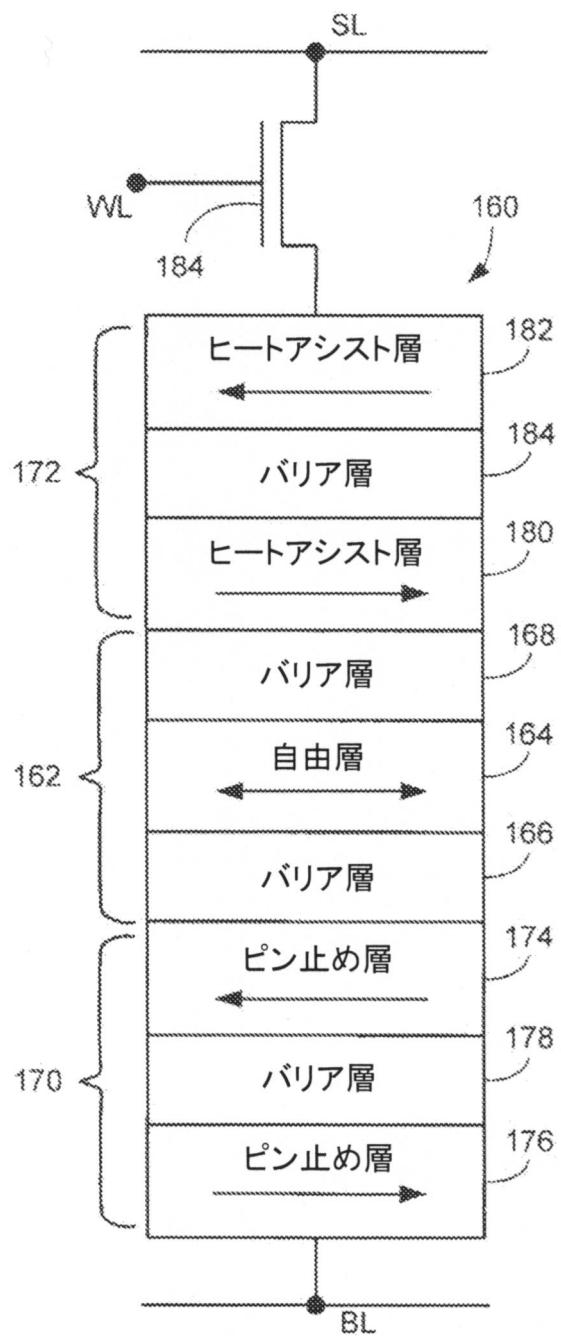

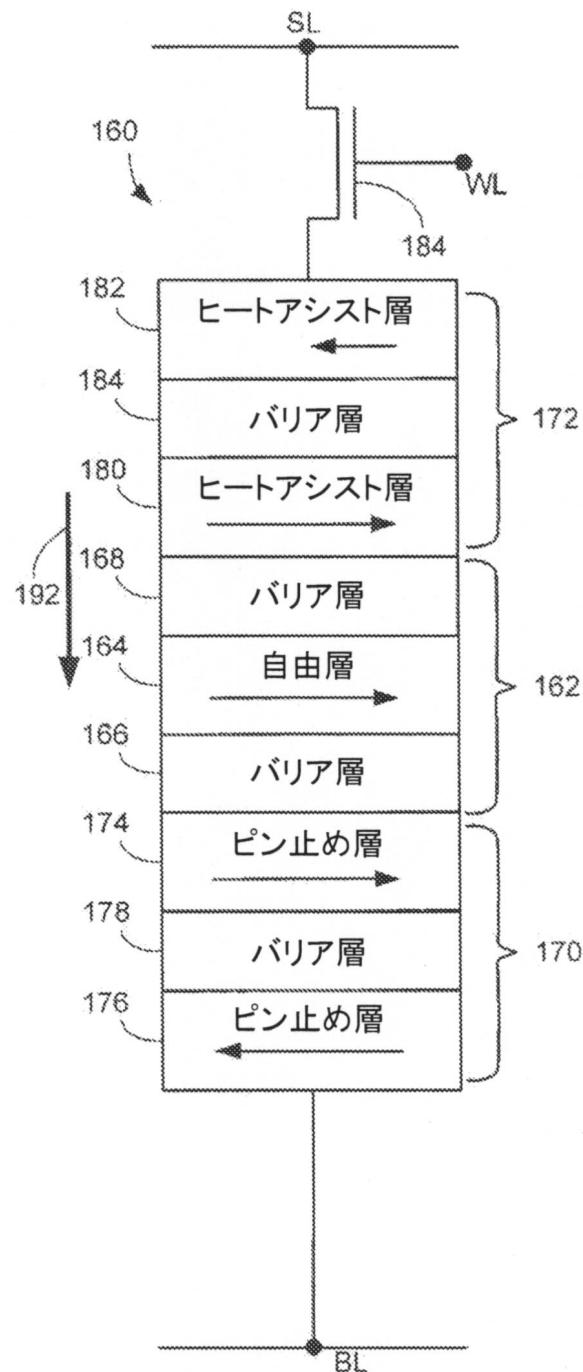

【図3】図3は、一般的に、本発明のさまざまな実施例に従って構成され、作動される、図2のメモリセルの構成を示す。

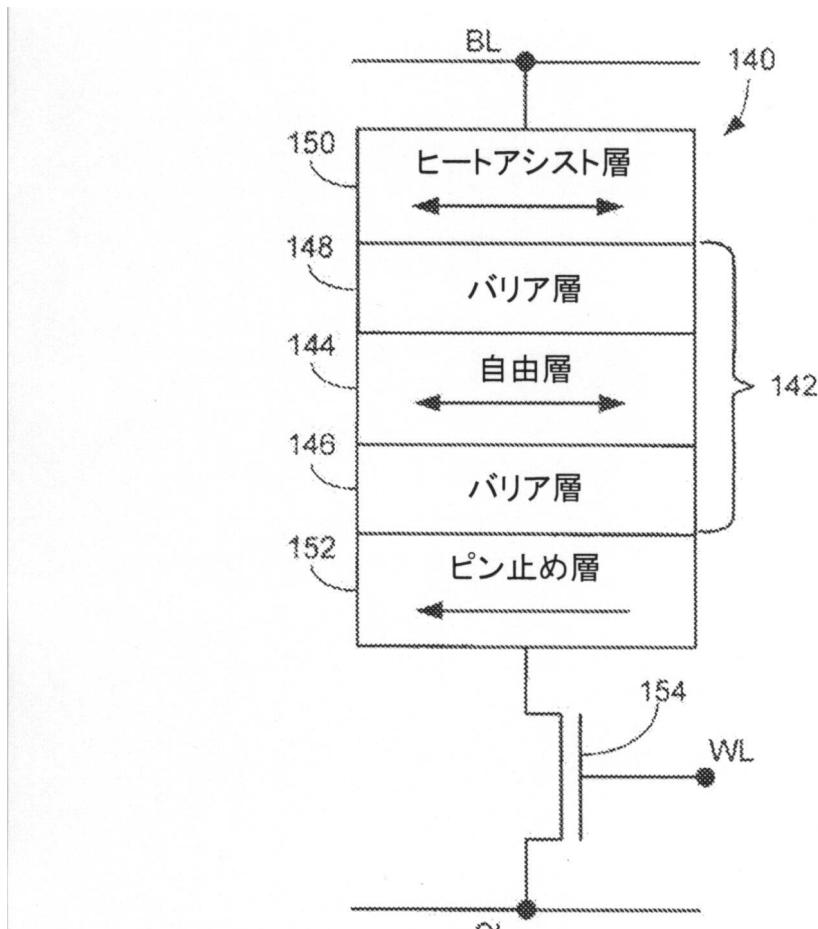

【図4】図4は、本発明のさまざまな実施例に従って構成され、動作される例示の抵抗性検知素子を表わす。

20

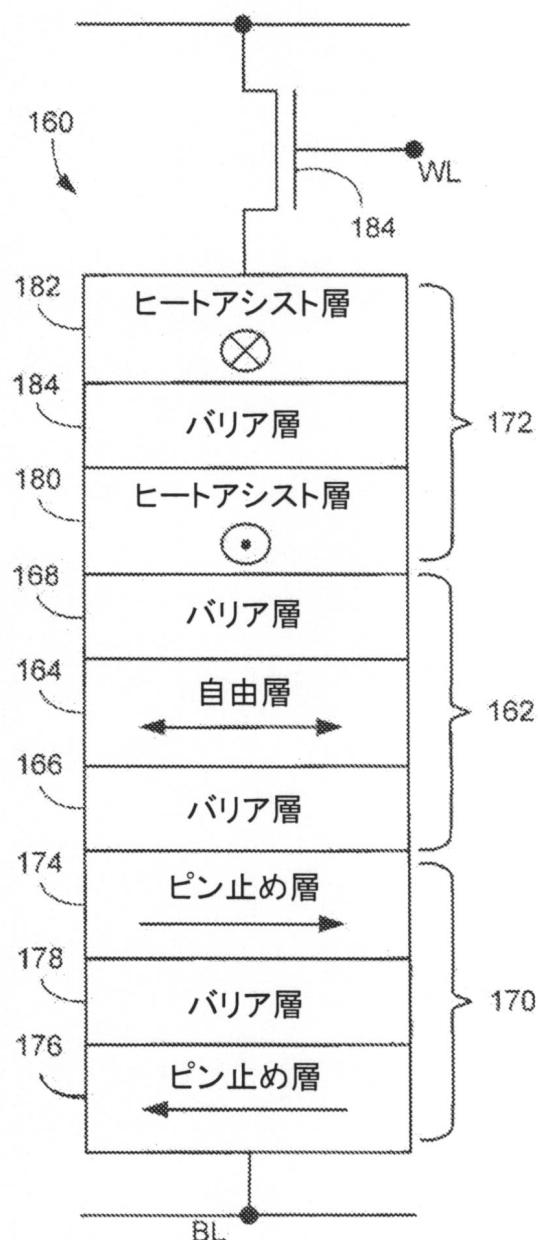

【図5】図5は、本発明のさまざまな実施例に従って構成され、動作される例示の抵抗性検知素子を示す。

【図6】図6は、本発明のさまざまな実施例に従って構成され、動作される別の例示の抵抗性検知素子を示す。

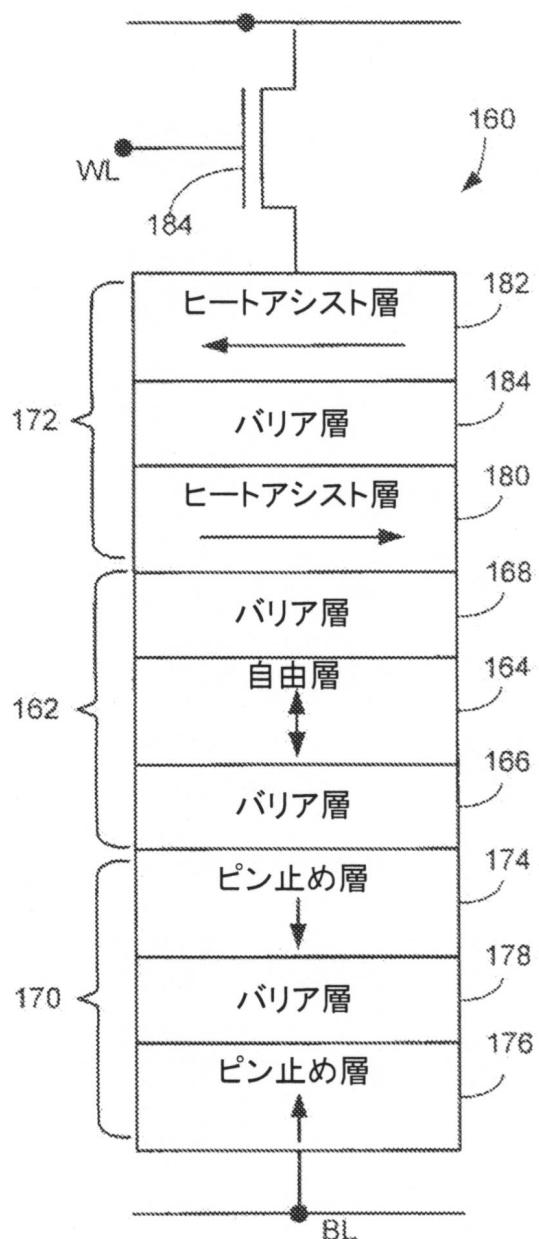

【図7】図7は、本発明のさまざまな実施例に従って構成され、動作される別の例示の抵抗性検知素子を表す。

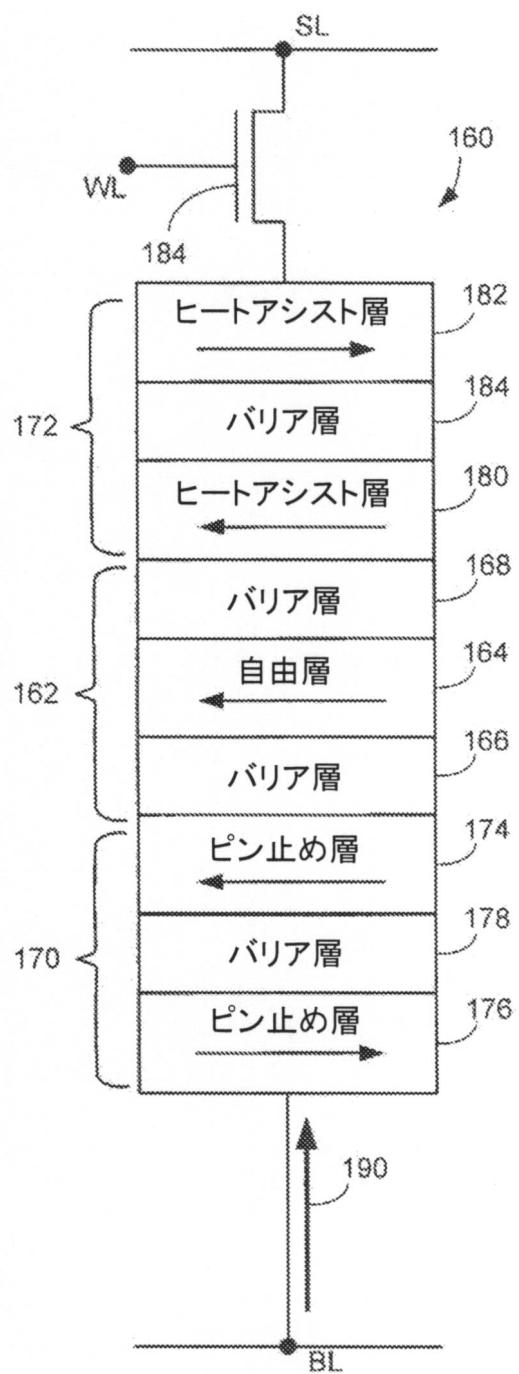

【図8】図8は、本発明のさまざまな実施例に従う抵抗性検知素子の例示の動作を一般的に示す。

【図9】図9は、本発明のさまざまな実施例に従う抵抗性検知素子の例示の動作を提供する。

30

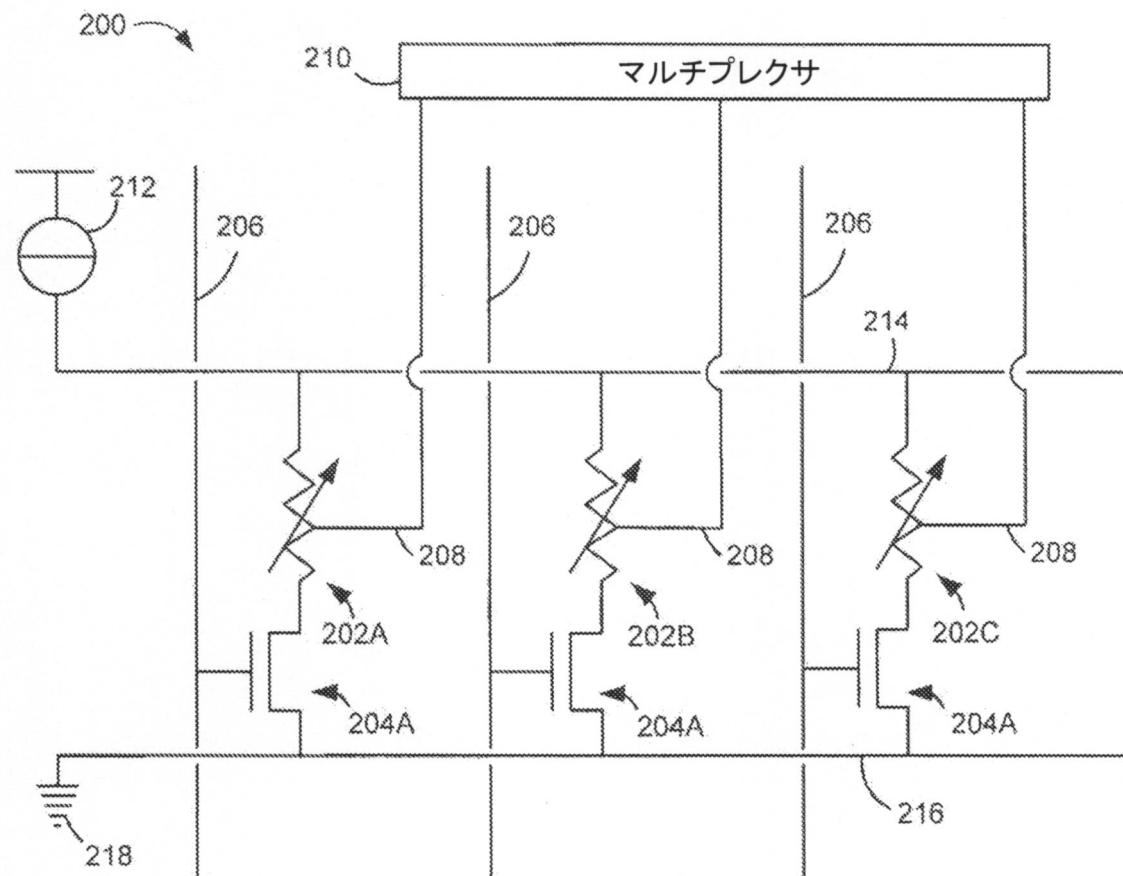

【図10】図10は、本発明のさまざまな実施例に従って構成される抵抗性検知素子の例示のアレイと、本発明のさまざまな実施例に従う動作とを表す。

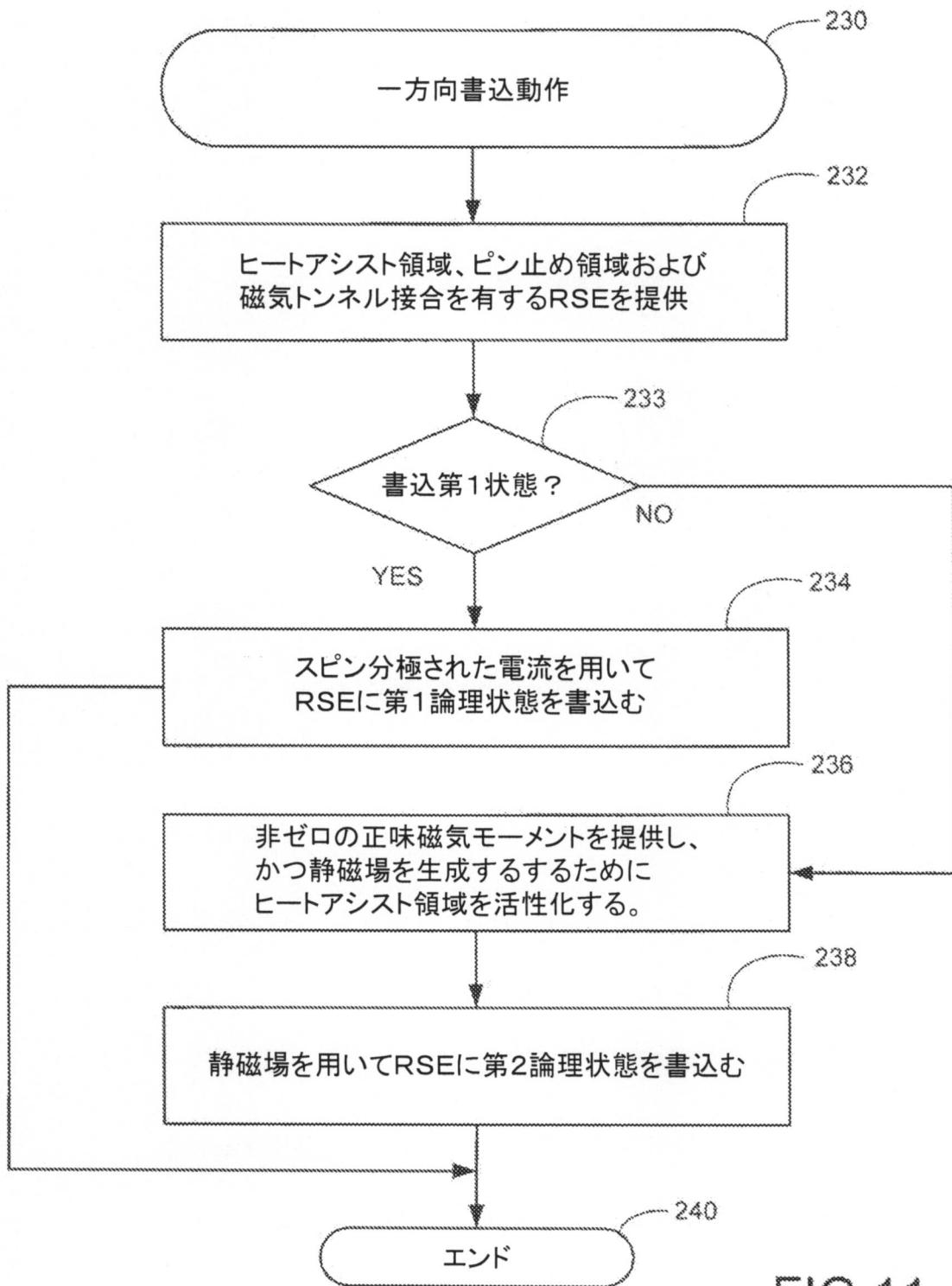

【図11】図11は、本発明のさまざまな実施例に従って実行されるステップの一般的な実例となる単極書き動作のフローチャートである。

## 【発明を実施するための形態】

## 【0010】

詳細な説明

図1は、本発明のさまざまな実施例に従って構成されて動作されるデータ記憶デバイス100の機能ブロック図を提供する。デバイス100は、トップレベルコントローラ（C P U）102、インターフェイス（I / F）回路104、不揮発性データ記憶アレイ106を含む。I / F回路104は、アレイ106とホストデバイスとの間でデータを転送するようにコントローラ102の指令の下で作動する。

40

## 【0011】

図2は、図1のアレイ106において用いられるユニットセル100構成の機能ブロック図を表す。ユニットセル110は、スイッチングデバイス114に直列に接続された抵抗性検知素子（R S E）112を有する。スイッチングデバイス114は、セルへの通電を効果的に防ぐために、図示される開位置においてユニットセル110の抵抗を増加させるように機能する。閉位置は、ユニットセル110を通る読出電流および書き電流を許容する。

## 【0012】

50

図3は、120において例示のRSE構成を示す。RSE120は、バリア層128(たとえば酸化マグネシウム、MgO)によって隔てられた2つの強磁性層124, 126から形成された磁気トンネル接合(MTJ)122を含むスピノン注入ランダムアクセスメモリ(STRAM)セルとして構成される。MTJ122の抵抗は、強磁性層124, 126の相対的な磁化方向に関連して定められる。磁化方向が同じ(平行)である場合、MTJは低抵抗状態( $R_L$ )となる。磁化方向が反対(逆平行)である場合、MTJは高抵抗状態( $R_H$ )になる。

#### 【0013】

リファレンス層126の磁化方向は、リファレンス層をピン止め磁化層(たとえば永久磁石など)に連結することによって固定される。自由層124の磁化方向は、リファレンス層126における磁化によって分極された駆動電流を通過させることにより変わり得る。

#### 【0014】

MTJ122によって記憶された論理状態を読み出すため、比較的小さい電流がソース線(SL)とビット線(BL)との間でMTJを通過させられる。論理0の状態と論理1の状態の各々におけるMTJの低抵抗と高抵抗との差により、ビットラインにおける電圧が異なり得る。ビットラインにおける電圧は適切な検知増幅器を用いて検知され得る。スイッチングデバイス130は、読み動作および書き動作の間ににおいてMTJ122への選択的なアクセスを許容する。スイッチングデバイス130は、メタルオキサイドセミコンダクタフィールドエフェクトトランジスタ(MOSFET)として特徴付けられ得る。示されるように、ワード線(WL)はトランジスタ130のゲート端子に接続される。

#### 【0015】

動作可能ではあるものの、図2, 3において示されたようなユニットセルは、非対称の書き電流特性などの欠点を有し得る。たとえば、図3におけるRSE120を逆平行高抵抗状態(ハードプログラミング方向)に設定するには、RSEを平行低抵抗状態(イージープログラミング方向)に設定するのに比べて大きな書きドライバ力が必要とされ得る。書き電流フローの方向に関する、ユニットセル内でのRSEとスイッチングデバイスの相対的な順序もそのような非対称の書き特性に寄与し得る。

#### 【0016】

したがって、本発明のさまざまな実施例は、一般的に、改善された書き特性を有する新規なメモリセル構造に向けられる。以下に説明するように、メモリセル構造は、ヒートアシスト領域を有するヒートアシスト領域、磁気トンネル接合(MTJ)、ピン止め領域を少なくとも有する抵抗性検知素子(RSE)を含む。スピノン分極された電流を用いて第1の論理状態がMTJに書き込まれている間、ピン止め領域およびヒートアシスト領域の各々は実質的にゼロの正味磁気モーメントを有する。

#### 【0017】

さらに、静磁場を用いて第2の論理状態がMTJに書き込まれているとき、ピン止め領域は実質的にゼロの正味磁気モーメントを有し、ヒートアシスト領域は非ゼロの正味磁気モーメントを有する。論理状態は、両方とも、メモリセルを同じ方向に通過する単極の書き電流を用いて書き込まれる。

#### 【0018】

図4は、さまざまな実施例に従って、図2のユニットセル110において用いることができるRSE140の例示の構成を提供する。RSE140は、自由層144と第1バリア層146と、第2バリア層148とを含む磁気トンネル接合142によって特徴付けられる。いくつかの実施例において、自由層144は、磁気極性を維持することができる強磁性素材であり、第1バリア層146および第2バリア層148は酸化バリア層である。第1酸化層146および第2酸化層148はさまざまな素材から構成され得、酸化物に限定されない。すなわち、望まれざる磁気パルスから自由層144を遮蔽するために、磁気トンネル接合142において酸化物とは別のバリア素材が用いられ得る。

#### 【0019】

10

20

30

40

50

さらに、RSE140の磁気トンネル接合142はヒートアシスト層150とピン止め層152との間に配置される。ヒートアシスト層150は、2つの対向する方向のどちらかにおけるモーメントを有する磁気極性を記憶することができる。一方、ピン止め層152は、一方向のモーメントを有する磁気極性を有する。いくつかの実施例において、磁気トンネル接合142上において正味ゼロの磁気モーメントを与えるために、ピン止め層152の磁気極性はヒートアシスト層150の磁気極性と反対である。ピン止め層152の磁気モーメントはヒートアシスト層150の磁気モーメントと反対である。

#### 【0020】

さらに、任意にRSE140を選択することを許容するためにスイッチングデバイス154もまたRSE140に接続される。RSE140に対するスイッチングデバイスの位置は限定されず、本発明の精神から逸脱しない範囲で変更され得ることが理解され得る。

10

#### 【0021】

なお、いくつかの実施例において、ヒートアシスト層150は第1の温度においてゼロの正味磁気モーメントを有するが、上昇した第2の温度において非ゼロの正味磁気モーメントを有する。図4において示されるように、ヒートアシスト層150は、希土類遷移金属等の単一の強磁性素材およびTbCoFe等のそれらの合金であり得るが、これらに限定されない。しかしながら、図5において示されるように、ヒートアシスト領域を形成するために複数のヒートアシスト層150が組合せて用いられ得る。

#### 【0022】

図5は、本発明のさまざまな実施例に従うRSE160の例示の構造を示す。自由層164と第1および第2酸化層166および168を有する磁気トンネル接合162が示され、ピン止め領域170とヒートアシスト領域172との間に配置される。ピン止め領域170は、酸化層178によって接続された第1および第2ピン止め層174および176を含む。磁気トンネル接合162にゼロの正味磁気モーメントを与えるため、ピン止め層176および178は反対の磁気モーメントを有するように構成される。

20

#### 【0023】

しかしながら、本発明の精神から逸脱しない範囲で任意の好ましい間隔素材を用いることができ、ピン止め層176とピン止め層178とを隔てる酸化素材の使用は必要ではない。同様に、第1のピン止め層176と第2のピン止め層178の特定の磁化方向は限定されず、ゼロの正味磁気モーメントを生み出す任意のさまざまな構成とすることができる。当業者はスイッチングデバイス184の位置がヒートアシスト領域172に隣接する理解することができるが、本発明の精神に弊害をもたらすことなくピン止め領域170に隣接するように配置することも可能である。

30

#### 【0024】

上述したように、ヒートアシスト領域172は、第1の温度において磁気トンネル接合162にゼロの正味磁気モーメントを与えるように構成された複数のヒートアシスト層180および182を含む。ピン止め領域170と同様に、ヒートアシスト層180および182は反対の磁気モーメントを生み出す磁気方向を有する。酸化物あるいは同種のバリア層184が磁気モーメントを隔てるためにヒートアシスト層180と182との間に配置されている。

40

#### 【0025】

そのような訳で、RSE160は、ピン止め層176およびピン止め層174の両方の磁気モーメントのバランスと、ヒートアシスト層180およびヒートアシスト層182の両方の磁気モーメントのバランスとに起因して、ゼロの正味磁気モーメントを有する。一旦自由層164が磁気極性を有すると、RSE160の磁気状態が現れ、論理状態を読み出すことができる。なお、合成フェリ磁性素材を用いて、1つの層が他のヒートアシスト層に比べて高いキュリー温度を有するように複数のヒートアシスト層が構成され得る。したがって、所定の温度において、ヒートアシスト層180および182の磁気モーメントは、ヒートアシスト領域172と同様に、温度によって望まれるように操作され得る。

#### 【0026】

50

図 6 および 7 において、本発明のさまざまな実施例に従う代替的な構成で図 5 の R S E 1 6 0 が一般的に記載される。図 6 において示されるように、ヒートアシスト層 1 8 0 およびヒートアシスト層 1 8 2 の各々の磁気モーメントは、ヒートアシスト領域 1 7 2 と同じく、磁気トンネル接合 1 6 2 およびピン止め領域 1 7 0 の磁気モーメントに対して垂直である。この構成も、第 2 の温度において自由層 1 6 4 に論理状態を書込むために要求される電流の量を大幅に下げつつ、第 1 の温度において磁気トンネル接合にゼロの正味磁気モーメントを与える。

#### 【 0 0 2 7 】

対称的に、図 7 において示されるように、ヒートアシスト領域 1 7 2 に対して垂直な異方性を有するように磁気トンネル接合 1 6 2 およびピン止め領域 1 7 0 が構成され得る。垂直な異方性にも拘らず、磁気トンネル接合 1 6 2 にもたらされる正味磁気モーメントは、第 2 の温度がヒートアシスト領域 1 7 2 に非ゼロの正味磁気モーメントを生成させ始めるまでゼロに保たれる。

#### 【 0 0 2 8 】

なお、図 6 および 7 において記載される R S E 1 6 0 の各々の領域の磁化方向は限定されない。たとえば、面内の磁化を有する、ヒートアシスト領域 1 7 2 に対して垂直な磁気モーメントをピン止め領域 1 7 0 が有する一方で、垂直な異方性を有するように磁気トンネル接合 1 6 2 が構成され得る。

#### 【 0 0 2 9 】

セルトランジスタの達成可能な最小サイズに関連するある問題が S T R A M セル（他の種類の R S E セルと同様に）について発見された。一般的に、セルトランジスタを損傷させずに書き動作を実行するのに必要な必須の書き電流密度とゲート制御電圧を受けることができるよう十分に大きくセルトランジスタを構成することが望まれる。それと同時に、トランジスタは、しばしばセルのスケーラビリティの制約要素になり得ることから、トランジスタの大きさを小さくすることにより、メモリアレイの全体的な密度を増加させることを促進することができる。

#### 【 0 0 3 0 】

関連する問題は書き電流の非対称性である。S T R A M セルは、しばしば、異なる論理状態を書込むためにセルを異なる方向に、書き電流が通過するように構成される。これは他の種類の R S E セルにとっても真実であり得る。たとえば、第 1 の方向に書き電流を適用することによってセルの抵抗を低くし、それによって第 1 の論理状態（たとえば論理 0 ）を識別する。書き電流を逆の第 2 の方向に適用することによって、セルの抵抗を高くし、それによって逆の論理状態（たとえば論理 1 ）を識別する。

#### 【 0 0 3 1 】

セルの構成に依存して、セルを一方の方向に書込むことが他方の方向に書込むことに比べて困難であり得る。複数の要因がそのような非対称性に寄与し得る。1 つの要因は、書き電流を適用する方向についての磁気トンネル接合とスイッチングデバイス素子との相対的な順番に関連する。すなわち、書き電流が磁気トンネル接合を先に通過するか、あるいはスイッチングデバイスを先に通過するかに関連する。他の要因も磁気トンネル接合（または他の可変抵抗性要素）内の構成および層の順番に関連し得る。

#### 【 0 0 3 2 】

他の要因も、磁気トンネル接合（または別の可変抵抗性素子）内の層の構成と順番に関連し得る。

#### 【 0 0 3 3 】

図 5 の例示の R S E 1 6 0 について、スイッチングデバイス 1 8 4 よりも前に磁気トンネル接合 1 6 2 に書き電流が遭遇するような方向（この方向は「イージー」方向と呼ばれる）に電流が通過するとき、磁気トンネル接合 1 6 2 の状態を書込むことが比較的容易であることが予期される。一方、書き電流が磁気トンネル接合に遭遇するよりも前にトランジスタ（ドレインソース接合）を通過する場合、反対方向（この方向は「ハード」方向と呼ばれる）に書き込むことはより困難になるであろう。

10

20

30

40

50

## 【0034】

したがって、以下に説明されるように、本発明のさまざまな実施例は、単方向かつ单極の電流と静磁場とを用いてさまざまな論理状態を RSE に書込むことを容易にするための新規の構造および技術を利用する。単一の電流、極性および方向を RSE に対して用いることにより、RSE およびユニットセルの両方の書き込み電流の非対称性を完全に避けることができる。一方、論理状態を RSE に書込むのに静磁場を用いると、向上されたユニットセルのデグラデーションに起因して、データ記憶の改善された信頼性との組合せにおいて有利な電力消費を与え得る。

## 【0035】

図 5 の RSE 160 の例示の動作を与える図 8 および 9 が参考される。図 8 において、RSE 160 はスイッチング素子（トランジスタ）184 と直列の可変抵抗として描かれる。スイッチングデバイス 184 とソース線とがヒートアシスト領域 172 と隣接して配置される一方で、ビット線はピン止め領域 170 に隣接して配置される。なお、ヒートアシスト領域 172 は、ゼロの正味磁気モーメントが生成される第 1 の温度において示される。

10

## 【0036】

ビット線からピン止め領域 170 に書き込み電流 190 が流れるとき、ピン止め領域 170 とヒートアシスト領域 172 の両方のバランスのとれた磁気モーメントに起因して、RSE 160 はゼロの正味磁気モーメントを有する。いくつかの実施例において、磁気トンネル接合 162 の自由層 164 の磁気方向を第 1 の極性にするために書き込み電流 190 が RSE 160 を通過するとき、書き込み電流 190 はスピン分極される。セットの大部分は、所定の論理状態に対応する、RSE 160 についての関連付けられた抵抗を有する。書き込み電流 190 が RSE 160 、スイッチングデバイス 184 およびソース線を通過した後、磁気モーメントに関してヒートアシスト領域 172 の磁気モーメントとピン止め領域 170 の磁気モーメントとはバランスがとれたままであるため、RSE 160 は自由層 164 からの一般的な磁気モーメントを被る。

20

## 【0037】

第 2 の論理状態を RSE 160 に書込むため、図 9 は、静磁場 192 の生成と機能を記載する。RSE 160 に第 2 の論理状態を書込むことが望まれる場合、ヒートアシスト領域 172 が第 2 の温度まで加熱され、ヒートアシスト層 180 またはヒートアシスト層 182 のいずれか一方が修正された磁気モーメントを有する。ヒートアシスト領域 172 における磁気モーメントのバランスが崩れることにより、非ゼロの正味磁気モーメントと、磁気トンネル接合 162 の自由層 164 の極性を第 2 の論理状態に切換えるのに十分に強い静磁場とを生み出す。

30

## 【0038】

なお、静磁場 192 の生成と利用の間ににおいて、ピン止め領域 170 はゼロの正味磁気モーメントでバランスがとれたままである。ピン止め領域 170 のゼロの正味磁気モーメントにより、もしピン止め領域 170 の磁気モーメントが補われる必要があったとしたならば要求されるであろう強度よりも小さい強度で静磁場が自由層 164 の磁気極性を変えることができる。

40

## 【0039】

結果として、RSE 160 のさまざまな領域の正味ゼロの磁気モーメントにより、信頼性、能力および電力消費を改善することができる。单極性かつ一方向の書き込み電流を使用することにより、書き込み電流の非対称性を補うためにしばしば要求される複雑性を大幅に低減できる。一方、静磁場の使用によって、双方向の書き込み電流では実現し得なかった精度と低い電力消費を提供することができる。

## 【0040】

さらにまた、ヒートアシスト領域 172 を第 2 の温度まで加熱する態様は限定されない。すなわち、ヒートアシスト領域 172 の温度を上昇させ、静磁場を生成するのにさまざまな構成要素または手法が用いられ得る。さらに、ヒートアシスト領域 172 の温度を上

50

昇させるのに R S E 1 6 0 全体に電流を通過させることは要求されない。たとえば、ヒートアシスト領域 1 7 2 は、磁気トンネル接合 1 6 2 およびピン止め領域 1 7 0 から独立して加熱され得る。したがって、ヒートアシスト領域 1 7 2 の制御および操作は、非ゼロの正味磁気モーメントを生み出し、静磁場に関連したさまざまな態様において促進され得る。

【 0 0 4 1 】

抵抗性検知素子に論理状態を書込むのに双方向の書き込み電流を使用すると、高い電流消費、損なわれた信頼性、および複雑な書き込み電流非対称性補償回路などの多くの不利益があることが理解され得る。実際、反対方向に書き込み電流を抵抗性検知素子に通過させることの不正確さおよび不一致性を考慮すると、双方向の書き込み電流を使用することには利益よりも多くの不利益がある。

10

【 0 0 4 2 】

したがって、本発明のさまざまな実施例は、一般的に、単極および一方向の書き込み電流の間は実質的にゼロの正味磁気モーメントを有するが、抵抗性検知素子に論理状態を書込むために静磁場が用いられるときに非ゼロの正味磁気モーメントを有する特定の領域を有する、正確かつ信頼性の高い抵抗性検知素子を提供するように動作する。抵抗性検知素子を反対方向に通過する書き込み電流の代わりに静磁場を用いることにより、電力消費を下げつつよりよい能力を得ることができる。

【 0 0 4 3 】

前述の特徴および利点を説明するために図 1 0 により例示の実施例が説明される。図 1 0 は、半導体アレイに配置された、図 5 から 9 によって説明されたような抵抗性検知素子のアレイ 2 0 0 を示す。より具体的には、図 1 0 は、関連付けられたスイッチングデバイス（トランジスタ）2 4 0 A - C を各々が有する、2 0 2 A - 2 0 2 C で記された 3 つの S T R A M セルを記す。スイッチング素子は各々、望まれるとおりに特定の 1 つあるいはそれ以上の抵抗性検知素子を選択することができるワード線 2 0 6 に接続されかつワード線 2 6 0 によって制御される。

20

【 0 0 4 4 】

そのようなセルの任意の数の列および行を有するようにアレイを拡張することができることが予期され、そのため、図 7 における単純な 2 × 2 アレイは単なる説明の目的のためだけのものであり限定されない。アレイ上のワード線、ビット線およびソース線のさまざまな方向も例示に過ぎず、任意に配向され得る。抵抗性検知素子 2 0 2 A - C の各々は、マルチプレクサ 2 1 0 に連結されたヒートアシスト線 2 0 8 にも接続される。ヒートアシスト線 2 0 8 は、電流を抵抗性検知素子の全体に通過させずに、抵抗性検知素子のヒートアシスト領域が第 1 の温度から第 2 の温度に加熱されることを許容する。

30

【 0 0 4 5 】

しかしながら、ヒートアシスト線 2 0 8 の構成は限定されず、1 つのヒートアシスト線 2 0 8 は、任意の数の抵抗性検知素子に接続されることができる。同様に、マルチプレクサ 2 1 0 の数および位置は図 1 0 に示される構成に限定されない。たとえば、マルチプレクサ 2 1 0 は、抵抗性検知素子の各々の行または列に対して実装され得る。

【 0 0 4 6 】

40

動作中、アレイ 2 0 0 は、抵抗性検知素子 2 0 2 A - C の各々あるいはすべてに対してドライバ 2 1 0 から電圧を供給できる。いくつかの実施例において、各々の望まれたスイッチングデバイス 2 0 4 A - C 上のゲートをワードライン 2 0 6 に動作させることによって選択された所定の数の抵抗性検知素子 2 0 2 A - C にビット線 2 1 4 を通って供給される電圧をドライバ 2 1 2 は生成する。抵抗性検知素子を通った後、電圧は、グランド 2 1 8 までソース線 2 1 6 を通過し得る。

【 0 0 4 7 】

なお、抵抗性検知素子 2 0 2 A - C の静磁場書き込み能力により、反対方向（ソース線からビット線）に電流を抵抗性検知素子に通過させることができる第 2 の電圧ドライバは必要でない。しかしながら、ビット線 2 1 4 上に位置するドライバ 2 1 2 の構成は限定されず

50

、本発明の精神から逸脱しない範囲で、ドライバ 212 とグランド 218 の位置を逆にすることができる。

【0048】

図 11 は、一方向書込動作 230 のフローチャートを提供し、一般的に、本発明のさまざまな実施例に従って実行されるステップの実例となり得る。ステップ 232 にて、少なくともヒートアシスト領域、ピン止め領域および磁気トンネル接合を有する抵抗性検知素子 (RSE) が提供される。ステップ 234 にて、スピン分極された電流を用いて第 1 の論理状態が RSE に書き込まれる。いくつかの実施例において、ヒートアシスト領域の温度は、実質的にゼロの正味磁気モーメントが生成される第 1 の温度である。同様に、ステップ 234 の間、ピン止め領域はゼロの正味磁気モーメントを有するものとして特徴付けられる。

10

【0049】

その後、非ゼロの正味磁気モーメントを与え、静磁場を生成するように、ステップ 236 において RSE のヒートアシスト領域が活性化される。ステップ 238 において、静磁場は、RSE に第 2 の論理状態を書込むように RSE の磁気トンネル接合をマイグレートする。そしてルーチンはステップ 240 において終了する。

【0050】

一方向書込動作 230 のさまざまなステップは限定されるものではなく、ステップは省略されたり、任意の数だけ繰返されたりし得る。すなわち、第 2 の論理状態を書込むことなく第 1 の論理状態が RSE に繰返し書き込まれたり、その逆もあり得る。

20

【0051】

上記に説明したさまざまな実施例は、セルの抵抗性検知素子およびスイッチングデバイスの相対的な連続順序に基づいてハード方向およびイージー方向を識別するが、それは必ずしも限定されない。むしろ、さまざまなメモリセル構成は、代替的に、いくつかの別のセルの特徴に基づいて「イージー」および「ハード」方向を有し得ることが予期される。ここで開示されたさまざまな実施例は、セルの信頼性を損なわずに読出電流の対称性を得ることに関して、他の種類のメモリセルと同様に、同等に適していることが理解されるであろう。

【0052】

当業者に理解されるように、ここで説明されたさまざまな実施例は、速くかつ信頼性のある態様でデータを抵抗性検知素子に有利に書込むことをもたらす。单一の一方向書込電流を用いてさまざまな抵抗状態を書込む能力によって、電力消費を上げない一貫したデータ書込が可能となる。静磁場を用いて論理状態を抵抗性検知素子に書込むことにより、任意の電子データ記憶デバイスの効率と複雑性とを大幅に改善することができる。さらに、静磁場書込の動的性質は、書込電流駆動能力に関する増大された能力をもたらす。しかしながら、ここで述べられたさまざまな実施例は無数の潜在的なアプリケーションを有し、特定の電子メディアの分野あるいはデータ記憶デバイスの種類に限定されないことが理解されるであろう。

30

【0053】

上記の説明において本発明のさまざまな実施例の多数の特徴と利点が説明されたが、発明のさまざまな実施例の構成と機能との詳細と共に説明されたが、この詳細な説明は説明のためだけのものであり、詳細において、特に部品の構成および配置に関して、添付の特許請求の範囲に表わされた用語の広い一般的な意味によって示される最大の範囲で本発明の原則内で変更がなされ得ることが理解される。

40

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【 图 5 】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10】

FIG.10

【図11】

FIG.11

---

フロントページの続き

(72)発明者 シー , ハイウェン

アメリカ合衆国、95120 カリフォルニア州、サン・ノゼ、チコリー・コート、1111

(72)発明者 タン , マイケル

アメリカ合衆国、55438 ミネソタ州、ブルーミントン、ウェスト・ナインティフィフス・ストリート、7850

審査官 上田 智志

(56)参考文献 国際公開第2009/078202 (WO, A1)

特表2011-507243 (JP, A)

国際公開第2010/021213 (WO, A1)

特開2008-028362 (JP, A)

米国特許出願公開第2008/0291721 (US, A1)

(58)調査した分野(Int.Cl. , DB名)

H01L 21/8246 ,

27/105 , 27/22 ,

29/82 ,

43/00 - 43/14