(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-245431

(P2008-245431A)

(43) 公開日 平成20年10月9日(2008.10.9)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

H02M 3/155

テーマコード(参考)

B

H

5 H 7 3 0

H

審査請求 未請求 請求項の数 10 O L (全 19 頁)

(21) 出願番号

特願2007-82596 (P2007-82596)

(22) 出願日

平成19年3月27日 (2007.3.27)

(71) 出願人 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100117385

弁理士 田中 裕人

(74) 代理人 100098431

弁理士 山中 郁生

(72) 発明者 長谷川 守仁

愛知県春日井市高蔵寺町二丁目1844番

2 富士通ヴィエルエスアイ株式会社内

F ターム(参考) 5H730 AA04 AA20 AS01 BB13 BB57

DD04 DD28 FD01 FF01 FG05

FV05 FV09 XC14 XC16 XX03

XX04 XX37 XX44

(54) 【発明の名称】 DC - DC コンバータ、電源供給方法および電源供給システム

## (57) 【要約】

【課題】 起動時のソフトスタート動作をディジタル制御により行なう場合に、ソフトスタート時間の調整や変更を、回路構成の変更を必要とすることなく柔軟に行なうことが可能なDC - DCコンバータ、電源供給方法および電源供給システムを提供すること

【解決手段】 DC - DCコンバータ1は、メインスイッチングトランジスタFET1と同期整流トランジスタFET2とのONとOFFとを制御するPWM制御部PWM1とを備えたDC - DCコンバータ1において、周波数信号FOSC1を分周して分周周波数信号を出力する分周器DIV1と、分周周波数信号と加算値入力端子A[6:0]の信号とに基づいて加算動作する加算器AC1と加算器AC1の出力に基づいてソフトスタート用信号を生成するDAコンバータDA1と、を備えることを特徴とする。

【選択図】 図1

第1実施形態にかかるDC-DCコンバータの構成を示す回路図

## 【特許請求の範囲】

## 【請求項 1】

ソフトスタート用信号を入力するための入力部を備え出力電圧信号と基準電圧信号との差を増幅して出力する誤差増幅器と、前記誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングトランジスタとのONとOFFとを制御するPWM制御回路とを備えたDC-DCコンバータにおいて、

周波数信号を分周して分周周波数信号を出力する分周器と、

前記分周周波数信号と制御信号とに基づいて加算動作するアキュムレータと、

前記アキュムレータの出力に基づいて前記ソフトスタート用信号を生成するDAコンバータと、

を備えることを特徴とするDC-DCコンバータ。

## 【請求項 2】

前記アキュムレータは、加算値としての前記制御信号に基づいてソフトスタート時間を制御すること

を特徴とする請求項1に記載のDC-DCコンバータ。

## 【請求項 3】

前記アキュムレータは、前記制御信号の値が増加すると前記ソフトスタート時間を短くする制御を行うこと

を特徴とする請求項2に記載のDC-DCコンバータ。

## 【請求項 4】

ソフトスタート時間は、

$$(V_{ref}/AN * V_{dac}) \times N / fosc$$

$V_{ref}$ ：基準電圧、AN：制御信号、 $V_{dac}$ ：DAコンバータの分解能、

N：分周比、 $fosc$ ：周波数信号、

で設定されることを特徴とする請求項1乃至請求項3の何れかに記載のDC-DCコンバータ。

## 【請求項 5】

前記アキュムレータは、リセット信号に基づいてソフトスタートをリセットすることを特徴とする請求項1乃至請求項4の何れかに記載のDC-DCコンバータ。

## 【請求項 6】

前記ソフトスタート信号が所定値になると、前記アキュムレータは前記DAコンバータに出力する信号を一定値にすること

を特徴とする請求項1乃至請求項5の何れかに記載のDC-DCコンバータ。

## 【請求項 7】

CPUと、

ソフトスタート用信号を入力するための入力部を備え出力電圧信号と基準電圧信号との差を増幅して出力する誤差増幅器と、該誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングトランジスタとのONとOFFとを制御するPWM制御回路とを備えたDC-DCコンバータと、

を有する電源供給システムにおいて、

前記DC-DCコンバータは、

周波数信号を分周して分周周波数信号を出力する分周器と、

前記CPUから供給される制御信号と前記分周周波数信号とに基づいて動作するアキュムレータと、

前記アキュムレータの出力に基づいて前記ソフトスタート用信号を生成するDAコンバータと、

を備えることを特徴とする電源供給システム。

## 【請求項 8】

基準電圧信号又はソフトスタート信号の低電位側の信号と出力電圧信号との誤差を増幅し、前記誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングト

10

20

30

40

50

ランジスタとのONとOFFとをPWM制御する制御を行って、前記出力電圧信号を出力する電源供給方法において、

周波数信号を分周して分周周波数信号を出力し、

前記分周周波数信号に基づいて設定信号の累積加算を行い、

前記累積加算結果に基づいて前記ソフトスタート用信号を生成することを備えることを特徴とする電源供給方法。

【請求項 9】

第1ソフトスタート用信号を入力するための入力部を備え第1の出力電圧信号と第1基準電圧信号との差を増幅して出力する第1の誤差増幅器と、

第2ソフトスタート用信号を入力するための入力部を備え第2の出力電圧信号と第2基準電圧信号との差を増幅して出力する第2の誤差増幅器と、

前記第1の誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングトランジスタとのONとOFFとを制御する第1のPWM制御回路と、

前記第2の誤差増幅器の出力を用いて第3スイッチングトランジスタと第4スイッチングトランジスタとのONとOFFとを制御する第2のPWM制御回路と、

を備えたDC-DCコンバータにおいて、

周波数信号を分周して分周周波数信号を出力する分周器と、

前記分周周波数信号と第1の制御信号とにに基づいて加算動作する第1のアキュムレータと、

前記分周周波数信号と第2の制御信号とにに基づいて加算動作する第2のアキュムレータと、

前記第1のアキュムレータの出力に基づいて前記第1のソフトスタート用信号を生成する第1のDAコンバータと、

前記第2のアキュムレータの出力に基づいて前記第2のソフトスタート用信号を生成する第2のDAコンバータと、

を備えることを特徴とするDC-DCコンバータ。

【請求項 10】

CPUと、

第1ソフトスタート用信号を入力するための入力部を備え第1の出力電圧信号と第1基準電圧信号との差を増幅して出力する第1の誤差増幅器と、

第2ソフトスタート用信号を入力するための入力部を備え第2の出力電圧信号と第2基準電圧信号との差を増幅して出力する第2の誤差増幅器と、

前記第1の誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングトランジスタとのONとOFFとを制御する第1のPWM制御回路と、

前記第2の誤差増幅器の出力を用いて第3スイッチングトランジスタと第4スイッチングトランジスタとのONとOFFとを制御する第2のPWM制御回路と、

周波数信号を分周して分周周波数信号を出力する分周器と、

前記CPUから供給される第1の制御信号と前記分周周波数信号とにに基づいて加算動作する第1のアキュムレータと、

前記CPUから供給される第2の制御信号と前記分周周波数信号とにに基づいて加算動作する第2のアキュムレータと、

前記第1のアキュムレータの出力に基づいて前記第1のソフトスタート用信号を生成する第1のDAコンバータと、

前記第2のアキュムレータの出力に基づいて前記第2のソフトスタート用信号を生成する第2のDAコンバータと、

を備えることを特徴とする電源供給システム。

【発明の詳細な説明】

【技術分野】

10

20

30

40

50

## 【0001】

本発明は、スイッチング電源のソフトスタート動作時の制御を行うDC-DCコンバータおよび電源供給システムに関するものであり、特に、多チャネルスイッチング電源に対してディジタル制御によりソフトスタート動作が行なわれる際のソフトスタート時間の調整を行なうDC-DCコンバータ、電源供給方法および電源供給システムに関するものである。

## 【背景技術】

## 【0002】

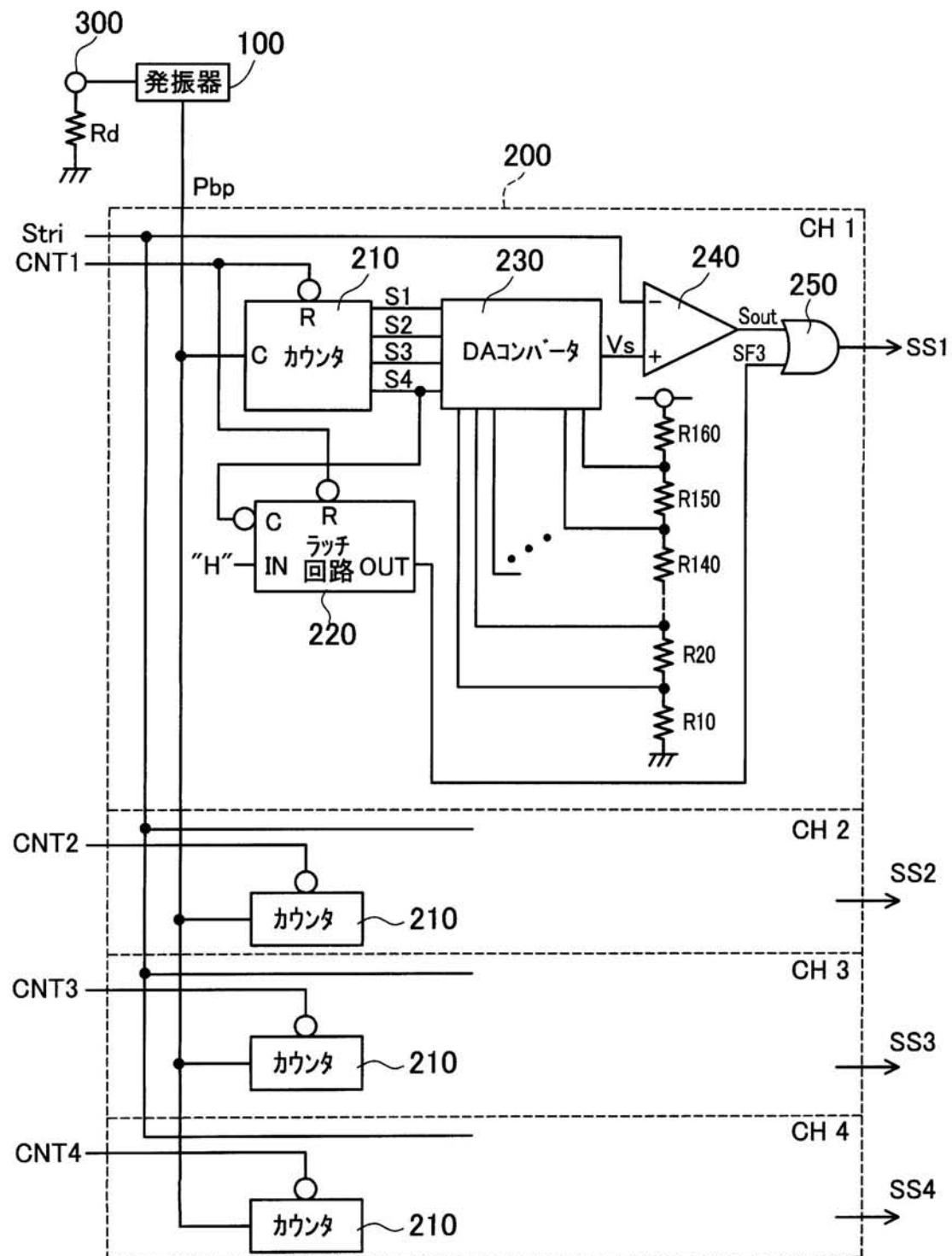

特許文献1に開示されている多チャネル電源回路装置を図5に示す。発振器100は、ソフトスタート設定端子300に接続した抵抗Rdの抵抗値に応じた発振周期で基本パルスPbpを生成する。カウンタ回路210は、発振器100から基本パルスPbpが入力され、そのパルス数を計数することによって、4ビットのディジタル信号S1～S4をカウントアップするものである。DAコンバータ230は、カウンタ回路210から入力されるディジタル信号S1～S4を、16段階に抵抗分圧されたアナログ信号Vsに変換して出力するものである。16の抵抗R1～R16の直列抵抗回路が用いられる。アナログ信号Vsは、4ビットのディジタル信号S1～S4に応じて順次1段階ずつ切り替えられ、逐次に上昇する電圧信号として出力される。これにより、ソフトスタート動作が行われる。

10

## 【0003】

なお、ソフトスタート回路に関するその他の関連技術として、特許文献2および3が開示されている。

20

## 【0004】

【特許文献1】特開2004-23948号公報

【特許文献2】特開2006-288054号公報

【特許文献3】特開2004-173386号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0005】

上記に記載した特許文献1では、ソフトスタート時間を規定して逐次に上昇するアナログ信号Vsの時間傾きは、カウンタ回路210から出力されるディジタル信号S1～S4のビット数に応じて可変とすることは可能ではある。

30

## 【0006】

DAコンバータ230では、通常、後段回路などの整合性から、出力されるアナログ信号Vsの、最小電圧値および最大電圧値は予め定められた電圧値に設定される。入力されるディジタル信号は、最小電圧値から最大電圧値に至るまでの間を、ディジタル信号の論理レベルの組合せ数で均等に分割して得られる電圧値に対応させてアナログ信号にDA変換される。発振器100で生成される基本パルスPbpの発振周期が一定であれば、ディジタル信号を構成するビット数が少数ビットであるほど、アナログ信号Vsが最小電圧値から最大電圧値に至るまでの時間が短くなり、時間傾きは急になる。これにより、ソフトスタート時間は短くなる。

40

## 【0007】

例えば、ディジタル信号が4ビットで構成されれば、アナログ信号Vsは、16段階で最小電圧値から最大電圧値に至る。また、ディジタル信号が5ビットで構成されれば、アナログ信号Vsは、32段階で最小電圧値から最大電圧値に至る。一定の発振周期で基本パルスPbpが生成されれば、最小電圧値から最大電圧値に至る段階数がより少ない段階数である4ビット構成のディジタル信号の場合に、アナログ信号Vsは急な傾きで電圧上昇する。

## 【0008】

このため、特許文献1においてソフトスタート時間を調整するためには、カウンタ回路210でカウントされるディジタル信号のビット数を調整しなければならない。加えて、

50

調整されたディジタル信号のビット数に応じて、D A コンバータ 230 では、ディジタル信号からアナログ信号 V<sub>s</sub> に D A 変換する電圧値も変更しなければならない。ソフトスタート時間の調整に応じて、カウンタ回路 210 および D A コンバータ 230 の回路構成を変更しなければならず、実使用状態でのソフトスタート時間の調整、変更が困難になるおそれがあり問題である。また、実使用状態でのソフトスタート時間の調整、変更を可能とするためには、カウンタ回路 210 および D A コンバータ 230 の回路構成の切り替えや変更を可能としなければならず、回路規模の増大を招来するおそれがあり問題である。

#### 【0009】

本発明は前記背景技術に鑑みなされたものであり、起動時のソフトスタート動作をディジタル制御により行なう場合に、ソフトスタート時間の調整や変更を、回路構成の変更を必要とすることなく柔軟に行なうことが可能な D C - D C コンバータ、電源供給方法および電源供給システムを提供することを目的とする。

10

#### 【課題を解決するための手段】

#### 【0010】

その解決手段は、ソフトスタート用信号を入力するための入力部を備え出力電圧信号と基準電圧信号との差を増幅して出力する誤差増幅器と、前記誤差増幅器の出力を用いて第 1 スイッチングトランジスタと第 2 スイッチングトランジスタとの ON と OFF とを制御する P W M 制御回路とを備えた D C - D C コンバータにおいて、周波数信号を分周して分周周波数信号を出力する分周器と、前記分周周波数信号と制御信号とに基づいて加算動作するアキュムレータと前記アキュムレータの出力に基づいて前記ソフトスタート用信号を生成する D A コンバータと、を備えることを特徴とする D C - D C コンバータである。

20

#### 【0011】

また、他の解決手段は、C P U と、ソフトスタート用信号を入力するための入力部を備え出力電圧信号と基準電圧信号との差を増幅して出力する誤差増幅器と、該誤差増幅器の出力を用いて第 1 スイッチングトランジスタと第 2 スイッチングトランジスタとの ON と OFF とを制御する P W M 制御回路とを備えた D C - D C コンバータと、を有する電源供給システムにおいて、前記 D C - D C コンバータは、周波数信号を分周して分周周波数信号を出力する分周器と、前記 C P U から供給される制御信号と前記分周周波数信号とに基づいて動作するアキュムレータと前記アキュムレータの出力に基づいて前記ソフトスタート用信号を生成する D A コンバータと、を備えることを特徴とする電源供給システムである。

30

#### 【0012】

またさらに、他の解決手段は、基準電圧信号又はソフトスタート信号の低電位側の信号と出力電圧信号との誤差を増幅し、前記誤差増幅器の出力を用いて第 1 スイッチングトランジスタと第 2 スイッチングトランジスタとの ON と OFF とを P W M 制御する制御を行って、前記出力電圧信号を出力する電源供給方法において、周波数信号を分周して分周周波数信号を出力し、前記分周周波数信号に基づいて設定信号の累積加算を行い、前記累積加算結果に基づいて前記ソフトスタート用信号を生成することを備えることを特徴とする電源供給方法である。

30

#### 【0013】

本発明では、分周周波数信号ごとに制御信号の値が順次加算され、アキュムレータの出力に基づく値が D A 変換されて順次増加するソフトスタート用信号が出力される。さらに、このソフトスタート用信号により、D C - D C コンバータの出力電圧が制御される。

40

これにより、起動時のソフトスタート動作をディジタル制御により行なう場合に、ソフトスタート時間の調整や変更を、回路構成の変更を必要とすることなく柔軟に行なうことが可能となる。

#### 【0014】

また、他の解決手段は、第 1 ソフトスタート用信号を入力するための入力部を備え第 1 の出力電圧信号と第 1 基準電圧信号との差を増幅して出力する第 1 の誤差増幅器と、第 2 ソフトスタート用信号を入力するための入力部を備え第 2 の出力電圧信号と第 2 基準電圧

50

信号との差を増幅して出力する第2の誤差増幅器と、前記第1の誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングトランジスタとのONとOFFとを制御する第1のPWM制御回路と、前記第2の誤差増幅器の出力を用いて第3スイッチングトランジスタと第4スイッチングトランジスタとのONとOFFとを制御する第2のPWM制御回路と、を備えたDC-DCコンバータにおいて、周波数信号を分周して分周周波数信号を出力する分周器と、前記分周周波数信号と第1の制御信号とに基づいて加算動作する第1のアキュムレータと、前記分周周波数信号と第2の制御信号とに基づいて加算動作する第2のアキュムレータと前記第1のアキュムレータの出力に基づいて前記第1のソフトスタート用信号を生成する第1のDAコンバータと、前記第2のアキュムレータの出力に基づいて前記第2のソフトスタート用信号を生成する第2のDAコンバータと、を備えることを特徴とするDC-DCコンバータである。

10

## 【0015】

また、他の解決手段は、CPUと、第1ソフトスタート用信号を入力するための入力部を備え第1の出力電圧信号と第1基準電圧信号との差を増幅して出力する第1の誤差増幅器と、第2ソフトスタート用信号を入力するための入力部を備え第2の出力電圧信号と第2基準電圧信号との差を増幅して出力する第2の誤差増幅器と、前記第1の誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングトランジスタとのONとOFFとを制御する第1のPWM制御回路と、前記第2の誤差増幅器の出力を用いて第3スイッチングトランジスタと第4スイッチングトランジスタとのONとOFFとを制御する第2のPWM制御回路と、周波数信号を分周して分周周波数信号を出力する分周器と、前記CPUから供給される第1の制御信号と前記分周周波数信号とに基づいて加算動作する第1のアキュムレータと、前記CPUから供給される第2の制御信号と前記分周周波数信号とに基づいて加算動作する第2のアキュムレータと前記第1のアキュムレータの出力に基づいて前記第1のソフトスタート用信号を生成する第1のDAコンバータと、前記第2のアキュムレータの出力に基づいて前記第2のソフトスタート用信号を生成する第2のDAコンバータと、を備えることを特徴とする電源供給システムである。

20

## 【0016】

本発明では、第1のアキュムレータおよび第2のアキュムレータの加算動作に共通に使用される分周周波数信号が生成され、第1の出力電圧信号および第2の出力電圧信号の生成部ごとにソフトスタート回路が備えられている。それぞれのソフトスタート回路は、初期化動作の後に動作を開始し、共通の分周周波数信号に応じて第1の制御信号および第2の制御信号をそれぞれ順次加算し、その加算結果をDA変換して、順次増加する第1のソフトスタート用信号および第2のソフトスタート用信号をそれぞれ出力する。さらに、それぞれのソフトスタート回路は、そのソフトスタート用信号に応じて出力電圧を制御する。

30

これにより、制御信号を第1の出力電圧および第2の出力電圧の生成部ごとに設定することにより、第1の出力電圧および第2の出力電圧の生成部ごとにソフトスタートの電圧傾きを設定することが、回路構成の変更を必要とすることなく柔軟に行なうことが可能となる。

40

## 【発明の効果】

## 【0017】

本発明によれば、起動時のソフトスタート動作をデジタル制御により行なう場合に、ソフトスタート時間の調整や変更を、回路構成の変更を必要とすることなく柔軟に行なうことが可能なDC-DCコンバータ、電源供給方法および電源供給システムを提供することが可能となる。

## 【発明を実施するための最良の形態】

## 【0018】

以下、本発明のDC-DCコンバータおよび電源供給システムについて具体化した実施形態を図1～図4に基づき図面を参照しつつ詳細に説明する。

## 【0019】

50

## (第1実施形態)

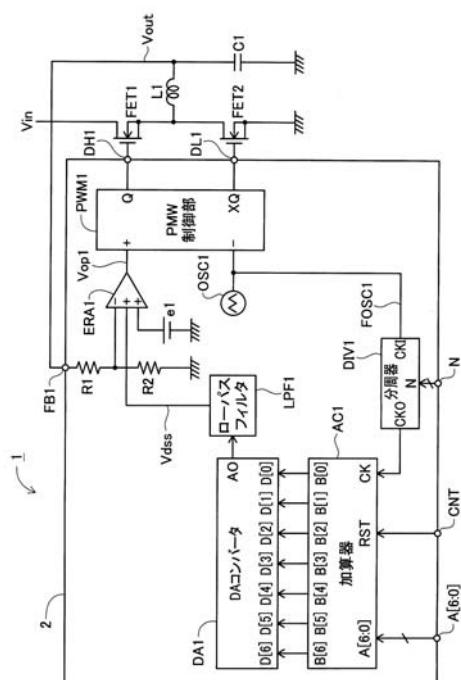

図1は、第1実施形態にかかるDC-DCコンバータ1の構成を示す回路図である。DC-DCコンバータ1はメインスイッチングトランジスタFET1がNMOSで構成される降圧型DC-DCコンバータである。

## 【0020】

DC-DCコンバータ1は制御回路2と、メインスイッチングトランジスタFET1と、同期整流トランジスタFET2と、コイルL1と、容量素子C1とを備えている。入力電源Vinと、接地電位との間に、メインスイッチングトランジスタFET1および同期整流トランジスタFET2がこの順で接続されている。また、メインスイッチングトランジスタFET1と、同期整流トランジスタFET2との接続点には、コイルL1の一端が接続されている。コイルL1の他端は容量素子C1および制御回路2のフィードバック端子FB1に接続されている。

## 【0021】

制御回路2は、メインスイッチングトランジスタFET1および同期整流トランジスタFET2を制御する回路である。制御回路2は、三角波発振器OSC1と、分周器DIV1と、加算器AC1と、DAコンバータDA1と、ローパスフィルタLPF1と、抵抗素子R1, R2と、基準電源e1と、エラーアンプERA1と、PWM制御部PWM1とを備えている。

## 【0022】

三角波発振器OSC1の出力信号は、PWM制御部PWM1のマイナス端子に入力されると共に分周器DIV1のクロック入力端子CKIに入力されている。分周器DIV1の分周比端子Nは、制御回路2の分周比端子Nに接続されている。制御回路2の分周比端子Nに入力される値は、不図示のCPUにより可変に調整される。分周比端子Nの信号の大きさを変えることにより、分周器DIV1の分周比を変えることができる。例えば、分周比端子Nの信号が2の場合は、分周器DIV1は2分周器として動作し、分周比端子Nの信号が3の場合は、分周器DIV1は3分周器として動作する。これにより、後述の加算器AC1のクロック入力端子CKに入力するクロック信号の周波数を柔軟に調整することができる。

## 【0023】

加算器AC1では、クロック入力端子CKに分周器DIV1のクロック出力端子CKOが接続され、リセット入力端子RSTに制御回路2の制御端子CNTが接続されている。また、加算値入力端子A[6:0]には、制御回路2の加算値入力端子A[6:0]が接続されている。制御回路2の制御端子CNTおよび加算値入力端子A[6:0]には、不図示のCPUにより信号が入力制御される。また、加算値出力端子B[6:0]はDAコンバータDA1の入力端子D[6:0]に接続されている。

## 【0024】

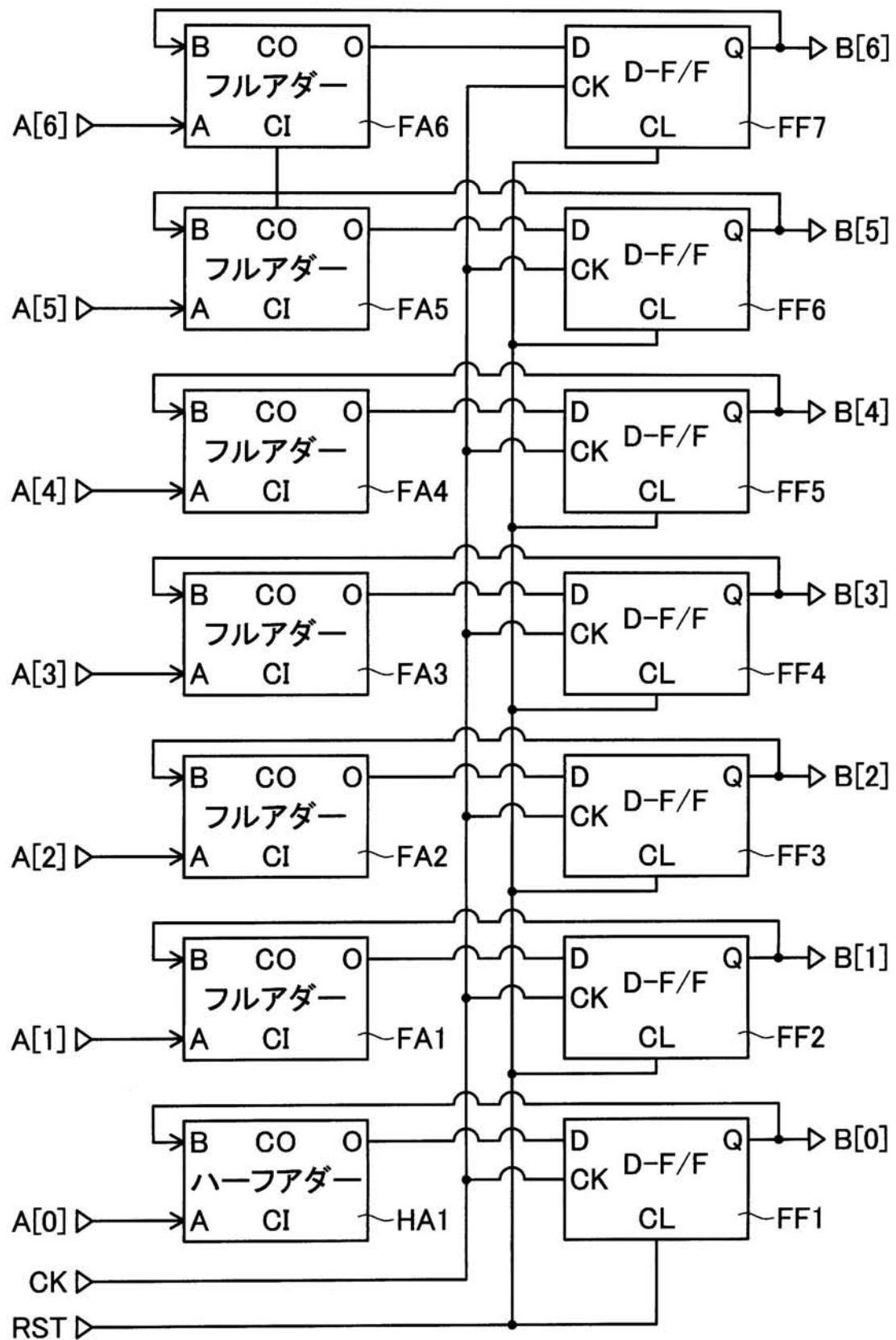

次いで、加算器AC1の構成について説明する。図2は加算器AC1の一例を示す回路図である。加算器AC1は、ハーフアダーハA1と、フルアダーフA1～フA6と、Dフリップフロップ(図中ではD-F/Fと表記)FF1～FF7とを備えている。

## 【0025】

ハーフアダーハA1のキャリー出力端子COはフルアダーフA1のキャリー入力端子CIに接続されている。以後、フルアダーフAn(n=1～5)のキャリー出力端子COはフルアダーフAn+1のキャリー入力端子CIに接続され、7ビットの加算器を構成する。また、ハーフアダーハA1およびフルアダーフA1～フA6の結果出力端子Oは、DフリップフロップFF1～FF7のデータ端子Dに接続されており、出力端子QはハーフアダーハA1およびフルアダーフA1～フA6の加算入力端子Bに接続されている。

## 【0026】

加算器AC1のクロック入力端子CKは、DフリップフロップFF1～FF7のクロック入力端子CKに接続されている。従って、加算器AC1のクロック入力端子CKにクロック信号が入力されるたびに加算値入力端子A[6:0]の値が加算されていくこととな

10

20

30

40

50

る。これにより、ソフトスタート時間の調整や変更を、回路構成の変更を必要とすることなく柔軟に行うことが可能となる。

また、DフリップフロップFF1～FF7のクリア端子CLには加算器AC1のリセット入力端子\_RSTが接続されている。これにより、リセット入力端子\_RSTがハイレベルになるとDフリップフロップFF1～FF7はリセットされて、B[6:0]が0となる。

#### 【0027】

図1に戻り、DAコンバータDA1は公知のR2Rラダー回路で構成されており、入力端子D[6:0]の信号に基づく値のアナログ電圧をアナログ出力端子AOから出力する。

10

#### 【0028】

アナログ出力端子AOからの信号はローパスフィルタLPF1を介して、ソフトスタート電圧V<sub>ds</sub>sとしてエラーアンプERA1の非反転入力端子に入力される。

#### 【0029】

フィードバック端子FB1からの信号は抵抗素子R1, R2で分圧され、エラーアンプERA1の反転端子に入力される。一方、基準電源e1の出力電圧がエラーアンプERA1の非反転端子に入力される。エラーアンプERA1では、非反転端子に入力されるソフトスタート電圧V<sub>ds</sub>sと基準電源e1の出力電圧のうち、ソフトスタート電圧V<sub>ds</sub>sを優先して、出力電圧V<sub>op</sub>1の出力が決定される。

20

#### 【0030】

PWM制御部PWM1では、プラス端子に出力電圧V<sub>op</sub>1が入力される。そして、制御回路2のハイサイド出力端子DH1を介してメインスイッチングトランジスタFET1を制御する出力端子Qからの信号と、制御回路2のローサイド出力端子DL1を介して同期整流トランジスタFET2を制御する出力端子XQからの信号が出力される。

#### 【0031】

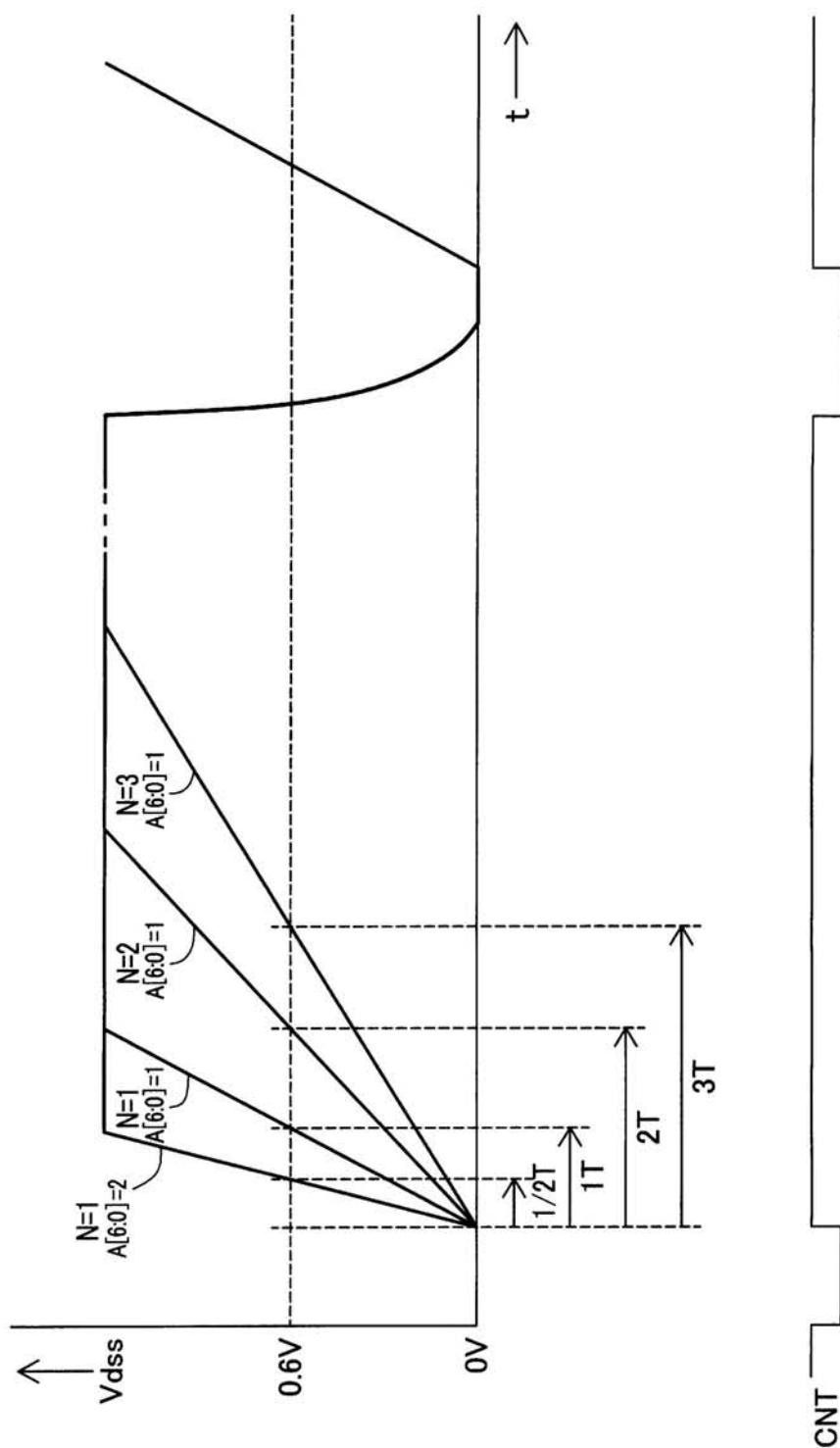

次いで、第1実施形態にかかるDC-DCコンバータ1の動作について説明する。図3は第1実施形態にかかるDC-DCコンバータ1の動作を示すタイミングチャートである。横軸は時間tであり、縦軸はソフトスタート電圧V<sub>ds</sub>sの値である

#### 【0032】

加算値入力端子A[6:0]の信号が1の場合には、分周比端子Nの信号が1, 2, 3の値を取ると、それに応じて、ソフトスタート電圧V<sub>ds</sub>sがリファレンス電源e1の電圧(本例では0.6V)に達するソフトスタート時間Tが1T, 2T, 3Tに変化する。また、加算値入力端子A[6:0]の信号の値を2にすると、ソフトスタート時間が1/2Tとなる。

30

#### 【0033】

また、この場合のソフトスタート時間Tは、 $T = (V_{e1} / A[6:0] * V_{dac}) \times N / FOSC1$ となる。ここで、V<sub>e1</sub>はリファレンス電源e1の電圧、V<sub>dac</sub>はDAコンバータの分解能、FOSC1は三角波発振器OSC1の発振周波数である。

#### 【0034】

以上詳細に説明したとおり、第1実施形態に係るDC-DCコンバータ1によれば、起動時のソフトスタート動作をディジタル制御により行なう場合に、ソフトスタート時間の調整や変更を、回路構成の変更を必要とすることなく柔軟に行うことが可能なソフトスタート回路を構成することができる。

40

#### 【0035】

##### (第2実施形態)

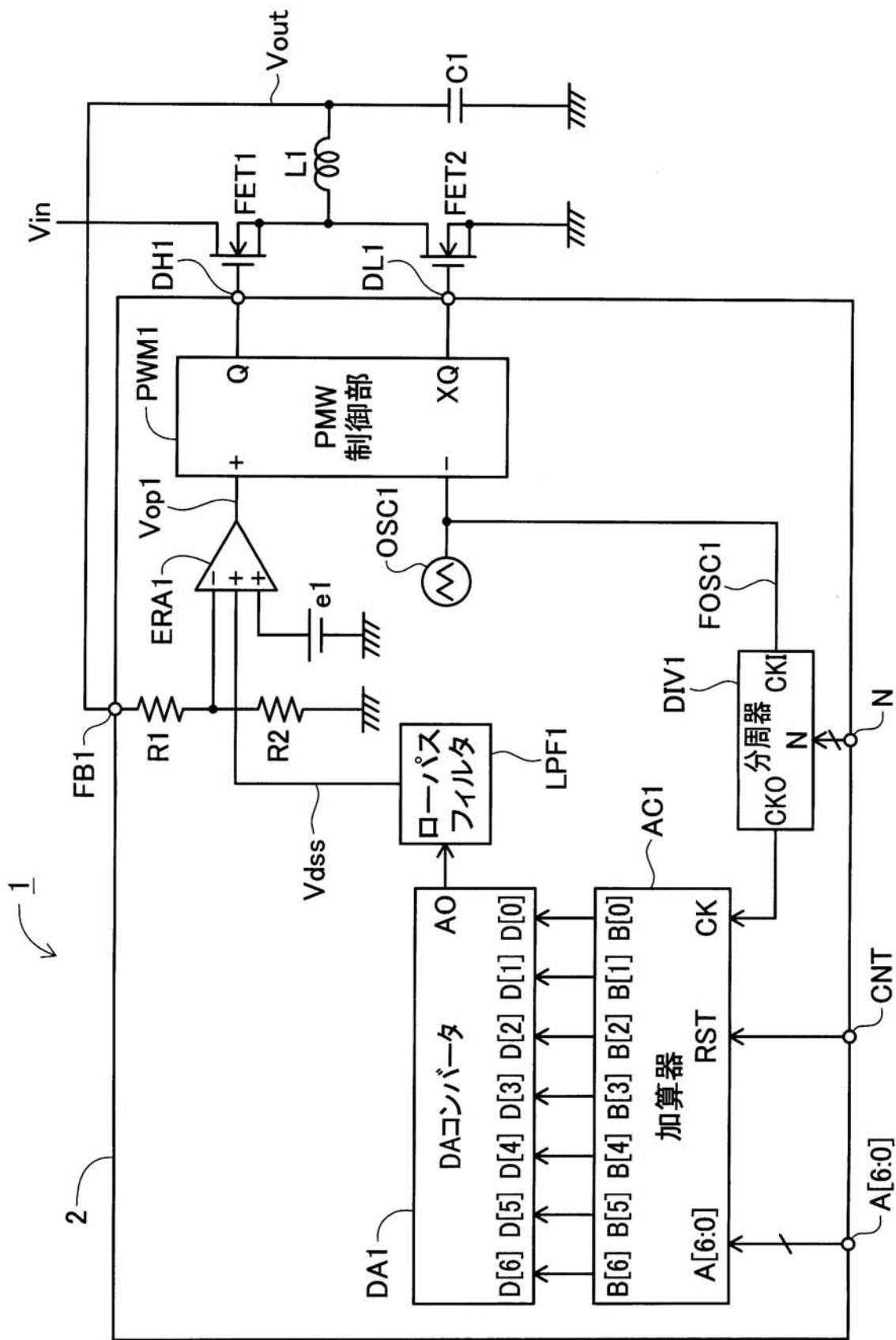

次いで第2実施形態にかかる2チャネルDC-DCコンバータ11について説明する。図4は、第2実施形態にかかる2チャネルDC-DCコンバータ11の構成を示す回路図である。2チャネルDC-DCコンバータ11は、第1実施形態にかかるDC-DCコンバータ1を2チャネル組み合わせた降圧型のDC-DCコンバータである。

#### 【0036】

50

2チャネルDC-DCコンバータ11は、制御回路12と、第1メインスイッチングトランジスタFET11と、第1同期整流トランジスタFET12と、第1コイルL11と、第1容量素子C11と、第2メインスイッチングトランジスタFET13と、第2同期整流トランジスタFET14と、第2コイルL12と、第2容量素子C12とを備えている。

【0037】

入力電源Vin11と、接地電位との間に、NMOSからなる第1メインスイッチングトランジスタFET11および第1同期整流トランジスタFET12がこの順で接続されている。また、第1メインスイッチングトランジスタFET11と、第1同期整流トランジスタFET12との接続点には、第1コイルL11の一端が接続されている。第1コイルL11の他端は第1容量素子C11および制御回路12のフィードバック端子FB11に接続されている。10

【0038】

一方、入力電源Vin12と、接地電位との間に、NMOSからなる第2メインスイッチングトランジスタFET13および第2同期整流トランジスタFET14がこの順で接続されている。また、第2メインスイッチングトランジスタFET13と、第2同期整流トランジスタFET14との接続点には、第2コイルL12の一端が接続されている。第2コイルL12の他端は第2容量素子C12および制御回路12のフィードバック端子FB12に接続されている。20

【0039】

制御回路12は、第1メインスイッチングトランジスタFET11、第1同期整流トランジスタFET12、第2メインスイッチングトランジスタFET13および第2同期整流トランジスタFET14を制御する回路である。制御回路12は、三角波発振器OSC11と、分周器DIV11と、加算器AC11, AC12と、DAコンバータDA11, DA12と、ローパスフィルタLPF11, LPF12と、抵抗素子R11~R14と、基準電源e11, e12と、エラーアンプERA11, ERA12と、PWM制御部PWM11, PWM12とを備えている。

【0040】

三角波発振器OSC11の出力信号は、PWM制御部PWM11, PWM12のマイナス端子に入力されると共に分周器DIV11のクロック入力端子CKIに入力されている。分周器DIV11の分周比端子Nは、制御回路12の分周比端子N11に接続されている。制御回路12の分周比端子N11に入力される値は、不図示のCPUにより制御される。第1実施形態にかかるDC-DCコンバータ1と同様に、分周比端子N11の信号の大きさを変えることにより、分周器DIV11の分周比を可変に調整することができる。30

【0041】

加算器AC11では、クロック入力端子CKに分周器DIV11のクロック出力端子CKOが接続され、リセット入力端子RSTに制御回路12の制御端子CNT11が接続されている。また、加算値入力端子A[6:0]には、制御回路12の加算値入力端子A11[6:0]が接続されている。制御回路12の制御端子CNT11および加算値入力端子A11[6:0]は、不図示のCPUにより制御される。また、加算値出力端子B[6:0]はDA11の入力端子D[6:0]に接続されている。なお、加算器AC11の構成は第1実施形態の加算器AC1(図2)と同様であるので説明は省略する。40

【0042】

DAコンバータDA11は公知のR2Rラダー回路で構成されており、入力端子D[6:0]の信号に基づく値のアナログ電圧をアナログ出力端子AOから出力する。

【0043】

アナログ出力端子AOからの信号はローパスフィルタLPF11を介して、ソフトスタート電圧Vdss11としてエラーアンプERA11の非反転入力端子に入力される。

【0044】

フィードバック端子FB11からの信号は抵抗素子R11, R12で分圧され、エラー

10

20

30

40

50

アンプ ERA11 の反転端子に入力される。一方、基準電源 e11 の出力電圧が ERA11 の非反転端子に入力される。エラーアンプ ERA11 では、非反転端子に入力されるソフトスタート電圧 Vdss11 と基準電源 e11 の出力電圧のうち、ソフトスタート電圧 Vdss11 を優先して、出力電圧 Vop11 の出力が決定される。

【0045】

PWM制御部 PWM11 では、プラス端子に出力電圧 Vop11 が入力される。そして、制御回路12 のハイサイド出力端子 DH11 を介して第1メインスイッチングトランジスタ FET11 を制御する出力端子 Q からの信号と、制御回路12 のローサイド出力端子 DL11 を介して第1同期整流トランジスタ FET12 を制御する出力端子 XQ からの信号とが出力される。

10

【0046】

加算器 AC12 では、クロック入力端子 CK に分周器 DIV12 のクロック出力端子 CKO が接続され、リセット入力端子 RST に制御回路12 の制御端子 CNT12 が接続されている。また、加算値入力端子 A[6:0] には、制御回路12 の加算値入力端子 A12[6:0] が接続されている。制御回路12 の制御端子 CNT12 および加算値入力端子 A12[6:0] は、不図示の CPU により制御される。また、加算値出力端子 B[6:0] は DA12 の入力端子 D[6:0] に接続されている。なお、加算器 AC12 の構成は第1実施形態の加算器 AC1 (図2) と同様であるので説明は省略する。

【0047】

DAコンバータ DA12 は公知の R2R ラダー回路で構成されており、入力端子 D[6:0] の信号に基づく値のアナログ電圧をアナログ出力端子 A0 から出力する。

20

【0048】

アナログ出力端子 A0 からの信号はローパスフィルタ LPF12 を介して、ソフトスタート電圧 Vdss12 としてエラーアンプ ERA12 の非反転入力端子に入力される。

【0049】

フィードバック端子 FB12 からの信号は抵抗素子 R13, R14 で分圧され、エラーアンプ ERA12 の反転端子に入力される。一方、基準電源 e12 の出力電圧が ERA12 の非反転端子に入力される。エラーアンプ ERA12 では、非反転端子に入力されるソフトスタート電圧 Vdss12 と基準電源 e12 の出力電圧のうち、ソフトスタート電圧 Vdss12 を優先して、出力電圧 Vop12 の出力が決定される。

30

【0050】

PWM制御部 PWM12 では、プラス端子に出力電圧 Vop12 が入力される。そして、制御回路12 のハイサイド出力端子 DH12 を介して第2メインスイッチングトランジスタ FET13 を制御する出力端子 Q からの信号と、制御回路12 のローサイド出力端子 DL12 を介して第2同期整流トランジスタ FET14 を制御する出力端子 XQ からの信号とが出力される。

【0051】

以上詳細に説明したとおり、第2実施形態にかかる2チャネル DC-DC コンバータ11 によれば、起動時のソフトスタート動作をディジタル制御により行なう場合に、ソフトスタート時間の調整や変更を、回路構成の変更を必要とすることなく柔軟に行なうことが可能なソフトスタート回路を構成することができる。

40

【0052】

また、第2実施形態にかかる2チャネル DC-DC コンバータ11 では、加算値入力端子 A11[6:0] と、加算値入力端子 A12[6:0] とを個別に設定することができる。これによりチャネルごとにソフトスタートの電圧傾きを設定することが、回路構成の変更を必要とすることなく柔軟に行なうことができる。

【0053】

なお、本発明は前記各実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良、変形が可能であることは言うまでもない。

例えば、第1実施形態および第2実施形態においては、降圧型の DC-DC コンバータ

50

について説明したが、本発明はこれに限定されるものではなく、昇圧型や昇降圧型の D C - D C コンバータにも同様に適用することができることは言うまでもない。

また、第 1 実施形態および第 2 実施形態においては、メインスイッチングトランジスタに N M O S を用いた構成について説明したが、本発明はこれに限定されるものではなく、メインスイッチングトランジスタに P M O S を用いた構成にも同様に適用することができる。

さらに、第 2 実施形態では 2 チャネル D C - D C コンバータ 1 1 の構成について説明したが、さらに多チャネルの D C - D C コンバータにも同様に適用することができる。

【 0 0 5 4 】

なお、三角波発振器の出力信号 F O S C 1 , F O S C 1 1 は周波数信号の一例、加算値入力端子 A [ 6 : 0 ] , A 1 1 [ 6 : 0 ] , A 1 2 [ 6 : 0 ] の信号の値は制御信号の一例、分周器 D I V 1 , D I V 1 1 , D I V 1 2 の出力信号は分周周波数信号の一例、エラーアンプ E R A 1 は誤差増幅器の一例、E R A 1 1 は第 1 の誤差増幅器の一例、E R A 1 2 は第 2 の誤差増幅器の一例である。

【 0 0 5 5 】

ここで、本発明の技術思想により、背景技術における課題を解決するための手段を以下に列記する。

( 付記 1 ) ソフトスタート用信号を入力するための入力部を備え出力電圧信号と基準電圧信号との差を増幅して出力する誤差増幅器と、前記誤差増幅器の出力を用いて第 1 スイッチングトランジスタと第 2 スイッチングトランジスタとの O N と O F F とを制御する P W M 制御回路とを備えた D C - D C コンバータにおいて、

周波数信号を分周して分周周波数信号を出力する分周器と、

前記分周周波数信号と制御信号とに基づいて加算動作するアキュムレータと、

前記アキュムレータの出力に基づいて前記ソフトスタート用信号を生成する D A コンバータと、

を備えることを特徴とする D C - D C コンバータ。

( 付記 2 ) 前記アキュムレータは、加算値としての前記制御信号に基づいてソフトスタート時間を制御すること

を特徴とする付記 1 に記載の D C - D C コンバータ。

( 付記 3 ) 前記アキュムレータは、前記制御信号の値が増加すると前記ソフトスタート時間を短くする制御を行うこと

を特徴とする付記 2 に記載の D C - D C コンバータ。

( 付記 4 ) ソフトスタート時間は、

$( V_{ref} / AN * V_{dac} ) \times N \div f_{osc}$

$V_{ref}$  : 基準電圧、 A N : 制御信号、  $V_{dac}$  : D A コンバータの分解能、

N : 分周比、  $f_{osc}$  : 周波数信号、

で設定されることを特徴とする付記 1 乃至付記 3 の何れかに記載の D C - D C コンバータ。

( 付記 5 ) 前記アキュムレータは、リセット信号に基づいてソフトスタートをリセットすること

を特徴とする付記 1 乃至付記 4 の何れかに記載の D C - D C コンバータ。

( 付記 6 ) 前記ソフトスタート信号が所定値になると、前記アキュムレータは前記 D A コンバータに出力する信号を一定値にすること

を特徴とする付記 1 乃至付記 5 の何れかに記載の D C - D C コンバータ。

( 付記 7 ) 前記誤差増幅器は、前記基準電圧信号又は前記ソフトスタート信号の低電位側の信号と前記出力電圧信号との誤差を増幅すること

を特徴とする付記 1 乃至付記 6 の何れかに記載の D C - D C コンバータ。

( 付記 8 ) C P U と、

ソフトスタート用信号を入力するための入力部を備え出力電圧信号と基準電圧信号との差を増幅して出力する誤差増幅器と、該誤差増幅器の出力を用いて第 1 スイッチングトラン

10

20

30

40

50

ジスタと第2スイッチングトランジスタとのONとOFFとを制御するPWM制御回路とを備えたDC-DCコンバータと、

を有する電源供給システムにおいて、

前記DC-DCコンバータは、

周波数信号を分周して分周周波数信号を出力する分周器と、

前記CPUから供給される制御信号と前記分周周波数信号とに基づいて動作するアキュムレータと、

前記アキュムレータの出力に基づいて前記ソフトスタート用信号を生成するDAコンバータと、

を備えることを特徴とする電源供給システム。

(付記9) 前記CPUからリセット信号が供給され、前記DC-DCコンバータは該リセット信号に基づいてソフトスタートをリセットすることを特徴とする付記8に記載の電源供給システム。

(付記10) 前記CPUから分周比信号が供給され、前記分周器は該分周比信号に基づいて前記周波数信号を分周することを特徴とする付記8又は付記9に記載の電源供給システム。

(付記11) 基準電圧信号又はソフトスタート信号の低電位側の信号と出力電圧信号との誤差を増幅し、前記誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングトランジスタとのONとOFFとをPWM制御する制御を行って、前記出力電圧信号を出力する電源供給方法において、

周波数信号を分周して分周周波数信号を出力し、

前記分周周波数信号に基づいて設定信号の累積加算を行い、

前記累積加算結果に基づいて前記ソフトスタート用信号を生成することを備えることを特徴とする電源供給方法。

(付記12) 前記設定信号の値が増加するとソフトスタート時間を短くする制御を行うことを特徴とする付記11に記載の電源供給方法。

(付記13) ソフトスタート時間は、

$$(V_{ref}/AN * V_{dac}) \times N / f_{osc}$$

V<sub>ref</sub>：基準電圧、AN：制御信号、V<sub>dac</sub>：DAコンバータの分解能、

N：分周比、f<sub>osc</sub>：周波数信号、

で設定されることを特徴とする付記12又は付記13に記載の電源供給方法。

(付記14) 第1ソフトスタート用信号を入力するための入力部を備え第1の出力電圧信号と第1基準電圧信号との差を増幅して出力する第1の誤差増幅器と、

第2ソフトスタート用信号を入力するための入力部を備え第2の出力電圧信号と第2基準電圧信号との差を増幅して出力する第2の誤差増幅器と、

前記第1の誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングトランジスタとのONとOFFとを制御する第1のPWM制御回路と、

前記第2の誤差増幅器の出力を用いて第3スイッチングトランジスタと第4スイッチングトランジスタとのONとOFFとを制御する第2のPWM制御回路と、

を備えたDC-DCコンバータにおいて、

周波数信号を分周して分周周波数信号を出力する分周器と、

前記分周周波数信号と第1の制御信号とに基づいて加算動作する第1のアキュムレータと、

前記分周周波数信号と第2の制御信号とに基づいて加算動作する第2のアキュムレータと、

前記第1のアキュムレータの出力に基づいて前記第1のソフトスタート用信号を生成する第1のDAコンバータと、

前記第2のアキュムレータの出力に基づいて前記第2のソフトスタート用信号を生成する第2のDAコンバータと、

10

20

30

40

50

第2のD Aコンバータと、

を備えることを特徴とするD C - D Cコンバータ。

(付記15) 前記第1のアキュムレータは、加算値としての前記第1の制御信号に基づいて第1のソフトスタート時間を制御し、

前記第2のアキュムレータは、加算値としての前記第2の制御信号に基づいて第2のソフトスタート時間を制御し、

を特徴とする付記14に記載のD C - D Cコンバータ。

(付記16) 前記第1のアキュムレータと前記第2のアキュムレータとは、前記第1の制御信号又は戦記第2の制御信号の値が増加すると前記第1のソフトスタート時間又は前記第2のソフトスタート時間を短くする制御を行うこと

10

を特徴とする付記15に記載のD C - D Cコンバータ。

(付記17) ソフトスタート時間は、

$$(V_{ref} / AN * V_{dac}) \times N / f_{osc}$$

$V_{ref}$  : 基準電圧、  $AN$  : 制御信号、  $V_{dac}$  : D Aコンバータの分解能、

$N$  : 分周比、  $f_{osc}$  : 周波数信号、

で設定されることを特徴とする付記1乃至付記3の何れかに記載のD C - D Cコンバータ。

(付記18) 前記第1のアキュムレータは、第1のリセット信号に基づいて第1のソフトスタートをリセットし、

前記第2のアキュムレータは、第2のリセット信号に基づいて第2のソフトスタートをリセットすること

を特徴とする付記14乃至付記17の何れかに記載のD C - D Cコンバータ。

(付記19) C P Uと、

第1ソフトスタート用信号を入力するための入力部を備え第1の出力電圧信号と第1基準電圧信号との差を増幅して出力する第1の誤差増幅器と、

第2ソフトスタート用信号を入力するための入力部を備え第2の出力電圧信号と第2基準電圧信号との差を増幅して出力する第2の誤差増幅器と、

前記第1の誤差増幅器の出力を用いて第1スイッチングトランジスタと第2スイッチングトランジスタとのONとOFFとを制御する第1のP W M制御回路と、

前記第2の誤差増幅器の出力を用いて第3スイッチングトランジスタと第4スイッチングトランジスタとのONとOFFとを制御する第2のP W M制御回路と、

周波数信号を分周して分周周波数信号を出力する分周器と、

前記C P Uから供給される第1の制御信号と前記分周周波数信号に基づいて加算動作する第1のアキュムレータと、

前記C P Uから供給される第2の制御信号と前記分周周波数信号に基づいて加算動作する第2のアキュムレータと、

前記第1のアキュムレータの出力に基づいて前記第1のソフトスタート用信号を生成する第1のD Aコンバータと、

前記第2のアキュムレータの出力に基づいて前記第2のソフトスタート用信号を生成する第2のD Aコンバータと、

を備えることを特徴とする電源供給システム。

(付記20) 前記C P Uから分周比信号が供給され、前記分周器は該分周比信号に基づいて前記周波数信号を分周すること

を特徴とする付記19に記載の電源供給システム。

【図面の簡単な説明】

【0056】

【図1】第1実施形態にかかるD C - D Cコンバータの構成を示す回路図である。

【図2】加算器の一例を示す回路図である。

【図3】第1実施形態にかかるD C - D Cコンバータの動作を示すタイミングチャートである。

40

50

【図4】第2実施形態にかかる2チャネルDC-DCコンバータの構成を示す回路図である。

【図5】従来技術の多チャネル電源回路装置の構成を示す回路図である。

【符号の説明】

【0057】

1 DC-DCコンバータ

11 2チャネルDC-DCコンバータ

2, 12 制御回路

AC1, AC11, AC12 加算器

DA1, DA11, DA12 DAコンバータ

DIV1, DIV11, DIV12 分周器

ERA1, ERA11, ERA12 エラーアンプ

OSC1, OSC11, OSC12 三角波発振器

【図 1】

第1実施形態にかかるDC-DCコンバータの構成を示す回路図

【図2】

### 加算器の一例を示す回路図

【図3】

第1実施形態にかかるDC-DCコンバータの

動作を示すタイミングチャート

【 図 4 】

## 第2実施形態にかかる2チャネルDC-DCコンバータの構成を示す回路図

【図5】

従来技術の多チャネル電源回路装置の構成を示す回路図