(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5669175号

(P5669175)

(45) 発行日 平成27年2月12日(2015.2.12)

(24) 登録日 平成26年12月26日(2014.12.26)

(51) Int.Cl.

F 1

G06F 12/00 (2006.01)

G06F 13/16 (2006.01)G06F 12/00 564D

G06F 12/00 597D

G06F 13/16 510A

請求項の数 14 (全 24 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2010-146142 (P2010-146142) |

| (22) 出願日  | 平成22年6月28日 (2010.6.28)       |

| (65) 公開番号 | 特開2012-8920 (P2012-8920A)    |

| (43) 公開日  | 平成24年1月12日 (2012.1.12)       |

| 審査請求日     | 平成25年3月27日 (2013.3.27)       |

前置審査

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (74) 代理人  | 100089071<br>弁理士 玉村 静世                               |

| (72) 発明者  | 諏訪 元大<br>神奈川県川崎市中原区下沼部1753番地<br>ルネサスエレクトロニクス株式会社内    |

| (72) 発明者  | 松田 俊和<br>北海道亀田郡七飯町字中島145番地 株式会社ルネサス北日本セミコンダクタ内       |

| 審査官       | 松永 稔                                                 |

最終頁に続く

(54) 【発明の名称】電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1半導体部品搭載領域に形成された複数の第1端子、第2半導体部品搭載領域に形成された複数の第2端子、および前記複数の第1端子と前記複数の第2端子とをそれぞれ繋ぐ複数の伝送経路、を有する基板と、

前記第1半導体部品搭載領域に搭載された第1半導体部品と、

前記第2半導体部品搭載領域に搭載された第2半導体部品と、

を含み、

前記第2半導体部品は、クロック信号に同期動作される複数のメモリデバイスを有し、

前記第1半導体部品は、前記第2半導体部品を制御するメモリコントローラを有し、

前記複数の伝送経路は、前記第1半導体部品から前記第2半導体部品に前記クロック信号を供給するクロック伝送経路、前記第1半導体部品から前記第2半導体部品にコマンド及びアドレス信号を供給するコマンドアドレス伝送経路、前記第1半導体部品と前記第2半導体部品との間でデータ伝送を行うためのデータ系伝送経路、及び前記クロック信号と前記コマンド及びアドレス信号の有効性を示すための第1コントロール系信号を前記第1半導体部品から前記第2半導体部品に伝送する第1コントロール系伝送経路とを含み、

前記基板は更に、グランドプレーンと、前記第1コントロール系伝送経路の途中から分岐してグランドプレーンに至る第1特定伝送経路と、前記第1特定伝送経路に直列配置された第1容量素子とを有し、

前記第1容量素子は前記第1コントロール系伝送経路の信号伝送方向基端から前記第1

10

20

特定伝送経路への分岐点までの経路の寄生容量よりも大きな容量値を持ち、

前記第2半導体部品は、モジュール基板に前記複数のメモリデバイスが搭載されたメモリモジュールであり、

前記クロック伝送経路から供給される前記クロック信号を受ける前記モジュール基板内のクロック配線、前記コマンドアドレス伝送経路から供給される前記コマンド及びアドレス信号を受ける前記モジュール基板内の信号線、及び前記第1コントロール系伝送経路から供給される前記第1コントロール系信号を受ける前記モジュール基板内の信号線に、前記複数のメモリデバイスの対応端子がフライ・バイ形態で接続されており、

前記第1コントロール系伝送経路から供給される前記第1コントロール系信号を受ける前記モジュール基板内の前記信号線の端部には、終端抵抗が接続されている、電子機器。

10

#### 【請求項2】

請求項1記載の電子機器において、

前記第1コントロール系伝送経路上における前記第1半導体部品から前記第1特定伝送経路への分岐点までの距離は、前記第1コントロール系伝送経路上における前記分岐点から第2半導体部品までの距離よりも短い、電子機器。

#### 【請求項3】

請求項1記載の電子機器において、

前記メモリデバイスはDDR3-SDRAMであり、

前記第1コントロール系信号は、前記DDR3-SDRAMにおけるチップ選択信号及びクロックイネーブル信号である、電子機器。

20

#### 【請求項4】

請求項1記載の電子機器において、

前記複数の伝送経路は更に、前記データ系伝送経路の伝送特性を選択的に切り換えるための第2コントロール系信号を前記第1半導体部品から前記第2半導体部品に伝送する第2コントロール系伝送経路を含み、

前記基板は更に、前記第2コントロール系伝送経路の途中から分岐してグランドプレーンに至る第2特定伝送経路と、前記第2特定伝送経路に直列配置された第2容量素子とを有し、

前記第2容量素子は前記第2コントロール系伝送経路の信号伝送方向基端から前記第2特定伝送経路への分岐点までの経路の寄生容量よりも大きな容量値を持つ、電子機器。

30

#### 【請求項5】

請求項4記載の電子機器において、

前記第2コントロール系伝送経路上における前記第1半導体部品から前記第2特定伝送経路への分岐点までの距離は、前記第2コントロール系伝送経路上における前記分岐点から第2半導体部品までの距離よりも短い、電子機器。

#### 【請求項6】

請求項4記載の電子機器において、

前記クロック伝送経路から供給される前記クロック信号を受ける前記モジュール基板内のクロック配線、前記コマンドアドレス伝送経路から供給される前記コマンド及びアドレス信号を受ける前記モジュール基板内の信号線、前記第1コントロール系伝送経路からの前記第1コントロール系信号を受ける前記モジュール基板内の信号線、及び前記第2コントロール系伝送経路から供給される前記第2コントロール系信号を受ける前記モジュール基板内の信号線に、前記複数のメモリデバイスの対応端子がフライ・バイ形態で接続されている、電子機器。

40

#### 【請求項7】

請求項6記載の電子機器において、

前記第2半導体部品はDDR3-SDRAMであり、

前記メモリデバイスは、前記データ系伝送経路に対応する終端抵抗として利用可能なオンダイターミネーションを有し、

前記第2コントロール系信号は、前記オンダイターミネーションの有効又は無効を指示

50

するオンダイターミネーション指示信号である、電子機器。

**【請求項 8】**

請求項 4 記載の電子機器において、

前記基板は複数の配線層を有し、

前記第1コントロール系伝送経路及び第2コントロール系伝送経路は、前記複数の配線層のうちの最上層および最下層のそれぞれの配線層に形成され、

前記複数の第1端子及び第2端子のそれぞれは前記複数の配線層のうちの最上層に形成されている、電子機器。

**【請求項 9】**

請求項 8 記載の電子機器において、

10

前記グランドプレーンは、前記複数の配線層のうちの最上層と最下層との間の内層の配線層に形成され、

前記第1特定伝送経路及び前記第2特定伝送経路は、前記基板に形成されたスルーホールに設けられたビア配線を介して前記グランドプレーンとそれぞれ電気的に接続され、

前記ビア配線のそれぞれは、平面視において、前記第1コントロール系伝送経路及び第2コントロール系伝送経路に含まれる互いに隣り合う配線に共通接続される、電子機器。

**【請求項 10】**

基板に第1半導体部品と前記第1半導体部品が制御する第2半導体部品が搭載された電子機器であって、

前記第2半導体部品はクロック信号に同期動作される複数のメモリデバイスを有し、

20

前記基板は前記第2半導体部品を前記第1の半導体部品に接続するための複数の伝送経路を有し、

前記複数の伝送経路は、前記第1半導体部品から前記第2半導体部品に前記クロック信号を供給するクロック伝送経路、前記第1半導体部品から前記第2半導体部品にコマンド及びアドレス信号を供給するコマンドアドレス伝送経路、前記第1半導体部品と前記第2半導体部品との間でデータ伝送を行うためのデータ系伝送経路、及び前記クロック信号と前記コマンド及びアドレス信号の有効性を示すための第1コントロール系信号を前記第1半導体部品から前記第2半導体部品に伝送する第1コントロール系伝送経路とを含み、

前記基板は更に、グランドプレーンと、前記第1コントロール系伝送経路の途中から分岐してグランドプレーンに至る特定伝送経路と、前記特定伝送経路に直列配置された容量素子とを有し、

30

前記容量素子は、それがない場合に比べて前記第1コントロール系信号のスルーレートを小さくし且つタイミングウインドウを大きくし、

前記第2半導体部品は、モジュール基板に前記複数のメモリデバイスが搭載されたメモリモジュールであり、

前記クロック伝送経路から供給される前記クロック信号を受ける前記モジュール基板内のクロック配線、前記コマンドアドレス伝送経路から供給される前記コマンド及びアドレス信号を受ける前記モジュール基板内の信号線、及び前記第1コントロール系伝送経路から供給される前記第1コントロール系信号を受ける前記モジュール基板内の信号線に、前記複数のメモリデバイスの対応端子がフライ・バイ形態で接続されており、

40

前記第1コントロール系伝送経路から供給される前記第1コントロール系信号を受ける前記モジュール基板内の前記信号線の端部には、終端抵抗が接続されている、電子機器。

**【請求項 11】**

請求項 10 記載の電子機器において、

前記複数の伝送経路は更に、前記データ系伝送経路の伝送特性を選択的に切り換えるための第2コントロール系信号を前記第1半導体部品から前記第2半導体部品に伝送する第2コントロール系伝送経路を含み、

前記基板は更に、前記第2コントロール系伝送経路の途中から分岐してグランドプレーンに至る第2特定伝送経路と、前記第2特定伝送経路の途中に直列配置された第2容量素子を有し、

50

前記第2容量素子は、それがない場合に比べて前記第2コントロール系信号のスルーレートを小さくし且つタイミングウインドウを大きくする、電子機器。

【請求項12】

請求項10記載の電子機器において、

前記第2半導体部品は、前記第2コントロール系伝送経路から供給される第2コントロール系信号を受けるモジュール基板内の信号線に前記複数のメモリデバイスの対応端子がフライ・バイ形態で接続されている、電子機器。

【請求項13】

請求項12記載の電子機器において、

前記メモリデバイスはDDR3-SDRAMであり、

10

前記第1コントロール系信号は、DDR3-SDRAMにおけるチップ選択信号及びクロックイネーブル信号である、電子機器。

【請求項14】

請求項13記載の電子機器において、

前記メモリデバイスは、前記データ系伝送経路に対応する終端抵抗として利用可能なオンダイタミネーションを有し、

前記第2コントロール系信号は、前記オンダイタミネーションの有効又は無効を指示するオンダイタミネーション指示信号である、電子機器。

【発明の詳細な説明】

【技術分野】

20

【0001】

本発明は、配線層を持つ基板にアクセスされる半導体部品とアクセスする半導体部品を搭載した電子機器におけるアクセス制御信号の波形改善に係り、例えばDDR3-SDRAM(Double-Data-Rate3 Synchronous Dynamic Random Access Memory)を搭載したDIMM(Dual In-line Memory Module)が装着されるプロセッサボード若しくはコントロールボードなどに適用して有効な技術に関する。

【背景技術】

【0002】

DDR3-SDRAMに代表されるようなクロック信号に同期動作されるクロック同期メモリは、これに供給されるクロック信号やコマンド及びアドレス信号が有効であることを示すためのイネーブル制御信号を、当該クロック信号やコマンド及びアドレス信号と共に入力することになる。これらイネーブル制御信号によってクロック信号やコマンド及びアドレス信号が有効であることが指示されると、それに同期してクロック同期メモリは内部ロジックによるタイミングシーケンスに従ってアクセス動作を行う。アクセス動作におけるリードデータやライトデータの確定した状態はデータストローブ信号によって通知される。

30

【0003】

例えばDIMMのようなメモリモジュールには複数のクロック同期メモリが搭載され、それら複数のクロック同期メモリは同期的に並列動作される。この同期的並列動作のために非特許文献1ではDIMMに搭載される複数個のDDR2-SDRAMに共通に供給されるクロック信号やコマンド及びアドレス信号などのためのモジュール基板上の配線をT分岐構造とすることが記載される。T分岐構造によってDIMMのモジュール端子から夫々のDDR2-SDRAMのクロック端子やコマンド及びアドレス端子までの信号配線を等長化することが容易になる。一方、DDR3-SDRAMを搭載したDIMMについての規格に言及した非特許文献2ではモジュール基板上のクロック信号やコマンド及びアドレス信号のための配線構造にはT分岐構造ではなくフライ・バイ構造を採用することが記載される。フライ・バイ構造は一筆書きされる信号線に複数のDDR3-SDRAMの外部端子を順次数珠繋ぎの形態で接続する構造であって、配線の等長化を優先させずにDDR3-SDRAMを最短距離で接続することを優先させようとするものである。動作の高

40

50

速化にしたがって配線の等長化が厳しくなってくると等長化のための配線の引き回しが多くなって結局信号の波形品質の劣化を招くことになるからである。フライ・バイ構造によつて生ずる配線の非等長化に対しては、フライ・バイ構造の配線で供給されるクロック信号などの伝播遅延に合わせてデータストローブ信号の入力タイミングなどを遅延させるレベリング制御が行われることになっている。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】JEDEC Standard No. 21C, Revision 1.0 Release 18A, 4.20.18 - 204-Pin DDR3 SDRAM Unbuffered SO-DIMM Design Specification, page 4.20.18-01 - 4.20.1 10

1-60.

【非特許文献2】JEDEC Standard No. 21C, Revision 2.5 Release 18, 4.20.11 - 200-Pin DDR2 SDRAM Unbuffered SO-DIMM Design Specification, page 4.20.11-01 - 4.20.11-66.

【発明の概要】

【発明が解決しようとする課題】

【0005】

DIMMなどのメモリモジュールは各種コンピュータシステムのメインメモリなどに広く適用され、DIMMに搭載されたDDR形態のSDRAMに対するメモリインタフェース制御及びタイミング制御などはプロセッサコアなどからのアクセス要求にしたがってメモリコントローラが行う。メモリコントローラはその動作モードに応じてDDR2-SDRAM搭載のDIMMとDDR3-SDRA搭載のDIMMというように規格の異なる複数種類のメモリモジュールの制御に適用できることがコスト並びに汎用性という点で望ましい。

【0006】

しかしながら、一つのメモリコントローラが制御対象とする複数種類のDIMMにおけるモジュール内配線構造の性質が本質的に異なるとき、レベリング制御のような出力する信号のタイミング制御だけでは対処できない場合のあることが本発明者によって明らかにされた。例えばモジュール内配線がT分岐構造の場合とフライ・バイ構造との場合では、信号線で生ずる信号反射の状況が大きく異なり、データストローブ信号のレベリング制御で全て解決できるというわけではない。すなわち、フライ・バイ構造のモジュール内配線では入力信号の上流側のメモリデバイスは、それよりも下流側のメモリデバイスの入力容量成分を介して反射されるノイズを重畠的に受ける結果、信号入力端に近いメモリデバイス（入力信号の上流側のメモリデバイス）ほど、入力信号波形が歪む。このような歪みは信号のハイレベル期間やローレベル期間若しくは信号周期に影響を及ぼすことになり、その信号が規定するタイミング上の有効期間（タイミングウインドウ）を狭める結果になる。

【0007】

このような信号反射による影響を緩和するにはモジュール内配線の終端抵抗とシリーズ抵抗の値を調整して対処することも可能であるが、メモリ動作周波数が高くなるにしたがって信号波形に重畠される高調波成分（高周波成分）が多くなり、その高調波成分に反射波が重畠されて十分対処できない場合が想定される。さらに、DDR3-SDRAMを搭載するDIMMは非特許文献2に記載されるように予め決まった終端抵抗がモジュール基板に実装されるため、上述の終端抵抗とシリーズ抵抗の値を相互に調整して対処することはできない。

【0008】

高調波成分を抑制するには信号のスルーレートすなわち変化速度を遅くすればよいが、メモリコントローラの出力バッファのスルーレートを低くするとDDR2-SDRAM搭載の等長化配線を採用したDIMMの場合に駆動能力が低下する虞を生ずる。これに対し、動作モードによって前記出力バッファの駆動能力を可変にすると、メモリコントローラ 50

の回路規模が増大して、DIMMの構造ごとにメモリコントローラを分けるのと同様にコストが上昇してしまう。DIMMとメモリコントローラを接続する配線に挿入されたシリーズ抵抗だけでは高調波成分を抑圧には効果的ではない。

#### 【0009】

本発明の目的は、アクセスを制御する半導体部品に負担をかけることなく当該半導体部品が出力する信号の高調波成分によって当該信号によるタイミングウインドウが不所望に狭められることを抑制することにある。

#### 【0010】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

10

#### 【課題を解決するための手段】

#### 【0011】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

#### 【0012】

すなわち、基板上でアクセスを制御する半導体部品が出力するクロック信号やコマンド及びアドレス信号の有効性を示すイネーブル制御信号を基板上でアクセスされる別の半導体部品に供給する信号伝送経路の所定ノードから分岐してグランドプレーンに至る特定伝送経路に容量素子を直列配置する。前記容量素子は、イネーブル制御信号の高調波成分に対してグランドプレーンへのショート経路として機能し、当該容量素子がない場合に比べて前記イネーブル制御信号のスルーレートを小さくし且つそのタイミングウインドウを大きくする。

20

#### 【発明の効果】

#### 【0013】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

#### 【0014】

すなわち、アクセスを制御する半導体部品に負担をかけることなく当該半導体部品が出力する信号の高調波成分によって当該信号によるタイミングウインドウが不所望に狭められることを抑制することができる。

30

#### 【図面の簡単な説明】

#### 【0015】

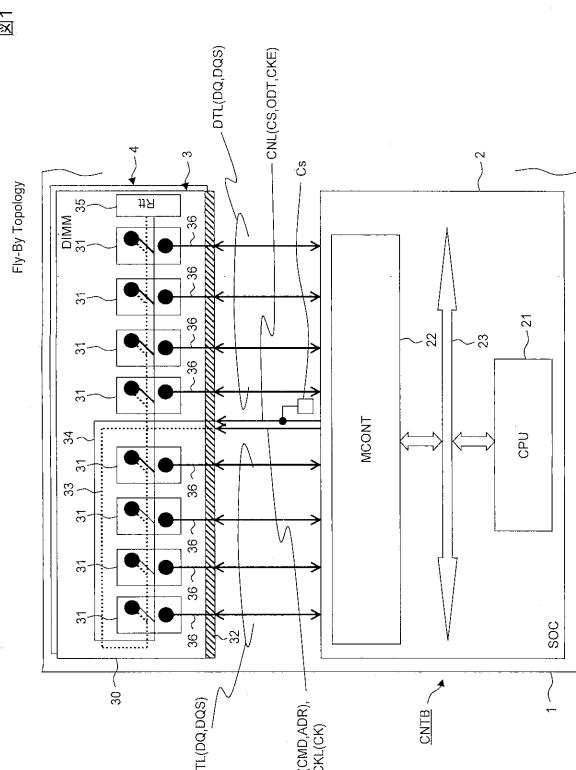

【図1】図1はDDR3-SDRAMから成るフライ・バイ構造のDIMMを搭載したコントロールボードを例示するブロック図である。

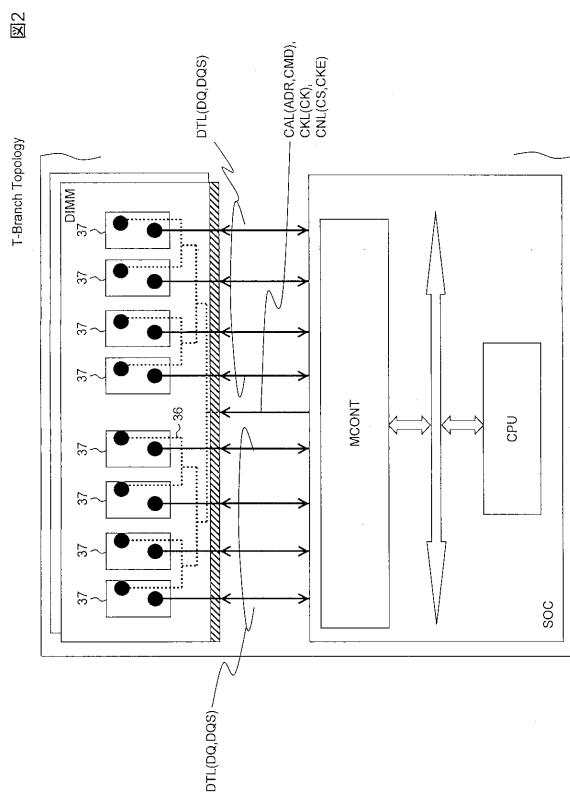

【図2】図2はDDR2-SDRAMから成るT分岐構造のDIMMを搭載したコントロールボードを比較例として示すブロック図である。

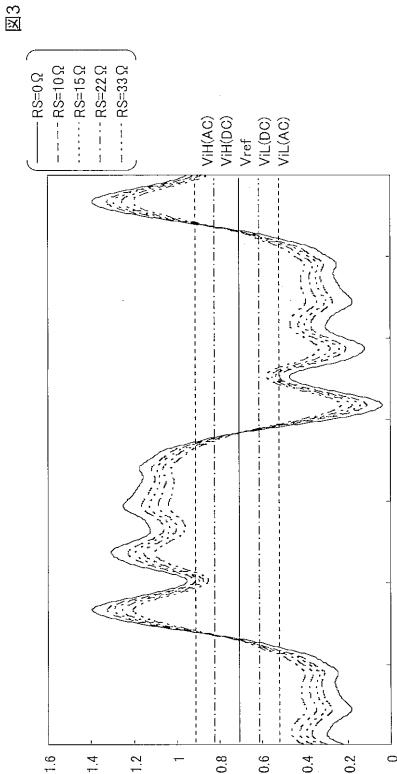

【図3】図3は容量素子Csを採用しない場合の比較例に係るシミュレーション波形を示し、特にモジュール内配線の最も下流（終端抵抗最も近い位置）のDDR3-SDRAM近傍におけるパルス信号のシミュレーション波形を例示する波形図である。

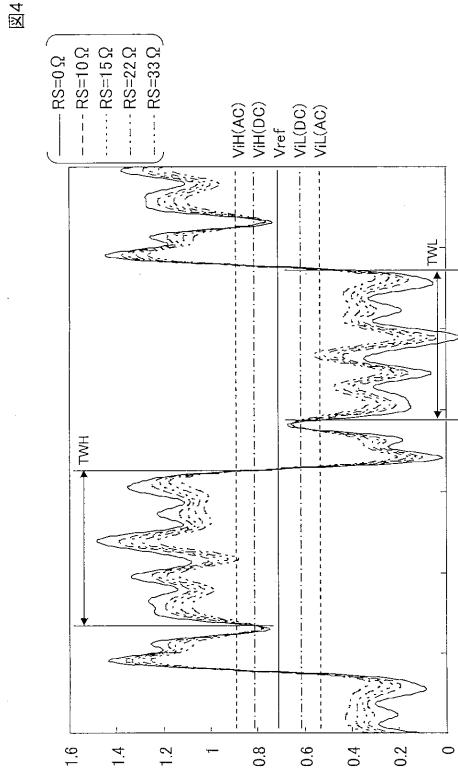

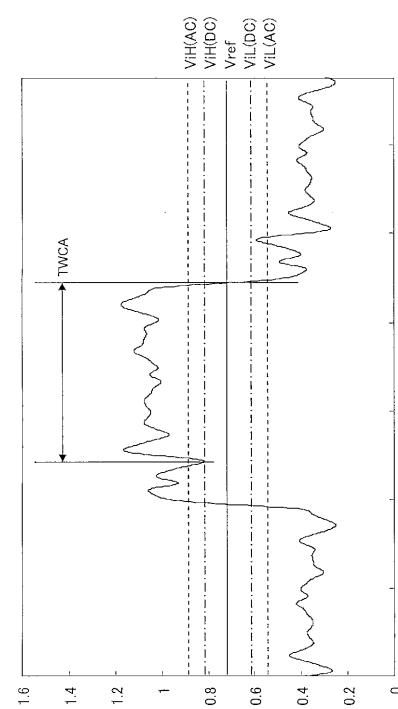

【図4】図4は容量素子Csを採用しない場合の比較例に係るシミュレーション波形を示し、特にモジュール内配線の最も上流（終端抵抗から最も遠い位置）のDDR3-SDRAM近傍におけるパルス信号のシミュレーション波形を例示する波形図である。

40

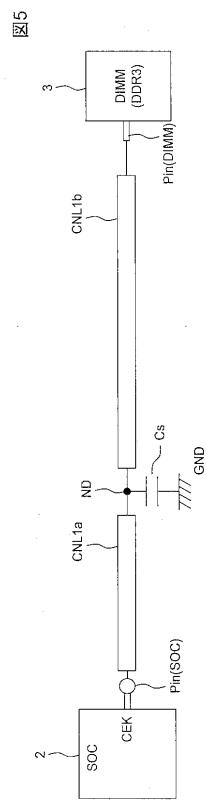

【図5】図5はコントロール系伝送経路CNLの信号線に対する容量素子Csの接続状態がを模式的に示す回路図である。

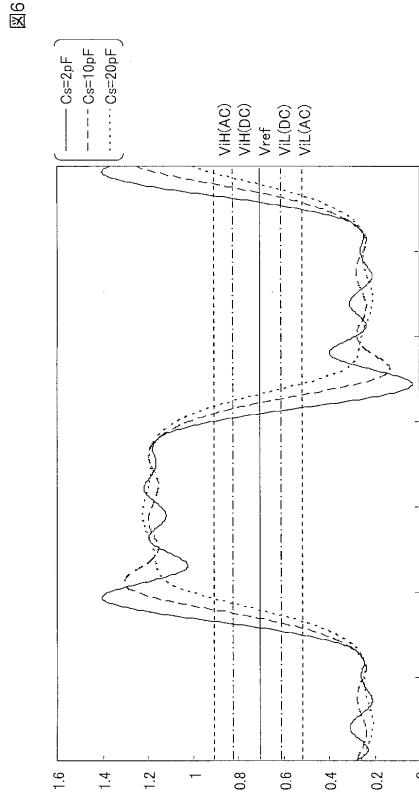

【図6】図6は容量素子Csを採用した場合のシミュレーション波形を示し、特にモジュール内配線の最も下流（終端抵抗に最も近い位置）のDDR3-SDRAM近傍におけるパルス信号のシミュレーション波形を例示する波形図である。

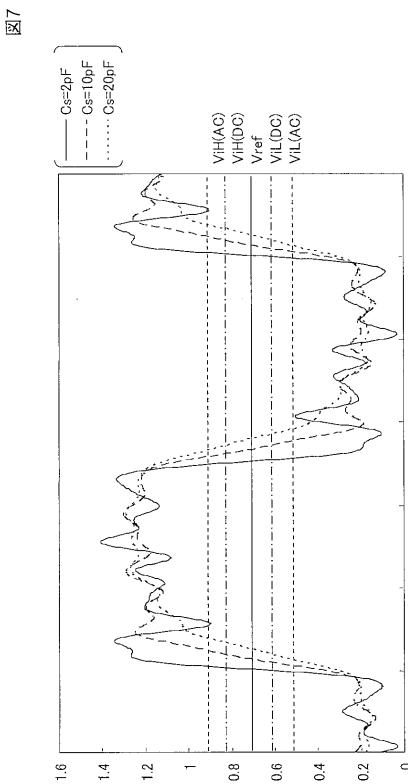

【図7】図7は容量素子Csを採用した場合のシミュレーション波形を示し、特にモジュール内配線の最も上流（終端抵抗から最も遠い位置）のDDR3-SDRAM近傍におけるパルス信号のシミュレーション波形を例示する波形図である。

50

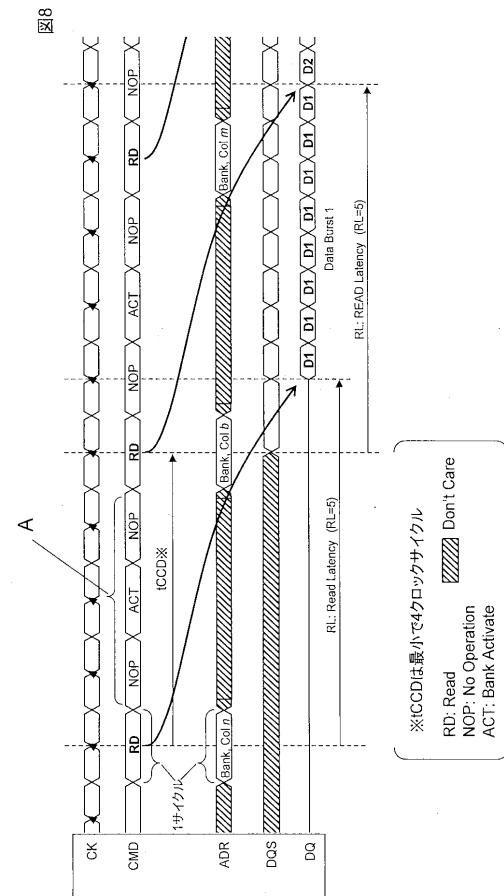

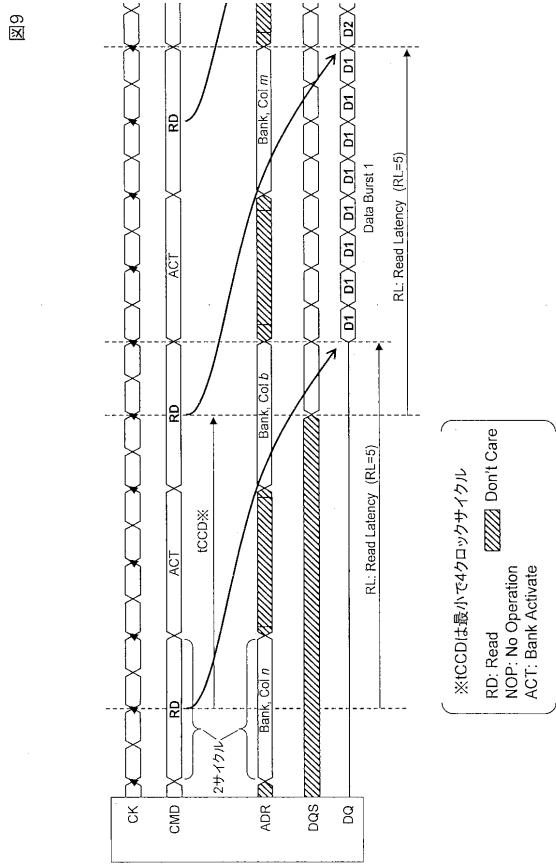

【図8】図8はコマンド及びアドレス信号の有効期間をクロック信号の1サイクルとする場合のリード動作タイミングを例示するタイミングチャートである。

【図9】図9はコマンド及びアドレス信号の有効期間をクロック信号の2サイクルとする場合のリード動作タイミングを例示するタイミングチャートである。

【図10】図10はコマンド及びアドレス信号のタイミングウインドウが狭くなった場合の波形を例示する波形図である。

【図11】図11は図1のコントロールボードの縦断面構造を詳細に示す縦断面図である。

【図12】図12は図1のコントロールボードの平面構造を詳細に示す平面図である。

【図13】図13はS O CやD I M Mを実装する回路基板上の実装面(表面)における容量素子近傍の配線パターンを詳細に例示する平面図である。 10

【図14】図14は回路基板の裏面における容量素子近傍の配線パターンを詳細に例示する平面図である。

#### 【発明を実施するための形態】

##### 【0016】

###### 1. 実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものと例示するに過ぎない。

##### 【0017】

###### [1] <コントロール系配線とGnd間に特定容量を配置>

本発明の代表的な実施の形態に係る電子機器(CNTB)は、第1半導体部品搭載領域(2M)に形成された複数の第1端子(12)、第2半導体部品搭載領域(3M, 4M)に形成された複数の第2端子(11)、および前記複数の第1端子(12)と前記複数の第2端子(11)とをそれぞれ繋ぐ伝送経路(CNL)を有する基板(1)と、前記第1半導体部品搭載領域に搭載された第1半導体部品(2)と、前記第2半導体部品搭載領域に搭載された第2半導体部品(3, 4)と、を含む。前記第2半導体部品は、クロック信号に同期動作される複数のメモリデバイス(31)を有し、前記第1半導体部品は、前記第2半導体部品を制御するメモリコントローラ(22)を有する。前記複数の伝送経路は、前記第1半導体部品から前記第2半導体部品に前記クロック信号(CK)を供給するクロック伝送経路(CKL)、前記第1半導体部品から前記第2半導体部品にコマンド(CMD)及びアドレス信号(ADR)を供給するコマンドアドレス伝送経路(CAL)、前記第1半導体部品と前記第2半導体部品との間でデータ伝送を行うためのデータ系伝送経路(DTL)、及び前記クロック信号と前記コマンド及びアドレス信号の有効性を示すための第1コントロール系信号(CKE, CS)を前記第1半導体部品から前記第2半導体部品に伝送する第1コントロール系伝送経路(CNL(CS, CKE))とを含む。前記基板は更に、グランドプレーン(L2(GND))と、前記第1コントロール系伝送経路の途中から分岐してグランドプレーンに至る第1特定伝送経路(Vi(Cs))と、前記第1特定伝送経路に直列配置された第1容量素子(Cs(CS), Cs(CKE))とを有する。前記第1容量素子は前記第1コントロール系伝送経路の信号伝送方向基端(CNL\_B)から前記第1特定伝送経路への分岐点までの経路の寄生容量よりも大きな容量値を持つ。 30

##### 【0018】

前記第1容量素子は、第1コントロール系伝送経路における寄生容量成分とは区別できる大きさを有し、第1コントロール系信号に重畠されている高調波成分に対してグランドプレーンへのショート経路として機能し、当該容量素子がない場合に比べて前記第1コントロール系信号のスルーレートを小さくし且つそのタイミングウインドウを大きくする。 40

##### 【0019】

第1コントロール系信号はその性質上前記クロック信号と前記コマンド及びアドレス信号の有効性を示すための信号であり、第1コントロール系信号の信号波形の品質劣化すな

10

20

30

40

50

わちタイミングウインドウの狭小化が抑制される結果、第1半導体部品のメモリコントローラが第1コントロール系信号を活性化したクロック信号サイクル内で第2半導体部品はコマンド及びアドレス信号を取り込んでメモリ動作を開始することができる。換言すれば、第1半導体デバイスは第1コントロール系信号を活性化したクロックサイクルから正規のレイテンシを待ってメモリ動作の確定を得ることができる。

#### 【0020】

コマンド及びアドレス信号それ自体の信号伝達経路には高調波成分を抑圧する容量素子を採用しない。コマンド及びアドレス信号は第1コントロール系信号の変化タイミングに従ってその有効性が判別される側の信号であるからその変化タイミングを包含するクロック信号サイクルの単位で信号値が確定されていれば十分であり、第1コントロール系信号ほど厳しいタイミングウインドウは要求されない。このような性質のコマンド及びアドレス信号に対しては高調波成分を抑圧する容量素子を採用しないから、過剰な回路素子による回路規模の増大やコスト上昇が抑制される。10

#### 【0021】

##### 〔2〕<メモリコントローラ寄りに第1容量を配置>

項1記載の電子装置において、前記第1コントロール系伝送経路上における前記第1半導体部品から前記第1特定伝送経路への分岐点までの距離は、前記第1コントロール系伝送経路上における前記分岐点から第2半導体部品までの距離よりも短い。

#### 【0022】

第1半導体部品に近い位置に前記第1容量素子を配置するほど高調波成分による影響を小さくすることができる。20

#### 【0023】

##### 〔3〕<フライ・バイ構造>

項1記載の電子機器において、前記第2半導体部品は、モジュール基板(30)に前記複数のメモリデバイス(31)が搭載されたメモリモジュールであり、前記クロック伝送経路から供給されるクロック信号を受けるモジュール基板内のクロック配線(33)、前記コマンドアドレス伝送経路から供給されるコマンド及びアドレス信号を受けるモジュール基板内の信号線(33)、及び第1コントロール系伝送経路からの第1コントロール系信号を受けるモジュール基板内の信号線(34)に、前記複数のメモリデバイスの対応端子がフライ・バイ形態で接続されている。30

#### 【0024】

T分岐構造のモジュール内配線を有するメモリモジュールを用いる場合に比べてフライ・バイ構造のモジュール内配線を有するメモリモジュールを用いるほうが高調波成分の悪影響を強く受けるからである。

#### 【0025】

##### 〔4〕<DDR3>

項3記載の電子装置において、前記メモリデバイスはDDR3-SDRAMである。前記第1コントロール系信号は、前記DDR3-SDRAMにおけるチップ選択信号(CS)及びクロックイネーブル信号(CKE)である。

#### 【0026】

DDR3-SDRAMを用いたメモリモジュールを採用したときチップ選択信号及びクロックイネーブル信号で顕在化する問題に対処することができる。40

#### 【0027】

##### 〔5〕<ODT配線とGnd間に特定容量を配置>

項1記載の電子機器において、前記複数の伝送経路は更に、前記データ系伝送経路の伝送特性を選択的に切り換えるための第2コントロール系信号(ODT)を前記第1半導体部品から前記第2半導体部品に伝送する第2コントロール系伝送経路CNL(ODT)を含む。前記基板は更に、前記第2コントロール系伝送経路の途中から分岐してグランドブレーンに至る第2特定伝送経路(Vi(CS))と、前記第2特定伝送経路の途中に直列配置された第2容量素子(Cs(ODT))とを有する。前記第2容量素子は前記第2コ50

ントロール系伝送経路の信号伝送方向基端から前記第2特定伝送経路への分岐点までの経路の寄生容量よりも大きな容量値を持つ。

【0028】

前記第2容量素子は、第2コントロール系伝送経路における寄生容量成分とは区別できる大きさを有し、第2コントロール系信号に重畠されている高調波成分に対してグランドプレーンへのショート経路として機能し、当該容量素子がない場合に比べて前記イネーブル制御信号のスルーレートを小さくし且つそのタイミングウインドウを大きくする。

【0029】

第2コントロール系信号はデータ系伝送経路の伝送特性を選択的に切り換えるための信号であり、この信号の信号波形の品質劣化すなわちタイミングウインドウの狭小化が抑制される結果、第1半導体部品のメモリコントローラが第2コントロール系信号を活性化したクロック信号サイクル内で第2半導体部品はデータ伝送系の伝送特性を切り換えることができる。

【0030】

〔6〕<メモリコントローラ寄りに第2容量を配置>

項5記載の電子装置において、前記第2コントロール系伝送経路上における前記第1半導体部品から前記第2特定伝送経路への分岐点までの距離は、前記第2コントロール系伝送経路上における前記分岐点から第2半導体部品までの距離よりも短い。

【0031】

第1半導体部品に近い位置に前記第2容量素子を配置するほど高調波成分による影響を小さくすることができる。

【0032】

〔7〕<フライ・バイ構造>

項5記載の電子機器において、前記第2半導体部品は、モジュール基板に前記複数のメモリデバイスが搭載されたメモリモジュールであり、前記クロック伝送経路から供給されるクロック信号を受けるモジュール基板内のクロック配線、前記コマンドアドレス伝送経路から供給されるコマンド及びアドレス信号を受けるモジュール基板内の信号線、第1コントロール系伝送経路からの第1コントロール系信号を受けるモジュール基板内の信号線、及び前記第2コントロール系伝送経路から供給される第2コントロール系信号を受けるモジュール基板内の信号線に、前記複数のメモリデバイスの対応端子がフライ・バイ形態で接続されている。

【0033】

T分岐構造のモジュール内配線を有するメモリモジュールを用いる場合に比べてフライ・バイ構造のモジュール内配線を有するメモリモジュールを用いるほうが高調波成分の悪影響を強く受けるからである。

【0034】

〔8〕<DDR3>

項7記載の電子装置において、前記第2半導体部品はDDR3-SDRAMであり、前記メモリデバイスは、前記データ系伝送経路に対応する終端抵抗として利用可能なオンダイターミネーションを有し、前記入力端子から入力される選択信号は、前記オンダイターミネーションの有効又は無効を指示するオンダイターミネーション指示信号である。

【0035】

DDR3-SDRAMを用いたメモリモジュールを採用したときオンダイターミネーション指示信号で顕在化する問題に対処することができる。

【0036】

〔9〕<コントロール系伝送経路は多層配線基板の最上層、最下層において引き回し>

項5記載の電子装置において、前記基板は複数の配線層(L1～L6)を有し、前記第1コントロール系伝送経路及び第2コントロール系伝送経路は、前記複数の配線層のうちの最上層(L1)および最下層(L6)のそれぞれの配線層に形成され、前記複数の第1端子及び第2端子のそれぞれは前記複数の配線層のうちの最上層に形成されている。

10

20

30

40

50

## 【0037】

基板に第1半導体部品及び第2半導体部品を搭載するのに有利である。

## 【0038】

[10] <複数の容量素子をグランドプレーンに接続するビア配線の共通化>

項9記載の電子装置において、前記グランドプレーンは、前記複数の配線層のうちの最上層と最下層との間の内層の配線層に形成される。前記特定電層経路は、前記基板に形成されたスルーホールに設けられたビア配線(Vicrom)を介して前記グランドプレーンとそれぞれ電気的に接続される。前記ビア配線のそれぞれは、平面視において、前記第1コントロール系伝送経路及び第2コントロール系伝送経路に含まれる互いに隣り合う配線に共通接続される。

10

## 【0039】

[11] <フライ・バイ構造のコントロール系配線とGnd間に特定容量を配置>

本発明の別の実施の形態に係る電子機器は、基板に第1半導体部品と前記第1半導体部品が制御する第2半導体部品が搭載された機器であって、前記第2半導体部品はクロック信号に同期動作される複数のメモリデバイスを有する。前記基板は前記第2半導体部品を前記第1の半導体部品に接続するための複数の信号経路を有する。前記複数の信号経路は、前記第1半導体部品から前記第2半導体部品に前記クロック信号を供給するクロック伝送経路、前記第1半導体部品から前記第2半導体部品にコマンド及びアドレス信号を供給するコマンドアドレス伝送経路、前記第1半導体部品と前記第2半導体部品との間でデータ伝送を行うためのデータ系伝送経路、及び前記クロック信号と前記コマンド及びアドレス信号の有効性を示すための第1コントロール系信号を前記第1半導体部品から前記第2半導体部品に伝送する第1コントロール系伝送経路とを含む。前記基板は更に、グランドプレーンと、前記第1コントロール系伝送経路の途中から分岐してグランドプレーンに至る特定伝送経路と、前記特定伝送経路に直列配置された容量素子とを有する。前記容量素子は、それがない場合に比べて前記第1コントロール系信号のスルーレートを小さくし且つタイミングウインドウを大きくする。

20

## 【0040】

前記第1容量素子は、第1コントロール系信号に重畠されている高調波成分に対してグランドプレーンへのショート経路として機能し、当該容量素子がない場合に比べて前記第1コントロール系信号のスルーレートを小さくし且つそのタイミングウインドウを大きくする。

30

## 【0041】

第1コントロール系信号の信号波形の品質劣化すなわちタイミングウインドウの狭小化が抑制される結果、第1半導体部品のメモリコントローラが第1コントロール系信号を活性化したクロック信号サイクル内で第2半導体部品はコマンド及びアドレス信号を取り込んでメモリ動作を開始することができる。換言すれば、第1半導体デバイスは第1コントロール系信号を活性化したクロックサイクルから正規のレイテンシを待ってメモリ動作の確定を得ることができる。

## 【0042】

コマンド及びアドレス信号それ自体の信号伝達経路には高調波成分を抑圧する容量素子を採用しないから、過剰な回路素子による回路規模の増大やコスト上昇が抑制される。

40

## 【0043】

[12] <ODT配線とGnd間に特定容量を配置>

項11記載の電子機器において、前記複数の伝送経路は更に、前記データ系伝送経路の伝送特性を選択的に切り換えるための前記第2コントロール系信号を前記第1半導体部品から前記第2半導体部品に伝送する第2コントロール系伝送経路を含む。前記基板は更に、前記第2コントロール系伝送経路の途中から分岐してグランドプレーンに至る第2特定伝送経路と、前記第2特定伝送経路の途中に直列配置された第2容量素子を有する。前記第2容量素子は、それがない場合に比べて前記第2コントロール系信号のスルーレートを小さくし且つタイミングウインドウを大きくする。

50

## 【0044】

前記第2容量素子は、第2コントロール系信号に重畠されている高調波成分に対してグランドプレーンへのショート経路として機能し、当該容量素子がない場合に比べて前記イネーブル制御信号のスルーレートを小さくし且つそのタイミングウインドウを大きくする。

## 【0045】

第2コントロール系信号はデータ系伝送経路の伝送特性を選択的に切り換えるための信号であり、この信号の信号波形の品質劣化すなわちタイミングウインドウの狭小化が抑制される結果、第1半導体部品のメモリコントローラが第2コントロール系信号を活性化したクロック信号サイクル内で第2半導体部品はデータ伝送系の伝送特性を切り換えることができる。10

## 【0046】

## 〔13〕&lt;フライ・バイ構造&gt;

項12記載の電子機器において、前記クロック伝送経路から供給されるクロック信号を受けるモジュール基板内のクロック配線、前記コマンドアドレス伝送経路から供給されるコマンド及びアドレス信号を受けるモジュール基板内の信号線、及び第1コントロール系伝送経路からの第1コントロール系信号を受けるモジュール基板内の信号線に、前記複数のメモリデバイスの対応端子がフライ・バイ形態で接続されている。

## 【0047】

T分岐構造のモジュール内配線を有するメモリモジュールを用いる場合に比べてフライ・バイ構造のモジュール内配線を有するメモリモジュールを用いるほうが高調波成分の悪影響を強く受けるからである。20

## 【0048】

## 〔14〕&lt;フライ・バイ構造&gt;

項13記載の電子機器において、前記第2半導体部品は、前記第2コントロール系伝送経路から供給される第2コントロール系信号を受けるモジュール基板内の信号線に前記複数のメモリデバイスの対応端子がフライ・バイ形態で接続されている。

## 【0049】

T分岐構造のモジュール内配線を有するメモリモジュールを用いる場合に比べてフライ・バイ構造のモジュール内配線を有するメモリモジュールを用いるほうが高調波成分の悪影響を強く受けるからである。30

## 【0050】

## 〔15〕&lt;DDR3&gt;

項14記載の電子装置において、前記メモリデバイスはDDR3-SDRAMであり、前記第1コントロール系信号は、DDR3-SDRAMにおけるチップ選択信号及びクロックイネーブル信号である。

## 【0051】

DDR3-SDRAMを用いたメモリモジュールを採用したときチップ選択信号及びクロックイネーブル信号で顕在化する問題に対処することができる。

## 【0052】

## 〔16〕&lt;DDR3&gt;

項15記載の電子装置において、前記メモリデバイスは、前記データ系伝送経路に対応する終端抵抗として利用可能なオンダイターミネーションを有し、前記入力端子から入力される選択信号は、前記オンダイターミネーションの有効又は無効を指示するオンダイターミネーション指示信号である。

## 【0053】

DDR3-SDRAMを用いたメモリモジュールを採用したときオンダイターミネーション指示信号で顕在化する問題に対処することができる。

## 【0054】

2. 実施の形態の詳細

10

20

30

40

50

実施の形態について更に詳述する。

**【0055】**

《DIMMを搭載したコントロールボード》

図1には本発明に係る電子機器の一実施の形態がブロック図によって示される。同図には、特に制限されないが、プリンタやイメージスキャナなどの機器に搭載されてその動作を制御するコントロールボードが示される。同図に示されるコントロールボードCNTBは、制御対象機器に応じた制御機能を実現するためのシステムオンチップのマイクロコンピュータ(SOC、半導体部品)2と、マイクロコンピュータ2のワーク領域などに用いられるメモリモジュールとしてのDIMM(半導体部品)3,4などが配線基板1に実装されて成る。図示は省略するが配線基板1にはその他の半導体部品が実施されてよいことは言うまでもない。マイクロコンピュータ2は第1半導体部品の一例であり、DIMM3,4は第2半導体部品の一例である。

10

**【0056】**

マイクロコンピュータ2は、特に制限されないが、中央処理装置(CPU)21と共にメモリコントローラ(MCONT)22や図示を省略する周辺回路モジュールなどが内部バス23に接続されて構成され、CPU21がプログラムにしたがって命令を実行することによって機器制御を行う。メモリコントローラ22は、特に制限されないが、DDR3-SDRAMやDDR2-SDRAMに対するメモリインターフェース制御機能を備える。ここでは、DIMM3,4はDDR3-SDRAMを搭載して構成されるものとする。CPU21などによるアクセス対象がDIMM3,4であるとき、メモリコントローラ22は内部バス23から供給されるアクセスアドレスにしたがってDIMM3,4のDDR3-SDRAMをアクセスするために必要なタイミングでインターフェース信号を生成してDIMM3,4を制御する。

20

**【0057】**

マイクロコンピュータ2とDIMM3,4との接続は配線基板1上の配線などによって構成される伝送経路によって接続される。伝送経路は、前記マイクロコンピュータ1からDIMM3,4にクロック信号CKを供給するクロック伝送経路CKL、マイクロコンピュータ2からDIMM3,4にコマンドCMD及びアドレス信号ADRを供給するコマンドアドレス伝送経路CAL、マイクロコンピュータ2とDIMM3,4との間でデータDQ及びデータストローブ信号DQSなどの伝送を行うためのデータ系伝送経路DTL、及びマイクロコンピュータ2からDIMM3,4にコントロール信号としてチップ選択信号CS、クロックイネーブル信号CKE及びオンダイターミネーション信号ODTを供給するためのコントロール系伝送経路CNLからなる。ここではクロック信号CKは差動クロック信号である。コマンドCMDはローアドレスストローブ信号(RAS)、カラムアドレスストローブ信号(CAS)、及びライトイネーブル信号(WE)などのストローブ信号のレベルの組み合わせに応じてコマンドを指示するクロック信号CKはクロックイネーブル信号CKEのアサートによって有意とされ、DDR3-SDRAMはクロック信号CKの立ち上がりと立下りの夫々のタイミングに同期して外部へのデータの読み出し及び書き込みが可能にされる。DDR3-SDRAMに対するコマンド入力はチップセレクト信号(CS)がイネーブルレベルのときに有効とされ、コマンドは信号RAS、CAS、WEのレベルの組合せ等によって指示される。コマンドにはローアドレス系のアクティブコマンド(ACT)、カラムアドレス系コマンドとしてのリードコマンド(RD)及びライトコマンド(WR)等がある。アクティブコマンドはローアドレスを指示してローアドレス系をアクティブにするためのコマンドである。リードコマンドは、ローアドレス系がアクティブにされた後にカラムアドレスを指示してカラム系をリード動作させるコマンドである。ライトコマンドはローアドレス系がアクティブにされた後にカラムアドレスを指示してカラム系をライト動作させるコマンドである。ライトコマンド及びリードコマンドで指示されるカラム系動作はバーストアクセス動作とされ、カラムアドレスで指示されたアドレスを基点にバースト数分のデータを連続的にリード又はライトする。DDR3-SDRAMはバースト数8を基本とする。ライトコマンド及びリードコマンドで指示されるカラ

30

40

50

ム系動作によって最初の読み出しデータが確定し、あるいは最初に書き込みデータを入力可能になるまでには、カラム系回路の動作が所定の状態に到達するのを待たなければならない。リード動作におけるそのような遅延時間をリードレイテンシ、ライト動作におけるそのような遅延時間をライトレイテンシと称し、回路構成上クロック信号CKの複数周期分の時間として決められる。オンダイターミネーション信号ODTはDDR3-SDRAMが内蔵するデータ系配線の終端に配置された終端抵抗を有効にするか否かを指示する信号であり、DQ, DQSなどのデータ系信号のチップ内配線に対してだけ有意とされる。

#### 【0058】

前記チップ選択信号CSはコマンド及びアドレス信号の有効性を示すための第1コントロール系信号、クロックイネーブル信号CKEはクロック信号の有効性を示すための第1コントロール系信号の一例とされ、オンダイターミネーション信号ODTはデータ系伝送経路の伝送特性を選択的に切り換えるための第2コントロール系信号の一例とされる。

#### 【0059】

DDR3-SDRAMを搭載したDIMM3, 4の構成は非特許文献2に示される仕様に準拠して構成される。例えばその詳細が代表的に示されたDIMM3は、モジュール内配線が形成されたモジュール基板30に搭載された複数個のDDR3-SDRAM31を有し、モジュール基板30の一長手辺にはモジュールインターフェース端子列32が形成され、このモジュールインターフェース端子列32を介して配線基板1の装着コネクタに結合される。上記非特許文献2の記載からも明らかのように、DIMM3, 4において、モジュールインターフェース端子列32とDDR3-SDRAM31の対応端子とを接続する一部のモジュール内配線にはフライ・バイ構造を採用する。すなわち、クロック信号CK、コマンドCMD及びアドレス信号ADRの夫々のモジュール内配線33と、コントロール信号CS, CKE, ODTの夫々のモジュール内配線34には、一筆書きされる信号線に複数のDDR3-SDRAM31の対応外部端子を順次数珠繋ぎの形態で接続する構造が採用される。更に、夫々のモジュール内配線33, 34の信号線にはモジュール基板30上に予め設けられた終端抵抗(Rtt)35が接続される。図1においてモジュール内配線33, 34及び終端抵抗35は便宜上夫々一個を代表的に図示しているが、実際には信号ごとに設けられている。データDQ及びデータストローブ信号DQSに対応するモジュール内配線36は信号ごとに個別化されている。

#### 【0060】

DIMM3, 4のモジュール内配線33, 34に採用したフライ・バイ構造に対し、図2の比較例に示されるようにDDR2-SDRAM37を搭載したDIMMのモジュール内配線のうち、クロック信号CK、コマンドCMD、アドレス信号ADR、コントロール信号CS, CKEの夫々のモジュール内配線36には等長化を目的としたT分岐構造が採用される。

#### 【0061】

DIMM3, 4ではモジュール内配線33, 34がフライ・バイ構造で短配線にされ、T分岐構造を採用したときのように無理に配線の等長化を行うことによって逆に配線の引き回しが多くなって信号の波形品質が劣化する虞はない。DIMM3, 4における配線の非等長化に対してはクロック信号CKなどの伝播遅延に合わせてデータストローブ信号DQSの入力タイミングなどを遅延させるレベリング制御で対処することになっている。レベリング制御の対象にならないフライ・バイ構造のモジュール内配線33, 34では入力信号の上流側のDDR3-SDRAMはそれよりも下流側のDDR3-SDRAMの入力容量成分を介して反射されるノイズを重畠的に受ける結果、信号経路の上流に近いDDR3-SDRAMの入力信号波形ほど歪むこととなる。このような歪みを緩和してタイミングウインドウが不所望に狭くならないようするために、コントロール系伝送経路CNLのチップ選択信号CS, クロックイネーブル信号CKE及びオンダイターミネーション信号ODTの各信号線には配線基板1のグランドパターンとの間に容量素子Csを直列配置する。

#### 【0062】

10

20

30

40

50

### 《C sによる波形改善作用》

容量素子C sによる波形改善作用をシミュレーション波形などを用いて説明する。

#### 【0063】

図3、図4は容量素子C sを採用しない場合の比較例に係るシミュレーション波形を示す。図3にはモジュール内配線33, 34の最も下流（終端抵抗35に最も近い位置）のDDR3-SDRAM近傍におけるパルス信号のシミュレーション波形が例示され、図4にモジュール内配線33, 34の最も上流（終端抵抗35から最も遠い位置）のDDR3-SDRAM近傍におけるパルス信号のシミュレーション波形が例示される。各シミュレーション波形は基板上1における対応するシリーズ抵抗（SR）の値を0乃至33で調整したときに対応される。伝送線の信号反射による影響を緩和するには伝送線の終端抵抗とシリーズ抵抗の値を調整して対処することが望ましいが、DIMM3, 4の終端抵抗35の値はDIMM3, 4のモジュール基板30で予め決められていて調整対象にはならず、シリーズ抵抗SRの値だけを調整しても良好な波形改善を得ることは難しい。その上、メモリ動作周波数（クロック信号CKの周波数）が高くなるにしたがって信号波形に重畠される高調波成分（高周波成分）が多くなり、その高調波成分に反射波が重畠され、波形改善を更に困難にしている。特に、モジュール内配線33, 34はフライ・バイ構造であるが故に、図4のように終端抵抗35から最も遠いDDR3-SDRAMへの入力波形の歪が最も大きくなり、ハイレベルの信号波形の立ち上がり直後にそのレベルがハイレベルの閾値電圧ViH(DC)よりも低くなる期間を生じ、また、ローレベルの信号波形の立ち下がり直後にそのレベルがローレベルの閾値電圧ViL(DC)よりも高くなる期間を生じ、ハイレベルのタイミングウインドウTWHとローレベルのタイミングウンドウTWLが狭くなる。10

#### 【0064】

図5にはコントロール系伝送経路CNLの信号線に対する容量素子C sの接続状態が模式的な回路図で例示される。ここではクロックイネーブル信号CKEの信号線CNL1を代表的に示す。信号線CNL1はCNL1aとCNL1bの部分に分けて図示してある。Pin(SOC)はマイクロコンピュータ1におけるクロックイネーブル信号CKEの出力端子、Pin(DIMM)はDIMM3におけるクロックイネーブル信号CKEの入力端子である。容量素子C sの一端はCNL1aとCNL1bの接続点NDに結合され、容量素子C sの他端は回路基板の回路基板のグランドプレーン、すなわちグランド電圧GNに接続される。出力端子Pin(SOC)から接続点NDまでの配線経路長は。接続点NDから入力端子Pin(DIMM)までの配線経路長よりも短く、接続点NDは極力入力端子Pin(SOC)の近傍にされる。20

#### 【0065】

容量素子C sはクロックイネーブル信号CKEに重畠されて出力される高調波成分、すなわち高周波成分に対してショート、それよりも低周波成分に対してはオープンとして機能するから、接続ノードNDを超えて信号配線CNL1bに至るクロックイネーブル信号CKEから高調波成分が抑圧される。この結果、DIMM3のモジュール内配線の最上流に位置するDDR3-SDRAMのクロックイネーブル信号CKEの入力端子近傍の信号波形がそれよりも下流のDDR3-SDRAMの入力容量などからの反射波の影響を受けても前述の高調波成分による影響が少なくなり、その結果、信号反射の影響による信号波形の歪みは小さくされる。容量素子C sが出力端子Pin(SOC)の近傍であればあるほど信号反射に対する高調波成分の関与を小さくすることができる。30

#### 【0066】

図6、図7は容量素子C sを採用した場合のシミュレーション波形を示す。図6にはモジュール内配線33, 34の最も下流（終端抵抗35に最も近い位置）のDDR3-SDRAM近傍におけるパルス信号のシミュレーション波形が例示され、図7にモジュール内配線33, 34の最も上流（終端抵抗35から最も遠い位置）のDDR3-SDRAM近傍におけるパルス信号のシミュレーション波形が例示される。各図には、基板上1において、対応する容量素子C sの値を2pF, 10pF, 20pFとしたときのシミュレーシ4050

ヨン波形を示す。図6及び図7のいずれにおいても容量素子C<sub>s</sub>の容量値が10pFのとき最も良好な波形改善効果を得ることができる。容量素子C<sub>s</sub>の容量値が20pFの場合には波形の鈍りが大きくなりすぎる。図6,7のシミュレーション波形から明らかのように、容量素子C<sub>s</sub>は周波数の高いパルス状信号に重畠された高調波成分を伝送線路の上流端近傍で抑圧して、当該パルス状信号のスルーレートを小さくするように作用する。スルーレートが小さくなりすぎると逆にタイミングウインドウも小さくなってしまうので、容量素子C<sub>s</sub>の容量値は10pFのような特定値でタイミングウインドウを最大とする最適値が存在するが、具体的な値は伝送条件によって相違され、例えば、DDR3-SDRAMの外部入力端子の入力容量である1.5pFの2乃至20倍の範囲で決定すればよいと考えられる。この容量素子C<sub>s</sub>を機能的に規定すれば、前記容量素子C<sub>s</sub>は、それがない場合に比べてクロックイネーブル信号CKEのようなコントロール系信号のスルーレートを小さくし且つタイミングウインドウを大きくするものとされる。また、この容量素子C<sub>s</sub>は、端子Pin(SOC)からノードNDに至る配線の寄生容量よりも大きな容量値として規定される。信号のスルーレートを緩和させるという作用は抵抗素子を用いても行うことができるが、DDR3-DIMMのように終端抵抗の値が一定の場合には、振幅が小さくなってしまい、容量素子C<sub>s</sub>を用いたときのような高調波成分の吸収という作用を期待することはできず、DRAMスペックを満足できない。容量素子C<sub>s</sub>の採用は、一見するとデバイスの入力容量と同じく信号反射に悪影響を及ぼすと懸念されるであろうが、高調波成分を吸収することによって得られる信号波形歪の抑圧効果の方が、DDR3-SDRAMに対する良好なアクセス制御上優位となる。

#### 【0067】

特に図示はしないが、コントロール系伝送経路CNLのチップ選択信号CS及びオンダイタミネーション信号ODTの各信号線の容量素子C<sub>s</sub>についても同様であるからその詳細な説明は省略する。

#### 【0068】

コントロール系伝送経路CNLのクロックイネーブル信号CKE及びチップ選択信号CSはその性質上前記クロック信号と前記コマンド及びアドレス信号の有効性を示すための信号であり、クロックイネーブル信号CKE及びチップ選択信号CSの信号波形の品質劣化すなわちタイミングウインドウの狭小化を前記容量素子C<sub>s</sub>の採用によって抑制する結果、マイクロコンピュータ2のメモリコントローラ22がクロックイネーブル信号CKEやチップ選択信号CSを活性化したクロック信号サイクル内でDIMM3,4はコマンド及びアドレス信号を取り込んでメモリ動作を開始することができる。換言すれば、マイクロコンピュータ2はクロックイネーブル信号CKEやチップ選択信号CSを活性化したクロックサイクルから正規のレイテンシを待ってメモリ動作の確定を得ることができる。

#### 【0069】

DDR3-SDRAMにオンチップされているオンダイタミネーションによるデータ系伝送経路の伝送特性を選択的に切り換えるための信号であるオンダイタミネーション信号ODTのコントロール系伝送経路CNLに対しても容量素子C<sub>s</sub>を設けることにより、上記同様にオンダイタミネーション信号ODTの信号波形のタイミングウインドウの狭小化を抑制することができるから、マイクロコンピュータ2のメモリコントローラ22がオンダイタミネーション信号ODTを活性化したクロック信号サイクル内でDIMM3,4はデータ系伝送系の伝送特性を切り換えることができる。クロック信号サイクル内でデータ系伝送系の伝送特性を切り換えることができない場合には、それによって切換えが遅れたサイクルでデータ系信号配線における不所望な信号反射の影響を強く受ける虞を生ずる。

#### 【0070】

コマンドアドレス伝送経路CALに接続するモジュール内配線33についてもフライ・バイ構造が採用されているので、図4など説明したと同様に高調波によりタイミングウインドウが狭小化される。しかしながら、以下の理由により、コマンドアドレス伝送経路CALには容量素子C<sub>s</sub>を設けることはしない。

## 【0071】

第1には、コマンド及びアドレス信号は、コントロール系信号のひとつであるチップ選択信号C Sの変化タイミングに従ってその有効性が判別される側の信号であるから、その変化タイミングを包含するクロック信号サイクルの単位で信号値が確定されていれば十分であり、チップ選択信号のような信号コントロール系信号ほど厳しいタイミングウンドウは要求されない。このような性質のコマンド及びアドレス信号に対しては高調波成分を抑圧する容量素子C sを採用しないから、容量素子C sによる回路規模の増大やコスト上昇を最小限に抑えることができる。

## 【0072】

第2には、DDR3 - SDRAMの規格上、コマンド及びアドレス信号の有効サイクルをクロック信号の2サイクルに拡大することが可能であるから、そうすることにより、当該信号のタイミングウンドウが多少狭くなっても実質的な支障を生じ難い。すなわち、チップセレクト信号C Sに代表されるコントロール信号（アクセスストローブ信号）はクロック信号C Kのサイクル時間と同じ時間でイネーブルレベルに制御され、チップセレクト信号C Sのローレベル期間で有効にされるコマンド及びアドレス信号はクロック信号の2サイクル単位で変化させることが許容される。例えば、図8にはコマンド及びアドレス信号の有効期間をクロック信号C Kの1サイクル（1クロックサイクル）とする場合のリード動作タイミングが例示され、図9にはコマンド及びアドレス信号の有効期間をクロック信号の2サイクル（2クロックサイクル）とする場合のリード動作タイミングが例示される。何れの場合にもリードレイテンシ（RL）は5クロックサイクルとされ、また、カラム系コマンドの間は最小で3クロックサイクル分空けることが必要とされるものとする。図8においてアドレス・コマンド信号の有効期間を1クロックサイクルとする場合、カラム系コマンドの間にはAの部分で示されるように最低3クロックサイクル空く。この3クロックサイクルの空きに着目すると、図9のようにコマンド及びアドレス信号の有効期間を2クロックサイクルにしても読み込み動作のデータレートとタイミングは図8と同じになる。したがって、図10に例示されるようにコマンド及びアドレス信号にタイミングウンドウがT W C Aのように狭くなっても実質的な支障を生じ難い。なお、図示はないが、書き込みの場合も同様である。

10

20

## 【0073】

## 《C sのレイアウト構成》

30

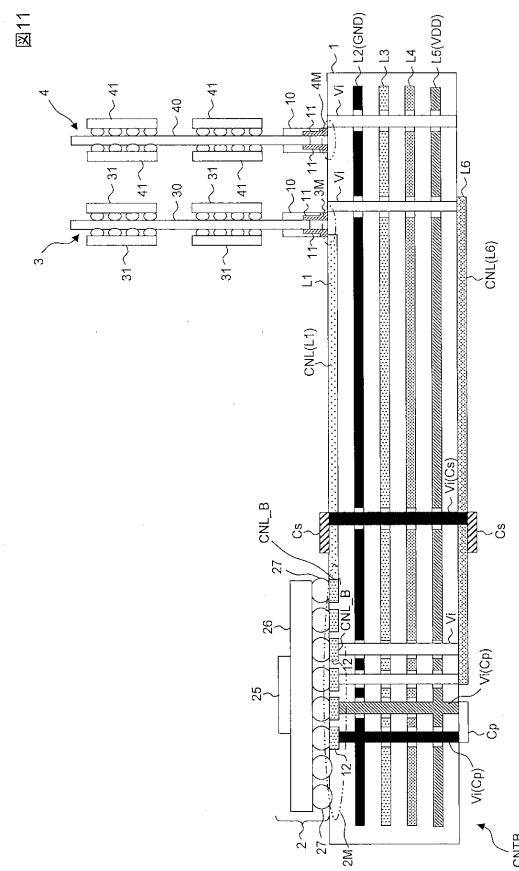

図11は図1のコントロールボードの縦断面構造を詳細に示す。

## 【0074】

コントロールボードC NTBの配線基板1は、特に制限されないが、ガラスエポキシ樹脂基板に6層の配線層L 1～L 6が夫々絶縁されて形成され、配線層L 1～L 6の間の電気的な接続は、配線基板1の表裏方向にスルーホールを設け、スルーホールに金属を充填したビア配線V iを導電接続の対象とする配線層の配線に結合することによって行われる。配線層L 2には回路のグランド電位G NDが与えられるグランドプレーンが形成され、配線層L 5には電源電圧V DDが与えられる電源プレーンが形成される。配線層L 1, L 3, L 4, L 6には所望の信号配線、電源配線、及びグランド配線などが形成される。

40

## 【0075】

上記DIMM3, 4はメモリモジュールコネクタ10に着脱自在に搭載され、DIMM3, 4の前記モジュールインターフェース端子列の端子はメモリモジュールコネクタ10の対応端子に接触されて、配線層L 1, K 4, L 6の信号配線、電源配線及びグランド配線に接続される。

## 【0076】

マイクロコンピュータ2は底面に実装用の半田バンプ電極27を有するパッケージ26と、パッケージ26の表面の電極パッド（図示せず）に搭載したマイクロコンピュータチップ25とから成る。パッケージ26には半田バンプ電極27を対応する電極パッドに接続するパッケージ配線が形成されている。マイクロコンピュータ2の半田バンプ27は配線層L 1に形成された対応する電極パッド12の上に載置されて結合固定される。C pは

50

電源安定化のためのバイパスコンデンサであり、一例として回路基板1の裏面に配置され、ビア配線Vi(Cp)を介してマイクロコンピュータ1に接続される。2Mはマイクロコンピュータ2の搭載領域を概念的に示し、3MはDIMM3の搭載領域を概念的に示し、4MはDIMM4の搭載領域を概念的に示したものである。

#### 【0077】

図11にはコントロール系伝送経路CNLの配線としてコントロール配線CNL(L1)、CNL(L6)が例示される。コントロール配線CNL(L1)は配線層L1に形成され、コントロール配線CNL(L6)は配線層L6に形成される。コントロール配線CNL(L1)、CNL(L6)のマイクロコンピュータ2寄りの位置には夫々容量素子Csの一方の容量電極が結合され、双方の容量素子Csの他方の容量電極は共通のビア配線Vi(Cs)に接続され、当該ビア配線Vi(Cs)は配線層のグランドプレーンL2(GND)に接続される。

10

#### 【0078】

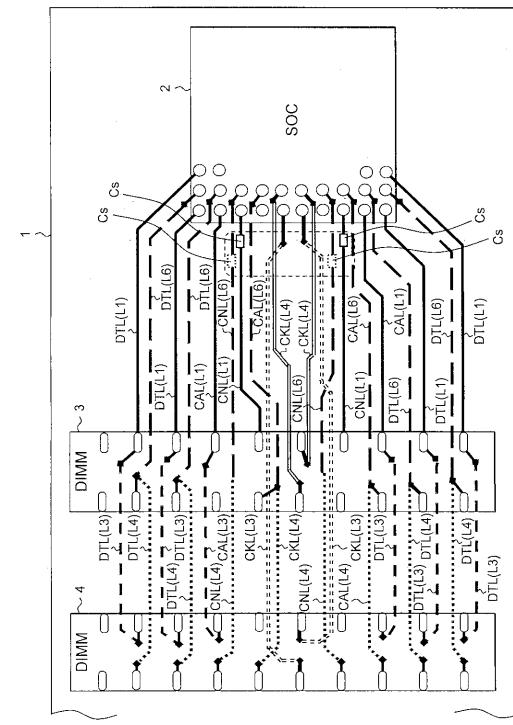

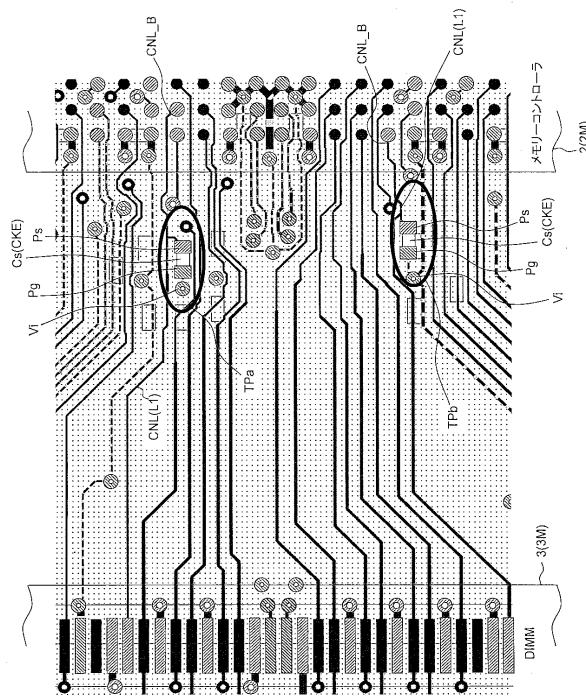

図12は図1のコントロールボードの平面構造を詳細に示す。

#### 【0079】

同図にはクロック伝送経路CKLとして配線層L3に形成されたクロック配線CKL(L3)、配線層L4に形成されたクロック配線CLK(L4)が代表的に示される。コマンドアドレス伝送経路CALとして配線層L1に形成されたコマンドアドレス配線CAL(L1)、配線層L6に形成されたコマンドアドレス配線CAL(L6)などが代表的に示される。データ系伝送経路DTLとして配線層L6に形成されたデータ系配線DTL(L1)、配線層L6に形成されたデータ系配線DTL(L6)などが代表的に示される。コントロール系伝送経路CNLとして配線層L6に形成されたコントロール系配線CNL(L1)、配線層L6に形成されたコントロール系配線CNL(L6)などが代表的に示される。

20

#### 【0080】

マイクロコンピュータ2の近傍においてコントロール系配線CNL(L1)、CNL(L6)には前記容量素子Csが接続されている。

#### 【0081】

図13にはSOCやDIMMを実装する回路基板上の実装面(表面)における容量素子近傍の配線パターンが詳細に例示される。

30

#### 【0082】

TPaの部分に例示される容量素子Cs(CKE)はコントロール系配線CNL(L1)に接続される容量素子であり、例えばここではコントロール系配線CNL(L1)に伝達されるクロックイネーブル信号CKEのスルーレートを緩和するために用いられる。Psは当該コントロール系配線CNL(L1)に結合する電極パッド、Pgはビア配線Viを介してグランドプレーンL2(GND)に結合する電極パッドであり、容量素子Cs(CKE)の夫々の容量電極は対応する電極パッドPs、Pgに半田などで固定される。容量素子Cs(CKE)にはチップコンデンサなどを用いればよい。TPbで示される部分についても同様である。

#### 【0083】

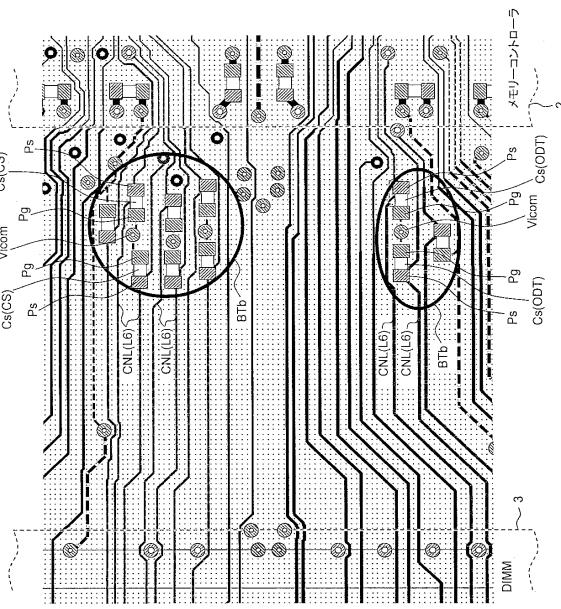

図14はSOCやDIMMを実装する回路基板上の裏面における容量素子近傍の配線パターンが詳細に例示される。

#### 【0084】

BTaの部分に例示される容量素子Cs(CS)はコントロール系配線CNL(L6)に接続される容量素子であり、例えばここではコントロール系配線CNL(L6)に伝達されるチップ選択信号CSのスルーレートを緩和するために用いられる。Psは当該コントロール系配線CNL(L6)に結合する電極パッド、Pgはビア配線Vi comを介してグランドプレーンL2(GND)に結合する電極パッドである。ここでは容量素子Cs(CS)を接続すべきコントロール系配線CNL(L6)が比較的密集しているため、2個の電極パッドPgを1個のビア配線Vi comに共通接続して面積の利用効率を高める

40

50

ように考慮されている。

**【0085】**

B T b の部分に例示される容量素子 C s ( O D T ) はコントロール系配線 C N L ( L 6 ) に接続される容量素子であり、例えばここではコントロール系配線 C N L ( L 6 ) に伝達されるオンダイターミネーション信号 O D T のスルーレートを緩和するために用いられる。 P s は当該コントロール系配線 C N L ( L 6 ) に結合する電極パッド、 P g はピア配線 V i c o m を介してグランドプレーン L 2 ( G N D ) に結合する電極パッドである。上記同様に、ここでも容量素子 C s ( O D T ) を接続すべきコントロール系配線 C N L ( L 6 ) が比較的密集しているため、2個の電極パッド P g を1個のピア配線 V i c o m に共通接続して面積の利用効率を高めるように考慮されている。

10

**【0086】**

なお、図 11 及び図 13において C N L \_ B はコントロール系配線 C N L ( L 1 ) 、 C N L ( L 6 ) の信号伝送方向基端を示している。この信号伝送方向基端 C N L \_ B は、マイクロコンピュータ 2 の一部である半田バンプ 27 が搭載される端子である電極パッド 12 とコントロール系配線 C N L ( L 1 ) 、 C N L ( L 6 ) との接続端部に相等する。

**【0087】**

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

20

**【0088】**

例えば、配線基板の配線総数は6層に限定されず、8層、あるいはそれ以上であってもよい。

**【0089】**

また、上記実施の形態では、複数の D I M M が配線基板(基板) 1 に搭載されていることについて説明したが、1つのマイクロコンピュータ 2 に対して、 D I M M は1つしか搭載されていなくてもよい。

30

**【0090】**

また、上記実施の形態では、回路基板にパッケージされた半導体部品とモジュール化された半導体部品を搭載したコントロールボード若しくはシステムボードを一例としたが、本発明はそれに限定されず、1つのインタボーナ基板(配線基板)上にコントロールチップのような半導体部品と複数のメモリチップを有するメモリ系の半導体部品とを搭載する、所謂、 S I P ( System In Package ) 型の半導体装置としての電子機器にも適用することが可能である。電子機器の適用範囲はプリンタやイメージスキャナに限定されず、ビデオカメラ、デジタルスチルカメラ、携帯端末などにも適用可能である。

**【0091】**

上記実施の形態では、容量素子 C s をチップコンデンサなどのチップ部品で構成する場合について説明したが、回路基板の配線層の配線パターンを用いて容量素子を構成することも可能であるが、高周波成分の除去によって信号のスルーレートを緩和するためには少なくとも 3 p F 以上の容量値が必要であり、これを配線パターンで形成する場合には、非常に大きな配線パターンを形成しなければならず、現実的ではなく、電子機器の小型化という観点からは、上記実施の形態のように、チップ部品を使用することが好ましい。

40

**【符号の説明】**

**【0092】**

- C N T B コントロールボード

- 2 マイクロコンピュータ ( S O C )

- 3 , 4 D I M M ( メモリモジュール )

- 1 配線基板

- 2 1 中央処理装置 ( C P U )

- 2 2 メモリコントローラ ( M C N T )

- C K クロック信号

50

|                             |                            |    |

|-----------------------------|----------------------------|----|

| C K L                       | クロック伝送経路                   |    |

| A D R                       | コマンド C M D 及びアドレス信号        |    |

| C A L                       | コマンドアドレス伝送経路               |    |

| D Q                         | データ                        |    |

| D Q S                       | データストローブ信号                 |    |

| D T L                       | データ系伝送経路                   |    |

| C S                         | チップ選択信号                    |    |

| C K E                       | クロックイネーブル信号                |    |

| O D T                       | オンダイタミネーション信号              |    |

| C N L                       | コントロール系伝送経路                | 10 |

| 3 0                         | モジュール基板                    |    |

| 3 1                         | D D R 3 - S D R A M        |    |

| 3 2                         | モジュールインターフェース端子列           |    |

| 3 3                         | C K、C M D、A D R のモジュール内配線  |    |

| 3 4                         | C S、C K E、O D T のモジュール内配線  |    |

| 3 5                         | 終端抵抗                       |    |

| 3 6                         | D Q、D Q S のモジュール内配線        |    |

| C N L 1                     | クロックイネーブル信号配線              |    |

| C N L 1 a、C N L 1 b         | C N L 1 の部分配線              |    |

| P i n ( D I M M )           | クロックイネーブル信号 C K E の入力端子    | 20 |

| P i n ( S O C )             | クロックイネーブル信号 C K E の出力端子    |    |

| C s                         | 容量素子                       |    |

| N D                         | C N L 1 a と C N L 1 b の接続点 |    |

| L 1 ~ L 6                   | 配線層                        |    |

| V i                         | ビア配線                       |    |

| C N L ( L 1 )               | コントロール配線                   |    |

| L 2 ( G N D )               | グランドプレーン                   |    |

| C K L ( L 3 )、C L K ( L 4 ) | クロック配線                     |    |

| C s ( C K E )               | 容量素子                       |    |

| V i c o m                   | ビア配線                       | 30 |

| C s ( C S )                 | 容量素子                       |    |

| C N L ( L 6 )               | コントロール系配線                  |    |

| C s ( O D T )               | 容量素子                       |    |

| C N L _ B                   | 信号伝送方向基端                   |    |

【図1】

【 四 2 】

【図3】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

図13

【図14】

図14

---

フロントページの続き

(56)参考文献 特開2002-271108(JP,A)

特開2010-123203(JP,A)

特開2003-173317(JP,A)

特開2004-152131(JP,A)

特開2003-085121(JP,A)

特開2003-045172(JP,A)

特開2009-294864(JP,A)

特開2009-217800(JP,A)

特開2000-100162(JP,A)

特開2004-152350(JP,A)

実開平04-050933(JP,U)

特表2008-502056(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00

G 06 F 13 / 16

G 11 C 11 / 407

H 03 K 19 / 0175