(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5153378号

(P5153378)

(45) 発行日 平成25年2月27日(2013.2.27)

(24) 登録日 平成24年12月14日(2012.12.14)

(51) Int.Cl.

F 1

H04N 5/357 (2011.01)

H04N 5/3745 (2011.01)H04N 5/335 570

H04N 5/335 745

請求項の数 4 (全 13 頁)

(21) 出願番号 特願2008-35222 (P2008-35222)

(22) 出願日 平成20年2月15日 (2008.2.15)

(65) 公開番号 特開2009-194764 (P2009-194764A)

(43) 公開日 平成21年8月27日 (2009.8.27)

審査請求日 平成23年1月13日 (2011.1.13)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 渡邊 高典

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 鈴木 肇

最終頁に続く

(54) 【発明の名称】 固体撮像装置及びその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換により電荷を生成及び蓄積する複数の光電変換素子と、

電荷を保持するための一のフローティングディフュージョン部と、

前記複数の光電変換素子に蓄積された電荷を前記一のフローティングディフュージョン部にそれぞれ転送する複数の転送スイッチと、

前記一のフローティングディフュージョン部に保持された電荷に対応する電圧を増幅する増幅トランジスタと

を含む複数の画素回路を2次元に配列した撮像領域と、

前記複数の転送スイッチを制御する垂直走査回路と、

前記増幅トランジスタにより増幅された電圧を読み出すための水平走査回路と、

前記増幅トランジスタに供給する電源電圧を制御することにより前記増幅トランジスタを活性状態にし、前記増幅トランジスタに供給する電源電圧を制御することにより前記増幅トランジスタを不活性状態にする電源回路とを有し、

前記増幅トランジスタの活性状態を維持したまま前記複数の転送スイッチが前記複数の光電変換素子の電荷を順次前記一のフローティングディフュージョン部に転送し、前記水平走査回路により前記複数の光電変換素子の電荷に応じた電圧を順次読み出し、

前記増幅トランジスタの活性状態を維持する期間は、水平走査期間の少なくとも一部を含み、

一の前記画素回路からの信号を読み出す水平走査期間に、別の一の前記画素回路の前記

10

20

増幅トランジスタが活性状態であることを特徴とする固体撮像装置。

**【請求項 2】**

前記水平走査回路は、前記一のフローティングディフュージョン部の電圧をリセットした状態で前記増幅トランジスタが出力するリセット出力電圧と前記光電変換素子の電荷を前記一のフローティングディフュージョン部に転送した状態で前記増幅トランジスタが出力する信号出力電圧との差分を出力し、

前記増幅トランジスタを活性状態にした後において、前記一のフローティングディフュージョン部をリセットしてから前記複数の光電変換素子のうちの最初の光電変換素子の前記リセット出力電圧のサンプルホールドまでの期間と、前記複数の光電変換素子のうちの最初の光電変換素子の電荷の転送から2番目の光電変換素子の前記リセット出力電圧のサンプルホールドまでの期間とが同じ長さであることを特徴とする請求項1記載の固体撮像装置。

**【請求項 3】**

前記画素回路は、さらに前記一のフローティングディフュージョン部の電圧をリセットするリセットトランジスタを有し、

前記複数の光電変換素子の電荷を前記一のフローティングディフュージョン部に転送し、該フローティングディフュージョン部に転送された電荷に対応する電圧を増幅した出力電圧をサンプルホールドしてから、前記一のフローティングディフュージョン部をリセットすることを特徴とする請求項1又は2記載の固体撮像装置。

**【請求項 4】**

光電変換により電荷を生成及び蓄積する複数の光電変換素子と、

電荷を保持するための一のフローティングディフュージョン部と、

前記複数の光電変換素子に蓄積された電荷を前記一のフローティングディフュージョン部にそれぞれ転送する複数の転送スイッチと、

前記一のフローティングディフュージョン部に保持された電荷に対応する電圧を増幅する増幅トランジスタと

を含む複数の画素回路を2次元に配列した撮像領域と、

前記複数の転送スイッチを制御する垂直走査回路と、

前記増幅トランジスタにより増幅された電圧を読み出すための水平走査回路と、

前記増幅トランジスタに供給する電源電圧を制御することにより前記増幅トランジスタを活性状態にして前記増幅トランジスタに供給する電源電圧を制御することにより前記増幅トランジスタを不活性状態にする電源回路とを有する固体撮像装置の駆動方法であって、

前記増幅トランジスタの活性状態を維持したまま前記複数の転送スイッチが前記複数の光電変換素子の電荷を順次前記一のフローティングディフュージョン部に転送し、前記水平走査回路により前記複数の光電変換素子の電荷に応じた電圧を順次読み出し、

前記増幅トランジスタの活性状態を維持する期間は、水平走査期間の少なくとも一部を含み、

一の前記画素回路からの信号を読み出す水平走査期間に、別の一の前記画素回路の前記増幅トランジスタを活性状態にすることを特徴とする固体撮像装置の駆動方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、固体撮像装置及びその駆動方法に関する。

**【背景技術】**

**【0002】**

近年、固体撮像装置は広く、動画、静止画及び様々な撮像用途に用いられてきている。特に画素内に増幅MOSトランジスタを持ち、周辺回路をオンチップ化できるCMOSセンサの性能向上はめざましく、画質の向上はとどまるところを知らない。CMOSセンサの画質を更に向上するためには、画素内の増幅MOSトランジスタで発生するランダムノ

10

20

30

40

50

イズ、固定ノイズを低減することが重要な課題となっている。

【0003】

増幅MOSトランジスタのリセットノイズの除去は、相関二重サンプリング技術にて除去する手法が広く用いられている。相関二重サンプリングは、増幅MOSトランジスタの入力部をリセットした状態の出力（以下、リセット出力）と、光電変換素子の信号電荷を増幅MOSトランジスタの入力部に転送した状態の出力（以下、信号出力）の差分を求める。これにより、光電変換素子の信号電荷量を低ノイズで読み出す技術が相関二重サンプリングである。この技術を用いることによりCMOSセンサの画質は著しく向上している。

【0004】

また、固体撮像装置の技術の進化は、光学サイズの縮小化、多画素化を目的として画素ピッチは縮小化の一途をたどっており、画素ピッチを縮小しても光電変換素子の信号電荷量を維持することも重要な課題となっている。

【0005】

この課題に対する解決手段として、画素共有化技術にて光電変換素子の面積を確保する技術が用いられている。画素共有化技術とは、増幅MOSトランジスタやリセットMOSトランジスタなどの画素内回路を複数の光電変換素子で共有化することにより光電変換素子1つあたりの素子数を削減する技術である。画素共有化技術を用いた画素回路の構成及び駆動方法については下記の特許文献1に開示されている。

【0006】

一方、増幅MOSトランジスタで発生するノイズとして、 $1/f$ ノイズも重要な要素として知られている。MOSトランジスタの $1/f$ ノイズに関しては様々な研究がなされているが、特に固体撮像装置における振る舞いに関して、下記の特許文献2にて記載がなされている。

【0007】

【特許文献1】特開2005-198001号公報

【特許文献2】特開2003-032554号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

特許文献2に記載の現象は、本発明者の研究によると、トランジスタのバイアスに変化があった際に、トランジスタの出力は100ms程度の比較的長い時間に渡りバイアス変化の影響が残っていると考えられる。さらにこの考え方に基づき本発明者が研究した結果によると、増幅MOSトランジスタの出力はゲート電位が大きく変動した後、等価回路の時定数に比べて非常に長い時定数にて出力値が微小な変化をすることが解った。

【0009】

増幅MOSトランジスタの出力値が微小な変化をしている期間に相関二重サンプリングを行うと、微小な変化分が擬似信号として正しい信号に重畠される。擬似信号の振幅が、画素ごとにばらつく場合は固定パターンとなり、撮像面内で傾向を持つ場合はシェーディングとなって画質を悪化させる要因となる。

【0010】

本発明の目的は、増幅トランジスタによる擬似信号の発生を抑制し、固定パターンノイズ、シェーディングの少ない固体撮像装置及びその駆動方法を提供することである。

【課題を解決するための手段】

【0011】

本発明の固体撮像装置は、光電変換により電荷を生成及び蓄積する複数の光電変換素子と、電荷を保持するための一のフローティングディフュージョン部と、前記複数の光電変換素子に蓄積された電荷を前記一のフローティングディフュージョン部にそれぞれ転送する複数の転送スイッチと、前記一のフローティングディフュージョン部に保持された電荷に対応する電圧を増幅する増幅トランジスタとを含む複数の画素回路を2次元に配列した

10

20

30

40

50

撮像領域と、前記複数の転送スイッチを制御する垂直走査回路と、前記増幅トランジスタにより増幅された電圧を読み出すための水平走査回路と、前記増幅トランジスタに供給する電源電圧を制御することにより前記増幅トランジスタを活性状態にし、前記増幅トランジスタに供給する電源電圧を制御することにより前記増幅トランジスタを不活性状態にする電源回路とを有し、前記増幅トランジスタの活性状態を維持したまま前記複数の転送スイッチが前記複数の光電変換素子の電荷を順次前記一のフローティングディフュージョン部に転送し、前記水平走査回路により前記複数の光電変換素子の電荷に応じた電圧を順次読み出し、前記増幅トランジスタの活性状態を維持する期間は、水平走査期間の少なくとも一部を含み、一の前記画素回路からの信号を読み出す水平走査期間に、別の一の前記画素回路の前記増幅トランジスタが活性状態であることを特徴とする。

10

#### 【0012】

また、本発明の固体撮像装置の駆動方法は、光電変換により電荷を生成及び蓄積する複数の光電変換素子と、電荷を保持するための一のフローティングディフュージョン部と、前記複数の光電変換素子に蓄積された電荷を前記一のフローティングディフュージョン部にそれぞれ転送する複数の転送スイッチと、前記一のフローティングディフュージョン部に保持された電荷に対応する電圧を増幅する増幅トランジスタとを含む複数の画素回路を2次元に配列した撮像領域と、前記複数の転送スイッチを制御する垂直走査回路と、前記増幅トランジスタにより増幅された電圧を読み出すための水平走査回路と、前記増幅トランジスタに供給する電源電圧を制御することにより前記増幅トランジスタを活性状態にして前記増幅トランジスタに供給する電源電圧を制御することにより前記増幅トランジスタを不活性状態にする電源回路とを有する固体撮像装置の駆動方法であって、前記増幅トランジスタの活性状態を維持したまま前記複数の転送スイッチが前記複数の光電変換素子の電荷を順次前記一のフローティングディフュージョン部に転送し、前記水平走査回路により前記複数の光電変換素子の電荷に応じた電圧を順次読み出し、前記増幅トランジスタの活性状態を維持する期間は、水平走査期間の少なくとも一部を含み、一の前記画素回路からの信号を読み出す水平走査期間に、別の一の前記画素回路の前記増幅トランジスタを活性状態にすることを特徴とする。

20

#### 【発明の効果】

#### 【0013】

増幅トランジスタによる擬似信号の発生を抑制することで、固定パターンノイズやシェーディングを少なくすることができる。

30

#### 【発明を実施するための最良の形態】

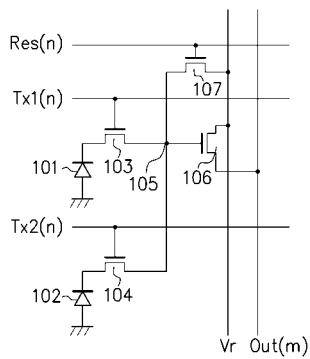

#### 【0014】

##### (第1の実施形態)

図1は本発明の第1の実施形態による画素の等価回路図である。以下、MOS電界効果トランジスタを単にMOSトランジスタという。101及び102は光電変換素子であり、それぞれ転送スイッチ103、104を介してフローティングディフュージョン部(以下、FD部)105に接続されている。FD部105は、実際には増幅MOSトランジスタ106のゲート容量、リセットMOSトランジスタ107のソース容量、転送スイッチ103、104のドレイン容量及びこれらを接続する配線の寄生容量によって形成されるノードである。転送スイッチ103及び104のゲートはそれぞれ信号 $T \times 1(n)$ 、 $T \times 2(n)$ により制御される。リセットMOSトランジスタ107のゲートは信号Res(n)により制御される。ここでnは画素の行のアドレスを示している。増幅MOSトランジスタ106のドレインと、リセットMOSトランジスタ107のドレインは電源電圧 $V_r$ に接続されている。電源電圧 $V_r$ は可変電源であり、時刻によって異なる電位を与えることができる。増幅MOSトランジスタ106のソースは垂直信号線Out(m)に接続されている。ここでmは画素の列のアドレスを示している。垂直信号線Out(m)には不図示のサンプルホールド回路が設けられており、垂直信号線Out(m)に出力された信号を保持することができる。電源回路が電源電圧 $V_r$ を制御する。

40

#### 【0015】

50

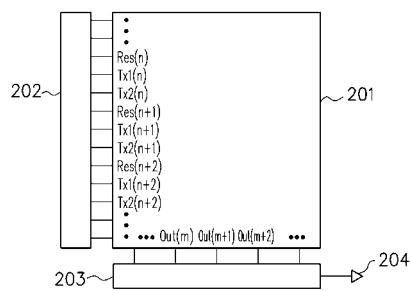

図1は2つの光電変換素子101及び102で画素回路を共有化した単位セルであるが、単位セルを二次元に配列することで撮像領域を構成することができる。図2は本発明の第1の実施形態における固体撮像装置のブロック図であり、撮像領域201、垂直走査回路202及び水平走査回路203にて構成される。水平走査回路203は、サンプルホールド回路にて保持されている信号を順次選択し、出力部である出力204へ転送する。

#### 【0016】

相関二重サンプリングは、増幅MOSトランジスタ106の入力部をリセットした状態の出力（以下、リセット出力）と、光電変換素子101又は102の信号電荷を増幅MOSトランジスタ106の入力部に転送した状態の出力（以下、信号出力）の差分を求める。信号出力には、光電変換により得られた信号電荷量に加えてリセット出力に相当する電荷量も含まれる。そこで、リセット出力と信号出力との差分を取ることで光電変換素子101又は102の信号電荷量を低ノイズで読み出す技術が相関二重サンプリングである。ここでは、不図示のサンプルホールド回路でリセット出力と信号出力を保持する場合を例に説明している。

#### 【0017】

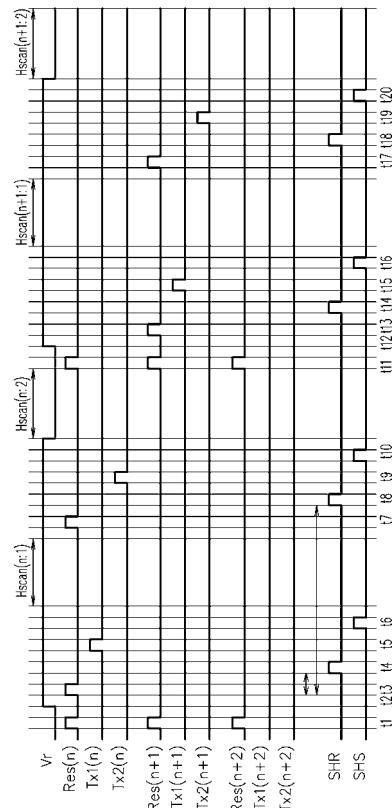

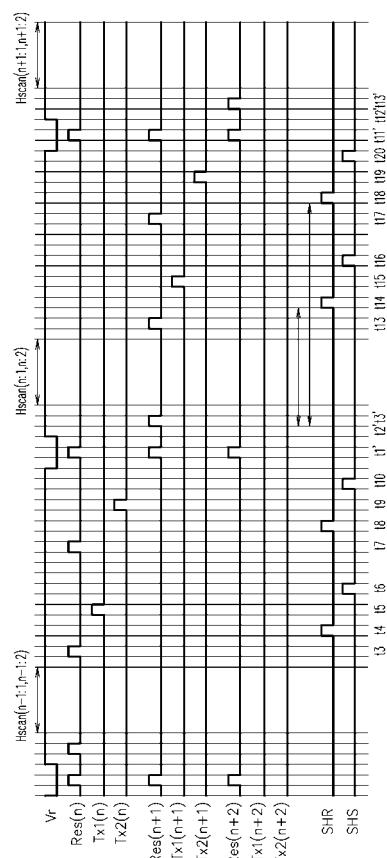

図3は本発明の第1の実施形態の固体撮像装置の駆動方法を示すタイミング図である。時刻t1において信号Res(n)、Res(n+1)、Res(n+2)…がハイレベルになり、各行のリセットMOSトランジスタ107がオンする。このとき電源電圧Vrはローレベルであり各FD部105は低い電位にリセットされる。すなわち、不活性状態となる。時刻t2において電源電圧Vrがハイレベルになり、時刻t3において選択行のみのリセットMOSトランジスタ107は信号Res(n)によりオンする。つまり、活性状態となる。ここまで駆動により選択行のFD部105のみが高い電位となり、垂直信号線Out(m)、Out(m+1)、Out(m+2)…の電位は選択行の増幅MOSトランジスタ106によって決定される。この状態では、n行の増幅MOSトランジスタ106のみが活性状態であり、それ以外の行、すなわちn+1、n+2行…の増幅MOSトランジスタ106は不活性の状態となる。次に、時刻t4にサンプルホールドパルスSHRを用いてリセット出力をサンプルホールド回路によりサンプルホールドする。次に、時刻t5に信号Tx1(n)により光電変換素子101の信号電荷をFD部105に転送した後、時刻t6にサンプルホールドパルスSHSを用いて信号出力をサンプルホールド回路によりサンプルホールドする。次に、水平走査期間Hscan(n:1)において水平走査を行った後、今度はt7~t10の動作にてTx2(n)でアドレスされる光電変換素子102の信号電荷を読み出し、水平走査期間Hscan(n:2)において水平走査を行う。なお、図3においては時刻t1とt3に分けてRes(n)のパルスをハイレベルにしているが、時刻t1~t3にかけて連続してハイレベルパルスを与えて読み出し動作は可能である。

#### 【0018】

従来の固体撮像装置の駆動方法では、水平走査期間Hscan(n:1)の後にFD部105を低い電位にリセットして増幅MOSトランジスタ106を不活性化した後、再びFD部105を高い電位にリセットして増幅MOSトランジスタ106を活性化していた。従来の固体撮像装置では光電変換素子102の読み出しは増幅MOSトランジスタ106を活性化した後の比較的短い時間、具体的には数μs~数十μs以内に相関二重サンプリング読み出しを行うことになり、上述の〔発明が解決しようとする課題〕が発生する。

#### 【0019】

一方、本実施形態においては水平走査期間Hscan(n:1)の間もFD部105は高い電位のまま保持するため、光電変換素子102の信号電荷の読み出しは比較的長い期間に渡り活性化状態にあった増幅MOSトランジスタ106にて行われる。具体的には増幅MOSトランジスタ106の活性化から読み出しまでの期間は、ノイズ出力の読み出しに対してはt2~t8、信号出力の読み出しに対してはt2~t10である。この期間は水平走査期間を含むため、例えばHD(High Definition)動画の場合、およそ15ms以上に及ぶ。

10

20

30

40

50

## 【0020】

以上の駆動により、本発明の第1の実施形態においては信号 $T \times 2 (n)$ 、 $T \times 2 (n + 1)$ 、 $T \times 2 (n + 2)$ ・・・により転送される信号電荷量の読み出しに対する擬似信号を特に低減することができる。撮影した画像のノイズ感は各画素のノイズ量の和に依存するため、本実施形態により擬似信号を低減することで画質を向上することが可能である。

## 【0021】

## (第2の実施形態)

本発明の第1の実施形態においては、信号 $T \times 1 (n)$ により転送した信号電荷量の読み出しの後、水平走査期間 $H \text{ scan} (n)$ を経た後に信号 $T \times 2 (n)$ により信号電荷の転送を行っている。本実施形態は信号 $T \times 1 (n)$ 及び $T \times 2 (n)$ による信号電荷を水平走査回路203内に設けられたラインメモリに保持した後、水平走査を行う場合においても効果を得ることができる。

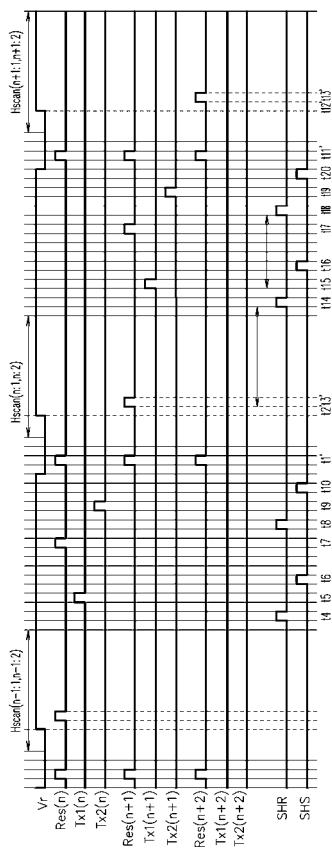

## 【0022】

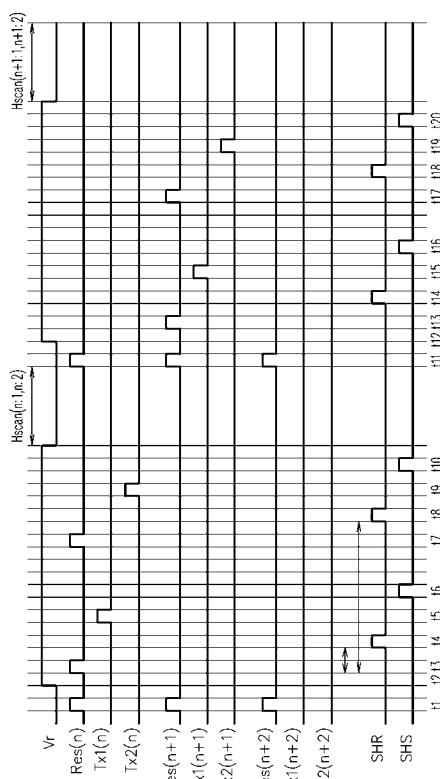

図4に本発明の第2の実施形態の固体撮像装置の駆動方法を示すタイミング図である。画素の等価回路及び固体撮像装置のブロック図は第1の実施形態と同じである。本実施形態が第1の実施形態と異なる点は水平走査期間 $H \text{ scan} (n : 1, n : 2)$ の前に信号 $T \times 1 (n)$ 及び $T \times 2 (n)$ で転送される信号電荷をサンプルホールドしている事である。このような駆動を行う利点は、1フレームを読み出すために必要な水平走査期間の回数が半分になり、読み出しの高速化が容易になる事である。本実施形態の駆動タイミングの特徴は、信号 $T \times 2 (n)$ で転送される信号電荷の読み出しを行う直前に増幅MOSトランジスタ106を不活性状態にすることなく相関二重サンプリングを行う点である。具体的には、増幅MOSトランジスタ106の活性化から読み出しまでの期間は、ノイズ出力の読み出しに対しては $t_2 \sim t_8$ 、信号出力の読み出しに対しては $t_2 \sim t_{10}$ である。

## 【0023】

本実施形態によれば、信号 $T \times 2 (n)$ 、 $T \times 2 (n + 1)$ 、 $T \times 2 (n + 2)$ ・・・により転送される信号電荷量の読み出しに対する擬似信号を低減しつつ、読み出しの高速化を図ることができる。

## 【0024】

## (第3の実施形態)

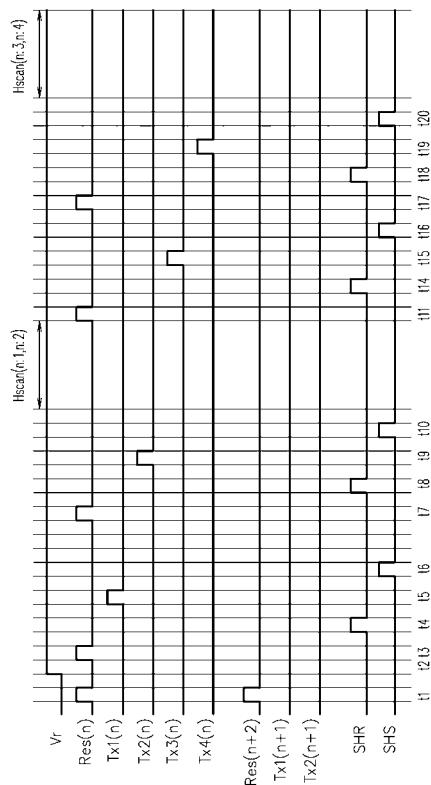

図5に本発明の第3の実施形態の固体撮像装置の駆動方法を示すタイミング図である。画素の等価回路及び固体撮像装置のブロック図は第1及び第2の実施形態と同等である。本実施形態が第2の実施形態と異なる点は、期間 $t_1'$ が、リセット出力のサンプルホールド( $t_8$ )及び信号出力のサンプルホールド( $t_{10}$ )と、水平走査期間 $H \text{ scan} (n : 1, n : 2)$ の間にある点である。期間 $t_1'$ は、信号 $R \text{ es} (n)$ 、 $R \text{ es} (n + 1)$ 、 $R \text{ es} (n + 2)$ ・・・を一斉にハイレベルにして、各FD部105を低い電位にリセットする期間である。FD部105を低い電位にリセットするためには電源電圧 $V_r$ を低い電位にする必要がある。時刻 $t_1'$ においては信号 $R \text{ es} (n + 1)$ によりアドレスされる増幅MOSトランジスタ106は、他の行の増幅MOSトランジスタ106と同様に不活性状態になっている。本実施形態では、その直後の時刻 $t_3'$ において信号 $R \text{ es} (n + 1)$ によりアドレスされる増幅MOSトランジスタ106は活性化される。水平走査期間 $H \text{ scan} (n : 1, n : 2)$ の間を含め増幅MOSトランジスタ106は活性化状態にあり、その後に信号 $T \times 1 (n + 1)$ 及び $T \times 2 (n + 1)$ により転送される信号電荷を順次読み出している。本実施形態においては、信号 $T \times 1 (n + 1)$ 及び $T \times 2 (n + 1)$ の両者の読み出しに対して、増幅MOSトランジスタ106に十分長い活性化期間を設けることができる。具体的には、増幅MOSトランジスタ106の活性化から読み出しまでの期間は、信号 $T \times 1 (n + 1)$ に対応するノイズ出力の読み出しに対しては $t_3' \sim t_{14}$ 、信号出力の読み出しに対しては $t_3' \sim t_{16}$ である。そして、信号 $T \times 2 (n + 1)$ に対応するノイズ出力の読み出しに対しては $t_3' \sim t_{18}$ 、信号出力の

10

20

30

40

50

読み出しに対しては  $t_{3'} \sim t_{20}$  である。

【0025】

以上、本発明の第3の実施形態によれば、信号  $T \times 1 (n)$  及び  $T \times 2 (n)$  により転送される信号電荷量に対応する読み出しの両者に対して擬似信号を低減することができる。そのため、【発明が解決しようとする課題】に対する改善効果がより顕著であることに加え、さらに、以下の効果が得られる。

【0026】

従来の画素共有化技術を用いた際には、増幅MOSトランジスタのバイアス変化が起きた時刻から相關二重サンプルリングを行うまでの時間が画素ごとに異なり、擬似信号の大きさが周期的に変化するという問題が発生する。この問題は、単板式カラーの固体撮像装置においては偽色の発生といった問題を引き起こす。

10

【0027】

本発明の第3の実施形態においては、画素共有化を行った固体撮像装置においても増幅MOSトランジスタによる擬似信号の発生を抑制しつつ周期的な擬似信号の変化を低減し、色再現性の良好な固体撮像装置を提供することが可能である。

【0028】

(第4の実施形態)

図6に本発明の第4の実施形態の固体撮像装置の駆動方法を示すタイミング図である。画素の等価回路及び固体撮像装置のブロック図は第1及び第3の実施形態と同等である。本実施形態が第3の実施形態と異なる点は信号  $Res (n+1)$  をハイレベルにして、FD部105を低い電位にリセットする期間  $t_{1'}$  を、水平走査期間  $Scan (n:1, n:2)$  の期間内に設けた点である。本実施形態では、増幅MOSトランジスタ106の活性化から読み出しまでの期間は、信号  $T \times 1 (n+1)$  に対応するノイズ出力の読み出しに対しては  $t_{3'} \sim t_{14}$ 、信号出力の読み出しに対しては  $t_{3'} \sim t_{16}$  である。そして、信号  $T \times 2 (n+1)$  に対応するノイズ出力の読み出しに対しては  $t_{3'} \sim t_{18}$ 、信号出力の読み出しに対しては  $t_{3'} \sim t_{20}$  である。

20

【0029】

さらに、本実施形態においては第3の実施形態で得られる効果に加えて、新たな効果も得られる。本発明者の研究により、以下の事が判明した。上記の特許文献2にて記載されているMOSトランジスタのオン・オフの切り替わりによってMOSトランジスタの特性が変化する。その事のみならず、MOSトランジスタのオン・オフ状態が切り替わるほどゲートバイアスの変動で無くても、ゲートバイアス変動の影響を受けてMOSトランジスタ特性が変化する事が判明した。駆動タイミングを示す図6における時刻  $t_{15}$  においては、増幅MOSトランジスタ106は活性化状態を維持しつつも、ゲートバイアスに変動が起きている。このゲートバイアス変動に起因したMOSトランジスタ特性の変化が小さいながらも発生する。より具体的には、転送スイッチ(転送MOSトランジスタ)103又は104がオンすると、増幅MOSトランジスタ106のチャネル下に存在する電荷が減少して過渡的に浮遊状態となる。このため、時刻  $t_{15}$  における動作により増幅MOSの特性が変化することになる。

30

【0030】

一方、時刻  $t_{17}$  では増幅MOSトランジスタ106のゲート電位がリセットされるが、ここでは既に活性状態にある増幅MOSトランジスタ106に対して、高い電位に変化する。そのため、時刻  $t_{15}$  とは異なり、時刻  $t_{17}$  での電位の変化は、サンプルホールドされる信号に対しての影響はあまりない。なお、ここでは各光電変換素子で蓄積される電荷は電子であるとして説明したが、各光電変換素子で蓄積される電荷が正孔であったとしても同様の議論ができる。

40

【0031】

本実施形態では、 $t_{3'}$  の時刻を調整することによって信号  $T \times 1 (n+1)$  により行う読み出しと信号  $T \times 2 (n+1)$  により行う読み出しの際に発生する増幅MOSトランジスタ106の特性変化量を同等に揃えることが可能となる。すなわち、若干の増幅MOS

50

Sトランジスタ106の特性変化を残しつつも、画素共有化を行った固体撮像装置においても周期的な擬似信号の変化を低減し、色再現性の良好な固体撮像装置を提供することができる。よって、上述の第3の実施形態と同様に、あるいはそれ以上の改善効果にて、画素共有化を行った固体撮像装置においても周期的な擬似信号の変化を低減し、色再現性の良好な固体撮像装置を提供することができる。

【0032】

さらに加えて、本実施形態では以下の効果が得られる。CMOSセンサにおいては、画素ごとにある増幅MOSトランジスタを駆動するための定電流源が列ごとに設けられている。すなわち、増幅MOSトランジスタを駆動状態にする際には、列数分の定電流源が電流を流すことになり、大きな消費電力を必要とする。本実施形態においては、水平走査期間中に電源電圧V<sub>r</sub>が常にハイレベルである必要がない。そのため、電源電圧V<sub>r</sub>のローレベル期間には増幅MOSトランジスタ106には電流が流れないか、もしくは著しく電流を低減することができる。それにより、本実施形態では定電流源による消費電流を大きく低減することが可能となる。よって、本実施形態では固体撮像装置の消費電力の低減が可能となる。

10

【0033】

(第5の実施形態)

前記、本発明の第1～第4の実施形態においては2つの光電変換素子101及び102で画素回路を共有化した例について記載した。本発明は上述の等価回路に限定されるものでは無く、3つ以上の光電変換素子にて画素回路を共有化した場合にもさらに大きな効果を得ることができる。例えば、上記の特許文献1の図1に記載されるように4つの光電変換素子にて画素回路を共有化した場合にも、第1から第4の実施形態と同様の考え方にて増幅MOSトランジスタを活性化する期間を長くすることが可能である。

20

【0034】

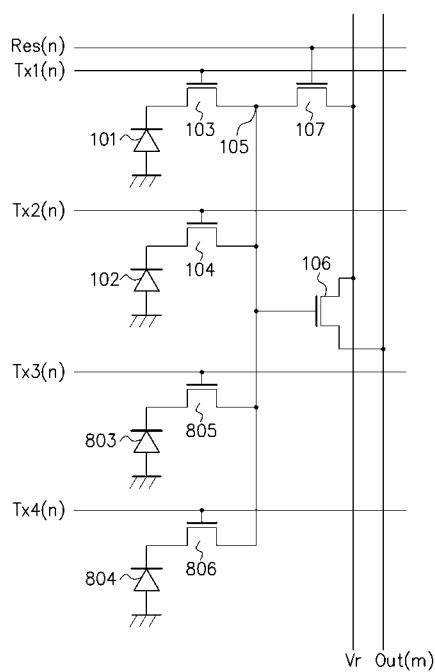

図8は、本発明の第5の実施形態による画素の等価回路図である。101、102、803及び804は光電変換素子であり、それぞれ転送スイッチ103、104、805及び806を介してFD部105に接続されている。FD部105は、実際には増幅MOSトランジスタ106のゲート容量、リセットMOSトランジスタ107のソース容量、転送スイッチ103、104、805、806のドレイン容量及びこれらを接続する配線の寄生容量によって形成されるノードである。転送スイッチ103、104、805及び806のゲートはそれぞれ信号T<sub>x1</sub>(n)、T<sub>x2</sub>(n)、T<sub>x3</sub>(n)、T<sub>x4</sub>(n)により制御される。リセットMOSトランジスタ107のゲートは信号Res(n)により制御される。ここでnは画素の行のアドレスを示している。増幅MOSトランジスタ106のドレインと、リセットMOSトランジスタ107のドレインは電源電圧V<sub>r</sub>に接続されている。電源電圧V<sub>r</sub>は可変電源であり、時刻によって異なる電位を与えることができる。増幅MOSトランジスタ106のソースは垂直信号線Out(m)に接続されている。ここでmは画素の列のアドレスを示している。垂直信号線Out(m)には不図示のサンプルホールド回路が設けられており、垂直信号線に出力された信号を保持することができる。

30

【0035】

図7に本発明の第5の実施形態の固体撮像装置の駆動方法を示すタイミング図である。図7のタイミング図では4つの光電変換素子101、102、803、804のそれぞれに対応する転送スイッチ103、104、805、806のゲートに印加するパルスをT<sub>x1</sub>(n)、T<sub>x2</sub>(n)、T<sub>x3</sub>(n)、T<sub>x4</sub>(n)で記述した。本実施形態では増幅MOSトランジスタ106の不活性化は時刻t<sub>1</sub>で行われ、選択行の増幅MOSトランジスタ106は時刻t<sub>2</sub>において活性化した後、信号T<sub>x1</sub>(n)～T<sub>x4</sub>(n)により転送された電荷の読み出しが行われるまで、活性化状態を維持する。

40

【0036】

なお、図7においては4行分の信号の水平走査は、水平走査期間H<sub>scan</sub>(n:1, n:2)とH<sub>scan</sub>(n:3, n:4)の2回に分けて行っているが、4行分の信号を

50

保持するラインメモリを設ければ、一回の水平走査にて行うことも可能である。

【0037】

第1の実施形態においては1つの増幅MOSトランジスタに接続された2つの光電変換素子のうち、2つ目に読み出す光電変換素子の読み出しにおいて本発明の効果を得ることができた。本実施形態で示したように、4つの光電変換素子にて共有化した場合には3/4の光電変換素子の読み出しにおいて本発明の効果を得ることができる。

【0038】

本実施形態では第1の実施形態の駆動方法を4つの光電変換素子101、102、803、804にて共有化した場合に拡張する例を示したが、第2～第4の実施形態の駆動方法を4つ以上の光電変換素子にて共有化した場合の駆動に拡張することも可能である。

10

【0039】

以上、本発明の第5の実施形態では、増幅MOSトランジスタによる擬似信号の発生を抑制することで、固定パターンノイズやシェーディングの少ない固体撮像装置を実現することができる。さらに、擬似信号の大きさが周期的に変化するという問題を抑制することができるため、特に単板式カラーの固体撮像装置において良好な色再現性を実現することが可能となる。加えて、定電流源の消費電力を低減することが可能となり、低消費電力の固体撮像装置を提供することが可能となる。

【0040】

以上のように、第1～第5の実施形態の固体撮像装置は、撮像領域201、垂直走査回路202及び水平走査回路203を有する。撮像領域201は、複数の光電変換素子101、102と、一のフローティングディフュージョン部105と、複数の転送スイッチ103、104と、増幅トランジスタ106と、リセットトランジスタ107とを含む画素回路を2次元に配列している。複数の光電変換素子101、102は、光電変換により電荷を生成及び蓄積する。一のフローティングディフュージョン部105は、電荷を蓄積する。複数の転送スイッチ103、104は、前記複数の光電変換素子101、102に蓄積された電荷を前記一のフローティングディフュージョン部105にそれぞれ転送する。増幅トランジスタ106は、前記フローティングディフュージョン部105に蓄積された電荷に対応する電圧を増幅する。リセットトランジスタ107は、前記フローティングディフュージョン部105の電圧をリセットする。垂直走査回路202は、前記転送スイッチ103、104及び前記リセットトランジスタ107を制御する。水平走査回路203は、前記増幅トランジスタ106により増幅された電圧を出力部へ順次転送する。電源回路は、増幅トランジスタ106に供給する電源電圧VRをハイレベルにすることにより増幅トランジスタ106を活性状態にして増幅トランジスタ106に供給する電源電圧VRをローレベルにすることにより増幅トランジスタ106を不活性状態にする。電源回路は、水平走査回路203内の設けてもよいし、垂直走査回路202又は撮像領域201に設けてもよい。上記実施形態では、前記増幅トランジスタの活性状態を維持したまま前記複数の転送スイッチが前記複数の光電変換素子の電荷を順次前記フローティングディフュージョン部に転送し、前記水平走査回路が前記複数の光電変換素子の電荷に応じた電圧を順次読み出す。

20

【0041】

図3、5、6、7では、前記増幅トランジスタ106の活性状態を維持する期間は、水平走査期間H scanの少なくとも一部を含む。

30

【0042】

固体撮像装置は、相關二重サンプリングを行う。前記フローティングディフュージョン部105の電圧をリセットした状態で前記増幅トランジスタ106はリセット出力電圧を出力する。また、前記光電変換素子101、102の電荷を前記フローティングディフュージョン部105に転送した状態で前記増幅トランジスタ106は信号出力電圧を出力する。前記水平走査回路203は、前記リセット出力電圧と前記信号出力電圧との差分を出力する。

【0043】

40

50

図6において、前記増幅トランジスタ106を活性状態にした後において、時刻t3'から時刻t14までの期間と時刻t15から時刻t18までの期間とが同じ長さである。ここで、同じ長さとは、全く同一であることを意味するものではなく、多少の違いは許容される。時刻t3'から時刻t14までの期間は、前記フローティングディフュージョン部105をリセットしてから前記複数の光電変換素子のうちの最初の光電変換素子の前記リセット出力電圧のサンプルホールドまでの期間である。時刻t15から時刻t18までの期間は、前記複数の光電変換素子のうちの最初の光電変換素子の電荷の転送から2番目の光電変換素子の前記リセット出力電圧のサンプルホールドまでの期間である。

## 【0044】

ところで、一のフローティングディフュージョン部を複数の光電変換素子で共有する画素構成を有する固体撮像装置においては、複数の光電変換素子で蓄積された電荷をフローティングディフュージョン部で加算することができる。そのような場合でも本発明は適用可能で、加算する光電変換素子からの電荷を全てフローティングディフュージョン部に転送し、サンプルホールド回路でサンプルホールドさせた後にフローティングディフュージョン部をリセットすればよい。

## 【0045】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

## 【図面の簡単な説明】

## 【0046】

【図1】本発明の第1の実施形態による画素の等価回路図である。

【図2】本発明の第1の実施形態における固体撮像装置のブロック図である。

【図3】本発明の第1の実施形態の固体撮像装置の駆動方法を示すタイミング図である。

【図4】本発明の第2の実施形態の固体撮像装置の駆動方法を示すタイミング図である。

【図5】本発明の第3の実施形態の固体撮像装置の駆動方法を示すタイミング図である。

【図6】本発明の第4の実施形態の固体撮像装置の駆動方法を示すタイミング図である。

【図7】本発明の第5の実施形態の固体撮像装置の駆動方法を示すタイミング図である。

【図8】本発明の第5の実施形態による画素の等価回路図である。

## 【符号の説明】

## 【0047】

101、102 光電変換素子

103、104 転送スイッチ

105 FD部

106 増幅MOSトランジスタ

107 リセットMOSトランジスタ

201 撮像領域

202 垂直走査回路

203 水平走査回路

204 出力

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【 义 6 】

【 図 7 】

【 四 8 】

---

フロントページの続き

(56)参考文献 特表2008-500768(JP,A)

特開2005-268537(JP,A)

特開2004-172950(JP,A)

特開2003-046864(JP,A)

特開平09-046596(JP,A)

特開2006-302970(JP,A)

特開2007-202044(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762