(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7068676号

(P7068676)

(45)発行日 令和4年5月17日(2022.5.17)

(24)登録日 令和4年5月9日(2022.5.9)

|                         |                      |

|-------------------------|----------------------|

| (51)国際特許分類              | F I                  |

| H 01 L 21/205 (2006.01) | H 01 L 21/205        |

| H 01 L 21/338 (2006.01) | H 01 L 29/80 H       |

| H 01 L 29/778 (2006.01) | H 01 L 29/80 C       |

| H 01 L 29/812 (2006.01) | H 01 L 29/80 E       |

| H 01 L 21/337 (2006.01) | H 01 L 29/78 3 0 1 B |

請求項の数 13 (全11頁) 最終頁に続く

|                   |                                  |          |                                                                                                                                  |

|-------------------|----------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2018-534035(P2018-534035)      | (73)特許権者 | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 7 5 2 6 5<br>- 5 4 7 4 ダラス メイル ステイション<br>3 9 9 9 ピーオーボックス 6 5 5 4 7 4 |

| (86)(22)出願日       | 平成28年12月28日(2016.12.28)          | (74)代理人  | 100098497<br>弁理士 片寄 恒三                                                                                                           |

| (65)公表番号          | 特表2019-500755(P2019-500755<br>A) | (72)発明者  | アサド マフムード ハイダー<br>アメリカ合衆国 7 5 0 2 5 テキサス州<br>ブレイノ, ロングビュードライブ 9<br>2 0 9                                                         |

| (43)公表日           | 平成31年1月10日(2019.1.10)            | (72)発明者  | カリド ファリード<br>アメリカ合衆国 7 5 0 7 4 テキサス州<br>ブレイノ, ブラブーラ ドライブ 1 2                                                                     |

| (86)国際出願番号        | PCT/US2016/069051                |          | 最終頁に続く                                                                                                                           |

| (87)国際公開番号        | WO2017/117315                    |          |                                                                                                                                  |

| (87)国際公開日         | 平成29年7月6日(2017.7.6)              |          |                                                                                                                                  |

| 審査請求日             | 令和1年12月23日(2019.12.23)           |          |                                                                                                                                  |

| (31)優先権主張番号       | 14/981,348                       |          |                                                                                                                                  |

| (32)優先日           | 平成27年12月28日(2015.12.28)          |          |                                                                                                                                  |

| (33)優先権主張国・地域又は機関 | 米国(US)                           |          |                                                                                                                                  |

(54)【発明の名称】 IIIA - N族デバイスのための非エッチ気体冷却エピタキシャルスタック

## (57)【特許請求の範囲】

## 【請求項 1】

III A - N族トランジスタを製造する方法であって、

堆積システムの堆積チャンバにおいて第1の温度で基板上に少なくとも第1の III A - N族バッファ層を堆積することと、

前記堆積システムの前記堆積チャンバにおいて前記第1の温度より低いか又は等しい第2の温度で前記第1の III A - N族バッファ層上に少なくとも1つの III A - N族表面キャップ層を堆積することであって、その後、前記堆積チャンバがベントされる冷却温度まで継続的に前記堆積チャンバに気体混合物を供給する冷却プロセスを用いて前記基板を550又は550より低い温度まで冷却し、前記気体混合物がNH<sub>3</sub>と容量で40%未満のH<sub>2</sub>を含む少なくとも1つの他の気体とを含み、前記 III A - N族表面キャップ層の表面において、(i)2乗平均平方根(rms)粗さが10より大きく、(ii)2nm深さより大きいピット層に対するピット密度が0.05μmより小さな平均ピット直径で10ピット/μm<sup>2</sup>よりも小さくなるように、前記気体混合物が前記堆積チャンバにおいて前記キャップ層に対して非エッチである雰囲気を提供する、前記堆積することと、前記 III A - N族表面キャップ層上にゲート誘電体層を形成することと、

前記ゲート誘電体層上に金属ゲート電極を形成することと、

前記 III A - N族表面キャップ層へのソースコンタクトを有するソースと前記 III A - N族表面キャップ層へのドレインコンタクトを有するドレインとを形成することと、

を含む、方法。

**【請求項 2】**

請求項 1 に記載の方法であって、

前記第 1 の I I I A - N 族バッファ層を堆積した後で前記 I I I A - N 族表面キャップ層を堆積する前に、前記基板を前記第 1 の温度からキャップ層堆積温度へ冷却する間に前記冷却プロセスを用いることを更に含む、方法。

**【請求項 3】**

請求項 1 に記載の方法であって、

前記堆積システムが、有機金属化学気相成長 (MOCVD) システム、分子ビームエピタキシー (MBE) システム、又はハイドライド気相エピタキシー (HYPE) システムを含む、方法。

10

**【請求項 4】**

請求項 1 に記載の方法であって、

前記 I I I A - N 族表面キャップ層の厚みが 0.5 nm と 30 nm との間の範囲である、方法。

**【請求項 5】**

請求項 1 に記載の方法であって、

前記第 1 の I I I A - N 族バッファ層と前記 I I I A - N 族表面キャップ層との両方が、 GaN 又は AlGaN を含む、方法。

**【請求項 6】**

請求項 1 に記載の方法であって、

前記基板が、サファイア、シリコン、又はシリコンカーバイド (SiC) を含む、方法。

20

**【請求項 7】**

請求項 1 に記載の方法であって、

前記気体混合物が N<sub>2</sub> を更に含む、方法。

**【請求項 8】**

請求項 1 に記載の方法であって、

前記気体混合物が H<sub>2</sub> を含まない、方法。

**【請求項 9】**

I I I A - N 族トランジスタを製造する方法であって、

堆積システムの堆積チャンバにおいて第 1 の温度で基板上に第 1 の I I I A - N 族バッファ層を堆積することと、

30

前記堆積チャンバにおける雰囲気が前記第 1 の I I I A - N 族バッファ層に対して非エッチであるように NH<sub>3</sub> と少なくとも 1 つの他の気体とを含む気体混合物を用いて前記第 1 の温度より低い第 2 の温度で前記基板を冷却することと、

前記堆積システムの堆積チャンバにおいて前記第 2 の温度で前記第 1 の I I I A - N 族バッファ層上に I I I A - N 族表面キャップ層を堆積することであって、前記堆積チャンバがベントされるまで 550 以下への冷却プロセスが続き、前記冷却プロセスが NH<sub>3</sub> と N<sub>2</sub> とを含む前記堆積チャンバに供給される気体混合体を利用する、前記堆積することと、前記 I I I A - N 族表面キャップ層上にゲート誘電体層を形成することと、

前記ゲート誘電体層上に金属ゲート電極を形成することと、

40

前記 I I I A - N 族表面キャップ層へのソースコンタクトを有するソースと前記 I I I A - N 族表面キャップ層へのドレインコンタクトを有するドレインとを形成することと、を含む、方法。

**【請求項 10】**

請求項 9 に記載の方法であって、

前記堆積システムが、有機金属化学気相成長 (MOCVD) システム、分子ビームエピタキシー (MBE) システム、又はハイドライド気相エピタキシー (HYPE) システムを含む、方法。

**【請求項 11】**

請求項 9 に記載の方法であって、

50

前記 I II A - N 族表面キャップ層の厚さが 0 . 5 nm と 30 nm との間の範囲にある、方法。

**【請求項 12】**

請求項 9 に記載方法であって、

前記基板がシリコン基板である、方法。

**【請求項 13】**

I II A - N 族トランジスタを製造する方法であって、

堆積システムの堆積チャンバにおいて第 1 の温度で少なくとも第 1 の I II A - N 族バッファ層を基板上に堆積すること、

前記堆積システムの前記堆積チャンバにおいて前記第 1 の温度より低い第 2 の温度で前記第 1 の I II A - N 族バッファ層上に少なくとも 1 つの I II A - N 族表面キャップ層を堆積することであって、続いて、前記堆積チャンバがベントされる冷却温度まで継続的に前記堆積チャンバに気体混合物を提供する冷却プロセスを用いて前記基板を 550 度以下に冷却し、前記気体混合物が NH<sub>3</sub> と容量で 40 % 未満の H<sub>2</sub> を含む少なくとも 1 つの他の気体とを含み、前記 I II A - N 族表面キャップ層の表面において、( i ) 2 乗平均平方根 ( rms ) 粗さが 1 nm 未満であり、( ii ) 2 nm 深さより大きいピットに対するピット密度が 0 . 05 μm より小さな平均ピット直径で 10 ピット / μm<sup>2</sup> 未満であるように、前記気体混合物が前記 I II A - N 族表面キャップ層に対して非エッチである前記堆積チャンバにおける雰囲気を提供する、前記堆積することと、

前記 I II A - N 族表面キャップ層上にゲート誘電体層を形成することと、

前記ゲート誘電体層上に金属ゲート電極を形成することと、

前記 I II A - N 族表面キャップ層へのソースコンタクトを有するソースと前記 I II A - N 族表面キャップ層へのドレインコンタクトを有するドレインとを形成することと、

を含む、方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本願は、I II A - N 族 ( Group IIIA-N ) ( 例えば、GaN ) 電界効果トランジスタ ( FET ) に関し、更に特定して言えば、このような FET のためのバッファ層に関連する。

**【背景技術】**

**【0002】**

ガリウム窒化物 ( GaN ) は、通常用いられる I II A - N 族材料であり、I II A - N 族要素 ( Ga 、ボロン、アルミニウム、インジウム、及びタリウムなど ) は、13 族要素と称されることもある。GaN は、ウルツ鉛結晶構造を有するバイナリ II IA / V 直接バンドギャップ半導体である。室温で 3 . 4 eV の ( シリコンに対する 1 . 1 eV に対して ) 比較的広いバンドギャップは、オプトエレクトロニクス、高パワーデバイス、及び高周波数電子デバイスにおける様々な用途に対して特殊な特性を与える。

**【0003】**

GaN 及びシリコンは著しい熱膨張係数ミスマッチを有するので、通常、ひずみ管理のためにシリコン基板と GaN 層との間にバッファ層が用いられる。このバッファ技術は、ヘテロ構造 FET ( H FET ) 又は変調ドープ FET ( MODFET ) デバイスとしても知られる高電子移動度トランジスタ ( HEMT ) のために通常用いられる、大抵の GaN オン Si 技術のベースを形成し、これらのデバイスは、( MOSFET に対して概してみられるような ) ドープされる領域の代わりに、チャネルとして異なるバンドギャップを有する 2 つの材料間の接合 ( 即ち、ヘテロ接合 ) を組み込む電界効果トランジスタである。このようなデバイスのための幾つかのバッファ配置は、超格子構造又は段階的バッファ構造を用いる。

**【0004】**

少なくとも一つのバッファ層の堆積の後、GaN キャップ層堆積が続く。従来のバッファ層及びキャップ層堆積プロセスは、それぞれの堆積温度からの冷却の間、NH<sub>3</sub> 及び H<sub>2</sub>

10

20

30

40

50

を用いる。H<sub>2</sub> 体積流量は、N H<sub>3</sub> 体積流量の概して数倍である。

【発明の概要】

【0005】

記載される例において、III A - N 族トランジスタのためのエピタキシャルスタックを製造する方法が、堆積システムの堆積チャンバにおいて基板上に少なくとも一つのIII A - N 族バッファ層を堆積することを含む。その後、第1のIII A - N 族バッファ層上に、少なくとも一つのIII A - N 族キャップ層が堆積される。キャップ層堆積のための堆積温度からの冷却の間、堆積チャンバに供給される気体混合物は、N H<sub>3</sub> 及び少なくとも一つの他の気体を含む。この気体混合物は、堆積チャンバにおいてキャップ層に対して非エッチングである雰囲気を提供し、そのため、キャップ層の表面において、(a) 二乗平均平方根 (rms) 粗さが 10 μm より小さくなり、(b) 0.05 μm より小さく平均ピット直径で、2 nm 深さより大きいピットのためのピット密度が 10 ピット / μm<sup>2</sup> よりも小さくなるようにする。

10

【図面の簡単な説明】

【0006】

【図1】例示の一実施例に従った、パワーIII A - N 族トランジスタのための少なくとも一つの低欠陥密度キャップ層を含むエピタキシャル層スタックを製造する例示の方法における工程のフローチャートである。

【0007】

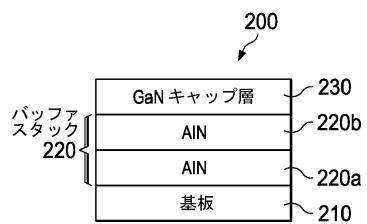

【図2】例示の一実施例に従った、低欠陥密度キャップ層を上に備えるIII A - N 族バッファ層を含む、例示のデバイススタックの断面図である。

20

【0008】

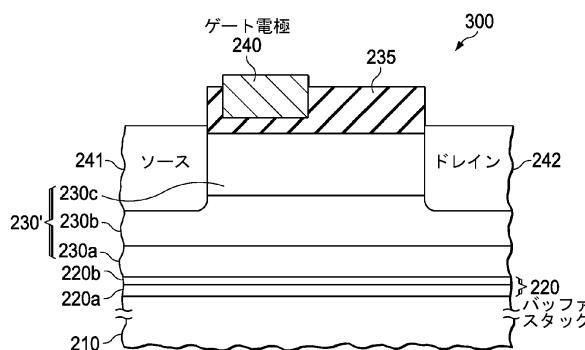

【図3A】例示の一実施例に従った、低欠陥密度キャップ層を有するエピタキシャル層スタックを備える、例示のデブリーションモード高電子移動度トランジスタ (HEMT) の断面図である。

【0009】

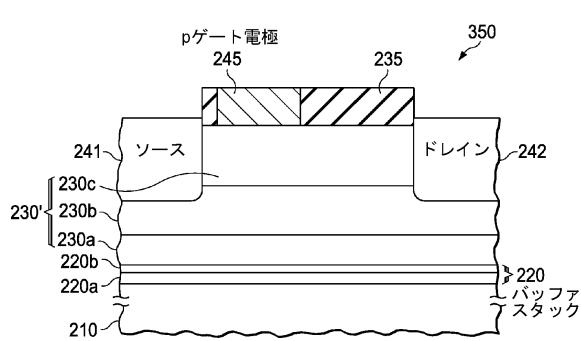

【図3B】例示の一実施例に従った、低欠陥密度キャップ層を有するエピタキシャル層スタックを備えるノーマリーオフゲートを備える、例示のエンハンスマントモードHEMTの断面図である。

【0010】

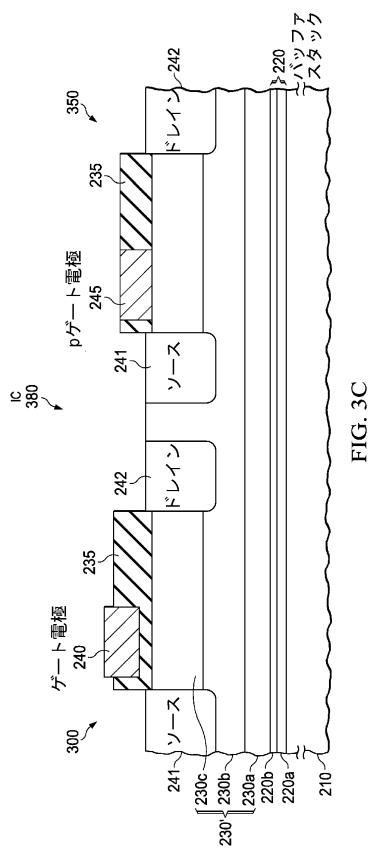

【図3C】図3Aに示すデブリーションモードHEMTパワーデバイス及び図3Bに示すエンハンスマントモードHEMTを含む例示のICの断面図であり、これらのデバイスは、いずれもバッファスタック上の同じ低欠陥密度キャップ層上有る。

30

【発明を実施するための形態】

【0011】

図面は必ずしも一定の縮尺で描いてはいない。図面において、類似の参照番号は、類似の又は等価の要素を示す。幾つかの例示の行為又は事象は、異なる順で及び/又は他の行為又は事象と同時に起こり得る。また、幾つかの例示の行為又は事象は、本記載に従った方法論を実装するために必要とされない可能性がある。

【0012】

40

例示の実施例は、III A - N 族デバイスのためのエピタキシャルIII A - N 族キャップ層堆積後の冷却の間、堆積チャンバに供給される従来のN H<sub>3</sub> 及びH<sub>2</sub> 気体混合物が、冷却時にキャップ層におけるピットとなり、これらが、優先的なエッチングが起こり得る後続のエッチング/洗浄の後、悪化し得ることを認識している。H<sub>2</sub> は、III A - N 族キャップ層 (GaN 又はAlGaNなど) を攻撃し得、ピットを生じさせる。キャップ層における欠陥 (ピットなど) は、パワートランジスタにおける欠陥となり、充分に高い密度でそういった欠陥が存在する場合、それらはデバイス欠陥となる恐れがある。

【0013】

記載される例において、基板上の少なくとも一つのバッファ層の堆積の後、N H<sub>3</sub> 及び少なくとも一つのその他の気体を含む供給気体混合物を用いる冷却プロセスを用いるキャッ

50

層堆積が続き、この気体混合物は、堆積チャンバにおいて、第1のIIIA-N族層に対して非エッティングである雰囲気を提供する。本明細書において用いられる「非エッチである」とは、キャップ層の結果として得られる表面が、(a) 10より小さい二乗平均平方根( $\text{rms}$ )粗さ、及び(b) 0.05  $\mu\text{m}$ より小さな平均ピット直径で、10ピット/ $\mu\text{m}^2$ よりも小さい、2 nm深さより大きいピット層に対するピット密度を有することを指す。一例では、冷却の間、 $\text{NH}_3$ 及び $\text{N}_2$ のみを有する気体混合物を用いる。

#### 【0014】

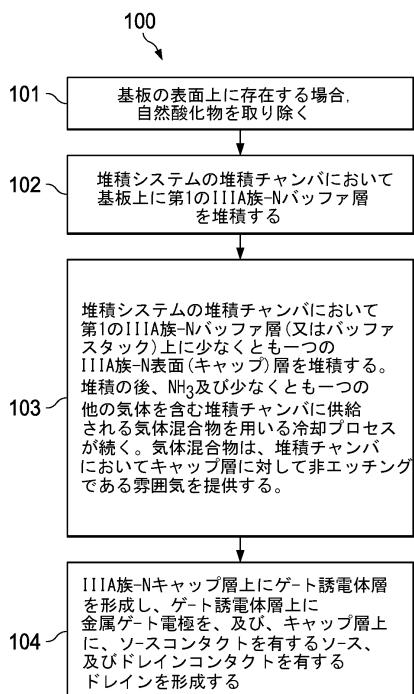

図1は、例示の一実施例に従った、IIIA-N族パワートランジスタのための低欠陥密度キャップ層を含むエピタキシャル層スタックを製造する例示の方法100における工程のフローチャートである。全てのそれぞれのバッファ及びIIIA-N族キャップ層は、有機金属化学気相成長(MOCVD)システム、分子ビームエピタキシー(MBE)システム、又はハイドライド気相エピタキシー(HVPE)システムを用いて、単一の実施においてエピタキシャル成長され得る。

10

#### 【0015】

工程101は、基板(例えば、ウェハ)の表面上に存在する場合、自然酸化物を取り除くことを含む。基板は、サファイア、シリコン、又はシリコンカーバイド(SiC)を含み得る。

#### 【0016】

工程102は、概して1050～1300の堆積温度を用いて、堆積システムの堆積チャンバにおいて基板上に少なくとも第1のIIIA-N族バッファ層を堆積することを含む。バッファ層は、1ミクロン～10ミクロンの厚みであり得る。本明細書に記載されるIIIA-N族バッファ層及びキャップ層は、一般式 $\text{Al}_x\text{Ga}_y\text{In}_{1-x-y}\text{N}$ によって表され得、ここで、 $0 < x \leq 1$ 、 $0 \leq y \leq 1$ 、 $0 < x+y \leq 1$ である。例えば、IIIA-N族層は、 $\text{AlN}$ 、 $\text{AlGaN}$ 、 $\text{AlInN}$ 、及び $\text{AlInGaN}$ のうち少なくとも一つを含み得る。ボロン(B)などの他のIIIA族要素も含まれ得、Nは、リン(P)、砒素(As)、又はアンチモン(Sb)によって部分的に置き換えられ得る。IIIA族窒化物化合物半導体の各々は、Si、C、Ge、Se、O、Fe、Mn、Mg、Ca、Be、Cd、及びZnから選択される任意選択のドーパントを含み得る。

20

#### 【0017】

バッファ層堆積の後、任意選択で、一層高いバッファ層堆積温度(例えば、1250)から、900～1050などのキャップ層堆積の一層低い堆積温度までの、 $\text{NH}_3$ 及び少なくとも一つの他の気体を含む堆積チャンバに供給される気体混合物を用いる冷却プロセス冷却が続き得、この気体混合物は、堆積チャンバにおいて第1のIIIA-N族バッファ層に対して非エッティングである雰囲気を提供する。この冷却プロセスの間のランプダウンレートは、概して5/分～40/分である。その他の気体は、 $\text{N}_2$ 、Ar、He、Ne、Kr、及び/又はこのような気体の組み合わせであり得る。一つの特定の実施例において、 $\text{NH}_3$ が2～20リットル/分で供給され、 $\text{N}_2$ が50～150リットル/分で供給される。混合物が非エッチのままである限り、水素( $\text{H}_2$ )が容量で $\text{H}_2$ 約40%まで提供され得る。

30

#### 【0018】

工程102に続いて、この方法は、任意選択で、バッファスタックを形成するため、第1のIIIA-N族バッファ層上に少なくとも第2のIIIA-N族バッファ層を堆積することを含み得る。他のバッファ層堆積工程が、記載された冷却プロセスを含む本明細書において上記した工程102と同じプロセスの低欠陥密度堆積プロセスを用い得る。

40

#### 【0019】

工程103は、第1のIIIA-N族バッファ層(又はバッファスタック)上に、少なくとも一つのIIIA-N族キャップ層を堆積することを含む。本明細書において上述したように、キャップ層堆積温度は、概して900～1050である。

#### 【0020】

キャップ層堆積の後、 $\text{NH}_3$ 及び少なくとも一つの他の気体を含む気体混合物を用いる、

10

20

30

40

50

堆積温度から概して 300 ~ 550 の温度までの冷却プロセスが続き、この気体混合物は、堆積チャンバにおいてキャップ層に対して非エッチングである雰囲気を提供する。本明細書において上記したように、ここでの「非エッチである」とは、結果として得られるキャップ層が、(a) 10 より小さい二乗平均平方根 (rms) 粗さ、及び、(b) 0.05 μm より小さな平均ピット直径で、10 ピット / μm<sup>2</sup> よりも小さい、2 nm 深さより大きなピット層に対するピット密度を有することを指す。表面粗さは、原子間力顕微鏡 (AFM) システムによって測定され得、ピット密度は、KLA-Tencor CANDELA (登録商標) 8620 検査システムなどの欠陥分析ツールによって測定され得る。

#### 【0021】

その他の気体は、N<sub>2</sub>、Ar、He、Ne、Kr、及び／又はこのような気体の組み合わせであり得る。一つの特定の実施例において、NH<sub>3</sub> が 2 ~ 20 リットル／分で供給され、N<sub>2</sub> が 50 ~ 150 リットル／分で供給される。混合物が非エッチのままである限り、水素 (H<sub>2</sub>) が、容量で H<sub>2</sub> 約 40 % まで提供され得る。この冷却プロセスの間のランプダウンレートは、概して 5 / 分 ~ 40 / 分であり、本明細書において上記したように、300 ~ 550 の温度まで冷却し得、堆積チャンバは、大気に対して排気され、その後、ウェハのポートが概して堆積チャンバから取り除かれる。

#### 【0022】

工程 104 は、キャップ層上にゲート誘電体層（例えば、SiN、SiON、Al<sub>2</sub>O<sub>3</sub>、AlN、シリコン酸化物、又はこれらの層の任意のものの組み合わせ）を形成すること、ゲート誘電体層上に金属ゲート電極を形成すること、並びに、キャップ層上に、ソースコンタクトを有するソース、及びドレインコンタクトを有するドレインを形成することを含む。ゲート電極は、一実施例において TiW 合金を含み得る。ソース及びドレインは、一つの特定の実施例において、Ti / Al / TiN などの金属スタックをスパッタリングすることによって形成され得る。

#### 【0023】

図 2 は、例示の一実施例に従った、多層バッファスタック（バッファ層スタック）220 を含む例示のデバイススタック 200 の断面図であり、多層バッファスタック 220 は、いずれも基板（例えば、シリコン）210 上の AlN 層として示される、第 1 の IIIA - N 族バッファ層 220a 及び第 2 の IIIA - N 族バッファ層 220b を含む。GaN 層として示される IIIA - N 族キャップ層 230 が、第 2 の IIIA - N 族バッファ層 220b 上にあり、IIIA - N 族キャップ層 230 は、冷却の間、堆積チャンバにおいてキャップ層に対して非エッチである雰囲気を用いるキャップ層冷却プロセスを用いて形成される低欠陥密度を有する。別の配置において、第 1 の IIIA - N 族バッファ層 220a が AlN を含み、第 2 の IIIA - N 族バッファ層 220b が GaN を含み、IIIA - N 族キャップ層 230 が AlGaN を含む。IIIA - N 族キャップ層 230 のための例示の厚み範囲は、HEMT 層として用いることができる 5 ~ 300 、第 2 の IIIA - N 族バッファ層 220b のための 50 ~ 300 、及び、第 1 の IIIA - N 族バッファ層 220a のための 0.1 μm ~ 5 μm であり得る。

#### 【0024】

例示の実施例の利点には、一層高いトランジスタ降伏電圧、一層低い漏れ電流、及び低減された基板撓み／ワープを可能にするために、本質的にボイド及びクラックフリーのキャップ層を含む、本質的にボイド及びクラックフリーのエピタキシャル GaN 膜スタックを堆積する能力が含まれる。例えば、パワートランジスタが、1 μamp / mm<sup>2</sup> の漏れ電流密度で、少なくとも 100 V の降伏電圧を提供し得る。

#### 【0025】

記載されるエピタキシャルスタックを用い得るパワー半導体デバイスの例には、HEMT、ダブルヘテロ構造電界効果トランジスタ (DHFET)、ヘテロ接合バイポーラトランジスタ (HBT)、及びバイポーラ接合トランジスタ (BJT) が含まれる。ヘテロ構造 FET (HFET) 又は変調ドープされた FET (MODFET) としても知られる HE

10

20

30

40

50

M Tは、（金属酸化物半導体電界効果トランジスタ（M O S F E T）に対して概してみられるような）ドープされた領域の代わりに、2次元電子ガス（2 D E G）チャネル層として異なるバンドギャップを備える2つの半導体材料間の接合（即ち、ヘテロ接合）を組み込む電界効果トランジスタである。H E M Tは、G a N及びA l G a Nなどの広帯域ギャップを有する化合物半導体を含む。G a N及びI I I A - N材料システムにおける高電子飽和速度に起因して、G a N H E M Tにおける電子移動度は、金属酸化物半導体電界効果トランジスタ（M O S F E T）などの他の一般的なトランジスタのものより高い。

#### 【0026】

図3 Aは、例示の一実施例に従った、基板210上のバッファ層スタック220上にI I I A - N族キャップ層230'を含んで示される記載されるエピタキシャルスタックを備える、例示のデブリーションモードH E M Tパワーデバイス300の断面図である。H E M Tパワーデバイス300は、シリコン窒化物又はシリコンオキシナイトライドを含むなど、ゲート誘電体層235を有して示される。I I I A - N族キャップ層230'は低欠陥密度キャップ層であり、I I I A - N族キャップ層230'の表面は、(a) 10より小さい二乗平均平方根(r m s)粗さ、及び、(b) 0.05 μmより小さな平均ピット直径で、10ピット/μm<sup>2</sup>よりも小さい、2nm深さより大きいピット層のためのピット密度を有する。この実施例において、I I I A - N族キャップ層230'は、最頂部(第1の)G a N層230cと、第2のI I I A - N族バッファ層220b上にある最低部(第2の)G a N層230aとの間に挟まれる、A l G a N層230bを含み得る。最頂部G a N層230c及び最低部G a N層230aは概して、各々、1×10<sup>15</sup> cm<sup>-3</sup>~1×10<sup>18</sup> cm<sup>-3</sup>のドーピング濃度を有する。ドーパントは、炭素、マグネシウム、シリコン、又は亜鉛、又はこのようなドーパントの組み合わせを含み得る。

10

20

30

#### 【0027】

H E M Tパワーデバイス300は、ディスクリートデバイス、又はI C上の多くのデバイスの一つであり得る。より概して言えば、I I I A - N族キャップ層230'は、G a N、I n N、A 1 N、A l G a N、A l I n N、I n G a N、及びA l I n G a Nの一つ又は複数を含み得る。本明細書において上記したように、I I I A - N族層は、Bなどの他のI I I A族要素を含み得、Nは、P、A s、又はS bによって部分的に置き換えられ得、また、任意選択のドーパントを含み得る。別の特定の例において、I I I A - N族キャップ層230'は、A l<sub>x</sub> G a<sub>y</sub> N層又はI n<sub>x</sub> A l<sub>y</sub> N層の頂部上のG a N層を含み得る。更に別の特定の例は、A l G a N上のI n A l N上のG a Nを含み得る3層スタックであるI I I A - N族キャップ層230'である。

#### 【0028】

H E M Tパワーデバイス300は、ソース241、ドレイン242、及びゲート電極240を含む。ゲート電極240は、ソース241とドレイン242との間に、ドレイン242よりもソース241の近くに置かれる。ソース241、ドレイン242、及びゲート電極240は、金属及び/又は金属窒化物で形成され得るが、例示の実施例はそれらに限定されない。

#### 【0029】

図3 Bは、例示の一実施例に従った、基板210上にバッファ層スタック220として示されるバッファ層上にI I I A - N族キャップ層230'を備えるノーマリーオフゲートを備える、例示のエンハンスマントモードH E M Tパワーデバイス350の断面図である。I I I A - N族キャップ層230'は、低欠陥密度キャップ層であり、I I I A - N族キャップ層230'の表面が、(a) 10より小さい二乗平均平方根(r m s)粗さ、及び、(b) 0.05 μmより小さな平均ピット直径で、10ピット/μm<sup>2</sup>よりも小さい、2nm深さより大きいピット層のためのピット密度を有する。この実施例において、ゲート電極は、I I I A - N族キャップ層230c(例えば、G a N層)と直接接するpドープされたゲート電極245(pゲート電極として示される)。図3 Cは、いずれも同じキャップ層及びバッファ層スタックを用いる、図3 Aに示すデブリーションモードH E M Tパワーデバイス300及び図3 Bに示すエンハンスマントモードH E M Tを含む、例示のI C

40

50

380の断面図である。

### 【0030】

例示の実施例が更に、以下の例により例示される。

### 【0031】

キャップ層冷却のためのNH<sub>3</sub>/H<sub>2</sub>気体混合物を用いて形成される既知のキャップ層と比べた、NH<sub>3</sub>/N<sub>2</sub>キャップ層冷却を用いて形成されるSi基板上のキャップ層に対してAFMデータが取られた。一例において、NH<sub>3</sub>/N<sub>2</sub>フローレシオは、50~150リットル/分の範囲のNH<sub>3</sub>及びN<sub>2</sub>の2~20リットル/分のフローで、1:10である。堆積されると、記載されたNH<sub>3</sub>/N<sub>2</sub>キャップ層冷却で処理されたウェハは、幾つかの異なる実施からのウェハからのデータで、一貫して表面ピットがないことを示した。これに対し、既知のNH<sub>3</sub>/H<sub>2</sub>キャップ層冷却で処理されたウェハは、幾つかの異なる実施からのウェハから得たデータで、10nmから~200nmまでの範囲のサイズで、一貫して、1×10<sup>10</sup>/cm<sup>2</sup>の表面ピットを示した。

10

### 【0032】

キャップ層におけるピットは、欠陥サイトにおいて優先的なエッティングが成されることが分っている後続のエッティング/洗浄の後、悪化し得ることも分かった。NH<sub>3</sub>/N<sub>2</sub>冷却されたキャップ層プロセスからのキャップ層と、キャップ層冷却のためにN<sub>2</sub>/H<sub>2</sub>気体混合物を用いて形成された既知のキャップ層とを備えるウェハが、2セットの洗浄プロセスを受けた。両方のキャップ層プロセスのためのウェハに対して、AFM分析が実施された。NH<sub>3</sub>/N<sub>2</sub>冷却されたキャップ層からのキャップ層を備えるウェハでは、堆積されたピットの深さは、約0.7nm~1nmであり、2セットの洗浄プロセスの後、約0.7nm~1nmの深さのままであった。既知のNH<sub>3</sub>/H<sub>2</sub>冷却されたプロセスからのキャップ層を備えるウェハでは、堆積されたピットの深さは、約1nm~3nmであり、その深さは、2セットの洗浄プロセスの後、6nm~10nmの深さまで増大された。

20

### 【0033】

高温逆バイアス(HTRB)HEMTデバイスデータが得られ、ここで、キャップ層はGaNを含んでおり、バッファ層は、N<sub>2</sub>/NH<sub>3</sub>キャップ層冷却を用いて形成されるAlGaN、及び既知のNH<sub>3</sub>/H<sub>2</sub>キャップ層冷却を用いて形成される制御GaNキャップ層を含んでいた。

30

### 【0034】

HTRB欠陥は、GaNキャップ層ピットに起因する信頼性欠陥に関連していた。既知のN<sub>2</sub>/H<sub>2</sub>キャップ層冷却を用いて形成される制御GaNキャップ層を有するHEMTは、5%~10%のバーンイン故障率を有し、NH<sub>3</sub>/N<sub>2</sub>キャップ層冷却を用いて形成されるGaNキャップ層を有するHEMTは、2%未満のHTRB欠陥故障率を有していた。

### 【0035】

例示の実施例は、種々の異なるデバイス及び関連する製品を形成するための種々のアッセンブリフローに統合される得る半導体ダイを形成するために有用である。こういった半導体ダイは、その中に種々の要素を含み得、及び/又はその上に種々の層を含み得、これらには、障壁層、誘電体層、デバイス構造、能動要素、並びに、ソース領域、ドレイン領域、ピットライン、ベース、エミッタ、コレクタ、導電性ライン、及び導電性ビアを含む受動要素、が含まれる。また、こういった半導体ダイは、バイポーラ、絶縁ゲートバイポーラトランジスタ(IGBT)、CMOS、BiCMOS、及びMEMSを含む種々のプロセスから形成され得る。

40

### 【0036】

本発明の特許請求の範囲内で、説明した例示の実施例に改变が成され得、他の実施例も可能である。

50

## 【図面】

## 【図1】

FIG. 1

## 【図2】

FIG. 2

10

## 【図3 A】

FIG. 3A

## 【図3 B】

FIG. 3B

30

40

50

【図 3 C】

FIG. 3C

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類 F I

H 01 L 29/808 (2006.01)

H 01 L 21/336 (2006.01)

H 01 L 29/78 (2006.01)

0 9

審査官 田中 崇大

(56)参考文献 特開2015-185809 (JP, A)

特開2001-320084 (JP, A)

特開2003-031845 (JP, A)

特開2007-184353 (JP, A)

特開2008-098603 (JP, A)

特開2014-197645 (JP, A)

特開2015-192026 (JP, A)

特開2013-074209 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 01 L 21 / 205

H 01 L 21 / 338

H 01 L 21 / 337

H 01 L 21 / 336