(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4114668号

(P4114668)

(45) 発行日 平成20年7月9日(2008.7.9)

(24) 登録日 平成20年4月25日(2008.4.25)

(51) Int.Cl.

F 1

|             |              |                  |      |       |      |

|-------------|--------------|------------------|------|-------|------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/36  |      |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20  | 622E |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G09G | 3/20  | 623H |

| <b>G11C</b> | <b>19/00</b> | <b>(2006.01)</b> | G09G | 3/20  | 670E |

| <b>G11C</b> | <b>19/28</b> | <b>(2006.01)</b> | GO2F | 1/133 | 550  |

請求項の数 8 (全 53 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2005-87463 (P2005-87463)    |

| (22) 出願日  | 平成17年3月25日 (2005.3.25)        |

| (65) 公開番号 | 特開2006-267753 (P2006-267753A) |

| (43) 公開日  | 平成18年10月5日 (2006.10.5)        |

| 審査請求日     | 平成19年5月18日 (2007.5.18)        |

早期審査対象出願

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 304053854<br>エプソンイメージングデバイス株式会社<br>長野県安曇野市豊科田沢6925   |

| (74) 代理人  | 100104433<br>弁理士 宮園 博一                               |

| (72) 発明者  | 堀端 浩行<br>東京都港区浜松町二丁目4番地1号 三洋<br>エプソンイメージングデバイス株式会社内  |

| (72) 発明者  | 千田 みちる<br>東京都港区浜松町二丁目4番地1号 三洋<br>エプソンイメージングデバイス株式会社内 |

| 審査官       | 小松 徹三                                                |

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1シフト信号を出力する第1シフトレジスタ回路部と、

前記第1シフトレジスタ回路部の次段に配置されるとともに、第2シフト信号を出力する第2シフトレジスタ回路部と、

第1電位でオンする第1導電型の複数のトランジスタによって構成され、前記第1シフト信号および前記第2シフト信号が入力されるとともに、前記第1シフト信号と、前記第2シフト信号とを論理合成してシフト出力信号を出力する論理合成回路部と、

を含むシフトレジスタ回路を備え、前記第1シフトレジスタ回路部および前記第2シフトレジスタ回路部は、両方とも、所定の駆動信号に応答して、前記第1シフト信号または前記第2シフト信号が出力されるノードの電位を前記論理合成回路部のトランジスタがオンしない第2電位にリセットするためのリセットトランジスタを含み、

前記論理合成回路部のトランジスタは、

ソース／ドレインの一方が前記第1電位と前記第2電位とに切り替わる第1信号を供給する第1信号線に接続されるとともに、ゲートに前記第1シフト信号が入力される第1トランジスタと、

前記第1トランジスタのソース／ドレインの他方にソース／ドレインの一方が接続されるとともに、ゲートに前記第2シフト信号が入力される第2トランジスタとを含み、

前記第1シフト信号および前記第2シフト信号が前記第1電位のときに、前記第1トランジスタをリセットする。

10

20

ンジスタおよび前記第2トランジスタがオン状態になるとともに、前記第1信号線から前記第1トランジスタのソース／ドレンインの一方に前記第1電位の前記第1信号が供給されることにより、前記第1トランジスタおよび前記第2トランジスタを介して前記第1電位の前記シフト出力信号が出力され、

前記第1シフト信号が前記第1電位から前記第2電位に変化する直前に、前記第1信号線から前記第1トランジスタのソース／ドレンインの一方に前記第2電位の前記第1信号が供給されることにより、前記第1トランジスタおよび前記第2トランジスタを介して前記第2電位の前記シフト出力信号が出力され、

前記第1シフトレジスタ回路部は、ドレンインに少なくとも前記第1電位が供給されるとともに、ゲートが前記第1シフト信号が出力されるノードに接続される第3トランジスタと、前記第3トランジスタのゲート－ソース間に接続される第1容量とを含み、

前記第2シフトレジスタ回路部は、ドレンインに少なくとも前記第1電位が供給されるとともに、ゲートが前記第2シフト信号が出力されるノードに接続される第4トランジスタと、前記第4トランジスタのゲート－ソース間に接続される第2容量とを含む、表示装置。

【請求項2】

前記所定の駆動信号は、前記シフトレジスタ回路による走査を開始させるためのスタート信号である、請求項1に記載の表示装置。

【請求項3】

前記第1シフトレジスタ回路部および前記第2シフトレジスタ回路部の少なくとも一方は、前段の第1回路部と後段の第2回路部とを含み、

前記第2回路部は、前記第2電位側と前記第1シフト信号または前記第2シフト信号が出力されるノードとの間に接続されるとともに、前記第1回路部の出力ノードにゲートが接続された第1導電型の第5トランジスタを含み、

前記リセットトランジスタは、前記所定の駆動信号に応答して、前記第1回路部の出力ノードを前記第1電位にリセットする機能を有し、

前記リセットトランジスタにより前記第1回路部の出力ノードが前記第1電位にリセットされることに応答して、前記第5トランジスタがオン状態になることによって、前記第2回路部の前記第1シフト信号または前記第2シフト信号が出力されるノードが前記第2電位にリセットされる、請求項1または2に記載の表示装置。

【請求項4】

前記リセットトランジスタは、前記第1電位側と前記第1回路部の出力ノードとの間に接続されているとともに、前記所定の駆動信号を供給する第1駆動信号線にゲートが接続されている、請求項3に記載の表示装置。

【請求項5】

前記第1駆動信号線は、前記所定の駆動信号としての前記シフトレジスタ回路の走査を開始させるためのスタート信号を供給するスタート信号線である、請求項4に記載の表示装置。

【請求項6】

前記リセットトランジスタは、前記所定の駆動信号に応答して、前記第3トランジスタまたは前記第4トランジスタのソースの電位を前記第2電位にリセットする機能も有している、請求項1に記載の表示装置。

【請求項7】

前記シフトレジスタ回路は、ゲート線を駆動するためのシフトレジスタ回路、および、ドレンイン線を駆動するためのシフトレジスタ回路の少なくとも一方に適用されている、請求項1～6のいずれか1項に記載の表示装置。

【請求項8】

前記第1シフトレジスタ回路部、前記第2シフトレジスタ回路部および前記論理合成回路部を構成するトランジスタと、前記リセットトランジスタとは、第1導電型を有する、請求項1～7のいずれか1項に記載の表示装置。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置に関し、特に、シフトレジスタ回路を備えた表示装置に関する。

**【背景技術】****【0002】**

従来、シフトレジスタ回路を備えた表示装置が知られている（たとえば、特許文献1参照）。

**【0003】**

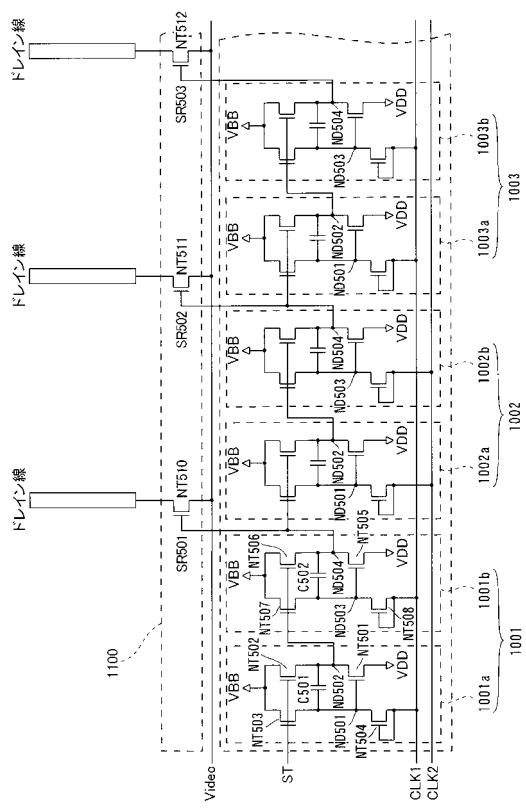

図18は、上記特許文献1に開示された従来の一例による表示装置のドレイン線を駆動させるシフトレジスタ回路の回路構成を説明するための回路図である。図18を参照して、従来の一例による表示装置のドレイン線を駆動させるシフトレジスタ回路では、複数段のシフトレジスタ回路部1001～1003が設けられている。1段目のシフトレジスタ回路部1001は、前段の第1回路部1001aおよび後段の第2回路部1001bによって構成されている。また、1段目のシフトレジスタ回路部1001の第1回路部1001aは、nチャネルトランジスタNT501～NT503と、ダイオード接続されたnチャネルトランジスタNT504と、容量C501とを含んでいる。また、1段目のシフトレジスタ回路部1001の第2回路部1001bは、nチャネルトランジスタNT505～NT507と、ダイオード接続されたnチャネルトランジスタNT508と、容量C502とを含んでいる。以下、nチャネルトランジスタNT501～NT508は、トランジスタNT501～NT508と称する。

10

**【0004】**

また、第1回路部1001aにおいて、トランジスタNT501のドレインは、正側電位VDDに接続されるとともに、ソースは、トランジスタNT502のドレインと接続されている。また、トランジスタNT501のゲートは、ノードND501に接続されている。トランジスタNT502のソースは、負側電位VBBに接続されている。また、トランジスタNT502のゲートにはスタート信号STが供給される。また、トランジスタNT501のゲートが接続されたノードND501と、負側電位VBBとの間には、トランジスタNT503が接続されている。また、トランジスタNT503のゲートには、スタート信号STが供給される。また、トランジスタNT501のゲートとソースとの間には、容量C501が接続されている。また、トランジスタNT501のゲートが接続されたノードND501と、クロック信号線CLK1との間にダイオード接続されたトランジスタNT504が接続されている。

20

**【0005】**

また、第2回路部1001bにおいて、トランジスタNT505のドレインは、正側電位VDDに接続されている。トランジスタNT505のソースは、トランジスタNT506のドレインと接続されている。また、トランジスタNT505のゲートは、ノードND503に接続されている。トランジスタNT506のソースは、負側電位VBBに接続されている。また、トランジスタNT506のゲートは、第1回路部1001aのトランジスタNT501とトランジスタNT502との間に設けられたノードND502に接続されている。

30

**【0006】**

また、トランジスタNT505のゲートが接続されたノードND503と、負側電位VBBとの間には、トランジスタNT507が接続されている。また、トランジスタNT507のゲートは、第1回路部1001aのノードND502に接続されている。また、トランジスタNT505のゲートとソースとの間には、容量C502が接続されている。また、トランジスタNT505のゲートが接続されたノードND503と、クロック信号線CLK1との間にダイオード接続されたトランジスタNT508が接続されている。

40

**【0007】**

また、トランジスタNT505のソースとトランジスタNT506のドレインとの間に

50

設けられたノード N D 5 0 4 (出力ノード) から 1 段目のシフトレジスタ回路 1 0 0 1 のシフト出力信号 S R 5 0 1 が出力される。また、2 段目以降のシフトレジスタ回路部 1 0 0 2 および 1 0 0 3 は、1 段目のシフトレジスタ回路部 1 0 0 1 と同様の回路構成を有する。すなわち、2 段目のシフトレジスタ回路部 1 0 0 2 は、1 段目のシフトレジスタ回路部 1 0 0 1 の第 1 回路部 1 0 0 1 a および第 2 回路部 1 0 0 1 b と同様の回路構成を有する第 1 回路部 1 0 0 2 a および第 2 回路部 1 0 0 2 b を含んでいる。2 段目のシフトレジスタ回路部 1 0 0 2 の第 1 回路部 1 0 0 2 a は、1 段目のシフトレジスタ回路部 1 0 0 1 の第 2 回路部 1 0 0 1 b のノード N D 5 0 4 (出力ノード) に接続されている。これにより、1 段目のシフトレジスタ回路部 1 0 0 1 のシフト出力信号 S R 5 0 1 は、2 段目のシフトレジスタ回路部 1 0 0 2 の第 1 回路部 1 0 0 2 a に入力される。また、2 段目のシフトレジスタ回路部 1 0 0 2 には、1 段目のシフトレジスタ回路部 1 0 0 1 に供給されるクロック信号 C L K 1 とタイミングの異なるクロック信号 C L K 2 を供給するクロック信号線 (C L K 2) が接続されている。また、2 段目のシフトレジスタ回路部 1 0 0 2 の第 2 回路部のノード N D 5 0 4 (出力ノード) から 2 段目のシフトレジスタ回路部 1 0 0 2 のシフト出力信号 S R 5 0 2 が出力される。

10

#### 【0 0 0 8】

また、3 段目のシフトレジスタ回路部 1 0 0 3 は、1 段目のシフトレジスタ回路部 1 0 0 1 の第 1 回路部 1 0 0 1 a および第 2 回路部 1 0 0 1 b と同様の回路構成を有する第 1 回路部 1 0 0 3 a および第 2 回路部 1 0 0 3 b を含んでいる。3 段目のシフトレジスタ回路部 1 0 0 3 の第 1 回路部 1 0 0 3 a は、2 段目のシフトレジスタ回路部 1 0 0 2 の第 2 回路部 1 0 0 2 b のノード N D 5 0 4 (出力ノード) に接続されている。これにより、2 段目のシフトレジスタ回路部 1 0 0 2 のシフト出力信号 S R 5 0 2 は、3 段目のシフトレジスタ回路部 1 0 0 3 の第 1 回路部 1 0 0 3 a に入力される。また、3 段目のシフトレジスタ回路部 1 0 0 3 には、1 段目のシフトレジスタ回路部 1 0 0 1 と同じクロック信号 C L K 1 を供給するクロック信号線 (C L K 1) が接続されている。また、3 段目のシフトレジスタ回路部 1 0 0 3 の第 2 回路部のノード N D 5 0 4 (出力ノード) から 3 段目のシフトレジスタ回路部 1 0 0 3 のシフト出力信号 S R 5 0 3 が出力される。このシフト出力信号 S R 5 0 3 は、図示しない次段のシフトレジスタ回路部の第 1 回路部に入力される。

20

#### 【0 0 0 9】

また、各段のシフトレジスタ回路部 1 0 0 1 ~ 1 0 0 3 のノード N D 5 0 4 は、水平スイッチ 1 1 0 0 に接続されている。具体的には、水平スイッチ 1 1 0 0 は、複数のトランジスタ N T 5 1 0 ~ N T 5 1 2 を備えている。このトランジスタ N T 5 1 0 ~ N T 5 1 2 のゲートは、それぞれ、1 段目 ~ 3 段目のシフトレジスタ回路 1 0 0 1 ~ 1 0 0 3 のノード N D 5 0 4 に接続されている。これにより、各段のシフトレジスタ回路部 1 0 0 1 ~ 1 0 0 3 のシフト出力信号 S R 5 0 1 ~ S R 5 0 3 は、それぞれ、水平スイッチ 1 1 0 0 のトランジスタ N T 5 1 0 ~ N T 5 1 2 のゲートに入力される。また、トランジスタ N T 5 1 0 ~ N T 5 1 2 のドレインは、それぞれ、各段のドレイン線に接続されている。また、トランジスタ N T 5 1 0 ~ N T 5 1 2 のソースは、ビデオ信号線 V i d e o に接続されている。

30

#### 【0 0 1 0】

上記のように構成することによって、従来の一例による表示装置のドレイン線を駆動させるシフトレジスタ回路では、各段のシフトレジスタ回路部 1 0 0 1 ~ 1 0 0 3 によって H レベルに立ち上がるタイミングがシフトされたシフト出力信号 S R 5 0 1 ~ S R 5 0 3 が水平スイッチ 1 1 0 0 のトランジスタ N T 5 1 0 ~ N T 5 1 2 のゲートにそれぞれ入力される。これにより、水平スイッチ 1 1 0 0 のトランジスタ N T 5 1 0 ~ N T 5 1 2 が順次オン状態になるので、トランジスタ N T 5 1 0 ~ N T 5 1 2 を介して、ビデオ信号線 V i d e o から各段のドレイン線に、順次、映像信号が出力されるように構成されている。

40

#### 【0 0 1 1】

【特許文献 1】特開 2 0 0 5 - 1 7 9 7 3 号公報

【発明の開示】

## 【発明が解決しようとする課題】

## 【0012】

しかしながら、図18に示した従来の一例によるシフトレジスタ回路を備えた表示装置では、シフトレジスタ回路に正側電位VDDと負側電位VBBとを供給した後、シフトレジスタ回路による走査をまだ行っていない状態で、各段のシフトレジスタ回路部1001～1003の出力ノードであるノードND504の電位が正側電位VDDと負側電位VBBとの間の不安定な電位になるという不都合がある。これにより、ノードND504にゲートが接続された水平スイッチ1100のトランジスタNT510～NT512が意図しないタイミングでオンする場合があるという不都合がある。この場合には、そのオン状態になったトランジスタNT510～NT512を介して、ビデオ信号線Videoから映像信号がドレイン線に出力されるので、意図しないタイミングでドレイン線に映像信号が出力されるという問題点がある。10

## 【0013】

この発明は、上記のような課題を解決するためになされたものであり、この発明の1つの目的は、ゲート線やドレイン線に意図しないタイミングで信号が出力されるのを抑制することが可能な表示装置を提供することである。

## 【課題を解決するための手段および発明の効果】

## 【0014】

上記目的を達成するために、この発明の一の局面による表示装置は、第1シフト信号を出力する第1シフトレジスタ回路部と、第1シフトレジスタ回路部の次段に配置されるとともに、第2シフト信号を出力する第2シフトレジスタ回路部と、第1電位でオンする第1導電型の複数のトランジスタによって構成され、第1シフト信号および第2シフト信号が入力されるとともに、第1シフト信号と、第2シフト信号とを論理合成してシフト出力信号を出力する論理合成回路部とを含むシフトレジスタ回路を備えている。また、第1シフトレジスタ回路部および第2シフトレジスタ回路部は、両方とも、所定の駆動信号に応答して、第1シフト信号または第2シフト信号が出力されるノードの電位を論理合成回路部のトランジスタがオンしない第2電位にリセットするためのリセットトランジスタを含み、論理合成回路部のトランジスタは、ソース／ドレインの一方が第1電位と第2電位とに切り替わる第1信号を供給する第1信号線に接続されるとともに、ゲートに第1シフト信号が入力される第1トランジスタと、第1トランジスタのソース／ドレインの他方にソース／ドレインの一方が接続されるとともに、ゲートに第2シフト信号が入力される第2トランジスタとを含み、第1シフト信号および第2シフト信号が第1電位のときに、第1トランジスタおよび第2トランジスタがオン状態になるとともに、第1信号線から第1トランジスタのソース／ドレインの一方で第1電位の第1信号が供給されることにより、第1トランジスタおよび第2トランジスタを介して第1電位のシフト出力信号が出力され、第1シフト信号が第1電位から第2電位に変化する直前に、第1信号線から第1トランジスタのソース／ドレインの一方で第2電位の第1信号が供給されることにより、第1トランジスタおよび第2トランジスタを介して第2電位のシフト出力信号が出力され、第1シフトレジスタ回路部は、ドレインに少なくとも第1電位が供給されるとともに、ゲートが第1シフト信号が出力されるノードに接続される第3トランジスタと、第3トランジスタのゲート-ソース間に接続される第1容量とを含み、第2シフトレジスタ回路部は、ドレインに少なくとも第1電位が供給されるとともに、ゲートが第2シフト信号が出力されるノードに接続される第4トランジスタと、第4トランジスタのゲート-ソース間に接続される第2容量とを含む。30

## 【0015】

この一の局面による表示装置では、上記のように、第1シフトレジスタ回路部が所定の駆動信号に応答して第1シフト信号または第2シフト信号が出力されるノードの電位を論理合成回路部のトランジスタがオンしない第2電位にリセットするためのリセットトランジスタを含むように構成することによって、シフトレジスタ回路への電源投入後に、所定の駆動信号を入力して、リセットトランジスタにより第1シフト信号または第2シフト信4050

号が出力されるノードの電位を第2電位にリセットすれば、論理合成回路部へ出力される第1シフト信号および第2シフト信号の少なくとも一方を論理合成回路部のトランジスタがオンしない第2電位に固定することができる。これにより、論理合成回路部の2つのトランジスタのゲートにそれぞれ第1シフト信号と第2シフト信号とを入力するとともに、その2つのトランジスタを介して出力される信号を第1シフト信号と第2シフト信号とが論理合成されたシフト出力信号として用いる場合に、第1シフト信号および第2シフト信号の少なくとも一方を論理合成回路部のトランジスタがオンしない第2電位に固定することができるので、論理合成回路部の2つのトランジスタの少なくとも一方をオフ状態に保持することができる。このため、論理合成回路部の2つのトランジスタを介してシフト出力信号は出力されないので、ゲート線やドレイン線に意図しないタイミングで信号が出力されるのを抑制することができる。また、論理合成回路部のトランジスタは、ソース／ドレインの一方が第1電位と第2電位とに切り替わる第1信号を供給する第1信号線に接続されるとともに、ゲートに第1シフト信号が入力される第1トランジスタと、第1トランジスタのソース／ドレインの他方にソース／ドレインの一方が接続されるとともに、ゲートに第2シフト信号が入力される第2トランジスタとを含み、第1シフト信号および第2シフト信号が第1電位のときに、第1トランジスタおよび第2トランジスタがオン状態になるとともに、第1信号線から第1トランジスタのソース／ドレインの一方に第1電位の第1信号が供給されることにより、第1トランジスタおよび第2トランジスタを介して第1電位のシフト出力信号が出力され、第1シフト信号が第1電位から第2電位に変化する直前に、第1信号線から第1トランジスタのソース／ドレインの一方に第2電位の第1信号が供給されることにより、第1トランジスタおよび第2トランジスタを介して第2電位のシフト出力信号が出力される。このように構成すれば、第1シフト信号および第2シフト信号が第1電位のときに、論理合成回路部の第1トランジスタおよび第2トランジスタの2つのトランジスタを介して、第1電位の第1シフト信号と第1電位の第2シフト信号とを論理合成した第1電位のシフト出力信号を出力することができるとともに、第1シフト信号が第1電位から第2電位に変化する直前に、論理合成回路部の第1トランジスタおよび第2トランジスタの2つのトランジスタを介して、第2電位の第1シフト信号と第1電位の第2シフト信号とを論理合成した第2電位のシフト出力信号を出力することができる。これにより、容易に、論理合成回路部から第1シフト信号と第2シフト信号とを論理合成したシフト出力信号を出力することができる。また、第1シフトレジスタ回路部は、ドレインに少なくとも第1電位が供給されるとともに、ゲートが第1シフト信号が出力されるノードに接続される第3トランジスタと、第3トランジスタのゲート－ソース間に接続される第1容量とを含み、第2シフトレジスタ回路部は、ドレインに少なくとも第1電位が供給されるとともに、ゲートが第2シフト信号が出力されるノードに接続される第4トランジスタと、第4トランジスタのゲート－ソース間に接続される第2容量とを含む。このように構成すれば、たとえば、第3トランジスタ（第4トランジスタ）のドレインに正側電位VDDが供給されるとともに、第3トランジスタ（第4トランジスタ）のゲート電位をVDDよりも第3トランジスタ（第4トランジスタ）のしきい値電圧（Vt）以上の所定の電圧（V）分高い電位まで上昇させることができるので、論理合成回路部の第1トランジスタおよび第2トランジスタのゲートに、それぞれ、VDD + Vtよりも高い電位（VDD + V）を有する第1シフト信号および第2シフト信号を供給することができる。これにより、論理合成回路部の第1トランジスタおよび第2トランジスタを介して出力されるシフト出力信号の電位が、VDDから第1トランジスタおよび第2トランジスタのしきい値電圧（Vt）分だけ低下するのを抑制することができる。また、第3トランジスタ（第4トランジスタ）のドレインに負側電位VBBが供給されるとともに、第3トランジスタ（第4トランジスタ）のゲート電位をVBBよりも第3トランジスタ（第4トランジスタ）のしきい値電圧（Vt）以上の所定の電圧（V）分低い電位まで低下させることができるので、論理合成回路部の第1トランジスタおよび第2トランジスタのゲートに、それぞれ、VBB - 10

20

30

40

50

$V_t$ よりも低い電位 ( $V_{DD} - V_t$ ) を有する第1シフト信号および第2シフト信号を供給することができる。これにより、論理合成回路部の第1トランジスタおよび第2トランジスタを介して出力されるシフト出力信号の電位が、 $V_{BB}$ から第1トランジスタおよび第2トランジスタのしきい値電圧 ( $V_t$ ) 分だけ上昇するのを抑制することができる。

【0016】

上記一の局面による表示装置において、好ましくは、第1シフトレジスタ回路部および第2シフトレジスタ回路部は、両方とも、リセットトランジスタを含む。このように構成すれば、リセットトランジスタにより第1シフトレジスタ回路部から出力される第1シフト信号と、第2シフトレジスタ回路部から出力される第2シフト信号とを両方とも論理合成回路部のトランジスタがオンしない第2電位に固定することができる。これにより、論理合成回路部の2つのトランジスタのゲートにそれぞれ第1シフト信号と第2シフト信号とを入力するとともに、その2つのトランジスタを介して出力される信号を第1シフト信号と第2シフト信号とが論理合成されたシフト出力信号として用いる場合に、論理合成回路部の2つのトランジスタを両方ともオフ状態に保持することができる。このため、論理合成回路部からゲート線やドレイン線に意図しないタイミングで信号が出力されるのをより確実に抑制することができる。

10

【0017】

上記一の局面による表示装置において、好ましくは、所定の駆動信号は、シフトレジスタ回路による走査を開始させるためのスタート信号である。このように構成すれば、所定の駆動信号を生成するための信号生成回路を別途形成する必要がないので、表示装置の回路構成が複雑化するのを抑制することができる。

20

【0018】

上記一の局面による表示装置において、好ましくは、第1シフトレジスタ回路部および第2シフトレジスタ回路部の少なくとも一方は、前段の第1回路部と後段の第2回路部とを含み、第2回路部は、第2電位側と第1シフト信号または第2シフト信号が出力されるノードとの間に接続されるとともに、第1回路部の出力ノードにゲートが接続された第1導電型の第1トランジスタを含み、リセットトランジスタは、所定の駆動信号に応答して、第1回路部の出力ノードを第1電位にリセットする機能を有し、リセットトランジスタにより第1回路部の出力ノードが第1電位にリセットされることに応答して、第1トランジスタがオン状態になることによって、第2回路部の第1シフト信号または第2シフト信号が出力されるノードが第2電位にリセットされる。このように構成すれば、リセットトランジスタにより所定の駆動信号に応答して第1回路部の出力ノードを第1電位にリセットすることによって、第1回路部の出力ノードにゲートが接続された第1導電型の第1トランジスタをオンさせることができるので、第1トランジスタを介して第2電位側から第1シフト信号または第2シフト信号が出力されるノードに第2電位を供給することができる。これにより、容易に、所定の駆動信号に応答して、第1シフト信号または第2シフト信号が出力されるノードの電位を第2電位にリセットすることができる。

30

【0019】

上記リセットトランジスタが第1回路部の出力ノードを第1電位にリセットする機能を有する構成において、好ましくは、リセットトランジスタは、第1電位側と第1回路部の出力ノードとの間に接続されているとともに、所定の駆動信号を供給する第1駆動信号線にゲートが接続されている。このように構成すれば、容易に、リセットトランジスタに、所定の駆動信号に応答して、第1回路部の出力ノードを第1電位にリセットする機能を持たせることができる。

40

【0020】

上記第1駆動信号線を含む構成において、第1駆動信号線は、所定の駆動信号としてのシフトレジスタ回路の走査を開始させるためのスタート信号を供給するスタート信号線である。このように構成すれば、所定の駆動信号としてスタート信号を用いることができる。所定の駆動信号を生成するための信号生成回路を別途形成する必要がない。これにより、表示装置の回路構成が複雑化するのを抑制することができる。また、第1駆動信号

50

線としてスタート信号を供給するスタート信号線を用いることによって、所定の駆動信号を供給するための第1駆動信号線として、別途配線を設ける必要がないので、表示装置の回路規模が増大するのを抑制することができる。

【0021】

上記一の局面による表示装置において、好ましくは、論理合成回路部のトランジスタは、ソース／ドレインの一方が第1電位と第2電位とに切り替わる第1信号を供給する第1信号線に接続されるとともに、ゲートに第1シフト信号が入力される第2トランジスタと、第2トランジスタのソース／ドレインの他方にソース／ドレインの一方が接続されるとともに、ゲートに第2シフト信号が入力される第3トランジスタとを含み、第1シフト信号および第2シフト信号が第1電位のときに、第2トランジスタおよび第3トランジスタがオン状態になるとともに、第1信号線から第2トランジスタのソース／ドレインの一方に第1電位の第1信号が供給されることにより、第2トランジスタおよび第3トランジスタを介して第1電位のシフト出力信号が出力され、第1シフト信号が第1電位から第2電位に変化する際に、第1信号線から第2トランジスタのソース／ドレインの一方に第2電位の第1信号が供給されることにより、第2トランジスタおよび第3トランジスタを介して第2電位のシフト出力信号が出力される。このように構成すれば、第1シフト信号および第2シフト信号が第1電位のときに、論理合成回路部の第2トランジスタおよび第3トランジスタの2つのトランジスタを介して、第1電位の第1シフト信号と第1電位の第2シフト信号とを論理合成した第1電位のシフト出力信号を出力することができるとともに、第1シフト信号が第1電位から第2電位に変化する際に、論理合成回路部の第2トランジスタおよび第3トランジスタの2つのトランジスタを介して、第2電位の第1シフト信号と第1電位の第2シフト信号とを論理合成した第2電位のシフト出力信号を出力することができる。これにより、容易に、論理合成回路部から第1シフト信号と第2シフト信号とを論理合成したシフト出力信号を出力することができる。

10

20

30

40

【0027】

上記第4トランジスタおよび第5トランジスタを含む構成において、好ましくは、リセットトランジスタは、所定の駆動信号に応答して、第4トランジスタまたは第5トランジスタのソースの電位を第2電位にリセットする機能も有している。このように構成すれば、たとえば、第4トランジスタ（第5トランジスタ）がnチャネルトランジスタであるとともに、第4トランジスタ（第5トランジスタ）のドレインに正側電位VDD（第1電位）を供給して、第4トランジスタ（第5トランジスタ）のソースの電位を上昇させるのに先立って、第4トランジスタ（第5トランジスタ）のソースの電位を負側電位VBB（第2電位）にリセットすれば、第4トランジスタ（第5トランジスタ）のソースの電位が負側電位VBBから正側電位VDDに上昇する電位差の分、第4トランジスタ（第5トランジスタ）のゲート電位を上昇させることができ。これにより、第4トランジスタ（第5トランジスタ）のソースの電位を正側電位VDDと負側電位VBBとの間の不安定な電位から上昇させる場合に比べて、第4トランジスタ（第5トランジスタ）のゲート電位をより上昇させることができるので、より確実に第4トランジスタ（第5トランジスタ）のゲート電位をVDDよりも第4トランジスタ（第5トランジスタ）のしきい値電圧（Vt）以上の所定の電圧（V）分高い電位まで上昇させることができる。また、第4トランジスタ（第5トランジスタ）がpチャネルトランジスタであるとともに、第4トランジスタ（第5トランジスタ）のドレインに負側電位VBB（第1電位）を供給して、第4トランジスタ（第5トランジスタ）のソースの電位を正側電位VDD（第2電位）にリセットすれば、第4トランジスタ（第5トランジスタ）のソースの電位が正側電位VDDから負側電位VBBに低下する電位差の分、第4トランジスタ（第5トランジスタ）のゲート電位を低下させることができ。これにより、第4トランジスタ（第5トランジスタ）のソースの電位を正側電位VDDと負側電位VBBとの間の不安定な電位から低下させる場合に比べて、第4トランジスタ（第5トランジスタ）のゲート電位をより低下させることができるので、より確実に第4トランジスタ（第5トランジスタ）のゲート電位をVBBよりも第

50

4トランジスタ（第5トランジスタ）のしきい値電圧（ $V_t$ ）以上の所定の電圧（ $V$ ）分低い電位まで低下させることができる。

【0028】

上記一の局面による表示装置において、好ましくは、シフトレジスタ回路は、ゲート線を駆動するためのシフトレジスタ回路、および、ドレイン線を駆動するためのシフトレジスタ回路の少なくとも一方に適用されている。このように構成すれば、容易に、ゲート線およびドレイン線の少なくとも一方に意図しないタイミングで信号が出力されるのを抑制することができる。

【0029】

上記一の局面による表示装置において、好ましくは、第1シフトレジスタ回路部、第2シフトレジスタ回路部および論理合成回路部を構成するトランジスタと、リセットトランジスタとは、第1導電型を有する。このように構成すれば、第1シフトレジスタ回路部、第2シフトレジスタ回路部および論理合成回路部を構成するトランジスタと、リセットトランジスタとを第1導電型または第2導電型の2種類の導電型を有するトランジスタによって構成する場合に比べて、それらのトランジスタを形成する際のイオン注入工程の回数およびイオン注入マスクの枚数を低減することができる。これにより、製造プロセスが複雑化するのを抑制することができるとともに、製造コストが増大するのを抑制することができる。

【発明を実施するための最良の形態】

【0030】

以下、本発明の実施形態を図面に基づいて説明する。

【0031】

（第1実施形態）

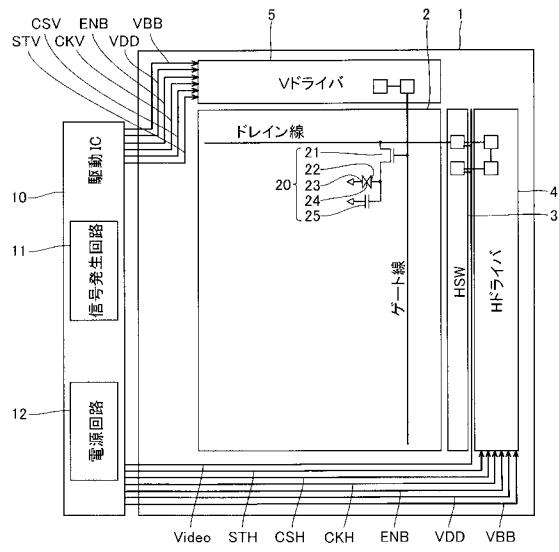

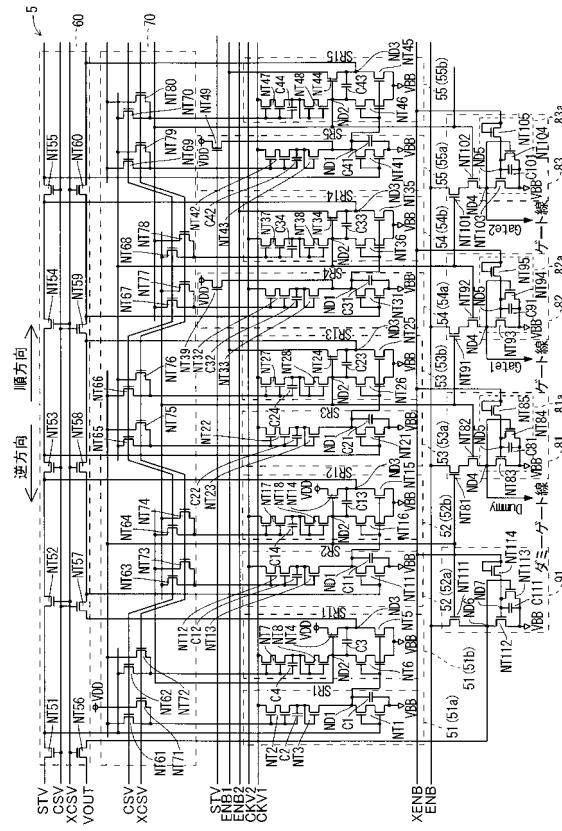

図1は、本発明の第1実施形態による液晶表示装置を示した平面図である。図2は、図1に示した第1実施形態による液晶表示装置のVドライバ内部の回路図である。

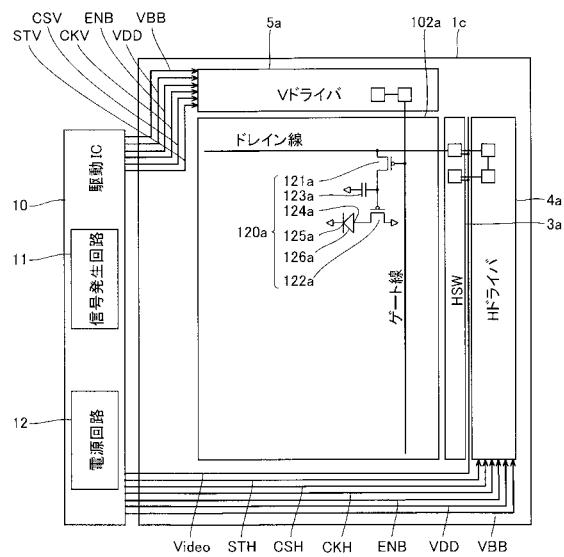

【0032】

まず、図1を参照して、この第1実施形態では、基板1上に、表示部2が設けられている。この表示部2には、画素20がマトリクス状に配置されている。なお、図1では、図面の簡略化のため、1つの画素20のみを図示している。各々の画素20は、nチャネルトランジスタ21（以下、トランジスタ21という）、画素電極22、画素電極22に対向配置された各画素20に共通の対向電極23、画素電極22と対向電極23との間に挟持された液晶24、および、補助容量25によって構成されている。そして、トランジスタ21のソースは、画素電極22および補助容量25に接続されているとともに、ドレインは、ドレイン線に接続されている。このトランジスタ21のゲートはゲート線に接続されている。

【0033】

また、表示部2の一辺に沿うように、基板1上に、表示部2のドレイン線を駆動（走査）するための水平スイッチ（H SW）3およびHドライバ4が設けられている。また、表示部2の他の辺に沿うように、基板1上に、表示部2のゲート線を駆動（走査）するためのVドライバ5が設けられている。なお、図1の水平スイッチ3には、2つのスイッチのみを図示しているが、実際は画素数に応じた数のスイッチが配置されている。また、図1のHドライバ4およびVドライバ5には、それぞれ、シフトレジスタ回路部を2つのみ図示しているが、実際は画素数に応じた数のシフトレジスタ回路部が配置されている。

【0034】

また、基板1の外部には、駆動IC10が設置されている。この駆動IC10は、信号発生回路11および電源回路12を備えている。駆動IC10からHドライバ4へは、ビデオ信号Video、スタート信号STH、走査方向切替信号CSH、クロック信号CKH、イネーブル信号ENB、正側電位VDDおよび負側電位VBBが供給される。また、駆動IC10からVドライバ5へは、スタート信号STV、イネーブル信号ENB、走査方向切替信号CSV、クロック信号CKV、正側電位VDDおよび負側電位VBBが供給

10

20

30

40

50

される。

【0035】

また、図2に示すように、第1実施形態では、Vドライバ5の内部に、複数段のシフトレジスタ回路部51～55と、走査方向切替回路部60と、入力信号切替回路部70と、複数段の論理合成回路部81～83と、回路部91とが設けられている。なお、図2では、図面の簡略化のため、5段分のシフトレジスタ回路部51～55および3段分の論理合成回路部81～83のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。

【0036】

そして、1段目のシフトレジスタ回路部51は、前段の第1回路部51aと、後段の第2回路部51bとによって構成されている。第1回路部51aは、nチャネルトランジスタNT1およびNT2と、ダイオード接続されたnチャネルトランジスタNT3と、容量C1およびC2とを含む。また、第2回路部51bは、nチャネルトランジスタNT4、NT5、NT6およびNT7と、ダイオード接続されたnチャネルトランジスタNT8と、容量C3およびC4とを含む。以下、nチャネルトランジスタNT1～NT8は、それぞれ、トランジスタNT1～NT8と称する。

【0037】

また、1段目のシフトレジスタ回路部51に設けられたトランジスタNT1～NT8は、すべてn型のMOSトランジスタ（電界効果型トランジスタ）からなるTFT（薄膜トランジスタ）により構成されている。また、トランジスタNT1、NT2、NT6、NT7およびNT8は、互いに電気的に接続された2つのゲート電極を有する。また、第1回路部51aにおいて、トランジスタNT1のソースは、負側電位VBBに接続されるとともに、ドレインは、第1回路部51aの出力ノードであるノードND1に接続されている。また、容量C1の一方の電極は、負側電位VBBに接続されるとともに、他方の電極は、ノードND1に接続されている。また、トランジスタNT2のソースは、トランジスタNT3を介してノードND1に接続されるとともに、ドレインは、クロック信号線（CKV1）に接続されている。また、容量C2は、トランジスタNT2のゲートとソースとの間に接続されている。

【0038】

また、第2回路部51bにおいて、トランジスタNT4のソースは、ノードND3に接続されるとともに、ドレインは、正側電位VDDに接続されている。このトランジスタNT4のゲートは、ノードND2に接続されている。また、トランジスタNT5のソースは、負側電位VBBに接続されるとともに、ドレインは、ノードND3に接続されている。このトランジスタNT5のゲートは、第1回路部51aのノードND1に接続されている。また、トランジスタNT6のソースは、負側電位VBBに接続されるとともに、ドレインは、ノードND2に接続されている。このトランジスタNT6のゲートは、第1回路部51aのノードND1に接続されている。また、トランジスタNT6は、トランジスタNT5がオン状態のときに、トランジスタNT4をオフ状態にするために設けられている。また、トランジスタNT7のソースは、トランジスタNT8を介してノードND2に接続されるとともに、ドレインは、クロック信号線（CKV1）に接続されている。また、容量C3は、トランジスタNT4のゲートとソースとの間に接続されている。また、容量C4は、トランジスタNT7のゲートとソースとの間に接続されている。

【0039】

また、2段目～5段目のシフトレジスタ回路部52～55は、上記した1段目のシフトレジスタ回路部51とほぼ同様の回路構成を有する。具体的には、2段目～5段目のシフトレジスタ回路部52～55は、それぞれ、1段目のシフトレジスタ回路部51の第1回路部51aとほぼ同様の回路構成を有する第1回路部52a～55aと、第2回路部51bとほぼ同様の回路構成を有する第2回路部52b～55bとによって構成されている。

【0040】

2段目のシフトレジスタ回路部52は、1段目のシフトレジスタ回路部51のトランジ

10

20

30

40

50

スタNT1～NT8に対応するnチャネルトランジスタNT11～NT18と、容量C1～C4に対応する容量C11～C14とを含む。なお、nチャネルトランジスタNT14は、本発明の「第3トランジスタ」および「第4トランジスタ」の一例であり、nチャネルトランジスタNT16は、本発明の「第5トランジスタ」の一例である。また、容量C13は、本発明の「第1容量」および「第2容量」の一例である。以下、nチャネルトランジスタNT11～NT18は、それぞれ、トランジスタNT11～NT18と称する。また、3段目のシフトレジスタ回路部53は、1段目のシフトレジスタ回路部51のトランジスタNT1～NT8に対応するnチャネルトランジスタNT21～NT28と、容量C1～C4に対応する容量C21～C24とを含む。なお、nチャネルトランジスタNT24は、本発明の「第3トランジスタ」および「第4トランジスタ」の一例であり、nチャネルトランジスタNT26は、本発明の「第5トランジスタ」の一例である。また、容量C23は、本発明の「第1容量」および「第2容量」の一例である。以下、nチャネルトランジスタNT21～NT28は、それぞれ、トランジスタNT21～NT28と称する。10

#### 【0041】

また、4段目のシフトレジスタ回路部54は、1段目のシフトレジスタ回路部51のトランジスタNT1～NT8に対応するnチャネルトランジスタNT31～NT38と、容量C1～C4に対応する容量C31～C34とを含む。なお、nチャネルトランジスタNT34は、本発明の「第3トランジスタ」および「第4トランジスタ」の一例であり、nチャネルトランジスタNT36は、本発明の「第5トランジスタ」の一例である。また、容量C33は、本発明の「第1容量」および「第2容量」の一例である。以下、nチャネルトランジスタNT31～NT38は、それぞれ、トランジスタNT31～NT38と称する。また、5段目のシフトレジスタ回路部55は、1段目のシフトレジスタ回路部51のトランジスタNT1～NT8に対応するnチャネルトランジスタNT41～NT48と、容量C1～C4に対応する容量C41～C44とを含む。なお、nチャネルトランジスタNT44は、本発明の「第3トランジスタ」および「第4トランジスタ」の一例であり、nチャネルトランジスタNT46は、本発明の「第5トランジスタ」の一例である。また、容量C43は、本発明の「第1容量」および「第2容量」の一例である。以下、nチャネルトランジスタNT41～NT48は、それぞれ、トランジスタNT41～NT48と称する。20

#### 【0042】

ここで、第1実施形態では、4段目のシフトレジスタ回路部54の第1回路部54aは、シフト信号SR4を出力するノードND2の電位を負側電位VBBにリセットするためのnチャネルトランジスタNT39を含んでいる。また、5段目のシフトレジスタ回路部55の第1回路部55aは、シフト信号SR5を出力するノードND2の電位を負側電位VBBにリセットするためのnチャネルトランジスタNT49を含んでいる。以下、nチャネルトランジスタNT39およびNT49は、それぞれ、リセットトランジスタNT39およびNT49と称する。30

#### 【0043】

また、リセットトランジスタNT39のドレインには、正側電位VDDが供給されるとともに、ソースは、4段目のシフトレジスタ回路部54の第1回路部54aの出力ノードであるノードND1に接続されている。また、リセットトランジスタNT39のゲートには、スタート信号STVを供給するためのスタート信号線(STV)が接続されている。なお、スタート信号STVは、本発明の「所定の駆動信号」の一例であり、スタート信号線(STV)は、本発明の「第1駆動信号線」の一例である。これにより、Hレベルのスタート信号STVに応答してリセットトランジスタNT39がオンすると、リセットトランジスタNT39を介して正側電位VDDが供給されることにより、第1回路部54aのノードND1の電位が正側電位VDD(Hレベル)になるように構成されている。そして、第1回路部54aのノードND1の電位が正側電位VDD(Hレベル)になると、第2回路部54bのトランジスタNT36がオンするので、トランジスタNT36を介して負40

側電位VBBが供給されることにより、シフト信号SR4を出力する第2回路部54bのノードND2が負側電位VBBにリセットされるように構成されている。

【0044】

また、リセットトランジスタNT49のドレインには、正側電位VDDが供給されるとともに、ソースは、5段目のシフトレジスタ回路部55の第1回路部55aの出力ノードであるノードND1に接続されている。また、リセットトランジスタNT49のゲートには、スタート信号STVを供給するためのスタート信号線(STV)が接続されている。これにより、5段目のシフトレジスタ回路部55では、上記した4段目のシフトレジスタ回路部54と同様にして、シフト信号SR5を出力する第2回路部55bのノードND2が負側電位VBBにリセットされるように構成されている。

10

【0045】

また、2段目のシフトレジスタ回路部52のトランジスタNT12およびNT17と、4段目のシフトレジスタ回路部54のトランジスタNT32およびNT37とは、クロック信号線(CKV2)に接続されている。また、3段目のシフトレジスタ回路部53のトランジスタNT22およびNT27と、5段目のシフトレジスタ回路部55のトランジスタNT42およびNT47とは、クロック信号線(CKV1)に接続されている。すなわち、クロック信号線(CKV1)とクロック信号線(CKV2)とが1段毎に交互に接続されている。

【0046】

また、第1実施形態では、3段目以降のシフトレジスタ回路部53～55に、イネーブル信号線(ENB1)とイネーブル信号線(ENB2)とが1つずつ交互に接続されている。なお、このイネーブル信号線(ENB1)および(ENB2)は、本発明の「第2信号線」および「第3信号線」の一例である。このイネーブル信号線(ENB1)を介して、所定のタイミングで電位がLレベルからHレベルに切り替わるイネーブル信号ENB1が供給されるとともに、イネーブル信号線(ENB2)を介して、イネーブル信号ENB2と異なるタイミングで電位がLレベルからHレベルに切り替わるイネーブル信号ENB2が供給されるように構成されている。そして、3段目のシフトレジスタ回路部53および5段目のシフトレジスタ回路部55では、それぞれ、トランジスタNT24およびNT44のドレインにイネーブル信号線(ENB1)が接続されている。また、4段目のシフトレジスタ回路部54では、トランジスタNT34のドレインに、イネーブル信号線(ENB2)が接続されている。

20

【0047】

また、走査方向切替回路部60は、nチャネルトランジスタNT51～NT60を含む。以下、nチャネルトランジスタNT51～NT60は、それぞれ、トランジスタNT51～NT60と称する。このトランジスタNT51～NT60は、すべてn型のMOSトランジスタからなるTFTにより構成されている。

30

【0048】

また、トランジスタNT51～NT55は、この順番でソース/ドレインの一方とソース/ドレインの他方とが互いに接続されている。また、トランジスタNT51、NT53およびNT55のゲートには、走査方向切替信号線(CSV)が接続されているとともに、トランジスタNT52およびNT54のゲートには、反転走査方向切替信号線(XCSV)が接続されている。すなわち、トランジスタNT51～NT55のゲートには、それぞれ、走査方向切替信号線(CSV)と反転走査方向切替信号線(XCSV)とが交互に接続されている。

40

【0049】

また、トランジスタNT56は、後述する回路部91のノードND6に接続されている。また、トランジスタNT57～NT60は、この順番でソース/ドレインの一方とソース/ドレインの他方とが互いに接続されている。トランジスタNT56、NT58およびNT60のゲートには、反転走査方向切替信号線(XCSV)が接続されているとともに、トランジスタNT57およびNT59のゲートには、走査方向切替信号線(CSV)が

50

接続されている。すなわち、トランジスタNT56～NT60のゲートには、それぞれ、反転走査方向切替信号線(XCSV)と走査方向切替信号線(CSV)とが交互に接続されている。

#### 【0050】

なお、走査方向が順方向の場合には、走査方向切替信号CSVがHレベル(VDD)になるように、かつ、反転走査方向切替信号XCSVがLレベル(VBB)になるように制御される。このため、走査方向が順方向の場合には、トランジスタNT51、NT53、NT55、NT57およびNT59がオン状態になるように、かつ、トランジスタNT52、NT54、NT56、NT58およびNT60がオフ状態になるように制御される。また、走査方向が逆方向の場合には、走査方向切替信号CSVがLレベル(VBB)になるように、かつ、反転走査方向切替信号XCSVがHレベル(VDD)になるように制御される。このため、走査方向が逆方向の場合には、トランジスタNT51、NT53、NT55、NT57およびNT59がオフ状態になるように、かつ、トランジスタNT52、NT54、NT56、NT58およびNT60がオン状態になるように制御される。

10

#### 【0051】

また、1段目のシフトレジスタ回路部51のトランジスタNT1のゲートが、走査方向切替回路部60のトランジスタNT51のソース/ドレインの他方(トランジスタNT52のソース/ドレインの一方)に接続されているとともに、1段目のシフトレジスタ回路部51のノードND3が、走査方向切替回路部60のトランジスタNT57のソース/ドレインの一方に接続されている。

20

#### 【0052】

また、2段目のシフトレジスタ回路部52のトランジスタNT11のゲートが、走査方向切替回路部60のトランジスタNT57のソース/ドレインの他方(トランジスタNT58のソース/ドレインの一方)に接続されているとともに、2段目のシフトレジスタ回路部52のノードND3が、走査方向切替回路部60のトランジスタNT52のソース/ドレインの他方(トランジスタNT53のソース/ドレインの一方)に接続されている。

#### 【0053】

また、3段目のシフトレジスタ回路部53のトランジスタNT21のゲートが、走査方向切替回路部60のトランジスタNT53のソース/ドレインの他方(トランジスタNT54のソース/ドレインの一方)に接続されているとともに、3段目のシフトレジスタ回路部53のノードND3が、走査方向切替回路部60のトランジスタNT58のソース/ドレインの他方(トランジスタNT59のソース/ドレインの一方)に接続されている。

30

#### 【0054】

また、4段目のシフトレジスタ回路部54のトランジスタNT31のゲートが、走査方向切替回路部60のトランジスタNT59のソース/ドレインの他方(トランジスタNT60のソース/ドレインの一方)に接続されているとともに、4段目のシフトレジスタ回路部54のノードND3が、走査方向切替回路部60のトランジスタNT54のソース/ドレインの他方(トランジスタNT55のソース/ドレインの一方)に接続されている。

#### 【0055】

また、5段目のシフトレジスタ回路部55のトランジスタNT41のゲートが、走査方向切替回路部60のトランジスタNT55のソース/ドレインの他方に接続されているとともに、5段目のシフトレジスタ回路部55のノードND3が、走査方向切替回路部60のトランジスタNT60のソース/ドレインの他方に接続されている。

40

#### 【0056】

各段のシフトレジスタ回路部51～55と走査方向切替回路部60とを上記のように接続することによって、走査方向に応じて、所定段のシフトレジスタ回路部の第1回路部に走査方向に対して前段の出力信号(SR11～SR15)が入力されるように制御される。ただし、走査方向が順方向の場合の先頭段のシフトレジスタ回路部51の第1回路部51aには、スタート信号STVが入力される。

#### 【0057】

50

また、入力信号切替回路部70は、ゲートが走査方向切替信号線(CSV)に接続されたnチャネルトランジスタNT61～NT70と、ゲートが反転走査方向切替信号線(XCSV)に接続されたnチャネルトランジスタNT71～NT80とを含む。以下、nチャネルトランジスタNT61～NT80は、それぞれ、トランジスタNT61～NT80と称する。また、入力信号切替回路部70を構成するトランジスタNT61～NT80は、すべてn型のMOSトランジスタからなる TFTにより構成されている。

#### 【0058】

また、走査方向切替信号線(CSV)に接続されたnチャネルトランジスタと、ゲートが反転走査方向切替信号線(XCSV)に接続されたnチャネルトランジスタとは、各段のシフトレジスタ回路部51～55に対して、それぞれ2つずつ配置されている。具体的には、1段目のシフトレジスタ回路部51に対応して、ゲートが走査方向切替信号線(CSV)に接続されたトランジスタNT61およびNT62と、ゲートが反転走査方向切替信号線(XCSV)に接続されたトランジスタNT71およびNT72とが配置されている。トランジスタNT61およびNT71のソース／ドレインの一方は、1段目のシフトレジスタ回路部51のトランジスタNT2のゲートに接続されている。トランジスタNT61のソース／ドレインの他方は、2段目のシフトレジスタ回路部52のノードND2に接続されているとともに、トランジスタNT71のソース／ドレインの他方は、正側電位VDDに接続されている。また、トランジスタNT62およびNT72のソース／ドレインの一方は、1段目のシフトレジスタ回路部51のトランジスタNT7のゲートに接続されている。トランジスタNT62のソース／ドレインの他方は、スタート信号STVが供給される走査方向切替回路部60のトランジスタNT51のソース／ドレインの他方(トランジスタNT52のソース／ドレインの一方)およびトランジスタNT1のゲートに接続されているとともに、トランジスタNT72のソース／ドレインの他方は、2段目のシフトレジスタ回路部52のノードND2に接続されている。

#### 【0059】

また、2段目のシフトレジスタ回路部52に対応して、ゲートが走査方向切替信号線(CSV)に接続されたトランジスタNT63およびNT64と、ゲートが反転走査方向切替信号線(XCSV)に接続されたトランジスタNT73およびNT74とが配置されている。トランジスタNT63およびNT73のソース／ドレインの一方は、2段目のシフトレジスタ回路部52のトランジスタNT12のゲートに接続されている。トランジスタNT63のソース／ドレインの他方は、3段目のシフトレジスタ回路部53のノードND2に接続されているとともに、トランジスタNT73のソース／ドレインの他方は、1段目のシフトレジスタ回路部51のノードND2に接続されている。また、トランジスタNT64およびNT74のソース／ドレインの一方は、2段目のシフトレジスタ回路部52のトランジスタNT17のゲートに接続されている。トランジスタNT64のソース／ドレインの他方は、1段目のシフトレジスタ回路部51のノードND2に接続されているとともに、トランジスタNT74のソース／ドレインの他方は、3段目のシフトレジスタ回路部53のノードND2に接続されている。

#### 【0060】

また、3段目のシフトレジスタ回路部53に対応して、ゲートが走査方向切替信号線(CSV)に接続されたトランジスタNT65およびNT66と、ゲートが反転走査方向切替信号線(XCSV)に接続されたトランジスタNT75およびNT76とが配置されている。トランジスタNT65およびNT75のソース／ドレインの一方は、3段目のシフトレジスタ回路部53のトランジスタNT22のゲートに接続されている。トランジスタNT65のソース／ドレインの他方は、4段目のシフトレジスタ回路部54のノードND2に接続されているとともに、トランジスタNT75のソース／ドレインの他方は、2段目のシフトレジスタ回路部52のノードND2に接続されている。また、トランジスタNT66およびNT76のソース／ドレインの一方は、3段目のシフトレジスタ回路部53のトランジスタNT27のゲートに接続されている。トランジスタNT66のソース／ドレインの他方は、2段目のシフトレジスタ回路部52のノードND2に接続されていると

10

20

30

40

50

ともに、トランジスタNT76のソース／ドレインの他方は、4段目のシフトレジスタ回路部54のノードND2に接続されている。

【0061】

また、4段目のシフトレジスタ回路部54に対応して、ゲートが走査方向切替信号線(CSV)に接続されたトランジスタNT67およびNT68と、ゲートが反転走査方向切替信号線(XCSV)に接続されたトランジスタNT77およびNT78とが配置されている。トランジスタNT67およびNT77のソース／ドレインの一方は、4段目のシフトレジスタ回路部54のトランジスタNT32のゲートに接続されている。トランジスタNT67のソース／ドレインの他方は、5段目のシフトレジスタ回路部55のノードND2に接続されているとともに、トランジスタNT77のソース／ドレインの他方は、3段目のシフトレジスタ回路部53のノードND2に接続されている。また、トランジスタNT68およびNT78のソース／ドレインの一方は、4段目のシフトレジスタ回路部54のトランジスタNT37のゲートに接続されている。トランジスタNT68のソース／ドレインの他方は、3段目のシフトレジスタ回路部53のノードND2に接続されているとともに、トランジスタNT78のソース／ドレインの他方は、5段目のシフトレジスタ回路部55のノードND2に接続されている。

【0062】

また、5段目のシフトレジスタ回路部55に対応して、ゲートが走査方向切替信号線(CSV)に接続されたトランジスタNT69およびNT70と、ゲートが反転走査方向切替信号線(XCSV)に接続されたトランジスタNT79およびNT80とが配置されている。トランジスタNT69およびNT79のソース／ドレインの一方は、5段目のシフトレジスタ回路部55のトランジスタNT42のゲートに接続されている。トランジスタNT69のソース／ドレインの他方は、図示しない6段目のシフトレジスタ回路部のノードND2に接続されているとともに、トランジスタNT79のソース／ドレインの他方は、4段目のシフトレジスタ回路部54のノードND2に接続されている。また、トランジスタNT70およびNT80のソース／ドレインの一方は、5段目のシフトレジスタ回路部55のトランジスタNT47のゲートに接続されている。トランジスタNT70のソース／ドレインの他方は、4段目のシフトレジスタ回路部54のノードND2に接続されているとともに、トランジスタNT80のソース／ドレインの他方は、図示しない6段目のシフトレジスタ回路部のノードND2に接続されている。

【0063】

入力信号切替回路部70を構成するトランジスタNT61～NT80を上記のように構成することによって、走査方向が順方向の場合には、トランジスタNT61～NT70がオン状態になるように、かつ、トランジスタNT71～NT80がオフ状態になるように制御される。また、各段のシフトレジスタ回路部51～55と入力信号切替回路部70とを上記のように接続することによって、走査方向に応じて、所定段のシフトレジスタ回路部の第1回路部に走査方向に対して次段のシフト信号(SR1～SR5)が入力されるように、かつ、所定段のシフトレジスタ回路部の第2回路部に走査方向に対して前段のシフト信号(SR1～SR5)が入力されるように制御される。ただし、初段のシフトレジスタ回路部51の第1回路部51aには、スタート信号STVが入力される。

【0064】

また、論理合成回路部81～83は、それぞれ、ダミーゲート線(Dummy)、1段目のゲート線(Gate1)および2段目のゲート線(Gate2)に接続されている。なお、ダミーゲート線(Dummy)は、表示部2に設けられた画素20(図1参照)に接続されないゲート線である。また、論理合成回路部81～83は、それぞれ、対応する所定段のシフトレジスタ回路部から出力されたシフト信号と、その所定段の次段のシフトレジスタ回路部から出力されたシフト信号とを論理合成して、各段のゲート線にシフト出力信号を出力するように構成されている。また、ダミーゲート線(Dummy)に接続される論理合成回路部81は、nチャネルトランジスタNT81～NT84と、ダイオード接続されたnチャネルトランジスタNT85と、容量C81とを含む。なお、nチャネル

10

20

30

40

50

トランジスタNT81は、本発明の「第1トランジスタ」の一例であり、nチャネルトランジスタNT82は、本発明の「第2トランジスタ」の一例である。以下、nチャネルトランジスタNT81～NT85は、それぞれ、トランジスタNT81～NT85と称する。

【0065】

また、トランジスタNT83～NT85と、容量C81とによって、電位固定回路部81aが構成されている。この電位固定回路部81aは、論理合成回路部81からLレベルのシフト出力信号がダミーゲート線(Dummy)に出力される際、そのシフト出力信号のLレベルの電位を固定するために設けられている。また、論理合成回路部81を構成するトランジスタNT81～NT85は、すべてn型のMOSトランジスタからなるTFTにより構成されている。また、トランジスタNT81のドレインは、イネーブル信号線(ENB)に接続されるとともに、ソースは、トランジスタNT82のドレインに接続されている。また、トランジスタNT82のソースは、ノードND4(ダミーゲート線)に接続されている。トランジスタNT81のゲートは、2段目のシフトレジスタ回路部52のシフト信号SR2が出力されるノードND2に接続されるとともに、トランジスタNT82のゲートは、3段目のシフトレジスタ回路部53のシフト信号SR3が出力されるノードND2に接続されている。

【0066】

また、トランジスタNT83のソースは、負側電位VBBに接続されるとともに、ドレインは、ノードND4(ダミーゲート線)に接続されている。このトランジスタNT83のゲートは、ノードND5に接続されている。また、トランジスタNT84のソースは、負側電位VBBに接続されるとともに、ドレインは、ノードND5に接続されている。このトランジスタNT84のゲートは、ノードND4(ダミーゲート線)に接続されている。また、容量C81の一方の電極は、負側電位VBBに接続されるとともに、他方の電極は、ノードND5に接続されている。また、ノードND5は、トランジスタNT85を介して、反転イネーブル信号線(XENB)に接続されている。

【0067】

また、1段目のゲート線(Gate1)に接続される論理合成回路部82は、ダミーゲート線(Dummy)に接続される論理合成回路部81と同様の回路構成を有する。具体的には、1段目のゲート線(Gate1)に接続される論理合成回路部82は、ダミーゲート線(Dummy)に接続される論理合成回路部81のトランジスタNT81～NT85と、容量C81とに対応するnチャネルトランジスタNT91～NT95と、容量C91とを含む。なお、nチャネルトランジスタNT91は、本発明の「第1トランジスタ」の一例であり、nチャネルトランジスタNT92は、本発明の「第2トランジスタ」の一例である。以下、nチャネルトランジスタNT91～NT95は、それぞれ、トランジスタNT91～NT95と称する。また、ダミーゲート線(Dummy)に接続される論理合成回路部81の電位固定回路部81aに対応する電位固定回路部82aが、トランジスタNT93～NT95と、容量C91とによって構成されている。

【0068】

なお、1段目のゲート線(Gate1)に接続される論理合成回路部82において、トランジスタNT91のゲートは、3段目のシフトレジスタ回路部53のシフト信号SR3が出力されるノードND2に接続されるとともに、トランジスタNT92のゲートは、4段目のシフトレジスタ回路部54のシフト信号SR4が出力されるノードND2に接続されている。また、ノードND5は、トランジスタNT95を介して、反転イネーブル信号線(XENB)に接続されている。

【0069】

また、2段目のゲート線(Gate2)に接続される論理合成回路部83は、ダミーゲート線(Dummy)に接続される論理合成回路部81と同様の回路構成を有する。具体的には、2段目のゲート線(Gate2)に接続される論理合成回路部83は、ダミーゲート線(Dummy)に接続される論理合成回路部81のトランジスタNT81～NT85と、容量C81とによって構成されている。

10

20

30

40

50

5と、容量C81とに対応するnチャネルトランジスタNT101～NT105と、容量C101とを含む。なお、nチャネルトランジスタNT101は、本発明の「第1トランジスタ」の一例であり、nチャネルトランジスタNT102は、本発明の「第2トランジスタ」の一例である。以下、nチャネルトランジスタNT101～NT105は、それぞれ、トランジスタNT101～NT105と称する。また、ダミーゲート線(Dummy)に接続される論理合成回路部81の電位固定回路部81aに対応する電位固定回路部83aが、トランジスタNT103～NT105と、容量C101とによって構成されている。

#### 【0070】

なお、2段目のゲート線(Gate2)に接続される論理合成回路部83において、トランジスタNT101のゲートは、4段目のシフトレジスタ回路部54のシフト信号SR4が出力されるノードND2に接続されるとともに、トランジスタNT102のゲートは、5段目のシフトレジスタ回路部55のシフト信号SR5が出力されるノードND2に接続されている。また、ノードND5は、トランジスタNT105を介して、反転イネーブル信号線(XENB)に接続されている。

#### 【0071】

また、回路部91は、nチャネルトランジスタNT111～NT113と、ダイオード接続されたnチャネルトランジスタNT114と、容量C111とを含む。以下、nチャネルトランジスタNT111～NT114は、それぞれ、トランジスタNT111～NT114と称する。また、回路部91を構成するトランジスタNT111～NT114は、すべてn型のMOSトランジスタからなるTFTにより構成されている。

#### 【0072】

そして、トランジスタNT111のドレインは、イネーブル信号線(XENB)に接続されるとともに、ソースは、ノードND6に接続されている。このトランジスタNT111のゲートは、2段目のシフトレジスタ回路部52のノードND2に接続されている。トランジスタNT112のソースは、負側電位VBBに接続されるとともに、ドレインは、ノードND6に接続されている。このトランジスタNT112のゲートは、ノードND7に接続されている。トランジスタNT113のソースは、負側電位VBBに接続されるとともに、ドレインは、ノードND7に接続されている。このトランジスタNT113のゲートは、ノードND6に接続されている。容量C111の一方の電極は、負側電位VBBに接続されるとともに、他方の電極は、ノードND7に接続されている。また、ノードND6は、走査方向切替回路部60のトランジスタNT56のソース/ドレインの他方に接続されている。また、ノードND7は、トランジスタNT114を介して、反転イネーブル信号線(XENB)に接続されている。

#### 【0073】

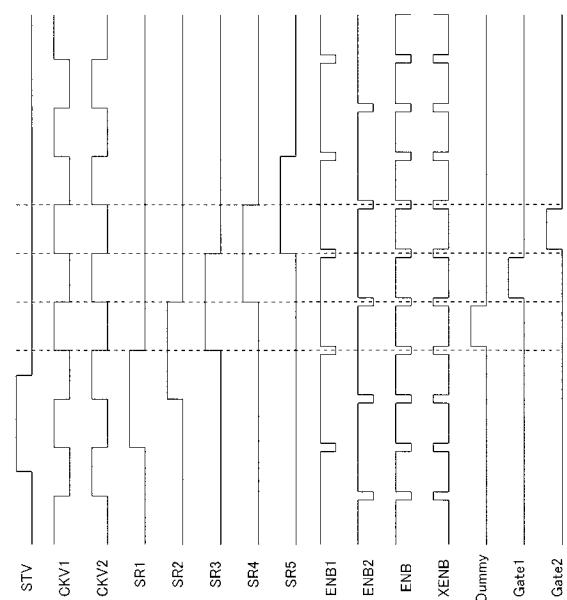

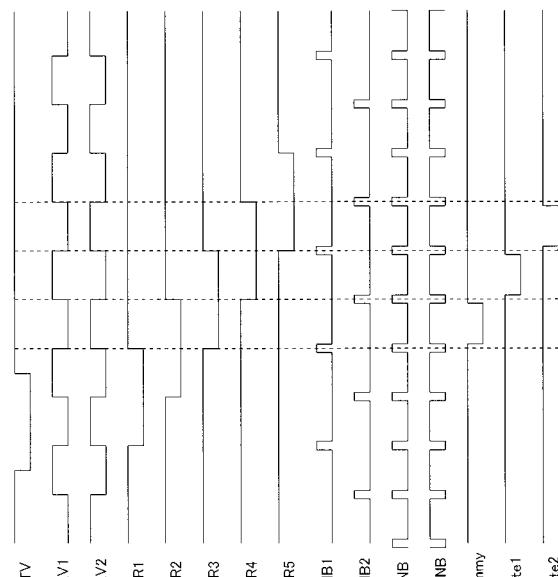

図3は、本発明の第1実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図1～図3を参照して、第1実施形態による液晶表示装置のVドライバの動作について説明する。

#### 【0074】

まず、図2中の順方向に沿って、各段のゲート線にタイミングのシフトしたシフト出力信号が順次出力される場合(順方向走査の場合)について説明する。まず、電源を投入することにより、Vドライバ5の各段のシフトレジスタ回路部に正側電位VDDおよび負側電位VBBを供給する。そして、順方向走査の場合には、走査方向切替信号CSVがHレベルに保持されるとともに、反転走査方向切替信号XCSVがLレベルに保持される。これにより、順方向走査時には、走査方向切替信号CSVがゲートに入力されるトランジスタNT51、NT53、NT55、NT57、NT59およびNT61～70がオン状態に保持される。また、反転走査方向切替信号XCSVがゲートに入力されるトランジスタNT52、NT54、NT56、NT58、NT60およびNT71～80がオフ状態に保持される。そして、初期状態では、各段のシフトレジスタ回路部51～55のノードND1～ND3の電位は、正側電位VDDと負側電位VBBとの間の不安定な電位となって

10

20

30

40

50

いる。これにより、初期状態では、各段のシフトレジスタ回路部 5 1 ~ 5 5 から出力されるシフト信号 S R 1 ~ S R 5 と、出力信号 S R 1 1 ~ S R 1 5 とは、正側電位 V D D と負側電位 V B B との間の不安定な電位となっている。この状態で、図 3 に示すように、スタート信号 S T V を H レベルに上昇させる。

【 0 0 7 5 】

これにより、第 1 実施形態では、H レベルのスタート信号 S T V が 4 段目のシフトレジスタ回路部 5 4 の第 1 回路部 5 4 a のリセットトランジスタ N T 3 9 のゲートに入力される。このため、リセットトランジスタ N T 3 9 がオンするので、リセットトランジスタ N T 3 9 を介して正側電位 V D D が 4 段目のシフトレジスタ回路部 5 4 の第 1 回路部 5 4 a のノード N D 1 に供給される。これにより、初期状態では正側電位 V D D と負側電位 V B B との間の不安定な電位であった第 1 回路部 5 4 a のノード N D 1 の電位が正側電位 V D D ( H レベル ) にリセットされる。このため、第 1 回路部 5 4 a のノード N D 1 に繋がる第 2 回路部 5 4 b のトランジスタ N T 3 6 および N T 3 5 のゲートにそれぞれ正側電位 V D D ( H レベル ) が印加される。これにより、トランジスタ N T 3 6 および N T 3 5 がオンするので、トランジスタ N T 3 6 および N T 3 5 を介して、4 段目のシフトレジスタ回路部 5 4 のノード N D 2 および N D 3 にそれぞれ負側電位 V B B が供給される。

【 0 0 7 6 】

このため、初期状態では正側電位 V D D と負側電位 V B B との間の不安定な電位であった 4 段目のシフトレジスタ回路部 5 4 のノード N D 2 および N D 3 の電位は、スタート信号 S T V が H レベルの期間において、負側電位 V B B にリセットされる。これにより、4 段目のシフトレジスタ回路部 5 4 のノード N D 2 および N D 3 からそれぞれ出力されるシフト信号 S R 4 および出力信号 S R 1 4 は、共に、負側電位 V B B ( L レベル ) にリセットされる。

【 0 0 7 7 】

そして、L レベルのシフト信号 S R 4 は、論理合成回路部 8 2 のトランジスタ N T 9 2 のゲート、および、論理合成回路部 8 3 のトランジスタ N T 1 0 1 のゲートに入力されるので、これらのトランジスタ N T 9 2 および N T 1 0 1 はオフ状態に固定される。また、L レベルのシフト信号 S R 4 は、入力信号切替回路部 7 0 のオン状態のトランジスタ N T 6 5 を介して、3 段目のシフトレジスタ回路部 5 3 のトランジスタ N T 2 2 のゲートに入力される。これにより、3 段目のシフトレジスタ回路部 5 3 のトランジスタ N T 2 2 は、オフ状態に固定される。また、L レベルのシフト信号 S R 4 は、入力信号切替回路部 7 0 のオン状態のトランジスタ N T 7 0 を介して、5 段目のシフトレジスタ回路部 5 5 のトランジスタ N T 4 7 のゲートに入力される。これにより、5 段目のシフトレジスタ回路部 5 5 のトランジスタ N T 4 7 は、オフ状態に固定される。

【 0 0 7 8 】

また、4 段目のシフトレジスタ回路部 5 4 のノード N D 3 から出力される L レベルの出力信号 S R 1 4 は、走査方向切替回路部 6 0 のオン状態のトランジスタ N T 5 5 を介して、5 段目のシフトレジスタ回路部 5 5 のトランジスタ N T 4 1 のゲートに入力される。これにより、5 段目のシフトレジスタ回路部 5 5 のトランジスタ N T 4 1 は、オフ状態に固定される。

【 0 0 7 9 】

また、5 段目のシフトレジスタ回路部 5 5 では、H レベルのスタート信号 S T V が第 1 回路部 5 5 a のリセットトランジスタ N T 4 9 のゲートに入力されることにより、上記した 4 段目のシフトレジスタ回路部 5 4 と同様にして、ノード N D 1 の電位が正側電位 V D D ( H レベル ) にリセットされるとともに、ノード N D 2 および N D 3 の電位が負側電位 V B B ( L レベル ) にリセットされる。これに伴って、5 段目のシフトレジスタ回路部 5 5 のノード N D 2 および N D 3 からそれぞれ出力されるシフト信号 S R 5 および出力信号 S R 1 5 も負側電位 V B B ( L レベル ) にリセットされる。そして、この L レベルのシフト信号 S R 5 は、論理合成回路部 8 3 のトランジスタ N T 1 0 2 のゲートと、論理合成回路部 8 3 のトランジスタ N T 1 0 1 に対応する論理合成回路部 8 3 の次段の論理合成回路

10

20

30

40

50

部の n チャネルトランジスタのゲートとに入力される。これにより、これらのトランジスタがオフ状態に固定される。また、 L レベルのシフト信号 S R 5 は、入力信号切替回路部 7 0 のオン状態のトランジスタ N T 6 7 を介して、 4 段目のシフトレジスタ回路部 5 4 のトランジスタ N T 3 2 のゲートに入力される。これにより、トランジスタ N T 3 2 は、オフ状態に固定される。

#### 【 0 0 8 0 】

上記のようにして、スタート信号 S T V が H レベルになる期間には、 4 段目以降の全てのシフトレジスタ回路部において、ノード N D 1 の電位と、ノード N D 2 および N D 3 の電位とがそれぞれ正側電位 V D D と負側電位 V B B とに一括してリセットされる。そして、これに伴って、 4 段目以降のシフトレジスタ回路部からそれぞれ出力されるシフト信号および出力信号が負側電位 V B B ( L レベル ) にリセットされる。これにより、その L レベルのシフト信号または出力信号がゲートに入力される各段のシフトレジスタ回路部のトランジスタと各段の論理合成回路部の論理合成を行うトランジスタとが、オフ状態に固定される。

10

#### 【 0 0 8 1 】

また、 H レベルのスタート信号 S T V は、走査方向切替回路部 6 0 のオン状態のトランジスタ N T 5 1 を介して 1 段目のシフトレジスタ回路部 5 1 のトランジスタ N T 1 のゲートに入力される。このため、トランジスタ N T 1 がオン状態になる。この後、トランジスタ N T 2 のドレインに入力されるクロック信号 C K V 1 が H レベルに上昇する。

20

#### 【 0 0 8 2 】

この際、 1 段目のシフトレジスタ回路部 5 1 のトランジスタ N T 2 のゲートに、 2 段目のシフトレジスタ回路部 5 2 から出力されるシフト信号 S R 2 がオン状態のトランジスタ N T 6 1 を介して入力されている。なお、このときのトランジスタ N T 2 のゲートに入力されるシフト信号 S R 2 は、正側電位 V D D と負側電位 V B B との間の不安定な電位ではあるが、トランジスタ N T 2 をオフさせることが可能な電位になっている。これにより、トランジスタ N T 2 は、オフ状態になっている。

#### 【 0 0 8 3 】

また、 1 段目のシフトレジスタ回路部 5 1 のトランジスタ N T 1 がオン状態でトランジスタ N T 2 がオフ状態であるので、トランジスタ N T 1 を介して負側電位 V B B から L レベルの電位が供給されることによりノード N D 1 の電位が L レベルに低下する。これにより、 1 段目のシフトレジスタ回路部 5 1 のノード N D 1 にゲートが接続されるトランジスタ N T 5 および N T 6 がオフ状態になる。また、 H レベルのスタート信号 S T V は、オン状態のトランジスタ N T 5 1 および N T 6 2 を介して、 1 段目のシフトレジスタ回路部 5 1 のトランジスタ N T 7 のゲートにも入力される。これにより、トランジスタ N T 7 はオン状態になっている。そして、トランジスタ N T 7 のドレインに入力されるクロック信号 C K V 1 の電位が H レベルに上昇する。

30

#### 【 0 0 8 4 】

この際、トランジスタ N T 7 がオン状態であっても、トランジスタ N T 6 がオフ状態であるので、トランジスタ N T 7 、 N T 8 および N T 6 を介してクロック信号線 ( C K V 1 ) と、負側電位 V B B との間で貫通電流が流れることはない。また、 H レベルのクロック信号 C K V 1 がトランジスタ N T 7 と、ダイオード接続されたトランジスタ N T 8 とを介して入力されることにより、 1 段目のシフトレジスタ回路部 5 1 のノード N D 2 の電位が H レベルに上昇する。これにより、トランジスタ N T 4 がオン状態になる。そして、正側電位 V D D からトランジスタ N T 4 を介してノード N D 3 に H レベル ( V D D ) の電位が供給される。

40

#### 【 0 0 8 5 】

この際、トランジスタ N T 4 がオン状態であっても、トランジスタ N T 5 がオフ状態であるので、トランジスタ N T 4 および N T 5 を介して、正側電位 V D D と負側電位 V B B との間で貫通電流が流れることはない。そして、正側電位 V D D からトランジスタ N T 4 を介してノード N D 3 に H レベル ( V D D ) の電位が供給されることにより、 1 段目のシ

50

フレジスタ回路部51のノードND3の電位は、VDD側に上昇する。この際、1段目のシフトレジスタ回路部51のノードND2の電位は、容量C3によってトランジスタNT4のゲート-ソース間電圧が維持されるように、ノードND3の電位の上昇に伴ってブートされることにより上昇する。これにより、ノードND2の電位がVDDよりもトランジスタNT4のしきい値電圧(Vt)以上の所定の電圧(V)分高い電位まで上昇する。その結果、1段目のシフトレジスタ回路部51のノードND2からVDD+Vt以上の電位(VDD+V)を有するHレベルのシフト信号SR1が出力される。また、同時に、1段目のシフトレジスタ回路部のノードND3からHレベル(VDD)の出力信号SR11が出力される。

【0086】

10

そして、1段目のシフトレジスタ回路部51のHレベル(VDD)の出力信号SR11は、オン状態のトランジスタNT57を介して2段目のシフトレジスタ回路部52のトランジスタNT11のゲートに入力される。これにより、トランジスタNT11は、オン状態になる。そして、1段目のシフトレジスタ回路部51のHレベル(VDD+V)のシフト信号SR1は、オン状態のトランジスタNT64のドレインに入力される。この際、トランジスタNT64のゲート電圧は走査方向切替信号CSVの電位(VDD)に等しいので、トランジスタNT64のソースに接続されるトランジスタNT17のゲート電圧は(VDD-Vt)に充電される。これにより、トランジスタNT17は、オン状態になる。

【0087】

20

また、2段目のシフトレジスタ回路部52のトランジスタNT12のゲートには、3段目のシフトレジスタ回路部53のノードND2から出力されるシフト信号SR3がオン状態のトランジスタNT63を介して入力されている。なお、このときのトランジスタNT12のゲートに入力されるシフト信号SR3は、正側電位VDDと負側電位VBBとの間の不安定な電位ではあるが、トランジスタNT12をオフさせることが可能な電位になっている。これにより、トランジスタNT12は、オフ状態になっている。

【0088】

この後、2段目のシフトレジスタ回路部52のトランジスタNT17のドレインに入力されるクロック信号CKV2の電位がLレベル(VBB)からHレベル(VDD)に上昇する。これにより、トランジスタNT17では、容量C14の機能によりゲート-ソース間電圧が保持されながら、ゲート電位がVDD-VtからVDDとVBBとの電位差分上昇する。このため、2段目のシフトレジスタ回路部52のノードND2の電位は、トランジスタNT17のしきい値電圧(Vt)分低下することなく、Hレベル(VDD)の電位に上昇する。この後、上記した1段目のシフトレジスタ回路部51の動作と同様にして、2段目のシフトレジスタ回路部52のノードND2からVDD+Vt以上の電位(VDD+V)を有するHレベルのシフト信号SR2が出力される。また、同時に、2段目のシフトレジスタ回路部52のノードND3からHレベル(VDD)の出力信号SR12が出力される。

【0089】

30

そして、2段目のシフトレジスタ回路部52のHレベル(VDD+V > VDD+Vt)のシフト信号SR2は、ダミーゲート線に繋がる論理合成回路部81のトランジスタNT81のゲートに入力される。また、Hレベル(VDD+V > VDD+Vt)のシフト信号SR2は、ゲートにVDDの走査方向切替信号CSVが入力されることによりオンしているトランジスタNT61およびNT66のドレインに入力される。これにより、トランジスタNT61およびNT66のソース電位は、(VDD-Vt)になるので、1段目のシフトレジスタ回路部51のトランジスタNT2のゲートと、3段目のシフトレジスタ回路部53のトランジスタNT27のゲートとには、(VDD-Vt)の電位が入力される。また、Hレベル(VDD)の出力信号SR12は、オン状態のトランジスタNT53を介して3段目のシフトレジスタ回路部53のトランジスタNT21のゲートに入力される。

40

50

## 【0090】

そして、ダミーゲート線に繋がる論理合成回路部81のトランジスタNT81は、Hレベル( $V_{DD} + V_{t}$ )のシフト信号SR2がゲートに入力されることにより、オン状態になる。この際、トランジスタNT83は、オン状態に保持されているので、トランジスタNT83を介してノードND4に負側電位VBBが供給される。また、この際、トランジスタNT82のゲートには、3段目のシフトレジスタ回路部53のノードND2から正側電位VDDと負側電位VBBとの間の不安定な電位のシフト信号SR3が入力されている。これにより、トランジスタNT82は、意図しないオン状態になる場合がある。

## 【0091】

トランジスタNT82が意図しないオン状態になる場合には、トランジスタNT81およびNT82を介して供給されるイネーブル信号ENBにより、ノードND4の電位がVBBよりも高い電位に上昇する。これにより、論理合成回路部81のノードND4から、意図しないタイミングでVBBよりも高い電位のシフト出力信号Dummymがダミーゲート線に出力される場合がある。なお、このように意図しないタイミングでVBBよりも高い電位のシフト出力信号Dummymがダミーゲート線に出力されたとしても、ダミーゲート線は画素20(図1参照)に接続されていないので、映像の表示に影響を及ぼすことはない。

## 【0092】

また、( $V_{DD} - V_t$ )の電位がトランジスタNT61からゲートに入力されることにより、1段目のシフトレジスタ回路部51のトランジスタNT2は、オン状態になる。そして、トランジスタNT2およびNT7のドレインに入力されるクロック信号CKV1の電位はLレベルに低下する。この際、1段目のシフトレジスタ回路部51のノードND1の電位は、Lレベルに保持される。これにより、1段目のシフトレジスタ回路部51のトランジスタNT5およびNT6は、オフ状態に保持される。

## 【0093】

また、クロック信号CKV1がLレベルに低下することにより、トランジスタNT8のゲート電圧はLレベルに低下するので、トランジスタNT8はオフ状態になる。これにより、1段目のシフトレジスタ回路部51のノードND2の電位は、Hレベル( $V_{DD} + V_t$ )に保持されるので、1段目のシフトレジスタ回路部51からHレベル( $V_{DD} + V_t$ )のシフト信号SR1が続けて出力される。また、1段目のシフトレジスタ回路部51のノードND2の電位がHレベル( $V_{DD} + V_t$ )に保持されることにより、トランジスタNT4はオン状態に保持されるので、1段目のシフトレジスタ回路部51のノードND3からHレベル( $V_{DD}$ )の出力信号SR11が続けて出力される。

## 【0094】

また、( $V_{DD} - V_t$ )の電位がトランジスタNT66からゲートに入力されることにより、3段目のシフトレジスタ回路部53のトランジスタNT27は、オン状態になる。また、トランジスタNT21は、ゲートにHレベル( $V_{DD}$ )の出力信号SR12が入力されることによりオン状態になる。このとき、3段目のシフトレジスタ回路部53のトランジスタNT22は、オフ状態に固定されている。そして、トランジスタNT21がオンすることによりトランジスタNT21を介して負側電位VBBが供給されることによって、3段目のシフトレジスタ回路部53のノードND1の電位は、負側電位VBB(Lレベル)に固定される。これにより、トランジスタNT25およびNT26はオフ状態になる。

## 【0095】

このとき、クロック信号線(CKV1)からオン状態のトランジスタNT27を介してトランジスタNT28のゲートに供給されるクロック信号CKV1がHレベル( $V_{DD}$ )からLレベル(VBB)に低下するので、トランジスタNT28はオフ状態になる。これにより、3段目のシフトレジスタ回路部53のノードND2の電位は、正側電位VDDと負側電位VBBとの間の不安定な電位に保持される。このため、3段目のシフトレジスタ回路部53のノードND2から正側電位VDDと負側電位VBBとの間の不安定な電位の

10

20

30

40

50

シフト信号 S R 3 が続けて出力される。また、このとき、3段目のシフトレジスタ回路部 5 3 のノード N D 3 の電位も正側電位 V D D と負側電位 V B B との間の不安定な電位に保持されることにより、3段目のシフトレジスタ回路部 5 3 のノード N D 3 から正側電位 V D D と負側電位 V B B との間の不安定な電位の出力信号 S R 1 3 が続けて出力される。

【 0 0 9 6 】

そして、スタート信号 S T V の電位が L レベルに低下する。これにより、1段目のシフトレジスタ回路部 5 1 のトランジスタ N T 1 がオフ状態になる。このため、1段目のシフトレジスタ回路部 5 1 のノード N D 1 の電位は、L レベルに保持されるので、トランジスタ N T 5 および N T 6 は、オフ状態に保持される。また、スタート信号 S T V の電位が L レベルに低下することにより、スタート信号 S T V がトランジスタ N T 5 1 および N T 6 2 を介してゲートに入力されるトランジスタ N T 7 もオフ状態になる。これにより、1段目のシフトレジスタ回路部 5 1 のノード N D 2 の電位は、H レベル ( V D D + V ) に保持されるとともに、ノード N D 3 の電位は、H レベル ( V D D ) に保持される。このため、1段目のシフトレジスタ回路部 5 1 から、H レベル ( V D D + V ) のシフト信号 S R 1 と、H レベル ( V D D ) の出力信号 S R 1 1 とが続けて出力される。

【 0 0 9 7 】

また、L レベルに低下したスタート信号 S T V は、4段目のシフトレジスタ回路部 5 4 のリセットトランジスタ N T 3 9 、5段目のシフトレジスタ回路部 5 5 のリセットトランジスタ N T 4 9 、および、図示しない6段目以降のシフトレジスタ回路部の上記のリセットトランジスタ N T 3 9 および N T 4 9 に対応する n チャネルトランジスタのゲートにも入力されるので、これらのトランジスタはオフする。これにより、4段目以降のシフトレジスタ回路部において、ノード N D 1 は、H レベルの電位を保持しながらフローティング状態になるとともに、ノード N D 2 および N D 3 の電位は L レベルに保持される。このため、4段目以降のシフトレジスタ回路部のノード N D 2 から出力されるシフト信号とノード N D 3 から出力される出力信号とは、共に、L レベルに保持される。

【 0 0 9 8 】

この後、3段目のシフトレジスタ回路部 5 3 のトランジスタ N T 2 7 のドレインに入力されるクロック信号 C K V 1 が H レベルに上昇する。これにより、3段目のシフトレジスタ回路部 5 3 のノード N D 2 の電位は H レベル ( V D D ) に上昇するので、シフト信号 S R 3 の電位は H レベルに上昇する。また、3段目のシフトレジスタ回路部 5 3 のノード N D 2 にゲートが接続されたトランジスタ N T 2 4 はオン状態になる。このとき、トランジスタ N T 2 4 のドレインに L レベルのイネーブル信号 E N B 1 が供給されているので、トランジスタ N T 2 4 のソース電位 ( ノード N D 3 の電位 ) は L レベルに保持される。

【 0 0 9 9 】

この後、第1実施形態では、イネーブル信号 E N B 1 の電位が L レベルから H レベルに上昇する。これにより、3段目のシフトレジスタ回路部 5 3 のノード N D 3 の電位が H レベル ( V D D ) に上昇するので、出力信号 S R 1 3 の電位も H レベル ( V D D ) に上昇する。なお、この際、3段目のシフトレジスタ回路部 5 3 のノード N D 2 の電位は、容量 C 2 3 によりトランジスタ N T 2 4 のゲート - ソース間電圧が維持されるようにノード N D 3 の電位の上昇に伴ってブートされることによって、V D D からさらに上昇する。これにより、3段目のシフトレジスタ回路部 5 3 のノード N D 2 の電位は、V D D よりもしきい値電圧 ( V t ) 以上の所定の電圧 ( V ) 分高い電位 ( V D D + V > V D D + V t ) まで上昇する。なお、このときのノード N D 2 の電位 ( V D D + V ) は、上記した1段目のシフトレジスタ回路部 5 1 および 2段目のシフトレジスタ回路部 5 2 において、上昇した後のノード N D 2 の電位 ( V D D + V ) よりもさらに高い電位となる。そして、3段目のシフトレジスタ回路部 5 3 のノード N D 2 から V D D + V t 以上の電位 ( V D D + V ) を有する H レベルのシフト信号 S R 3 が出力される。

【 0 1 0 0 】

そして、H レベル ( V D D + V > V D D + V t ) のシフト信号 S R 3 は、ダミーゲート線に繋がる論理合成回路部 8 1 のトランジスタ N T 8 2 のゲートと、1段目のゲート線

10

20

30

40

50

に繋がる論理合成回路部 8 2 のトランジスタ N T 9 1 のゲートとに入力される。また、H レベル (  $V_{DD} + V_t > V_{DD} + V_t$  ) のシフト信号 S R 3 は、オン状態のトランジスタ N T 6 3 のドレインに入力されるとともに、オン状態のトランジスタ N T 6 8 のドレインに入力される。また、H レベル (  $V_{DD}$  ) の出力信号 S R 13 は、オン状態のトランジスタ N T 5 9 を介して 4 段目のシフトレジスタ回路部 5 4 のトランジスタ N T 3 1 のゲートに入力される。

#### 【 0 1 0 1 】

この際、第 1 実施形態では、ダミーゲート線に繋がる論理合成回路部 8 1 において、トランジスタ N T 8 1 および N T 8 2 のゲートにそれぞれ入力されるシフト信号 S R 2 とシフト信号 S R 3 とが両方とも H レベルになるので、トランジスタ N T 8 1 およびトランジスタ N T 8 2 が両方ともオン状態になる。これにより、イネーブル信号線 ( E N B ) からトランジスタ N T 8 1 および N T 8 2 を介してノード N D 4 にイネーブル信号 E N B が供給される。このイネーブル信号 E N B は、シフト信号 S R 1 および S R 2 が両方とも H レベルになった時点では、L レベルであり、その後わずかな期間後に L レベルから H レベルに電位が切り替わる。これにより、ダミーゲート線に繋がる論理合成回路部 8 1 のノード N D 4 の電位が L レベルから H レベルに上昇するので、論理合成回路部 8 1 からダミーゲート線に H レベルのシフト出力信号 D u m m y が outputされる。すなわち、イネーブル信号 E N B が L レベルの間は、シフト出力信号 D u m m y の電位は、強制的に L レベルに保持されるとともに、イネーブル信号 E N B の電位が L レベルから H レベルに上昇するのに伴って、H レベルに上昇される。

10

#### 【 0 1 0 2 】

なお、この際、ダミーゲート線に繋がる論理合成回路部 8 1 のノード N D 4 の電位 ( シフト出力信号 D u m m y の電位 ) が H レベルに上昇するのに伴って、ノード N D 4 にゲートが接続されたトランジスタ N T 8 4 がオン状態になる。これにより、トランジスタ N T 8 4 を介して負側電位 V B B から L レベルの電位がトランジスタ N T 8 3 のゲートに供給されるので、トランジスタ N T 8 3 は、オフ状態になる。このため、トランジスタ N T 8 1 および N T 8 2 が両方ともオン状態になった場合にも、トランジスタ N T 8 3 がオフ状態になるので、トランジスタ N T 8 1 、 N T 8 2 および N T 8 3 を介して、イネーブル信号線 ( E N B ) と負側電位 V B B との間で貫通電流が流れるのが抑制される。

20

#### 【 0 1 0 3 】

また、第 1 実施形態では、トランジスタ N T 8 1 および N T 8 2 のゲートに、  $V_{DD}$  よりもしきい値電圧 (  $V_t$  ) 以上の所定の電圧 (  $V$  または  $V_{DD}$  ) 分高い電位 (  $V_{DD} + V_t$  ) の H レベルのシフト信号 S R 2 および S R 3 がそれぞれ入力される。これにより、トランジスタ N T 8 1 のドレインに  $V_{DD}$  の電位を有する H レベルのイネーブル信号 E N B が供給された場合に、ダミーゲート線に繋がる論理合成回路部 8 1 のノード N D 4 に現れる電位が、  $V_{DD}$  からトランジスタ N T 8 1 および N T 8 2 のしきい値電圧 (  $V_t$  ) 分低下するのが抑制される。このため、論理合成回路部 8 1 からダミーゲート線に出力されるシフト出力信号 D u m m y の電位が H レベルから低下するのが抑制される。

30

#### 【 0 1 0 4 】

また、1 段目のゲート線に繋がる論理合成回路部 8 2 では、トランジスタ N T 9 1 のゲートに 3 段目のシフトレジスタ回路部 5 3 の H レベル (  $V_{DD} + V_t$  ) のシフト信号 S R 3 が入力されることにより、トランジスタ N T 9 1 はオンする。このとき、トランジスタ N T 9 2 がオフ状態に固定されているので、イネーブル信号線 ( E N B ) からトランジスタ N T 9 1 および N T 9 2 を介してノード N D 4 にイネーブル信号 E N B は供給されない。

40

#### 【 0 1 0 5 】

なお、この時点より前の反転イネーブル信号 X E N B が H レベルの期間において、反転イネーブル信号線 ( X E N B ) にゲートが接続されたトランジスタ N T 9 5 がオンする。これにより、トランジスタ N T 9 5 を介して論理合成回路部 8 2 のノード N D 5 に H レベル

50

ルの反転イネーブル信号 X E N B が供給される。このため、ノード N D 5 にゲートが接続されたトランジスタ N T 9 3 がオンするとともに、容量 C 9 1 が充電される。これにより、トランジスタ N T 9 3 を介して負側電位 V B B ( L レベル ) が論理合成回路部 8 2 のノード N D 4 に供給される。このため、論理合成回路部 8 2 から 1 段目のゲート線に L レベルのシフト出力信号 G a t e 1 が出力される。なお、この際、論理合成回路部 8 2 のノード N D 4 の電位が L レベルになることにより、そのノード N D 4 にゲートが接続されるトランジスタ N T 9 4 はオフ状態になる。これにより、論理合成回路部 8 2 のノード N D 5 の電位は H レベルに保持される。

#### 【 0 1 0 6 】

そして、反転イネーブル信号 X E N B の電位が H レベルから L レベルに切り替わる際には、トランジスタ N T 9 5 はオフするので、トランジスタ N T 9 5 を介してノード N D 5 に、 L レベルの反転イネーブル信号 X E N B は供給されない。これにより、トランジスタ N T 9 3 はオン状態に保持されるので、トランジスタ N T 9 3 を介して、ノード N D 4 に負側電位 V B B が続けて供給される。このため、反転イネーブル信号 X E N B が H レベルの期間に加えて L レベルの期間にも、論理合成回路部 8 2 のノード N D 4 から 1 段目のゲート線に L レベルのシフト出力信号 G a t e 1 が出力される。

#### 【 0 1 0 7 】

また、 H レベル ( V D D + V ) > V D D + V t ) のシフト信号 S R 3 が、ゲートに V D D の走査方向切替信号 C S V が入力されることによりオンしているトランジスタ N T 6 3 のドレインに入力されることにより、トランジスタ N T 6 3 のソース電位は、 ( V D D - V t ) になる。これにより、 2 段目のシフトレジスタ回路部 5 2 のトランジスタ N T 1 2 のゲートには、 ( V D D - V t ) の電位が入力される。このため、トランジスタ N T 1 2 がオン状態になる。この際、クロック信号 C K V 2 の電位が L レベルである。これにより、 2 段目のシフトレジスタ回路部 5 2 のノード N D 1 の電位は L レベルに保持されるので、トランジスタ N T 1 5 および N T 1 6 はオフ状態に保持される。また、この際、トランジスタ N T 1 8 のゲート電位はクロック信号 C K V 2 により L レベルになるので、トランジスタ N T 1 8 はオフしている。したがって、ノード N D 2 の電位は、 H レベル ( V D D + V ) に保持される。これにより、 2 段目のシフトレジスタ回路部 5 2 から H レベル ( V D D + V ) のシフト信号 S R 2 が続けて出力される。また、トランジスタ N T 1 5 がオフ状態に保持されることにより、 2 段目のシフトレジスタ回路部 5 2 のノード N D 3 の電位は、 H レベル ( V D D ) に保持される。これにより、 2 段目のシフトレジスタ回路部 5 2 から H レベル ( V D D ) の出力信号 S R 1 2 が続けて出力される。

#### 【 0 1 0 8 】

また、 1 段目のシフトレジスタ回路部 5 1 では、 H レベル ( V D D + V ) のシフト信号 S R 2 がドレインに入力されるトランジスタ N T 6 1 から続けて ( V D D - V t ) の電位がゲートに入力されることにより、トランジスタ N T 2 がオン状態に保持される。この状態で、クロック信号 C K V 1 が L レベル ( V B B ) から H レベル ( V D D ) に立ち上がる所以、トランジスタ N T 2 のソース電位が上昇する。この際、トランジスタ N T 2 では、容量 C 2 によりゲート - ソース間電圧が保持されながら、ゲート電位が ( V D D - V t ) から V D D と V B B との電位差分上昇する。これにより、 1 段目のシフトレジスタ回路部 5 1 のノード N D 1 の電位 ( トランジスタ N T 2 のソース電位 ) は、トランジスタ N T 2 のしきい値電圧 ( V t ) 分低下することなく、 H レベル ( V D D ) の電位に上昇する。

#### 【 0 1 0 9 】

そして、 1 段目のシフトレジスタ回路部 5 1 のノード N D 1 の電位が H レベルに上昇することにより、トランジスタ N T 5 および N T 6 がオン状態になる。この際、トランジスタ N T 7 がオフ状態であるので、トランジスタ N T 6 を介して負側電位 V B B から L レベルの電位が供給されることにより、 1 段目のシフトレジスタ回路部 5 1 のノード N D 2 の電位は L レベルに低下する。これにより、 1 段目のシフトレジスタ回路部 5 1 から出力されるシフト信号 S R 1 の電位は、 L レベルに低下する。また、ノード N D 2 の電位が L レベルに低下することにより、トランジスタ N T 4 はオフ状態になる。これにより、トラン

10

20

30

40

50

ジスタNT5を介して負側電位VBBからLレベルの電位が供給されることにより、1段目のシフトレジスタ回路部51のノードND3の電位はLレベルに低下する。このため、1段目のシフトレジスタ回路部51から出力される出力信号SR11の電位は、Lレベルに低下する。また、1段目のシフトレジスタ回路部51のノードND1の電位がHレベルに上昇した際、容量C1が充電される。これにより、次にトランジスタNT1がオン状態になって、トランジスタNT1を介して負側電位VBBからLレベルの電位が供給されるまで、ノードND1の電位がHレベルに保持される。このため、次にトランジスタNT1がオン状態になるまで、トランジスタNT5およびNT6がオン状態に保持されるので、シフト信号SR1および出力信号SR11の電位はLレベルに保持される。

## 【0110】

10

そして、イネーブル信号ENBの電位がHレベルからLレベルに低下する。これにより、ダミーゲート線に繋がる論理合成回路部81では、トランジスタNT81およびNT82を介して、Lレベルの電位が供給されることにより、ノードND4の電位がLレベルに低下する。このため、論理合成回路部81からダミーゲート線に出力されるシフト出力信号Dummyの電位は、Lレベルに低下する。また、イネーブル信号ENBがHレベルからLレベルに低下するのと同時に、反転イネーブル信号XENBがLレベルからHレベルに上昇する。これにより、Hレベルの反転イネーブル信号XENBが、ダミーゲート線に繋がる論理合成回路部81のダイオード接続されたトランジスタNT85を介してトランジスタNT83のゲートに入力される。これにより、トランジスタNT83は、オン状態になる。このため、トランジスタNT83を介して負側電位VBBからLレベルの電位が供給されることにより、ダミーゲート線に繋がる論理合成回路部81のノードND4の電位は、Lレベルに固定される。これにより、論理合成回路部81からダミーゲート線に出力されるシフト出力信号Dummyの電位は、Lレベルに固定される。

## 【0111】

20

また、Hレベルの反転イネーブル信号XENBがトランジスタNT83のゲートに入力された際、容量C81が充電される。これにより、次に、トランジスタNT84がオン状態になって負側電位VBBからトランジスタNT84を介してLレベルの電位が供給されるまで、ノードND5の電位（トランジスタNT83のゲート電位）は、Hレベルに保持される。このため、次にトランジスタNT84がオン状態になるまで、トランジスタNT83はオン状態に保持されるので、論理合成回路部81からダミーゲート線に出力されるシフト出力信号Dummyの電位はLレベルに固定された状態で保持される。

## 【0112】

30

また、クロック信号CKV2がHレベルに上昇することにより、2段目のシフトレジスタ回路部52において、オン状態のトランジスタNT12を介してHレベルのクロック信号CKV2がノードND1に供給される。これにより、ノードND1にゲートが接続されるトランジスタNT15およびNT16はオン状態になる。このため、トランジスタNT16を介して負側電位VBBからノードND2にLレベルの電位が供給される。これにより、2段目のシフトレジスタ回路部52のノードND2から出力されるシフト信号SR2の電位はLレベルに低下する。また、ノードND2の電位がLレベルに低下することにより、トランジスタNT14がオフする。これにより、トランジスタNT15を介して負側電位VBBからLレベルの電位が供給されることによって、ノードND3の電位はLレベルに低下する。これにより、2段目のシフトレジスタ回路部52のノードND3から出力される出力信号SR12の電位は、Lレベルに低下する。

## 【0113】

40

また、4段目のシフトレジスタ回路部54では、Hレベル（VDD+V<sub>t</sub>）のシフト信号SR3がドレインに入力されるトランジスタNT68から、（VDD-V<sub>t</sub>）の電位がトランジスタNT37のゲートに入力される。また、トランジスタNT31のゲートにHレベル（VDD）の出力信号SR13が入力される。また、トランジスタNT32はオフ状態に固定されている。この状態で、トランジスタNT37のドレインに入力されるクロック信号CKV2の電位がHレベル（VDD）に上昇した後、トランジスタNT34のド

50

レインに入力されるイネーブル信号 E N B 2 の電位が L レベル ( V B B ) から H レベル ( V D D ) に上昇する。これにより、上記した 3 段目のシフトレジスタ回路部 5 3 の動作と同様にして、4 段目のシフトレジスタ回路部 5 4 から V D D + V t 以上の電位 ( V D D + V ) を有する H レベルのシフト信号 S R 4 と、H レベル ( V D D ) の出力信号 S R 1 4 とが出力される。

【 0 1 1 4 】

そして、1 段目のゲート線に繋がる論理合成回路部 8 2 では、トランジスタ N T 9 1 のゲートに H レベル ( V D D + V ) のシフト信号 S R 3 が入力されるとともに、トランジスタ N T 9 2 のゲートに H レベル ( V D D + V ) のシフト信号 S R 4 が入力される。これにより、トランジスタ N T 9 1 とトランジスタ N T 9 2 とが両方ともオン状態になるので、イネーブル信号線からトランジスタ N T 9 1 および N T 9 2 を介してノード N D 4 にイネーブル信号 E N B が供給される。このイネーブル信号 E N B は、シフト信号 S R 3 および S R 4 が両方とも H レベルになることによりトランジスタ N T 9 1 および N T 9 2 が両方ともオン状態になった時点では、L レベルであり、その後わずかな期間後に L レベルから H レベルに電位が切り替わる。これにより、1 段目のゲート線に繋がる論理合成回路部 8 2 のノード N D 4 の電位が H レベルに上昇するので、論理合成回路部 8 2 から 1 段目のゲート線に H レベルのシフト出力信号 G a t e 1 が出力される。

【 0 1 1 5 】

すなわち、シフト出力信号 G a t e 1 の電位は、イネーブル信号 E N B が L レベルの間は、強制的に L レベルに保持されるとともに、イネーブル信号 E N B の電位が L レベルから H レベルに上昇するのに伴って、L レベルから H レベルに上昇される。したがって、イネーブル信号 E N B が L レベルの際、論理合成回路部 8 1 からダミーゲート線に出力されるシフト出力信号 D u m m y も強制的に L レベルに保持されているので、シフト出力信号 D u m m y が H レベルから L レベルに立ち下がるタイミングと、シフト出力信号 G a t e 1 が L レベルから H レベルに立ち上がるタイミングとが重なるのが抑制される。これにより、シフト出力信号 D u m m y が H レベルから L レベルに立ち下がるタイミングと、シフト出力信号 G a t e 1 が L レベルから H レベルに立ち上がるタイミングとが重なることに起因して、ノイズが発生するのが抑制される。

【 0 1 1 6 】

この後、上記した 3 段目のシフトレジスタ回路部 5 3 と同様の動作が、4 段目以降のシフトレジスタ回路部 5 4 および 5 5 において順次行われる。また、上記したダミーゲート線に繋がる論理合成回路部 8 1 と同様の動作が、1 段目以降のダミーゲート線に繋がる論理合成回路部 8 2 および 8 3 において行われる。そして、各段のシフトレジスタ回路部から H レベルのシフト信号と、H レベルの出力信号とが出力されるタイミングがシフトする。これに伴って、前段のシフト信号と次段のシフト信号とが両方とも H レベルになるタイミングも後段に進むにつれてシフトする。これにより、前段の H レベルのシフト信号と、次段の H レベルのシフト信号とが重なる期間において、イネーブル信号 E N B が H レベルに上昇することにより、各段の論理合成回路部から対応するゲート線に H レベルのシフト出力信号が出力されるタイミングも後段に進むにつれてシフトする。そして、このタイミングのシフトした H レベルのシフト出力信号により、各段のゲート線が順次駆動される。

【 0 1 1 7 】

上記のようにして、第 1 実施形態による液晶表示装置の各段のゲート線が、順次、駆動 (走査) される。そして、上記の動作が最後のゲート線の走査が終了されるまで繰り返される。その後、再度、1 段目のシフトレジスタ回路部 5 1 から上記の動作が繰り返し行われる。

【 0 1 1 8 】

次に、図 2 中の逆方向に沿って、各段のゲート線にタイミングのシフトしたシフト出力信号が順次出力される場合 (逆方向走査の場合) には、走査方向切替信号 C S V が L レベルに保持されるとともに、反転走査方向切替信号 X C S V が H レベルに保持される。これにより、逆方向走査時には、走査方向切替信号 C S V がゲートに入力されるトランジスタ

10

20

30

40

50

NT51、NT53、NT55、NT57、NT59およびNT61～70がオフ状態に保持されるとともに、反転走査方向切替信号XCSVがゲートに入力されるトランジスタNT52、NT54、NT56、NT58、NT60およびNT71～80がオン状態に保持される。そして、逆方向走査時には、上記した順方向走査時と同様の動作が、図2中の逆方向に沿って各段のシフトレジスタ回路部と、各段のゲート線に繋がる論理合成回路部とにおいて行われる。この際、前段のシフトレジスタ回路部から次段のシフトレジスタ回路部にシフト信号および出力信号が入力される場合や、次段のシフトレジスタ回路部から前段のシフトレジスタ回路部にシフト信号および出力信号が入力される場合には、上記したHレベルの反転走査方向切替信号XSCVによってオン状態にされたトランジスタNT52、NT54、NT58、NT60およびNT71～80を介してそれぞれ入力される。

10

### 【0119】

第1実施形態では、上記のように、シフトレジスタ回路部54に、シフト信号SR4が出力されるノードND2と負側電位VBBとの間に接続されたトランジスタNT36のゲートが接続される第1回路部54aのノードND1を正側電位VDDにリセットするためのリセットトランジスタNT39を設けることによって、Vドライバ5への正側電位VD<sub>D</sub>および負側電位VBBの供給後、Hレベルのスタート信号STVを入力してリセットトランジスタNT39により第1回路部54aのノードND1を正側電位VDDにリセットすれば、トランジスタNT36がオンするので、トランジスタNT36を介して、ノードND2に負側電位VBBを供給することができる。これにより、シフト信号SR4を負側電位VBBに固定することができる。また、シフトレジスタ回路部55に、シフト信号SR5が出力されるノードND2と負側電位VBBとの間に接続されたトランジスタNT46のゲートが接続される第1回路部55aのノードND1を正側電位VDDにリセットするためのリセットトランジスタNT49を設けることによって、Vドライバ5への正側電位VD<sub>D</sub>および負側電位VBBの供給後、Hレベルのスタート信号STVを入力してリセットトランジスタNT49により第1回路部55aのノードND1を正側電位VDDにリセットすれば、トランジスタNT46がオンするので、トランジスタNT46を介して、ノードND2に負側電位VBBを供給することができる。これにより、シフト信号SR5を負側電位VBBに固定することができる。これにより、論理合成回路部83のトランジスタNT101およびNT102を両方ともオフ状態に保持することができる。このため、論理合成回路部83のトランジスタNT101およびNT102を介してシフト出力信号Gate2は出力されないので、ゲート線に意図しないタイミングでシフト出力信号Gate2が出力されるのを抑制することができる。

20

### 【0120】

また、第1実施形態では、シフトレジスタ回路部53～55のトランジスタNT24、NT34およびNT44のゲートにクロック信号CKV1およびCKV2を交互に供給するとともに、ドレインにタイミングの異なるイネーブル信号ENB1およびENB2を交互に供給することによって、たとえば、3段目のシフトレジスタ回路部53において、クロック信号CKV1によりトランジスタNT24がオン状態になった後、イネーブル信号ENB1によりトランジスタNT24のソース電位がVBBからVDDに上昇するので、その電位の上昇分(V<sub>t</sub>)だけトランジスタNT24のゲート電位を上昇させることができる。また、4段目のシフトレジスタ回路部54において、クロック信号CKV2によりトランジスタNT34がオン状態になった後、イネーブル信号ENB2によりトランジスタNT34のソース電位がVBBからVDDに上昇するので、その電位の上昇分(V<sub>t</sub>)だけトランジスタNT34のゲート電位を上昇させることができる。これにより、トランジスタNT24およびNT34のドレインが固定的な正側電位VDDに接続されている場合に比べて、シフト信号SR3およびSR4の電位(VDD+V<sub>t</sub> < VDD+V<sub>t</sub>)をより高くすることができるので、容易に、シフト信号SR3およびSR4の電位を、VDDよりもしきい値電圧(V<sub>t</sub>)以上高い電位にすることができる。したがって、容易に、1段目のゲート線に繋がる論理合成回路部82のトランジスタNT91およびNT92のゲ

30

40

50

ートに、それぞれ、 $V_{DD} + V_t$  以上の電位 ( $V_{DD} + V_t$ ) を有するシフト信号 S R 3 および S R 4 を供給することができる。これにより、論理合成回路部 8 2 のトランジスタ N T 9 1 および N T 9 2 を介して 1 段目のゲート線に出力されるシフト出力信号 G a t e 1 の電位が、トランジスタ N T 9 1 および N T 9 2 のしきい値電圧 ( $V_t$ ) 分だけ低下するのを抑制することができる。

【 0 1 2 1 】

また、第 1 実施形態では、リセットトランジスタ N T 3 9 および N T 4 9 を用いてノード N D 2 の電位を負側電位 V B B にリセットする際に、リセットトランジスタ N T 3 9 および N T 4 9 のゲートに H レベルのスタート信号 S T V を入力することによって、リセットトランジスタ N T 3 9 および N T 4 9 を用いてノード N D 2 の電位を負側電位 V B B にリセットする際に、リセットトランジスタ N T 3 9 および N T 4 9 のゲートに入力する駆動信号を生成するために信号生成回路を別途形成する必要がないので、V ドライバ 5 を含む液晶表示装置の回路構成が複雑化するのを抑制することができる。

10

【 0 1 2 2 】

( 第 2 実施形態 )

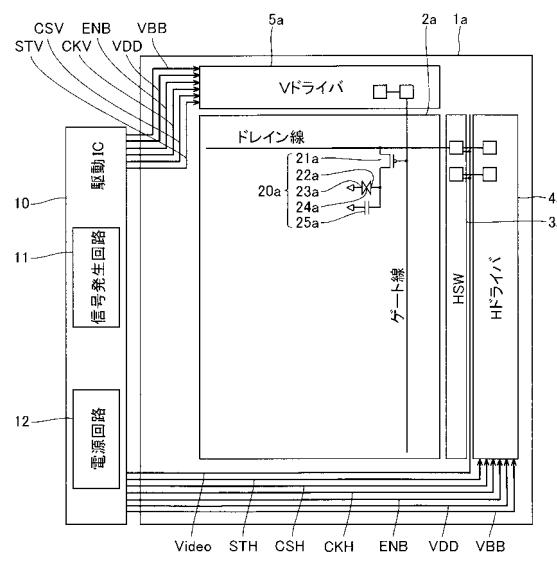

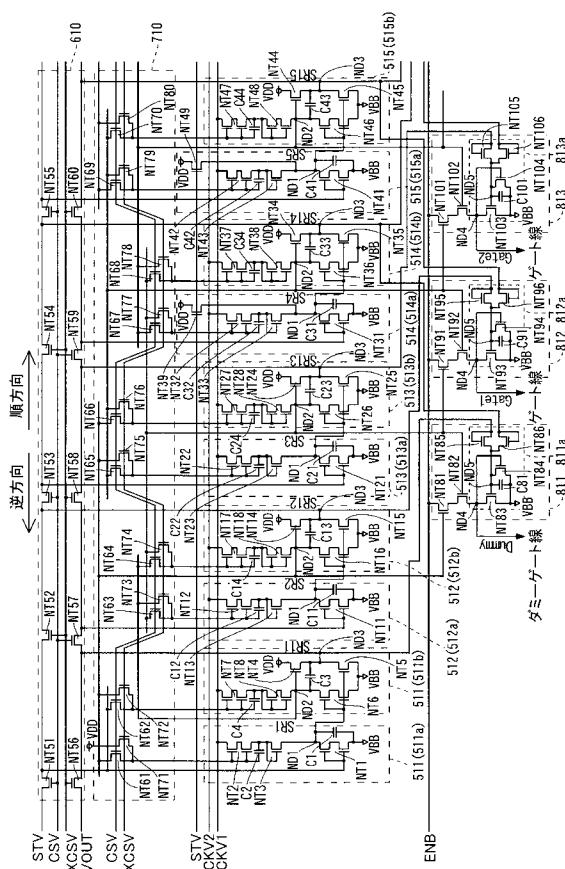

図 4 は、本発明の第 2 実施形態による液晶表示装置を示した平面図である。図 5 は、図 4 に示した第 2 実施形態による液晶表示装置の V ドライバ内部の回路図である。図 4 および図 5 を参照して、この第 2 実施形態では、上記第 1 実施形態の V ドライバを p チャネルトランジスタで構成する場合について説明する。

【 0 1 2 3 】

20

まず、図 4 を参照して、この第 2 実施形態では、基板 1 a 上に、表示部 2 a が設けられている。この表示部 2 a には、画素 2 0 a がマトリクス状に配置されている。なお、図 4 では、図面の簡略化のため、1 つの画素 2 0 a のみを図示している。各々の画素 2 0 a は、p チャネルトランジスタ 2 1 a (以下、トランジスタ 2 1 a という)、画素電極 2 2 a、画素電極 2 2 a に対向配置された各画素 2 0 a に共通の対向電極 2 3 a、画素電極 2 2 a と対向電極 2 3 a との間に挟持された液晶 2 4 a、および、補助容量 2 5 a によって構成されている。そして、トランジスタ 2 1 a のソースは、ドレイン線に接続されているとともに、ドレインは、画素電極 2 2 a および補助容量 2 5 a に接続されている。このトランジスタ 2 1 a のゲートはゲート線に接続されている。

【 0 1 2 4 】

30

また、表示部 2 a の一边に沿うように、基板 1 a 上に、表示部 2 a のドレイン線を駆動 (走査) するための水平スイッチ (H S W) 3 a および H ドライバ 4 a が設けられている。また、表示部 2 a の他の辺に沿うように、基板 1 a 上に、表示部 2 a のゲート線を駆動 (走査) するための V ドライバ 5 a が設けられている。なお、図 4 の水平スイッチ 3 a には、2 つのスイッチのみを図示しているが、実際は画素数に応じた数のスイッチが配置されている。また、図 4 の H ドライバ 4 a および V ドライバ 5 a には、それぞれ、シフトレジスタ回路部を 2 つのみ図示しているが、実際は画素数に応じた数のシフトレジスタ回路部が配置されている。また、基板 1 a の外部には、上記第 1 実施形態と同様、信号発生回路 1 1 および電源回路 1 2 を含む駆動 I C 1 0 が設置されている。

【 0 1 2 5 】

40

また、図 5 に示すように、第 2 実施形態では、V ドライバ 5 a の内部に、複数段のシフトレジスタ回路部 5 0 1 ~ 5 0 5 と、走査方向切替回路部 6 0 0 と、入力信号切替回路部 7 0 0 と、複数段の論理合成回路部 8 0 1 ~ 8 0 3 とが設けられている。なお、シフトレジスタ回路部 5 0 2 ~ 5 0 5 は、本発明の「第 1 シフトレジスタ回路部」および「第 2 シフトレジスタ回路部」の一例である。なお、図 5 では、図面の簡略化のため、5 段分のシフトレジスタ回路部 5 0 1 ~ 5 0 5 および 3 段分の論理合成回路部 8 0 1 ~ 8 0 3 のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。

【 0 1 2 6 】

1 段目のシフトレジスタ回路部 5 0 1 は、第 1 回路部 5 0 1 a と第 2 回路部 5 0 1 b と

50

によって構成されている。第1回路部501aは、pチャネルトランジスタPT1およびPT2と、ダイオード接続されたpチャネルトランジスタPT3と、容量C1およびC2とを含む。また、第2回路部501bは、pチャネルトランジスタPT4～PT7と、ダイオード接続されたpチャネルトランジスタPT8と、容量C3およびC4とを含む。以下、pチャネルトランジスタPT1～PT8は、それぞれ、トランジスタPT1～PT8と称する。

#### 【0127】

また、1段目のシフトレジスタ回路部501を構成するトランジスタPT1～PT8は、それぞれ、図2に示した第1実施形態の1段目のシフトレジスタ回路部51のトランジスタNT1～NT8に対応した位置に接続されている。ただし、上記第1実施形態と異なり、トランジスタPT1のソースは、正側電位VDDに接続されるとともに、トランジスタPT4のドレインは、負側電位VBBに接続されている。また、トランジスタPT5およびPT6のソースは、正側電位VDDに接続されている。

10

#### 【0128】

2段目のシフトレジスタ回路部502は、第1回路部502aと第2回路部502bによって構成されている。第1回路部502aは、pチャネルトランジスタPT11およびPT12と、ダイオード接続されたpチャネルトランジスタPT13と、容量C11およびC12とを含む。また、第2回路部502bは、pチャネルトランジスタPT14～PT17と、ダイオード接続されたpチャネルトランジスタPT18と、容量C13およびC14とを含む。なお、pチャネルトランジスタPT14は、本発明の「第3トランジスタ」および「第4トランジスタ」の一例であり、pチャネルトランジスタPT16は、本発明の「第5トランジスタ」の一例である。以下、pチャネルトランジスタPT11～PT18は、それぞれ、トランジスタPT11～PT18と称する。

20

#### 【0129】

また、2段目のシフトレジスタ回路部502を構成するトランジスタPT11～PT18は、それぞれ、図2に示した第1実施形態の2段目のシフトレジスタ回路部52のトランジスタNT11～NT18に対応した位置に接続されている。ただし、上記第1実施形態と異なり、トランジスタPT11のソースは、正側電位VDDに接続されるとともに、トランジスタPT14のドレインは、負側電位VBBに接続されている。また、トランジスタPT15およびPT16のソースは、正側電位VDDに接続されている。

30

#### 【0130】

3段目のシフトレジスタ回路部503は、第1回路部503aと第2回路部503bによって構成されている。第1回路部503aは、pチャネルトランジスタPT21およびPT22と、ダイオード接続されたpチャネルトランジスタPT23と、容量C21およびC22とを含む。また、第2回路部503bは、pチャネルトランジスタPT24～PT27と、ダイオード接続されたpチャネルトランジスタPT28と、容量C23およびC24とを含む。なお、pチャネルトランジスタPT24は、本発明の「第3トランジスタ」および「第4トランジスタ」の一例であり、pチャネルトランジスタPT26は、本発明の「第5トランジスタ」の一例である。以下、pチャネルトランジスタPT21～PT28は、それぞれ、トランジスタPT21～PT28と称する。

40

#### 【0131】

また、3段目のシフトレジスタ回路部503を構成するトランジスタPT21～PT28は、それぞれ、図2に示した第1実施形態の3段目のシフトレジスタ回路部53のトランジスタNT21～NT28に対応した位置に接続されている。ただし、上記第1実施形態と異なり、トランジスタPT21、PT25およびPT26のソースは、それぞれ、正側電位VDDに接続されている。

#### 【0132】

4段目のシフトレジスタ回路部504は、第1回路部504aと第2回路部504bによって構成されている。第1回路部504aは、pチャネルトランジスタPT31およびPT32と、ダイオード接続されたpチャネルトランジスタPT33と、容量C31お

50

およびC 3 2とを含む。また、第2回路部5 0 4 bは、pチャネルトランジスタP T 3 4～P T 3 7と、ダイオード接続されたpチャネルトランジスタP T 3 8と、容量C 3 3およびC 3 4とを含む。なお、pチャネルトランジスタP T 3 4は、本発明の「第3トランジスタ」および「第4トランジスタ」の一例であり、pチャネルトランジスタP T 3 6は、本発明の「第5トランジスタ」の一例である。以下、pチャネルトランジスタP T 3 1～P T 3 8は、それぞれ、トランジスタP T 3 1～P T 3 8と称する。

#### 【0133】

また、4段目のシフトレジスタ回路部5 0 4を構成するトランジスタP T 3 1～P T 3 8は、それぞれ、図2に示した第1実施形態の4段目のシフトレジスタ回路部5 4のトランジスタN T 3 1～N T 3 8に対応した位置に接続されている。ただし、上記第1実施形態と異なり、トランジスタP T 3 1、P T 3 5およびP T 3 6のソースは、それぞれ、正側電位V D Dに接続されている。

10

#### 【0134】

5段目のシフトレジスタ回路部5 0 5は、第1回路部5 0 5 aと第2回路部5 0 5 bによって構成されている。第1回路部5 0 5 aは、pチャネルトランジスタP T 4 1およびP T 4 2と、ダイオード接続されたpチャネルトランジスタP T 4 3と、容量C 4 1およびC 4 2とを含む。また、第2回路部5 0 5 bは、pチャネルトランジスタP T 4 4～P T 4 7と、ダイオード接続されたpチャネルトランジスタP T 4 8と、容量C 4 3およびC 4 4とを含む。なお、pチャネルトランジスタP T 4 4は、本発明の「第3トランジスタ」および「第4トランジスタ」の一例であり、pチャネルトランジスタP T 4 6は、本発明の「第5トランジスタ」の一例である。以下、pチャネルトランジスタP T 4 1～P T 4 8は、それぞれ、トランジスタP T 4 1～P T 4 8と称する。

20

#### 【0135】

また、5段目のシフトレジスタ回路部5 0 5を構成するトランジスタP T 4 1～P T 4 8は、それぞれ、図2に示した第1実施形態の5段目のシフトレジスタ回路部5 5のトランジスタN T 4 1～P T 4 8に対応した位置に接続されている。ただし、上記第1実施形態と異なり、トランジスタP T 4 1、P T 4 5およびP T 4 6のソースは、それぞれ、正側電位V D Dに接続されている。

#### 【0136】

ここで、第2実施形態では、4段目のシフトレジスタ回路部5 0 4の第1回路部5 0 4 aは、シフト信号S R 4を出力するノードN D 2の電位を正側電位V D DにリセットするためのpチャネルトランジスタP T 3 9を含んでいる。また、5段目のシフトレジスタ回路部5 0 5の第1回路部5 0 5 aは、シフト信号S R 5を出力するノードN D 2の電位を正側電位V D DにリセットするためのpチャネルトランジスタP T 4 9を含んでいる。以下、pチャネルトランジスタP T 3 9およびP T 4 9は、それぞれ、リセットトランジスタP T 3 9およびP T 4 9と称する。

30

#### 【0137】

また、リセットトランジスタP T 3 9のドレインには、負側電位V B Bが供給されるとともに、ソースは、4段目のシフトレジスタ回路部5 0 4の第1回路部5 0 4 aの出力ノードであるノードN D 1に接続されている。また、リセットトランジスタP T 3 9のゲートには、スタート信号S T Vを供給するためのスタート信号線(S T V)が接続されている。これにより、Lレベルのスタート信号S T Vに応答してリセットトランジスタP T 3 9がオンすると、リセットトランジスタP T 3 9を介して負側電位V B Bが供給されることにより、第1回路部5 0 4 aのノードN D 1の電位が負側電位V B B(Lレベル)になるように構成されている。そして、第1回路部5 0 4 aのノードN D 1の電位が負側電位V B B(Lレベル)になると、第2回路部5 0 4 bのトランジスタP T 3 6がオンするので、トランジスタP T 3 6を介して正側電位V D Dが供給されることにより、シフト信号S R 4を出力する第2回路部5 0 4 bのノードN D 2が正側電位V D Dにリセットされるように構成されている。

40

#### 【0138】

50

また、リセットトランジスタPT49のドレインには、負側電位VBBが供給されるとともに、ソースは、5段目のシフトレジスタ回路部505の第1回路部505aの出力ノードであるノードND1に接続されている。また、リセットトランジスタPT49のゲートには、スタート信号STVを供給するためのスタート信号線(STV)が接続されている。これにより、5段目のシフトレジスタ回路部505では、上記した4段目のシフトレジスタ回路部504と同様にして、シフト信号SR5を出力する第2回路部505bのノードND2が正側電位VDDにリセットされるように構成されている。

#### 【0139】

また、上記した各段のシフトレジスタ回路部501～505に設けられたトランジスタPT1～PT8、PT11～PT18、PT21～PT28、PT31～PT38およびPT41～PT48と、リセットトランジスタPT39およびPT49とは、全て、p型のMOSトランジスタからなるTFTにより構成されている。また、トランジスタPT1、PT2、PT6、PT7、PT8、PT11、PT12、PT16、PT17、PT18、PT21、PT22、PT26、PT27、PT28、PT31、PT32、PT36、PT37、PT38、PT41、PT42、PT46、PT47およびPT48は、それぞれ、互いに電気的に接続された2つのゲート電極を有する。

#### 【0140】

また、走査方向切替回路部600は、pチャネルトランジスタPT51～PT60を含む。以下、pチャネルトランジスタPT51～PT60は、それぞれ、トランジスタPT51～PT60と称する。このトランジスタPT51～PT60は、すべてp型のMOSトランジスタからなるTFTにより構成されている。そして、走査方向切替回路部600を構成するトランジスタPT51～PT60は、それぞれ、図2に示した第1実施形態の走査方向切替回路部60のトランジスタNT51～NT60に対応した位置に接続されている。

#### 【0141】

また、入力信号切替回路部700は、pチャネルトランジスタPT61～PT80を含む。以下、pチャネルトランジスタPT61～PT80は、それぞれ、トランジスタPT61～PT80と称する。このトランジスタPT61～PT80は、すべてp型のMOSトランジスタからなるTFTにより構成されている。そして、入力信号切替回路部700を構成するトランジスタPT61～PT80は、それぞれ、図2に示した第1実施形態の入力信号切替回路部70のトランジスタNT61～NT80に対応した位置に接続されている。ただし、上記第1実施形態と異なり、トランジスタPT71のソース／ドレインの他方は、負側電位VBBに接続されている。

#### 【0142】

また、論理合成回路部801～803は、それぞれ、ダミーゲート線、1段目のゲート線および2段目のゲート線に接続されている。ダミーゲート線に接続される論理合成回路部801は、pチャネルトランジスタPT81～PT84と、ダイオード接続されたpチャネルトランジスタPT85と、容量C81とを含む。なお、pチャネルトランジスタPT81は、本発明の「第1トランジスタ」の一例であり、pチャネルトランジスタPT82は、本発明の「第2トランジスタ」の一例である。以下、pチャネルトランジスタPT81～PT85は、それぞれ、トランジスタPT81～PT85と称する。また、トランジスタPT83～PT85と、容量C81とによって、電位固定回路部801aが構成されている。そして、ダミーゲート線に接続される論理合成回路部801を構成するトランジスタPT81～PT85は、それぞれ、図2に示した第1実施形態のダミーゲート線に接続される論理合成回路部81のトランジスタNT81～NT85に対応した位置に接続されている。ただし、トランジスタPT83のソースは、正側電位VDDに接続されている。

#### 【0143】

また、1段目のゲート線に接続される論理合成回路部802は、pチャネルトランジスタPT91～PT94と、ダイオード接続されたpチャネルトランジスタPT95と、容

10

20

30

40

50

量C91とを含む。なお、pチャネルトランジスタPT91は、本発明の「第1トランジスタ」の一例であり、pチャネルトランジスタPT92は、本発明の「第2トランジスタ」の一例である。以下、pチャネルトランジスタPT91～PT95は、それぞれ、トランジスタPT91～PT95と称する。また、トランジスタPT93～PT95と、容量C91とによって、電位固定回路部802aが構成されている。そして、1段目のゲート線に接続される論理合成回路部802を構成するトランジスタPT91～PT95は、それぞれ、図2に示した第1実施形態の1段目のゲート線に接続される論理合成回路部82のトランジスタNT91～NT95に対応した位置に接続されている。ただし、トランジスタPT93のソースは、正側電位VDDに接続されている。

## 【0144】

10

また、2段目のゲート線に接続される論理合成回路部803は、pチャネルトランジスタPT101～PT104と、ダイオード接続されたpチャネルトランジスタPT105と、容量C101とを含む。なお、pチャネルトランジスタPT101は、本発明の「第1トランジスタ」の一例であり、pチャネルトランジスタPT102は、本発明の「第2トランジスタ」の一例である。以下、pチャネルトランジスタPT101～PT105は、それぞれ、トランジスタPT101～PT105と称する。また、トランジスタPT103～PT105と、容量C101とによって、電位固定回路部803aが構成されている。そして、2段目のゲート線に接続される論理合成回路部803を構成するトランジスタPT101～PT105は、それぞれ、図2に示した第1実施形態の2段目のゲート線に接続される論理合成回路部83のトランジスタNT101～NT105に対応した位置に接続されている。ただし、トランジスタPT103のソースは、正側電位VDDに接続されている。なお、上記の論理合成回路部801～803に設けられたトランジスタPT81～PT85、PT91～PT95およびPT101～PT105は、全て、p型のMOSトランジスタからなるTFTにより構成されている。

20

## 【0145】

また、回路部901は、pチャネルトランジスタPT111～PT113と、ダイオード接続されたpチャネルトランジスタPT114と、容量C111とを含んでいる。以下、pチャネルトランジスタPT111～PT114は、それぞれ、トランジスタPT111～PT114と称する。そして、回路部901を構成するトランジスタPT111～PT114は、それぞれ、図2に示した第1実施形態の回路部91のトランジスタNT111～NT114に対応した位置に接続されている。ただし、トランジスタPT112のソースは、正側電位VDDに接続されている。

30

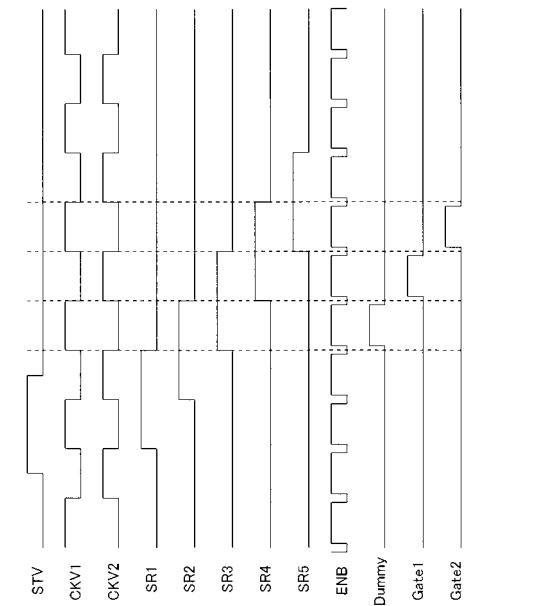

## 【0146】

図6は、本発明の第2実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図5および図6を参照して、第2実施形態によるVドライバ5aの動作を説明する。この第2実施形態によるVドライバ5aでは、図3に示した第5実施形態のスタート信号STV、クロック信号CKV1、CKV2、イネーブル信号ENB、ENB1、ENB2および反転イネーブル信号XENBのHレベルとLレベルとを反転させた波形の信号を、それぞれ、スタート信号STV、クロック信号CKV1、CKV2、イネーブル信号ENB、ENB1、ENB2および反転イネーブル信号XENBとして入力する。これにより、第2実施形態によるシフトレジスタ回路部501～505からは、図2に示した第1実施形態によるシフトレジスタ回路部51～55から出力されるシフト信号SR1～SR5および出力信号SR11～SR15のHレベルとLレベルとを反転させた波形を有する信号が出力される。また、第2実施形態による論理合成回路部801～803からは、図2に示した第1実施形態による論理合成回路部81～83から出力されるシフト出力信号Dummy、Gate1およびGate2のHレベルとLレベルとを反転させた波形を有する信号が出力される。この第2実施形態によるVドライバの上記以外の動作は、図2に示した上記第1実施形態によるVドライバの動作と同様である。

40

## 【0147】

なお、第2実施形態では、シフトレジスタ回路部503～505のトランジスタPT2

50

4、PT34およびPT44のゲートにクロック信号CKV1およびCKV2を交互に供給するとともに、ドレインにタイミングの異なるイネーブル信号ENB1およびENB2を交互に供給することによって、以下のような動作が行われる。たとえば、3段目のシフトレジスタ回路部503において、クロック信号CKV1によりトランジスタPT24がオン状態になった後、イネーブル信号ENB1によりトランジスタPT24のソース電位がVDDからVBBに低下するので、その電位の低下分(V)だけトランジスタPT24のゲート電位が低下する。また、4段目のシフトレジスタ回路部504において、クロック信号CKV2によりトランジスタPT34がオン状態になった後、イネーブル信号ENB2によりトランジスタPT34のソース電位がVDDからVBBに低下するので、その電位の低下分(V)だけトランジスタPT34のゲート電位が低下する。これにより、トランジスタPT24およびPT34のドレインが固定的な負側電位VBBに接続されている場合に比べて、シフト信号SR3およびSR4の電位(VBB-V < VBB-Vt)をより低くすることができるので、より容易に、シフト信号SR3およびSR4の電位を、VBBよりもしきい値電圧(Vt)以上低い電位にすることができる。したがって、より容易に、1段目のゲート線に繋がる論理合成回路部802のトランジスタPT91およびPT92のゲートに、それぞれ、VBB-Vt以下の電位(VBB-V)を有するシフト信号SR3およびSR4を供給することができる。これにより、論理合成回路部802のトランジスタPT91およびPT92を介して1段目のゲート線に出力されるシフト出力信号Gate1の電位が、しきい値電圧(Vt)分だけ上昇するのをより抑制することができる。

10

20

#### 【0148】

また、第2実施形態では、上記のように、リセットトランジスタPT39およびPT49を設けるとともに、スタート信号STVに応答してトランジスタPT39およびPT49をオンさせることによって、Vドライバを含む液晶表示装置において、ゲート線に意図しないタイミングでシフト出力信号が出力されるのを抑制することができるなどの上記第1実施形態と同様の効果を得ることができる。

#### 【0149】

##### (第3実施形態)

図7は、本発明の第3実施形態による液晶表示装置のVドライバ内部の回路図である。図7を参照して、この第3実施形態では、上記第1実施形態の構成において、3段目以降のシフトレジスタ回路部においても、1段目および2段目のシフトレジスタ回路部と同様に、出力信号が出力されるノードに接続されたトランジスタのドレインに正側電位を供給するとともに、シフトレジスタ回路部の出力信号を用いて論理合成回路部から出力するシフト出力信号をLレベルに固定した状態で保持する場合について説明する。

30

#### 【0150】

すなわち、この第3実施形態によるVドライバでは、図7に示すように、複数段のシフトレジスタ回路部511～515と、走査方向切替回路部610と、入力信号切替回路部710と、複数段の論理合成回路部811～813とが設けられている。なお、シフトレジスタ回路部512～515は、本発明の「第1シフトレジスタ回路部」および「第2シフトレジスタ回路部」の一例である。なお、図7では、図面の簡略化のため、5段分のシフトレジスタ回路部511～515および3段分の論理合成回路部811～813のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。

40

#### 【0151】

そして、1段目のシフトレジスタ回路部511は、図2に示した第1実施形態の1段目のシフトレジスタ回路部51の第1回路部51aおよび第2回路部51bと同様の回路構成を有する第1回路部511aおよび第2回路部511bによって構成されている。また、2段目のシフトレジスタ回路部512は、図2に示した第1実施形態の2段目のシフトレジスタ回路部52の第1回路部52aおよび第2回路部52bと同様の回路構成を有する第1回路部512aおよび第2回路部512bによって構成されている。

50

## 【0152】

ここで、第3実施形態では、3段目のシフトレジスタ回路部513は、出力信号S R 13を出力するノードN D 3にソースが接続されたトランジスタN T 24のドレインに正側電位V D Dが供給されること以外は、図2に示した第1実施形態の3段目のシフトレジスタ回路部513の第1回路部513aおよび第2回路部513bと同様の回路構成を有する第1回路部513aおよび第2回路部513bを有している。また、4段目のシフトレジスタ回路部514は、出力信号S R 14を出力するノードN D 3にソースが接続されたトランジスタN T 34のドレインに正側電位V D Dが供給されること以外は、図2に示した第1実施形態の4段目のシフトレジスタ回路部514の第1回路部514aおよび第2回路部514bと同様の回路構成を有する第1回路部514aおよび第2回路部514bを有している。10

また、5段目のシフトレジスタ回路部515は、出力信号S R 15を出力するノードN D 3にソースが接続されたトランジスタN T 44のドレインに正側電位V D Dが供給されること以外は、図2に示した第1実施形態の5段目のシフトレジスタ回路部515の第1回路部515aおよび第2回路部515bと同様の回路構成を有する第1回路部515aおよび第2回路部515bを有している。

## 【0153】

また、走査方向切替回路部610は、図2に示した第1実施形態の走査方向切替回路部60と同様の回路構成を有する。ただし、第3実施形態では、トランジスタN T 56のソース／ドレインの他方と、トランジスタN T 57のソース／ドレインの一方とが接続されている。また、第3実施形態の入力信号切替回路部710は、図2に示した第1実施形態の入力信号切替回路部70と同様の回路構成を有する。20

## 【0154】

また、ダミーゲート線に接続される論理合成回路部811は、トランジスタN T 81～N T 84と、ダイオード接続されたトランジスタN T 85およびN T 86と、容量C 81とを含む。すなわち、第3実施形態の論理合成回路部811は、図2に示した第1実施形態の論理合成回路部81の回路構成において、ダイオード接続されたトランジスタN T 86を加えた回路構成を有する。また、トランジスタN T 83～N T 86と、容量C 81とによって、電位固定回路部811aが構成されている。また、第3実施形態では、トランジスタN T 85のソースは、1段目のシフトレジスタ回路部511の出力信号S R 11が出力されるノードN D 3に接続されている。また、トランジスタN T 86のソースは、4段目のシフトレジスタ回路部514の出力信号S R 14が出力されるノードN D 3に接続されるとともに、ドレインは、論理合成回路部811のノードN D 5に接続されている。30

## 【0155】

また、1段目のゲート線に接続される論理合成回路部812は、トランジスタN T 91～N T 94と、ダイオード接続されたトランジスタN T 95およびN T 96と、容量C 91とを含む。すなわち、第3実施形態の論理合成回路部812は、図2に示した第1実施形態の論理合成回路部82の回路構成において、ダイオード接続されたトランジスタN T 96を加えた回路構成を有する。また、トランジスタN T 93～N T 96と、容量C 91とによって、電位固定回路部812aが構成されている。また、第3実施形態では、トランジスタN T 95のソースは、2段目のシフトレジスタ回路部512の出力信号S R 12が出力されるノードN D 3に接続されている。また、トランジスタN T 96のソースは、5段目のシフトレジスタ回路部515の出力信号S R 15が出力されるノードN D 3に接続されるとともに、ドレインは、論理合成回路部812のノードN D 5に接続されている。40

## 【0156】

また、2段目のゲート線に接続される論理合成回路部813は、トランジスタN T 101～N T 104と、ダイオード接続されたトランジスタN T 105およびN T 106と、容量C 101とを含む。すなわち、第3実施形態の論理合成回路部813は、図2に示した第1実施形態の論理合成回路部83の回路構成において、ダイオード接続されたトラン50

ジスタNT106を加えた回路構成を有する。また、トランジスタNT103～NT106と、容量C101とによって、電位固定回路部813aが構成されている。また、第3実施形態では、トランジスタNT105のソースは、3段目のシフトレジスタ回路部513の出力信号SR13が出力されるノードND3に接続されている。また、トランジスタNT106のソースは、図示しない6段目のシフトレジスタ回路部のシフト信号が出力されるノードに接続されるとともに、ドレインは、論理合成回路部813のノードND5に接続されている。

#### 【0157】

図8は、本発明の第3実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図7および図8を参照して、第3実施形態によるVドライバの動作について説明する。

10

#### 【0158】

この第3実施形態によるVドライバの動作は、基本的には、上記第1実施形態によるVドライバの動作と同様である。ただし、この第3実施形態によるVドライバでは、上記第1実施形態と異なり、3段目以降のシフトレジスタ回路部513～515の出力信号SR13～SR15が出力されるノードND3に接続されたトランジスタNT24～NT44のドレインに、正側電位VDDを供給する。すなわち、第3実施形態では、3段目以降のシフトレジスタ回路部513～515において、上記した第1実施形態による1段目および2段目のシフトレジスタ回路部と同様の動作が行われる。

#### 【0159】

また、第3実施形態では、論理合成回路部811～813から各段のゲート線に出力するシフト出力信号Dummy、Gate1およびGate2の電位をLレベルに固定する際、シフトレジスタ回路部からの出力信号を用いて電位を固定する。たとえば、1段目のゲート線に繋がる論理合成回路部812において、共にオン状態になっているトランジスタNT91およびNT92を介してHレベルのイネーブル信号ENBが供給されることにより、1段目のゲート線に出力するシフト出力信号Gate1がHレベルになっている。この後、イネーブル信号ENBの電位がLレベルに低下する。これにより、Lレベルのイネーブル信号ENBがトランジスタNT91およびNT92を介して供給されることにより、1段目のゲート線に出力されるシフト出力信号Gate1の電位がLレベルに低下する。

20

#### 【0160】

この後、第3実施形態では、Hレベル(VDD)の出力信号SR15が、1段目のゲート線に繋がる論理合成回路部812のトランジスタNT93のゲートにダイオード接続されたトランジスタNT96を介して入力される。これにより、トランジスタNT93は、オン状態になる。このため、トランジスタNT93を介して負側電位VBBからLレベルの電位が供給されることにより、1段目のゲート線に繋がる論理合成回路部812のノードND4の電位は、Lレベルに固定される。これにより、論理合成回路部812から1段目のゲート線に出力されるシフト出力信号Gate1の電位は、Lレベルに固定される。また、第3実施形態では、Hレベル(VDD)の出力信号SR15がトランジスタNT93のゲートに入力された際、容量C91が充電される。これにより、次に、トランジスタNT94がオン状態になって負側電位VBBからトランジスタNT94を介してLレベルの電位が供給されるまで、ノードND5の電位(トランジスタNT93のゲート電位)は、Hレベルに保持される。このため、次にトランジスタNT94がオン状態になるまで、トランジスタNT93はオン状態に保持されるので、論理合成回路部812から1段目のゲート線に出力されるシフト出力信号Gate1の電位はLレベルに固定された状態で保持される。

30

#### 【0161】

そして、各段の論理合成回路部において、上記した1段目のゲート線に繋がる論理合成回路部812の動作と同様の動作により、シフトレジスタ回路部の出力信号を用いてシフト出力信号の電位がLレベルに固定される。第3実施形態によるVドライバの上記以外の

40

50

動作は、上記第1実施形態によるVドライバの動作と同様である。

【0162】

なお、第3実施形態では、トランジスタNT4、NT14、NT24、NT34およびNT44のゲートとソースとの間に、それぞれ、容量C3、C13、C23、C33およびC43を接続するとともに、トランジスタNT4、NT14、NT24、NT34およびNT44のドレインに正側電位VDDを供給することによって、以下のような動作が行われる。たとえば、2段目のシフトレジスタ回路部512において、クロック信号CKV2に応答してトランジスタNT14がオンする際に、容量C13が接続されたトランジスタNT14のゲート-ソース間電圧を維持するように、トランジスタNT14のソース電位の上昇に伴ってトランジスタNT14のゲート電位(シフト信号SR2の電位)が上昇する。また、3段目のシフトレジスタ回路部513において、クロック信号CKV1に応答してトランジスタNT24がオンする際に、容量C23が接続されたトランジスタNT24のゲート-ソース間電圧を維持するように、トランジスタNT24のソース電位の上昇に伴ってトランジスタNT24のゲート電位(シフト信号SR3の電位)が上昇する。上記のようにして、トランジスタNT14のゲート電位(シフト信号SR2の電位)と、トランジスタNT24のゲート電位(シフト信号SR3の電位)とがVDDよりもしきい値電圧(Vt)以上の所定の電圧(V)分高い電位まで低下するので、ダミーゲート線に繋がる論理合成回路部811のトランジスタNT81およびトランジスタNT82のゲートに、それぞれ、VDD+Vtよりも高い電位(VDD+V)を有するシフト信号SR2およびSR3が供給される。これにより、論理合成回路部811のトランジスタNT81およびNT82を介してダミーゲート線に出力されるシフト出力信号Dummyの電位が、VDDからトランジスタNT81およびNT82のしきい値電圧(Vt)分だけ低下するのが抑制される。10

【0163】

また、第3実施形態では、上記のように、リセットトランジスタNT39およびNT49を設けるとともに、スタート信号STVに応答してトランジスタNT39およびNT49をオンさせることによって、ゲート線に意図しないタイミングでシフト出力信号が出力されるのを抑制することができるなどの上記第1実施形態と同様の効果を得ることができる。20

【0164】

(第4実施形態)

図9は、本発明の第4実施形態による液晶表示装置のVドライバ内部の回路図である。図9を参照して、この第4実施形態では、上記第3実施形態のVドライバをpチャネルトランジスタで構成する場合について説明する。

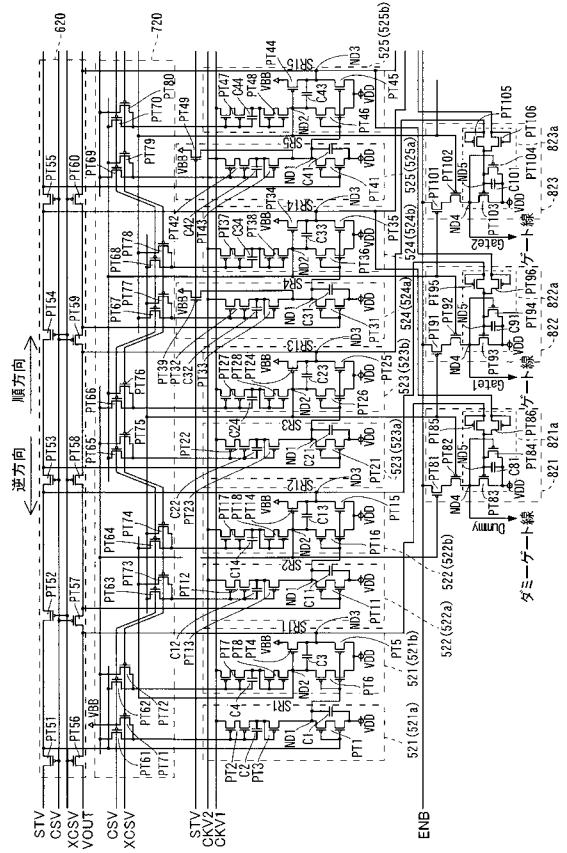

【0165】

この第4実施形態によるVドライバでは、図9に示すように、複数段のシフトレジスタ回路部521～525と、走査方向切替回路部620と、入力信号切替回路部720と、複数段の論理合成回路部821～823とが設けられている。なお、シフトレジスタ回路部521～525は、本発明の「第1シフトレジスタ回路部」および「第2シフトレジスタ回路部」の一例である。なお、図9では、図面の簡略化のため、5段分のシフトレジスタ回路部521～525および3段分の論理合成回路部821～823のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。40

【0166】

そして、1段目のシフトレジスタ回路部521は、図5に示した第2実施形態の1段目のシフトレジスタ回路部501の第1回路部501aおよび第2回路部501bと同様の回路構成を有する第1回路部521aおよび第2回路部521bによって構成されている。また、2段目のシフトレジスタ回路部522は、図5に示した第2実施形態の2段目のシフトレジスタ回路部502の第1回路部502aおよび第2回路部502bと同様の回路構成を有する第1回路部522aおよび第2回路部522bによって構成されている。50

## 【0167】

ここで、第4実施形態では、3段目以降のシフトレジスタ回路部523～525の出力信号S R 13～S R 15を出力するノードN D 3にソースが接続されたトランジスタP T 24～P T 44のドレインには、それぞれ、負側電位V B Bが供給されている。すなわち、第4実施形態では、3段目以降のシフトレジスタ回路部523～525は、全て同じ回路構成を有している。具体的には、3段目～5段目のシフトレジスタ回路部は、第2実施形態によるシフトレジスタ回路部の第1回路部および第2回路部と同様の回路構成を有する第1回路部および第2回路部を有している。

## 【0168】

また、走査方向切替回路部620は、基本的には、図5に示した第2実施形態による走査方向切替回路部600と同様の回路構成を有している。ただし、第4実施形態による走査方向切替回路部620では、トランジスタP T 56のソース／ドレインの他方と、トランジスタP T 57のソース／ドレインの一方とが接続されている。また、入力信号切替回路部720は、図5に示した第2実施形態の入力信号切替回路部700と同様の回路構成を有する。

10

## 【0169】

また、論理合成回路部821～823は、図7に示した第3実施形態の論理合成回路部811～813を構成するnチャネルトランジスタをpチャネルトランジスタで置き換えた構成を有している。具体的には、第4実施形態によるダミーゲート線に繋がる論理合成回路部821は、図7に示した第3実施形態の論理合成回路部811のトランジスタN T 81～N T 86をそれぞれトランジスタP T 81～P T 86で置き換えた回路構成を有している。また、第4実施形態による1段目のゲート線に繋がる論理合成回路部822は、図7に示した第3実施形態の論理合成回路部812のトランジスタN T 91～N T 96をそれぞれトランジスタP T 91～P T 96で置き換えた回路構成を有している。また、第4実施形態による2段目のゲート線に繋がる論理合成回路部823は、図7に示した第3実施形態の論理合成回路部813のトランジスタN T 101～N T 106をそれぞれトランジスタP T 101～P T 106で置き換えた回路構成を有している。また、第4実施形態では、論理合成回路部821～823のトランジスタP T 83、P T 93およびP T 103のソースは、正側電位V D Dに接続されている。

20

## 【0170】

30

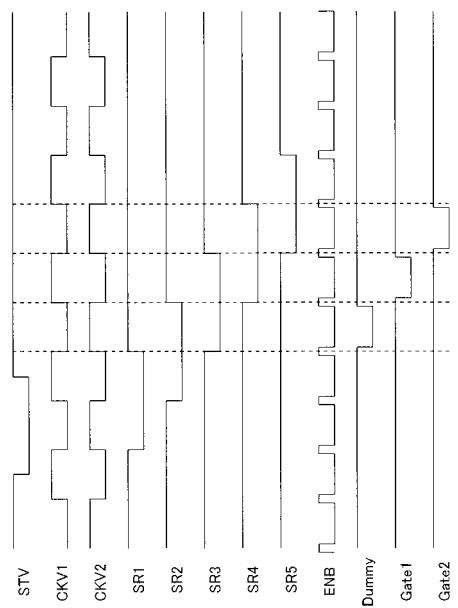

図10は、本発明の第4実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図9および図10を参照して、第4実施形態によるVドライバの動作を説明する。この第4実施形態によるVドライバでは、図8に示した第3実施形態のスタート信号S T V、クロック信号C K V 1、C K V 2およびイネーブル信号E N BのHレベルとLレベルとを反転させた波形の信号を、それぞれ、スタート信号S T V、クロック信号C K V 1、C K V 2およびイネーブル信号E N Bとして入力する。これにより、第3実施形態によるシフトレジスタ回路部521～525からは、図7に示した第3実施形態によるシフトレジスタ回路部511～515から出力されるシフト信号S R 1～S R 5および出力信号S R 11～S R 15のHレベルとLレベルとを反転させた波形を有する信号がそれぞれ出力される。また、第4実施形態による論理合成回路部821～823からは、図7に示した第3実施形態による論理合成回路部811～813から出力されるシフト出力信号D u m m y、G a t e 1およびG a t e 2のHレベルとLレベルとを反転させた波形を有する信号が出力される。この第4実施形態によるVドライバの上記以外の動作は、図7に示した上記第3実施形態によるVドライバの動作と同様である。

40

## 【0171】

なお、第4実施形態では、トランジスタP T 4、P T 14、P T 24、P T 34およびP T 44のゲートとソースとの間に、それぞれ、容量C 3、C 13、C 23、C 33およびC 43を接続するとともに、トランジスタP T 4、P T 14、P T 24、P T 34およびP T 44のドレインに負側電位V B Bを供給することによって、以下のような動作が行われる。たとえば、2段目のシフトレジスタ回路部522において、クロック信号C K V

50

2に応答してトランジスタPT14がオンする際に、容量C13が接続されたトランジスタPT14のゲート-ソース間電圧を維持するように、トランジスタPT14のソース電位の低下に伴ってトランジスタPT14のゲート電位(シフト信号SR2の電位)が低下する。また、3段目のシフトレジスタ回路部523において、クロック信号CKV1に応答してトランジスタPT24がオンする際に、容量C23が接続されたトランジスタPT24のゲート-ソース間電圧を維持するように、トランジスタPT24のソース電位の低下に伴ってトランジスタPT24のゲート電位(シフト信号SR3の電位)が低下する。上記のようにして、トランジスタPT14のゲート電位(シフト信号SR2の電位)と、トランジスタPT24のゲート電位(シフト信号SR3の電位)とがVBBよりもしきい値電圧(Vt)以上の所定の電圧(V)分低い電位まで低下するので、ダミーゲート線に繋がる論理合成回路部821のトランジスタPT81およびトランジスタPT82のゲートに、それぞれ、VBB-Vtよりも低い電位(VBB-Vt)を有するシフト信号SR2およびSR3が供給される。これにより、論理合成回路部821のトランジスタPT81およびPT82を介してダミーゲート線に出力されるシフト出力信号Dummypの電位が、VBBからトランジスタPT81およびPT82のしきい値電圧(Vt)分だけ上昇するのが抑制される。

10

#### 【0172】

また、第4実施形態では、上記のように、リセットトランジスタPT39およびPT49を設けるとともに、スタート信号STVに応答してトランジスタPT39およびPT49をオンさせることによって、ゲート線に意図しないタイミングでシフト出力信号が出力されるのを抑制することができるなどの上記第3実施形態と同様の効果を得ることができる。

20

#### 【0173】

##### (第5実施形態)

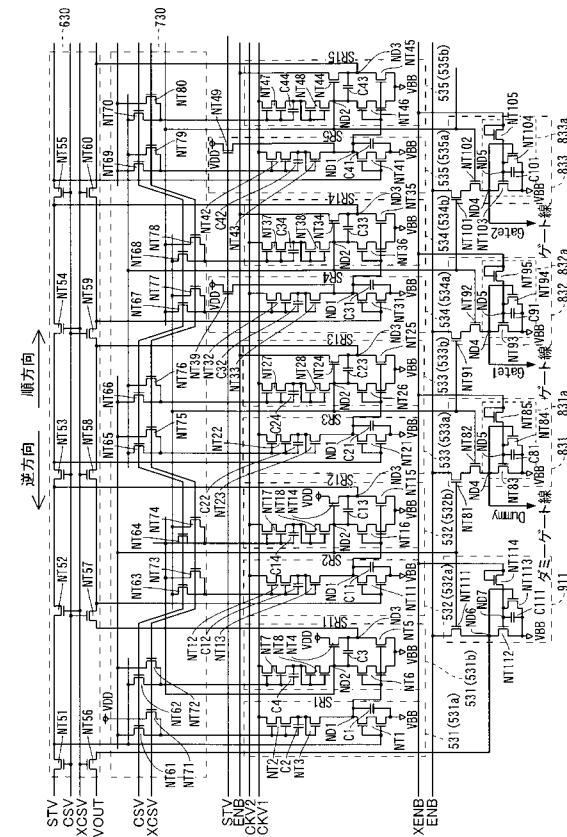

図11は、本発明の第5実施形態による液晶表示装置のVドライバ内部の回路図である。図11を参照して、この第5実施形態では、上記第1実施形態の構成において、3段目以降のシフトレジスタ回路部の出力信号が出力されるノードに接続されたトランジスタのドレインに共通のイネーブル信号を供給する場合について説明する。

#### 【0174】

すなわち、この第5実施形態によるVドライバでは、図11に示すように、複数段のシフトレジスタ回路部531～535と、走査方向切替回路部630と、入力信号切替回路部730と、複数段の論理合成回路部831～833と、回路部911とが設けられている。なお、図11では、図面の簡略化のため、5段分のシフトレジスタ回路部531～535および3段分の論理合成回路部831～833のみを図示しているが、実際は画素数に応じた数のシフトレジスタ回路部および論理合成回路部が設けられている。

30

#### 【0175】

そして、1段目のシフトレジスタ回路部531は、図2に示した第1実施形態の1段目のシフトレジスタ回路部51の第1回路部51aおよび第2回路部51bと同様の回路構成を有する第1回路部531aおよび第2回路部531bによって構成されている。また、2段目のシフトレジスタ回路部532は、図2に示した第1実施形態の2段目のシフトレジスタ回路部52の第1回路部52aおよび第2回路部52bと同様の回路構成を有する第1回路部532aおよび第2回路部532bによって構成されている。

40

#### 【0176】

ここで、第5実施形態では、3段目のシフトレジスタ回路部533、4段目のシフトレジスタ回路部534および5段目のシフトレジスタ回路部535のそれぞれに、イネーブル信号線(ENB)が接続されている。具体的には、3段目のシフトレジスタ回路部533は、第1回路部533aと第2回路部533bによって構成されている。第1回路部533aおよび第2回路部533bは、それぞれ、図2に示した第1実施形態の3段目のシフトレジスタ回路部53の第1回路部53aおよび第2回路部53bと同様の回路構成を有する。そして、この第5実施形態では、トランジスタNT24のドレインに、イネー

50

ブル信号線(ENB)が接続されている。

【0177】

また、4段目のシフトレジスタ回路部534は、第1回路部534aと第2回路部534bとによって構成されている。第1回路部534aおよび第2回路部534bは、それぞれ、図2に示した第1実施形態の4段目のシフトレジスタ回路部54の第1回路部54aおよび第2回路部54bと同様の回路構成を有する。そして、この第5実施形態では、トランジスタNT34のドレインに、イネーブル信号線(ENB)が接続されている。また、5段目のシフトレジスタ回路部535は、第1回路部535aと第2回路部535bとによって構成されている。第1回路部535aおよび第2回路部535bは、それぞれ、図2に示した第1実施形態の5段目のシフトレジスタ回路部55の第1回路部55aおよび第2回路部55bと同様の回路構成を有する。そして、この第5実施形態では、トランジスタNT44のドレインに、イネーブル信号線(ENB)が接続されている。10

【0178】

また、走査方向切替回路部630は、図2に示した第1実施形態の走査方向切替回路部60と同様の回路構成を有する。また、第5実施形態の入力信号切替回路部730は、図2に示した第1実施形態の入力信号切替回路部70と同様の回路構成を有する。また、第5実施形態の論理合成回路部831～833は、図2に示した第1実施形態の論理合成回路部81～83と同様の回路構成を有する。また、論理合成回路部831～833は、それぞれ、図2に示した第1実施形態の電位固定回路部81a～83aと同様の回路構成を有する電位固定回路部831a～833aを備えている。また、回路部911は、図2に示した第1実施形態の回路部91と同様の回路構成を有する。20

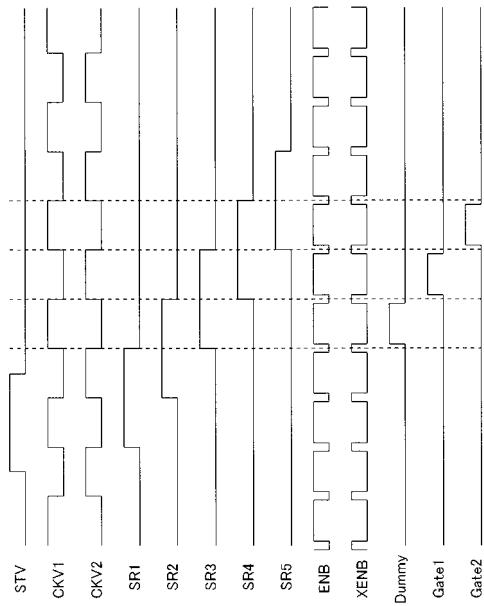

【0179】

図12は、本発明の第5実施形態による液晶表示装置のVドライバの動作を説明するための電圧波形図である。次に、図11および図12を参照して、第5実施形態によるVドライバの動作について説明する。

【0180】

この第5実施形態によるVドライバの動作は、基本的には、上記第1実施形態によるVドライバの動作と同様である。ただし、この第5実施形態によるVドライバでは、上記第1実施形態と異なり、3段目以降のシフトレジスタ回路部533～535の出力信号SR13～SR15が出力されるノードND3に接続されたトランジスタNT24～NT44のドレインに、共通のイネーブル信号ENBを供給する。30

【0181】

具体的には、1段目および2段目のシフトレジスタ回路部531および532(図11参照)における動作は、図2に示した第1実施形態による1段目および2段目のシフトレジスタ回路部51および52における動作と同様である。そして、2段目のシフトレジスタ回路部532からHレベル(VDD+V<sub>t</sub>)のシフト信号SR2がトランジスタNT66のドレインに入力される。これにより、ゲートにVDDの電位の走査方向切替信号CSVが入力されることによりオンしているトランジスタNT66のソース電位は、(VDD-V<sub>t</sub>)の電位になる。このため、3段目のシフトレジスタ回路部533のトランジスタNT27のゲートに(VDD-V<sub>t</sub>)の電位が入力される。40

【0182】

また、トランジスタNT21のゲートにHレベル(VDD)の出力信号SR12が入力される。また、トランジスタNT22のゲートには、4段目のシフトレジスタ回路部534からLレベルのシフト信号SR4が入力される。これにより、トランジスタNT21およびNT27は、オン状態になるとともに、トランジスタNT22はオフ状態になる。このため、トランジスタNT21を介して負側電位VBBからLレベルの電位が供給されることにより、3段目のシフトレジスタ回路部533のノードND1の電位はLレベルに低下する。これにより、トランジスタNT25およびNT26は、オフ状態になる。この状態で、トランジスタNT27のドレインに入力されるクロック信号CKV1がLレベルからHレベルに上昇する。これにより、3段目のシフトレジスタ回路部533のノードND

2 の電位はHレベルに上昇するので、トランジスタNT24はオン状態になる。このとき、トランジスタNT24のドレインにLレベルのイネーブル信号ENBが供給されているので、トランジスタNT24のソース電位(ノードND3の電位)はLレベルに保持される。

#### 【0183】

この後、第5実施形態では、イネーブル信号ENBの電位がLレベルからHレベルに上昇する。これにより、3段目のシフトレジスタ回路部533のノードND3の電位がHレベルに上昇する。この際、3段目のシフトレジスタ回路部533のノードND2の電位は、容量C23によってトランジスタNT24のゲート-ソース間電圧が維持されるようになり、ノードND3の電位の上昇に伴ってブーストされることにより上昇する。これにより、3段目のシフトレジスタ回路部533のノードND2の電位がVDDよりもしきい値電圧(Vt)以上の所定の電圧(V)分高い電位(VDD+Vt > VDD+V)まで上昇する。なお、このときのノードND2の電位(VDD+Vt)は、1段目および2段目のシフトレジスタ回路部511および512において、上昇した後のノードND2の電位(VDD+Vt)よりもさらに高い電位となる。そして、3段目のシフトレジスタ回路部533のノードND2からVDD+Vt以上の電位(VDD+Vt)を有するHレベルのシフト信号SR3が出力される。そして、4段目以降のシフトレジスタ回路部534および535においても、上記した3段目のシフトレジスタ回路部533と同様の動作により、上記第1実施形態によるシフトレジスタ回路部から出力されるHレベル(VDD+Vt)のシフト信号よりもさらに高いVDD+Vt以上の電位(VDD+Vt)を有するHレベルのシフト信号SR4およびSR5が出力される。

#### 【0184】

そして、3段目のシフトレジスタ回路部513のHレベル(VDD+Vt > VDD+Vt)のシフト信号SR3は、トランジスタNT63およびNT68のドレインにそれぞれ入力される。これにより、ゲートにVDDの電位の走査方向切替信号CSVが入力されることによりオンしているトランジスタNT63およびNT68のソース電位は、共に、(VDD-Vt)の電位になる。このため、2段目のシフトレジスタ回路部532のトランジスタNT12のゲートと、4段目のシフトレジスタ回路部534のトランジスタNT37のゲートとに(VDD-Vt)の電位が入力される。この状態で、クロック信号CKV2がLレベル(VBB)からHレベル(VDD)に立ち上がることにより、2段目のシフトレジスタ回路部532のトランジスタNT12では、容量C12によりゲート-ソース間電圧が保持されながら、ゲート電位が(VDD-Vt)からVDDとVBBとの電位差分上昇する。これにより、トランジスタNT12のノードND1側に発生する電位がVDDからトランジスタNT12のしきい値電圧(Vt)分低下するのが抑制される。このため、2段目のシフトレジスタ回路部532のノードND1に生じるHレベルの電位が低下するのが抑制される。また、4段目のシフトレジスタ回路部534のトランジスタNT37のゲートに(VDD-Vt)の電位が入力された状態で、クロック信号CKV2がLレベル(VBB)からHレベル(VDD)に立ち上がることにより、トランジスタNT37では、容量C34によりゲート-ソース間電圧が保持されながら、ゲート電位が(VDD-Vt)からVDDとVBBとの電位差分上昇する。これにより、トランジスタNT37のノードND2側に発生する電位がVDDからトランジスタNT37のしきい値電圧(Vt)分低下するのが抑制される。このため、4段目のシフトレジスタ回路部534のノードND2に生じるHレベルの電位が低下するのが抑制される。上記のようにして、各段のシフトレジスタ回路部において、クロック信号CKV1またはCKV2の電位がHレベル(VDD)に上昇するのに伴って、ノードND1またはND2の電位が上昇する場合に、ノードND1およびND2に生じるHレベルの電位が低下するのが抑制される。

#### 【0185】

また、3段目のシフトレジスタ回路部533のHレベル(VDD+Vt)のシフト信号SR3は、1段目のゲート線に繋がる論理合成回路部832のトランジスタNT91のゲートにも入力される。また、1段目のゲート線に繋がる論理合成回路部832のトランジ

10

20

30

40

50

スタ N T 9 2 のゲートには、4段目のシフトレジスタ回路部のHレベル( V D D + V )のシフト信号S R 4 が入力される。これにより、1段目のゲート線に繋がる論理合成回路部8 3 2において、トランジスタN T 9 1のドレインに入力されるイネーブル信号E N Bの電位がHレベル( V D D )の電位に上昇した場合に、ノードN D 4に発生する電位がV D D からトランジスタN T 9 1およびN T 9 2のしきい値電圧( V t )分低下するのが抑制される。このようにして、2段目以降のゲート線に繋がる論理合成回路部においても同様に、イネーブル信号E N Bの電位がHレベル( V D D )に上昇するのに伴って、ノードN D 4の電位が上昇する場合に、ノードN D 4に生じるHレベルの電位が低下するのが抑制される。これにより、各段のゲート線に出力されるシフト出力信号G a t e 1およびG a t e 2のHレベルの電位が低下するのが抑制される。

10

#### 【 0 1 8 6 】

第5実施形態によるVドライバの上記以外の動作は、上記第1実施形態によるVドライバの動作と同様である。

#### 【 0 1 8 7 】