**【特許請求の範囲】****【請求項 1】**

基板と、

前記基板上に形成されるゲート線と、

前記基板上に形成され、前記ゲート線と交差するデータ線と、

前記基板上に形成される画素電極とを含み、

前記画素電極は、

前記ゲート線に平行な第1主辺と、

前記データ線に平行な第2主辺と、

前記第1主辺の一部に連続し前記第1主辺と所定角度をなす第1斜辺と、

10

前記第1斜辺に連続し前記第1斜辺と所定角度をなし、更に前記第2主辺に所定角度をなして連続する第2斜辺とを含み、

前記第1主辺と第1斜辺とがなす第1斜角と前記第1主辺と第2斜辺とがなす第2斜角は互いに異なる液晶表示装置。

**【請求項 2】**

前記第1主辺と前記第2斜辺がなす角は0～45°であり、前記第2斜辺と前記第1斜辺がなす角は0～45°である請求項1に記載の液晶表示装置。

**【請求項 3】**

前記第1主辺、前記第2斜辺、前記第1斜辺及び前記第2主辺は、順に隣接する請求項2に記載の液晶表示装置。

20

**【請求項 4】**

前記第2斜辺は前記ゲート線と隣接する請求項1に記載の液晶表示装置。

**【請求項 5】**

前記画素電極と対向する共通電極をさらに含み、

前記共通電極には前記第1斜辺と実質的に平行な第1切開部が形成されている請求項1に記載の液晶表示装置。

**【請求項 6】**

前記画素電極に前記第1斜辺と実質的に平行な第2切開部が形成される請求項1に記載の液晶表示装置。

30

**【請求項 7】**

前記第2斜辺の少なくとも一部と重畳する維持電極線をさらに含む請求項1に記載の液晶表示装置。

**【請求項 8】**

前記画素電極は、間隙を間に置いて互いに離間している第1及び第2副画素電極を含む請求項1に記載の液晶表示装置。

**【請求項 9】**

前記間隙は前記第1斜辺と平行な斜線部を含む請求項8に記載の液晶表示装置。

**【請求項 10】**

第1副画素電極と前記第2副画素電極の電圧は互いに異なる請求項8に記載の液晶表示装置。

40

**【請求項 11】**

前記第1副画素電極と前記第2副画素電極は、1つの画像情報から得られた互いに異なるデータ電圧の印加を受ける請求項10に記載の液晶表示装置。

**【請求項 12】**

前記第1副画素電極に接続される第1薄膜トランジスタと、

前記第2副画素電極に接続される第2薄膜トランジスタと、

前記第1薄膜トランジスタに接続される第1信号線と、

前記第2薄膜トランジスタに接続される第2信号線と、

前記第1及び第2薄膜トランジスタに接続され、前記第1及び第2信号線と交差する第3信号線とをさらに含む請求項11に記載の液晶表示装置。

50

**【請求項 1 3】**

前記第1及び第2薄膜トランジスタは、各々前記第1及び第2信号線からの信号によってターンオンして前記第3信号線からの信号を伝達する請求項12に記載の液晶表示装置。

**【請求項 1 4】**

前記第1及び第2薄膜トランジスタは、各々前記第3信号線からの信号によってターンオンして前記第1及び第2信号線からの信号を伝達する請求項12に記載の液晶表示装置。

**【請求項 1 5】**

前記第1副画素電極と前記第2副画素電極は容量性結合する請求項10に記載の液晶表示装置。

10

**【請求項 1 6】**

前記第1副画素電極に接続される第1薄膜トランジスタと、

前記第1薄膜トランジスタに接続される第1信号線と、

前記第1薄膜トランジスタに接続され、前記第1信号線と交差する第1信号線とをさらに含む請求項15に記載の液晶表示装置。

20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は液晶表示装置に関する。

**【背景技術】****【0002】**

液晶表示装置は、現在最も広く使用されている平板表示装置（フラットパネルディスプレイ）のうちの1つであって、画素電極と共に電場生成電極が形成されている2枚の表示板とその間に挟持された液晶層とからなり、電場生成電極に電圧を印加して液晶層に電場を生成し、これを通じて液晶層の液晶分子の配向を決定し、入射光の偏光を制御することによって画像を表示する。

30

**【0003】**

また、液晶表示装置は、各画素電極に接続されているスイッチング素子及びスイッチング素子を制御して画素電極に電圧を印加するためのゲート線とデータ線などの複数の信号線を含む。

このような液晶表示装置の中でも、電場が印加されない状態で液晶分子の長軸を表示板に対して垂直をなすように配列した垂直配向方式（vertically aligned mode）の液晶表示装置は、コントラスト比が大きく、基準視野角が広いので脚光を浴びている。

**【0004】**

垂直配向方式の液晶表示装置で広い基準視野角を実現するための具体的な方法としては、電場生成電極に切開部を形成する方法と、電場生成電極上に突起を形成する方法などがある。切開部及び突起は、液晶分子が傾く方向（tilt direction）を決定し、これらを適切に配置して液晶分子の傾斜方向を複数方向に分散することによって基準視野角を広くすることができる。

40

**【0005】**

このような液晶表示装置では輝度を高めるために、液晶層にかかる電場の強さを大きくすることもある。このために画素電極に印加する電圧を高くし、これによって画素電極に印加される電圧を伝達するデータ線と、画素電極の間に形成される電場も大きくなる。このような電場は、画素電極の周縁近傍に位置した液晶分子の配列を乱し、その結果、液晶の応答時間が長くなるという問題がある。

50

**【0006】**

一方、突起や切開部が設けられる部分は光透過が難しいため、これらが多いほど開口率が低下する。しかし、開口率を高めるために突起や切開部の間の間隔を広げると、突起や切開部による効果は相対的に減少し、データ線による電場の乱れが大きくなつて応答時間が長くなる場合がある。

しかし、画素電極がゲート線及びデータ線に対して平行な長方形状に形成される液晶表示装置では、隣接した画素電極の間に生じる電場により液晶分子の配列が乱れてテキスチャ(*texture*)が発生し、その結果、透過率が減少し、画面の残像が増加する。

#### 【0007】

また、このようなテキスチャを減らすために共通電極の切開部に画素電極の辺と重畳する部分を設けたりもするが、この場合、開口率が減少するという問題が生じる。

10

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0008】

そこで、本発明は上記従来の問題点に鑑みてなされたものであつて、本発明の目的は、開口率及び透過率を高め、残像発生を防止することである。

#### 【課題を解決するための手段】

#### 【0009】

上記目的を達成するためになされた本発明による液晶表示装置は、基板と、前記基板上に形成されているゲート線と、前記基板上に形成され、前記ゲート線と交差するデータ線と、前記基板上に形成されている画素電極とを含み、前記画素電極は、前記ゲート線に平行な第1主辺と、前記データ線に平行な第2主辺と、前記第1主辺の一部に連続し前記第1主辺と所定角度をなす第1斜辺と、前記第1斜辺に連続し前記第1斜辺と所定角度をなし、更に前記第2主辺に所定角度をなして連続する第2斜辺とを含み、前記第1主辺と第1斜辺とがなす第1斜角と前記第1主辺と第2斜辺とがなす第2斜角は互いに異なる。

20

#### 【0010】

前記第1主辺と前記第2斜辺がなす角は0～45°であり、前記第2斜辺と前記第1斜辺がなす角は0～45°であることが好ましい。

前記第1主辺、前記第2斜辺、前記第1斜辺及び前記第2主辺は順に隣接することが好ましい。

前記第2斜辺は前記ゲート線と隣接することが好ましい。

30

#### 【0011】

前記画素電極と対向する共通電極をさらに含み、前記共通電極に前記第1斜辺と実質的に平行な第1切開部が形成されることが好ましい。

前記画素電極に前記第1斜辺と実質的に平行な第2切開部が形成されることが好ましい。

。

前記第2斜辺の少なくとも一部と重畳する維持電極線をさらに含むことが好ましい。

#### 【0012】

前記画素電極は、間隙を間に置いて互いに離間している第1及び第2副画素電極を含むことが好ましい。

前記間隙は、前記第1斜辺と平行な斜線部を含むことが好ましい。

40

第1副画素電極と前記第2副画素電極の電圧は互いに異なることが好ましい。

前記第1副画素電極と前記第2副画素電極は、1つの画像情報から得られた互いに異なるデータ電圧の印加を受けることが好ましい。

#### 【0013】

前記第1副画素電極に接続される第1薄膜トランジスタ、前記第2副画素電極に接続される第2薄膜トランジスタ、前記第1薄膜トランジスタに接続される第1信号線、前記第2薄膜トランジスタに接続される第2信号線、並びに、前記第1及び第2薄膜トランジスタに接続され、前記第1及び第2信号線と交差する第3信号線をさらに含むことが好ましい。

#### 【0014】

50

前記第1及び第2薄膜トランジスタは、各々前記第1及び第2信号線からの信号によってターンオン（導通）して前記第3信号線からの信号を伝達することが好ましい。

前記第1及び第2薄膜トランジスタは、各々前記第3信号線からの信号によってターンオンして前記第1及び第2信号線からの信号を伝達することが好ましい。

前記第1副画素電極と前記第2副画素電極は、容量性結合することが好ましい。

#### 【0015】

前記第1副画素電極に接続される第1薄膜トランジスタ、前記第1薄膜トランジスタに接続される第1信号線、前記第1薄膜トランジスタに接続され、前記第1信号線と交差する第1信号線をさらに含むことが好ましい。

10

#### 【発明の効果】

#### 【0016】

本発明によれば、液晶分子のテキスチャの発生を防止して透過率を高め、液晶表示装置の応答速度を向上させるという効果がある。

#### 【発明を実施するための最良の形態】

#### 【0017】

本発明に係る液晶表示装置を実施するための最良の形態の具体例を図面を参照しながら説明する。本発明は、多様な形態で実現することができ、ここで説明する実施形態に限定されるものではない。図面は、各種層及び領域を明確に表現するために、厚さを拡大して示している。明細書全体を通じて類似した部分については同一の参照符号を付けている。層、膜、領域、板などの部分が、他の部分の「上に」あるとするとき、これは他の部分の「すぐ上に」ある場合に限らず、その中間に更に他の部分がある場合も含む。逆に、ある部分が他の部分の「すぐ上に」あるとするとき、これは中間に他の部分がない場合を意味する。

20

#### 【0018】

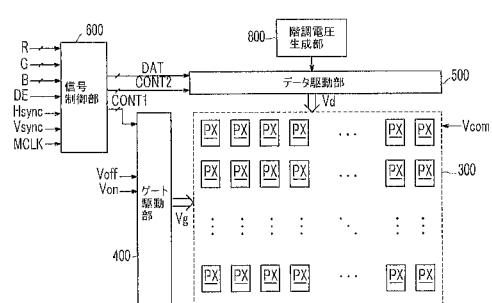

まず、図1及び図2を参照して本発明の一実施形態に係る液晶表示装置について詳細に説明する。

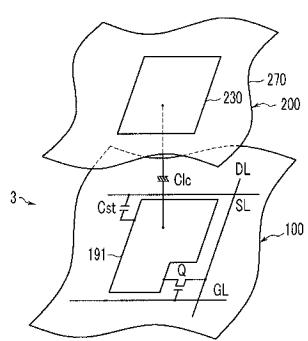

図1は、本発明の一実施形態に係る液晶表示装置のブロック図であり、図2は、本発明の一実施形態に係る液晶表示装置の画素に対する等価回路図である。

図1に示すように、本発明の一実施形態に係る液晶表示装置は、液晶表示板組立体（liquid crystal panel assembly）300、これに接続されるゲート駆動部400及びデータ駆動部500、データ駆動部500に接続される階調電圧生成部800、並びにこれらを制御する信号制御部600を含む。

30

#### 【0019】

液晶表示板組立体300は、等価回路的に複数の信号線（図示せず）とこれに接続されほぼ行列状に配列された複数の画素（pixel）（PX）を含む。これに対し、図2に示した構造のように、液晶表示板組立体300は、互いに対向する下部及び上部表示板100、200とその間に挟持された液晶層3を含む。

信号線は、ゲート信号（走査信号とも言う）を伝達する複数のゲート線（図示せず）とデータ信号を伝達する複数のデータ線（図示せず）とを含む。ゲート線はほぼ行方向に延びて互いにほぼ平行であり、データ線はほぼ列方向に延びて互いにほぼ平行である。

40

#### 【0020】

図2に示すように、各画素（PX）、例えば、ゲート線（GL）とデータ線（DL）に接続される画素（PX）は、信号線（GL、DL）に接続されるスイッチング素子（Q）と、これに接続される液晶キャパシタ（liquid crystal capacitor）（CLC）及びストレージキャパシタ（storage capacitor）（CST）を含む。ストレージキャパシタ（CST）は必要に応じて省略することもできる。

#### 【0021】

スイッチング素子（Q）は、下部表示板100に設けられている薄膜トランジスタなどの三端子素子であって、その制御端子はゲート線（GL）に接続されており、入力端子はデータ線（DL）に接続されており、出力端子は液晶キャパシタ（CLC）及びストレー

50

ジキャパシタ (Cst) に接続されている。

液晶キャパシタ (C1c) は、下部表示板 100 の画素電極 191 と上部表示板 200 の共通電極 270 を 2 つの端子とし、2 つの電極 (191, 270) の間の液晶層 3 は誘電体として機能する。画素電極 191 は、スイッチング素子 (Q) に接続され、共通電極 270 は、上部表示板 200 の全面に形成されて共通電圧 (Vcom) の印加を受ける。図 2 と異なり、共通電極 270 が下部表示板 100 に設けられる場合もあり、その場合には 2 つの電極 (191, 270) のうちの少なくとも 1 つを線形状または棒形状に形成してもよい。

#### 【0022】

液晶キャパシタ (C1c) の補助的役割を果たすストレージキャパシタ (Cst) は、下部表示板 100 に設けられた別の維持電極線 (SL) と画素電極 191 が絶縁体を介在して重畠することによって構成され、共通電圧 (Vcom) などの定められた電圧の印加により所定の電圧を維持する。しかし、ストレージキャパシタ (Cst) は、画素電極 191 が絶縁体を媒介としてすぐ上の前段ゲート線との重畠により形成することも可能である。

#### 【0023】

一方、色表示を実現するために、各画素 (PX) が基本色のうちの 1 つを固有に表示する空間分割方式、各画素 (PX) が時間によって交互に基本色を表示する時間分割方式などの方式により、これら基本色の空間的、時間的作用で所望の色が認識されるように構成できる。基本色の例としては赤色、緑色、青色などの三原色がある。図 2 は、空間分割の一例であって、各画素 (PX) が画素電極 191 に対応する上部表示板 200 の領域に基本色のうちの 1 つを示すカラーフィルタ 230 を備えている。図 2 と異なり、カラーフィルタ 230 は、下部表示板 100 の画素電極 191 の上または下に形成することもできる。

#### 【0024】

液晶表示板組立体 300 の外側面には光を偏光させる少なくとも 1 つの偏光子 (図示せず) が取り付けられている。

さらに、図 1 に示す階調電圧生成部 800 は、画素 (PX) の透過率に関連する複数の階調電圧 (または基準階調電圧) を生成する。

ゲート駆動部 400 は、液晶表示板組立体 300 のゲート線に接続されてゲートオン電圧 (Von) とゲートオフ電圧 (Voff) の組み合わせからなるゲート信号 (Vg) をゲート線に印加する。

#### 【0025】

データ駆動部 500 は、液晶表示板組立体 300 のデータ線に接続され、階調電圧生成部 800 からの階調電圧を選択し、これをデータ信号としてデータ線に印加する。階調電圧生成部 800 が全体階調に対する電圧を全て提供するのではなく、決められた数の基準階調電圧のみを提供する場合は、データ駆動部 500 は基準階調電圧を分圧して全体階調に対する階調電圧を生成し、その中からデータ信号を選択するように構成することもできる。

#### 【0026】

信号制御部 600 は、ゲート駆動部 400 及びデータ駆動部 500 などを制御する。

このような駆動装置 (400, 500, 600, 800) の各々は、少なくとも 1 つの集積回路チップの形態で液晶表示板組立体 300 上に直接装着することができ、フレキシブル印刷回路フィルム (flexible printed circuit film) (図示せず) 上に装着して TCP (tape carrier package) の形態で液晶表示板組立体 300 に付着することもでき、別の印刷回路基板 (printed circuit board) (図示せず) 上に装着することもできる。これと異なり、これらの駆動装置 (400, 500, 600, 800) を液晶表示板組立体 300 に集積することもできる。また、駆動装置 (400, 500, 600, 800) は単一チップで集積することもでき、これら駆動装置の少なくとも 1 つまたはこれら駆動装置を構成する少

10

20

30

40

50

なくとも 1 つの回路素子を当該单一チップの外側に位置して設けることもできる。

#### 【 0 0 2 7 】

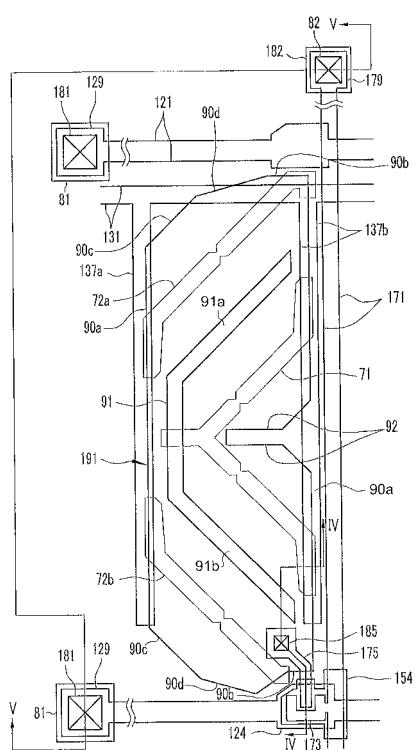

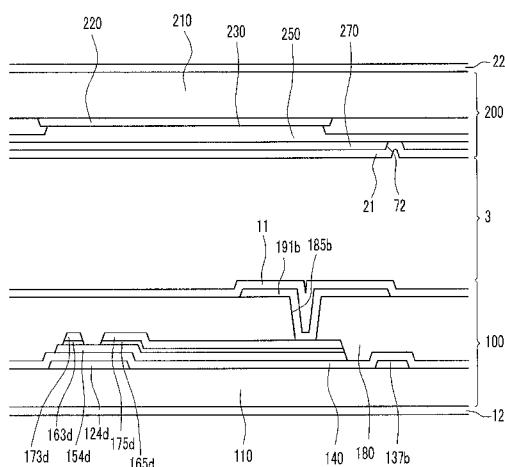

次に、図 3 ~ 図 6 a、並びに図 1 及び図 2 を参照して本発明の一実施形態に係る液晶表示板組立体について詳細に説明する。

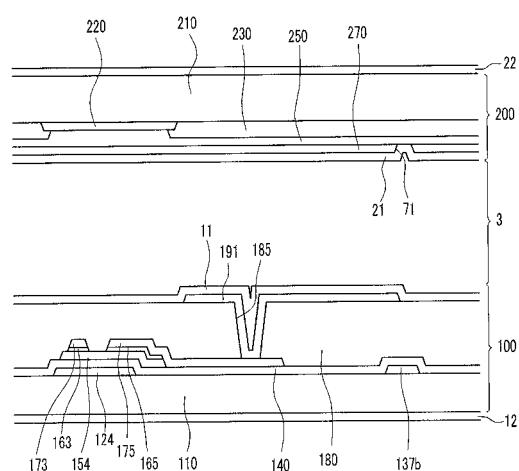

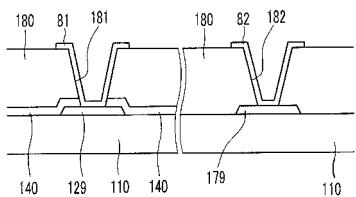

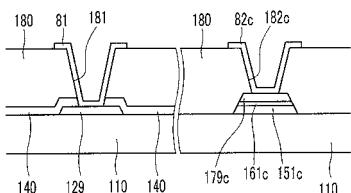

図 3 は、本発明の一実施形態に係る液晶表示板組立体の配置図であり、図 4 及び図 5 は、各々図 3 に示す液晶表示板組立体の IV-IV 及び V-V 線に沿った断面図であり、図 6 a は、本発明の一実施形態に係る液晶表示板組立体の一部分を液晶分子の傾く方向と共に示す図である。

#### 【 0 0 2 8 】

図 3、図 4 及び図 5 に示すように、本発明の実施形態に係る液晶表示板組立体は、互いに對向する下部表示板 100 と上部表示板 200、及びこれらの 2 つの表示板 100、200 の間に挟持された液晶層 3 を含む。まず、下部表示板 100 について説明する。

透明なガラスまたはプラスチックなどからなる絶縁基板 110 上に複数のゲート線 121 及び複数の維持電極線 131 を含むゲート導電体が形成されている。ゲート線 121 は、ゲート信号を伝達し、主に図の横方向に延びている。各ゲート線 121 は上下に突出した複数のゲート電極 124 と、他の層または外部駆動回路との接続のために幅が広く形成された端部 129 を含む。ゲート信号を生成するゲート駆動回路（図示せず）は、基板 110 上に取り付けられるフレキシブル印刷回路フィルム（図示せず）上に装着することができ、また基板 110 上に直接装着することもでき、基板 110 に集積することも可能である。ゲート駆動回路が基板 110 上に集積される場合、ゲート線 121 を延長してこれと直接接続することが可能である。

#### 【 0 0 2 9 】

維持電極線 131 は、所定電圧の印加を受けるものであって、ゲート線 121 とほぼ平行に延長される幹線と、これから分岐した複数の第 1 及び第 2 維持電極（137a、137b）を含む。維持電極線 131 の各々は、隣接した 2 つのゲート線 121 の間に位置する。第 1 及び第 2 維持電極（137a、137b）は、図の縦方向に延びて互いに對向する。維持電極線 131 の形状及び配置は多様に変更することが可能であり、図示した者に限定するものではない。

#### 【 0 0 3 0 】

ゲート導電体 121、131 は、アルミニウム（Al）やアルミニウム合金などアルミニウム系金属、銀（Ag）や銀合金など銀系金属、銅（Cu）や銅合金など銅系金属、モリブデン（Mo）やモリブデン合金などモリブデン系金属、クロム（Cr）、タンタル（Ta）及びチタニウム（Ti）などで形成することができる。これらは物理的性質が異なる 2 つの導電膜（図示せず）を含む多重膜構造とすることもできる。このうちの 1 つの導電膜は、信号遅延や電圧降下を減らすことができるよう比抵抗（resistivity）の低い金属、例えば、アルミニウム系金属、銀系金属、銅系金属などで形成できる。もう 1 つの導電膜は、他の物質、特に ITO（indium tin oxide）及びIZO（indium zinc oxide）との物理的、化学的、電気的接触特性に優れた物質、例えばモリブデン系金属、クロム、タンタル、チタニウムなどで形成することができる。このような組み合わせの好適例には、クロム下部膜とアルミニウム（合金）上部膜及びアルミニウム（合金）下部膜とモリブデン（合金）上部膜がある。ゲート導電体（121、131）は、その他にも多様な金属または導電体で構成することができる。

#### 【 0 0 3 1 】

ゲート導電体（121、131）の側面は基板 110 面に対して傾斜しており、その傾斜角は約 30° ~ 約 80° であることが好ましい。

ゲート導電体（121、131）上に窒化ケイ素（SiNx）または酸化ケイ素（SiOx）などからなるゲート絶縁膜 140 が形成されている。

ゲート絶縁膜 140 上に水素化非晶質シリコン（非晶質シリコンは a-Si と略称する）または多結晶シリコン（polysilicon）などで構成される複数の島状半導体 154 が形成されている。半導体 154 は、ゲート電極 124 上に位置する。

10

20

30

40

50

## 【0032】

半導体154上に1対の島状オーミック接触部材(ohmic contact)(163、165)が形成されている。オーミック接触部材(163、165)は、リンなどのn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどの物質、または、シリサイド(silicide)で構成される。

また、半導体154とオーミック接触部材(163、165)の側面は、基板110面に対して傾斜しており、その傾斜角は30°～80°程度である。

## 【0033】

オーミック接触部材(163、165)及びゲート絶縁膜140上に複数のデータ線171と複数のドレイン電極175を含むデータ導電体が形成されている。10

データ線171は、データ信号を伝達し、主に図の縦方向に延長されてゲート線121及び維持電極線131と交差する。各データ線171は、ゲート電極124に向かってそれぞれ延長されてU字状に曲がった複数のソース電極173と、他の層またはデータ駆動部500との接続のために面積が広く形成された端部179を含む。データ駆動部500が基板110上に集積されている場合、データ線171が延びてこれと直接接続することができる。

## 【0034】

ドレイン電極175は、データ線171と分離されており、ゲート電極124を中心にソース電極173と対向する。各ドレイン電極175は、広い一端部と棒状の他端部を有しており、棒状の端部は、ソース電極173で一部囲まれている。20

1つのゲート電極124、1つのソース電極173及び1つのドレイン電極175は、半導体154と共に1つの薄膜トランジスタ(TFT)をなし、薄膜トランジスタのチャネル(channel)は、ソース電極173とドレイン電極175の間の半導体154に形成される。

## 【0035】

データ導電体(171、175)は、モリブデン、クロム、タンタル及びチタニウムなど耐火性金属(refractory metal)またはこれらの合金で形成されることが好ましく、耐火性金属膜(図示せず)と低抵抗導電膜(図示せず)を含む多重膜構造とすることができます。多重膜構造の例には、クロムまたはモリブデン(合金)下部膜とアルミニウム(合金)上部膜の二重膜、モリブデン(合金)下部膜とアルミニウム(合金)中間膜とモリブデン(合金)上部膜の三重膜がある。データ導電体(171、175)は、その他にも多様な金属または導電体で形成することができる。30

## 【0036】

また、データ導電体(171、175)は、その側面が基板110面に対して30°～80°程度の傾斜角で傾斜していることが好ましい。

オーミック接触部材(163、165)は、その下の半導体154とその上のデータ導電体(171、175)の間にのみ存在し、これらの間の接触抵抗を低くする。半導体154は、ソース電極173とドレイン電極175との間、およびその他の部分において、データ導電体(171、175)で覆われずに露出している部分がある。

## 【0037】

データ導電体(171、175)及び半導体154の露出している部分上に保護膜180が形成されている。保護膜180は、無機絶縁物または有機絶縁物などで構成され、表面が平坦化された構成とすることもできる。有機絶縁物は4.0以下の誘電定数を有することが好ましく、感光性を有することもできる。しかし、保護膜180は、有機膜の優れた絶縁特性を生かすとともに、下方に位置する半導体154の破損を防止するために、下部無機膜と上部有機膜との二重膜構造とすることができます。40

## 【0038】

保護膜180にデータ線171の端部179とドレイン電極175の一端を各々露出する複数のコンタクトホール(接触孔)(182、185)が形成されており、保護膜180とゲート絶縁膜140にはゲート線121の端部129をそれぞれ露出する複数のコン

タクトホール 181 が形成されている。

保護膜 180 上に複数の画素電極 191 及び複数の接触補助部材 (81、82) が形成されている。これらは ITO または IZO などの透明な導電物質やアルミニウム、銀、クロムまたはその合金などの反射性金属で形成することができる。

#### 【0039】

画素電極 191 は、コンタクトホール 185 を介してドレイン電極 175 と物理的、電気的に接続されており、ドレイン電極 175 からデータ電圧の印加を受ける。データ電圧が印加された画素電極 191 は、共通電圧の印加を受ける共通電極表示板 200 の共通電極 270 と共に電場を生成することにより、2つの電極 (191、270) の間の液晶層 3 の液晶分子の方向を決定する。このように決定された液晶分子の方向によって液晶層 3 を通過する光の偏光が変わる。画素電極 191 と共通電極 270 は、キャパシタ (以下、液晶キャパシタという) を構成し、薄膜トランジスタがターンオフした後にも印加された電圧を維持する。

#### 【0040】

画素電極 191 は、維持電極 (137a、137b) をはじめとする維持電極線 131 と重畳し、画素電極 191 が維持電極線 131 と重畳してなすキャパシタをストレージキャパシタといい、ストレージキャパシタは液晶キャパシタの電圧維持能力を強化する。

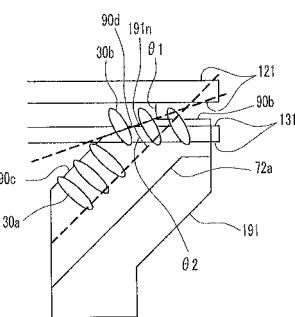

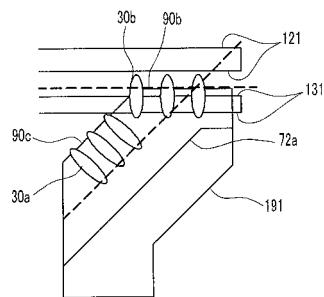

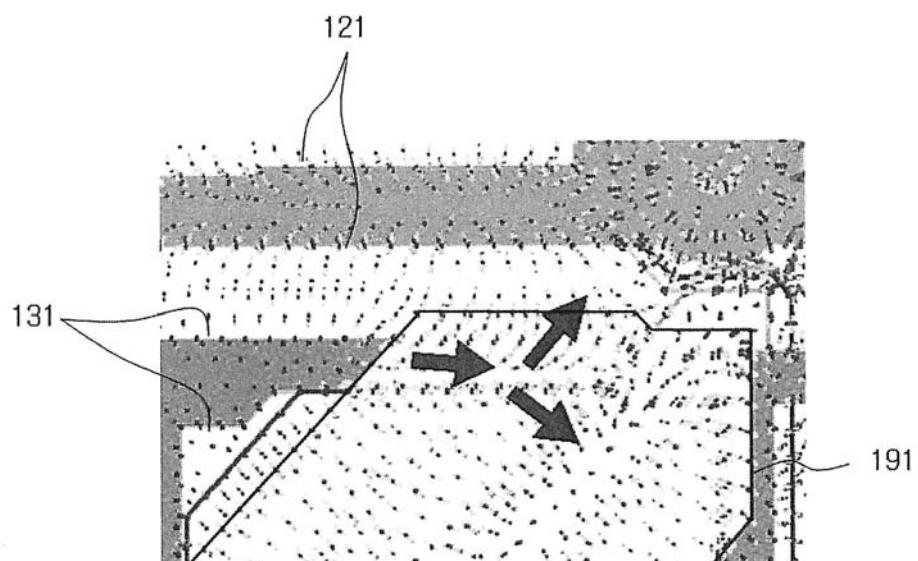

図 6a 及び図 3 に示すように、各画素電極 191 は、データ線 171 にほぼ平行な1対の縦辺 (90a)、ゲート線にほぼ平行な1対の横辺 (90b) を備えるほぼ四角形状に形成されている。

#### 【0041】

各画素電極 191 は、左側角部が面取り (chamfered) されて第 1 斜辺 90c をなす。第 1 斜辺 90c はゲート線 121 に対して約 45° の角度をなす。

第 1 斜辺 90c と横辺 90b の間は、第 2 斜辺 90d で連結されている。第 2 斜辺 90d は、ゲート線 121 と斜角 (-1) をなし、その斜角 (-1) は第 1 斜辺 90c がゲート線 121 となす斜角より小さい。第 2 斜辺 90d とゲート線 121 とがなす角度 (1) は 0 ~ 45° であり、第 2 斜辺 90d と第 1 斜辺 90c とがなす角度 (2) は 0 ~ 45° であることが好ましい。

#### 【0042】

画素電極 191 に第 1 中央切開部 91 及び第 2 中央切開部 92 が形成され、画素電極 191 は、これらの切開部 (91、92) によって複数の領域に分割される。切開部 (91、92) は、画素電極 191 を 2 等分する仮想の横中心線に対してほぼ反転対称をなす。

第 1 中央切開部 91 は、縦部及びこれに連結された1対の斜線部を含む。縦部は画素電極 191 の横中心線に垂直に短く延び、1対の斜線部は横部から画素電極 191 の右側辺に向かって第 1 斜辺 90c とほぼ平行に延びる上部切開部 91a 及び下部切開部 91b を備えている。

#### 【0043】

画素電極 191 の下半部は、第 1 中央切開部 91 の斜線部である下部切開部 91b によって 2 つの領域に分割され、上半部も第 1 中央切開部 91 の斜線部である上部切開部 91a によって 2 つの領域に分割される。このとき、領域の数または切開部の数は、画素電極 191 の大きさ、画素電極 191 の横辺と縦辺の長さ比、液晶層 3 の種類や特性などの設計要素によって変更することができる。

#### 【0044】

第 2 中央切開部 92 は、画素電極 191 の横中心線に沿って延びる横部を含む。

接触補助部材 (81、82) は、各々コンタクトホール 181、182 を介してゲート線 121 の端部 129 及びデータ線 171 の端部 179 に接続される。接触補助部材 (81、82) は、ゲート線 121 の端部 129 及びデータ線 171 の端部 179 と外部装置との接着性を補完し、これらを保護する。

#### 【0045】

次に、上部表示板 200 について説明する。

10

20

30

40

50

透明なガラスまたはプラスチックなどからなる絶縁基板 210 上に遮光部材 220 が形成されている。遮光部材 220 は、ブラックマトリックス (black matrix)とも呼ばれ、画素電極 191 の間の光漏れを防止する。この遮光部材 220 は、画素電極 191 と対向し、画素電極 191 とほぼ同一の形状を有する複数の開口部 (図示せず) を備える構成とすることも可能である。

#### 【0046】

さらに、基板 210 上には複数のカラーフィルタ 230 が形成されている。各カラーフィルタ 230 は、赤色、緑色及び青色の三原色など基本色のうちの 1 つを表示するように構成できる。

カラーフィルタ 230 及び遮光部材 220 上にオーバーコート層 (overcoat) 250 が形成されている。オーバーコート層 250 は絶縁物で形成することができ、カラーフィルタ 230 が露出するのを防止し、平坦面を提供する。オーバーコート層 250 は省略することもできる。

#### 【0047】

オーバーコート層 250 上には共通電極 270 が形成されている。共通電極 270 は、ITO、IZOなどの透明な導電体などからなり、共通電極 270 には複数の切開部 (71、72a、72b) 群が形成されている。

1つの切開部 (71~72b) 群は、1つの画素電極 191 と対向し、中央切開部 71、上部切開部 72a 及び下部切開部 72b を含む。切開部 (71~72b) のそれぞれは、画素電極 191 の隣接切開部 (91~92b) の間または切開部 (92a、92b) と画素電極 191 の面取りされた斜辺 (90a、90b) の間に配置されている。また、各切開部 (71~72b) は、画素電極 191 の上部切開部 92a または下部切開部 92b とほぼ平行に延びた少なくとも一つの斜線部を含む。切開部 (71~72b) は、画素電極 191 の横中心線に対してほぼ反転対称をなす。

#### 【0048】

上部及び下部切開部 (72a、72b) は、各々斜線部と横部及び縦部を含む。斜線部はほぼ画素電極 191 の上側または下側辺から左側辺に延びている。横部及び縦部は、斜線部の各端から画素電極 191 の辺に沿って辺と重畠しながら延びて斜線部と鈍角をなす。

中央切開部 71 は、中央横部、1対の斜線部及び1対の縦断縦部を含む。中央横部は、ほぼ画素電極 191 の左側辺から画素電極 191 の横中心線に沿って右側に延びている。1対の斜線部は、中央横部の端から画素電極 191 の右側辺に向かって中央横部と鈍角をなしながら、各々上部及び下部切開部 (72a、72b) とほぼ平行に延びている。縦断縦部は、該当斜線部の端から画素電極 191 の右側辺に沿って右側辺と重畠しながら延びて斜線部と鈍角をなす。

#### 【0049】

また、切開部 (71~72b) の数は設計要素によって変わり、遮光部材 220 が切開部 (71~72b) と重畠して切開部 (71~72b) 近傍の光漏れを遮断することができる。

少なくとも 1 つの切開部 (71~72b、91、92) は、突起 (protusion) (図示せず) や陥没部 (depression) (図示せず) で代替することができる。突起は有機物または無機物で形成することができ、電場生成電極 (191、270) の上または下に配置される。

#### 【0050】

表示板 100、200 の内側面には配向膜 (11、21) が形成され、これらは垂直配向膜であってもよい。

表示板 100、200 の外側面には偏光子 (12、22) が設けられているが、2つの偏光子 (12、22) の偏光軸は直交し、このうちの 1 つの偏光軸はゲート線 (121) に対して平行であることが好ましい。反射型液晶表示装置の場合には、2つの偏光子 (12、22) の 1 つを省略してもよい。

10

20

30

40

50

## 【0051】

液晶表示装置は、偏光子(12、22)、位相遅延膜、表示板(100、200)及び液晶層3に光を供給する照明部(図示せず)を含んでもよい。

液晶層3は負の誘電率異方性を有し、液晶層3の液晶分子は、電場のない状態でその長軸が2つの表示板の表面に対して垂直をなすように配向されている。

次に、このような液晶表示装置の動作を詳細に説明する。

## 【0052】

信号制御部600は、外部のグラフィック制御部(図示せず)から入力画像信号(R、G、B)及びその表示を制御する入力制御信号を受信する。入力画像信号(R、G、B)は、各画素(PX)の輝度(luminance)情報を含み、輝度は決められた数、例えば、1024( $=2^{10}$ )、256( $=2^8$ )または64( $=2^6$ )個の階調(gray)を有している。入力制御信号の例には、垂直同期信号(Vsync)と水平同期信号(Hsync)、メインクロック(MCLK)、データタイネーブル信号(DE)などがある。

10

## 【0053】

信号制御部600は、入力画像信号(R、G、B)と入力制御信号に基づいて入力画像信号(R、G、B)を液晶表示板組立体300及びデータ駆動部500の動作条件に合うように適切に処理し、ゲート制御信号(CONT1)及びデータ制御信号(CONT2)などを生成した後、ゲート制御信号(CONT1)をゲート駆動部400に送出し、データ制御信号(CONT2)と処理した画像信号(DAT)をデータ駆動部500に出力する。出力画像信号(DAT)はデジタル信号として決められた数の値(または階調)を有する。

20

## 【0054】

ゲート制御信号(CONT1)は、走査開始を指示する走査開始信号(STV)とゲートオン電圧(Von)の出力周期を制御する少なくとも1つのクロック信号を含む。また、ゲート制御信号(CONT1)は、ゲートオン電圧(Von)の持続時間を限定する出力イネーブル信号(OE)をさらに含んでもよい。

データ制御信号(CONT2)は、1つの束の副画素に対する画像データの転送開始を知らせる水平同期開始信号(STH)と液晶表示板組立体300にデータ信号の印加を指示するロード信号(Load)及びデータクロック信号(HCLK)を含む。さらに、データ制御信号(CONT2)は、共通電圧(Vcom)に対するデータ信号の電圧極性(以下、共通電圧に対するデータ信号の電圧極性を略してデータ信号の極性という)を反転させる反転信号(RVS)をさらに含んでもよい。

30

## 【0055】

信号制御部600からのデータ制御信号(CONT2)によって、データ駆動部500は、1つの束の副画素に対するデジタル画像信号(DAT)を受信し、各デジタル画像信号(DAT)に対応する階調電圧を選択することによってデジタル画像信号(DAT)をアナログデータ信号に変換した後、これを該当データ線に印加する。

ゲート駆動部400は、信号制御部600からのゲート制御信号(CONT1)によってゲートオン電圧(Von)をゲート線に印加して、このゲート線に接続されたスイッチング素子をターンオンさせる。その結果、データ線に印加されたデータ信号がターンオンしたスイッチング素子を介して該当画素に印加される。

40

## 【0056】

1水平周期(1Hともいい、水平同期信号Hsync及びデータタイネーブル信号DEの一周期と同一である。)を単位として該当過程を繰り返すことによって、全体画素(PX)にデータ信号を印加して1フレーム(frame)の画像を表示する。

1フレームが終了すれば次のフレームが開始され、各画素(PX)に印加されるデータ信号の極性が直前フレームでの極性と反対になるようにデータ駆動部500に印加される反転信号(RVS)の状態が制御される(フレーム反転)。このとき、1フレーム内でも反転信号(RVS)の特性によって1つのデータ線を介して流れるデータ信号の極性を反

50

転させることもでき（例：行反転、ドット反転）、1つの束の画素に印加されるデータ信号の極性も互いに反転させることができる（例：列反転、ドット反転）。

#### 【0057】

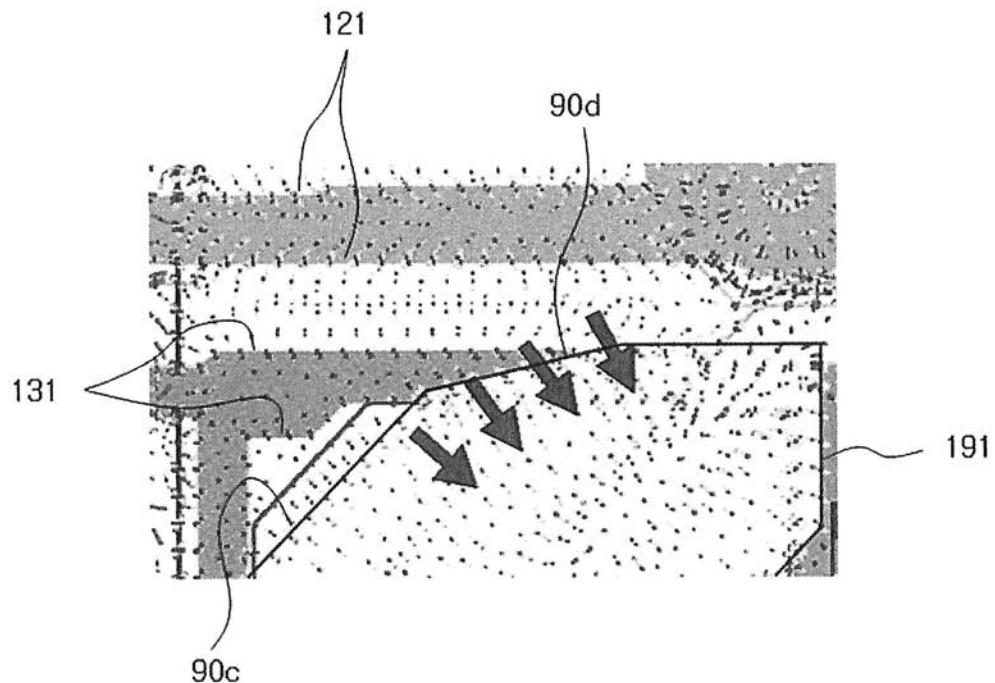

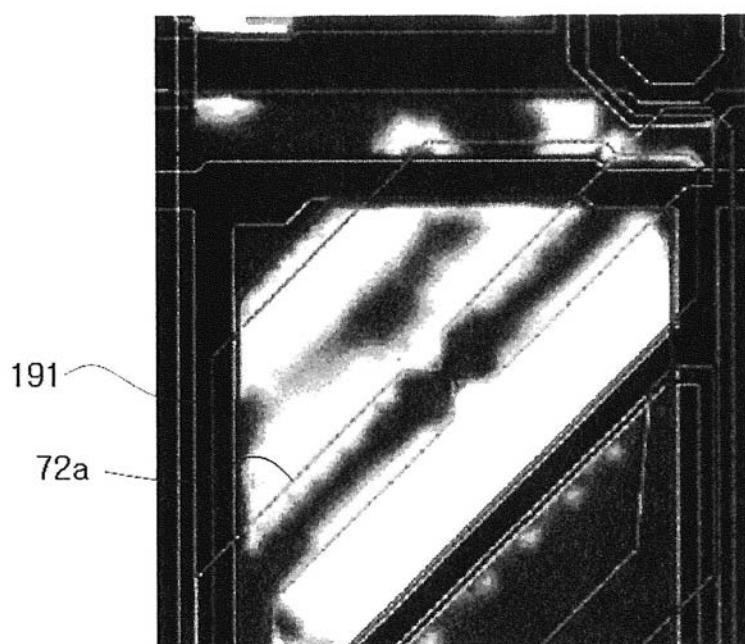

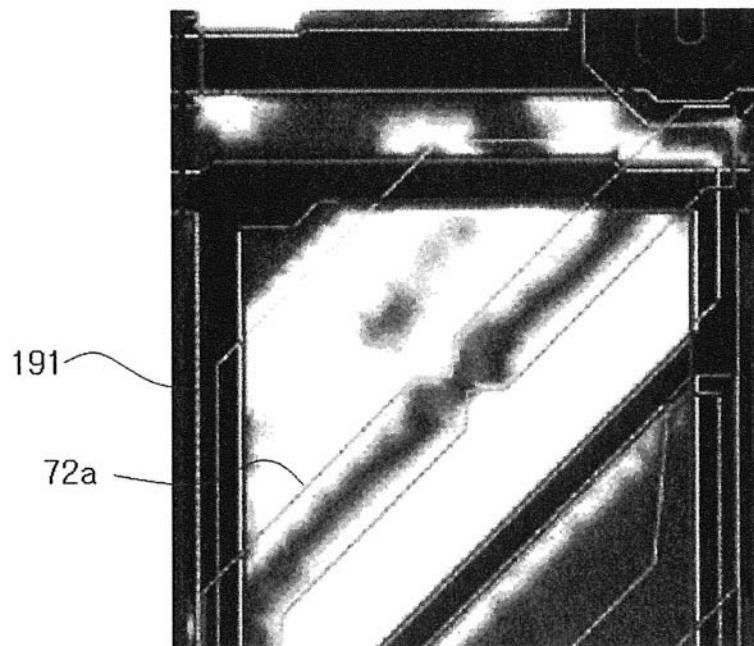

次に、図6b、7a～図9c、並びに上記の図3及び図6aを参照して本発明の一実施形態に係る液晶表示装置の液晶分子の傾く方向について詳細に説明する。

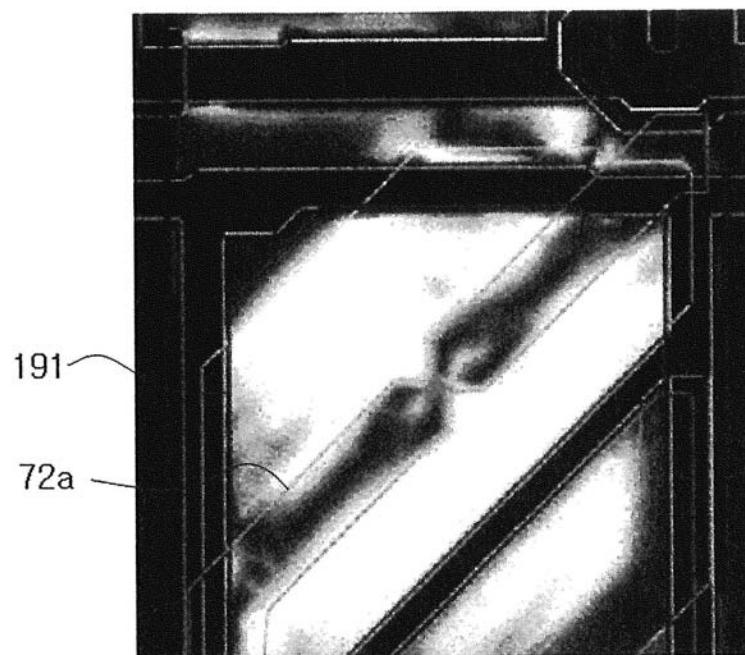

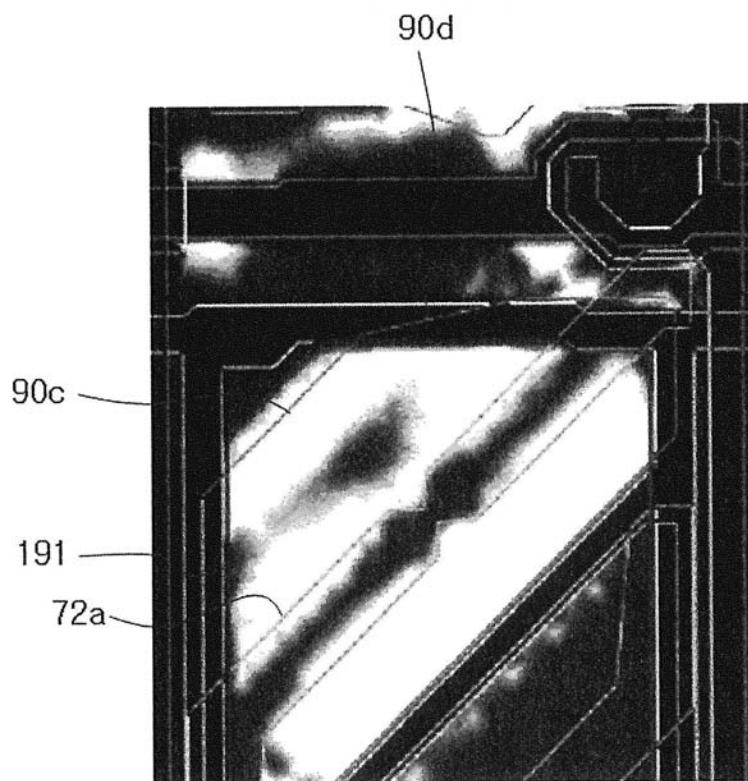

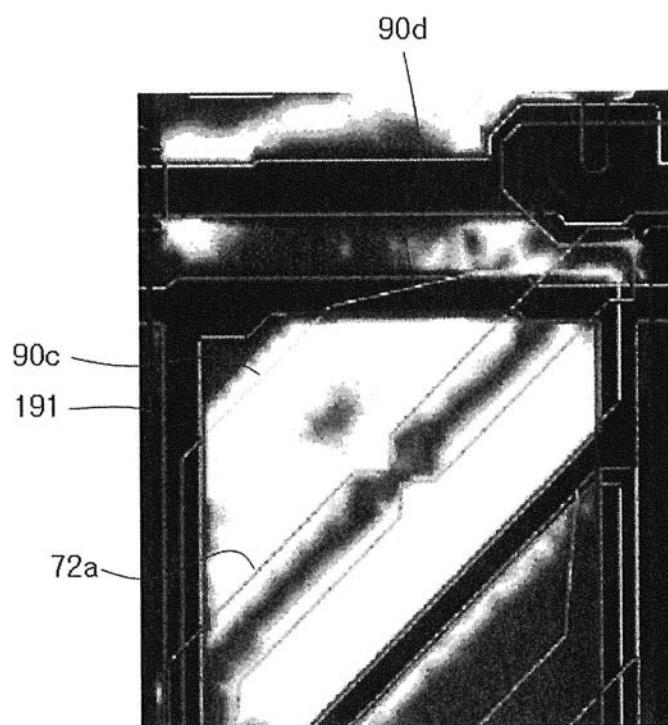

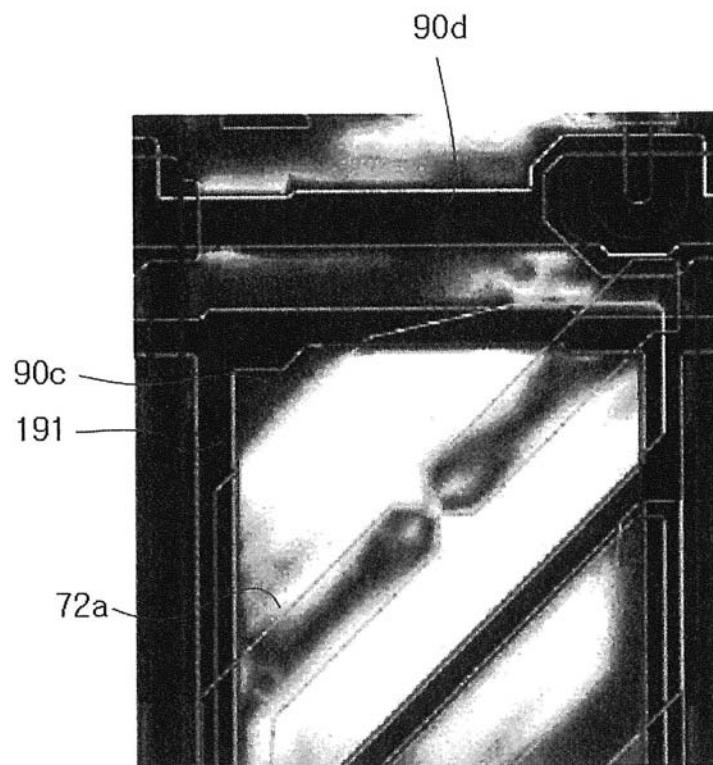

図6aは、本発明の一実施形態に係る液晶表示板組立体の一部分で液晶分子の傾く方向を示す図である。図6bは、従来技術による液晶表示板組立体の一部分で液晶分子の傾く方向を示す図である。図7aは、従来技術による液晶表示板組立体の液晶分子の動きをシミュレーションした図である。図7bは、本発明の一実施形態に係る液晶表示板組立体の液晶分子の動きをシミュレーションした図である。図8a～図8cは、従来技術による液晶表示板組立体の時間によって液晶分子が動く様子を光学シミュレーションした図である。図9a～図9cは、本発明の一実施形態に係る液晶表示板組立体の時間によって液晶分子が動く様子を光学シミュレーションした図である。

10

#### 【0058】

液晶分子が傾く方向は、1次的に電場生成電極（191、270）の切開部（71、72a、72b、91、92）と画素電極191の斜辺（90c、90d）が主電場を歪曲して生成する水平成分によって決定される。このような主電場の水平成分は、切開部（71、72a、72b、91、92）の辺と画素電極191の斜辺（90c、90d）にほぼ垂直である。

20

#### 【0059】

切開部（71、72a、72b、91、92）によって分割された各副領域上の液晶分子はほぼ主辺に垂直である方向に傾くので、その傾く方向はほぼ四つの方向である。このように液晶分子が傾く方向を多様にする場合、液晶表示装置の基準視野角が大きくなる。

図6b及び図7aに示すように、画素電極191の斜辺90cの周辺にある液晶分子30aは、斜辺90c及び共通電極の切開部72aの辺に垂直な方向に傾く。しかし、画素電極191のうちのゲート線121と平行な第2主辺90b近傍にある液晶分子30bは、他の画素電極191の第2主辺90bに垂直な方向に傾く。さらに、この部分の液晶分子30bは、ゲート線121に近いため、ゲート線121に沿って流れるゲート電圧による影響を受ける。従って、この部分の液晶分子30bは、画素電極191の斜辺90cの周辺にある液晶分子30aが傾く方向と異なり、テキスチャ（textue）が発生する。このため、液晶分子30bの応答速度が低下し、画面残像が発生する。

30

#### 【0060】

これに対し、図6a及び図7bのように、画素電極191の第1斜辺90cと横辺90bの間に第2斜辺90dを形成する場合、液晶分子30bは第2斜辺90dに垂直な方向に傾く。従って、ゲート線121を流れるゲート電圧の影響にもかかわらず液晶分子30bが第1斜辺90cに垂直な方向に近く傾くので、テキスチャの発生を抑制できる。

図8a～図8c及び図9a～図9cに示すように、従来技術による液晶表示板組立体及び本発明の一実施形態に係る液晶表示板組立体において、いずれの場合も時間が経つほどテキスチャの発生が減少する。しかし、図8aと図9aを比較する場合、時間が充分に経過するまでは、従来技術による液晶表示板組立体におけるテキスチャの発生が多いことが分かる。これに対し、本発明の一実施形態に係る液晶表示板組立体では、初期のテキスチャの発生が著しく少なく、液晶の応答速度が速いことが分かる。

40

#### 【0061】

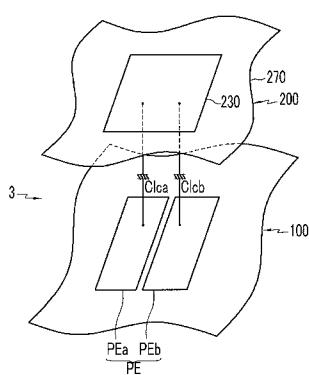

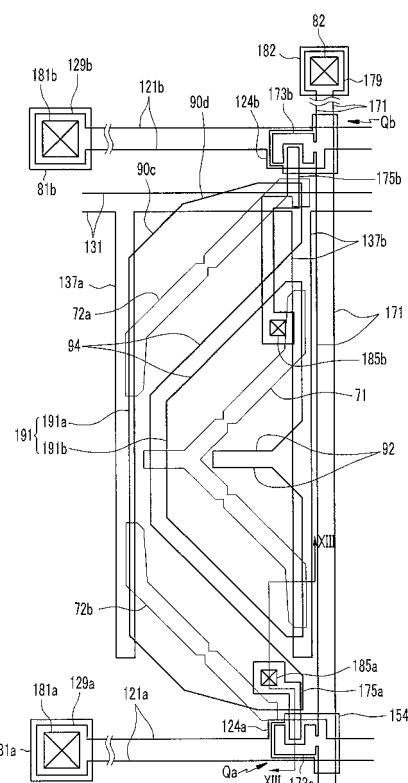

次に、図10～図13を参照して本発明の他の実施形態に係る液晶表示板組立体について詳細に説明する。

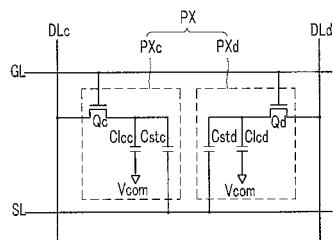

図10は、本発明の他の実施形態に係る液晶表示板組立体の2つの副画素の等価回路図である。

図10に示すように、各画素（PX）は1対の副画素を含み、各副画素は液晶キャパシタ（C1ca、C1cb）を含む。2つの副画素のうちの少なくとも1つは、ゲート線、データ線及び液晶キャパシタ（C1ca、C1cb）に接続されたスイッチング素子（図

50

示せず)を含む。

【0062】

液晶キャパシタ(C1ca、C1cb)は、下部表示板100の副画素電極(PEa、PEb)と上部表示板200の共通電極270を2つの端子とし、副画素電極(PEa、PEb)と共に共通電極270の間の液晶層3は誘電体として機能する。1対の副画素電極(PEa、PEb)は互いに分離されており、1つの画素電極(PE)をなす。共通電極270は、上部表示板200の全面に形成され、共通電圧(Vcom)の印加を受ける。液晶層3は負の誘電率異方性を有し、液晶層3の液晶分子は電場のない状態でその長軸が2つの表示板の表面に対して垂直をなすように配向することができる。

【0063】

この他に、カラーフィルタ230及び偏光子(図示せず)については既に説明したので省略する。

以下、図11、図12、図13、並びに上記の図1及び図11を参照して本発明の他の実施形態に係る液晶表示板組立体について詳細に説明する。

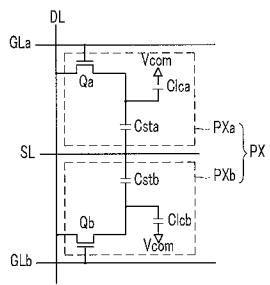

図11は、本発明の他の実施形態に係る液晶表示板組立体の1つの画素の等価回路図である。

【0064】

図11に示すように、この実施形態に係る液晶表示板組立体は、複数対のゲート線(GLa、GLb)、複数のデータ線(DL)及び複数の維持電極線(SL)を含む信号線と、これに接続された複数の画素(PX)とを含む。

各画素(PX)は、1対の副画素(PXa、PXb)を含み、各副画素(PXa、PXb)は、各々該当ゲート線(GLa、GLb)及びデータ線(DL)に接続されているスイッチング素子(Qa、Qb)と、これに接続された液晶キャパシタ(C1ca、C1cb)、並びにスイッチング素子(Qa、Qb)及び維持電極線(SL)に接続されるストレージキャパシタ(Csta、Cstb)を含む。

【0065】

各スイッチング素子(Qa、Qb)は、下部表示板100に設けられている薄膜トランジスタなどの三端子素子であって、その制御端子はゲート線(GLa、GLb)に接続されており、入力端子はデータ線(DL)に接続されており、出力端子は液晶キャパシタ(C1ca、C1cb)及びストレージキャパシタ(Csta、Cstb)に接続されている。

【0066】

液晶キャパシタ(C1ca、C1cb)の補助的役割を果たすストレージキャパシタ(Csta、Cstb)は、下部表示板100に設けられた維持電極線(SL)と画素電極(PE)が絶縁体を介在して重畳することにより形成されており、維持電極線(SL)に共通電圧(Vcom)などの定められた電圧が印加されることによって、所定電圧を維持するように構成される。ストレージキャパシタ(Csta、Cstb)は、副画素電極(PEa、PEb)が絶縁体を媒介としてすぐ上の前段ゲート線と重畳することにより構成することも可能である。

【0067】

このような液晶キャパシタ(C1ca、C1cb)などについては既に説明したので、詳細な説明は省略する。

このような液晶表示板組立体を含む液晶表示装置において、信号制御部600が1つの画素(PX)に対する入力画像信号(R、G、B)を受信して、2つの副画素(PXa、PXb)に対する出力画像信号(DAT)に変換し、データ駆動部500に転送することができる。これと異なり、階調電圧生成部800で2つの副画素(PXa、PXb)に対する階調電圧群を別々に生成し、これを交互にデータ駆動部500に提供したり、データ駆動部500でこれを交互に選択したりすることによって、2つの副画素(PXa、PXb)に互いに異なる電圧を印加することができる。ただし、このとき、2つの副画素(PXa、PXb)の合成ガンマ曲線が正面での基準ガンマ曲線に近づくように画像信号を補

10

20

30

40

50

正するか、階調電圧群を生成することが好ましい。例えば、正面での合成ガンマ曲線は、この液晶表示板組立体に最も適するように決められた正面での基準ガンマ曲線と一致するようにし、側面での合成ガンマ曲線は、正面での基準ガンマ曲線に最も近づくようにする。

#### 【0068】

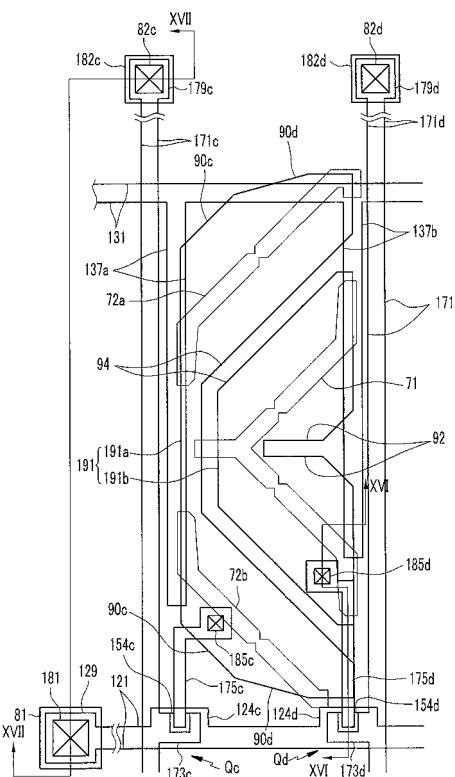

図11に示した液晶表示板組立体の一例について図12及び図13を参照して詳細に説明する。

図12は、本発明の他の実施形態に係る液晶表示板組立体の配置図である。図13は、図12に示した液晶表示板組立体のXIII-XIII線に沿った断面図である。

図12及び図13に示した液晶表示板組立体は、互いに対向する下部表示板100と上部表示板200、及びこれら2つの表示板の間に挟持された液晶層3を含む。

#### 【0069】

この実施形態に係る液晶表示板組立体の層状構造は、ほぼ図3～図5に示した液晶表示板組立体の層状構造と同一である。

次に、図12及び図13を参照して下部表示板について説明する。絶縁基板110上に複数対の第1及び第2ゲート線(121a、121b)と維持電極線131を含む複数のゲート導電体が形成されている。各ゲート線(121a、121b)は、第1及び第2ゲート電極(124a、124b)と端部(129a、129b)を含む。維持電極線131は、維持電極(137a、137b)を含む。ゲート導電体(121a、121b、131)上にゲート絶縁膜140が形成されている。ゲート絶縁膜140上に第1及び第2島型半導体(154a、154b)が形成され、その上に複数のオーミック接触部材(163a、165a)が形成されている。オーミック接触部材(163a、165a)及びゲート絶縁膜140上には複数のデータ線171と複数対の第1及び第2ドレイン電極(175a、175b)を含むデータ導電体が形成されている。データ線171は、複数対の第1及び第2ソース電極(173a、173b)と端部179を含む。データ導電体(171、175a、175b)及び露出している半導体(154a、154b)部分上に保護膜180が形成され、保護膜180及びゲート絶縁膜140に複数のコンタクトホール(181a、181b、182、185a、185b)が形成されている。保護膜上には複数の画素電極191と複数の接触補助部材(81a、81b、82)が形成されている。画素電極191、接触補助部材(81a、81b、82)及び保護膜上には配向膜11が形成されている。

#### 【0070】

次に、図12及び図13に示す液晶表示板組立体の上部表示板について説明する。絶縁基板210上に遮光部材220、オーバーコート層250、共通電極270、及び配向膜21が形成されている。

図12及び図13に示す液晶表示板組立体は、図3～図5の液晶表示板組立体とは異なり、画素電極191が互いに分離されている第1及び第2副画素電極(191a、191b)を含む。第1及び第2副画素電極(191a、191b)は間隙94を間に置いて互いに離間している。間隙94は、第1斜辺(90c)と平行な斜線部を含む。

#### 【0071】

第2副画素電極(191b)は、中央切開部92を含む。第1副画素電極(191a)は、第1及び第2ゲート線(121a、121b)と隣接し、第1斜辺(90c)及び第2斜辺(90d)を含む。第1斜辺90c及び第2斜辺90dは、図3の液晶表示板組立体と同一であるので、詳細な説明は省略する。

1対の副画素電極(191a、191b)に1つの入力画像信号に対して予め設定された互いに異なるデータ電圧が印加されるが、その大きさは副画素電極(191a、191b)の大きさ及び形状によって設定できる。副画素電極(191a、191b)の面積は互いに異なってもよい。例えば第2副画素電極191bは、第1副画素電極191aに比べて高い電圧の印加を受け、第1副画素電極191aより面積が大きい。

#### 【0072】

10

20

30

40

50

液晶分子の傾く角度は電場の強さによって変わるので、2つの液晶キャパシタ（C1c a、C1c b）の電圧が互いに異なるので液晶分子の傾く角度が異なり、これによって2つの副画素の輝度が異なる。従って、第1液晶キャパシタ（C1c a）の電圧と第2液晶キャパシタ（C1c b）の電圧を適切に調整すれば、側面から見る画像を正面から見る画像に最大に近づけることができる。つまり、側面ガンマ曲線を正面ガンマ曲線に最大に近づけることが可能で、その結果側面視認性を向上することができる。

#### 【0073】

また、高い電圧の印加を受ける第1副画素電極191aの面積を第2副画素電極191bの面積より小さくすれば、側面ガンマ曲線を正面ガンマ曲線により近づけることができる。特に第1及び第2副画素電極（191a、191b）の面積比がほぼ1:2～1:3である場合、側面ガンマ曲線が正面ガンマ曲線にさらに近づくようになり側面視認性が一層良くなる。10

#### 【0074】

副画素電極（191a、191b）の間の電圧差によって副次的に生成される副電場（secondary electric field）の方向は副領域の主辺と垂直である。これにより、副電場の方向と主電場の水平成分の方向とが一致する。結局副画素電極（191a、191b）の間の副電場は、液晶分子の傾斜方向の結晶を強化する方向に作用する。

#### 【0075】

また、図12及び図13の液晶表示板組立体は、図3～図6に示した液晶表示板組立体と異なり、2つのゲート線（121a、121b）、ゲート電極（124a、124b）、島状半導体（154a、154b）、ソース電極（173a、173b）、ドレイン電極（175a、175b）を含む。20

第1及び第2ゲート電極（124a、124b）、第1及び第2ソース電極（173a、173b）、並びに第1及び第2ドレイン電極（175a、175b）は、第1及び第2半導体（154a、154b）と共に第1及び第2薄膜トランジスタ（TFT）（Qa、Qb）をなし、第1及び第2薄膜トランジスタ（Qa、Qb）のチャネル（channel）は、第1及び第2ソース電極（173a、173b）と第1及び第2ドレイン電極（175a、175b）の間の第1及び第2半導体（154a、154b）に形成される。30

#### 【0076】

また、この実施形態による液晶表示板組立体は、図3～図5に示した液晶表示板組立体と異なり、上部表示板200にカラーフィルタがなく、下部表示板100の保護膜180の下に複数のカラーフィルタ230が形成されている。

カラーフィルタ230は、画素電極191列に沿って周期的に曲がって縦に長く延び、ゲート線121の端部129及びデータ線171の端部179が位置する周辺領域には存在しない。カラーフィルタ230にはコンタクトホール185aが通過し、コンタクトホール185aより大きな貫通孔235が形成されている。

#### 【0077】

隣接するカラーフィルタ230は、データ線171上で重畠して、隣接する画素電極191の間から漏洩する光を遮断する遮光部材の機能を有してもよい。この場合、上部表示板200の遮光部材を省略してもよく、その結果工程が簡単になる。40

カラーフィルタ230の下にも保護膜（図示せず）を設けてもよい。

共通電極表示板200のオーバーコート層250は省略してもよい。

#### 【0078】

図3～図6に示した液晶表示板組立体の特徴の多くは、図12及び図13に示した液晶表示板組立体にも適用可能である。

次に、図10に示した液晶表示板組立体の他の例に対し図14～図16を参照して詳細に説明する。

図14は、本発明の他の実施形態に係る液晶表示板組立体の1つの画素の等価回路図で50

ある。

【0079】

図14に示すように、この実施形態による液晶表示板組立体は、複数のゲート線（GL）、複数対のデータ線（DLc、DLd）及び複数の維持電極線（SL）を含む信号線と、これに接続された複数の画素（PX）とを含む。

各画素（PX）は、1対の副画素（PXc、PXd）を含み、各副画素（PXc、PXd）は、各々該当ゲート線（GL）及びデータ線（DLc、DLd）に接続されるスイッチング素子（Qc、Qd）と、これに接続された液晶キャパシタ（C1cc、C1cd）並びにスイッチング素子（Qc、Qd）及び維持電極線（SL）に接続されるストレージキャパシタ（Cstc、Cstd）を含む。

10

【0080】

また、各スイッチング素子（Qc、Qd）は、下部表示板100に設けられている薄膜トランジスタなどの三端子素子であって、その制御端子はゲート線（GL）に接続されており、入力端子はデータ線（DLc、DLd）に接続されており、出力端子は液晶キャパシタ（C1cc、C1cd）及びストレージキャパシタ（Cstc、Cstd）に接続されている。

【0081】

液晶キャパシタ（C1cc、C1cd）とストレージキャパシタ（Cstc、Cstd）、及びこのような液晶表示板組立体を含む液晶表示装置の動作などは、上記の実施形態と実質的に同一であるので詳細な説明は省略する。しかし、図12に示した液晶表示板組立体において、1つの画素（PX）を構成する2つの副画素（PXa、PXa）が時差を持ってデータ電圧の印加を受けるのに対し、この実施形態では、2つの副画素（PXc、PXd）が同一時間にデータ電圧の印加を受ける。

20

【0082】

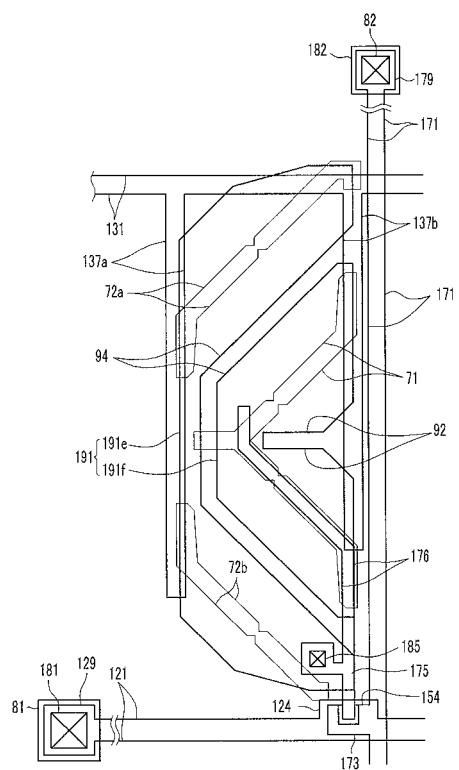

次に、図14に示した液晶表示板組立体の一例について図15～図17を参照して詳細に説明する。

図15は、本発明の他の実施形態に係る液晶表示板組立体の配置図であり、図16及び図17は、各々図15に示した液晶表示板組立体のXVI-XVI及びXVII-XVII線に沿った断面図である。

【0083】

図15～図17に示したように、この実施形態による液晶表示板組立体は、互いに対向する下部表示板100と上部表示板200、これら2つの表示板の間に挟持された液晶層3、及び表示板の外側面に取り付けられている1対の偏光子（12、22）を含む。

30

図15～図17の実施形態による液晶表示板組立体の層状構造は、図3～図5に示した液晶表示板組立体の層状構造とほぼ同一である。

【0084】

図15の実施形態による液晶表示板組立体の下部表示板について説明する。絶縁基板110上に複数のゲート線121及び複数の維持電極線131を含むゲート導電体が形成されている。各ゲート線121は複数対の第1及び第2ゲート電極（124c、124d）と端部129を含む。各維持電極線131は維持電極（137a、137b）を含む。ゲート導電体121上にゲート絶縁膜140が形成されている。ゲート絶縁膜140上に第1及び第2島型半導体（154c、154d）が形成され、その上には複数のオーミック接触部材（163c、163d）が形成されている。オーミック接触部材（163c、163d）上に複数対の第1及び第2データ線（171c、171d）と複数の第1及び第2ドレン電極（175c、175d）を含むデータ導電体が形成されている。第1及び第2データ線（171c、171d）は、各々複数の第1及び第2ソース電極（173c、173d）と端部（179a、179b）を含む。データ導電体（171c、171d、175c、175d）及び露出している半導体（154c、154d）部分上に保護膜180が形成され、保護膜180及びゲート絶縁膜140に複数のコンタクトホール（181、182c、182d、185c、185d）が形成されている。保護膜上に第1及

40

び第2副画素電極(191a、191b)を含む複数の画素電極191と、複数の接触補助部材(81、82c、82d)が形成されている。画素電極191、接触補助部材(81、82c、82d)及び保護膜上には配向膜11が形成されている。

#### 【0085】

図15及び図16の液晶表示板組立体の上部表示板について説明する。絶縁基板210上に遮光部材220、複数のカラーフィルタ230、オーバーコート層250、共通電極270、及び配向膜21が形成されている。

しかし、図15の実施形態による液晶表示板組立体において、図12及び図13に示した液晶表示板組立体と比較する場合、ゲート線121の数は半分であり、その代わりデータ線(171c、171d)の数は2倍である。そして、1つの画素電極191をなす第1及び第2副画素電極(191a、191b)に接続された第1及び第2薄膜トランジスタ(Qc、Qd)が同一のゲート線121、互いに異なるデータ線(171c、171d)に接続されている。

#### 【0086】

さらに、半導体(154c、154d)は、データ線(171c、171d)及びドレイン電極(175c、175c)に沿って延長されて線状半導体151をなし、オーミック接触部材163dは、データ線(171c、171d)に沿って延長されて線状オーミック接触部材161を構成する。線状半導体151は、データ線171、ドレイン電極(175c、175d)及びその下部のオーミック接触部材(161、165d)と実質的に同一の平面形状を有している。

#### 【0087】

このような薄膜トランジスタ表示板を本発明の一実施形態により製造する方法において、データ線(171c、171d)とドレイン電極(175c、175d)、半導体151及びオーミック接触部材(161、165b)を1度の写真工程で形成する。

このような写真工程で使用する感光膜は、位置によって厚さが異なり、特に厚さが薄くなる順に第1部分と第2部分を含む。第1部分は、データ線(171c、171d)とドレイン電極(175c、175d)が占める配線領域に位置し、第2部分は、薄膜トランジスタのチャネル領域に位置する。

#### 【0088】

位置によって感光膜の厚さが異なるようにする方法にはいろいろな方法があるが、例えば、光マスクに透光領域(light transmitting area)及び遮光領域(light blocking area)の他に、半透明領域(translucent area)を設ける方法がある。半透明領域にはスリットパターン(slit pattern)、格子パターン(lattice pattern)、または透過率が中間であるか厚さが中間である薄膜が設けられる。スリットパターンを使用する場合には、スリットの幅やスリット間の間隔が写真工程に使用する露光器の分解能(resolution)より小さいことが好ましい。他の例には、リフローの可能な感光膜を使用する方法がある。つまり、透光領域と遮光領域のみを有する通常の露光マスクにリフロー可能な感光膜を形成した後、リフローさて感光膜が残留しない領域に流れるようにすることによって薄い部分を形成する。このようにすることで1度の写真工程を減らすことができるので製造方法が簡単になる。

#### 【0089】

図3～図5に示した液晶表示板組立体の特徴の多くは、図15及び図16に示した液晶表示板組立体にも適用可能である。

次に、図18及び図19を参照して本発明の他の実施形態に係る液晶表示板組立体について詳細に説明する。

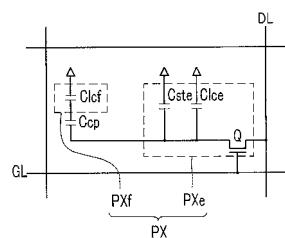

図18は、本発明の他の実施形態に係る液晶表示板組立体の1つの画素の等価回路図である。

#### 【0090】

図18に示すように、この実施形態による液晶表示板組立体は、複数のゲート線(GL)

10

20

30

40

50

)と複数のデータ線(DL)を含む信号線と、これに接続される複数の画素(PX)を含む。

各画素(PX)は、1対の第1及び第2副画素(PXe、PXf)と2つの副画素(PXe、PXf)の間に接続される結合キャパシタ(Ccp)を含む。

#### 【0091】

第1副画素(PXe)は、該当ゲート線(GL)及びデータ線(DL)に接続されるスイッチング素子(Q)と、これに接続される第1液晶キャパシタ(C1ce)及びストレージキャパシタ(Cst)を含み、第2副画素(PXf)は、結合キャパシタ(Ccp)に接続される第2液晶キャパシタ(C1cf)を含む。

また、スイッチング素子(Q)は、下部表示板100に備えられている薄膜トランジスタなどの三端子素子であって、その制御端子はゲート線(GL)に接続されており、入力端子はデータ線(DL)に接続されており、出力端子は液晶キャパシタ(C1ce)、ストレージキャパシタ(Cste)及び結合キャパシタ(Ccp)に接続されている。

#### 【0092】

このようなスイッチング素子(Q)は、ゲート線(GL)からのゲート信号によってデータ線(DL)からのデータ電圧を第1液晶キャパシタ(C1ce)及び結合キャパシタ(Ccp)に印加し、結合キャパシタ(Ccp)は、この電圧をその大きさを変えて第2液晶キャパシタ(C1cf)に伝達する。

ストレージキャパシタ(Cste)に共通電圧(Vcom)が印加され、キャパシタ(C1ce、Cste、C1cf、Ccp)とその静電容量を同一の図面符号で示す場合、第1液晶キャパシタ(C1ce)に充電された電圧(Ve)と第2液晶キャパシタ(C1cf)に充電された電圧(Vf)とが次のような関係を有する。

#### 【0093】

$$V_f = V_e \times (C_{cp} / (C_{cp} + C_{1cf}))$$

Ccp/(Ccp+C1cf)の値が1より小さいので、第2液晶キャパシタ(C1cf)に充電された電圧(Vf)は、第1液晶キャパシタ(C1ce)に充電された電圧(Ve)に比べて常に小さい。この関係は、ストレージキャパシタ(Cste)に印加された電圧が共通電圧(Vcom)でない場合にも同様に成立する。

#### 【0094】

第1液晶キャパシタ(C1ce)に充電された電圧(Ve)と第2液晶キャパシタ(C1cf)に充電された電圧(Vf)の適正な比率は、結合キャパシタ(Ccp)の静電容量を調節することによって得ることができる。

次に、このような液晶表示板組立体の一例について図19を参照して詳細に説明する。

図19は、本発明の他の実施形態に係る液晶表示板組立体を示す配置図である。

#### 【0095】

この実施形態による液晶表示板組立体の層状構造は、図4、図13及び図16に示した液晶表示板組立体の層状構造とほぼ同一であるので、別途図示せずに図4、図13及び図16に示した図面符号と同一の図面符号を使用して説明する。

図19に示すように、この実施形態による液晶表示板組立体は、互いに対向する下部表示板(図示せず)と上部表示板(図示せず)、及びこれら2つの表示板の間に挟持された液晶層(図示せず)を含む。

#### 【0096】

この実施形態による液晶表示板組立体の層状構造は、図3～図5に示した液晶表示板組立体の層状構造とほぼ同一である。

まず、下部表示板について説明する。絶縁基板(図示せず)上に複数のゲート線121を含む複数のゲート導電体が形成されている。各ゲート線121は、ゲート電極124と端部129とを含む。ゲート導電体121上にゲート絶縁膜(図示せず)が形成されている。ゲート絶縁膜上に島状半導体154が形成され、その上に複数のオーミック接触部材(図示せず)が形成されている。オーミック接触部材及びゲート絶縁膜上には、複数のデータ線171と複数のドレンイン電極175を含むデータ導電体が形成されている。データ

10

20

30

40

50

線 171 は、複数のソース電極 173 と端部 179 とを含む。データ導電体 (171、175) 及び露出している半導体 154 部分上に保護膜 (図示せず) が形成され、保護膜及びゲート絶縁膜に複数のコンタクトホール (181、182、185) が形成されている。保護膜上に複数の画素電極 191 と複数の接触補助部材 (81、82) が形成されている。画素電極 191、接触補助部材 (81、82) 及び保護膜上には配向膜 (図示せず) が形成されている。

#### 【0097】

次に、上部表示板について説明する。絶縁基板 (図示せず) 上に遮光部材 (図示せず)、複数のカラーフィルタ (図示せず)、蓋膜 (図示せず)、共通電極 (図示せず)、及び配向膜 (図示せず) が形成されている。

10

この実施形態による画素電極 191 及び共通電極 270 は、図 12 及び図 15 に示した液晶表示板組立体の画素電極 191 及び共通電極 270 とその形態が似ている。しかし、この実施形態による画素電極 191 は、図 3 と異なり、互いに分離されている第 1 及び第 2 副画素電極 (191a、191b) を含む。第 1 副画素電極 191a は、コンタクトホール 185 を介してドレイン電極 175 に接続されている。

#### 【0098】

この実施形態による液晶表示板組立体は、ドレイン電極 175 は結合電極 (coupling electrode) 176 を含む。結合電極 176 は、データ線 171 と実質的に平行に延びて、共通電極 270 の中央切開部 71 の斜線部及び縦部に沿って延びている。

20

前記結合電極 176 は、第 2 副画素電極 191b と重畠する。結合電極 176 と第 2 副画素電極 191b は、結合キャパシタ (Ccp) を構成する。

#### 【0099】

図 15 ~ 図 17 示した液晶表示板組立体の特徴の多くは、図 19 に示した液晶表示板組立体にも適用可能である。

尚、本発明は、上述の実施例に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【図面の簡単な説明】

#### 【0100】

【図 1】本発明の一実施形態に係る液晶表示装置のブロック図である。

30

【図 2】本発明の一実施形態に係る液晶表示板組立体の 1 つの画素に対する等価回路図である。

【図 3】本発明の一実施形態に係る液晶表示板組立体の配置図。

【図 4】図 3 に示した液晶表示板組立体の IV-IV 線に沿った断面図である。

【図 5】図 3 に示した液晶表示板組立体の V-V 線に沿った断面図である。

【図 6 a】本発明の一実施形態に係る液晶表示板組立体の一部分を液晶分子の傾く方向と共に示す図である。

【図 6 b】従来技術による液晶表示板組立体の一部分を液晶分子の傾く方向と共に示す図である。

【図 7 a】従来技術による液晶表示板組立体の液晶分子の動きをシミュレーションした図である。

40

【図 7 b】本発明の一実施形態に係る液晶表示板組立体の液晶分子の動きをシミュレーションした図である。

【図 8 a】従来技術による液晶表示板組立体の時間によって液晶分子が動く様子を光学シミュレーションした図である。

【図 8 b】従来技術による液晶表示板組立体の時間によって液晶分子が動く様子を光学シミュレーションした図である。

【図 8 c】従来技術による液晶表示板組立体の時間によって液晶分子が動く様子を光学シミュレーションした図である。

【図 9 a】本発明の一実施形態に係る液晶表示板組立体の時間によって液晶分子が動く様

50

子を光学シミュレーションした図である。

【図 9 b】本発明の一実施形態に係る液晶表示板組立体の時間によって液晶分子が動く様子を光学シミュレーションした図である。

【図 9 c】本発明の一実施形態に係る液晶表示板組立体の時間によって液晶分子が動く様子を光学シミュレーションした図である。

【図 10】本発明の他の実施形態に係る液晶表示装置の2つの副画素に対する等価回路図である。

【図 11】本発明の他の実施形態に係る液晶表示板組立体の1つの画素に対する等価回路図である。

【図 12】本発明の他の実施形態に係る液晶表示板組立体の配置図。 10

【図 13】図 12 に示した液晶表示板組立体のXIII-XIII線に沿った断面図である。

【図 14】本発明の他の実施形態に係る液晶表示板組立体の1つの画素に対する等価回路図である。

【図 15】本発明の他の実施形態に係る液晶表示板組立体の配置図。

【図 16】図 15 に示した液晶表示板組立体のXVI-XVI線に沿った断面図である。

【図 17】図 15 に示した液晶表示板組立体のXVII-XVII線に沿った断面図である。

【図 18】本発明の他の実施形態に係る液晶表示板組立体の1つの画素に対する等価回路図である。

【図 19】本発明の他の実施形態に係る液晶表示板組立体の配置図。 20

【符号の説明】

【0101】

12、22 偏光板

11、21 配向膜

71a～b、72 共通電極切開部

81、81a、81b、82、82a、82b 接触補助部材

92 画素電極切開部

94 間隙

110、210 基板

121、121a、121b、129a、129b ゲート線

124、124a、124b ゲート電極

131 維持電極線

137a、137b 維持電極

140 ゲート絶縁膜

154、154a、154b、154c、154d 半導体

161、163a、165a、163b、165b オーミック接触部材

171、171a、171b、176、179、179a、179b データ線

173、173a、173b、173c、173d ソース電極

175、175a、175b、175c、175d ドレイン電極

180 保護膜

181、181a、181b、182、182a、182b、185、185a、185b、185c、185d コンタクトホール

191、191a、191b 画素電極

220 遮光部材

230 カラーフィルタ

250 オーバーコート層

270 共通電極

300 液晶表示板組立体

400 ゲート駆動部

500 データ駆動部

600 信号制御部

10

20

30

40

50

## 800 階調電圧生成部

【図1】

【図2】

【図3】

【図4】

【 図 5 】

【図10】

【 図 1 1 】

【図 6 a】

【図 6 b】

【 図 1 2 】

【図13】

【図 1-4】

【図16】

〔 図 17 〕

【 図 1 5 】

【 四 1 8 】

【図 19】

【図 7 a】

【図 7 b】

【図 8 a】

【図 8 b】

【図 8 c】

【図 9 a】

【図 9 b】

【図 9 c】

---

フロントページの続き

(72)発明者 羅 柄 善

大韓民国京畿道水原市長安区栗田洞バムコットマウルツランチェアパート108棟301号

(72)発明者 奇 桐 賢

大韓民国忠清南道天安市雙龍3洞住公9団地アパート410棟1105号

(72)発明者 安 順 一

大韓民国忠清南道天安市鳳鳴洞チョンソル3次アパート304棟1309号

F ターム(参考) 2H092 GA13 GA15 GA17 GA29 GA30 GA33 GA41 GA43 HA04 HA12

HA18 JA26 JA37 JA41 JA46 JB05 JB16 JB42 JB69 KB14

MA12 NA01 NA07 PA08 PA09 QA09