(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5401444号

(P5401444)

(45) 発行日 平成26年1月29日(2014.1.29)

(24) 登録日 平成25年11月1日(2013.11.1)

(51) Int.Cl.

F 1

**G06F 13/16 (2006.01)**

G06F 13/16 510A

**G06F 12/06 (2006.01)**

G06F 12/06 515K

G06F 12/06 525A

請求項の数 22 (全 21 頁)

(21) 出願番号 特願2010-501086 (P2010-501086)

(86) (22) 出願日 平成20年3月19日 (2008.3.19)

(65) 公表番号 特表2010-524059 (P2010-524059A)

(43) 公表日 平成22年7月15日 (2010.7.15)

(86) 國際出願番号 PCT/US2008/057471

(87) 國際公開番号 WO2008/121559

(87) 國際公開日 平成20年10月9日 (2008.10.9)

審査請求日 平成23年3月18日 (2011.3.18)

(31) 優先権主張番号 60/909,359

(32) 優先日 平成19年3月30日 (2007.3.30)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 501055961

ラムバス・インコーポレーテッド

アメリカ合衆国、カリフォルニア州 9

4089, サニーヴェール, スイート 7

00, エンタープライズ ウエイ 105

O

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100109346

弁理士 大貫 敏史

(72) 発明者 ハンペル, クレイグ

アメリカ合衆国、カリフォルニア州 94

024, ロス アルトス, ベルビュー コ

ート 340

最終頁に続く

(54) 【発明の名称】異なる種類の集積回路メモリ素子を有する階層メモリモジュールを含むシステム

## (57) 【特許請求の範囲】

## 【請求項1】

メモリコントローラを有するメモリシステムであって、

第1のメモリ階層を定義する複数の揮発性メモリ素子の第1のセットであって、第1のメモリモジュール上に配置され、当該第1のメモリモジュールは前記メモリコントローラに結合される、第1のセットと、

第2のメモリ階層を定義する1以上の不揮発性メモリ素子の第2のセットであって、第2のメモリモジュール上に配置され、当該第2のメモリモジュールは前記第1のメモリモジュールに結合される、第2のセットと

を備え、

前記第1のメモリ階層は、前記メモリコントローラからメモリトランザクションを受け取り、

データが、前記第1のメモリ階層から前記第2のメモリ階層へ、選択的に書き込まれ、

前記第2のメモリモジュールは、当該第2のメモリモジュール上に存在しない下流にあるメモリ素子のセットと結合する集積回路バッファ素子であって、特定のメモリロケーションへの書き込み回数をカウントし、書き込み回数が閾値を超えている場合に、書き込み位置をリマップする集積回路バッファ素子を含む、

メモリシステム。

## 【請求項2】

前記第1のメモリ階層は、前記第2のメモリ階層において記憶するためにデータをキヤ

ッシュし、

前記メモリコントローラから受信した前記トランザクションは、キャッシュされた前記データに対するランダムアクセス書き込みトランザクションを含み、

前記トランザクションは、前記第1のメモリ階層から前記第2のメモリ階層へ選択的に送信され、前記第1のメモリ階層にキャッシュされた前記データの、ブロックをベースとした周期的な書き込みトランザクションを含み、前記キャッシュされたデータを前記1以上の不揮発性メモリ素子に記憶させる、請求項1記載のメモリシステム。

【請求項3】

前記第1のメモリ階層は、ポイントツーポイントデータリンクで前記メモリコントローラに結合されており、第2のメモリ階層は、ポイントツーポイントデータリンクで前記第1のメモリ階層に接続される、請求項2記載のメモリシステム。 10

【請求項4】

前記ポイントツーポイントデータリンクのそれぞれは、シリアルリンクである、請求項3記載のメモリシステム。

【請求項5】

前記第1のメモリ階層は、複数のDRAMを含んでおり、当該DRAMは、書き込み動作に関連するビットが前記複数のDRAMに同時に書き込まれるように編成されている、請求項2記載のメモリシステム。

【請求項6】

前記第1のメモリモジュールは、FBDIMMである、請求項2記載のメモリシステム。 20

【請求項7】

前記1以上の不揮発性メモリ素子は、フラッシュメモリ素子を含む、請求項1記載のメモリシステム。

【請求項8】

前記第1のメモリモジュール及び前記第2のメモリモジュールにシステムクロック信号を配布するクロックソースをさらに含む、請求項1記載のメモリシステム。

【請求項9】

メモリコントローラ及び少なくとも1つの不揮発性メモリ素子の下流セットを有するメモリシステムにおいて使用されるメモリモジュールであって、 30

前記メモリモジュール上に配置されて、第1のメモリ階層の少なくとも一部を構成する揮発性メモリ素子の第1のセットと、

前記メモリモジュールから前記下流セットに書き込みコマンドを選択的に開始して、前記不揮発性メモリ素子の第1のセットに亘って記憶されたデータ幅を示すデータを、データブロックとして前記下流セットの一部を構成する不揮発性メモリ素子の少なくとも1つに書き込む集積回路バッファであって、特定のメモリロケーションへの書き込み回数をカウントし、書き込み回数が閾値を超えている場合に、書き込み位置をリマップする集積回路バッファ素子を含み、

前記メモリモジュールが、前記メモリコントローラ及び前記メモリ素子の前記下流セットに接続するようになされており、 40

前記メモリモジュールは、前記メモリコントローラから複数のメモリトランザクションを受け取り、前記複数のメモリ動作を示す書き込みデータを蓄積し、前記メモリモジュールから前記下流セットに、蓄積された前記書き込みデータを含むデータブロックを選択的に転送するためのものである、メモリモジュール。

【請求項10】

前記揮発性メモリ素子の第1のセットはDRAM素子を含んでおり、当該DRAM素子は、共通のアドレス範囲を示す並列セットを編成しており、

前記メモリモジュールは、同様のアドレスにおける、前記DRAM素子の並列セットに、書き込みデータを蓄積し、

前記メモリモジュールは、前記並列セットから、前記下流セットにおいて記憶されるデ 50

ータ値のブロックに、前記書き込みデータをリマッピングすることにより、前記書き込みデータを、前記揮発性メモリ素子の第1のセットから前記下流セットに選択的に転送する、請求項9記載のメモリモジュール。

【請求項11】

前記第2のメモリモジュールはFBDIMMである、請求項6記載のメモリシステム。

【請求項12】

前記第1のメモリモジュール及び前記第2のメモリモジュールの少なくとも一方は、バッファされている、請求項1記載のメモリシステム。

【請求項13】

前記第1のメモリモジュール及び前記第2のメモリモジュールは、それぞれバッファされており、10

前記メモリコントローラと前記第1のメモリモジュールとの間のデータ通信は、前記メモリコントローラと前記第1のメモリモジュールのバッファとの間でなされ、

前記第1のメモリモジュールと前記第2のメモリモジュールとの間のデータ通信は、前記第1のメモリモジュールの前記バッファと前記第2のメモリモジュールのバッファとの間でなされる、請求項1記載のメモリシステム。

【請求項14】

前記第1のメモリモジュール及び前記第2のメモリモジュールのそれぞれのバッファは、当該対応するメモリモジュールにあるメモリデバイスへデータを転送する、少なくとも1つのトランザクションキューを含む、請求項13記載のメモリシステム。20

【請求項15】

前記集積回路バッファ素子は、マッピング回路をさらに含み、

前記マッピング回路は、前記1以上の不揮発性メモリ素子における欠陥又は劣化の少なくとも1つに応答して、前記第1のメモリモジュール及び前記第2のメモリモジュールの少なくとも1つにおいてデータが記憶される位置をリマップする、請求項1記載のメモリシステム。

【請求項16】

前記集積回路バッファ素子は、前記少なくとも1つの不揮発性メモリ素子における欠陥を検出する欠陥回路をさらに含み、30

前記マッピング回路は、前記欠陥回路に結合されており、当該欠陥回路によって検出された欠陥に応答する位置をリマップする、請求項15記載のメモリシステム。

【請求項17】

前記集積回路バッファ素子は、前記少なくとも1つの不揮発性メモリ素子における劣化を検出する耐久性回路をさらに含み、

前記マッピング回路は、前記耐久性回路に結合されており、当該耐久性回路によって検出された劣化に応答する位置をリマップする、請求項15記載のメモリシステム。

【請求項18】

前記マッピング回路は、前記メモリコントローラと共に配置される、請求項15記載のメモリシステム。

【請求項19】

前記マッピング回路は、前記第1のメモリモジュール上に位置する、請求項15記載のメモリシステム。40

【請求項20】

前記マッピング回路は、前記第2のメモリモジュール上に位置する、請求項15記載のメモリシステム。

【請求項21】

前記第1のメモリモジュール及び前記第2のメモリモジュールの少なくとも1つは、システムクロックに基づくローカルクロック信号を生成する位相ロック回路を含む、請求項1記載のメモリシステム。

【請求項22】

50

前記メモリモジュールは F B D I M M である、請求項 1 0 記載のメモリモジュール。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

分野

本明細書における開示は、一般的には集積回路素子および／またはこのような素子の高速信号伝送に関する。

【背景技術】

【0 0 0 2】

関連技術の背景

10

各種メモリ技術およびそのような各種メモリ技術を実施するメモリシステムの性能、耐久性、密度、コスト、および消費電力には著しい違いがある。特定のメモリ技術が比較的短い待ち時間または読み出しアクセス時間を有し得るのに対して、同じメモリ技術は、用途によっては適さないことがあり得る比較的長い書き込み時間を有し得る。特定のメモリ技術は、特定のメモリロケーションへの比較的少数の書き込み動作に制限され得る。限られた書き込み動作量を超えた後では、情報を確実にメモリロケーションに記憶し、メモリロケーションから検索することができない可能性がある。あるメモリ技術は、他のメモリ技術のおよそ 4 ~ 10 倍の密度であり得、または他のメモリ技術よりもはるかに小さな表面面積／容積を占有し得る。あるメモリ技術は、他のメモリ技術のおよそ半分のコストである。異なるメモリ技術でのメモリアクセス動作中、異なる電力消費率に繋がる様々な電圧または電流が使用され得る。したがって、あるメモリ技術は、他よりも大きな電力を消費する。

20

【発明の概要】

【課題を解決するための手段】

【0 0 0 3】

実施形態は、限定ではなく例として示される。添付図面中の図では、同様の参照番号は同様の要素を指す。

【図面の簡単な説明】

【0 0 0 4】

図面の簡単な説明

30

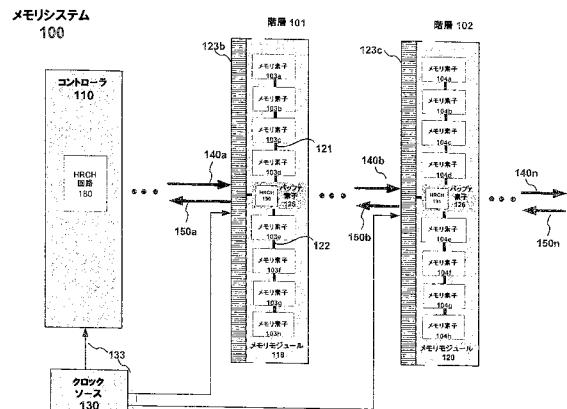

【図 1】メモリモジュールの配置および素子の種類に基づいて論理階層および物理階層に編成された階層メモリシステムを示す。

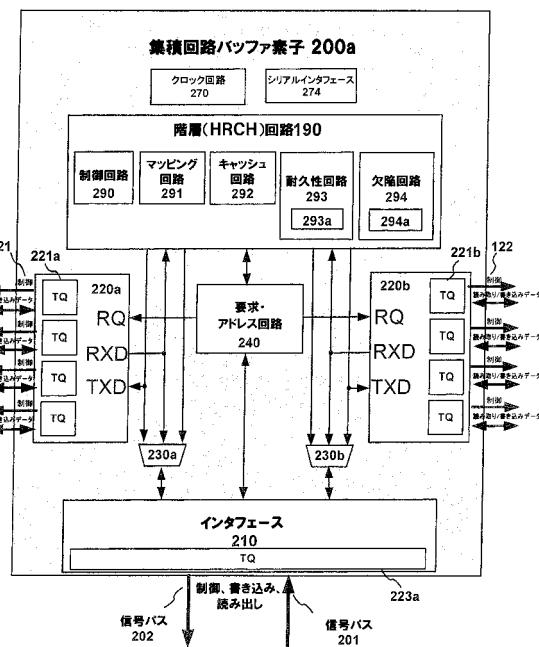

【図 2 A】階層回路を有する集積回路バッファ素子を示す。

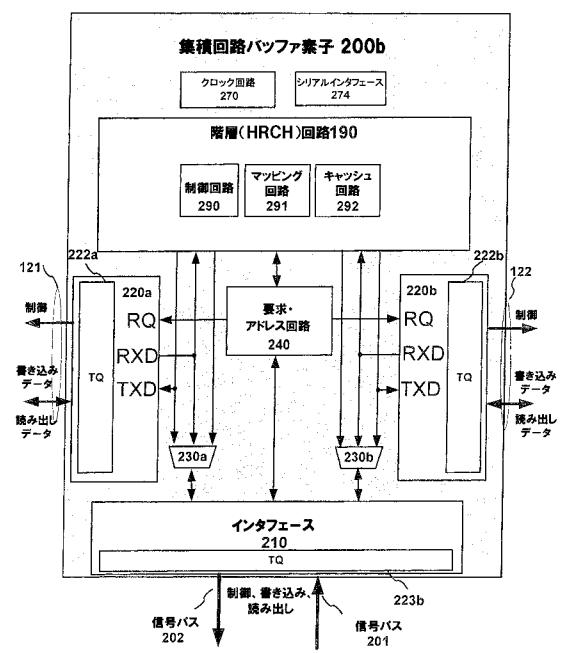

【図 2 B】図 2 A と同様の集積回路バッファ素子を示す。

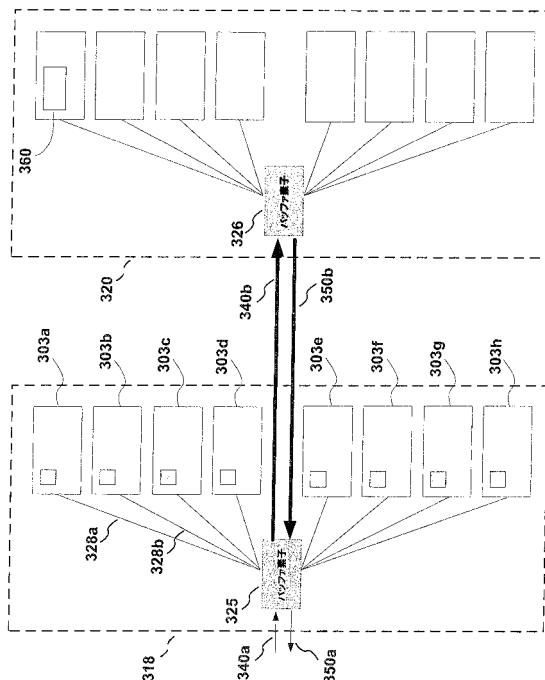

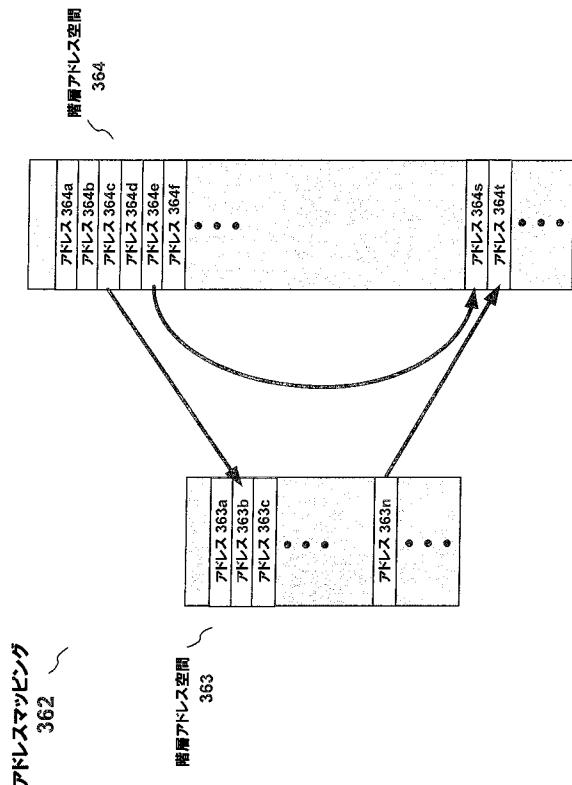

【図 3 A】異なる階層のモジュール間での相対データマッピングを示す。

【図 3 B】異なる階層のモジュール間での相対アドレスマッピングを示す。

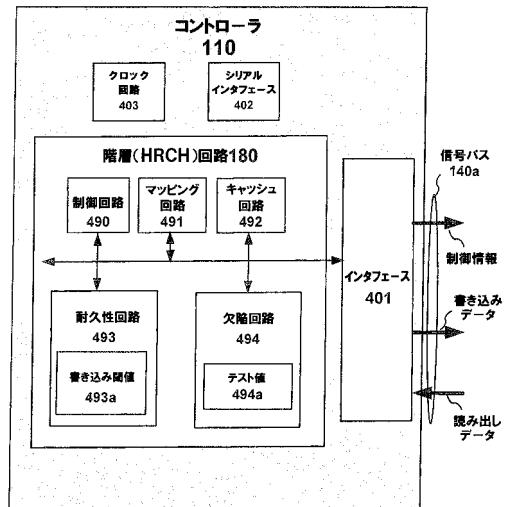

【図 4】階層回路を有するコントローラを示す。

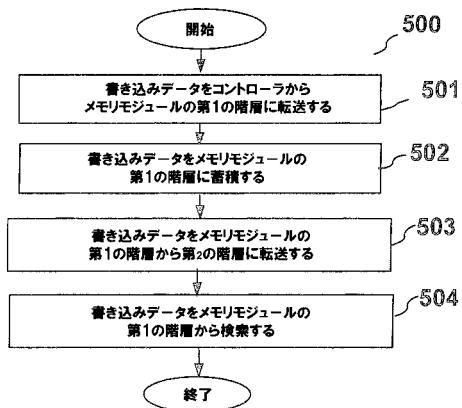

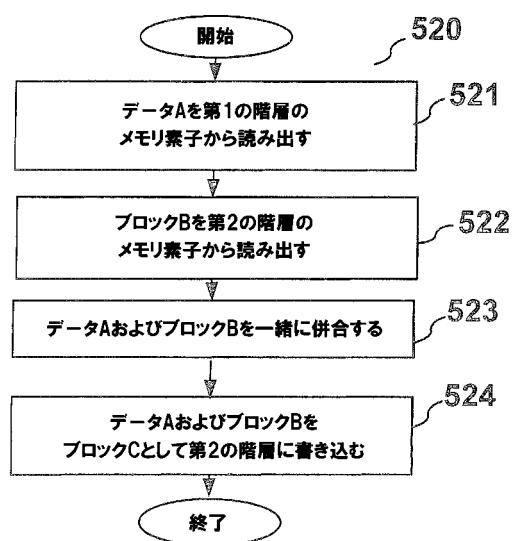

【図 5 A】メモリモジュール階層を有するメモリシステムの動作方法を示すフロー チャートである。

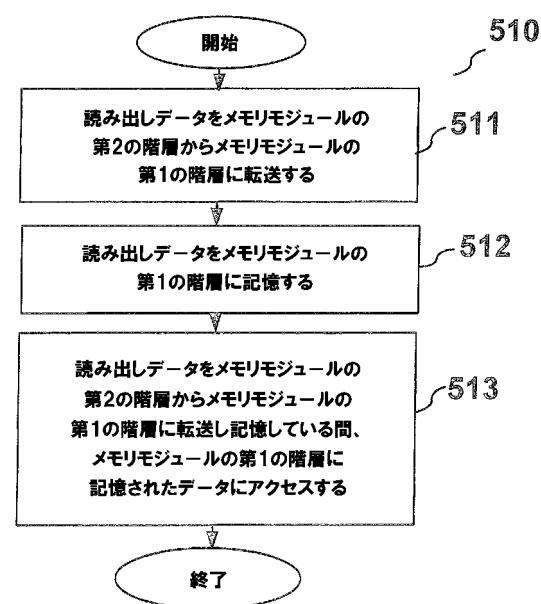

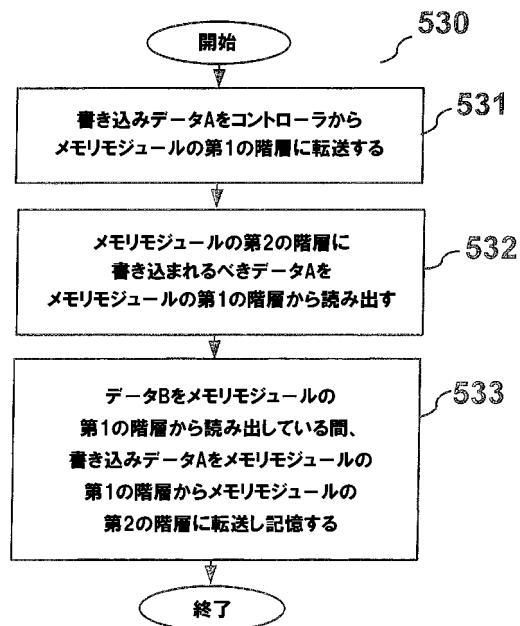

【図 5 B】メモリモジュール階層を有するメモリシステムの動作方法を示すフロー チャートである。

40

【図 5 C】メモリモジュール階層を有するメモリシステムの動作方法を示すフロー チャートである。

【図 5 D】メモリモジュール階層を有するメモリシステムの動作方法を示すフロー チャートである。

【発明を実施するための形態】

【0 0 0 5】

詳細な説明

メモリシステムは、他の実施形態もあるがこの実施形態では、コントローラと、異なる種類の集積回路メモリ素子を有するメモリモジュール階層とを含む。階層（メモリモジュ

50

ールの ) は、特定の種類の集積回路メモリ素子を有する 1 つまたは複数のメモリモジュールを含む。メモリモジュール階層は、単一の種類の集積回路メモリ素子を有するメモリモジュールを有するシステムと比較して、全体的なシステム性能を増大させることができる。第 1 の階層内の第 1 の種類の集積回路メモリ素子を使用することにより、全体的なシステム読み出し待ち時間を低減させ、書き込みデータの耐久性を増大させることができ、その一方で、より少ないコストおよびより低い消費電力を有する第 2 の種類の集積回路メモリを使用することにより、全体的なコストおよび消費電力は低減する。例えば、第 1 の階層は、コントローラおよび第 2 の階層の読み出し / 書き込みキャッシュとして機能することができるよう、少なくとも 1 つの揮発性メモリ素子が第 1 の階層に配置され、少なくとも 1 つの不揮発性メモリ素子が第 2 の階層に配置される。

10

#### 【 0 0 0 6 】

実施形態では、階層はデイジーチェーン様式で結合される。第 1 の信号バスが、コントローラを、揮発性集積回路メモリ素子を有する第 1 のメモリモジュールに結合する。第 2 の信号バスが、第 1 のメモリモジュールを、不揮発性メモリ素子を有する第 2 のメモリモジュールに結合する。制御情報および揮発性メモリ素子に記憶されるべき書き込みデータは、コントローラによって第 1 の信号バスで転送される。制御情報および不揮発性メモリ素子への書き込みデータは、コントローラから第 1 の信号バスで転送され、次いで、第 1 のメモリモジュールによって第 2 の信号バスで転送される。同様に、揮発性メモリ素子および不揮発性メモリ素子に記憶された読み出しデータは、コントローラによって第 1 の信号バスからアクセスされ、そして、第 1 のメモリモジュールによって第 2 の信号バスからアクセスされる。制御情報、読み出しデータ、および書き込みデータは、第 1 のメモリモジュールに配置された集積回路バッファ素子によって第 1 の信号バスと第 2 の信号バスとの間で転送することができる。

20

#### 【 0 0 0 7 】

メモリモジュール階層を有するメモリシステムの動作方法は、他の実施形態もあるがこの実施形態では、第 2 の階層に記憶された書き込みデータブロックを第 1 の階層にバッファ / キャッシュすることを含む。次いで、書き込みデータブロックは、制御信号に応答して、第 1 の階層内にキャッシュされた書き込みデータブロックを第 2 の階層に転送することにより、第 2 の階層にリライト ( またはリフレッシュ / 再記憶 ) することができる。コントローラが第 1 の階層に記憶されたデータ ( 読み出しデータまたは書き込みデータ ) にアクセスしている間、第 2 の階層からの読み出しデータをブロックで第 1 の階層に転送することができる。書き込みデータは、階層内の異なるメモリロケーションにリマッピングして分散させ、書き込み耐久性を最低限に抑えることができる。書き込みデータブロックが第 1 の階層から転送され、第 2 の階層に記憶されている間、第 2 の階層に記憶されるべき書き込みデータを第 1 の階層に記憶し、コントローラによって読み出すことができる。欠陥メモリロケーションが検出された場合、第 2 の階層に記憶されるべき書き込みデータを第 1 の階層内でリマッピングし記憶するか、または第 1 の階層内の異なるメモリロケーションにリマッピングし記憶することができる。

30

#### 【 0 0 0 8 】

図 1 は、メモリコントローラ 110 と、第 1 のメモリモジュール 118 の形態のメモリ素子の第 1 のセットと、第 2 のメモリモジュール 120 の形態のメモリ素子の第 2 のセットとを利用する完全バッファ型メモリシステム 100 の一実施形態を示す。ポイントツーポイントシリアルリンク 140 a、140 b、および 150 a、150 b の形態の上流信号バスおよび下流信号バスのそれぞれは、コントローラをメモリモジュールにデイジーチェーン構成で結合する。クロックソース 130 は、システムクロック信号をコントローラおよびメモリモジュールに配布する。

40

#### 【 0 0 0 9 】

一実施形態では、メモリコントローラ 110 は、完全バッファ型デュアルインラインメモリモジュール ( F B D I M M ) 信号伝送プロトコルに従って、シリアル化された制御信号、アドレス信号および書き込みデータ信号を送信し、シリアル化された読み出しデータ

50

信号を受信するという点で、FBDIMMとの併用に利用されるものと同様であり得る。一般に、これは、多重化された制御信号、アドレス信号、および書き込みデータ信号をコントローラから第1のメモリモジュールに下流シリアルリンク140aに沿って駆動するシリアルリンク送信器の形態の送信回路を含む。コントローラ上の受信器回路は、上流シリアルリンク150aとインターフェースして、シリアル化された読み出しデータを第1のモジュール118から受信する。コントローラは階層回路180を利用して、より完全に以下に開示するように、階層アクティビティを管理することができる。

#### 【0010】

引き続き図1を参照すると、第1のメモリモジュール118は、集積回路（IC）の形態のバッファ素子125と、ダイナミックランダムアクセスメモリ（DRAM）ICの形態の複数の揮発性メモリ素子103a～103hとを含む。バッファICは、コントローラ110および第2のメモリモジュール120と通信するための上流ポートおよび下流ポートの各ペアを含む。一実施形態では、バッファICは、コントローラ階層回路180を補うか、またはコントローラ階層回路180と置換され得る階層回路190を含む。バッファICは、制御／アドレスバスおよびデータバス（明確にするために、単一のバスとして示される）のそれぞれを介してDRAM素子と通信する。DRAM素子は、XDR（n）型またはDDR（n）型であってよく、一般に、非常に高速な読み書き時間および高密度を特徴とし得る。

#### 【0011】

図1をさらに参照すると、第2のメモリモジュール120は第1のメモリモジュール118と同様であり、バッファIC126および複数のメモリ素子104a～104hを有する。しかし、第2のモジュールのメモリ素子は、フラッシュメモリ等の不揮発性の種類のものである。フラッシュ素子は、低コスト、低電力、高密度を特徴とし、DRAMと同様の速度でデータを読み出すことが可能である。しかし、フラッシュ素子への書き込み動作には、通常、完了までに数ミリ秒かかることが多い消去時間が含まれる。さらに、フラッシュ素子は、同じ記憶ブロックへのデータ書き込みの点で限られた耐久性を有する。これに対処するために、バッファICは、より完全に以下に説明するように、不揮発性素子への書き込み動作を最適化する回路を含む。

#### 【0012】

一実施形態では、第1および第2のモジュール118および120は、上流シリアルリンク140および下流シリアルリンク150を介して、ポイントツーポイントディジーチェーン様式で各バッファICを介して相互接続される。このようにして、コントローラ110および第2のモジュール120が関わる任意のトランザクションでは、データは必然的に、第1のモジュール118を通って流れる。不揮発性素子セットよりも揮発性メモリ素子セットをコントローラの近くに位置決めすることにより、第1レベル階層および第2レベル階層のそれぞれを101および102において定義することができる。

#### 【0013】

上述した階層構造は、多くの方法で拡張可能である。例えば、1つまたは複数の揮発性メモリモジュールを第1レベル階層に編成し、第2レベルメモリ階層を確立する1つまたは複数の不揮発性モジュールの上流（コントローラのより近く）に位置決めすることができる。

#### 【0014】

各モジュールの位置および素子の種類によって定義される階層に従ってのシステムの動作をサポートするために、揮発性メモリモジュールおよび不揮発性メモリモジュールのバッファIC125および126は、より完全に以下に説明するように、トランザクションを調整するに当たってメモリコントローラ110を支援するロジックを含む。

#### 【0015】

図2Aは、一実施形態におけるHRCH回路190を有するICバッファ素子200aを示す。ICバッファ素子200aは、図1に示されるICバッファ素子126に対応し、1つまたは複数の不揮発性メモリモジュール120によって利用される。代替の実施形

10

20

30

40

50

態では、H R C H 回路 1 9 0 のうちの 1 つまたは複数の回路は、コントローラ 1 1 0 内に配置されてもよく、またはコントローラ 1 1 0 と I C バッファ素子 1 2 6 との間に分散してもよい。I C バッファ素子 2 0 0 a は、メモリモジュール上に配置してもよく、I C メモリ素子もしくはダイと共に共通のパッケージ内に収容されてもよく、またはパーソナルコンピュータもしくはサーバのマザーボード、例えば、メインメモリに配置されてもよい。I C バッファ素子 2 0 0 a は、埋め込みメモリサブシステム、例えば、コンピュータグラフィックスカード、ビデオゲームコンソール、またはプリンタ等で見出される埋め込みメモリサブシステム内で使用されてもよい。

#### 【 0 0 1 6 】

引き続き図 2 A を参照すると、制御情報、書き込みデータ、および読み出しデータを信号バス 2 0 1 から受信し、制御情報、書き込みデータ、および読み出しデータを、不揮発性集積回路メモリ素子（第 2 レベル階層に関連する）または揮発性集積回路メモリ素子（第 1 レベル階層に関連する）への信号バス 2 0 2 に出力するインターフェース 2 1 0 が示される。一実施形態では、信号バス 2 0 1 は、図 1 に示される信号バス 1 4 0 a、1 4 0 b に対応し、その一方で、信号バス 2 0 2 は信号バス 1 5 0 a、1 5 0 b に対応する。一実施形態では、I C バッファ素子 2 0 0 a に結合された集積回路メモリ素子を対象とした制御情報、書き込みデータ、および読み出しデータの多重化された組み合わせが、インターフェース 2 1 0 を介して受信され、インターフェース 2 1 0 は、例えば、制御情報を抽出することができる。例えば、メモリコマンドおよびアドレス情報を復号化し、信号バス 2 1 0 上の多重化情報から分離し、インターフェース 2 1 0 から要求・アドレス回路 2 4 0 に提供することができる。書き込みデータは、インターフェース 2 1 0 によってインターフェース 2 2 0 a、2 2 0 b に提供することができ、集積回路メモリ素子からの読み出しデータを 1 つまたは複数のインターフェース 2 2 0 a、2 2 0 b において受信し、マルチプレクサ 2 3 0 a、2 3 0 b を介してインターフェース 2 1 0 に提供することができる。

#### 【 0 0 1 7 】

インターフェース 2 2 0 a、2 2 0 b は別個のインターフェースとして示されるが、組み合わせられてもよい。インターフェース 2 2 0 a、2 2 0 b は、不揮発性メモリ素子に送信中であるか、または不揮発性メモリから受信中のデータを記憶するために使用されるトランザクションキュー 2 2 1 a、2 2 1 b を含む。バッファ 2 0 0 a が不揮発性メモリ素子に適用された場合、トランザクションキューは、トランザクションを記憶し、データを单一または制限された数のメモリ素子に宛てる。このデータ編成では、すべての素子ではなく少数のみのメモリ素子に書き込むことによってトランザクションが行われるため、トランザクションによって実行される書き込み動作の数が低減する。メモリ素子に送信中およびメモリ素子から送信中のデータは、インターフェース 2 1 0 内のトランザクションキュー 2 2 3 a に転送されてから、上流シリアルインターフェースおよび下流シリアルインターフェースに送信される。同様に、信号バス 2 0 1 からシリアルに受信されたトランザクションは、トランザクションキュー 2 2 3 a に記憶され、次いで、インターフェース 2 2 0 a、2 2 0 b 内のトランザクションキュー 2 2 1 a、2 2 1 b に転送されてから、メモリ素子に送信される。この編成では、上流リンクおよび下流リンクに接続されたシリアルインターフェース 2 1 0 上の単一のトランザクションが、信号バス 1 2 1 および 1 2 2 に接続された不揮発性メモリ素子のうちの 1 つのみまたは 2 つのみにマッピングされる。

#### 【 0 0 1 8 】

一実施形態では、クロック信号および他の情報が、信号バス 2 0 1 上で、またはシリアルバス等の他のバスによって受信される。一実施形態では、インターフェース 2 1 0 は、信号を信号バス 2 0 2 に出力し、信号バス 2 0 1 上で受信するために、送信回路または送信器と、受信器回路または受信器（またはまとめて送受信器と呼ばれる）を含む。同様に、インターフェース 2 2 0 a および 2 2 0 b は、それぞれ信号バス 1 2 1 および 1 2 2 を介して制御情報、読み出しデータ、および書き込みデータを集積回路メモリ素子に送信し、集積回路メモリ素子から受信する。一実施形態では、インターフェース 2 2 0 a、2 2 0 b は、信号バス 1 2 1 および 1 2 2 に信号を出力し、信号バス 1 2 1 および 1 2 2 に信号を受

10

20

30

40

50

信する送信器および受信器を含む。実施形態では、インターフェース 210、220a、および220b内の送信器および受信器は、単独または組み合わせで、信号バス121および122内の特定の信号線専用であるか、または共用される。

#### 【0019】

一実施形態では、インターフェース 220a、220b内の送信器および受信器は、同期 N A N D 型 (Synch Nand) フラッシュまたはN O R 型フラッシュ書き込み / 読み出し / 消去 / 制御信号等の標準揮発性メモリ素子信号伝送特性 (またはプロトコル) を有する信号を送受信する。

#### 【0020】

一実施形態では、インターフェース 220a、220bは、制御情報を单方向信号バスで 10 転送する送信器を含む一方で、書き込みデータおよび読み出しデータを双方向信号バスで転送する、書き込みデータおよび読み出しデータ用の送信器および受信器を含む。一実施形態では、インターフェース 220a、220b、および210内の送信器は、単独または組み合わせで、信号バス121、122、および401上に各信号を出力する出力ドライバ回路である。出力ドライバ回路は、プルアップ型、プルダウン型、および / またはプッシュプル型の出力ドライバ回路であつてよい。

#### 【0021】

一実施形態によれば、マルチプレクサ 230a および 230b は、インターフェース 210 とインターフェース 220a および 220b の間で帯域幅集約動作を実行すると共に、データを適切な発信元 (すなわち、信号バスのターゲットサブセット、内部データキャッシュ - キャッシュ回路 292) から適切な宛先にルーティングする。一実施形態では、帯域幅集約は、複数の信号バス実施形態内の各信号バスの (より小さな) 帯域幅を結合して、より小さな信号バスグループで利用される (より高い) 全体帯域幅に合わせることを含む。帯域幅集約は、通常、複数の信号バスとより小さな信号バスグループとの間でスループットの多重化および多重分離を利用する。一実施形態では、I C バッファ素子 200a は、インターフェース 210 の帯域幅と合ったインターフェース 220a および 220b の結合帯域幅を利用する。

#### 【0022】

図 2A をさらに参照すると、一実施形態では、H R C H 回路 190 は、制御回路 290 、マッピング回路 291 、キャッシュ (または記憶) 回路 292 、耐久性回路 293 (1つまたは複数の記憶された書き込み閾値 293a を含む) 、および欠陥回路 294 (1つまたは複数の記憶された欠陥メモアドレスを含む) を単独または組み合わせで含む。I C バッファ 200a 内に示された回路は、図 4 に示すように結合され得る。H R C H 回路 190 の 1つまたは複数の回路構成要素も、各種実施形態では、H R C H 回路 190 内ではなく、コントローラ 110 内、特に H R C H 回路 180 内に配置され得る。

#### 【0023】

制御回路 290 は、H R C H 回路 190 内の回路への制御信号の提供およびそのような回路からの制御信号の受信を担当する。一実施形態では、制御回路 290 は、インターフェース 210 から信号バス 201 を介して制御信号および / または値を受信することができる。制御情報は、コントローラ 110 、プログラマブル回路 (S P D 素子等) 、および / または別のメモリモジュールからのコマンドの形態で提供され得る。一実施形態では、制御回路 290 は、プロセッサ、コントローラユニット、および / または制御ロジックである。制御回路 290 は、図 4 に示される信号バス 405 と同様に、信号バスによって H R C H 内の他の回路に結合される。読み出しデータ、書き込みデータ、およびアドレス、ならびに制御信号は、信号バスを使用して回路間で転送され得る。一実施形態では、制御回路 290 は、I C バッファ素子 200a も操作し、圧縮 / 圧縮解除エンジンを含み得る。

#### 【0024】

マッピング回路 291 は、書き込み / 読み出しデータに関連するアドレスまたはメモリロケーションのリマッピングまたは再割り当てを担当する。マッピング回路 291 は、制御回路 290 (および / または耐久性回路 293 および欠陥回路 294) からの制御信号

10

20

30

40

50

に応答して、アドレスおよびデータを図3Aおよび図3Bに示されるようにリマッピングする。一実施形態では、マッピング回路291は、アドレス変換回路を含み得る。マッピング回路291は、キャッシング回路292内の関連する読み出し／書き込みデータと共に記憶されたアドレスをリマッピングし得る。マッピング回路291は、データをインタフェース210からインタフェース220内の適切なトランザクションキューに宛て、インタフェース210から受信したアドレスを選択された適切な素子およびメモリアドレスに変換し、変換されたものはインタフェース220a、220bに送信される。一般に、必要とされる書き込み動作の数を低減するために、揮発性メモリシステム内で、インタフェース210からの単一のトランザクションは1つまたは少数のメモリ素子に宛てられ、インタフェース210上の連続したアドレスが、単一のメモリ素子内の連続したロケーションに宛てられる。10

#### 【0025】

キャッシング回路292は、コントローラまたは別のメモリモジュールからの読み出し／書き込みデータを記憶するために使用される。一実施形態では、読み出し／書き込みデータは、システム100内のメモリロケーションへの関連するアドレスと共に記憶される。読み出し／書き込みデータは、64Kバイト、128Kバイト、256Kバイト、および／または512Kバイトのブロック等の連続したワードまたはバイトのグループで記憶し集めることができる。この場合、これらブロックをグループとして転送し記憶することができる。例えば、256Kバイトの書き込みデータブロック（信号バス140aおよび140bを介してコントローラ110から受信した）をバッファ素子125bのキャッシング回路292に記憶し、信号バス140cを介して、書き込みデータが記憶されている（または一実施形態では、前回の書き込み後に再記憶された）メモリモジュール120cに転送することができる。別の実施形態では、特定のメモリモジュールに関連付けられた集積回路メモリ素子が、キャッシング回路292に代えて、データブロックの記憶に使用される。20

#### 【0026】

耐久性回路293は、システム100内の特定のメモリロケーション（または複数のメモリロケーション）において行われた書き込み動作の数に基づいて、書き込み／読み取りデータをリマッピングすべきか否かを決定することを担当する。一実施形態では、耐久性回路293は、書き込み閾値を記憶し、または特定のメモリロケーションへのさらなる書き込みまたは記憶の確実性がなくなる危険性が生じる以前に、特定のメモリロケーションへの書き込み回数を制限する1つまたは複数のレジスタ等の記憶回路を含む。一実施形態では、耐久性回路293は、特定のメモリロケーションへの書き込み回数をカウントするカウンタと、カウント値を記憶している書き込み閾値と比較する比較回路とも含む。次いで、比較回路は、比較に応答して、特定のメモリロケーションに書き込むべきではないことを示す制御信号を制御回路290に出力し得る。次いで、マッピング回路291は、新しいアドレスを、1つまたは複数のメモリモジュールに記憶されるべき書き込み／読み出しデータに割り当てることができる。耐久性回路293は、特定のメモリロケーションに他のメモリロケーションほどはまだ書き込まれていないことを示す制御信号も生成し得、したがって、マッピング回路291は、不揮発性集積回路メモリ素子に記憶された書き込み／読み出しデータの分散を可能にする。3040

#### 【0027】

欠陥回路294は、1つまたは複数のメモリロケーションが欠陥を有するか否か、または情報を正確に記憶し出力していないかどうか決定することを担当する。一実施形態では、欠陥回路294は、制御回路290からの制御信号に応答して、別のメモリモジュール内の1つまたは複数のメモリロケーションに書き込まれる複数のテスト値294aを記憶する。次いで、比較回路により、他のメモリモジュールに記憶されたテスト値が再びI Cバッファ素子200aに読み出され、記憶された複数のテスト値294aと比較される。比較回路は、比較に応答して、メモリロケーションが欠陥を有することを示す信号を出力する。次いで、書き込み／読み出しデータのさらなるリマッピングが、識別された欠陥メ50

モリロケーションを含まないように、制御信号をマッピング回路 291 に出力することができる。一実施形態では、欠陥回路 294 は、制御回路 290 および / またはマッピング回路 291 によってアクセスされ得る欠陥メモリロケーションのアドレスを記憶する。一実施形態では、複数のテスト値 294a は、コントローラ 110 によって提供される疑似乱数生成器により、テストパターンとして生成されるか、または別のメモリモジュールの内容を読み取ることによって得られる。

#### 【 0028 】

代替の実施形態では、欠陥回路 294 は、メモリロケーションからの電流 / 電圧を感じし、電流 / 電圧を表す記憶されている値と比較して、メモリロケーションが欠陥を有するか否かを決定する感知回路を含む。

10

#### 【 0029 】

各種実施形態では、H R C H 回路 190 を含む I C バッファ素子 200a は、異なる動作モードで動作する。第 1 の動作モードでは、I C バッファ素子 200a は、別のメモリモジュールおよび / またはコントローラによってアクセスされるべき読み出し / 書き込みデータを記憶する。第 2 の動作モードでは、I C バッファ素子 200a は、別のメモリモジュール内のアドレスを読み出し / 書き込みデータに割り当て、データおよびアドレスを別のメモリモジュールに転送し、次いで、別のメモリモジュールは読み出し / 書き込みデータを記憶する。

#### 【 0030 】

クロック回路 270 は、外部クロックを基準にして内部クロック信号の位相または遅延を調整するための 1 つまたは複数のクロックアラインメント回路を含む。クロックアラインメント回路は、クロックソース 130 等の既存のクロック発生器からの外部クロックを利用してよく、または内部クロックを提供し、所定の時間関係を有する内部同期クロック信号を生成する内部クロック発生器を利用してよい。一実施形態では、クロック回路 270 は、位相ロックループ回路または遅延ロックループ回路を含む。一実施形態では、クロックアラインメント回路は、転送または受信された制御情報、読み取りデータ、および / または書き込みデータに対して時間関係を有する内部クロック信号を提供する。

20

#### 【 0031 】

実施形態では、インターフェース 220a、220b（ならびにインターフェース 210）内の送信器は、符号化クロック情報を含む差分信号を送信し、受信器は、符号化クロック情報を含む差分信号を受信する。一実施形態では、クロック回路 270 は、受信器によって受信されたデータに符号化されたクロック情報を抽出する。さらに、クロック情報は、送信器によって送信されるデータにも符号化される。例えば、クロック情報は、所与のデータビット数中に発生する信号遷移数が最小になることを保証することにより、データ信号に符号化してもよい。

30

#### 【 0032 】

シリアルインターフェース 274 は、シリアル情報をコントローラ 110、別の I C バッファ素子、または実施形態での他の構成回路から受信し / に送信するインターフェースである。シリアル情報は、I C バッファ素子 200a またはメモリモジュールの初期化値 / 信号を含むことができる。一実施形態では、シリアルインターフェース 274 は、コントローラ 110 によって使用されて、1 つまたは複数の書き込み閾値 293a および / またはテスト値 294a 等の値を H R C H 回路 190 に記憶し、かつ / または H R C H 回路 190 内の値を読み出す。

40

#### 【 0033 】

図 2B は、図 2A に示されるバッファ I C 200a と同様であるが、揮発性メモリモジュール 118（図 1）と併用されるバッファ I C 200b を示す。2 つのバッファ I C の回路の大半は同様であり、簡潔にするために、再び説明しない。しかし、耐久性回路 293a および欠陥回路 294a（図 2A）の省略等の回路に対する特定の変更が利用され得る。さらに、トランザクションキューおよびマッピング回路は、不揮発性モジュールバッファ I C 200a によって利用されるデータマッピングと異なるようにデータマッピング

50

グを処理する。

**【0034】**

マッピング回路291は、一般に、データをインターフェース220に宛てると共に、インターフェース220からデータをすべての素子に並列に宛てるよう構成され、同様のアドレスが、素子のうちのすべてまたは大半に同時に送信され、多くのデイス(deice)が単一のトランザクションによって選択される。

**【0035】**

インターフェース220a、220bは別個のインターフェースとして示されるが、組み合わせてもよい。インターフェース220a、220bは、揮発性メモリ素子に送信中または揮発性メモリ素子から受信中のデータの記憶に使用されるトランザクションキュー222a、222bを含む。バッファ200bがDRAMのような揮発性メモリ素子に適用される場合、トランザクションキューは、多くの素子に宛てられ、多くの素子に分散してトランザクションを記憶する。この場合、素子の結合帯域幅は並列にアクセスされて、トランザクションの帯域幅が最大化される。メモリ素子に送信中のデータおよびメモリ素子から送信中のデータは、インターフェース210内のトランザクションキュー223bに転送されてから、上流シリアルインターフェースおよび下流シリアルインターフェースに送信される。同様に、信号バス201からシリアルに受信されたトランザクションは、トランザクションキュー223bに記憶され、次いで、222a、222bにおけるトランザクションキューに転送されてから、メモリ素子に送信される。この編成では、インターフェース210内の上流リンクまたは下流リンク上の単一のトランザクションは、メモリから読み出されるとき、または書き込まれるときに、複数のメモリ素子にアクセスする。

10

**【0036】**

上述したように、フラッシュメモリ素子およびDRAMメモリ素子は、多くの異なる特性を有する。さらなる違いには、データ書き込み動作が素子内でどのように実行されるかが含まれる。

**【0037】**

図3Aは、DRAMベースのFBDIMMモジュール318とフラッシュベースのFB DIMMモジュール320との間の相対データマッピングの一例を示す。DRAMベースのFBDIMMメモリモジュール内では、モジュール上のDRAM素子303a～303hがデータバス幅を定義する。そして、この幅は、各クロックエッジにおいてすべてのDRAMに同時に書き込むことが可能なビット数を示す。同時書き込みのそれぞれは、図3Aの揮発性素子303a～303h内の影付きエリアによって象徴的に示されるように、各DRAM内の同じアドレスにおいて実行される。したがって、各クロックサイクル中に、データの部分が各DRAMに書き込まれる。バッファIC325は、シリアル化解除回路(図示せず)を提供して、上流シリアルリンク340aまたは下流シリアルリンク350bから受信されたシリアルストリームを並列データストリームに変換し、並列データバス328a～328hに沿って個々のDRAM素子に送信する。

30

**【0038】**

並列同時書き込み方式は、DRAMベースのメモリモジュールではうまく機能する一方で、種々の理由により、フラッシュベースのモジュール用のこのような方法は非現実的である。フラッシュ素子は、多くの場合、ブロックと呼ばれるメモリ単位で消去および再プログラムを行う。さらに、データをフラッシュ素子に記憶または書き込むには、ブロックを空にするか、または消去しなければならない。その結果、大半の場合、消去動作が書き込み動作の前に行われる。さらに、上述したように、フラッシュ素子は、通常、制限された書き込み耐久性を有する。

40

**【0039】**

図3Aをさらに参照すると、フラッシュベースのFBDIMMモジュール320は、最小数の素子を利用して、1つまたは複数の指定ブロック360(影付きブロックとして示される)内にデータを記憶するように、下流シリアルリンク340bから受信したシリアルデータをリマッピングするバッファIC326を含む。これにより、書き込み動作がブ

50

ロック当たりの利用可能ストレージ利用率を最大化し、すべての素子の耐久性に影響する書き込み動作の数を最小化することが保証される。このマッピングは、2つのモジュール間で上流バスに沿って逆方向にも作用することができる。このような状況では、所与のロックからのデータは、示されるマッピングと同様に、複数のDRAMにリマッピングされる。

#### 【0040】

図3Bは、第1の階層アドレス空間363と第2の階層アドレス空間364との間でのアドレスマッピング362を示す。一実施形態では、第1のアドレス空間363は、階層101（揮発性集積回路メモリ素子を有する）内のアドレス空間（またはアドレス指定可能なメモリロケーションの量）に対応し、階層アドレス空間364は、階層102（不揮発性ICを有する）内のアドレス空間に対応する。階層アドレス空間363は、少なくとも、アドレス指定可能なメモリロケーション366a～366nを含み、階層アドレス空間364は、少なくとも、アドレス指定可能なメモリロケーション368a～368tを含む。一実施形態では、階層アドレス空間364は、階層アドレス空間363よりもかなり大きい。本明細書において説明したように、回路および／または実行可能命令は、データを階層アドレス空間363または階層アドレス空間364にマッピングまたは割り当てる。一実施形態では、関連するデータは、一時には、階層アドレス空間363または364のうちの一方内のアドレスが割り当てられ、次いで、前に割り当てられていた階層アドレス空間内の異なるメモリロケーションまたは異なる階層アドレス空間内の異なるメモリロケーションにおける異なるアドレスがリマッピングまたは割り当てられた読み出しデータおよび／または書き込みデータであり得る。一実施形態では、図3Bに示されたメモリロケーションは、連続したメモリロケーションのブロックまたはグループに対応する。

10

20

#### 【0041】

例えば、メモリロケーション364aに記憶された、または記憶されるべきデータには、メモリロケーション363bへのアドレスがマッピングまたは割り当てられ、メモリロケーション363bに記憶される。同様に、メモリロケーション363nに記憶された、または記憶されるべきデータには、メモリロケーション364tへのアドレスがマッピングされ、メモリロケーション364tに記憶される。

#### 【0042】

メモリロケーション364eが割り当てられたデータに、メモリロケーション364sを再割り当てし、階層アドレス空間364内のメモリロケーション364sに記憶してもよい。階層アドレス空間364内のデータの再割り当ておよび記憶は、所定数の書き込み動作が特定のメモリロケーションにおいて発生した場合、かつ／または特定のメモリロケーションが欠陥を有するか、または信頼性が低いと判断された場合に行うことができる。

30

#### 【0043】

図4は、HRC H回路180を有する、図1に示されるコントローラ110を示す。HRC H回路180は、図2Aおよび図2Bに示されるHRC H回路190と同様に動作する。コントローラ110は、信号バス140a上で制御情報および読み出し／書き込みデータを転送する、インタフェース310と同様のインタフェース401も含む。コントローラ110は、制御データおよび読み出し／書き込みデータの同期および転送に使用される、クロック回路370と同様のクロック回路403も含む。シリアルインタフェース402は、I Cバッファ素子125a、125b、126a、および126b内のシリアルインタフェース374と共に使用されて、コントローラ110とI Cバッファ素子125a、125b、126a、および126bとの間にシリアル情報を提供する。

40

#### 【0044】

一実施形態では、コントローラ110またはI Cバッファ素子300の制御回路390は、システム100内の階層の数および種類を示す情報をSPD素子等の記憶回路から読み出す。次いで、制御回路390は、SPD素子から読み出された情報に応答して、適切な制御信号を生成することができる。

#### 【0045】

50

動作に際して、上述したシステムは、モジュールの位置（例えば、上流か下流か）および素子の種類（例えば、揮発性か不揮発性か）に基づいて階層を確立することができる。上流バスおよび下流バスを含む F B D I M M のようなインフラストラクチャに結合された場合、このような構造は、準拠違反の問題を回避しながら、揮発性メモリおよび不揮発性メモリの恩恵を利用する。

#### 【0046】

図 5 A ~ 図 5 D は、図 1 に示されるシステム 100 の動作方法 500、510、520、および 530 を示す。上述したデイジーチェーン接続されたポイントツーポイントリンク構造を利用するにより、後述する方法の多くは、同時に実行される複数の動作を含む。さらに、実施形態では、図 5 A ~ 図 5 D に示される論理ブロックは、単独または組み合わせでのハードウェア（例えば、回路）、ソフトウェア（実行可能な命令）、またはユーザの動作を表す。例えば、他の回路を有する、図 1 に示される H R C H 回路は、単独または組み合わせで、動作を実行することができる。示されていない他の論理ブロックを各種実施形態において含んでもよい。同様に、示されている論理ブロックは、各種実施形態において除外されてもよい。方法 500、510、520、および 530 について逐次論理ブロックで説明するが、方法の論理ブロックによって表される動作は、非常に素早く完了されるか、または略瞬時に完了され、同時に実行し得る。

#### 【0047】

図 5 A に示される方法 500 は、書き込みデータのバッファリングを含み、501 において、書き込みデータをメモリコントローラ 110 から 1つまたは複数のメモリモジュールの第 1 の階層 101 に転送することによって開始される。502 において、書き込みデータは第 1 の階層内で蓄積もされ、所定数の連続ビット値または書き込みデータブロックに集めることができる。次いで、503 において、第 1 の階層内に蓄積された書き込みデータを第 1 の階層のモジュールから第 2 の階層 102 の 1つまたは複数のメモリモジュールに転送することができる。次いで、504 において、第 1 の階層に記憶された書き込みデータを退避させることができる。方法 500 では、第 1 の階層は、第 2 の階層の書き込みキャッシュとして機能する。第 2 の階層モジュール内の不揮発性メモリ素子に関連する書き込み待ち時間は約数ミリ秒であり得るため、これは重要である。データが第 1 の階層から第 2 の階層に転送されている間に、書き込みデータを第 1 の階層内にキャッシングすることにより、コントローラは、第 2 の階層モジュールを待つ必要なく、他の動作を同時に実行することができる。

#### 【0048】

図 5 B は、第 1 の階層 101 が（コントローラ 100 に対して）第 2 の階層 102 の読み出しデータの読み出しキャッシュとして機能する、読み出しデータをキャッシングする方法 510 を示す。方法 510 は、511 および 512 において、読み出しデータを所定数の連続ビット値または読み出しデータブロックに集め、次いで、読み出しデータを第 2 の階層から第 1 の階層に転送することによって開始される。第 1 の階層は、513 において、読み出しデータブロックが第 2 の階層から第 1 の階層に転送されている間、コントローラと同時に書き込み動作および読み出し動作を同時に実行することができる。本明細書において説明する階層システムによって提供される別の有益な方法は、書き込みデータの併合を含む。場合によっては、いくつかの所望のデータの部分が第 2 の階層 102 内のモジュールにすでに記憶されている間、別の部分を第 1 の階層 101 内のモジュールに記憶することができる。第 2 の階層（不揮発性素子を有する）内のブロックへのいかなる書き込みも、まず、ブロック全体の内容を消去することを含む。したがって、ブロックの元の内容の消失を回避するために、図 5 C に示される「読み出し - 変更 - 書き込み」の形態の一連のステップを利用することができる。

#### 【0049】

図 5 C をさらに参照すると、書き込みデータを併合する方法 520 は、まず、521 において、所望のデータ「データ A」をモジュールの第 1 の階層 101 内の揮発性メモリ素子から読み出すことを含む。データは、揮発性メモリモジュールバッファ I C 125 また

10

20

30

40

50

は不揮発性メモリモジュールバッファ I C 1 2 6 のうちの一方に一時的に記憶することができる。次いで、ステップ 5 2 2 に示されるように、不揮発性素子からの所望のデータブロック「ブロック B」が、第 2 の階層 1 0 2 内のメモリモジュールから読み出され、データ A を記憶している同じバッファ I C 内に一時的に記憶される。次いで、ステップ 5 2 3 において、データ A およびブロック B は、バッファ回路によって一緒に併合される。次いで、5 2 4 において、併合データ「データ A」および「ブロック B」は、単一のデータブロック「ブロック C」として再び第 2 の階層に書き込まれる。

#### 【 0 0 5 0 】

図 5 D は、5 3 1 において、書き込みデータ A を第 1 の階層 1 0 1 に転送することによって開始される方法 5 3 0 を示し、書き込みデータ A は、書き込みデータブロックに記憶またはキャッシュされてから、第 2 の階層 1 0 2 に書き込まれる。5 3 2 において、第 1 の階層内にキャッシュされた書き込みデータ A のブロックがアクセスされる。次いで、5 3 3 において、キャッシュされた書き込みデータ A のブロックは、第 1 の階層から第 2 の階層に転送され、第 2 の階層に記憶され、その間、第 1 の階層内のデータ B が、読み出し動作等を通して同時にアクセスされる。図 5 D は、同時動作を含む方法の一実施形態を示すが、コントローラならびにバッファ素子 1 1 0 、1 2 5 、および 1 2 6 を相互接続するディジーチェーン接続された上流ポイントツーポイントリンク 1 4 0 a ~ 1 4 0 n および下流ポイントツーポイントリンク 1 5 0 a ~ 1 5 0 n により、同時動作の各種実施形態が可能である。例えば、コントローラ 1 1 0 と第 1 の階層のメモリ素子との間の読み出し動作および / または書き込み動作は、第 1 レベルのメモリ階層と第 2 レベルのメモリ階層との間で実行される書き込み動作および / または読み取り動作と同時に実行することができる。

10

20

#### 【 0 0 5 1 】

図 1 に示された実施形態に戻ると、メモリモジュール 1 2 0 a ~ 1 2 0 d は、信号バス 1 4 0 a ~ 1 4 0 d に結合するための、ピンおよび / またはボール等の複数の導通接点を有するインターフェース 1 2 3 a ~ 1 2 3 d を有する基板を含む。一実施形態では、複数の接点、はんだボール、またはピンがインターフェースに含まれ、インターフェースとメモリモジュール基板との間に電気接続を提供する。一実施形態では、インターフェースは、コネクタまたはプリント回路基板等の基板から着脱可能であり得る。一実施形態では、コントローラ 1 1 0 、集積回路メモリ素子 1 0 3 a ~ 1 0 3 p および 1 0 4 a ~ 1 0 4 p 、ならびに I C バッファ素子 1 2 5 a 、1 2 5 b 、1 2 6 a 、および 1 2 6 b は、集積モノリシック回路に別個に収容され、かつ / または複数のパッケージ内で結合される（例えば、単一のパッケージ内のメモリ素子およびバッファ素子）。パッケージは、1 つまたは複数の基板上に配置することができる。

30

#### 【 0 0 5 2 】

一実施形態では、1 つまたは複数の信号バス 1 4 0 a ~ 1 4 0 d は、1 つまたは複数の信号線を示すポイントツーポイントリンクであり、各信号線は、2 つのみの送受信器接続ポイントを有し、各送受信器接続ポイントは、送信器回路、受信器回路、または送受信器回路に結合される。例えば、ポイントツーポイントリンクは、一端に、またはその近傍に結合された送信器と、他端に、またはその近傍に結合された受信器とを含むことができる。

40

#### 【 0 0 5 3 】

実施形態では、1 つまたは複数の信号バス 1 4 0 a ~ 1 4 0 d は、異なる種類のバスまたはポイントツーポイントリンク構造を含むことができる。実施形態では、信号バスは、異なる種類の信号伝送およびクロッキング種別構造を有することもできる。異なるリンク構造を有する実施形態は、同時双方向リンク、時間多重化双方向リンク、および複数の單方向リンクを含む。電圧モード信号伝送または電流モード信号伝送は、これらリンク構造またはバス構造の任意のものに利用することができる。一実施形態では、信号バス 1 4 0 a ~ 1 4 0 d は、S M B u s 等のシリアルデータバスを含む。シリアルデータは、シリアルインターフェース 4 7 4 を介してコントローラ 1 1 0 を1 つまたは複数の I C バッファ素

50

子 1 2 5 a、1 2 5 b、1 2 6 a、および 1 2 6 b に結合することができる。

#### 【0054】

一実施形態では、1つまたは複数のメモリモジュール 1 2 0 a ~ 1 2 0 d は、標準 D I M M フォームファクタを有するデュアルラインメモリモジュール（「D I M M」）である。一実施形態では、メモリモジュールは、「システムインパッケージ」（「S I P」）のように、単一の単体パッケージに含むことができる。一種の S I P 実施形態では、メモリモジュールは、互いの上に積み重ねられ、導電性相互接続を介して結合された一続きの集積回路ダイ（すなわち、メモリ素子およびバッファ素子）を含むことができる。はんだボールまたは配線リードは、メモリモジュールをプリント回路ボード基板に固定して取り付けることができるよう、コネクタインタフェースとして利用することができる。コネクタインタフェースは、例えば、メモリモジュールがシステムの残りの部分から着脱可能なように、オス型部およびメス型部を含む物理的に分離可能な種類のものであってもよい。別の S I P 実施形態は、二次元構成で共通の基板平面上に配置され、単一のパッケージ筐体内に置かれたいくつかのメモリ素子およびバッファ素子を含むことができる。10

#### 【0055】

図 1 に示される実施形態では、集積回路メモリ素子 1 0 3 a ~ 1 0 3 p および 1 0 4 a ~ 1 0 4 p は、異なる種類の集積回路メモリ素子を含む。例えば、集積回路メモリ素子 1 0 3 a ~ 1 0 3 p は、揮発性集積回路メモリ素子であってもよく、その一方で、集積回路メモリ素子 1 0 4 a ~ 1 0 4 p は不揮発性集積回路メモリ素子であってもよい。一実施形態では、揮発性集積回路メモリ素子は、電力が素子から除去されると、記憶された情報が失われる複数のメモリセルを含む。これとは対照的に、一実施形態では、不揮発性集積回路メモリ素子は、電力が素子から除去されても情報が保持される複数のメモリセルを含む。20

#### 【0056】

揮発性メモリ素子の種類としては、ダイナミックランダムアクセスメモリ（「D R A M」）、分子電荷ベース（molecular charge-based）（ZettaCore）D R A M、浮遊ボディ（floating-body）D R A M、およびスタティックランダムアクセスメモリ（「S R A M」）が挙げられるが、これらに限定されない。D R A M の特定の種類としては、ダブルデータレート S D R A M（「D D R」）または後世代の S D R A M（例えば、「D D R 2」または「D D R 3」）、ならびに X D R（商標）D R A M または DIRECT RAMBUS（登録商標）D R A M（「D R D R A M」）が挙げられる。30

#### 【0057】

不揮発性メモリ素子の種類としては、電気的消去可能プログラム読み取り専用メモリ（「E E P R O M」）、フラッシュ（N A N D 型フラッシュおよびN O R 型フラッシュを含む）、O N O 型フラッシュ、磁気抵抗 R A M または磁気 R A M（「M R A M」）、強誘電性 R A M（「F R A M」）、ホログラフィック媒体、オボニック／位相変化、ナノ結晶、ナノチューブ R A M（Nanotube RAM）（N R A M - N a n t e r o）、M E M S 走査プロープシステム、M E M S カンチレバースイッチ、ポリマー、分子、ナノ浮遊ゲート、および单電子が挙げられるが、これらに限定されない。

#### 【0058】

不揮発性メモリ素子のいくつかの種類の一特性は、一度にバイトまたはワードをランダムアクセス様式で読み出し、またはプログラム／書き込むことができるが、一度にブロックを消去しなければならないことである。新しく消去されたブロックから始まり、そのブロック内の任意のバイトをプログラムすることができます。しかし、バイトがプログラムされると、通常、ブロック全体が消去されるまで、再び変更することができない。例えば、N O R 型フラッシュメモリ素子は、ランダムアクセスでの読み出し動作およびプログラム動作を提供することができるが、通常、ランダムアクセスでの書き換え動作または消去動作を提供することができない。40

#### 【0059】

集積回路メモリ素子は、複数の感知増幅器と共に行・デコーダ回路（row and decoder

50

circuit) によって(ワードおよびビットラインを介して)二次元メモリセルの1つまたは複数のストレージアレイ(またはバンク)を含むことができる。様々な量の電圧または電流を、ストレージアレイ内の1つまたは複数のメモリセルに付与して、論理値(例えば、論理1または論理0)に対応する電圧値を記憶したメモリセルのプログラム(書き込み)、読み出し、および/または消去を行うことができる。

#### 【0060】

図1に示される実施形態では、コントローラ110はマスタ装置であり、他のインタフェースまたは機能、例えば、チップセットのノースブリッジチップを含む集積回路素子であることができる。マスタ装置は、マイクロプロセッサまたはグラフィックスプロセッサユニット(「GPU」)またはビジュアルプロセッサユニット(「VPU」)上に集積することができる。マスタ装置は、フィールドプログラマブルゲートアレイ(「FPGA」)として実施することができる。システム100は、サーバ(例えば、ブレードサーバ)、パーソナルコンピュータ、グラフィックスカード、セットトップボックス、ケーブルモデル、携帯電話、ゲームコンソール、デジタルテレビジョンセット(例えば、高精細テレビジョン)(「HDTV」)、ファックス機、ケーブルモデル、デジタル多用途ディスク(「DVD」)プレーヤ、またはネットワークルータ等の様々なシステムまたはサブシステムに含むことができる。10

#### 【0061】

図1に示される実施形態では、システム100は、キーワードの入力に応答して、インターネット上に記憶されたウェブサイト(またはページ)へのハイパーリンク、イメージ、および/または動画を含む検索結果を提供する検索エンジンとして実行または機能する際に使用されるサーバに使用することができる。検索エンジン実施形態では、検索頻度の高い情報(例えば、最近の検索結果)は階層101に記憶することができ、その一方で、検索頻度が低い情報(例えば、インデックス)は階層102に記憶することができる。20

#### 【0062】

本明細書において説明した信号は、導電体によってコントローラ/メモリモジュール/素子/回路間および内で送信または受信し、制限なしで、電気信号の電圧レベルまたは電流レベルを変調することを含む任意の数の信号伝送技法を使用して生成することができる。信号は、任意の種類の制御情報およびタイミング情報(例えば、コマンド、アドレス値、クロック信号、および構成情報)ならびにデータを表すことができる。一実施形態では、制御情報、アドレス情報、またはデータ情報は、特定の信号線上で特定のビットウィンドウにおいてアサートされる1つまたは複数の信号を表す要求パケット内に含まれる。一実施形態では、要求パケットは、コントローラから1つまたは複数のメモリモジュールに提供されると共に、メモリモジュール間で提供される。30

#### 【0063】

実施形態では、信号バスは、相互接続、導電要素、接点、ピン、半導体基板内の領域、配線、金属トレース/信号線、または光電導体等の信号を単独でまたは組み合わせて転送する媒体である。一実施形態では、図に示された単一の信号バスを複数の信号バスで置き換えるてもよく、図に示された複数の信号バスを単一の信号バスで置き換えるてもよい。実施形態では、信号バスは、バスおよび/またはポイントツーポイント接続を含むことができる。一実施形態では、信号バスは、制御信号線およびデータ信号線を含む。代替の実施形態では、信号バスは、データ信号線のみまたは制御信号線のみを含む。さらに他の実施形態では、信号バスは、单方向(一方向に移動する信号)または双方向(2方向に移動する信号)または单方向信号線および双方向信号線の両方の組み合わせである。40

#### 【0064】

本明細書において開示された各種回路は、コンピュータ支援設計ツールを使用して記述され、挙動、レジスタ転送、論理構成要素、トランジスタ、レイアウトジオメトリ、および/または他の特性に関して各種コンピュータ可読媒体に具現されるデータおよび/または命令として表現(または表す)ことができることに留意されたい。このような回路表現を実装することができるファイルおよび他のオブジェクトのフォーマットとしては、C、50

Verilog、およびHDL等の挙動言語 (behavioral language) をサポートするフォーマット、RTLのようなレジスタレベル記述言語をサポートするフォーマット、GDSII、GDSIII、GDSIV、 CIF、MEBES等のジオメトリ記述言語をサポートするフォーマット、および任意の他の適したフォーマットおよび言語が挙げられるが、これらに限定されない。このようなフォーマットされたデータおよび/または命令を表現することができるコンピュータ可読媒体としては、各種形態（例えば、光学記憶媒体、磁気記憶媒体、または半導体記憶媒体）の不揮発性記憶媒体、ならびに無線、光、有線の信号伝送媒体またはこれらの任意の組み合わせを通してのこのようなフォーマットデータおよび/または命令の転送に使用することができる搬送波が挙げられるが、これらに限定されない。搬送波によるこのようなフォーマットデータおよび/または命令の転送の例としては、1つまたは複数のデータ転送プロトコル（例えば、HTTP、FTP、SMTPI等）を介してのインターネットおよび/または他のコンピュータネットワークを経由しての転送（アップロード、ダウンロード、電子メールなど）が挙げられるが、これに限定されない。1つまたは複数のコンピュータ可読媒体を介してコンピュータシステム内で受信された場合、このようなデータおよび/または上述した回路の命令ベースの表現は、ネットリスト生成プログラム、プレースアンドルート（place and route）プログラム等を限定なしで含む1つまたは複数の他のコンピュータプログラムの実行と併せて、コンピュータシステム内の処理エンティティ（例えば、1つまたは複数のプロセッサ）によって処理して、このような回路の物理的な現れの表現またはイメージを生成することができる。その後、このような表現またはイメージは、例えば、素子組み立てプロセス内で回路の各種構成要素の形成に使用される1つまたは複数のマスクの生成を可能にすることにより、素子の組み立てに使用することができる。

#### 【0065】

本明細書において説明した回路の機能は、部分的にまたは完全に、例えば、システム100内に記憶され実行可能なコンピュータ/プロセッサ実行可能命令（またはソフトウェア）で置き換えることも可能である。

#### 【0066】

好ましい実施形態の上記説明は、例示および説明のために提供された。網羅的であることや、実施形態を開示された厳密な形態に限定することは意図されない。変更および変形が当業者には明らかになるであろう。実施形態は、本発明の原理およびその実際の適用を最良に説明し、それにより、当業者が、意図される特定の用途に適した各種変更と共に各種実施形態に関して本発明を理解できるように、選択され説明された。本発明の範囲は以下の特許請求の範囲およびその等価物によって規定されることが意図される。

10

20

30

【図1】

【図2 A】

【図2 B】

【図3 A】

【図3B】

【図4】

【図5A】

【図5B】

【図 5 C】

【図 5 D】

---

フロントページの続き

(72)発明者 ホロウィッツ,マーク

アメリカ合衆国, カリフォルニア州 94025, メンロ パーク, サン マテオ ドライブ 1

309

審査官 野田 佳邦

(56)参考文献 特開2006-313538(JP,A)

特開2007-080258(JP,A)

国際公開第2005/038660(WO,A1)

国際公開第2008/074140(WO,A1)

米国特許出願公開第2006/0095671(US,A1)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00 - 12/06

G06F 13/16 - 13/18