(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-140657

(P2005-140657A)

(43) 公開日 平成17年6月2日(2005.6.2)

(51) Int.Cl.<sup>7</sup>GO1R 27/26

// GO1L 9/00

GO1P 15/125

F 1

GO1R 27/26

GO1L 9/00

GO1P 15/125C

305S

V

テーマコード(参考)

2FO55

2GO28

審査請求 未請求 請求項の数 4 O L (全 12 頁)

(21) 出願番号

(22) 出願日特願2003-377989 (P2003-377989)

平成15年11月7日 (2003.11.7)(71) 出願人 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 100095795

弁理士 田下 明人

(74) 代理人 100098567

弁理士 加藤 壮祐

(72) 発明者 板倉 敏和

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 与倉 久則

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

F ターム(参考) 2F055 AA40 BB20 CC60 DD20 EE25

FF13 GG33

最終頁に続く

(54) 【発明の名称】 静電容量型センサの容量変化検出回路

## (57) 【要約】

【課題】 静電容量素子に初期容量差がある場合でも正確な静電容量の変化を検出可能で且つ低コストな静電容量型センサの容量変化検出回路を提供する。

【解決手段】 各静電容量素子 C1, C2 に初期容量差 C がある場合でも、スイッチ 17 が閉じられている時間 (リセット時間) t と初期容量差 C との関係を最適化することにより、物理量の検出に十分正確な電圧信号 Vsy を得ることが可能になり、特別な回路を設けてコストを増大させることなく、各静電容量素子 C1, C2 の静電容量の変化を正確に検出することができる。

【選択図】 図 1

## 【特許請求の範囲】

## 【請求項 1】

物理現象に伴って生じる物理量に応じて静電容量が変化する可変容量素子と、前記可変容量素子の容量変化を電圧信号に変換する C - V 変換回路とを備えた静電容量型センサの容量変化検出回路であつて、

前記 C - V 変換回路は、

反転入力端子に前記可変容量素子が接続されたオペアンプと、

そのオペアンプの反転入力端子と出力端子の間に並列接続されたスイッチおよびコンデンサと

を有するスイッチトキャパシタ回路からなり、

前記スイッチが閉じられているリセット時間を  $t$  とし、前記物理量が零の初期状態における前記可変容量素子の初期容量を  $C$  とし、 $0.235 \sim 1150000$  の数値範囲をとる第 1 係数を  $m$  とし、 $0.360 \sim 1410000$  の数値範囲をとる第 2 係数を  $n$  としたときに、

$$t = (C - m) / n$$

の関係を満たすことを特徴とする静電容量型センサの容量変化検出回路。

## 【請求項 2】

前記可変容量素子は差動型可変容量素子であり、

前記初期容量  $C$  は、前記物理量が零の初期状態における差動型可変容量素子の初期容量の差であることを特徴とする請求項 1 に記載の静電容量型センサの容量変化検出回路。

## 【請求項 3】

前記可変容量素子は、前記物理量に応じて静電容量が変化するセンサ容量素子と、そのセンサ容量素子との容量差を求めるための基準容量となる固定容量素子とからなり、

前記初期容量  $C$  は、前記物理量が零の初期状態における前記センサ容量素子と前記固定容量素子との初期容量の差であることを特徴とする請求項 1 に記載の静電容量型センサの容量変化検出回路。

## 【請求項 4】

前記可変容量素子と前記 C - V 変換回路とをワンチップに集積化したことを特徴とする請求項 1 ~ 3 のいずれか 1 項に記載の静電容量型センサの容量変化検出回路。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、静電容量型センサの容量変化検出回路に係り、詳しくは、物理量を静電容量の変化によって検出する静電容量型センサの容量変化を検出することで検出対象の物理量を検出する容量変化検出回路に関するものである。

## 【背景技術】

## 【0002】

従来より、物理現象に伴って生じる物理量（例えば、加速度や圧力など）を静電容量の変化によって検出する静電容量型センサと、その静電容量型センサの容量変化を電気信号（電圧信号）に変換する容量変化検出回路とを組み合わせることにより、物理量に対応した電気信号を出力する検出装置が広く利用されている。

## 【0003】

例えば、特許文献 1 には、所定のセンサが検出対象の物理現象を静電容量の容量値の変動としてとらえ、その容量値の差をスイッチトキャパシタ部により電気信号に変換する容量型センサの容量変化検出回路において、前記スイッチトキャパシタ部が、第 1 のセンサ駆動信号で駆動され前記検出対象の変化容量を蓄積するセンサ容量素子と、第 2 のセンサ駆動信号で駆動され前記センサ容量素子の容量値との差をとるための基準容量となる参照容量素子と、一方の入力端子に前記センサ容量素子および前記参照容量素子の各一方端が共通接続されかつ出力端子から帰還容量素子と帰還制御スイッチとがそれぞれ並列接続状態で接続されるとともに他方の入力端子があらかじめ定めた基準電位に接続された帰還増

10

20

30

40

50

幅器とを有するものが開示されている。

【0004】

しかし、特許文献1の技術では、検出対象の物理量が零の初期状態（定常状態）におけるセンサ容量素子と参照容量素子の初期容量が同一になるように各容量素子を作成するのが難しく、各容量素子の初期容量に差（静電容量のアンバランス）が生じやすい。その各容量素子の初期容量差が帰還容量素子の容量を越えると、帰還容量素子が飽和して帰還増幅器の出力が一定になってしまい（出力感度が出なくなり）、物理量を検出できなくなる。

【0005】

そこで、本出願人は、特許文献2に開示されるように、物理量に応じて容量値が変化する可変容量（特許文献1の「センサ容量素子、参照容量素子」に相当）と、その可変容量の容量変化を電圧信号に変換するC-V変換回路（特許文献1の「スイッチトキャパシタ部」に相当）と、そのC-V変換回路の出力信号を電荷量としてそれぞれ異なるタイミングで保持する第1、第2の電荷保持部と、前記C-V変換回路の出力信号のオフセットを調整するための信号を電荷量として保持するオフセット調整用電荷保持部と、前記第1、第2の電荷保持部および前記オフセット調整用電荷保持部に保持された電荷量を統合した電荷量を保持する統合電荷保持部と、前記統合電荷保持部に保持された電荷を受け取り、その電荷量に基づいて前記物理量に応じた電圧を出力する出力部とを備えた信号処理装置を提案している。

【0006】

特許文献2の技術によれば、電圧で信号処理するのではなく、電荷量を用いて信号処理する新規な構成の信号処理装置とし、可変容量に大きなオフセット（初期容量差、静電容量のアンバランス）が発生したとしても、それを効果的に除去することができる。

【特許文献1】特開平8-145717号公報（第2～3頁、図1）

【特許文献2】特開2001-249028号公報（第2～5頁、図1、図2）

【発明の開示】

【発明が解決しようとする課題】

【0007】

特許文献2の技術では、可変容量のオフセット（初期容量差、静電容量のアンバランス）を除去するための回路（第1、第2の電荷保持部、オフセット調整用電荷保持部、統合電荷保持部、出力部）が必要であり、その回路を設ける分だけコストが増大するという問題があった。

【0008】

本発明は上記問題を解決するためになされたものであって、その目的は、可変容量素子に初期容量がある場合でも正確な静電容量の変化を検出可能で且つ低コストな静電容量型センサの容量変化検出回路を提供することにある。

【課題を解決するための手段】

【0009】

（請求項1）

請求項1に記載の発明は、物理現象に伴って生じる物理量に応じて静電容量が変化する可変容量素子と、前記可変容量素子の容量変化を電圧信号に変換するC-V変換回路とを備えた静電容量型センサの容量変化検出回路であって、前記C-V変換回路は、反転入力端子に前記可変容量素子が接続されたオペアンプと、そのオペアンプの反転入力端子と出力端子の間に並列接続されたスイッチおよびコンデンサとを有するスイッチトキャパシタ回路からなり、前記スイッチが閉じられているリセット時間をtとし、前記物理量が零の初期状態における前記可変容量素子の初期容量をCとし、0.235～1150000の数値範囲をとる第1係数をmとし、0.360～1410000の数値範囲をとる第2係数をnとしたときに、 $t = (C - m) / n$ の関係を満たす静電容量型センサの容量変化検出回路を技術的特徴とする。

【0010】

10

20

30

40

50

## (請求項 2)

請求項 2 に記載の発明は、請求項 1 に記載の静電容量型センサの容量変化検出回路において、前記可変容量素子は差動型可変容量素子であり、前記初期容量  $C$  は、前記物理量が零の初期状態における差動型可変容量素子の初期容量の差であることを技術的特徴とする。

## 【0011】

## (請求項 3)

請求項 3 に記載の発明は、請求項 1 に記載の静電容量型センサの容量変化検出回路において、前記可変容量素子は、前記物理量に応じて静電容量が変化するセンサ容量素子と、そのセンサ容量素子との容量差を求めるための基準容量となる固定容量素子とからなり、前記初期容量  $C$  は、前記物理量が零の初期状態における前記センサ容量素子と前記固定容量素子との初期容量の差であることを技術的特徴とする。

10

## 【0012】

## (請求項 4)

請求項 4 に記載の発明は、請求項 1 ~ 3 のいずれか 1 項に記載の静電容量型センサの容量変化検出回路において、前記可変容量素子と前記  $C$  -  $V$  変換回路とをワンチップに集積化したことを技術的特徴とする。

## 【発明の効果】

## 【0013】

## (請求項 1)

請求項 1 に記載の発明によれば、可変容量素子に初期容量がある場合でも、リセット時間と初期容量との関係を最適化することにより、物理量の検出に十分正確な電圧信号を得ることが可能になり、可変容量の静電容量の変化を正確に検出することができる。そして、請求項 1 に記載の発明によれば、特許文献 2 のように初期容量差を除去するための回路を設ける必要がないため、コストの増大を防止できる。

20

## 【0014】

## (請求項 2)

請求項 2 に記載の発明によれば、可変容量素子として差動型可変容量素子を用いることができる。

30

## 【0015】

## (請求項 3)

請求項 3 に記載の発明によれば、可変容量素子として、前記物理量に応じて静電容量が変化するセンサ容量素子と、そのセンサ容量素子との容量差を求めるための基準容量となる固定容量素子とを用いることができる。

40

## 【0016】

## (請求項 4)

請求項 4 に記載の発明によれば、可変容量素子と  $C$  -  $V$  変換回路とをワンチップに集積化することで両者を接続する接続ワイヤを省くことが可能になる。そのため、前記接続ワイヤの線路インピーダンスがワンチップ内部の配線の線路インピーダンスに置き換えられて非常に小さくなり、その分だけ線路インピーダンスと初期容量との乗算値である時定数を小さくすることが可能になることから、請求項 1 ~ 3 に記載の発明の効果を更に高めることができる。

## 【発明を実施するための最良の形態】

## 【0017】

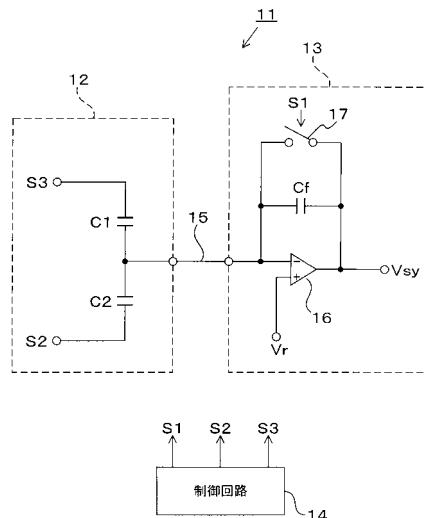

図 1 は、本発明を具体化した一実施形態に係る静電容量型センサの容量変化検出回路 1 1 の回路図である。容量変化検出回路 1 1 は、センサ部チップ 1 2 、回路部チップ 1 3 、制御回路 1 4 から構成されている。そして、各チップ 1 2 , 1 3 は接続ワイヤ 1 5 によって接続されている。制御回路 1 4 は、各チップ 1 2 , 1 3 を駆動制御するための制御信号  $S_1$  ~  $S_3$  を生成して各チップ 1 2 , 1 3 に出力する。

## 【0018】

50

センサ部チップ12は、静電容量素子（コンデンサ）C1，C2から構成されたチップ部品である。各静電容量素子C1，C2は直列接続され、静電容量素子C1には制御信号S3が印加され、静電容量素子C2には制御信号S2が印加される。尚、各制御信号S2，S3は互いに逆相の搬送波である。

【0019】

センサ部チップ12は、物理現象に伴って生じる物理量（例えば、加速度や圧力など）を各静電容量素子C1，C2の静電容量の変化によって検出する静電容量型センサである。

【0020】

例えば、物理量として加速度を検出する場合、直列接続された各静電容量素子C1，C2を、対向する固定電極の間に可動電極（中間電極）が配置された構造のコンデンサとし、当該可動電極が各静電容量素子C1，C2の接続された側の電極として共用することにより、各静電容量素子C1，C2を差動型可変容量素子（差動容量）とする。

【0021】

センサ部チップ12に加速度が印加されると、その加速度によって可動電極が変位し、その可動電極の変位に対応して各静電容量素子C1，C2の容量が共に変化する。そして、各静電容量素子C1，C2の容量差は加速度に比例して変化する。よって、各静電容量素子C1，C2の容量差の変化を検出すれば、加速度の変化を検出できる。

【0022】

回路部チップ13は、オペアンプ16、スイッチ17、コンデンサ（帰還容量）Cfから構成されたチップ部品である。オペアンプ16の反転入力端子には、接続ワイヤ15を介してセンサ部チップ12の各静電容量素子C1，C2の接続点（前記可動電極）が接続されている。オペアンプ16の非反転入力端子には、基準電圧Vr（例えば、2.5V）が印加されている。

【0023】

オペアンプ16の反転入力端子と出力端子の間には、スイッチ17とコンデンサCfが並列に接続されている。スイッチ17は、スイッチング素子（例えば、バイポーラトランジスタやFETなど）によって構成され、その開閉動作は制御信号S1によって切り替える。

【0024】

つまり、回路部チップ13は、スイッチトキャパシタ回路からなるC-V（静電容量-電圧）変換回路を構成し、各制御信号S2，S3の反転に伴って生じる各静電容量素子C1，C2の容量差の変化を電圧信号Vsに変換してオペアンプ16の出力端子から出力する。

【0025】

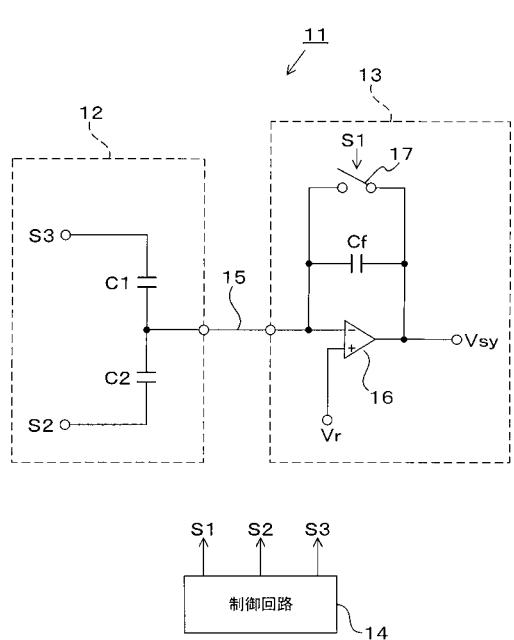

図2は、静電容量型センサの容量変化検出回路11の動作を説明するためのタイミングチャートである。

【0026】

以下、静電容量素子C1，C2およびコンデンサCfの静電容量をそれぞれ「C1」「C2」「Cf」と表記する。また、静電容量素子C1，C2およびコンデンサCfに蓄積される電荷量をそれぞれ「Q1」「Q2」「Qf」と表記する。そして、各制御信号S2，S3は、ハイレベルの電圧Vp（例えば、5V）とローレベルの電圧（=0V）の2つの電圧値をとり、その電圧振幅はVp（V）である。また、スイッチ17は、ハイ（H）レベルの制御信号S1によって閉じられ、ロー（L）レベルの制御信号S1によって開かれる。

【0027】

時刻T0では、各静電容量素子C1，C2にそれぞれ電荷量Q1（=C1×（0-Vr）），Q2（=C2×（Vp-Vr））が蓄積され、各電荷量Q1，Q2を合わせた総電荷量Qt（=Q1+Q2）が蓄積される。

【0028】

10

20

30

40

50

時刻  $T_1$  では、制御信号  $S_1$  に従ってスイッチ  $17$  が開かれ、オペアンプ  $16$  の反転入力端子と出力端子との間が直流的に開放状態となる。

【0029】

時刻  $T_2$  では、各静電容量素子  $C_1, C_2$  にそれぞれ電荷量  $Q_1 (= C_1 \times (V_p - V_r))$ ,  $Q_2 (= C_2 \times (0 - V_r))$  が蓄積され、各電荷量  $Q_1, Q_2$  を合わせた総電荷量  $Q_t (= Q_1 + Q_2)$  が蓄積される。

【0030】

このとき、スイッチ  $17$  が開かれており、オペアンプ  $16$  の反転入力端子と出力端子との間が直流的に開放状態であるため、コンデンサ  $C_f$  には電荷量  $Q_f (= Q_t - Q_t)$  が蓄積される。そのため、オペアンプ  $16$  の出力端子の電圧信号  $V_{sy}$  は、コンデンサ  $C_f$  の電荷量  $Q_f$  を静電容量  $C_f$  で除算した電圧値 ( $Q_f / C_f$ ) で安定する。10

【0031】

時刻  $T_3$  では、制御信号  $S_1$  に従ってスイッチ  $17$  が閉じられ、オペアンプ  $16$  の反転入力端子と出力端子との間が直流的に短絡状態（ボルテージフォロアの状態）となり、コンデンサ  $C_f$  に蓄積された電荷が放電されると共に、オペアンプ  $16$  の反転入力端子が基準電圧  $V_r$  と同電位となる。

【0032】

そして、以降の時刻  $T_4 \sim T_6$  では同様の動作が繰り返される。そのため、オペアンプ  $16$  の出力端子の電圧信号  $V_{sy}$  は、数式 1 によって表される最大電圧  $V_s$  (V) を電圧振幅とする矩形波となる。20

【0033】

$$V_s = V_p \times (C_1 - C_2) / C_f \dots \dots \dots \text{ (数式 1) } .$$

【0034】

[実施形態の作用・効果]

静電容量型センサの容量変化検出回路  $11$  では、検出対象の物理量が零の初期状態（正常状態）における各静電容量素子  $C_1, C_2$  の初期容量が同一になるように各静電容量素子  $C_1, C_2$  を作成するのが難しく、各静電容量素子  $C_1, C_2$  の初期容量に差（オフセット容量、静電容量のアンバランス）が生じやすい。

【0035】

その各静電容量素子  $C_1, C_2$  の初期容量差  $C$  が大きいと、スイッチ  $17$  を閉じてもコンデンサ  $C_f$  に蓄積された電荷を十分に放電させて完全にリセットさせることができなくなり、コンデンサ  $C_f$  に徐々に電荷が溜まり、正確な電圧信号  $V_{sy}$  が得られなくなる。そして、初期容量差  $C$  がコンデンサ  $C_f$  の容量  $C_f$  を越えると、コンデンサ  $C_f$  が飽和して電圧信号  $V_{sy}$  が一定になってしまい（出力感度が出なくなり）、物理量を検出できなくなる。30

【0036】

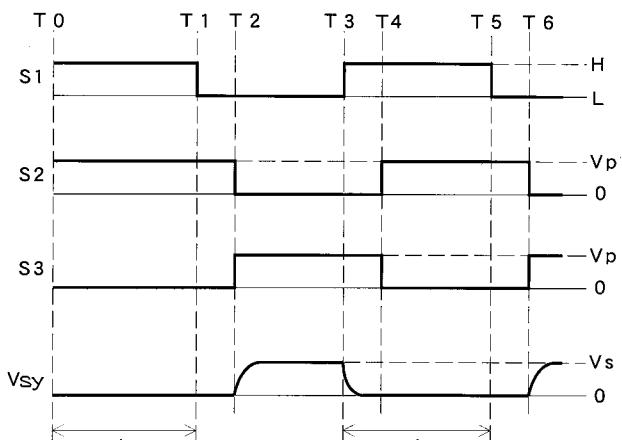

図 3 は、各静電容量素子  $C_1, C_2$  の初期容量差  $C$  が大きくなつた場合の電圧信号  $V_{sy}$  の変化を示すタイミングチャートである。

【0037】

初期容量差  $C$  が十分に小さい場合には、スイッチ  $17$  が閉じられると（図 2 に示す時刻  $T_3$ ）、電圧信号  $V_{sy}$  が速やかにローレベルになり、正常な電圧信号  $V_{sy}$  が得られる（1）。

【0038】

しかし、初期容量差  $C$  が大きくなつてゆくにつれて、スイッチ  $17$  が閉じられても電圧信号  $V_{sy}$  がなかなかローレベルにならず、電圧信号  $V_{sy}$  の「波形なまり」が増大してゆく（2 3 4）。そして、初期容量差  $C$  が非常に大きくなると、スイッチ  $17$  が閉じられても電圧信号  $V_{sy}$  がローレベルにならず一定になつてしまう。

【0039】

そこで、スイッチ  $17$  が閉じられている時間  $t$ （図 2 に示す時刻  $T_0 \sim T_1$  および時刻  $T_3 \sim T_5$  の時間。以下「リセット時間  $t$ 」と表記する）と、初期容量差（オフセット容40

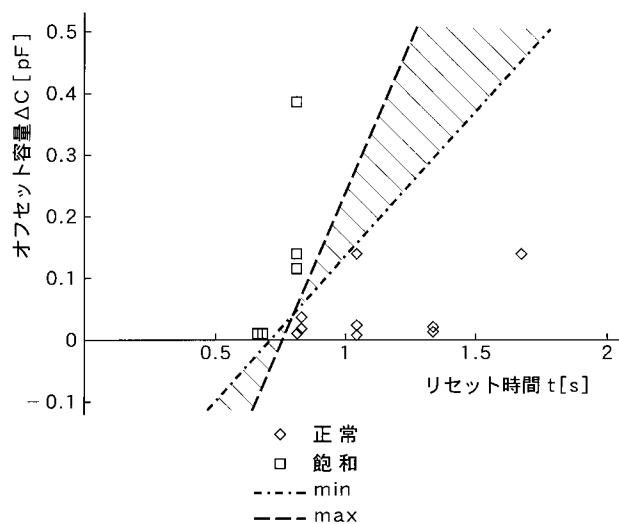

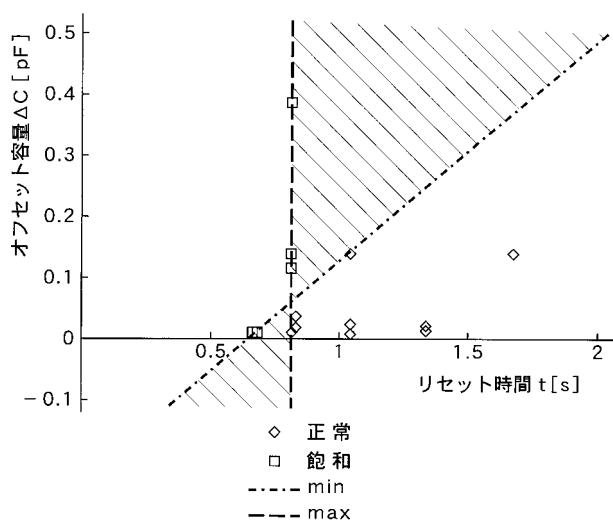

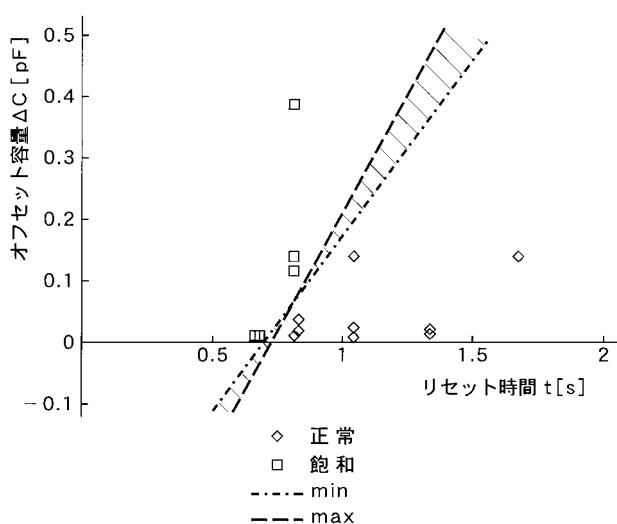

量)  $C$  とをそれぞれ変化させ、電圧信号  $V_{sy}$  が正常か又は飽和するかを調べる実験を行い、図 4 ~ 図 6 に示すグラフのデータ(実測値)を得た。

【0040】

図 4 ~ 図 6 に示すグラフのデータから、物理量の検出に十分正確な電圧信号  $V_{sy}$  が得られるリセット時間  $t$  と初期容量差  $C$  との関係は、各係数  $m$ ,  $n$  を用いた式 2 によって表されることが判明した。

【0041】

$$t = (C - m) / n \quad \dots \dots \dots \text{(式 2)}.$$

【0042】

ここで、係数  $m$  の範囲は約 0.235 ~ 1.150 000 が適当であり、望ましくは約 0.325 ~ 0.725、特に望ましくは約 0.433 ~ 0.595 である。 10

【0043】

係数  $m$  がこの範囲より大きくなると(つまり、リセット時間  $t$  を表す直線の切片が大きくなると)、電圧信号  $V_{sy}$  が飽和する領域でリセット時間  $t$  および初期容量差  $C$  を設定してもよいことになるため、係数  $m$  をこの範囲より大きくすることはできない。

【0044】

また、係数  $m$  がこの範囲より小さくなると(つまり、リセット時間  $t$  を表す直線の切片が小さくなると)、電圧信号  $V_{sy}$  が実際には飽和しない領域までリセット時間  $t$  および初期容量差  $C$  の設定を禁止してしまうような緩い規格になるため、係数  $m$  をこの範囲より小さくすることはできない。 20

【0045】

係数  $n$  の範囲は約 0.360 ~ 1.410 000 が適当であり、望ましくは約 0.460 ~ 0.960、特に望ましくは約 0.610 ~ 0.810 である。 20

【0046】

係数  $n$  がこの範囲より大きくなると(つまり、リセット時間  $t$  を表す直線の傾きが大きくなると)、電圧信号  $V_{sy}$  が飽和する領域でリセット時間  $t$  および初期容量差  $C$  を設定してもよいことになるため、係数  $n$  をこの範囲より大きくすることはできない。

【0047】

また、係数  $n$  がこの範囲より小さくなると(つまり、リセット時間  $t$  を表す直線の傾きが小さくなると)、電圧信号  $V_{sy}$  が実際には飽和しない領域までリセット時間  $t$  および初期容量差  $C$  の設定を禁止してしまうような緩い規格になるため、係数  $n$  をこの範囲より小さくすることはできない。 30

【0048】

図 4 に示す斜線の範囲は、リセット時間  $t$  および初期容量差  $C$  の適当な範囲を示すものである。図 5 に示す斜線の範囲は、リセット時間  $t$  および初期容量差  $C$  の望ましい範囲を示すものである。図 6 に示す斜線の範囲は、リセット時間  $t$  および初期容量差  $C$  の特に望ましい範囲を示すものである。

【0049】

以上詳述した本実施形態によれば、各静電容量素子  $C_1$ ,  $C_2$  に初期容量差  $C$  がある場合でも、リセット時間  $t$  と初期容量差  $C$  との関係を最適化することにより(式 2、図 4 ~ 図 6 の斜線範囲)、物理量の検出に十分正確な電圧信号  $V_{sy}$  を得ることが可能になり、各静電容量素子  $C_1$ ,  $C_2$  の静電容量の変化を正確に検出することができる。そして、本実施形態によれば、特許文献 2 のように初期容量差  $C$  を除去するための回路を設ける必要がないため、コストの増大を防止できる。 40

【0050】

[別の実施形態]

ところで、本発明は上記実施形態に限定されるものではなく、以下のように具体化してもよく、その場合でも、上記実施形態と同等もしくはそれ以上の作用・効果を得ることができる。

【0051】

10

20

30

40

50

(1) 上記実施形態では、各静電容量素子C1, C2を差動型可変容量素子としている。しかし、静電容量素子C1を固定電極と可動電極が対向した構造の可変容量コンデンサ(センサ容量素子)とし、静電容量素子C2を固定電極が対向した構造の通常の固定容量コンデンサ(固定容量素子)としてもよい。

【0052】

この場合、センサ部チップ12に加速度が印加されると、その加速度によって静電容量素子C1の可動電極が変位し、その可動電極の変位に対応して静電容量素子C1の容量が変化するのに対して、静電容量素子C2の容量は変化しない。そして、各静電容量素子C1, C2の容量差は加速度に比例して変化する。よって、各静電容量素子C1, C2の容量差の変化を検出すれば、加速度の変化を検出できる。つまり、容量一定の静電容量素子C2を、容量が変化する静電容量素子C1との容量差を求めるための基準容量として使用するわけである。

【0053】

(2) 上記(1)において、静電容量素子C2を省き、静電容量素子C1のみを設けるようにしてもよい。この場合、検出対象の物理量が零の初期状態における静電容量素子C1の初期容量が上記実施形態の初期容量差Cと同様に作用し、静電容量素子C1の初期容量分が電圧信号Vsyのオフセット電圧となって表れる。しかし、この場合でも、上記実施形態と同様にリセット時間tと初期容量差Cとの関係を最適化することにより(数式2、図4～図6の斜線範囲)、上記実施形態と同様の効果が得られる。

【0054】

(3) 図3に示す電圧信号Vsyの「波形なまり」は、各静電容量素子C1, C2の初期容量差Cだけでなく、各チップ12, 13を接続する接続ワイヤ15の線路インピーダンスZと初期容量差Cとの乗算値である時定数(=Z×C)が大きいほど当該波形なまりも大きくなる。

【0055】

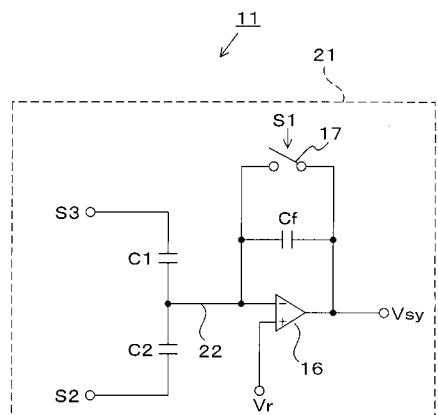

そこで、図7に示すように、各チップ12, 13をワンチップ21に集積化して接続ワイヤ15を省くようにすれば、接続ワイヤ15の線路インピーダンスZがワンチップ21内部の配線22の線路インピーダンスに置き換えられて非常に小さくなるため、その分だけ時定数を小さくすることが可能になり、上記実施形態の効果を更に高めることができる。

【図面の簡単な説明】

【0056】

【図1】図1は、本発明を具体化した一実施形態に係る静電容量型センサの容量変化検出回路11の回路図である。

【図2】図2は、静電容量型センサの容量変化検出回路11の動作を説明するためのタイミングチャートである。

【図3】図3は、各静電容量素子C1, C2の初期容量差Cが大きくなった場合の電圧信号Vsyの変化を示すタイミングチャートである。

【図4】図4は、リセット時間tおよび初期容量差(オフセット容量)Cを変化させた場合に電圧信号Vsyが正常か又は飽和するかを示すグラフである。図4に示す斜線の範囲は、リセット時間tおよび初期容量差Cの適当な範囲を示すものである。

【図5】図5は、リセット時間tおよび初期容量差(オフセット容量)Cを変化させた場合に電圧信号Vsyが正常か又は飽和するかを示すグラフである。図5に示す斜線の範囲は、リセット時間tおよび初期容量差Cの望ましい範囲を示すものである。

【図6】図6は、リセット時間tおよび初期容量差(オフセット容量)Cを変化させた場合に電圧信号Vsyが正常か又は飽和するかを示すグラフである。図6に示す斜線の範囲は、リセット時間tおよび初期容量差Cの特に望ましい範囲を示すものである。

【図7】図7は、本発明を具体化した別の実施形態に係る静電容量型センサの容量変化検出回路11の回路図である。

【符号の説明】

10

20

30

40

50

## 【0057】

1 1 ... 静電容量型センサの容量変化検出回路

1 2 ... センサ部チップ

1 3 ... 回路部チップ

1 4 ... 制御回路

1 5 ... 接続ワイヤ

1 6 ... オペアンプ

1 7 ... スイッチ

2 1 ... ワンチップ

C 1, C 2 ... 静電容量素子

C f ... コンデンサ

Vsy... 電圧信号

10

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

---

フロントページの続き

F ターム(参考) 2G028 AA05 BB06 CG07 EJ04 EJ06 FK01 GL08 MS03