(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6233971号

(P6233971)

(45) 発行日 平成29年11月22日(2017.11.22)

(24) 登録日 平成29年11月2日(2017.11.2)

(51) Int.Cl.

F 1

G 11 C 16/34 (2006.01)

G 11 C 16/04 (2006.01)G 11 C 16/34 116

G 11 C 16/04 120

請求項の数 5 (全 12 頁)

(21) 出願番号 特願2014-11512 (P2014-11512)

(22) 出願日 平成26年1月24日 (2014.1.24)

(65) 公開番号 特開2014-146407 (P2014-146407A)

(43) 公開日 平成26年8月14日 (2014.8.14)

審査請求日 平成29年1月18日 (2017.1.18)

(31) 優先権主張番号 13/751,548

(32) 優先日 平成25年1月28日 (2013.1.28)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

エヌエックスピー ユーエスエイ インコ

ーポレイテッド

N X P U S A, I n c.

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 チョン エム. ホン

アメリカ合衆国 78732 テキサス州

オースティン メディテラ ポイント

224

最終頁に続く

(54) 【発明の名称】スプリット・ゲート・ビット・セルのプログラミング

## (57) 【特許請求の範囲】

## 【請求項 1】

行および列に配列されているスプリット・ゲート・メモリ・セルの第1のセクタを有するスプリット・ゲート・メモリであって、各スプリット・ゲート・メモリ・セルは、制御ゲート、前記行のうちの1つに沿ったワード線に結合されている選択ゲート、前記列のうちの1つに沿ったビット線に結合されているドレイン端子、およびソース端子を有する、スプリット・ゲート・メモリにおける、選択的プログラミングの方法であって、

選択された行および選択された列に結合されることによってプログラミングのために選択されたスプリット・ゲート・メモリ・セルについて、前記制御ゲートを第1の電圧に結合すること、前記選択ゲートを第2の電圧に結合すること、前記ドレイン端子を、前記スプリット・ゲート・メモリ・セルを導電性にする電流シンクに結合すること、前記ソース端子を第3の電圧に結合すること、

非選択行に結合されることによってプログラムされないスプリット・ゲート・メモリ・セル・スプリット・ゲート・セルについて、前記制御ゲートを前記第1の電圧に結合すること、前記選択ゲートを、前記スプリット・ゲート・メモリ・セルが非選択である読み出し中に前記選択ゲートに印加される電圧よりも大きい第4の電圧に結合することを備える、方法。

## 【請求項 2】

非選択列および選択されたワード線に結合されることによってプログラムされないスプリット・ゲート・メモリ・セルについて、前記制御ゲートを前記第1の電圧に結合するこ

と、前記選択ゲートを前記第2の電圧に結合すること、前記ドレイン端子を、前記第4の電圧よりも大きい第5の電圧に結合すること、前記ソース端子を前記第3の電圧に結合することをさらに備える、請求項1に記載の方法。

【請求項3】

前記スプリット・ゲート・メモリ・セルがプログラムされないときに前記選択ゲートを第4の電圧に結合することは、前記スプリット・ゲート・メモリ・セルが閾値電圧を有し、前記第4の電圧が、前記ドレイン端子上の電圧を上回る前記閾値電圧よりも小さいことによってさらに特徴付けされる、請求項1に記載の方法。

【請求項4】

前記スプリット・ゲート・メモリ・セルがプログラムされないときに前記選択ゲートを第4の電圧に結合することは、該第4の電圧が、グランドよりも大きいことによってさらに特徴付けされる、請求項1に記載の方法。 10

【請求項5】

スプリット・ゲート・メモリであって、

行および列に配列されているスプリット・ゲート・メモリ・セルの第1のセクタであって、各スプリット・ゲート・メモリ・セルは、制御ゲート、前記行のうちの1つに沿ったワード線に結合されている選択ゲート、前記列のうちの1つに沿ったビット線に結合されているドレイン端子、およびソース端子を有する、前記第1のセクタと、

プログラミング回路であって、

選択された行および選択された列に結合されることによってプログラミングのために選択されたスプリット・ゲート・メモリ・セルについて、前記制御ゲートを第1の電圧に結合し、前記選択ゲートを第2の電圧に結合し、前記ドレイン端子を、前記スプリット・ゲート・メモリ・セルを導電性にする電流シンクに結合し、前記ソース端子を第3の電圧に結合すること、 20

非選択行に結合されることによってプログラムされないスプリット・ゲート・メモリ・セルについて、前記制御ゲートを前記第1の電圧に結合し、前記選択ゲートを、読み出し中に、非選択である前記スプリット・ゲート・メモリ・セルの前記選択ゲートに印加される電圧よりも大きい第4の電圧に結合することによってプログラミングするプログラミング回路とを備える、スプリット・ゲート・メモリ。 30

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、概してメモリに関し、より具体的には、スプリット・ゲート・ビット・セルのプログラミングに関する。

【背景技術】

【0002】

たとえば、スプリット・ゲート・フラッシュ・デバイスを含むスプリットゲート不揮発性メモリ(NVM)は、積層ゲートデバイスを超える利点を提供する。スプリット・ゲート・フラッシュ・セルにより、未選択であるが選択された行上にあるか、または代替的には選択された列上にあるメモリセルについて、プログラムディスターブの低減がもたらされる。通常、選択された行または選択された列上にあるセルは、選択されたセルに対して実行されている動作にかかわらず、ディスターブ効果を示す可能性が最も高い。スプリット・ゲート・フラッシュ・セルにより、選択された列または行上のセルに関するプログラムディスターブ問題が実質的に低減されており、未選択の行/未選択の列のセル上の消去ビットのプログラムディスターブが、主要なディスターブメカニズムである。スプリットゲート設計においてこれらのセルが影響を受けやすい理由の1つは、未選択のセルに加わる特定のストレスが、選択された行/未選択の列または未選択の行/選択された列上のセルに加わるストレスよりも多くのサイクルにわたって加わることである。 40

【先行技術文献】

50

## 【特許文献】

## 【0003】

【特許文献1】米国特許出願公開第2012/0261769号明細書

【特許文献2】米国特許出願公開第2013/0279267号明細書

## 【図面の簡単な説明】

## 【0004】

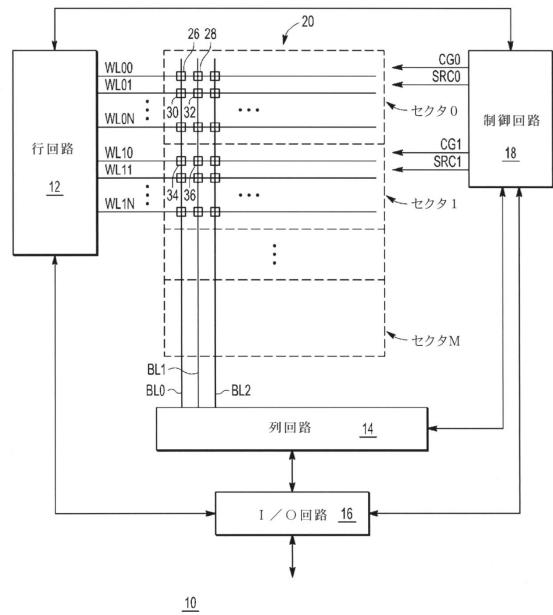

【図1】本開示の一実施形態に応じたメモリアレイを有するメモリシステムを示すプロック図。

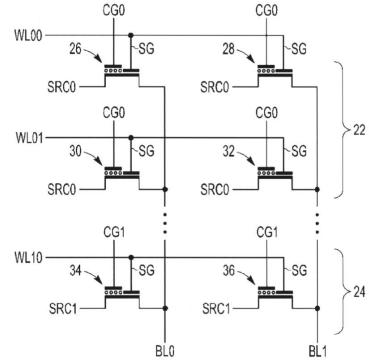

【図2】本開示の一実施形態に応じた、図1のメモリアレイの一部分をさらに詳細に示す概略図。

10

【図3】メモリシステムのプログラミング中に図1のアレイのさまざまなビットセルに印加される例示的なプログラム電圧を示す表形式の図。

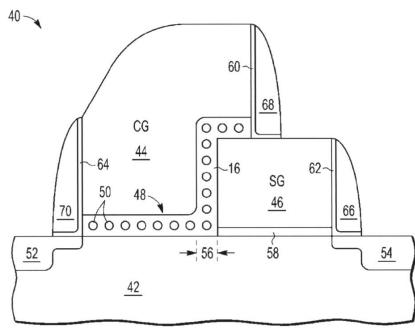

【図4】本開示の一実施形態に応じた図1のメモリアレイのビットセルのスプリット・ゲート・デバイスを示す断面図。

## 【発明を実施するための形態】

## 【0005】

本発明は例として示されており、添付の図面によって限定されない。図面において、同様の参照符号は類似の要素を示す。図面内の要素は簡潔かつ明瞭にするために示されており、必ずしも原寸に比例して描かれてはいない。

## 【0006】

20

スプリットゲートNVM内の選択されたスプリット・ゲート・メモリ・セルのプログラミング中、未選択の消去ビットにバイアスが加わる結果として、1つ以上の未選択の消去ビットが故意でなくプログラムされることになる場合がある。プログラムディスターブは一般的に、バンド間キャリア発生およびソース-ドレイン間漏れ電流によって引き起こされ、結果として電子が、故意でなくスプリットゲートNVMの未選択の消去ビットに注入されることになる。技術が進歩し、スプリット・ゲート・メモリ・セルの選択ゲート酸化物の厚さが低減するにつれて、バンド間キャリア発生はプログラムディスターブのより主要な発生源になる。それゆえ、一実施形態において、プログラムディスターブを低減するために、メモリの未選択の行上のメモリセルの選択ゲート（たとえば、ワード線）に印加されるバイアス電圧が、バンド間キャリア発生を低減する特定の選択ゲートバイアス電圧に設定される。一実施形態において、この選択ゲートバイアス電圧は、読み出し動作中に非選択スプリット・ゲート・メモリ・セルの選択ゲートに印加される電圧よりも大きい。プログラミング中に未選択の行上のメモリセルに印加されるこの選択ゲートバイアス電圧は、これらのスプリット・ゲート・メモリ・セルの間隙領域におけるバンド曲がりを低減する。選択ゲートと制御ゲートとの間、および選択ゲートとソースとの間で電位差が低減するため、バンド曲がりが低減する。バンド曲がりが低減することによって、間隙領域内で発生する電子/正孔対が低減し、これによって、未選択の行上のメモリセルへの電子の注入が低減する。このようにして、プログラムディスターブが低減され得る。

30

## 【0007】

図1は、本開示の一実施形態に応じたメモリシステム10をプロック図形式で示す。メモリシステム10は、メモリセル26、28、30、32、34、および36のような複数のメモリセルを含むスプリット・ゲート・メモリ・セル・アレイ20を含む。アレイ20は、任意の数のセクタに分割されてもよい。示されている実施形態において、アレイ20は、セクタ0、セクタ1、...、セクタMのような、M+1個のセクタを含む。メモリ10は、行回路12と、列回路14と、制御回路18と、I/O回路16とをも含む。制御回路18は、行回路12および列回路14の各々に結合されており、列回路14はI/O回路16に結合されている。I/O回路16は、行回路12および制御回路18にも結合されている。アレイ20は、BL0、BL1、BL2などを含む任意の数のビット線を含む。これらのビット線の各々は、アレイ20のビットセルに対する読み出し/書き込みのための適切な検知および書き込み回路を含む列回路14に結合されている。アレイ2

40

50

0の各セクタは、任意の数のワード線を含む。たとえば、セクタ0はN+1本のワード線WL00、WL01、...、WL0Nを含み、セクタ1はN+1本のワード線WL10、WL11、...、WL1Nを含む。これらのワード線の各々が行回路12に結合されている。メモリセルは各ワード線とビット線との交差点に結合されている。示されている実施形態において、メモリセル26はWL00およびBL0に結合されてセクタ0内にあり、メモリセル28はWL00およびBL1に結合されてセクタ0内にあり、メモリセル30はWL01およびBL0に結合されてセクタ0内にあり、メモリセル32はWL01およびBL1に結合されてセクタ0内にあり、メモリセル34はWL10およびBL0に結合されてセクタ1内にあり、メモリセル36はWL10およびBL1に結合されてセクタ1内にある。なお、各ワード線はアレイ20の行として称される場合があり、各ビット線は列として称される場合がある。下記にさらに詳細に説明するように、行回路12はワード線の各々に適切な電圧値を提供し、ワード線は各メモリセルの選択ゲートに結合されている。I/O回路16はアレイ20に対する読み出しあり書き込みのために必要に応じて行回路12、列回路14、および制御回路18と通信する。制御回路18も、アレイ20の各メモリセルの制御ゲートおよびソース端子に適切な電圧値を提供する。たとえば、セクタ0の各メモリセルの制御ゲートは制御ゲート電圧CG0を受け取るように結合されており、セクタ0の各メモリセルのソース端子はソース端子電圧SRC0を受け取るように結合されており、セクタ1の各メモリセルの制御ゲートは制御ゲート電圧CG1を受け取るように結合されており、セクタ1の各メモリセルのソース端子はソース端子電圧SRC1を受け取るように結合されている。示されている実施形態において、1つのセクタ内の各メモリセルは同じ制御ゲート電圧および同じソース端子電圧を受け取る。すなわち、示されている実施形態において、各セクタ内で、制御ゲート電圧（たとえば、CG0、CG1など）は共通の電圧ノードであり、ソース端子電圧（たとえば、SRC0、SRC1など）は共通の電圧ノードであることに留意されたい。

#### 【0008】

図2は、アレイ20の一部分をさらに詳細に示している。図2は、メモリセル26、28、30、32、34、および36を示している。メモリセル26は、CG0を受け取るように結合されている制御ゲート、WL00に結合されている選択ゲート、SRC0を受け取るように結合されているソース端子、および、BL0に結合されているドレイン端子を有する。メモリセル28は、CG0を受け取るように結合されている制御ゲート、WL00に結合されている選択ゲート、SRC0を受け取るように結合されているソース端子、および、BL1に結合されているドレイン端子を有する。メモリセル30は、CG0を受け取るように結合されている制御ゲート、WL01に結合されている選択ゲート、SRC0を受け取るように結合されているソース端子、および、BL0に結合されているドレイン端子を有する。メモリセル32は、CG0を受け取るように結合されている制御ゲート、WL01に結合されている選択ゲート、SRC0を受け取るように結合されているソース端子、および、BL1に結合されているドレイン端子を有する。メモリセル34は、CG1を受け取るように結合されている制御ゲート、WL10に結合されている選択ゲート、SRC1を受け取るように結合されているソース端子、および、BL0に結合されているドレイン端子を有する。メモリセル36は、CG1を受け取るように結合されている制御ゲート、WL10に結合されている選択ゲート、SRC1を受け取るように結合されているソース端子、および、BL1に結合されているドレイン端子を有する。

#### 【0009】

プログラム動作中、アレイ20の特定のメモリセルが、アクセス要求に対応するアクセスアドレスおよびデータによってプログラミングのために選択される。行回路12は、アクセスアドレスに対応する選択されたワード線をアクティブ化し、列回路14は電流シンクをアクセスアドレスに対応する選択されたビット線に結合し、これによって選択されたメモリセルが導電するようになる。示されている実施形態において、プログラム動作について、メモリセル26がプログラミングのために選択され、メモリセル28、30、32、34、および36は選択されていないと仮定される。この場合、選択されたワード線は

セクタ0（図2の符号22）内にあるためセクタ0が選択され、セクタ1（図2の符号24）を含むすべての他のセクタは非選択である。メモリセル26が選択される場合、WL00がアクティブ化されて、列回路14内の電流シンクが選択されたビット線BL0に結合される。

#### 【0010】

図3は、プログラム動作中に各メモリセルに印加されてもよい電圧値を表形式で示している。表の第1の列は、メモリセル位置に関する。各メモリセル位置について、最初の文字対はメモリセルが選択された行（SR）に結合されているか、または未選択の行（UR）に結合されているかを示し、次の文字対は、メモリセルが選択された列（SC）に結合されているか、または未選択の列（UC）に結合されているかを示している。さらに、表の最初の4行は、選択されたセクタ（すなわち、プログラミングのために選択されたメモリセルが位置するセクタ）の種々のメモリセル位置に対応する。それゆえ、選択されたセクタの各メモリセルは、SR SC、SR UC、UR SC、およびUR UCの4つの位置のうちの1つである。たとえば、メモリセル26がプログラミングのために選択されていると仮定されている図2を参照すると、メモリセル26は選択された行および選択された列に結合されており、従ってSR SC位置にあるメモリセルであり、メモリセル28は選択された行および未選択の列に結合されており、従ってSR UC位置にあり、メモリセル30は未選択の行および選択された列に結合されており、従ってUR SC位置にあり、メモリセル32は未選択の行および未選択の列に結合されており、従ってUR UC位置にある。なお、セクタ0内のWL00に結合されている（かつBL0に結合されていない）すべてのメモリセルはSR UC位置にあると考えられ、セクタ0内のBL0に結合されている（かつWL00に結合されていない）すべてのメモリセルはUR SC位置にあると考えられ、セクタ0内のWL00にもBL0にも結合されていないすべてのメモリセルはUR UC位置にあると考えられる。図3に戻って参照すると、表のその次の2行は未選択の（すなわち非選択の）セクタ（すなわち、選択されたメモリセルを含まない任意のセクタ）の種々のメモリセル位置に対応する。それゆえ、未選択のセクタの各メモリセルはUR SCおよびUR UCの2つの位置のうちの一方にある。たとえば、メモリセル26がプログラミングのために選択されていると仮定されている図2を参照すると、メモリセル34は未選択の行および選択された列に結合されており、従ってUR SC位置にあるメモリセルであり、メモリセル36は未選択の行および未選択の列に結合されており、従ってUR UC位置にあるメモリセルである。なお、BL0に結合されているセクタ0以外の任意のセクタ内のすべてのメモリセルはUR SC位置にあると考えられ、BL0に結合されていないセクタ0以外の任意のセクタ内のすべてのメモリセルはUR UC位置にあると考えられる。

#### 【0011】

選択されたメモリセル26のプログラミング中、ソース側注入が使用されて電子がメモリセルの電荷蓄積層内に蓄積される。これは、ドレイン端子とソース端子との間に電流を流し、流れている電流から電荷蓄積層内へ電子を注入するために制御ゲートに高電圧を印加することによって行われる。この電荷蓄積層は、電子を蓄積するためのナノ結晶を含んでもよい。それゆえ、図3の表によれば、選択されたメモリセル26をプログラムするために、9Vの電圧を制御ゲート（CG0）に印加し、1.0Vの電圧を選択ゲート（WL00）に印加して、BL0は結果として約0.3Vのドレイン端子上シンク電圧を生じさせる電流シンクに結合され、5Vの電圧をソース端子（SRC0）に印加する。この場合、メモリセル26のソース端子上の電圧SRC0、およびBL0の電流シンクへの結合の結果としてメモリセル26が導電し、それによって、ソース端子からBL0へと電流が流れ、制御ゲートに高電圧が印加される結果として、メモリセル26内に電子が注入される。それゆえ、プログラム動作中、選択されたメモリセルのドレイン端子はソースとして機能し、一方でソース端子はドレインとして機能することに留意されたい。しかしながら、読み出し動作（当該技術分野で既知のように実行される）の間、ドレイン端子はドレインとして機能し、ソース端子はソースとして機能する。

10

20

30

40

50

## 【0012】

なお、選択されたセクタについて、選択されたセクタ内のすべてのメモリセルの制御ゲートに同じ電圧値（たとえば、9V）が印加され、選択されたセクタ内のすべてのメモリセルのソース端子に同じ電圧値（たとえば、5V）が印加される。未選択の列に結合されているメモリセルについて、メモリセルのドレイン端子は、選択ゲートに印加される電圧よりも大きい電圧に（対応するビット線によって）結合されている。図3の例において、この電圧は1.25Vであってもよい。また、未選択の行および未選択の列に結合されているメモリセルについて、メモリセルのドレイン端子はまた（対応するビット線によって）、たとえば、1.25Vのような、選択ゲートに印加される電圧よりも大きい電圧に結合されてもよい。なお、選択された列に結合されているメモリセルについて、ドレイン端子（すなわち、対応するビット線）は、各ドレイン端子に対するシンク電圧を誘起してもよい電流シンクに結合されている。このシンク電圧は0.3Vであってもよい。それゆえ、図3の例によって示すように、プログラム動作中にプログラムされている（従って、SR\_SC位置にある）スプリット・ゲート・メモリ・セルについて、制御ゲートに印加される電圧は選択ゲートに印加されている電圧よりも大きく、ソース端子に印加されている電圧よりも大きい。また、選択された行に結合されている（従って、SR\_SCまたはSR\_UC位置にある）メモリセルの選択ゲートに印加される電圧、未選択の行に結合されている（従って、UR\_SCまたはUR\_UC位置にある）メモリセルの選択ゲートに印加される電圧よりも大きいことに留意されたい。また、ソース端子に印加される電圧は、SR\_SCまたはSR\_UC位置にあるメモリセルの選択ゲートに印加される電圧よりも大きい。

## 【0013】

選択されたメモリセル26のプログラミング中、WL00に結合されていないセクタ0内の任意のメモリセルの選択ゲートは、バンド間キャリア発生を低減する選択ゲートバイアス電圧に設定されている。一実施形態において、この選択ゲートバイアス電圧は、読み出し動作中に非選択メモリセルの選択ゲートに印加される電圧（VSGread\_desel ect edと称される場合もある）よりも大きい。この例において、読み出し中は非選択メモリセルの選択ゲートに0V（またはグランド）が提供されるが、WL00に結合されていないメモリセルの選択ゲートには0.2Vが提供される。それゆえ、0.2Vの選択ゲートバイアス電圧は、読み出し動作中の非選択メモリセルの選択ゲートに印加される電圧よりも大きい。さらに、一実施形態において、選択された行に結合されていないメモリセルに印加される選択ゲートバイアス電圧は、選択されたビット線のビット線電圧とメモリセルの閾値電圧との合計（「VBL+Vt」）以下である。それゆえ、図2および図3の例を参照すると、閾値電圧が0.5Vである場合、0.2Vは「0.3V+0.5V」以下である。すなわち、選択ゲートバイアス電圧は、ドレイン端子上の電圧（VBLに対応する）を上回るメモリセルの閾値電圧（Vt）よりも小さい。この選択ゲートバイアスを選択されたワード線に結合されていない任意のメモリセルに加えることによって、これらのメモリセルにおけるバンド間漏れ電流が低減される。なお、この選択ゲートバイアス電圧の値がVSGread\_desel ect edに等しい値から最大で「VBL+Vt」へと増大することによって、バンド間キャリア発生が低減する。それゆえ、VSGread\_desel ect edよりも大きい選択ゲートバイアス電圧はソース-ドレイン間漏れ電流を増大させる場合があるが、プログラムディステーブの主要な発生源であるバンド間キャリア発生が低減することに起因して、全体的なプログラムディステーブは低減される。

## 【0014】

なお図3を参照すると、選択されたワード線に結合されていない選択されたセクタのメモリセルに対してプログラミング中に印加される同じ選択ゲートバイアス電圧が、未選択のセクタ内のすべてのメモリセルの選択ゲートに印加可能であることに留意されたい。また、未選択のセクタについて、メモリセルがオフのままであることを保証するために制御ゲートおよびソース端子に電圧が印加される。それゆえ、図3の示されている実施形態に

おいて、1.5Vが未選択のセクタ内の任意のメモリセル（たとえば、メモリセル34および36）の制御ゲート（CG1）に印加される。一実施形態において、未選択のセクタ内のメモリセルの選択ゲートに印加される同じ電圧（たとえば、SG）が、未選択のセクタ内の任意のメモリセルのソース端子（SRC1）にも印加される。

#### 【0015】

図4は、アレイ20のメモリセルに使用されてもよいスプリット・ゲート・メモリ・セル40の一例を示している。メモリセル40は、ソース/ドレイン領域52および54を有する基板42と、ソース/ドレイン領域52および54の間の基板42の第1の部分の上の選択ゲート誘電体58と、選択ゲート誘電体58の上の選択ゲート46と、ソース/ドレイン領域52および54の間の（基板42の第1の部分に隣接する）基板42の第2の部分の上方において、選択ゲート46の側壁に重なる電荷蓄積層48と、電荷蓄積層48の上の制御ゲート44とを含む。メモリセル40は、SG46上においてCG44の第1の側壁に隣接するライナ60およびスペーサ68と、ソース/ドレイン領域54上においてSG46の側壁に隣接するライナ62およびスペーサ66と、ソース/ドレイン領域52上においてCG44の第2の側壁に隣接するライナ64およびスペーサ70とをも含む。電荷蓄積層は、絶縁材料によって包囲される複数のナノ結晶50を含んでもよい。なお、電荷蓄積層48が位置する、制御ゲート44および選択ゲート46の隣接する側壁間の領域により、基板42内に間隙領域56がもたらされる。メモリセル40がプログラム動作の間に未選択の行にあるとき、読み出し動作の間にメモリセル40が非選択であるときに選択ゲート46に印加される電圧よりも大きく、かつVBL+Vtよりも小さい電圧が選択ゲート46に印加される。

#### 【0016】

なお、プログラム動作中に未選択のメモリセルのプログラムディステップに影響を与える電界が間隙領域56において形成される。この間隙領域にわたる電界によってバンド曲がりが生じ、その結果として電子/正孔対が発生する。たとえば、メモリセル40がプログラム動作のために選択されないとき、間隙領域56の上の電界は、ソース端子電圧（たとえば、ソース/ドレイン領域52に印加されるSRC0）と選択ゲート電圧（たとえば、選択ゲート46に印加されるSG）との間の電圧差によって、および、制御ゲート端子電圧と選択ゲート電圧との間の電圧差によって求められる。選択ゲート電圧を、読み出し動作中に未選択であるときに受ける電圧（たとえば、0V）からメモリセル40が選択されていないプログラム動作中の0.2Vに増大させることによって、バンドギャップ領域56にわたる電界が低減され得る。このように、バンド間キャリア発生が低減され、それによって、より低電圧を印加するのと比較してプログラム動作中に発生する電子/正孔対が少なくなる。それゆえ、読み出し動作中に未選択であるときに印加される電圧よりも大きいが、ピット線電圧（ソース/ドレイン領域54上の電圧）とメモリセル40の閾値電圧との合計以下の選択ゲート電圧を印加することによって、プログラムディステップの低減を達成することができる。さらに、非選択メモリセル（URSC、URUC、またはSRC位置にあるものなど）は、選択されたメモリセル（SRC位置にある）と比較して、より多くのメモリサイクル中のプログラミング動作からのストレスを受けることに留意されたい。URUC位置にある非選択メモリセルがプログラミングから最も大きなストレスを受け、URSC位置にあるものが次に大きなストレスを受ける。それゆえ、プログラミング動作中にこれらの非選択メモリセルにおけるバンド間キャリア発生を低減することによって、全体的なプログラムディステップにより大きな影響を与えることが達成され得る。

#### 【0017】

これまでで、プログラムディステップが低減された、スプリットゲートNVM内のスプリット・ゲート・メモリ・セルをプログラミングするための方法が提供されたことを理解されたい。たとえば、未選択の行に結合されている任意のメモリセルの選択ゲートに、読み出し動作中に未選択であるときの選択ゲートに印加される電圧よりも大きいが、ドレン端子上の電圧よりも大きい閾値電圧以下である電圧を印加することによって、未選択の

行に結合されているメモリセルについてバンド間キャリア発生の低減を達成することができる。さらに、未選択の行に結合されているメモリセルの選択ゲートに印加される電圧の結果として、ソース・ドレイン間漏れが増大する場合があるが、プログラムディスターブにおいてはバンド間発生漏れが優勢であること、および、選択された行のメモリセルと比較して未選択の行のメモリセルにストレスが加わるサイクルの数が大きいことに起因して、スプリットゲートNVMメモリの消去ビットの全体的なプログラムディスターブが低減される。

【0018】

本明細書において記載される半導体基板は、ガリウムヒ素、シリコンゲルマニウム、シリコン・オン・インシュレータ(SOI)、シリコン、単結晶シリコンなど、および上記の組み合わせのような、任意の半導体材料または材料の組み合わせであることができる。

10

【0019】

本発明を実装する装置は、大部分について、当業者に既知の電子コンポーネントおよび回路から成っているため、本発明の基礎となる概念の理解および評価のために、ならびに本発明の教示を分かりにくくせず当該教示から注意を逸らせないために、回路の詳細は上記で例示されているように必要と考えられる範囲を超えては説明されない。

【0020】

本発明は特定の導電型または電位の極性に関して記載されているが、当業者には導電型および電位の極性は逆になってもよいことが理解される。

20

本明細書において、具体的な実施形態を参照して本発明を説明したが、添付の特許請求の範囲に明記されているような本発明の範囲から逸脱することなくさまざまな改変および変更を為すことができる。たとえば、各メモリセルを実装するのに異なるスプリットゲート構成が使用されてもよい。従って、本明細書および図面は限定的な意味ではなく例示とみなされるべきであり、すべてのこのような改変が本発明の範囲内に含まれることが意図されている。本明細書において具体的な実施形態に関して記載されているいかなる利益、利点、または問題に対する解決策も、任意のまたはすべての請求項の重要な、必要とされる、または基本的な特徴または要素として解釈されるようには意図されていない。

【0021】

本明細書において使用される場合、「結合されている」という用語は、直接結合または機械的結合に限定されるようには意図されていない。

30

別途記載されない限り、「第1の」と「第2の」のような用語は、そのような用語が説明する要素間で適宜区別するように使用される。従って、これらの用語は必ずしも、このような要素の時間的なまたは他の優先順位付けを示すようには意図されていない。

【0022】

以下は本発明のさまざまな実施形態である。

項目1は、行および列に配列されているスプリット・ゲート・メモリ・セルの第1のセクタを有するスプリット・ゲート・メモリにおける選択的プログラミングの方法を含み、各スプリット・ゲート・メモリ・セルは、制御ゲートと、行のうちの1つに沿ったワード線に結合されている選択ゲートと、列のうちの1つに沿ったビット線に結合されているドレイン端子と、ソース端子とを有する。選択的プログラミングの方法は、選択された行および選択された列に結合されることによってプログラミングのために選択されたスプリット・ゲート・メモリ・セルについて、制御ゲートを第1の電圧に結合すること、選択ゲートを第2の電圧に結合すること、ドレイン端子を、スプリット・ゲート・メモリ・セルを導電性にする電流シンクに結合すること、ソース端子を第3の電圧に結合すること、非選択行に結合されることによってプログラムされていないスプリット・ゲート・メモリ・セル・スプリット・ゲート・セルについて、制御ゲートを第1の電圧に結合すること、選択ゲートを、スプリット・ゲート・メモリ・セルが非選択である読み出し中に選択ゲートに印加される電圧よりも大きい第4の電圧に結合することを含む。項目2は項目1の方法を含み、非選択列および選択されたワード線に結合されることによってプログラミングされていないスプリット・ゲート・メモリ・セルについて、制御ゲートを第1の電圧に結合するこ

40

50

と、選択ゲートを第2の電圧に結合すること、ドレイン端子を、第4の電圧よりも大きい第5の電圧に結合すること、ソース端子を第3の電圧に結合することをさらに含む。項目3は項目2の方法を含み、非選択行に結合されることによってプログラムされず、かつ非選択列に結合されているとして特徴付けされているスプリット・ゲート・メモリ・セルについて、ドレイン端子を第5の電圧に結合することをさらに含む。項目4は項目3の方法を含み、非選択行に結合されることによってプログラムされておらず、かつ選択された列に結合されているとして特徴付けされているスプリット・ゲート・メモリ・セルについて、ドレイン端子を電流シンクに結合することをさらに含む。項目5は項目4の方法を含み、スプリット・ゲート・メモリは、行および列に配列されている第1のセクタに隣接する第2のセクタをさらに備え、第2のセクタの各スプリット・ゲート・メモリ・セルは、制御ゲートと、行のうちの1つに沿ったワード線に結合されている選択ゲートと、第1のセクタから伸長して列に沿っているビット線のうちの1つに結合されているドレイン端子と、ソース端子とを有し、当該方法は、第2のセクタが非選択であり、かつ列が選択であることによって非選択である第2のセクタのスプリット・ゲート・メモリ・セルについて、制御ゲートを第6の電圧に結合すること、選択ゲートを第4の電圧に結合すること、ドレイン端子を電流シンクに結合すること、ソース端子を第4の電圧に結合することをさらに含む。項目6は項目5の方法を含み、第2のセクタが非選択であり、かつ列が非選択であることによって非選択である第2のセクタのスプリット・ゲート・メモリ・セルについて、制御ゲートを第6の電圧に結合すること、選択ゲートを第4の電圧に結合すること、ドレイン端子を第6の電圧に結合すること、ソース端子を第4の電圧に結合することをさらに含む。項目7は項目1の方法を含み、スプリット・ゲート・メモリ・セルがプログラムされないときに選択ゲートを第4の電圧に結合することは、スプリット・ゲート・メモリ・セルが閾値電圧を有し、第4の電圧が、ドレイン端子上の電圧を上回る閾値電圧よりも小さいことによってさらに特徴付けされる。項目8は項目1の方法を含み、スプリット・ゲート・メモリ・セルがプログラムされないときに選択ゲートを第4の電圧に結合することは、第4の電圧が、グランドよりも大きいことによってさらに特徴付けされる。項目9は項目8の方法を含み、第1の電圧は第2の電圧および第3の電圧よりも大きく、第2の電圧は第4の電圧よりも大きく、第3の電圧は第2の電圧よりも大きい。項目10は項目1の方法を含み、各スプリット・ゲート・メモリ・セルのドレイン端子は、読み出されているときはドレインとして機能し、プログラムされているときはソースとして機能し、ソース端子は、読み出されているときはソースとして機能し、プログラムされているときはドレインとして機能する。

### 【0023】

項目11は、スプリット・ゲート・メモリであって、行および列に配列されているスプリット・ゲート・メモリ・セルの第1のセクタであって、各スプリット・ゲート・メモリ・セルは、制御ゲート、行のうちの1つに沿ったワード線に結合されている選択ゲート、列のうちの1つに沿ったビット線に結合されているドレイン端子、およびソース端子を有する、第1のセクタと、プログラミング回路であって、選択された行および選択された列に結合されることによってプログラミングのために選択されたスプリット・ゲート・メモリ・セルについて、制御ゲートを第1の電圧に結合し、選択ゲートを第2の電圧に結合し、ドレイン端子を、スプリット・ゲート・メモリ・セルを導電性にする電流シンクに結合し、ソース端子を第3の電圧に結合すること、非選択行に結合されることによってプログラムされないスプリット・ゲート・メモリ・セルについて、制御ゲートを第1の電圧に結合し、選択ゲートを、読み出し中に、非選択であるスプリット・ゲート・メモリ・セルの選択ゲートに印加される電圧よりも大きい第4の電圧に結合するによってプログラミングするプログラミング回路とを含む、スプリット・ゲート・メモリを含む。項目12は項目11のスプリット・ゲート・メモリを含み、プログラミング回路は、第5の電圧を、非選択列に結合されることによって非選択であるスプリット・ゲート・メモリ・セルのドレイン端子に結合し、第4の電圧は第5の電圧よりも小さいことを特徴とする。項目13は項目11のスプリット・ゲート・メモリを含み、プログラミング回路は、電流シンクが、当

該電流シンクの結合先であるソース端子上のシンク電圧を誘起し、シンク電圧は第4の電圧よりも大きいことを特徴とする。項目14は項目11のスプリット・ゲート・メモリを含み、プログラミング回路は、読み出し中に非選択であるスプリット・ゲート・メモリ・セルの選択ゲートに印加される電圧がグランドであることをさらに特徴とする。項目15は項目11のスプリット・ゲート・メモリを含み、行および列に配列されているスプリット・ゲート・メモリ・セルの第2のセクタをさらに含み、各スプリット・ゲート・メモリ・セルは、制御ゲート、行のうちの1つに沿ったワード線に結合されている選択ゲート、列のうちの1つに沿ったビット線に結合されているドレイン端子、およびソース端子を有し、プログラミング回路は、スプリット・ゲート・メモリ・セルの第1のセクタのプログラミング中に第2のセクタが非選択であるときに、第4の電圧を第2のセクタのスプリット・ゲート・メモリ・セルの選択ゲートに結合することをさらに特徴とする。

#### 【0024】

項目16は、スプリット・ゲート・メモリを選択的にプログラミングするための方法であって、行および列に配列されているスプリット・ゲート・メモリ・セルの第1のセクタを提供することであって、各スプリット・ゲート・メモリ・セルは、制御ゲートと、行のうちの1つに沿ったワード線に結合されている選択ゲートと、列のうちの1つに沿ったビット線に結合されているドレイン端子と、ソース端子とを有する、提供すること、プログラムされるべき選択されるスプリット・ゲート・メモリ・セルを特定し、選択された行および選択された列の両方には非選択スプリット・ゲート・メモリ・セルを特定するために列および行を選択すること、選択されたスプリット・ゲート・メモリ・セルに対して、第1の電圧を制御ゲートに結合すること、第2の電圧を選択ゲートに結合すること、電流シンクをドレイン端子に結合すること、第3の電圧をソース端子に結合すること、選択された行には非選択スプリット・ゲート・メモリ・セルの各々に対して、第4の電圧を選択ゲートに結合することを含み、第4の電圧はグランドよりも大きく第2の電圧よりも小さい、方法を含む。項目17は項目16の方法を含み、選択された行になく、かつ選択された列にはスプリット・ゲート・メモリ・セルの各々に対して、第5の電圧をドレイン端子に結合することをさらに含み、第5の電圧は第4の電圧よりも大きい。項目18は項目16の方法を含み、選択された行にはないが、選択された列にあるスプリット・ゲート・メモリ・セルの各々に対して、電流シンクをドレイン端子に結合することをさらに含む。項目19は項目18の方法を含み、電流シンクは、当該電流シンクの結合先であるドレイン端子上にシンク電圧をもたらし、シンク電圧は第4の電圧よりも大きい。項目20は項目16の方法を含み、第4の電圧を選択ゲートに結合することは、第3の電圧よりも小さいことによって、プログラム中、ソース端子はドレインとして機能し、ドレイン端子はソースとして機能することを特徴とする。

#### 【符号の説明】

#### 【0025】

26、28、30、32、34、36...スプリット・ゲート・メモリ・セル、44...制御ゲート、46...選択ゲート、52、54...ソース/ドレイン領域、WL00、WL01...ワード線、BL0、BL1...ビット線。

10

20

30

【図1】

【図2】

【図3】

|                    | メモリセル位置            | CG         | SG          | BL          | SRC         |

|--------------------|--------------------|------------|-------------|-------------|-------------|

| 選択されたセクタ<br>(セクタ0) | S R S C (ビットセル2 6) | 9V (CG0)   | 1.0V (WL00) | 0.3V (BL0)  | 5V (SRC0)   |

|                    | S R U C (ビットセル2 8) | 9V (CG0)   | 1.0V (WL00) | 1.25V (BL1) | 5V (SRC0)   |

|                    | U R S C (ビットセル3 0) | 9V (CG0)   | 0.2V (WL01) | 0.3V (BL0)  | 5V (SRC0)   |

| 未選択のセクタ<br>(セクタ1)  | U R U C (ビットセル3 2) | 9V (CG0)   | 0.2V (WL01) | 1.25V (BL1) | 5V (SRC0)   |

|                    | U R S C (ビットセル3 4) | 1.5V (CG1) | 0.2V (WL10) | 0.3V (BL0)  | 0.2V (SRC1) |

|                    | U R U C (ビットセル3 6) | 1.5V (CG1) | 0.2V (WL10) | 1.25V (BL1) | 0.2V (SRC1) |

【図4】

---

フロントページの続き

(72)発明者 ロナルド ジェイ . シズデク

アメリカ合衆国 78739 テキサス州 オースティン ゴーハム グレン レーン 5713

(72)発明者 ブライアン エイ . ウインステッド

アメリカ合衆国 78757 テキサス州 オースティン ジョー セイヤーズ アベニュー 5

709

審査官 後藤 彰

(56)参考文献 特開2003-309193 (JP, A)

特開2003-46002 (JP, A)

米国特許第7236398 (US, B1)

(58)調査した分野(Int.Cl., DB名)

G 11 C 16 / 34

G 11 C 16 / 04