(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6726448号

(P6726448)

(45) 発行日 令和2年7月22日(2020.7.22)

(24) 登録日 令和2年7月1日(2020.7.1)

(51) Int.Cl.

H01L 43/06 (2006.01)

F 1

H01L 43/06

D

請求項の数 8 (全 14 頁)

(21) 出願番号 特願2015-133595 (P2015-133595)

(22) 出願日 平成27年7月2日 (2015.7.2)

(65) 公開番号 特開2016-21568 (P2016-21568A)

(43) 公開日 平成28年2月4日 (2016.2.4)

審査請求日 平成30年6月5日 (2018.6.5)

(31) 優先権主張番号 14176835.8

(32) 優先日 平成26年7月11日 (2014.7.11)

(33) 優先権主張国・地域又は機関

歐州特許庁 (EP)

(73) 特許権者 513168367

ゼニス アーゲー

イスラエル・テクノロジーズ・リミテッド

ハーティツェントラルム 11

(74) 代理人 100091683

弁理士 ▲吉▼川 俊雄

(74) 代理人 100179316

弁理士 市川 寛奈

(72) 発明者 ポポヴィック ラディヴォイエ

イスラエル・テクノロジーズ・リミテッド

ハーティツェントラルム 11

(72) 発明者 ディミトリイエヴィック ササ

セルビア共和国 ニス、ムラモール アールエス-18251 ムラモール ビービ

—

最終頁に続く

(54) 【発明の名称】縦型ホール素子

## (57) 【特許請求の範囲】

## 【請求項 1】

4接点縦型ホール素子であって、ディープNウェル(NW)と、前記ディープNウェル(NW)の表面に並べられて直線の対称線(8)に沿って配置され、中央の対称面(9)に対して対称に配置された、第1の外側接点(4)と第1の内側接点(5)と第2の内側接点(6)及び第2の外側接点(7)とを備え、

前記第1の内側接点(5)および前記第2の内側接点(6)は同じ長さおよび同じ実効幅を有し、前記第1の外側接点(4)および前記第2の外側接点(7)は同じ長さおよび同じ実効幅を有し、

前記第1の内側接点(5)の長さ、前記第2の内側接点(6)の長さ、前記第1の外側接点(4)の長さ、および、前記第2の外側接点(7)の長さは前記直線の対称線(8)に沿って測定され、

前記第1の内側接点(5)の実効幅、前記第2の内側接点(6)の実効幅、前記第1の外側接点(4)の実効幅、および、前記第2の外側接点(7)の実効幅は前記直線の対称線(8)に対して直角に測定され、

前記第1の外側接点(4)の実効幅および前記第2の外側接点(7)の実効幅は、前記第1の内側接点(5)の実効幅および前記第2の内側接点(6)の実効幅よりも大きいことを特徴とする4接点縦型ホール素子。

## 【請求項 2】

P<sup>+</sup>ストライプ(10)は前記第1の内側接点(5)と前記第2の内側接点(6)との

間に配置され、前記  $P^+$  ストライプ (10) は距離をおいて前記第1の内側接点 (5) と前記第2の内側接点 (6) とから分離される、請求項1に記載の4接点縦型ホール素子。

#### 【請求項3】

ディープPウェルリング (PW) をさらに備え、前記ディープPウェルリング (PW) の内端 (11) が前記第1の内側接点 (5) の実効幅および前記第2の内側接点 (6) の実効幅を定義する請求項1または2に記載の4接点縦型ホール素子。

#### 【請求項4】

5接点縦型ホール素子であって、ディープNウェル (NW) と、前記ディープNウェル (NW) の表面に並べられて直線の対称線 (8) に沿って配置された、第1の外側接点 (4) と、第1の内側接点 (5) と、中央接点 (12) と、第2の内側接点 (6) と、及び第2の外側接点 (7) とを備え、10

前記第1の内側接点 (5) および前記第2の内側接点 (6) は、前記中央接点 (12) に対して対称に配置され、前記第1の外側接点 (4) および前記第2の外側接点 (7) は、前記中央接点 (12) に対して対称に配置され、15

前記第1の内側接点 (5) および前記第2の内側接点 (6) は、同じ長さおよび同じ実効幅を有し、前記第1の外側接点 (4) および前記第2の外側接点 (7) は、同じ長さおよび同じ実効幅を有し、20

前記第1の内側接点 (5) の長さ、前記第2の内側接点 (6) の長さ、前記第1の外側接点 (4) の長さ、および、前記第2の外側接点 (7) の長さは前記直線の対称線 (8) に沿って測定され、25

前記第1の内側接点 (5) の実効幅、前記第2の内側接点 (6) の実効幅、前記第1の外側接点 (4) の実効幅、および、前記第2の外側接点 (7) の実効幅は前記直線の対称線 (8) に対して直角に測定され、30

前記第1の外側接点 (4) および前記第2の外側接点 (7) は短絡されており、

前記第1の外側接点 (4) の実効幅および前記第2の外側接点 (7) の実効幅は、前記第1の内側接点 (5) の実効幅および前記第2の内側接点 (6) の実効幅よりも大きいことを特徴とする5接点縦型ホール素子。35

#### 【請求項5】

前記中央接点 (12) と前記第1の内側接点 (5) との間に配置された第1  $P^+$  ストライプ (10) と、前記中央接点 (12) と前記第2の内側接点 (6) との間に配置された第2  $P^+$  ストライプ (10) とをさらに備え、前記第1  $P^+$  ストライプ (10) は前記中央接点 (12) と前記第1の内側接点 (5) とから距離を置いて分離され、前記第2  $P^+$  ストライプ (10) は前記中央接点 (12) と前記第2の内側接点 (6) とから距離を置いて分離される、請求項4に記載の5接点縦型ホール素子。40

#### 【請求項6】

ディープPウェルリング (PW) をさらに備え、前記ディープPウェルリング (PW) の内端 (11) が前記第1の内側接点 (5) の実効幅と前記第2の内側接点 (6) の実効幅と、前記中央接点 (12) の実効幅を定義する請求項4または5に記載の5接点縦型ホール素子。45

#### 【請求項7】

4接点縦型ホール素子であって、ディープNウェル (NW) と、ディープPウェルリング (PW) と、前記ディープNウェル (NW) の表面に並べられて直線の対称線 (8) に沿って配置され、中央の対称面 (9) に対して対称に配置された、第1の外側接点 (4) と第1の内側接点 (5) と第2の内側接点 (6) 及び第2の外側接点 (7) とを備え、50

前記第1の内側接点 (5) および前記第2の内側接点 (6) は、同じ長さおよび同じ実効幅を有し、前記第1の外側接点 (4) および前記第2の外側接点 (7) は、同じ長さおよび同じ実効幅を有し、55

前記第1の内側接点 (5) の長さ、前記第2の内側接点 (6) の長さ、前記第1の外側接点 (4) の長さ、および、前記第2の外側接点 (7) の長さは前記直線の対称線 (8) に沿って測定され、60

前記第1の内側接点(5)の実効幅、前記第2の内側接点(6)の実効幅、前記第1の外側接点(4)の実効幅、および、前記第2の外側接点(7)の実効幅は前記直線の対称線(8)に対して直角に測定され、

P<sup>+</sup>ストライプ(10)が前記第1の内側接点(5)と前記第2の内側接点(6)との間に配置され、前記P<sup>+</sup>ストライプ(10)は距離をおいて前記第1の内側接点(5)と前記第2の内側接点(6)とから分離され、

前記ディープPウェルリング(PW)の内端(11)が前記第1の内側接点(5)の実効幅と前記第2の内側接点(6)の実効幅を定義することを特徴とする4接点縦型ホール素子。

**【請求項8】**

10

5接点縦型ホール素子であって、ディープNウェル(NW)と、ディープPウェルリング(PW)と、前記ディープNウェル(NW)の表面に並べられて直線の対称線(8)に沿って配置された、第1の外側接点(4)と、第1の内側接点(5)と、中央接点(12)と、第2の内側接点(6)と、及び、第2の外側接点(7)とを備え、

前記第1の内側接点(5)および前記第2の内側接点(6)は、前記中央接点(12)に対して対称に配置され、前記第1の外側接点(4)および前記第2の外側接点(7)は、前記中央接点(12)に対して対称に配置され、

前記第1の内側接点(5)および前記第2の内側接点(6)は、同じ長さおよび同じ実効幅を有し、前記第1の外側接点(4)および前記第2の外側接点(7)は、同じ長さおよび同じ実効幅を有し、

20

前記第1の内側接点(5)の長さ、前記第2の内側接点(6)の長さ、前記第1の外側接点(4)の長さ、および、前記第2の外側接点(7)の長さは前記直線の対称線(8)に沿って測定され、

前記第1の内側接点(5)の実効幅、前記第2の内側接点(6)の実効幅、前記第1の外側接点(4)の実効幅、および、前記第2の外側接点(7)の実効幅は前記直線の対称線(8)に対して直角に測定され、

前記第1の外側接点(4)および前記第2の外側接点(7)は短絡されており、

前記中央接点(12)と前記第1の内側接点(5)との間に配置された第1P<sup>+</sup>ストライプ(10)と、前記中央接点(12)と前記第2の内側接点(6)との間に配置された第2P<sup>+</sup>ストライプ(10)とをさらに備え、前記第1P<sup>+</sup>ストライプ(10)は前記中央接点(12)と前記第1の内側接点(5)とから距離を置いて分離され、前記第2P<sup>+</sup>ストライプ(10)は前記中央接点(12)と前記第2の内側接点(6)とから距離を置いて分離され、

30

前記ディープPウェルリング(PW)の内端(11)が前記第1の内側接点(5)の実効幅と前記第2の内側接点(6)の実効幅と、前記中央接点(12)の実効幅とを定義することを特徴とする5接点縦型ホール素子。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、例えばCMOS技術等の集積回路のIC(集積回路)技術を用いて作製した縦型ホール素子に関する。

40

**【背景技術】**

**【0002】**

ホール効果素子又はホール素子要するにホール素子またはホールセンサとして知られるものは、磁界ベクトルの測定すべき成分を電圧に変換する素子である。+ホール素子は、現在最も使用される磁気センサである。それらはホール素子、電流源、アンプ及び他の信号状態電子回路の組み合わせたものを内蔵した集積回路及び個別素子の双方として市販されている。ホール素子の動作および基本技術の原理は非特許文献1に記述されている。

**【0003】**

簡潔に言うと、ホール素子には2つのクラスがあって、それらは横型ホール素子と縦型

50

ホール素子として知られている。横型ホール素子は平面の形状を持ち、通常は活性チップ表面に対し平行に配置されて活性チップ表面に直角に通る磁界に反応しやすい。縦型ホール素子は板状の外形を持たず、活性チップ表面に対して垂直に配置された板のように作用し、活性チップ表面に平行に通る磁界に反応しやすい。

#### 【0004】

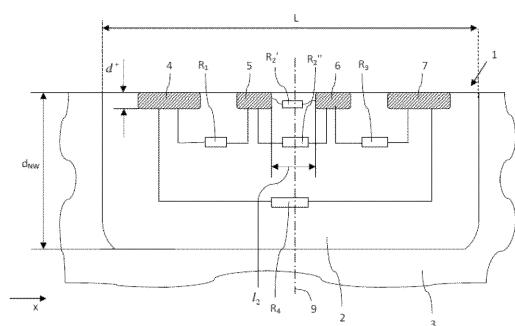

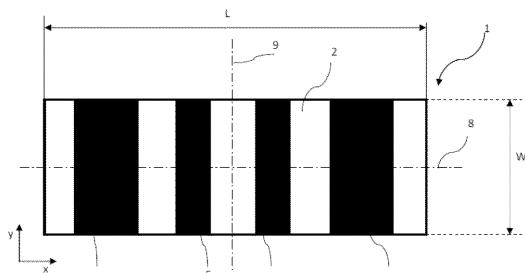

図1は従来の技術の縦型ホール素子1の断面図であり、図2はその平面図である。混乱を避けるため、下記の約束事が用いられている。縦型ホール素子の平面図を示す全ての図において、互いに直角に向き合うx軸とy軸は長さまたは幅を測定する方向を示すために用いられる。図2においては、Lなどのx軸に沿うどののような距離も長さと呼び、図2におけるWなどのy軸に沿うどののような距離も幅と呼ぶ。この約束事は検討中の構造の長さと幅の比に対して個別に適用される。10

#### 【0005】

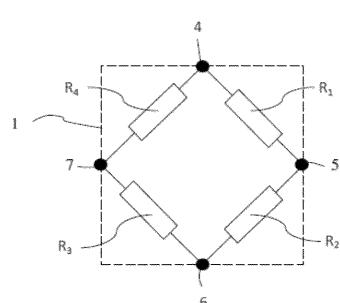

縦型ホール素子1はIC(集積回路)技術で作製される：縦型ホール素子はP型基板であるP型領域3に埋め込まれているN型領域2を有する。直線8に沿って配置された4つの高ドープN<sup>+</sup>領域がNウェルNWの表面に配置されて電気接点4～7を形成している。NウェルNWは深さd<sub>NW</sub>を有し、N<sup>+</sup>接点は深さd<sup>+</sup>を有する。縦型ホール素子1は長さLと幅Wを有する。縦型ホール素子1の2つの非隣接接点は入力端子として用いられ、他の2つの非隣接接点は出力端子として用いられる。例えば、接点4及び6は入力端子として使用でき、接点5及び7は出力端子として使用できる、逆もまた同様である。ホール素子1の接点4～7の間の電気抵抗R<sub>1</sub>、R<sub>2</sub>、R<sub>3</sub>及びR<sub>4</sub>は、図3に示すようなハイーストンブリッジで表すことができる。発明の一部として、抵抗R<sub>2</sub>はR<sub>2</sub>'、R<sub>2</sub>"の状態で2つの抵抗R<sub>2</sub>'及びR<sub>2</sub>"で構成されていると考えられる。20

#### 【0006】

ホール素子1に一定電流I<sub>in</sub>または一定電圧V<sub>in</sub>が入力端子を介して供給される。もしホール素子1が有効素子面に直角となる成分の磁界にさらされるならば、その時ホール効果の起電力は出力端子の間で作用する。出力端子の間に現れる電圧V<sub>out</sub>はホール素子1の出力電圧と呼ばれる。ホール素子の出力電圧は下記の式により与えられる：

$$V_{out} = V_{off} + S_I \times I_{in} \times B \text{ または } V_{out} = V_{off} + S_v \times V_{in} \times B \quad (1)$$

ここで、V<sub>off</sub>はオフセット電圧を示し、S<sub>I</sub>は電流関連感度を示し、Bは有効素子面に垂直な磁界の成分を示し、S<sub>v</sub>は電圧関連感度を示す。30

#### 【0007】

ホール素子は、磁界センサとして実用化に適するためには下記の主な特徴を持っている必要がある：

a) 低オフセット：例えば、シリコン集積ホール素子では、オフセット電圧V<sub>off</sub>はV<sub>off</sub> < 0.01 × V<sub>in</sub>であるはずである。

b) 使い勝手のよい共通出力電圧レベル：出力端子の電圧V<sub>out1</sub>及びV<sub>out2</sub>は入力電圧V<sub>in</sub>のおよそ中間くらいであるはずである：V<sub>out1</sub> ≈ 1/2 V<sub>in</sub> 及び V<sub>out2</sub> ≈ 1/2 V<sub>in</sub>40

c) 入力端子と出力端子の交換可能性：オフセット電圧の絶対値、出力電圧の共通レベル、入力抵抗および出力抵抗、および磁気感受性を備えるホール素子の特徴は、接点4及び6が入力端子として端子5及び7が出力端子として使用される場合と接点5及び7が入力端子として端子4及び6が出力端子として使用される場合とではほぼ等しいはずである。ホール素子の入力端子及び出力端子との交換可能性は、スピニング電流法として知られたホール素子のオフセット電圧を低減するための技術の適用のための前提条件である。

d) 高い磁気感受性：傾向としては低い供給電圧で最新のセンサシステムを操作するようになる；それゆえ、ホール素子の長所の最も関連した感受性の数字は、通常はS<sub>I</sub>ではなくS<sub>v</sub>である。例えばシリコン集積ホール素子としては、電圧に関連する磁気感受性S<sub>v</sub>はS<sub>v</sub> > 0.03 V/V T(ボルトテルサ当りボルト)であるべきである。

e) 低いフリッカ雑音(または1/f雑音として知られる)：例えばV<sub>in</sub> = 1 Vの時のホ50

ール素子供給電圧  $V_{in}$  でフリッカ雑音（雑音スペクトラル密度の  $1/f$  部分は熱雑音と同一である）のコーナー周波数  $f_c$  は  $f_c < 10 \text{ kHz}$  であるはずである。

#### 【0008】

もし4つの抵抗  $R_1$ 、 $R_2$ 、 $R_3$  及び  $R_4$  の全てがほぼ等しければ要件 a) から c) を満たす。電圧に関連する磁気感受性（要件 d）はホール素子に使用される材料とその外形の特徴との複合関数である。しかし、概略を言えば、抵抗  $R_1$ 、 $R_2$ 、 $R_3$  及び  $R_4$  が等しい値を有し、さらに“小さければ”要件 d) をより満たしやすい。ここで、“小さいこと”は抵抗の長さがその断面積の平方根以下であることを意味する。フリッカ雑音（要件 e）はホール素子に使用される材料の材質に多く依存し、さらにその表面の特性と保護に依存する。

10

#### 【0009】

理論的に言えば、どのような二次元の（平面の）横型ホール素子も等角写像として知られる数学的手法を用いて縦型ホール素子に変換することが可能である。しかし、接点の算出された次元を満足させることは実際にはほとんど不可能である。

#### 【0010】

それゆえ、集積縦型ホール素子を設計する際、全ての要件 a) ~ e) を同時に満足させることは重大な挑戦である。4接点縦型ホール素子の知られた全ての設計では、二つの外側接点 4 及び 7 の間の抵抗は 2 つの内側接点 5 及び 6 の間の抵抗よりも大変大きい、即ち、図 1 から認識できるように  $R_4 >> R_2$  となる。この不均衡は入力電圧の半分くらいのオフセット電圧を発生させる。抵抗  $R_2$  及び  $R_4$  の間の大きな相違は実際の CMOS 技術の様々な限定に起因するが、大きな 2 つの限定は下記のものである。

20

(i) 縦型ホール素子 1 の長さ  $L$  に対する N ウェル NW の小さな深さ  $d_{NW}$ （普通は、 $d_{NW} / L << 1$ ）。内側接点 5 及び 6 の名目上の大きさは大変小さく、実際 CMOS 技術の限度以下であることを等角写像で示すことができる。

(ii) 内側接点 5 及び 6 の間の小さな距離  $l_2$  と比べた  $N^+$  接点領域の実質的な深さ  $d^+$ 。この事実により、抵抗  $R_2$  が、素子表面に大変近くて平行な内側接点 5 及び 6 の 2 つの  $N^+$  領域の側壁の間を流れる電流の抵抗を表す  $R_2'$  と、素子表面の下方の“通常の”深さにある二つの内側接点 5 及び 6 の間を流れる電流の抵抗を表す  $R_2''$  の 2 つの抵抗の並列接続より構成される結果となる。並列接続した抵抗  $R_2'$  及び  $R_2''$  から構成された抵抗  $R_2$  は“通常の”  $R_2$  の抵抗よりも小さくなり、このことは  $R_2$  及び  $R_4$  の不均衡の問題をさらに悪化させる。

30

#### 【0011】

同様な問題は CMOS 技術で実装した 5 接点縦型ホール素子にも存在する。

#### 【先行技術文献】

#### 【特許文献】

#### 【0012】

【特許文献 1】米国特許第 4,782,375 号明細書

【特許文献 2】米国特許第 5,057,890 号明細書

【特許文献 3】米国特許第 7,872,322 号明細書

#### 【非特許文献】

40

#### 【0013】

【非特許文献 1】R S ポポヴィッチの書籍、表題“ホール効果素子”、物理学出版、ブリストルとフィラデルフィア、2004年 (the book by R S Popovici, entitled "HALL EFFECT DEVICES", Institute of Physics Publishing, Bristol and Philadelphia 2004)

#### 【0014】

先行技術の説明

縦型ホール素子は特許文献 1 で初めて説明された。この素子は直線に沿って配列された

50

5つの接点を有し、二つの最も外側の接点は短絡している。適切に設計された場合、5接点縦型ホール素子は要件a)、d)及びe)を満たせるが、既知の5接点構造では要件b)及びc)を満足させることははるかに困難である。

#### 【0015】

特許文献2に開示された4接点縦型ホール素子は交換可能性の要件c)を元来満足している。しかし、IC技術を用いて実装する場合、4接点縦型ホール素子は通常、大変大きなオフセットと低い電圧に関連する磁気感受性を有する；即ち、要件a)及びd)は満足されない。

#### 【0016】

特許文献3では、抵抗を抵抗 $R_4$ と平行に接続することにより集積4接点ホール素子のオフセットを低減することが提案された。この対策が上記にリストされた他の要件の満足を促進するか不安定にするかについては開示されなかった。10

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0017】

本発明はディープNウェルの表面上に直線に沿って配列した接点を有する4接点または5接点の縦型ホール素子に関する。4接点縦型ホール素子は2つの内側接点と2つの外側接点とを有する。接点は高ドープN<sup>+</sup>領域で形成されている。5接点縦型ホール素子は2つの内側接点の間に配置された中央接点を加えて有する。5接点縦型ホール素子の2つの外側接点を、例えば二つの外側接点を直接接続する金属線で短絡させている。対称理由として、2つの内側接点は同じ長さ及び同じ幅を有し、また2つの外側接点は同じ長さ及び同じ幅を有する。4接点縦型ホール素子及び5接点縦型ホール素子の双方とも、第1の対称線及び第1の対称線に直角に伸びる中央の対称面に対して対称である。20

#### 【0018】

本発明の目的は、上記の要件a)～e)の全てを満たし、商用のシリコンCMOS集積回路技術の工程を用いて作製可能な縦型ホール素子を開発することである。本発明は集積4接点及び5接点縦型ホール効果素子の斬新なレイアウトを提案するが、それは別個の作製工程を既存のシリコンCMOS技術へ追加する必要性なしに、ホール素子の高い磁気感受性を実行するだけでなく、抵抗 $R_1$ 、 $R_2$ 、 $R_3$ 及び $R_4$ の値を等しくすることを可能にする。本発明は次の通り抵抗 $R_4$ を低減し及び／または抵抗 $R_2$ を増加する縦型ホール素子の新しい設計を提案する（参照番号は図1及び図2を参照する）。30

#### 【0019】

#### a) 4接点縦型ホール素子

実施の形態によれば、外側接点の実効幅が内側接点の実効幅より大きい。それゆえ、その長さに沿う縦型ホール素子の結果として生じた実効幅は一様ではなく、内側接点の近くではより小さく外側接点の方ではより大きい。本設計は外側接点の間の抵抗 $R_4$ を低減する。

#### 【0020】

本発明の他の実施の形態によれば、P<sup>+</sup>ストライプは内側接点5及び6の間に配置される。P<sup>+</sup>ストライプは内側接点のN<sup>+</sup>領域と接触しない。P<sup>+</sup>ストライプは高ドープP<sup>+</sup>領域である。内側接点へのP<sup>+</sup>ストライプの距離が、使用されるIC技術のデザインルールが許容する最小距離よりも小さくなるように、P<sup>+</sup>ストライプの長さを選択するのが好ましい。本設計は内側接点の間の抵抗 $R_2$ を増加させる。40

#### 【0021】

さらなる実施の形態によれば、第1の実施の形態に従って外側接点の実効幅を内側接点の実効幅よりも大きくして抵抗 $R_4$ を低減し、かつ第2の実施の形態に従って内側接点の間のP<sup>+</sup>ストライプを配置することにより抵抗 $R_2$ を増大する。

#### 【0022】

#### b) 5接点縦型ホール素子

10

20

30

40

50

実施の形態によれば、外側接点の実効幅は内側接点の実効幅より大きく、かつ中央接点の実効幅は内側接点の実効幅と同一であるか、あるいはそれより小さいことが好ましい。その長さに沿った縦型ホール素子の結果として生じた実効幅は一様ではなく、中央接点の近くではより小さく外側接点の方ではより大きい。本設計は外側接点とこの外側接点から最も離れた内側接点との間の抵抗  $R_4$  を低減する。

#### 【0023】

他の実施の形態によれば、 $P^+$ ストライプは中央接点とその隣接する内側接点の各々との間に配置される。2つの $P^+$ ストライプは隣接接点の $N^+$ 領域と接触しない。2つの $P^+$ ストライプの長さを、隣接 $N^+$ 接点へのその距離が使用されるIC技術のデザインルールが許容する最小距離よりも小さくなるように選択するのが好ましい。10

#### 【0024】

本実施の形態の $P^+$ ストライプを第1の実施の形態の縦型ホール素子へ追加してもよい。。

#### 【0025】

内側接点の実効幅を追加のディープPウェルリングの内端のコースによって定義してもよい。ディープPウェルリングの内端によって囲まれたディープPウェルリングの開口の幅は、外側接点の方が内側接点よりも大きい。ディープPウェルリングはディープNウェルの深さよりも小さい深さを有する。ディープPウェルリングの側方拡散はディープNウェルリングの側方拡散よりも小さいので、縦型ホール素子の磁気感受性に対して最も寄与する活性領域の形状はよりよく定義される。20

#### 【0026】

接点の実効幅と言う用語は重要な $N^+$ 領域の表面にある接点の幅ではなく、ディープNウェル及び接点を形成するかなりドープされた $N^+$ 領域が一つに結合する領域の幅であることを意味する。

#### 【0027】

これらの全ての実施の形態の設計は抵抗 $R_1$ 、 $R_2$ 、 $R_3$ 及び $R_4$ を等しくすることが可能である。さらにこれらの設計はまた、4接点あるいは5接点縦型ホール素子の他の特徴を特に電圧に関連する磁気感受性について改善する。

#### 【0028】

その長さに沿った本発明の縦型ホール素子の変動幅は、図2に示すように幅Wが一定の従来の技術の縦型ホール素子の既知設計の全てと相違する。縦型ホール素子の幅Wは従来の横型ホール素子の厚さに相当する。横型ホール素子は活性層の一様な厚さを常に有する。明らかに、縦型ホール素子の幅Wの均一性は横型ホール素子に対する相似によるルールと考えられる。本発明はこのルールを捨てる。30

#### 【0029】

その長さに沿った本発明の縦型ホール素子の変動幅は、ホール素子の活性領域がはっきりと三次元であることを意味し、一方従来の技術の縦型ホール素子の活性領域は基本的に二次元である（活性領域は図3の面XYに存在する）。

#### 【0030】

浅い $P^+$ ストライプは $N^+$ 接点の三次元構造に由来するいくつかの負の効果を取り除き、負の効果を（図3の面XYにある）二次元接点のように作用させる。40

#### 【0031】

それゆえ、本発明の本質は、A)活性領域のいくつかの部分を二次元構造から三次元構造に変換すること、及び、B)活性領域の他のいくつかの部分を三次元構造から二次元構造に変換することによる、縦型ホール素子の特徴の改善である。最善の結果は、対策A)及びB)を組み合わせるときに実行される。

#### 【0032】

1番目の態様によれば、縦型ホール素子はディープNウェルと、ディープNウェルの表面に並べられて直線の対称線に沿って配置された2つの入力接点及び、2つの外側接点と50

を備え、2つの内側接点は同じ長さと同じ実効幅を有し、2つの外側接点は、同じ長さと同じ実効幅を有し、長さは直線の対称線に沿って測定されて幅は直線の対称線に対して直角に測定され、接点は中央の対称面に対して対称に配置され、そして外側接点の実効幅は、内側接点の実効幅よりも大きい。

**【0033】**

縦型ホール素子は内側接点の間に配置されるP<sup>+</sup>ストライプを備えててもよい、またP<sup>+</sup>ストライプは距離をおいて内側接点から分離される。

**【0034】**

縦型ホール素子は内側接点の間に配置された中央接点をさらに備えててもよい。

**【0035】**

縦型ホール素子は、中央接点と内側接点の1つとの間に配置されたP<sup>+</sup>ストライプと、中央接点ともう一方の内側接点との間に配置されるさらなるP<sup>+</sup>ストライプをさらに備えてよく、2つのP<sup>+</sup>ストライプが距離をおいて中央接点及び各隣接する内側接点とから分離される。

**【0036】**

縦型ホール素子は、ディープPウェルリングをさらに備えもよく、ディープPウェルリングの内側端面が内側接点の実効幅と、もし必要な場合には、中央接点の実効幅をも定義する。

**【0037】**

本明細書の一部に組み込まれ、また本明細書を構成する添付の図面は、本発明の1つまたは複数の実施の形態を例示し、詳細な説明と共に、本発明の原理及び実装を説明するのに役立つ。図面は明確にするための理由であり、正確には描かれていない。

**【図面の簡単な説明】**

**【0038】**

【図1】従来の技術に係る4接点縦型ホール素子の断面図を示す。

【図2】従来の技術に係る4接点縦型ホール素子の平面図を示す。

【図3】ホール素子の電気的等価回路を示す。

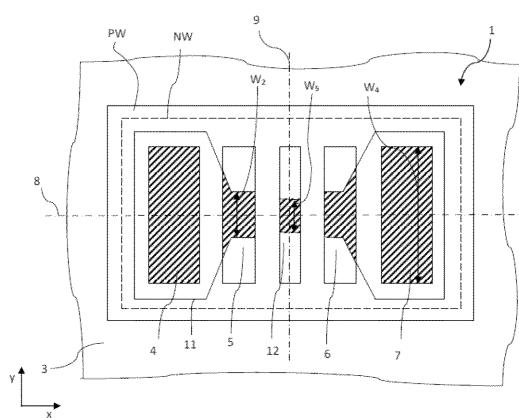

【図4】本発明に係る4接点縦型ホール素子の第1の実施の形態の平面図を示す。

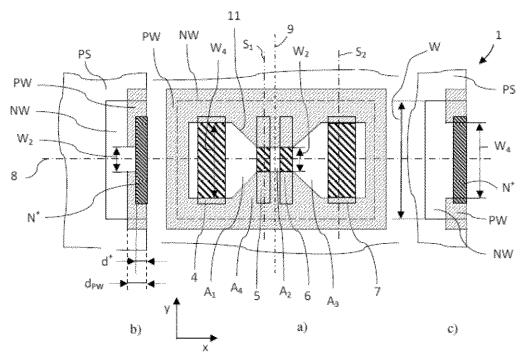

【図5】本発明に係る4接点縦型ホール素子の第2の実施の形態の1つの平面図と2つの断面図を示す。

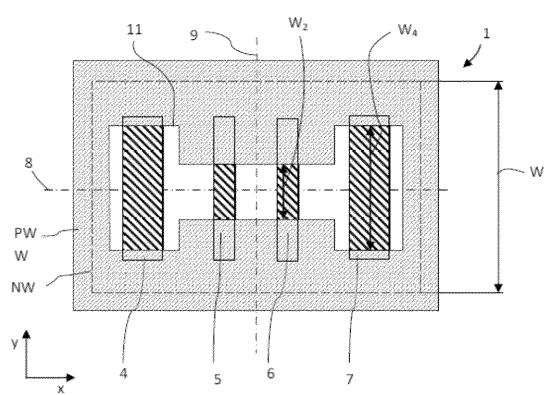

【図6】本発明に係る4接点縦型ホール素子の第3の実施の形態の平面図を示す。

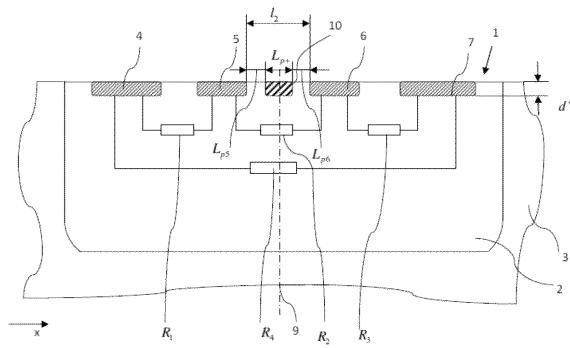

【図7】本発明に係る4接点縦型ホール素子の第4の実施の形態の断面図を示す。

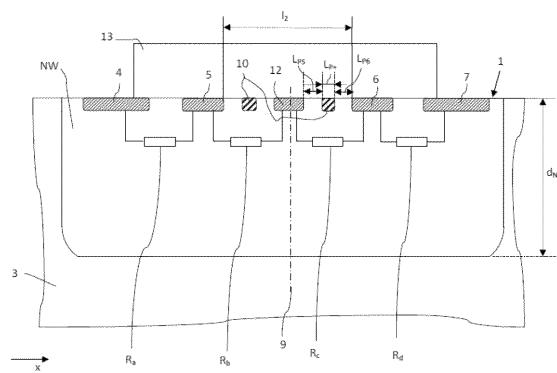

【図8】本発明に係る5接点縦型ホール素子の実施の形態の断面図を示す。

【図9】本発明に係る5接点縦型ホール素子の別の実施の形態の平面図を示す。

**【発明を実施するための形態】**

**【0039】**

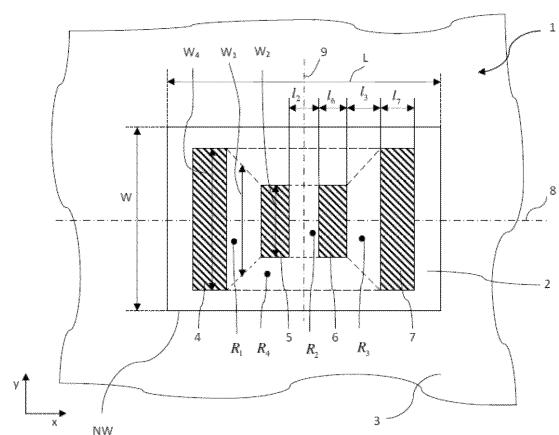

図4は本発明に係る4接点縦型ホール素子1の第1の実施の形態の平面図を示す。縦型ホール素子1は例えば周知のCMOS技術を用いて製造されており、低ドープP型基板3(基板ドープ量PSを有している)に埋め込まれたディープNウェルNWを備えている。このディープNウェルNWは長さLと幅Wの四角形の形状を有することが好ましい。縦型ホール素子1はNウェルNWの表面に並べられ、1番目の対称線8に沿って配置されて対称面9に対して対称の4つの電気接点4～7を有している。対称線8は直線で、対称面9に対して直角に走っている。電気接点4～7は図示されていない金属線で従来の方法で接続された高ドープN<sup>+</sup>領域で形成されている。電気接点4～7は、ほぼ四角形の形状を有している。内側接点5及び6は同じ長さl<sub>6</sub>と同じ幅w<sub>2</sub>を有し、外側接点4及び7は同じ長さl<sub>7</sub>と同じ幅w<sub>4</sub>を有している。内側接点5及び6の長さl<sub>6</sub>は、外側接点4及び7の長さl<sub>7</sub>よりも小さい、即ちl<sub>6</sub> < l<sub>7</sub>(1)が好ましいが、長さl<sub>6</sub>及びl<sub>7</sub>が等しくl<sub>6</sub> = l<sub>7</sub>であってもよい。

**【0040】**

内側接点5及び6の間の距離l<sub>2</sub>は、内側接点とその隣接する外側接点との間の距離1

10

20

30

40

50

<sub>3</sub>より小さく、即ち  $l_2 < l_3$  (2) が好ましいが、距離  $l_2$  及び  $l_3$  が等しく  $l_2 = l_3$  であってもよい。数式(1)及び(2)による好ましい距離は従来の技術の等角写像から知られており、ここでは議論しない。

#### 【0041】

本発明によれば、内側接点5及び6の幅  $w_2$  が外側接点4及び7の幅  $w_4$  よりも小さく、即ち  $w_2 < w_4$  (3) となっている。一実施の形態において、 $0.35 \mu\text{m}$  CMOS 技術を用いて、幅は  $w_4 = 2 \mu\text{m}$  及び  $w_2 = w_4 / 2 = 1 \mu\text{m}$  となるように選択された。

#### 【0042】

2つの外側接点4及び7の幅  $w_4$  は2つの内側接点5及び6の幅  $w_2$  より大きく、その長さに沿う縦型ホール素子の実効幅はかなり不均一である：内側接点5及び6の近くでは縦型ホール素子1の幅は外側接点4及び7の近くの縦型ホール素子1の幅よりもはるかに小さい。図1、図2及び図4の抵抗の平面形状を比較して抵抗  $R_1 \sim R_4$  の値に関するこれらの事柄の影響を予測することが可能である：従来の技術(図1及び図2)によれば、平面図で分かるように4つの全ての抵抗は等しい幅を有しており；一方、本発明(図4)によれば、平面図で分かるように抵抗の実効幅はかなり相違している。図4にある抵抗  $R_1 \sim R_4$  の領域は複雑な電流分布を持ち3次元の状態であるが、単一な形状でそれらを近似させることができる：平面図ではそれぞれ抵抗  $R_1$  及び  $R_3$  は中くらいの幅  $w_1$  のある台形として現われ、抵抗  $R_2$  及び  $R_4$  は幅  $w_2$  及び  $w_4$  の四角形として  $w_2 < w_4$  の状態で現われている。 $R_4 >> R_2$  即ち  $R_4 / R_2 >> 1$  という従来の技術の課題を思い出す。図1及び図4に示す縦型ホール素子の長さ  $L$  と他の全ての長さを同じに保持するならば、現在の  $w_2 < w_4$  の事柄は抵抗  $R_4 / R_2$  の比が下がること、即ち  $R_4 / R_2$  (本発明)  $< R_4 / R_2$  (従来の技術) を意味する。この事柄は、本発明が抵抗  $R_2$  及び  $R_4$  との間の不均衡を効果的に低減し、 $R_4 = R_2$  の状況に一致する機会をかなり増加させることを意味する。幅  $w_4$  及び  $w_2$  の比は少なくとも  $w_4 / w_2 > 1.2$  となる。

#### 【0043】

同様の分析は、変動する厚さもまた抵抗  $R_2$  及び  $R_4$  に対する抵抗  $R_1$  及び  $R_3$  の比に対して有益な影響を与えるという結論に帰着する。

#### 【0044】

縦型ホール素子では、有用な磁界依存起電力のほとんどはその素子の内側接点5及び6の近くに発生する。もし図4の内側接点5及び6の幅  $w_2$  が図3の幅  $W$  と等しいならば、またもし等しい供給電流が入力端子に供給されるのであれば、図1および図4に示すホール素子はそれらの出力端子でほぼ等しい電圧を有する。しかし、抵抗  $R_1$ 、 $R_3$  及び  $R_4$  が図4の素子においてより小さいので、本発明に係る縦型ホール素子の電圧に関連する磁気感度は従来の技術のそれよりも高くなる。

#### 【0045】

図5は本発明に係る4接点縦型ホール素子1の第2の実施の形態の1つの平面図a)と2つの断面図b)及びc)を示す。本縦型ホール素子の設計は、図4に示す縦型ホール素子1とは内側接点5及び6の実効幅がN<sup>+</sup>領域の名目上の幅ではなくて付加された適切な形状のPウェルリングPWにより定義される点で相違する。このPウェルリングPWは適度にドープされたP型領域で形成されている。N<sup>+</sup>領域、ディープPウェル及びディープNウェルの平均的ドーピングは、Doping N<sup>+</sup> >> Doping PW >> Doping NW (5) となるように選択される。それゆえ、これらの2つ以上の層が重なるとき最も高いドーピングの層が優位に立つ。図5a)に示す平面図は、a)内側接点5及び6の名目上の幅  $w_4$  は外側接点4及び7の名目上の幅と同一であり、かつb)PウェルリングPWは、外側接点4及び7近くよりも内側接点5及び6近くでより狭くなる内側形状を有していることを示す。

#### 【0046】

結果は、NウェルNWの表面のN<sup>+</sup>領域の幅は全てのN<sup>+</sup>領域に対して等しいが、d<sup>+</sup>から d<sub>PW</sub> の範囲の深さの内側接点5及び6の幅は、この深さの範囲の外側接点4及び7の幅よりも小さい。このことは、図示していない金属線でN<sup>+</sup>領域と接触することを容易

10

20

30

40

50

にし、これは素子の表面で発生することであるが、内側接点 5 及び 6 の実効幅を低減する。接点の実効幅は、 $N^+$  領域がディープ N ウェル NW と接触する領域の幅である。図 5 a ) の接点 4 ~ 7 の実線の境界線はチップの表面での接点 4 ~ 7 の大きさを示す一方、実線の境界線の斜線領域はチップの表面下の深さ  $d_{PW}$  での実効接触領域を示す。それゆえ、内側接点 5 及び 6 に対する実効幅は外側接点 4 及び 7 に対するよりも小さい。このことは図 5 a ) に示す線  $S_1$  及び  $S_2$  に沿った縦型ホール素子 1 の断面図を示す図 5 b ) 及び図 5 c ) にそれぞれ見ることができる。図 5 b ) に示すように、 $N^+$  領域の深さ  $d^+$  及び  $d_{PW}$  並びにディープ P ウェルリング PW は、 $d^+ < d_{PW}$  (6) となるように選択される。図 5 b ) 及び図 5 c ) に示すドーピングプロフィールは、接点 5 及び 6 の実効幅  $w_2$  が接点 4 及び 7 の実効幅  $w_4$  よりも小さいことを示す。

10

#### 【0047】

数式 (5) 及び (6) を満たすために、P ウェルリング PW が入力端子の間に流れる電流を  $A_1$ 、 $A_2$ 、 $A_3$  及び  $A_4$  で図 5 a ) に示された領域へ流すように、P ウェルリング PW の内端 11 の形状が選択される。内側接点 5 及び 6 の  $N^+$  領域の間の電気接点の幅とディープ N ウェル NW の隣接する部分の幅とが小さいこと - 図 5 b ) 参照 - 並びに外側接点 4 及び 7 の  $N^+$  領域間の接点の幅とディープ N ウェル NW の隣接する部分の幅が大きいこと - 図 5 c ) 参照 - がこのことを示す。その上、抵抗  $R_4$  の幅は図 5 c ) に示すようにディープ N ウェル NW の幅  $w$  によって基本的に与えられる。そこで、外側接点 4 及び 7 の間の距離が内側接点 5 及び 6 の間の距離よりも大きいにもかかわらず、これらの組の接点の間のディープ N ウェル NW の導電領域の幅が使い勝手の良い割合と相違している、即ち  $w_4 > w_2$  なので、この二組の接点の間の抵抗を等しく、即ち  $R_4 = R_2$  とすることが可能である。

20

#### 【0048】

それゆえ、説明した形状の付加的なディープ P ウェルリング PW を適用して抵抗  $R_1$ 、 $R_2$ 、 $R_3$  及び  $R_4$  の均一性を達成する手助けをする。その上、内側接点 5 及び 6 の間の電流を狭い幅  $w_2$  の経路へ押し流すことにより、縦型ホール素子 1 の電流関連感度を増加させることに帰着する。

#### 【0049】

図 6 は本発明に係る 4 接点縦型ホール素子の第 3 の実施の形態の平面図を示している。図 5 a ) に示す第 2 の実施の形態に対する唯一の相違は、ディープ P ウェルリング PW の内端 11 の異なる形状である。しかし、図 5 及び図 6 に示す実施の形態の基本的な特徴は同一である。

30

#### 【0050】

図 7 は本発明に係る 4 接点縦型ホール素子の第 4 の実施の形態の断面図を示す。縦型ホール素子 1 は内側接点 5 及び 6 の  $N^+$  領域の間に配置された  $P^+$  ストライプ 10 を有する。 $P^+$  ストライプ 10 は、 $N^+$  層の深さ  $d^+$  にほぼ等しい深さを有する浅い高ドープ P 型層を用いて実装される。 $P^+$  ストライプ 10 は、隣接する接点 5 または 6 及び 12 にこの  $P^+$  ストライプ 10 が接触しない、即ち  $P^+$  ストライプ 10 と内側の隣接する接点 5 または 6 及び 12 はそれぞれ距離  $L_{P5}$  及び  $L_{P6}$  により分離されるように選択された長さ  $L_{P+}$  を有する。 $P^+$  ストライプ 10 の  $P^+$  領域と隣接接点 5 または 6 及び 12 の  $N^+$  領域との間の分離はこれらの領域間のトンネル電流を避けるために必要である。 $P^+$  ストライプ 10 は N 型物質により囲まれているので、 $P^+$  ストライプ 10 は空乏層により隣接接点から分離される。この空乏層は接点 5 または 6 及び 12 の  $N^+$  領域の隣接する側壁の間に横電流が流れ込むのを妨げる。換言すれば、図 2 の抵抗  $R_2'$  により示される伝導路を取り除く。そうすることにより、内側接点 5 または 6 及び中央の接点 12 との間の結果として生じた抵抗  $R_b$  が増加し、抵抗  $R_a$  及び  $R_b$  をより容易に等しくできる。接点 5 または 6 及び 12 の  $N^+$  領域の隣接する側壁間のそのような横電流はホール電圧を増加するのではなく弱めるので、 $P^+$  ストライプ 10 の追加はホール素子 1 のより高い磁気感度を達成するために有益である。状況に応じて図 5 及び図 6 に示すような形狀のディープ P ウェル PW を、活性領域の幅並びに接点 5 及び 6 または全ての接点 4 ~ 7 の幅を定義するため

40

50

に使用してもよい。

#### 【0051】

十分に設計された4接点集積縦型ホール素子は内側接点5及び6の間に非常に短い距離 $l_2$ を有するはずである。この要求は、 $P^+$ 領域10、ギャップ $L_{P5}$ 、及び $L_{P6}$ の実現を不可能とするが、一方で与えられたCMOS技術のデザインルールを順守する。例えば、0.35 μm CMOS技術では、デザインルールは距離 $L_{P+}$ 、 $L_{P5}$ 及び $L_{P6}$ の各々の約0.5 μm、即ち $L_{P+} + L_{P5} + L_{P6} > 1.5 \mu m$ を許容する一方で、等角写像は $l_2 = L_{P+} + L_{P5} + L_{P6} = 0.5 \mu m$ であることを示唆する。しかしながら、IC技術のデザインルールは、ホール素子の分離ストライプの適切な機能ではなく、MOS-FETトランジスタの適切な機能を保証するために作り出されたものであり、このことはより簡潔で少ない要求の要件である。発明者の実験結果は、 $L_{P+} = 0.2 \mu m$ 及び $L_{P5} = L_{P6} = 0.15 \mu m$ を有する縦型ホール素子1は完全に機能し、十分な歩留まりで製造可能であることを示している。10

#### 【0052】

あるいは、ディープPウェルリングPWを使用する代わりに、ディープNウェルNWは、ディープPウェルリングPWのような形状をしているリングとなりうる。

#### 【0053】

主に、5接点縦型ホール素子を、各抵抗 $R_a$ 及び $R_d$ を減らすため；及び／または抵抗 $R_b$ 及び $R_c$ を増加するために類似した方法で直接設計することができる（これらの抵抗について図8参照）20

#### 【0054】

図8は5接点縦型ホール素子1の断面図を示す。5接点縦型ホール素子1は1つのディープNウェルNW、2つの内側接点5及び6、2つの外側接点4及び7、並びに内側接点5及び6の間に配置された中央接点12を有する。接点4～7及び12はディープNウェルNWの表面に並べられ直線の対称線に沿って配置される。2つの内側接点5及び6は同じ長さと同じ幅を持ち、2つの外側接点4及び7は同じ長さと同じ幅とを持っている。内側接点5及び6並びに外側接点4及び7は中央接点12に対して対称に配置されている。2つの外側接点4及び7は、例えば金属線13（象徴的に示されている）を介して直接にそれらを接続することにより短絡している。次いで、金属線13が接点4及び7を短絡させるのでホール素子の端子の1つとして機能する。縦型ホール素子1の通常の操作では、接点12及び金属線13が入力端子として接点5及び6が出力端子として使用されるか、接点5及び6が入力端子として接点12及び金属線13が出力端子として使用されるかのいずれかである。抵抗 $R_a$ 、 $R_b$ 、 $R_c$ 及び $R_d$ は素子の前記端子間の電気抵抗を記号で表示している。5接点縦型ホール素子1の電気等価回路は図3に示す抵抗と同様に、抵抗 $R_a$ 、 $R_b$ 、 $R_c$ 及び $R_d$ によって形成されたホイーストンブリッジである。対称理由として、 $R_a = R_d$ 及び $R_b = R_c$ である。30

#### 【0055】

図8は、 $P^+$ ストライプ10が内側接点5及び6の各々と中央接点12との間に配置された本発明に係る5接点縦型ホール素子1の実施の形態を示す。 $P^+$ ストライプ10は各々の隣接する内側接点5及び6並びに中央接点12から距離をおいて分離されている。等角写像により決められているように、 $P^+$ ストライプ10は短い距離 $l_2$ を保持しながら接点5及び12の間の抵抗 $R_b$ 並びに接点12及び6の間の抵抗 $R_c$ を増加させる。状況に応じて、ディープPウェルPWは活性領域の幅、並びに接点5、6及び12または接点4～7及び12の幅を定義するように用いてもよい。40

#### 【0056】

本発明に係る5接点縦型ホール素子の他の実施の形態において、外側接点4及び7の実効幅 $w_4$ は、 $w_2$ よりも若干長い内側接点5及び6の実効幅よりも大きい。このことは内側接点5及び6並びに中央接点12の $N^+$ 領域の幅を、図4に示す4接点縦型ホール素子1の実施の形態に類似して外側接点4及び7の $N^+$ 領域の幅よりも小さくすることにより、または図9に示すようにディープPウェルリングPWの内端11が適切に形成されたデ50

イープPウェルリングPWを付加することにより実行することが可能である。図9に示す実施の形態では、中央接点12の実効幅 $w_5$ は、 $w_2$ より若干大きい内側接点5及び6の実効幅よりも小さいが、中央接点12の幅を内側接点5及び6の実効幅と同一にしてもよい。

### 【0057】

状況によって、図8に示す $P^+$ ストライプ10を図9に示す縦型ホール素子1にまた加えてよい。

### 【0058】

実施の形態において、0.35 μm高電圧CMOS技術を用いて縦型ホール素子1を作製するが、ここでは下記のドープ層を提供する：ディープNウェルNWに対し、約5 μmの深さのディープNウェル層、ディープPウェルリングPWに対し、約2 μmの深さのディープPウェルPW層、 $N^+$ 領域に対し、約0.2 μmの深さのNMOSトランジスタのドレインおよびソースに使用される $N^+$ 層、 $P^+$ 領域に対し、約0.2 μmの深さのPMOSトランジスタのドレイン及びソースに使用される $P^+$ 層。10

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

---

フロントページの続き

審査官 上田 智志

(56)参考文献 米国特許出願公開第2010/0252900(US,A1)

特開2012-204836(JP,A)

特表2012-531757(JP,A)

米国特許出願公開第2012/0200290(US,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 43/06

G01R 33/07