RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 482 800**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 80 10843**

(54) Dispositif de protection d'un amplificateur de puissance, et émetteur comportant un tel dispositif.

(51) Classification internationale (Int. Cl.<sup>3</sup>). H 03 F 1/52, 3/20.

(22) Date de dépôt ..... 14 mai 1980.

(33) (32) (31) Priorité revendiquée :

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 47 du 20-11-1981.

(71) Déposant : Société anonyme dite : LE MATERIEL TELEPHONIQUE THOMSON-CSF, résidant

en France.

(72) Invention de : Claude Athenes, Jean-Claude Audrix et Joël Sarouille.

(73) Titulaire : *Idem* (71)

(74) Mandataire : P. Guiguet, Thomson-CSF - SCPI,

173, bd Haussmann, 75360 Paris Cedex 08.

L'invention concerne un dispositif de protection d'un amplificateur de puissance et plus particulièrement un dispositif de protection contre les surintensités.

Une solution pour protéger un amplificateur consiste à le dimensionner pour résister aux surintensités. Mais cette première solution a pour inconvénient d'augmenter considérablement le coût et la taille des équipements et, en outre, elle est inexploitable si l'on désire obtenir un dispositif de protection intégrable facilement.

10 Une autre solution consiste à utiliser des composants discrets tels que fusibles, résistances à coefficient de température positif ou négatif, et qui ne sont pas intégrables.

15 L'invention propose un dispositif de protection facilement intégrable qui assure la protection de l'amplificateur en présence d'une anomalie, avant qu'une détérioration ne se produise, et qui revient à l'état initial dès que l'anomalie disparaît.

Selon une caractéristique de l'invention, le dispositif de protection d'un amplificateur de puissance, comporte un premier inverseur dont l'entrée est reliée à la sortie du circuit qui 20 fournit le signal à amplifier, et dont la sortie est reliée à la borne d'entrée de l'amplificateur, et un circuit logique de protection qui comprend des moyens de détection d'une anomalie qui sont connectés d'une part à la borne de sortie de l'amplificateur et d'autre part à l'entrée du premier inverseur, et des moyens 25 de blocage de l'amplificateur reliés d'une part à la sortie des précédents moyens et d'autre part à la borne d'entrée de l'amplificateur.

Selon une autre caractéristique de l'invention, le dispositif de protection concerne la protection d'un transistor type MOS 30 utilisé comme amplificateur ayant un temps de réponse  $\theta$ , dont la grille, constituant la borne d'entrée, est reliée à la sortie du premier inverseur ayant un temps de réponse  $\theta_1$ , dont la source est reliée à la masse, et dont le drain, constituant la sortie est relié via une résistance de charge à la source de tension d'alimentation.

mentation, les moyens de détection d'anomalies comprennent un second inverseur, ayant un temps de réponse  $\theta_2$  supérieur à  $\theta + \theta_1$ , dont l'entrée est reliée à l'entrée du premier inverseur, et une porte logique "ET" dont l'une des entrées est reliée à la sortie 5 du second inverseur, et dont l'autre entrée est reliée au drain du transistor amplificateur, et les moyens de blocage comprennent un transistor de type MOS dont la grille est reliée à la sortie de la porte "ET" des moyens de détection d'anomalie, dont la source est reliée à la masse et dont le drain est relié à la grille du 10 transistor amplificateur.

Selon une autre caractéristique de l'invention, le dispositif de protection comporte un circuit d'alarme.

Selon une autre caractéristique de l'invention, le dispositif de protection est intégrable et peut être intégré sur le même 15 substrat que le transistor amplificateur.

D'autres caractéristiques de la présente invention apparaîtront plus clairement à la lecture de la description suivante d'un exemple de réalisation, cette description étant faite en relation avec les figures ci-annexées dans lesquelles :

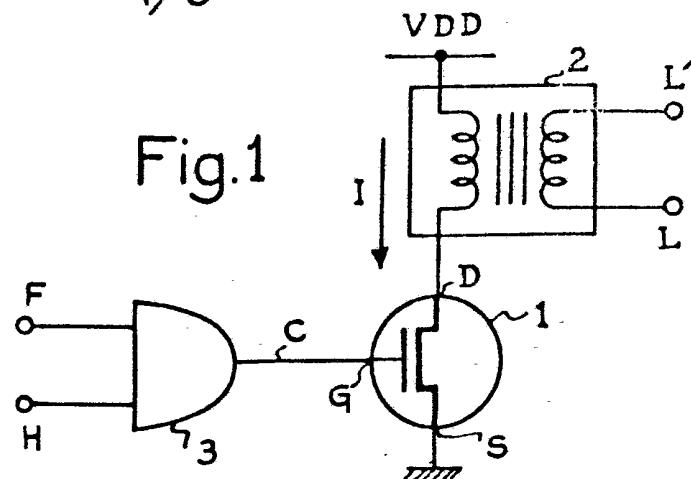

- 20 - la figure 1 représente, schématiquement, un émetteur classique comportant un transistor de type MOS comme amplificateur de puissance pour transmettre des informations sur une ligne à transformateur d'impulsion ;

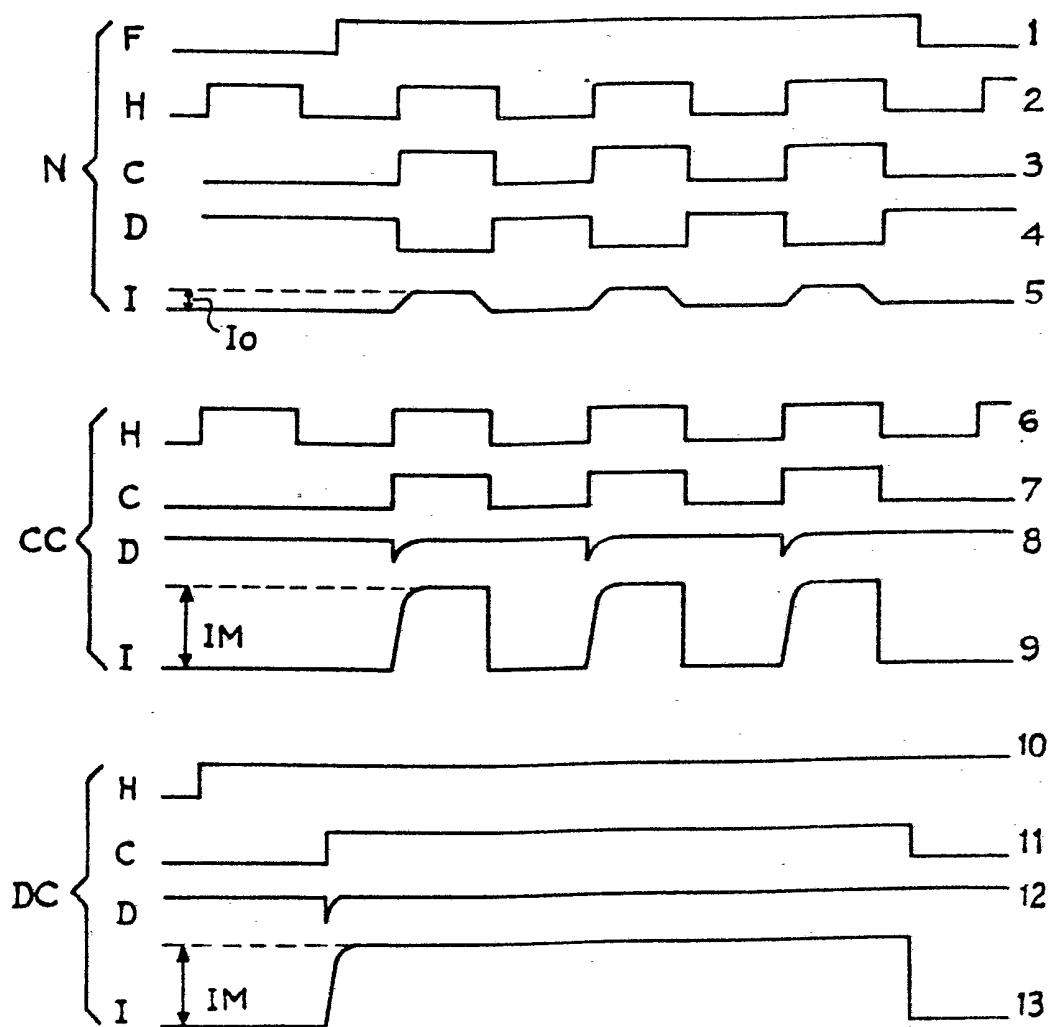

- la figure 2 donne les diagrammes des temps relatifs au fonctionnement de l'émetteur de la figure 1, d'une part en fonctionnement normal, d'autre part en cas d'anomalies ;

- la figure 3 représente un émetteur identique à celui de la figure 1, mais équipé d'un dispositif de protection de l'amplificateur de puissance conforme à l'invention ;

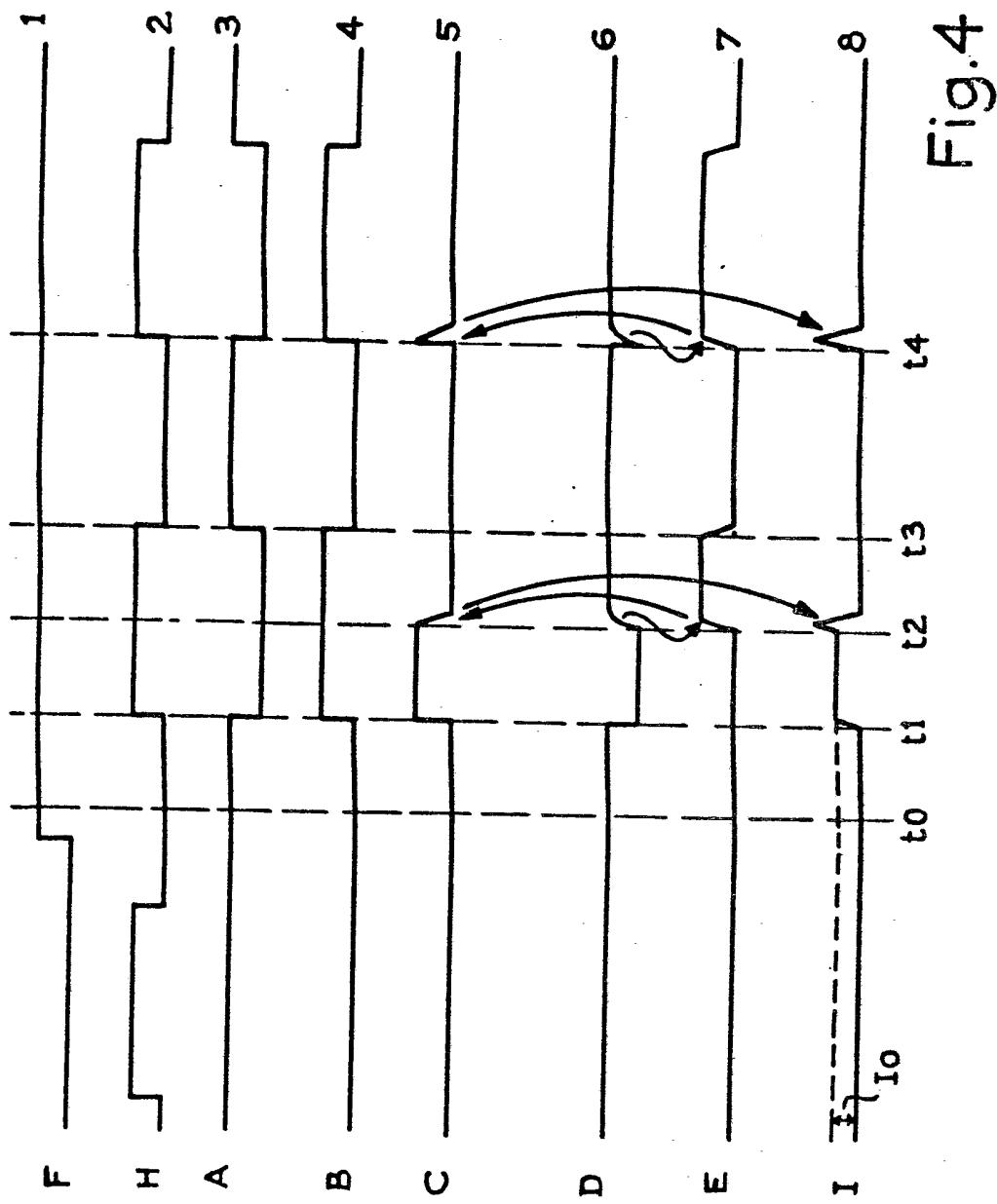

- 30 - la figure 4 donne les diagrammes des temps relatifs au fonctionnement de l'émetteur de la figure 3 ;

La figure 1 représente, schématiquement, un émetteur classique qui comprend un amplificateur de puissance constitué par un transistor 1 de type MOS dont la grille G constitue la borne d'entrée, dont la source S est reliée à la masse, et dont le 35 drain D constitue la borne de sortie.

Dans notre exemple, cet émetteur est destiné à émettre sur une ligne à transformateur d'impulsion 2 de rapport n.

La ligne de transmission est reliée aux bornes L et L' de l'enroulement secondaire du transformateur 2, et l'enroulement primaire est relié 5 d'une part à la borne D de sortie du transistor 1 et d'autre part à la source de tension d'alimentation VDD.

Dans notre exemple, les informations numériques F reçues en entrée de l'émetteur, doivent être transmises sur la ligne en code RZ ("retour à zéro"). C'est pourquoi, cet émetteur comporte 10 en entrée une porte logique "ET" 3 dont l'une des entrées reçoit le signal F à amplifier et transmettre, dont l'autre entrée reçoit un signal d'horloge H qui donne le gabarit des impulsions à transmettre et dont la sortie est reliée à la borne d'entrée G de l'amplificateur 1.

15 La figure 2 donne les diagrammes des temps relatifs au fonctionnement de l'émetteur représenté à la figure 1.

La ligne 1 représente le signal d'informations F.

Les lignes 2 à 5, regroupées par une accolade verticale, sont relatives au fonctionnement normal N de l'émetteur.

20 La ligne 2 représente le signal d'horloge H, et la ligne 3 représente le signal C issu de la porte logique "ET" 3, qui fournit les informations F codées en code RZ ("retour à zéro").

La ligne 4 représente le signal D issu de l'amplificateur 1. Lorsque le signal H est à l'état logique "1" en même temps que le 25 signal F, le signal C, et donc la grille G du transistor, est à l'état logique "1" ; ce qui entraîne que le transistor 1 est passant et par conséquent le signal D passe au niveau logique "0". Le transistor présente une faible impédance et engendre un courant à travers le primaire du transformateur 2 ; la valeur du courant 30 est donnée par le rapport de transformation n du transformateur 2.

En régime impulsional, la résistance série de charge vue par l'amplificateur est égale à  $R_1 + \frac{R_2}{n^2}$ ,  $R_1$  étant la résistance de l'enroulement primaire et  $R_2$  la résistance de l'enroulement secondaire.

35 Lorsque le signal C revient à l'état "0", la grille G du transistor 1 est, donc, à l'état "0" et le transistor 1 est à

nouveau bloqué ; il présente une impédance infinie et coupe le courant primaire, et par conséquent le courant secondaire. Le signal D revient à l'état "1".

La ligne 5 schématise la valeur du courant I qui circule dans l'enroulement primaire du transformateur 2 et dans le transistor 1, et qui prend la valeur  $I_0$  quand le signal C est au niveau logique "1".

Les lignes 6 à 9, regroupées par une accolade verticale, sont relatives au fonctionnement CC en cas de court-circuit en ligne, c'est-à-dire sur le secondaire du transformateur.

Les lignes 6 et 7 sont identiques respectivement aux lignes 2 et 3.

Puisqu'il y a un court-circuit au secondaire, la résistance secondaire ramenée au primaire est nulle et la résistance de charge de l'amplificateur devient  $R_1$  qui est très faible (inférieure à  $1 \Omega$ ). Lorsque le signal C est au niveau "1", le transistor 1 doit supporter la tension d'alimentation VDD entre ses bornes drain D et source S. Le signal D représenté à la figure 8 est au niveau logique "1". Un courant important  $I_M$ , représenté à la ligne 9, traverse le transistor 1, et la forte puissance dissipée dans le transistor 1 le détériore.

Les lignes 10 à 13, regroupées par une accolade verticale, sont relatives au fonctionnement DC en cas de signal d'horloge bloqué en permanence au niveau "1".

La ligne 10 représente le signal d'horloge H qui passe du niveau "0" au niveau et reste bloqué à "1".

La ligne 11 représente le signal C qui est en permanence au niveau "1", lorsque le signal d'informations F est au niveau "1". Sa grille étant au niveau "1", le transistor 1 de type MOS 30 est passant et un niveau continu apparaît aux bornes du transformateur 2 d'impulsion ; par conséquent, l'amplificateur 1 n'a plus pour résistance de charge que la très faible résistance du primaire  $R_1$  (inférieur à  $1 \Omega$ ).

Le signal D représenté à la ligne 12 est en permanence à "1" et un fort courant  $I_M$  représenté à la ligne 13 traverse le transistor 1, qui dissipe une puissance très importante tant que

le signal C reste au niveau "1", ce qui le détériore et risque de le détruire.

La figure 3 représente un exemple de réalisation d'un dispositif de protection, conforme à l'invention, et se rapportant à 5 l'émetteur que l'on vient de décrire.

Sur les figures 1 et 3, les éléments identiques portent les mêmes références.

L'émetteur représenté à la figure 3, comprend un amplificateur de puissance constitué par un transistor 1 de type MOS, 10 ayant un temps de réponse  $\theta_1$ , dont la source S est reliée à la masse, un transformateur d'impulsion 2 de rapport n dont l'enroulement primaire est relié d'un côté au drain D du transistor 1 et de l'autre côté à la source de tension d'alimentation VDD, et dont l'enroulement secondaire a ses bornes L et L' connectées 15 à la ligne de transmission.

L'émetteur comprend, également une porte logique "NON ET" 4 dont l'une des entrées reçoit le signal d'informations F, dont l'autre entrée reçoit le signal d'horloge H et dont la sortie fournit le signal A.

20 L'émetteur comprend, enfin, un dispositif de protection 5 qui comprend un premier inverseur 6, ayant un temps de réponse  $\theta_1$ , dont l'entrée est reliée à la sortie de la porte "NON ET" 4 et dont la sortie fournit le signal C à l'entrée G du transistor 1, un circuit logique de protection 7 et un circuit d'alarme 8.

25 Le circuit logique de protection 7 comprend des moyens de détection d'anomalies de fonctionnement constitués par un second inverseur 9, ayant un temps de réponse  $\theta_2$ , dont l'entrée est reliée à la sortie de la porte "NON ET" 4 de laquelle il reçoit le signal A, par une porte logique "ET" 10 dont l'une des entrées 30 est reliée au drain D du transistor 1, et dont l'autre entrée est reliée à la sortie de l'inverseur 9 qui lui fournit un signal B.

En outre, le circuit logique de protection 7 comprend des moyens de blocage de l'amplificateur constitués par un transistor 11 de type MOS dont la source S' est reliée à la masse, dont la grille G' est reliée à la sortie du circuit "ET" 10 qui

lui fournit un signal E, et dont le drain D' est relié à la grille G du transistor amplificateur 1.

Le circuit d'alarme 8 est constitué par une bascule 12 de mémorisation d'alarme dont l'entrée est reliée à la sortie du circuit "ET" 10 duquel elle reçoit le signal E, et dont la sortie est reliée à l'entrée de déclenchement d'un dispositif 13 capable de fournir une alarme qui peut être, par exemple, une alarme visuelle, ou un organe de supervision.

Le fonctionnement de l'émetteur muni du dispositif de protection 5 est décrit ci-dessous à l'aide des diagrammes des temps représentés à la figure 4.

La ligne 1 représente le signal d'informations F.

La ligne 2 représente le signal d'horloge H et

la ligne 3 représente le signal A, qui est issu de la porte logique "NON ET" 4 et qui est égal à  $\overline{F \cdot H}$ .

La ligne 4 représente le signal B qui est issu de l'inverseur 9 et qui est l'inverse du signal A.

La ligne 5 représente le signal C issu de l'inverseur 6.

Dans les conditions initiales données à l'instant  $t_0$  le signal d'informations est au niveau logique "1", le signal d'horloge H est au niveau "0" ; par conséquent le signal A est au niveau "1" et les signaux B et C sont au niveau "0".

Le signal C étant au niveau "0", la grille G du transistor amplificateur 1 est au niveau "0" et par conséquent, le transistor 1 est bloqué, son drain D est à la tension d'alimentation VDD, et le signal D, issu du drain D du transistor 1 et représenté à la ligne 6, est au niveau logique "1".

Il n'y a pas de courant I, représenté à la ligne 8, dans l'enroulement primaire du transformateur 2.

Le signal B étant au niveau "0", le signal D étant au niveau "1" et le signal E issu de la porte "ET" 10 étant égal à B.D, le signal E est au niveau "0" ; il est représenté à la ligne 7. Par conséquent, le transistor de protection 11 est bloqué.

Toujours en fonctionnement normal, à l'instant  $t_1$ , le signal d'horloge H passe au niveau "1" ; le signal F étant toujours à "1",

le signal A passe à "0" et les signaux B et C passent à "1".

Le signal C étant au niveau "1", la grille G du transistor 1 est au niveau "1" et par conséquent, le transistor est passant ; un courant de valeur  $I_0$  traverse ce transistor 1 et l'enroulement 5 primaire du transformateur 2.

Puisque aucune anomalie ne s'est produite, la tension au drain D du transistor 1 est faible (par exemple, inférieure à 0,5V pour un courant  $I_0$  de 20 mA), et le signal D est considéré comme étant à l'état logique "0". Le signal E, égal à B.D, est 10 encore au niveau "0" et le transistor de protection 11 est toujours bloqué.

En fonctionnement normal, le transistor de protection 11 est bloqué, et le fonctionnement de l'émetteur doit être identique à celui représenté dans l'accolade N de la figure 2.

15 Pour cela, il faut que le signal E soit au niveau "0", et il faut que, dans le cas représenté à l'instant  $t_1$ , la validation du circuit de protection par le signal B (signal B à "1") ne se présente pas avant que le signal D n'ait atteint son niveau normal "0". C'est pourquoi, il faut que le temps de réponse  $\theta_2$  de l'inverseur 9 duquel est issu le signal B, soit supérieur à la somme des temps de réponse  $\theta_1$  de l'inverseur et  $\theta$  du transis- tor amplificateur 1.

20 Lorsqu'une anomalie se présente, comme par exemple à l'instant  $t_2$ . Le courant I croît et la tension au drain D du transistor 1 aussi, jusqu'à ce qu'elle atteigne le seuil correspondant à un signal D au niveau logique "1".

25 Le signal D étant passé au niveau "1", et le signal B étant déjà au niveau "1", le signal E égal à B.D passe à "1", et la grille G' du transistor de protection 11 passe au niveau logique "1".

Par conséquent, le transistor 11 est rendu passant, son drain D' passe à la masse, et le signal C passe au niveau logique "0".

30 Le drain D' du transistor 11 étant relié à la grille G du transistor 1, le transistor 1 est bloqué, ce qui annule le courant I qui venait de prendre naissance.

Le transistor 1 n'a eu à supporter qu'un courant de valeur réduite pendant un temps très court, ce qui ne risque pas de le détériorer.

Si à l'instant  $t_3$ , le signal d'horloge H passe au niveau 5 logique "0", le signal B passe au niveau "0" et le signal E passe à "0" et le transistor de protection 11 est à nouveau bloqué ; le dispositif est revenu à l'état initial défini par l'instant  $t_0$ .

Le dispositif est prêt à fonctionner à nouveau, comme on l'a représenté à l'instant  $t_4$  à la figure 4.

10 On a vu ci-dessus que toute anomalie constatée se traduit par le passage au niveau logique "1" du signal E. Le circuit d'alarme 8 enregistre cette condition au moyen de la bascule 12, qui est reliée à un dispositif 13 capable de signaler l'anomalie et qui peut être une alarme visuelle ou un organe de supervision, ce 15 dernier pouvant être extérieur au circuit.

Un tel dispositif de protection permet une intégration conventionnelle des éléments utilisés : transistors de type MOS, et portes logiques réalisables par des transistors de type MOS.

De plus, le retard de l'inverseur 9 par rapport à l'inverseur 20 6 et au transistor 1 est très facilement réalisable et contrôlable en jouant sur la géométrie des transistors intégrés.

Enfin, le transistor émetteur 1 ne dissipant plus qu'une puissance très faible il peut être aussi intégré et l'on peut réaliser un émetteur muni de son dispositif de protection sur un 25 circuit intégré monolithique.

REVENDICATIONS

1. Dispositif de protection (5) d'un amplificateur de puissance (1), caractérisé en ce qu'il comporte un premier inverseur (6) dont l'entrée est reliée à la sortie du circuit qui fournit le signal (A) à amplifier, et dont la sortie est reliée à la borne 5 d'entrée (G) de l'amplificateur (1), et un circuit logique de protection (7) qui comprend des moyens de détection d'une anomalie qui sont connectés d'une part à la borne de sortie (D) de l'amplificateur (1) et d'autre part à l'entrée du premier inverseur (6), et des moyens de blocage de l'amplificateur reliés d'une part 10 à la sortie des précédents moyens et d'autre part à la borne d'entrée (G) de l'amplificateur (1).

2. Dispositif de protection (5) d'un amplificateur de puissance (1) selon la revendication 1, caractérisé en ce que l'amplificateur de puissance est un transistor (1) de type MOS, 15 ayant un temps de réponse  $\theta$ , dont la grille (G), constituant la borne d'entrée, est reliée à la sortie du premier inverseur ayant un temps de réponse  $\theta_1$ , dont la source (S) est reliée à la masse, et dont le drain (D), constituant la borne de sortie, est relié via une résistance de charge à la source de tension d'alimentation 20 (VDD), en ce que les moyens de détection d'anomalies comprennent un second inverseur (9), ayant un temps de réponse  $\theta_2$  supérieur à  $\theta + \theta_1$ , dont l'entrée est reliée à l'entrée du premier inverseur (6), et une porte logique "ET" (10) dont l'une des entrées est reliée à la sortie du second inverseur (9), dont l'autre entrée 25 est reliée au drain (D) du transistor amplificateur (1), et en ce que les moyens de blocage comprennent un transistor (11) de type MOS dont la grille (G') est reliée à la sortie de la porte "ET" des moyens de détection d'anomalies, dont la source (S') est reliée à la masse, et dont le drain (D') est relié à la grille (G). 30 du transistor amplificateur (1).

3. Dispositif de protection selon la revendication 2, caractérisé en ce qu'il comporte un circuit d'alarme (8) constitué par une bascule (12) de mémorisation d'alarme dont l'entrée est reliée à la sortie de la porte logique "ET" (10) des moyens de détection 35 d'anomalies, et dont la sortie est reliée à l'entrée de déclen-

chement d'un système d'alarme (13) d'un organe de supervision.

4. Emetteur comportant un amplificateur de puissance, caractérisé en ce qu'il comporte un dispositif de protection selon l'une quelconque des revendications 1 à 3.

5. Emetteur, caractérisé en ce qu'il comporte un amplificateur de puissance constitué par un transistor (1) de type MOS intégré sur un circuit intégré monolithique, et en ce qu'il comporte un dispositif de protection selon l'une quelconque des revendications 2 et 3, qui est intégré sur le même substrat.

1/3

Fig.1

Fig.2

2/3

Fig. 3

2482800

3/

13

Fig.4