(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) Int. Cl.<sup>6</sup>

G11C 16/00

(11) 공개번호 특 1995-0006867

(43) 공개일자 1995년03월21일

(21) 출원번호 특 1994-0020701

(22) 출원일자 1994년 08월 22일

(30) 우선권주장 8/109,887 1993년08월23일 미국(US)

(71) 출원인 어드밴스드 마이크로 디바이시즈, 인코포레이티드 미키오 이시마루

미합중국 캘리포니아 서니베일 원 에이엠디 플레이스 (우편번호 : 94088)

(72) 발명자 청 케이. 창

미합중국 캘리포니아 서니베일 산 후안 드라이브 627 #4 (우편번호 : 94086)

자니 씨. 첸

미합중국 캘리포니아 쿠퍼티노 웨스틀린 웨이 1038 (우편번호 : 95104)

マイケル エイ. バン バスカ크

미합중국 캘리포니아 산 호세 페이비언 드라이브 1742 (우편번호 : 95124)

리 이. 클리브랜드

신사철구 · 엉을

(54) 페이지 소거 구조를 갖는 플래시 아이피를 어레이용 돌리 어레이 전자

98

페이지 소거를 갖는 플래시 EEPROM 셀의 어레이에 대한 개선된 구조가 제공된다. 어레이는 다수의 반-섹터로 구성된다. 각각의 섹터에 있어서, 메모리 셀 트랜지스터의 소오스는 분리된 개별 접지라인에 접속된다. 접지라인회로는 반-섹터 접지라인신호를 발사이키도록 제공된다. 분리된 개별 접지라인은 소거하는 동안 사전결정된 파지티브 전위에 있는 반-섹터 접지라인신호를 수신하도록 접지라인회로에 접속된다.

附录二

53

면세점

「박며이 며치」

페이지 수거 규제를 가는 플래시 아이피를 어레이용 돌리 어레이 전자

### [도면이 가다한 선면]

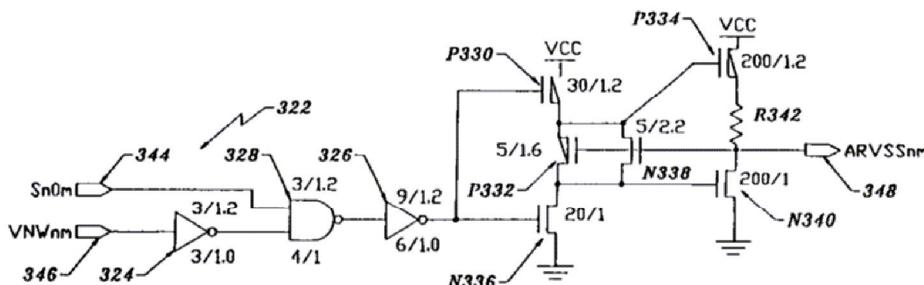

제3도는 볼 밖면에 따라 구성된 반-섹터(half-sector) 접지 라인 히트를 하나의 개략 히트로

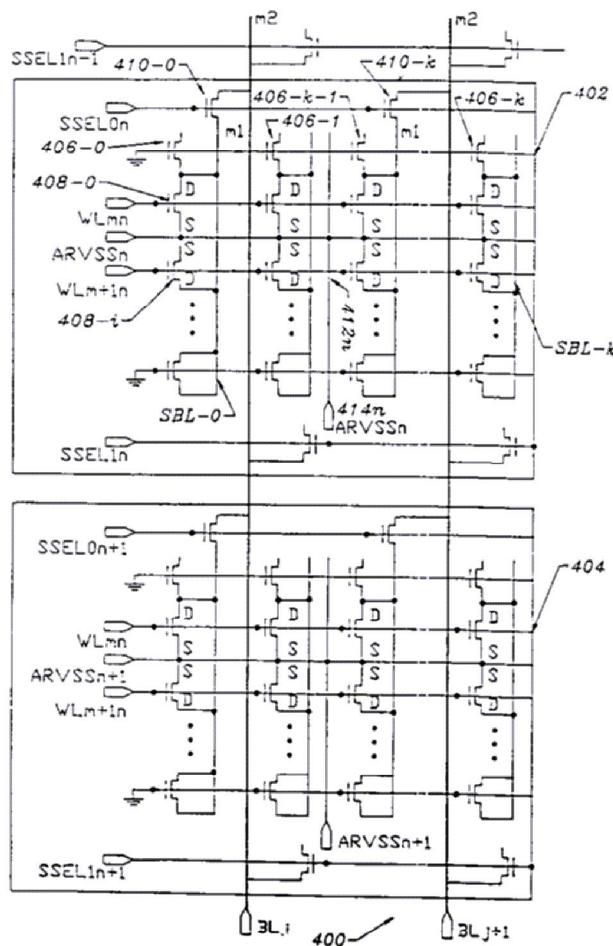

제4도는 복 발명의 구조를 사용한 플래시 EEPROM 메모리 셀의 두 개의 센터를 나타낸 도면

본 내용은 유불공개 것이므로 전문 내용을 숨기거나 알았을 때

(57) 청구의 범위

첨부 1

다수의 반-섹터로 구성된 어레이 수단을 갖는 반도체 집적회로 메모리 소자에 있어서, 각각의 상기 다수의 반-섹터는, 워드 라인의 행 및 상기 워드 라인의 행에 교차하는 비트 라인의 열로 배열되어지고, 소오스, 드레인, 부동 게이트 및 제어 게이트를 갖는 부동 게이트 트랜지스터를 각각 포함하는 다수의 메모리셀과, 상기 메모리 셀이 열을 형성하도록 반-섹터 비트라인 수단에 접속되어지고, 상기 열에서 상기 메모리 셀이 반-섹터 비트라인 수단에 병렬로 접속되어지도록, 상기 각각의 행에 있어서 메모리 셀의 드레인에 각각 접속되어진 다수의 반-섹터 비트라인 수단과, 상기 다수의 반-섹터 비트라인 수단에 기능적으로 접속되어 반-섹터를 선택하는 수단과, 상기 선택된 섹터상에서의 소거 동작동안 상기 다

수의 섹터에 있는 비-선택된 섹터가 영을 받지 않도록 반-섹터 점지 라인신호를 발생시키는 점지 라인회로 수단(322)으로 구성되고, 상기 각각의 행에 있는 상기 메모리 셀의 상기 제어 게이트는 상기 워드라인중 하나에 접속되고, 상기 메모리 셀의 상기 소오스는 분리된 개별 점지라인에 접속되고, 상기 분리된 개별 점지라인은 상기 점지라인회로 수단에 접속되어 상기 반-섹터 점지라인신호를 수신하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 2

제1항에 있어서, 상기 점지라인회로 수단은 반-섹터의 선택에 있어서 소거하는 동안 사전결정된 파지티브 전위에 있는 반-섹터 점지라인신호를 발생시키도록 반-섹터 선택신호에 응답하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 3

제2항에 있어서, 상기 반-섹터 점지라인신호는 상기 반-섹터의 비-선택에 있어서 소거하느 동안 점지 전위에 있는 것을 특징으로 하는 반도체 집적회로 메모리소자.

### 청구항 4

제1항에 있어서, 상기 반-섹터 선택 수단은 소오스, 드레인, 게이트를 각각 구비하는 다수의 반-섹터 선택 트랜지스터를 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 5

제4항에 있어서, 상기 각각의 반-섹터 비트 라인 수단은 상기 반-섹터 선택 트랜지스터중 하나의 소오스에 접속된 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 6

제5항에 있어서, 상기 반-섹터 선택 트랜지스터의 게이트는 반-섹터 선택신호를 수신하도록 접속되는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 7

제2항에 있어서, 상기 사전결정된 파지티브 전위는 대략 +5.0볼트인 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 8

제1항에 있어서, 소거하는 동안 선택된 섹터에 있는 상기 메모리 셀의 상기 제어 게이트에 비교적 네ги티브 전위를 발생시키고 공급하는 네가티브 서플라이 수단을 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 9

제8항에 있어서, 상기 네가티브 전위는 대략 -12.0볼트인 것을 특징으로 하는 반도체 집적회로 메모리 수단.

### 청구항 10

다수의 반-섹터로 구성된 어레이 수단을 갖는 반도체 집적회로 메모리 소자에 있어서, 상기 각각의 다수의 반-섹터는, 워드라인의 행 및 상기 워드라인의 행에 교차하는 비트라인의 열로 배열되어지고, 소오스, 드레인, 부동 게이트 및 제어 게이트를 갖는 부동 게이트 트랜지스터를 각각 포함하는 다수의 메모리 셀과, 상기 메모리 셀이 열을 형성하도록 반-섹터 비트라인 수단에 접속되어지고, 상기 열에서 상기 메모리 셀이 반-섹터 비트라인이 수단에 병렬로 접속되어지도록, 상기 각각의 행에 있어서 메모리 셀의 드레인에 각각 접속되어진 다수의 반-섹터 비트라인 수단과, 상기 다수의 반-섹터 비트라인 수단에 기능적으로 접속되어 반-섹터를 선택하는 수단과, 상기 선택된 섹터상에서의 소거 동작동안 상기 다수의 섹터에 있는 비-선택된 섹터가 영향을 받지 않도록 다중 반-섹터 점지 라인 신호를 발생시키는 다수의 점지 라인 회로 수단(322)으로 구성되고, 상기 각각의 행에 있는 상기 메모리 셀의 제어 게이트는 상기 워드라인중 하나에 접속되고, 상기 메모리 셀의 상기 소오스 분리된 개별 점지라인에 접속되고, 상기 분리된 개별 점지라인은 상기 다수의 점지라인회로 수단 중 관련된 하나에 접속되어 상기 반-섹터 점지라인신호중 부합하는 하나를 수신하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 11

제10항에 있어서, 상기 각각의 다수의 점지라인회로 수단은 상기 반-섹터의 선택에 있어서 소거하는 동안 사전결정된 파지티브 전위에 있는 다중 반-섹터 점지라인신호중 부합하는 하나를 발생시키도록 관련된 반-섹터 선택 신호에 응답하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 12

제11항에 있어서, 상기 각각의 다수의 반-섹터 점지라인신호는 상기 반-섹터의 비-선택에 있어서 소거하는 동안 점지 전위에 있는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

### 청구항 13

제10항에 있어서, 상기 반-섹터 선택 수단은 소오스, 드레인, 게이트를 각각 가지는 다수의 반-섹터

선택 트랜지스터를 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

#### 청구항 14

제13항에 있어서, 상기 각각의 반-섹터 비트라인 수단은 상기 반-섹터 선택 트랜지스터중 하나의 소오스에 접속된 것을 특징으로 하는 반도체 집적회로 메모리 소자.

#### 청구항 15

제14항에 있어서, 상기 반-섹터 선택 트랜지스터의 상기 게이트는 반-섹터 선택신호를 수신하도록 접속되는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

#### 청구항 16

제11항에 있어서, 상기 사전결정된 파지티브 전위는 대략 +5.0볼트인 것을 특징으로 하는 반도체 집적회로 메모리 소자.

#### 청구항 17

제10항에 있어서, 소거하는 동안 선택된 섹터에 있는 상기 메모리 셀의 상기 제어 게이트에 비교적 네가티브 전위를 발생시키고 공급하는 네가티브 서플라이 수단을 포함하는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

#### 청구항 18

제17항에 있어서, 상기 네가티브 전위는 대략 -12.0볼트인 것을 특징으로 하는 반도체 집적회로 메모리 소자.

#### 청구항 19

워드라인의 행 및 상기 워드라인의 행에 교차되는 비트라인의 열로 배열되고, 부동 게이트, 제어 게이트, 분리된 독립 접지라인에 접속된 소오스 영역 및 비트 라인중 각각의 하나에 접속된 드레인 영역을 각각 포함하고, 고온 전자를 그 부동 게이트로 이전함에 의해 각각 우수하게 프로그램가능하고, 그 부동 게이트로부터 그 소오스 영역으로 전자를 터널링함에 의해 각각 우수하게 소거가능한 다수의 메모리 셀을 포함하는 다수의 반-섹터를 포함하는 반도체 집적회로 메모리 소자로, 상기 각각의 다수의 반-섹터는, 반-섹터 접지라인신호를 발생시키는 접지라인회로 수단(322)을 포함하고, 상기 메모리 셀의 상기 제어 게이트는 플래시 소거하는 동안 비교적 네가티브 전위를 수신하고, 상기 분리된 독립 접지라인은 상기 접지라인회로 수단에 접속되어 상기 반-섹터 접지라인신호를 수신하는 것을 특징으로 하는 반도체 집저기회로 메모리 소자.

#### 청구항 20

제19항에 있어서, 상기 반-섹터 접지라인신호는 상기 반-섹터의 선택에 있어서 소거하는 동안 사전결정된 파지티브 전위에 있고, 상기 반-섹터의 비-섹터의 선택에 있어서 소거하는 동안 접지 전위에 있는 것을 특징으로 하는 반도체 집적회로 메모리 소자.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

#### 도면

##### 도면3

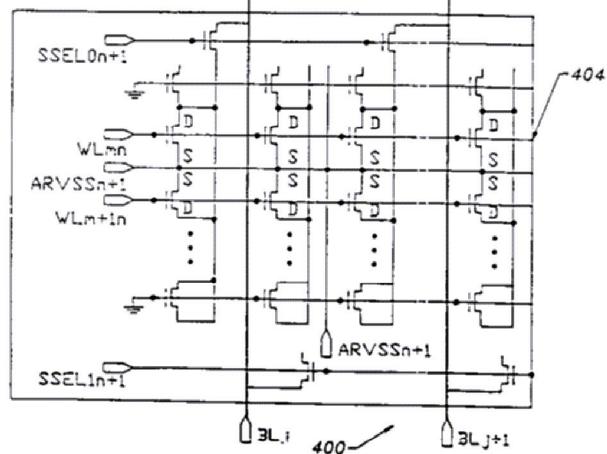

## 도면4