(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6126600号

(P6126600)

(45) 発行日 平成29年5月10日(2017.5.10)

(24) 登録日 平成29年4月14日(2017.4.14)

|              |            |

|--------------|------------|

| (51) Int.Cl. | F 1        |

| HO3M 9/00    | (2006.01)  |

| HO4L 25/02   | (2006.01)  |

| HO4L 7/00    | (2006.01)  |

| HO4L 7/033   | (2006.01)  |

| HO3M 9/00    | HO3M 9/00  |

| HO4L 25/02   | HO4L 25/02 |

| HO4L 7/00    | HO4L 7/00  |

| HO4L 7/033   | HO4L 7/033 |

|              | V          |

|              | 080        |

|              | 700        |

請求項の数 17 (全 13 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-525315 (P2014-525315)  |

| (86) (22) 出願日 | 平成24年8月16日 (2012.8.16)        |

| (65) 公表番号     | 特表2014-522204 (P2014-522204A) |

| (43) 公表日      | 平成26年8月28日 (2014.8.28)        |

| (86) 国際出願番号   | PCT/DE2012/200051             |

| (87) 国際公開番号   | W02013/023653                 |

| (87) 国際公開日    | 平成25年2月21日 (2013.2.21)        |

| 審査請求日         | 平成27年8月17日 (2015.8.17)        |

| (31) 優先権主張番号  | 102011052760.5                |

| (32) 優先日      | 平成23年8月16日 (2011.8.16)        |

| (33) 優先権主張国   | ドイツ (DE)                      |

|           |                                                                                                                                                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 509348867<br>シリコン・ライン・ゲー・エム・ペー・ハ<br>ー<br>ドイツ連邦共和国 80687 ミュンヘ<br>ン ランツベルガー・シュトラーセ 31<br>4 / テア・ドリッテン エルゲーベー<br>LANDSBERGER STR. 31<br>4 / 111 RGB., 80687<br>MUENCHEM, BUNDESRE<br>PUBLIK DEUTSCHLAND<br>(74) 代理人 110001818<br>特許業務法人 R&C |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

最終頁に続く

(54) 【発明の名称】回路装置および信号を送信するための方法

## (57) 【特許請求の範囲】

## 【請求項 1】

シングルエンド論理レベルベースのデータ信号およびクロック信号 (H S) と、差動データ信号および差動クロック信号 (L P) との両方を、少なくとも 1 つのシリアル化された共通信号ストリーム (S I) の形態で、少なくとも 1 つのデータソースに割り当て可能な少なくとも 1 つの送信装置 (S) と、少なくとも 1 つのデータシンクに割り当て可能な少なくとも 1 つの受信装置 (E) との間で伝送するための回路装置 (S, E) であって、前記差動データ信号および差動クロック信号 (L P) のデータ転送速度は、前記シングルエンド論理レベルベースのデータ信号およびクロック信号 (H S) のデータ転送速度よりも遅いことを特徴とする回路装置。

## 【請求項 2】

前記差動データ信号はコモンモードベースである請求項 1 に記載の回路装置。

## 【請求項 3】

前記送信装置 (S) は、

前記データ信号およびクロック信号 (H S ; L P) のための少なくとも 1 つの入力部 (E S) と、

入力部 (E S) の下流の、前記データ信号およびクロック信号 (H S ; L P) を受け取るための少なくとも 1 つの送信インタフェースロジック (L S) と、

送信インタフェースロジック (L S) の下流の、前記共通信号ストリーム (S I) を生成するための少なくとも 1 つのシリアルライザ (S E) と、

10

20

シリアルライザ (S E) の上流で、送信インターフェースロジック (L S) の少なくとも 1 つのクロックモジュール (C S) の下流に設けられた、少なくとも 1 つの基準クロックを生成するための少なくとも 1 つのクロック発振器 (P S) と、

シリアルライザ (S E) の下流の少なくとも 1 つの出力ドライバ (A T) と、

出力ドライバ (A T) の下流の、前記共通信号ストリーム (S I) を前記受信装置 (E) へ送信するための少なくとも 1 つの出力部 (A S) と、

を備えることを特徴とする請求項 1 または 2 に記載の回路装置。

【請求項 4】

前記クロック発振器 (P S) は、少なくとも位相ロックループとして構成されることを特徴とする請求項 3 に記載の回路装置。

10

【請求項 5】

前記クロック発振器 (P S) は、少なくとも 1 つのクロックマルチプライヤユニットとして構成されることを特徴とする請求項 4 に記載の回路装置。

【請求項 6】

前記シリアルライザ (S E) は、

前記送信インターフェースロジック (L S) の下流の、前記共通信号ストリーム (S I) のための、前記受信装置 (E) で認識可能な少なくとも 1 つのフレームを生成するための少なくとも 1 つのフレーマ (F R) と、

前記フレーマ (F R) の下流の、前記共通信号ストリーム (S I) を生成するための少なくとも 1 つのマルチブレクサ (M U) と、

20

を備えることを特徴とする請求項 3 ~ 5 の いずれか 一項に記載の回路装置。

【請求項 7】

前記シングルエンド論理レベルベースのデータ信号 (H S D 0, H S D 1, H S D 2, H S D 3) と前記差動データ信号 (D D 0 +, D D 0 -, D D 1 +, D D 1 -, D D 2 +, D D 2 -, D D 3 +, D D 3 -) との両方を、前記フレーマ (F R) に印加することができること、および、前記フレーマは、少なくとも 1 つの符号器 (K O) を用いて、前記差動データ信号 (D D 0 +, D D 0 -, D D 1 +, D D 1 -, D D 2 +, D D 2 -, D D 3 +, D D 3 -) を、前記シングルエンド論理レベルベースのデータ信号 (H S D 0, H S D 1, H S D 2, H S D 3) のストリームに埋め込むことを特徴とする請求項 4 又は 5 に記載の回路装置。

30

【請求項 8】

前記少なくとも 1 つの符号器は、少なくとも 1 つの 5 b / 6 b 符号器ブロックである請求項 7 に記載の回路装置。

【請求項 9】

前記マルチブレクサ (M U) は、

前記差動データ信号および / または差動クロック信号 (L P) と、前記シングルエンド論理レベルベースのデータ信号および / またはクロック信号 (H S) を識別するための少なくとも 1 つのフィルタ (F I) と、

前記フィルタ (F I) から来る前記差動データ信号および / または差動クロック信号 (L P) を追加的に印加することのできる少なくとも 1 つの追加的なマルチブレクサ (M U Z) と、

40

を備えることを特徴とする請求項 6 ~ 8 の いずれか 一項に記載の回路装置。

【請求項 10】

前記受信装置 (E) は、

前記送信装置 (S) によって送信された前記共通信号ストリーム (S I) のための少なくとも 1 つの入力部 (E E) と、

前記共通信号ストリーム (S I) を受け取るための少なくとも 1 つの入力増幅器 (E V) と、

前記データ信号およびクロック信号 (H S, L P) を前記共通信号ストリーム (S I) から復元するための少なくとも 1 つのクロックおよびデータリカバリユニット (C D) と

50

、 前記クロックおよびデータリカバリユニット( C D )の下流の、少なくとも1つの受信インタフェースロジック( L E )の少なくとも1つのクロックモジュール( C E )と、

前記クロックおよびデータリカバリユニット( C D )の下流の、前記データおよび/またはクロック信号( H S , L P )を再並列化するための、および再並列化された前記データおよび/またはクロック信号( H S , L P )を受信インタフェースロジック( L E )に割り当てるための少なくとも1つのデシリアライザ( D S )と、

前記受信インタフェースロジック( L E )の下流の、前記データ信号およびクロック信号( H S , L P )のための少なくとも1つの出力部( A E )と、

を備えることを特徴とする請求項1~9のいずれか一項に記載の回路装置。 10

【請求項11】

前記デシリアライザ( D S )は、

前記クロックおよびデータリカバリユニット( C D )の下流の、前記データおよび/またはクロック信号( H S , L P )を再並列化するための少なくとも1つのデマルチプレクサ( D M )と、

前記デマルチプレクサ( D M )の下流の、再並列化された前記データおよび/またはクロック信号( H S , L P )を、前記受信インタフェースロジック( L E )に割り当てるための少なくとも1つのデフレーマ( D F )と、

を備えることを特徴とする請求項10に記載の回路装置。 20

【請求項12】

前記デフレーマ( D F )は、前記差動データ信号( D D 0 + , D D 0 - , D D 1 + , D D 1 - , D D 2 + , D D 2 - , D D 3 + , D D 3 - )を、少なくとも1つの復号器( D K )を用いて、前記シングルエンド論理レベルベースのデータ信号( H S D 0 , H S D 1 , H S D 2 , H S D 3 )と分けて、再並列化された前記データ信号を、それぞれのデータライン( C H 0 + , C H 0 - , C H 1 + , C H 1 - , C H 2 + , C H 2 - , C H 3 + , C H 3 - )に割り当てる特徴とする請求項11に記載の回路装置。 20

【請求項13】

前記少なくとも1つの復号器は、少なくとも1つの5b/6b復号器ブロックである請求項12に記載の回路装置。 20

【請求項14】

前記共通信号ストリーム( S I )は、

少なくとも1つの光学媒体( O M )を介して、および/または

少なくとも1つの電気的またはガルバニックのリンク( G A )を介して、前記送信装置( S )と前記受信装置( E )との間で転送可能であることを特徴とする請求項1~13のいずれか一項に記載の回路装置。 30

【請求項15】

シングルエンド論理レベルベースのデータ信号およびクロック信号( H S )と、

差動データ信号および差動クロック信号( L P )との両方を、

少なくとも1つのシリアル化された共通信号ストリーム( S I )の形態で、少なくとも1つのデータソースに割り当てる可能な少なくとも1つの送信装置( S )と、少なくとも1つのデータシンクに割り当てる可能な少なくとも1つの受信装置( E )との間で伝送するための方法であって、前記差動データ信号および差動クロック信号( L P )のデータ転送速度が、前記シングルエンド論理レベルベースのデータ信号およびクロック信号( H S )のデータ転送速度よりも遅いことを特徴とする方法。 40

【請求項16】

前記差動データ信号はコモンモードベースである請求項15に記載の方法。

【請求項17】

前記送信装置( S )と前記受信装置( E )との間の共通信号ストリーム( S I )は、

少なくとも1つの光学媒体( O M )を介して、および/または

少なくとも1つの電気的またはガルバニックのリンク( G A )を介して転送されること 50

を特徴とする請求項 15 または 16 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、請求項 1 のプリアンブルに記載の回路装置、ならびに請求項 15 のプリアンブルに記載の対応する方法に関する。

【背景技術】

【0002】

ビット伝送層または物理層 (physical layer: PHY) は、OSI (Open Systems Interconnection) 参照モデルとも呼ばれる OSI 階層モデルの最下位層であり、コンピュータネットワークにおける通信プロトコルの設計基準としても役に立つ、国際標準化機構 (International Standards Organization: ISO) の階層モデルを示す。

10

【0003】

物理層 (PHY) は、結合、順方向誤り訂正 (Forward Error Correction: FEC)、電力制御、拡散 (符号分割多元接続) (Code Division Multiple Access: CDMA) 等に関与し、およびデータもアプリケーションも識別せず、0 と 1 のみを識別する。PHY は、その上のセキュリティ層 (データリンク層) (Data Link Layer: DLL) が、特に、媒体アクセス制御 (Media Access Control: MAC) 層と呼ばれる部分層を利用可能な論理チャネル (UMTS (Universal Mobile Telecommunications System) 用のトランスポートチャネル) を形成する。

20

【0004】

原理的に、D-PHY は、モバイル装置内のコンポーネント間の通信リンクのためのフレキシブルで、低コストで、高速のシリアルインタフェースを実現できる。

【0005】

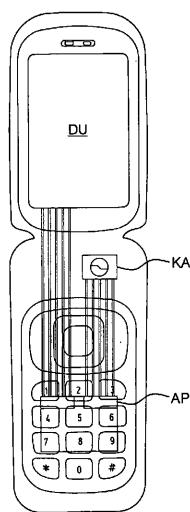

図 4 A に示すように、最新の携帯電話において、データソース、例えば、アプリケーションプロセッサは、関連するデータシンク上、例えば、関連するディスプレイ上での表示のために、イメージデータを D-PHY 信号として、MIPI-DSI (Mobile Industry Processor Interface - Display Serial Interface) に供給する。また、アプリケーションプロセッサ等のデータシンクは、関連するデータソースから、例えば、関連するカメラから、MIPI-CS (Camera Serial Interface) を介して、D-PHY フォーマットでイメージデータを受信することができる。

30

【0006】

D-PHY プロトコルに基づく DSI または DSI-2 または CSI または CSI-2 または CSI-3 は、4 つ以下の差動データラインと、差動クロックラインとを備え、これらは、銅ケーブルを用いて、該アプリケーションプロセッサを該ディスプレイおよび/または該カメラに接続する。差動データライン当たりのデータ転送速度は、最高で 1.5 Gbps (ギガビット/秒) である。

40

【0007】

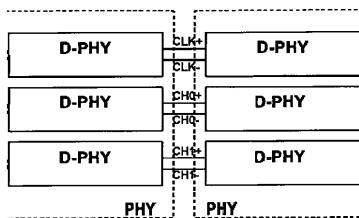

1 ~ 4 つの差動データ信号および差動クロックラインを介した、この従来の D-PHY - DSI 信号または D-PHY - CSI 信号の送信および受信は、マスター側のモジュール (データソース、例えば、カメラおよび/またはアプリケーションプロセッサ) と、スレーブ側のモジュール (データシンク、例えば、アプリケーションプロセッサおよび/またはディスプレイユニット) との間の (データレーン CH0+, CH0- および CH1+, CH1- と呼ばれる) 2 つのデータチャネルおよび (クロックレーン CLK+, CLK- と呼ばれる) クロックラインを手段として、図 4 B の D-PHY インタフェース構造に例として図示されている。

【0008】

この状況において、図4Aを見て分かるように、各関連するディプレイのための、または、各関連するカメラのためのデータ伝送には、最高10の銅線（例えば、2つのデータラインの4倍と、2つのクロックラインの1倍）を要する。

【0009】

ラインの数の望ましい低減を考えると、シリアル化された信号伝送を考慮すべきである。しかし、そのようなシリアル化は、エラーを起こしやすく、不安定なことが多い。

【発明の概要】

【発明が解決しようとする課題】

【0010】

上述した欠点および不十分な点を発端として、ならびに概略が説明された従来技術を考慮して、本発明の目的は、効率的なシリアル化信号伝送を、エラーのない安定した方法で、常に実行できるように、上述したタイプの回路装置および上述したタイプの方法をさらに発展させることである。

【課題を解決するための手段】

【0011】

この目的は、請求項1の特徴を有する回路装置と、請求項12の特徴を有する方法によって達成される。本発明の有利な実施形態および適切なさらなる発展は、それぞれの従属項において特徴付けられている。

【0012】

したがって、回路装置および方法が提案され、それを用いて、

論理レベルに基づく信号に対応するシングルエンド高速（H i g h S p e e d : H S

）データと、

特に、コモンモード信号に基づく信号に対応する差動低電力（L o w P o w e r : L P

）データと、

がシリアル化されて、共通信号ストリームを形成する。

【0013】

シリアル化された共通信号ストリームを伴うこの種の伝送路を用いて、H S / L P データは、少なくとも1つのマルチプレクサを本質的に備える少なくとも1つの送信ビルディングブロック（=送信装置）によって一括化されて、シリアル化された共通データストリームとして、受信ビルディングブロック（=受信装置）へ送信される。

【0014】

少なくとも1つのデマルチプレクサを本質的に備えるこの受信装置は、該シリアルデータを細分化して、それを元の形態でH S / L P データとして再び出力する。該送信装置に印加されたクロック（C l o c k : C L K）は、該マルチプレクサのクロック基準として機能し、および該共通シリアル信号ストリームに埋め込まれる。該受信装置は、このクロックを再生して、それをC L Kとして再出力する。

【0015】

全てのデータ入力部がH S データを処理する状況に基づく、データビルディングのための通常のアプローチは、該データが多重化されて、シリアルデータストリームとして送出されることである。

【0016】

しかし、M I P I - D - P H Y 規格においては、いわゆるL P 送信モードへのリターンは、H S データのシグナリングに用いられる電圧レベルの範囲外の電圧振幅によって伝えられることが既に合意されている。

【0017】

これらのL P 信号レベルは、既に説明したように、単純に一括化されたシリアルデータストリームのデータスペースで符号化することができない追加的な情報を示す。

【0018】

本発明によれば、特に、L P データだけを含み、H S レーンと並列に該マルチプレクサに入力される少なくとも1つの追加的な、特に仮想レーンを挿入することが提案されてい

10

20

30

40

50

る。これは、このために設けられた該マルチプレクサの入力部の H S データのための符号化スペースを拡大することなく、 L P 状態を伝えることを可能にする。

【 0 0 1 9 】

このレーン、具体的には、テレグラムレーンと呼ぶこともできる仮想レーンは、他のシステム関連情報を運ぶのにも用いることができ、例えば、該レーンは、該シリアルデータリンクが間もなく切断されるという情報を送信するのに用いることができるであろう。

【 0 0 2 0 】

本発明は、典型的には、シングルエンド論理レベルベースのデータ信号およびクロック信号と、特に、コモンモードベースの差動データ信号およびクロック信号の両方の、具体的には、 D - P H Y データ信号または D - P H Y クロック信号、例えば、 1 ~ 4 ビット幅の M I P I - D - P H Y データ信号および M I P I - D - P H Y クロック信号の、少なくとも 1 つのデータソース、具体的には、例えば、少なくとも高解像度カメラおよび / または画像ソースとして機能するカメラおよび / または少なくとも 1 つのアプリケーションプロセッサと、少なくとも 1 つのデータシンク、具体的には、少なくとも 1 つのアプリケーションプロセッサおよび / または少なくとも 1 つの高解像度ディスプレイユニットまたは例えば、画像シンクとして機能するディスプレイユニット、例えば、少なくとも 1 つのディスプレイまたは少なくとも 1 つのモニタとの間での、少なくとも 1 つのシリアルおよび / または一括の、具体的には、 C S I プロトコルベースのおよび / または C S I - 2 プロトコルベースのおよび / または C S I - 3 プロトコルベースのおよび / または D S I プロトコルベースのおよび / または D S I - 2 プロトコルベースの送信中に適用することができる。

10

【 0 0 2 1 】

前述したように、本発明に関する教示を有利な方法で具体化し、さらに発展させる様々な可能性がある。このため、一方において、請求項 1 に従属する請求項について、および請求項 12 について説明し、他方においては、本発明の追加的な実施形態、特徴および効果が、以下でより詳細に、とりわけ、図 1 A ~ 図 3 によって図示されている例示的な実施形態によって説明されている。

20

【 図面の簡単な説明 】

【 0 0 2 2 】

【 図 1 A 】本発明の方法に従って作動する、本発明に従って構成された回路装置の第 1 の部分、すなわち、送信装置の実施形態を示す、概念的略図である。

30

【 図 1 B 】図 1 A における送信装置のフレーマの実施形態の詳細を示す、概念的略図である。

【 図 1 C 】図 1 A の送信装置のマルチプレクサの実施形態の概念的略図である。

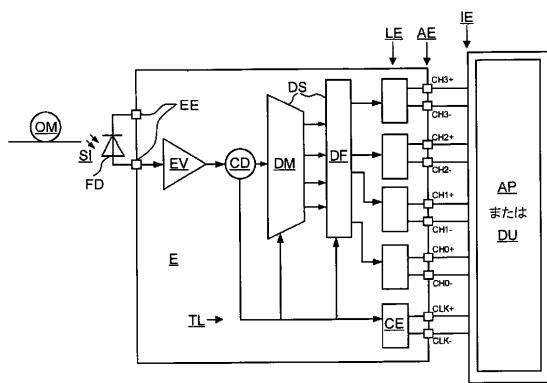

【 図 2 A 】本発明の方法に従って作動する、本発明に従って構成された回路装置の第 2 の部分、すなわち、送信装置の実施形態を示す、概念的略図である。

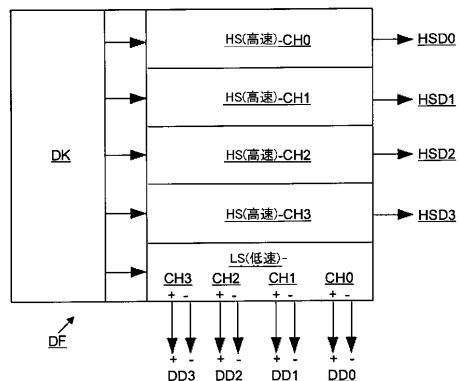

【 図 2 B 】図 2 A の受信装置のデフレーマの実施形態の詳細を示す、概念的略図である。

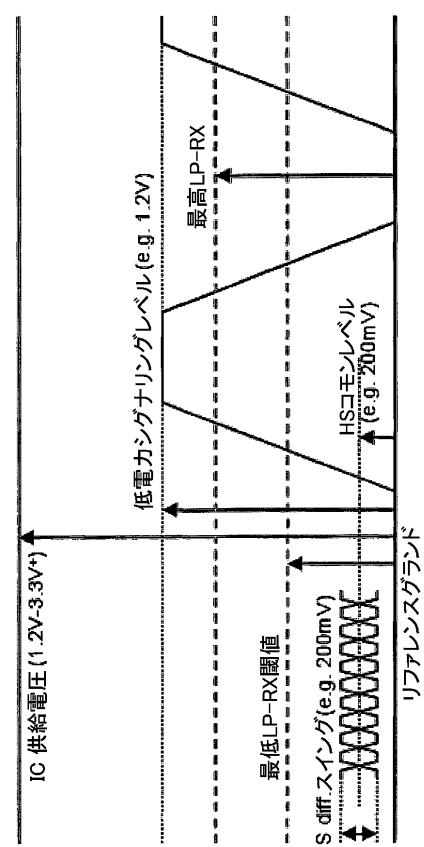

【 図 3 】 H S データ伝送および L P データ伝送の場合のそれぞれの電圧レベルの実施形態の概略図である。

【 図 4 A 】従来技術による装置の実施例の概念的略図である。

40

【 図 4 B 】図 4 A に示す装置がそれをベースにしている、 2 つのデータチャネルとクロックラインとを備えるインターフェース構造の実施例の概念的略図である。

【 発明を実施するための形態 】

【 0 0 2 3 】

図 1 A ~ 図 4 B において、類似のまたは同様の実施形態、要素または機能には、同一の参照数字が付けられている。

( 発明を具体化するための最良の方法 )

【 0 0 2 4 】

原理的には、

本発明による送信装置 S に関する図 1 A に示す実施形態によって、および

50

本発明による受信装置 E に関する図 2 A に示す実施形態によって、ケーブルベースのリンクを実現するおよび作動させるための、本発明による回路装置 A (図 1 A、図 2 A を参照) が得られ (本発明に関しては、互いに無関係に、送信装置 S と受信装置 E を実現すること、作動させることができある)、

そのリンクは、光学的に、具体的には、少なくとも 1 つの光学媒体に基づいて、例えば、光導波路 O M (図 1 A、図 2 A の詳細図を参照) に基づいて、例えば、少なくとも 1 つのガラス纖維に基づいて、および / または少なくとも 1 つのプラスチック纖維に基づいて多重化され、およびシリアル化され、および / または

そのリンクは、電気的にまたはガルバニックに、具体的には、少なくとも 1 つの電気的またはガルバニックなリンクに基づいて、例えば、少なくとも 1 つの銅線に基づいて、および / または例えば、少なくともプリント回路基板上に配列された少なくとも 1 つの電気的ラインに基づいて多重化されていない

ことが可能である。

#### 【 0 0 2 5 】

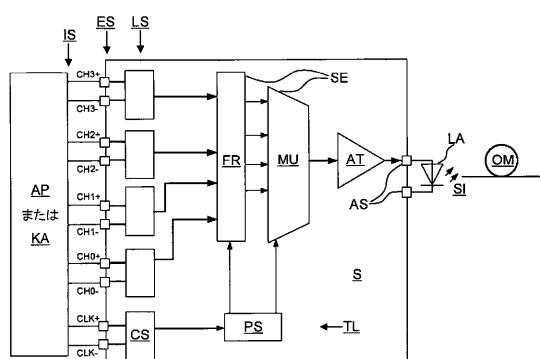

図 1 A は、D S I データ伝送インタフェース I S または C S I データ伝送インタフェース I S への接続のための送信装置 S の原理的構造の実施形態を示す。

#### 【 0 0 2 6 】

アプリケーションプロセッサ A P 内で、または、カメラ K A 内で生成された画像データは、D - P H Y 補正クロック信号 C L K + , C L K - とともに、最高で 4 ビット幅のデータ伝送インタフェース I S において、4 つ他のデータラインまたはデータチャネル C H 0 + , C H 0 - , C H 1 + , C H 1 - , C H 2 + , C H 2 - , C H 3 + , C H 3 - 上で D - P H Y 信号として利用可能になっている。

#### 【 0 0 2 7 】

送信装置 S は、これらの信号を集積インターフェースロジック L S において受け取り、そのブロックは、それらの信号が、D - P H Y 信号の正しい解釈のための、および高周波データストリーム (いわゆる H S データ) と低周波データストリーム (いわゆる低速 (L o w S p e e d : L S ) データ) を区別するための少なくとも 1 つの状態機械を有することを証明できる。

#### 【 0 0 2 8 】

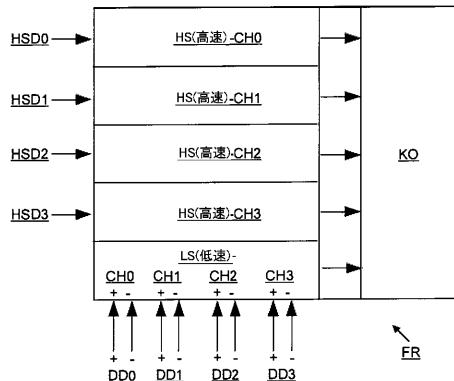

送信装置 S における次のフレーム F R (図 1 B の詳細図も参照) は、入力信号の直流 (D i r e c t C u r r e n t : D C ) 平衡を確保し、および受信側 (図 2 A を参照) で認識可能なフレームを生成し、そのことは、受信装置 E (図 2 A を参照) が、補正出力データラインまたは出力チャネル C H 0 + , C H 0 - , C H 1 + , C H 1 - , C H 2 + , C H 2 - , C H 3 + , C H 3 - に、受信したデータを再割当てすることを可能にする。

#### 【 0 0 2 9 】

詳細には、論理レベルベースのシングルエンドデータ信号 H S D 0 , H S D 1 , H S D 2 , H S D 3 と、差動データ信号 D D 0 + , D D 0 - , D D 1 + , D D 1 - , D D 2 + , D D 2 - , D D 3 + , D D 3 - の両方を、図 1 B によるフレーム F R に印加することができる。5 b / 6 b 符号化ブロックとして構成されたその符号器 K O を用いて、図 1 B による該フレームは、それらの差動データ信号 D D 0 + , D D 0 - , D D 1 + , D D 1 - , D D 2 + , D D 2 - , D D 3 + , D D 3 - を、シングルエンド論理レベルベースのデータ信号 H S D 0 , H S D 1 , H S D 2 , H S D 3 から成るストリームに埋め込む。

#### 【 0 0 3 0 】

フレーム F R に隣接するマルチプレクサ M U 、具体的には、H S M u x は、位相ロッカグループとして、具体的には、C M U として構成されたクロック発振器 P S を用いて、高周波シリアルまたは一括送信信号を生成し、その信号は、出力ドライバ A T を用いて、送信装置 S の出力 A S において利用可能になっている。フレーム F R とマルチプレクサ M U は、一緒にシリアルライザ S E を構成している。

#### 【 0 0 3 1 】

クロック発振器 P S を用いて、クロックポート C L K + , C L K - を介して、およびイ

10

20

30

40

50

ンタフェースロジックLSのクロックモジュールCSを介して供給されたD-PHYクロック信号は、シリアルライザSEのための、具体的には、そのマルチプレクサMUのための（クロック）基準として用いられ、および該シリアルデータストリームに、すなわち、シリアル化された出力信号に埋め込まれる。これにより、受信装置E（図2Aを参照）に伝達される共通信号ストリームSIが生成される。

【0032】

さらに図1Aを見て分かるように、出力ドライバATは、少なくとも1つの直接接続されたレーザLAを駆動するための、具体的には、少なくとも1つの面発光レーザ（Vertical Cavity Surface Emitting Laser diode:VCSEL）を駆動するための一体型レーザドライバとして実装されている。 10

【0033】

図2Aは、DSIデータ伝送インタフェースIEまたはCSIデータ伝送インタフェースIEへの接続のための受信装置Eの原理的構造の実施形態を示す。

【0034】

送信装置S（図1Aを参照）によって送出されたシリアルまたは一括データは、受信装置Eの入力増幅器EVを介して受け取られ、集積クロックまたはデータリカバリCDへ供給される。

【0035】

この集積クロックまたはデータリカバリCDは、共通信号ストリームSIから元のD-PHYクロックを再生し、その後、該クロックは、インタフェースロジックLEのクロックモジュールCEを介して、再び、DSIまたはCSIが直接、利用できるようにされる。残りのシリアルデータストリームは、デマルチプレクサDMによって細分化および並列化されて、原理的には、図1BによるフレーマFRの鏡像であるデフレーマDF（図2Bも参照）へ引き渡される。デマルチプレクサDMとデフレーマDFは、一緒にデシリアルライザDSを構成する。 20

【0036】

詳細には、図2BのデフレーマFRは、6b/5b復号器ブロックとして構成されたその復号器DKを用いて、差動データ信号は、DD0+, DD0-, DD1+, DD1-, DD2+, DD2-, DD3+, DD3-と、シングルエンド論理レベルベースのデータ信号HSD0, HSD1, HSD2, HSD3を分けて、再並列化されたデータ信号を、それぞれの適用可能なデータラインCH0+, CH0-, CH1+, CH1-, CH2+, CH2-, CH3+, CH3-に再割り当てすることができる。 30

【0037】

受信装置E内に図示されているインタフェースロジックブロックLEは、それぞれ、D-PHY論理信号の正しい解釈のための、および高周波データストリームと低周波データストリームを区別するための少なくとも1つの状態機械を備えていてもよい。

【0038】

図2Aの説明図を見ても分かるように、入力増幅器EVは、集積トランスインピーダンス増幅器として実装され、該増幅器は、フォトダイオードFDを受信装置Eに直接接続することを可能にしている。 40

【0039】

このようにして、本発明によれば、回路装置S, E（図1A、図2Aを参照）に関しては、送信装置S（図1Aを参照）と受信装置E（図2Aを参照）との間で、ケーブルベースの多重化リンクを光学的に、すなわち、例えば、ガラス纖維の形態および/またはプラスチック纖維の形態で構成された光導波路OMを用いて実現し、および作動させることができる。

【0040】

全てのデータ入力部ESが、シングルエンド論理レベルベースの信号に対応するHSデータを処理する状況に基づいて、データー括化のための通常のアプローチは、図1AによるマルチプレクサMUによって該データを多重化して、それをシリアル信号ストリームS 50

Iとして送出することである。

【0041】

しかし、M I P I - D - P H Y 規格においては、特に、コモンモードベースの差動信号に対応するL P送信モードへのリターンは、図3に示すように、H Sデータのシグナリングに用いられる電圧レベルの範囲外の電圧振幅によって伝えられることが既に合意されている。

【0042】

これらのL P信号レベルは、既に説明したように、単純に一括化されたシリアル信号ストリームS Iのデータスペースで符号化することができない追加的な情報を示す。

【0043】

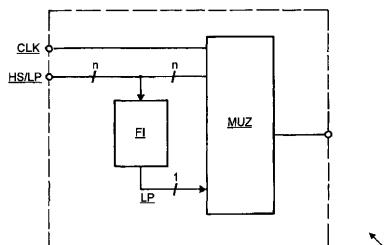

このため、特に、L Pデータだけを含み、H Sレーンと並列に該マルチプレクサM Uに入力される、図1Cによる追加的な仮想レーンが導入されている。

【0044】

のために、少なくとも1つのフィルタF Iが、マルチプレクサM UのH S / L Pデータ入力部に設けられ、該フィルタは、該データに固有の電圧レベルにより、L PデータとH Sデータを識別することができる。このフィルタF Iは、このようにして得られたL Pデータを、追加的な入力、いわば、仮想H Sデータレーンとして、さらなるまたは追加的なマルチプレクサM U Zへ供給する。

【0045】

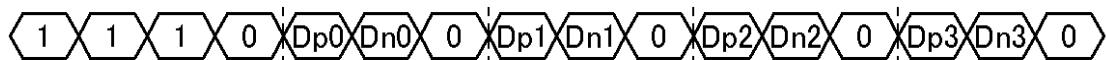

このレーンは、テレグラムレーンと呼ぶことができる。該仮想テレグラムレーンの例示的な構造は、以下のようになると思われる。

【0046】

【数1】

【0047】

該仮想テレグラムレーンの16のビットは、受信側Eで同期を実施するのに用いられる、最初の4ビット長の同期/スタートシーケンスと、

その後の、L Pデータごとの3ビットと、に分けられている。

【0048】

したがって、図示の実施形態においては、4つのレーン入力C H 0 + , C H 0 - , C H 1 + , C H 1 - , C H 2 + , C H 2 - , C H 3 + , C H 3 - が処理される。

【0049】

さらなるまたは追加的なマルチプレクサM U Zの上流でのL Pデータのシリアル化により、これらのL Pデータは、並列に送信されるH Sデータと同じデータ転送速度では送信されない。実施例として、ここで処理されるこのM I P I - D - P H Yシステムにおいては、いずれにしても、L Pデータのデータ転送速度は、H Sデータのデータ転送速度よりもかなり遅い。

【0050】

図2AによるデマルチプレクサD Mは、図1CによるマルチプレクサM Uの鏡像として構成することができる。

【符号の説明】

【0051】

E 受信装置

S 送信装置

A E 受信装置Eの出力部

10

20

30

40

50

|         |                                                                                                     |    |

|---------|-----------------------------------------------------------------------------------------------------|----|

| A P     | アプリケーションプロセッサ                                                                                       |    |

| A S     | 送信装置 S の出力部                                                                                         |    |

| A T     | 出力ドライバ、具体的には、レーザドライバ                                                                                |    |

| C D     | クロックおよびデータリカバリユニット                                                                                  |    |

| C E     | 受信インターフェースロジック L E のクロックモジュール                                                                       |    |

| C H 0 ± | 第 1 のデータラインまたは第 1 のチャネル                                                                             | 10 |

| C H 1 ± | 第 2 のデータラインまたは第 2 のチャネル                                                                             |    |

| C H 2 ± | 第 3 のデータラインまたは第 3 のチャネル                                                                             |    |

| C H 3 ± | 第 4 のデータラインまたは第 4 のチャネル                                                                             |    |

| C L K ± | クロックラインまたはクロックチャネル                                                                                  |    |

| C S     | 送信インターフェースロジック L S のクロックモジュール                                                                       |    |

| D D 0 ± | 第 1 のデータラインまたは第 1 のチャネル C H 0 ± 上の差動信号、具体的には、コモンモードベースのデータ信号                                        |    |

| D D 1 ± | 第 2 のデータラインまたは第 2 のチャネル C H 1 ± 上の差動信号、具体的には、コモンモードベースのデータ信号                                        |    |

| D D 2 ± | 第 3 のデータラインまたは第 3 のチャネル C H 2 ± 上の差動信号、具体的には、コモンモードベースのデータ信号                                        |    |

| D D 3 ± | 第 4 のデータラインまたは第 4 のチャネル C H 3 ± 上の差動信号、具体的には、コモンモードベースのデータ信号                                        |    |

| D F     | デフレーマ                                                                                               | 20 |

| D K     | デフレーマ D F の復号器、具体的には、6 b / 5 b 復号器ブロック                                                              |    |

| D M     | デマルチプレクサ                                                                                            |    |

| D S     | デシリアルライゼーション要素またはデシリアルライザ                                                                           |    |

| D U     | ディスプレイユニット                                                                                          |    |

| E E     | 受信装置 E の入力部                                                                                         |    |

| E S     | 送信装置 S の入力部                                                                                         |    |

| E V     | 入力増幅器、具体的には、トランスインピーダンス増幅器                                                                          |    |

| F D     | フォトダイオード                                                                                            |    |

| F I     | フィルタ、具体的には、データフィルタ、例えば、L P データフィルタ                                                                  |    |

| F R     | フレーマ                                                                                                | 30 |

| H S     | 高速                                                                                                  |    |

| H S D 0 | 第 1 のデータラインまたは第 1 のチャネル C H 0 ± 上のシングルエンド論理レベルベースのデータ信号                                             |    |

| H S D 1 | 第 2 のデータラインまたは第 2 のチャネル C H 1 ± 上のシングルエンド論理レベルベースのデータ信号                                             |    |

| H S D 2 | 第 3 のデータラインまたは第 3 のチャネル C H 2 ± 上のシングルエンド論理レベルベースのデータ信号                                             |    |

| H S D 3 | 第 4 のデータラインまたは第 4 のチャネル C H 3 ± 上のシングルエンド論理レベルベースのデータ信号                                             |    |

| I E     | データシンク関連の C S I および / または C S I - 2 および / または C S I - 3 および / または D S I および / または D S I - 2 インタフェース | 40 |

| I S     | データソース関連の C S I および / または C S I - 2 および / または C S I - 3 および / または D S I および / または D S I - 2 インタフェース |    |

| K A     | カメラ                                                                                                 |    |

| K O     | フレーマ F R の符号器、具体的には、5 b / 6 b 符号器ブロック                                                               |    |

| L A     | レーザ                                                                                                 |    |

| L E     | 受信インターフェースロジック                                                                                      |    |

| L P     | 低電力                                                                                                 |    |

| L S     | 送信インターフェースロジック                                                                                      |    |

| M U     | マルチプレクサ                                                                                             | 50 |

M U Z マルチプレクサ M U におけるさらなるまたは追加的なマルチプレクサ

O M 光学媒体、具体的には、光導波路、例えば、ガラス纖維および / またはプラスチック纖維

P S クロック発振器、具体的には、位相ロックループ、例えば、クロックマルチプライヤユニット

## S E シリアライゼーション要素またはシリアルライザ

S I 共通信号ストリーム

## TL クロックライン

【図 1 A】

【 図 1 B 】

### 【図1C】

**Fig. 1C**

### 【図2A】

【図2B】

【図3】

【図4A】

(従来技術)

【図4B】

(従来技術)

---

フロントページの続き

(72)発明者 ブロン, トーマス

ドイツ連邦共和国 80687 ミュンヘン エルゼンハイマーシュトラーセ 48 / デア・ツヴ

アイテン シリコン・ライン・ゲー・エム・ベー・ハーネ

(72)発明者 ズットトルブ, トーマス

ドイツ連邦共和国 80687 ミュンヘン エルゼンハイマーシュトラーセ 48 / デア・ツヴ

アイテン シリコン・ライン・ゲー・エム・ベー・ハーネ

(72)発明者 ヘルトケ, ホルガー

ドイツ連邦共和国 80995 ミュンヘン アム・ブリューテンアンガー 54ツェー

審査官 阿部 弘

(56)参考文献 國際公開第2008/126753 (WO, A1)

特開2008-160370 (JP, A)

米国特許出願公開第2009/0238576 (US, A1)

特開2006-033804 (JP, A)

特開2008-113321 (JP, A)

特開2010-050847 (JP, A)

特開2001-103028 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03M 9/00

H04L 7/00

H04L 7/033

H04L 25/02