(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7687768号**

**(P7687768)**

(45)発行日 令和7年6月3日(2025.6.3)

(24)登録日 令和7年5月26日(2025.5.26)

(51)国際特許分類

**G 0 6 F 12/00 (2006.01)**

F I

G 0 6 F 12/00 5 6 0 A

G 0 6 F 12/00 5 5 0 Z

請求項の数 26 外国語出願 (全32頁)

(21)出願番号 特願2020-150180(P2020-150180)

(22)出願日 令和2年9月7日(2020.9.7)

(65)公開番号 特開2021-111333(P2021-111333

A)

(43)公開日 令和3年8月2日(2021.8.2)

審査請求日 令和5年9月4日(2023.9.4)

(31)優先権主張番号 16/742,332

(32)優先日 令和2年1月14日(2020.1.14)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 591003943

インテル・コーポレーション

アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200

(74)代理人 110000877

弁理士法人 R Y U K A 国際特許事務所

(72)発明者 シェコウフェー カワミ

アメリカ合衆国 95054 カリフォルニア州・サンタクララ・ミッション カレッジ ブーレバード・2200 インテル・コーポレーション内

審査官 北村 学

最終頁に続く

(54)【発明の名称】 不揮発性メモリの自動インクリメント書き込みカウント

**(57)【特許請求の範囲】****【請求項1】**

データブロックをまとめて格納する複数の不揮発性(NV)メモリアレイであって、前記複数のNVメモリアレイのそれぞれが前記データブロックの一部を格納し、前記複数のNVメモリアレイのうちの1つのNVメモリアレイが前記データブロックの書き込みカウントをさらに格納する、複数のNVメモリアレイと、

前記データブロックを前記複数のNVメモリアレイに書き込むための書き込みコマンドを受信するコマンドバスインターフェースであって、前記書き込みコマンドの受信に応答して、前記複数のNVメモリアレイが、前記複数のNVメモリアレイにおける前記データブロックの内部的なブレイトリードを実行することに伴い、前記1つのNVメモリアレイは、前記書き込みカウントの前記内部的なブレイトリードを実行し、前記1つのNVメモリアレイの内部において前記書き込みカウントをインクリメントし、インクリメントした前記書き込みカウントを前記1つのNVメモリアレイに書き込む、コマンドバスインターフェースと

を備える不揮発性メモリデバイス。

**【請求項2】**

前記複数のNVメモリアレイは、別個のNVメモリチップを有する、請求項1に記載の不揮発性メモリデバイス。

**【請求項3】**

前記1つのNVメモリアレイはさらに、エラー検査訂正(ECC)データを格納する、

請求項 1 または 2 に記載の不揮発性メモリデバイス。

**【請求項 4】**

前記複数の NV メモリアレイは、書き込みカウント構成を格納するためのレジスタをさらに有し、前記 1 つの NV メモリアレイは、書き込みカウントモードのレジスタ構成を格納し、他の前記複数の NV メモリアレイは、前記書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する、請求項 1 から 3 のいずれか一項に記載の不揮発性メモリデバイス。

**【請求項 5】**

前記複数の NV メモリアレイは、自動インクリメントハードウェアをさらに有し、前記書き込みカウントモードは、前記自動インクリメントハードウェアを選択的に有効化または無効化する、請求項 4 に記載の不揮発性メモリデバイス。

10

**【請求項 6】**

前記複数の NV メモリアレイは、前記複数の NV メモリアレイにおける前記データブロックの前記プレライトリードを実行した後、前記複数の NV メモリアレイの前記プレライトリードにより読み出されたデータを、書き込まれるべきデータと比較し、前記書き込みコマンドに起因して異なる値を有するビットのみを書き込む、請求項 1 から 5 のいずれか一項に記載の不揮発性メモリデバイス。

**【請求項 7】**

前記 1 つの NV メモリアレイは、書き込み閾値を格納し、前記書き込みカウントが前記書き込み閾値に達したことに応答して、アラートを関連するコントローラへ渡す、請求項 1 から 6 のいずれか一項に記載の不揮発性メモリデバイス。

20

**【請求項 8】**

不揮発性メモリを有するシステムであって、

コントローラと、

不揮発性メモリデバイスと

を備え、

前記不揮発性メモリデバイスは、

データブロックをまとめて格納する複数の不揮発性 ( NV ) メモリアレイであって、前記複数の NV メモリアレイのそれが前記データブロックの一部を格納し、前記複数の NV メモリアレイのうちの 1 つの NV メモリアレイが前記データブロックの書き込みカウントをさらに格納する、複数の NV メモリアレイと、

30

前記データブロックを前記複数の NV メモリアレイに書き込むための書き込みコマンドを受信するコマンドバスインターフェースであって、前記書き込みコマンドの受信に応答して、前記複数の NV メモリアレイが、前記複数の NV メモリアレイにおける前記データブロックの内部的なプレライトリードを実行することに伴い、前記 1 つの NV メモリアレイは、前記書き込みカウントの前記内部的なプレライトリードを実行し、前記 1 つの NV メモリアレイの内部において前記書き込みカウントをインクリメントし、インクリメントした前記書き込みカウントを前記 1 つの NV メモリアレイに書き込む、コマンドバスインターフェースと

を有する、

40

システム。

**【請求項 9】**

前記複数の NV メモリアレイは、別個の NV メモリチップを含む、請求項 8 に記載のシステム。

**【請求項 10】**

前記 1 つの NV メモリアレイはさらに、エラー検査訂正 ( ECC ) データを格納する、請求項 8 または 9 に記載のシステム。

**【請求項 11】**

前記複数の NV メモリアレイは、書き込みカウント構成を格納するためのレジスタをさらに含み、前記 1 つの NV メモリアレイは、書き込みカウントモードのレジスタ構成を格

50

納し、他の前記複数のNVメモリアレイは、前記書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する、請求項8から10のいずれか一項に記載のシステム。

**【請求項12】**

前記複数のNVメモリアレイは、自動インクリメントハードウェアをさらに含み有し、前記書き込みカウントモードは、前記自動インクリメントハードウェアを選択的に有効化または無効化する、請求項11に記載のシステム。

**【請求項13】**

前記1つのNVメモリアレイは、書き込み閾値を格納し、前記書き込みカウントが前記書き込み閾値に達したことに応答して、アラートを前記コントローラへ渡す、請求項8から12のいずれか一項に記載のシステム。

10

**【請求項14】**

前記不揮発性メモリデバイスに結合されたホストプロセッサデバイス、

ホストプロセッサに通信可能に結合されたディスプレイ、

ホストプロセッサに通信可能に結合されたネットワークインターフェース、または、

前記システムに電力を供給するバッテリ

のうちの1または複数をさらに備える、請求項8から13のいずれか一項に記載のシステム。

**【請求項15】**

データを格納するための方法であって、

複数の不揮発性(NV)メモリアレイにおいてデータブロックをまとめて格納する段階であって、前記複数のNVメモリアレイのそれぞれが前記データブロックの一部を格納し、前記複数のNVメモリアレイのうちの1つのNVメモリアレイが前記データブロックの書き込みカウントをさらに格納する、段階と、

20

前記データブロックを前記複数のNVメモリアレイに書き込むための書き込みコマンドを受信する段階と

を備え、

前記書き込みコマンドの受信に応答して、前記複数のNVメモリアレイが、前記複数のNVメモリアレイにおける前記データブロックの内部的なプレライトリードを実行することに伴い、前記1つのNVメモリアレイは、前記書き込みカウントの前記内部的なプレライトリードを実行し、前記1つのNVメモリアレイの内部において前記書き込みカウントをインクリメントし、インクリメントした前記書き込みカウントを前記1つのNVメモリアレイに書き込む、

30

方法。

**【請求項16】**

前記複数のNVメモリアレイは、別個のNVメモリチップを含む、請求項15に記載の方法。

**【請求項17】**

前記1つのNVメモリアレイはさらに、エラー検査訂正(ECC)データを格納する、請求項15または16に記載の方法。

40

**【請求項18】**

前記複数のNVメモリアレイは、書き込みカウント構成を格納するレジスタをさらに含み、前記1つのNVメモリアレイは、書き込みカウントモードのレジスタ構成を格納し、他の前記複数のNVメモリアレイは、前記書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する、請求項15から17のいずれか一項に記載の方法。

**【請求項19】**

前記複数のNVメモリアレイは、自動インクリメントハードウェアをさらに含み、前記書き込みカウントモードは、前記自動インクリメントハードウェアを選択的に有効化または無効化する、請求項18に記載の方法。

**【請求項20】**

50

前記 1 つの N V メモリアレイはさらに、書き込み閾値を格納し、前記 1 つの N V メモリアレイは、前記書き込みカウントが前記書き込み閾値に達したことに応答して、アラートを関連するコントローラへ渡す、請求項 1 5 から 1 9 のいずれか一項に記載の方法。

#### 【請求項 2 1】

データを格納するための装置であって、複数の不揮発性 ( N V ) メモリアレイにおいてまとめてデータブロックを格納するための手段であって、前記複数の N V メモリアレイのそれぞれが前記データブロックの一部を格納し、前記複数の N V メモリアレイのうちの 1 つの N V メモリアレイが前記データブロックの書き込みカウントをさらに格納する、手段と、

前記データブロックを前記複数の N V メモリアレイに書き込むための書き込みコマンドを受信するための手段と、

前記書き込みコマンドの受信に応答して、前記複数の N V メモリアレイにおいて前記データブロックの内部的なプレライトリードを実行することに伴い、前記 1 つの N V メモリアレイにおいて、前記書き込みカウントの前記内部的なプレライトリードを実行し、前記 1 つの N V メモリアレイの内部において前記書き込みカウントをインクリメントし、およびインクリメントした前記書き込みカウントを前記 1 つの N V メモリアレイに書き込むための手段と

を備える装置。

#### 【請求項 2 2】

前記複数の N V メモリアレイは、別個の N V メモリチップを含む、請求項 2 1 に記載の装置。

#### 【請求項 2 3】

前記 1 つの N V メモリアレイはさらに、エラー検査訂正 ( E C C ) データを格納するための手段をさらに含む、請求項 2 1 または 2 2 に記載の装置。

#### 【請求項 2 4】

前記複数の N V メモリアレイは、書き込みカウント構成を格納するレジスタをさらに含み、前記 1 つの N V メモリアレイは、書き込みカウントモードのためのレジスタ構成を格納し、他の前記複数の N V メモリアレイは、前記書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する、請求項 2 1 から 2 3 のいずれか一項に記載の装置。

#### 【請求項 2 5】

前記複数の N V メモリアレイは、自動インクリメントハードウェアをさらに含み、前記書き込みカウントモードは、前記自動インクリメントハードウェアを選択的に有効化または無効化する、請求項 2 4 に記載の装置。

#### 【請求項 2 6】

前記 1 つの N V メモリアレイはさらに、書き込み閾値を格納し、前記 1 つの N V メモリアレイは、前記書き込みカウントが前記書き込み閾値に達したことに応答して、アラートを関連するコントローラへ渡す、請求項 2 1 から 2 3 のいずれか一項に記載の装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

説明は概して、不揮発性メモリデバイスに関し、より具体的な説明は、不揮発性メモリデバイス用のメタデータの追跡に関する。

##### 【背景技術】

##### 【0 0 0 2】

不揮発性 ( N V ) メモリデバイスは、書き込み耐久性が限られている。N V メモリは、デバイスへの電力が遮断された場合に状態が不確定であるメモリを指す。書き込み耐久性は、信頼性が無くなる前に当該媒体に書き込まれ得る回数を指す。加えて、当該媒体は、書き込みディスクライバを受ける。書き込みディスクライバとは、ターゲットメモリアドレスへのアクセスが繰り返されたことにより、隣接する位置のピクティムアドレスにおける値

10

20

30

40

50

に意図されていない変化がもたらされる状態である。

**【0003】**

書き込みの回数に関連する潜在的な問題があるので、システムは、どれくらいの頻度でデータのリフレッシュおよびデータの移動を行ってセルの耐久性および書き込みディスクを管理するかを決定するために、書き込みの回数を追跡する。書き込みの追跡に対する従来のアプローチは、ロック毎での書き込みの追跡である。データがロックに書き込まれるたびに、システムは、書き込みカウントにアクセスして書き込みカウントをインクリメントする。書き込みカウントが不揮発性媒体自体に格納されるシステムでは、アクセスには、ロックが書き込まれる前に、そのデータの読み取りが必要とされる。従来、媒体コントローラが、そのデータを読み取り、そのデータをインクリメントしてから、ユーザーデータと共に媒体へライトバックしている。このオペレーションにより、システムの有効書き込み帯域幅が低下する。

10

**【図面の簡単な説明】**

**【0004】**

以下の説明は、実装の例として与えられる例示を有する図についての議論を含む。図面は、例として理解されるべきであり、限定として理解されるべきではない。本明細書において用いられる場合、1または複数の例への言及は、本発明の少なくとも1つの実装に含まれる特定の特徴、構造または特性の説明と理解されるべきである。本明細書に現れる「一例において」または「代替的な例において」などの語句は、本発明の実装の例を提供し、必ずしも全てが同じ実装を指すわけではない。しかしながら、それらは、必ずしも相互に排他的であるわけでもない。

20

**【0005】**

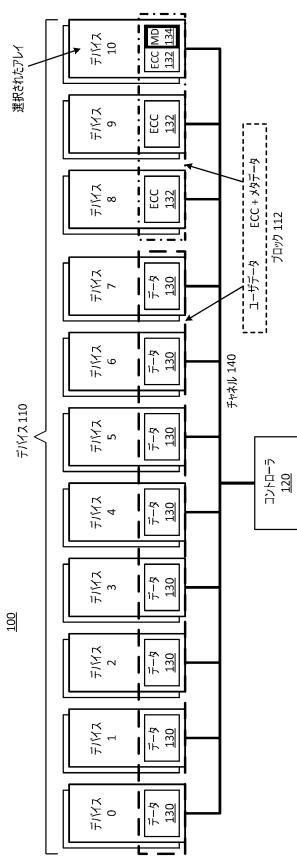

**【図1】**書き込みカウントを格納し、書き込みカウントに対して自動インクリメントを実行する選択されたメモリアレイを有するシステムの例のブロック図である。

**【0006】**

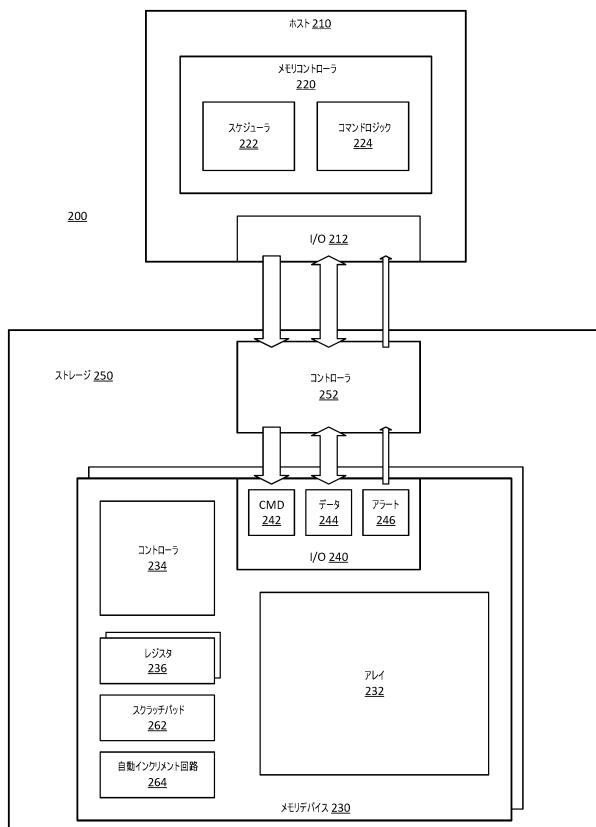

**【図2】**書き込みカウントメタデータに対して自動インクリメントを実行する選択されたメモリアレイを有するシステムの例のブロック図である。

30

**【0007】**

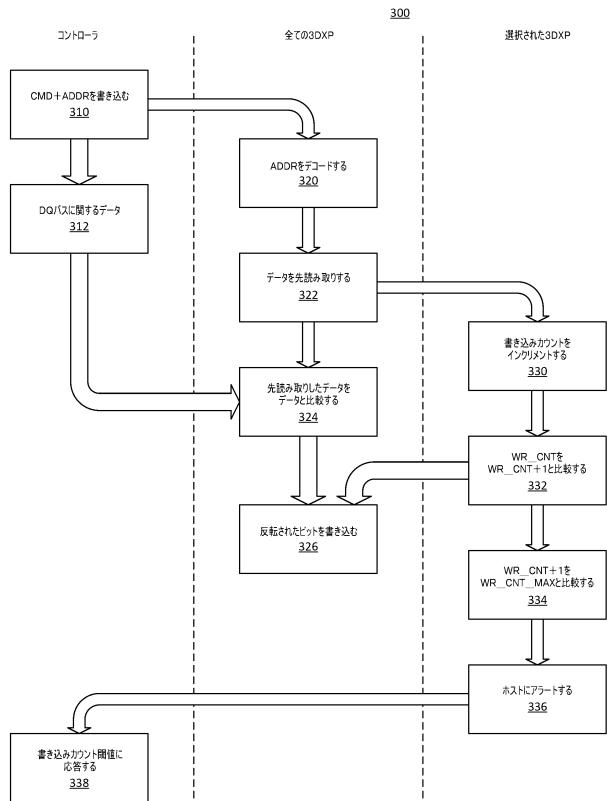

**【図3】**書き込みカウントメタデータに対して自動インクリメントを実行する実装のブロック図である。

**【0008】**

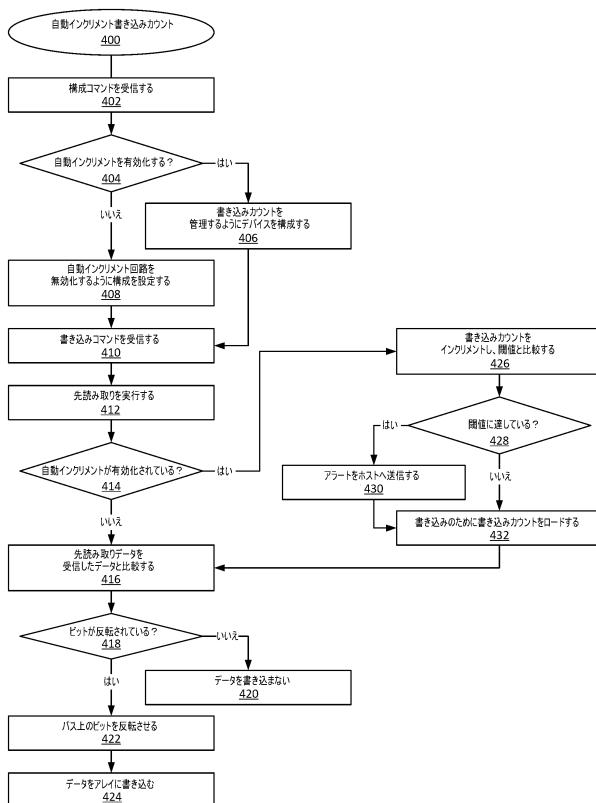

**【図4】**書き込みカウント自動インクリメントのための処理の例のフロー図である。

**【0009】**

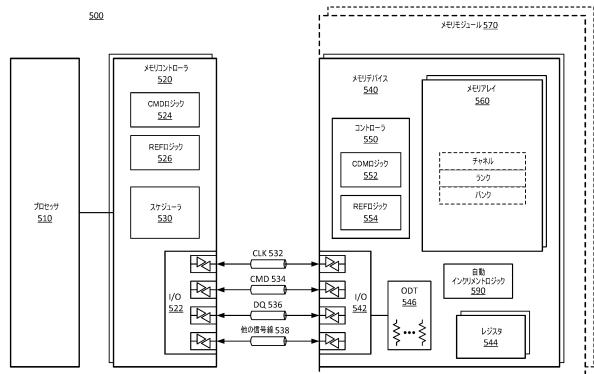

**【図5】**書き込みカウント自動インクリメントが実装され得るメモリサブシステムの例のブロック図である。

**【0010】**

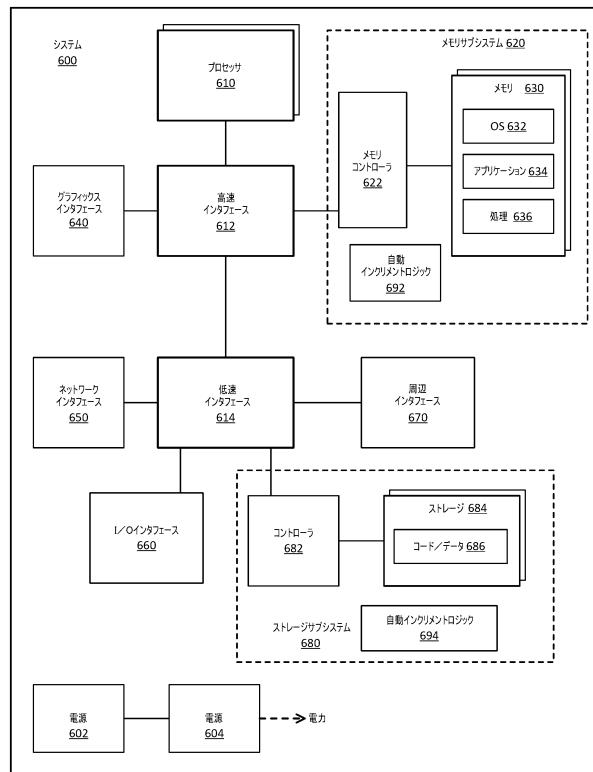

**【図6】**書き込みカウント自動インクリメントが実装され得るコンピューティングシステムの例のブロック図である。

40

**【0011】**

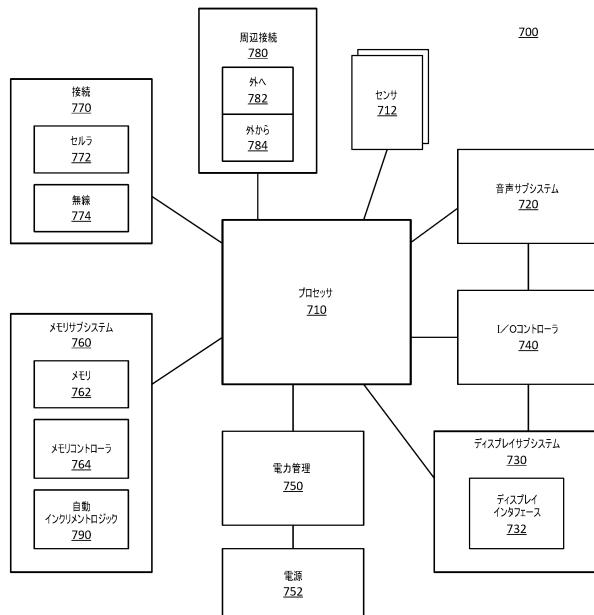

**【図7】**書き込みカウント自動インクリメントが実装され得るモバイルデバイスの例のブロック図である。

**【0012】**

特定の詳細および実装の説明を以下で行う。当該説明は、例のいくつかまたは全てと他の潜在的な実装を示し得る図の非限定的な説明を含む。

**【発明を実施するための形態】**

**【0013】**

本明細書において説明するように、システムは、複数のNVメモリアレイのうちの1つにメタデータを格納することにより、不揮発性(NV)メモリに対する書き込みの回数の追跡できる。一例において、NVメモリは、3次元クロスポイント(3DXP)記憶媒体を有するメモリデバイスである。複数のNVメモリアレイは、データブロックをまとめて

50

格納する。各アレイはデータブロックの一部を格納し、選択されたアレイが、当該データブロックのための書き込みカウントを格納する。システムは、どれくらいの頻度でデータのリフレッシュまたはデータの移動を行ってセルの耐久性と書き込みディスクストームを管理するかを決定するために、書き込みカウントを用い得る。

#### 【0014】

特定のNVメモリ技術の書き込み手順には、比較的長い時間が掛かり、多くの電力が用いられる。エネルギー使用量および書き込み遅延を管理するために、一例において、NVメモリは、書き込みのために変更されるビットのみを書き込む。NVメモリは、書き込みコマンドに応答して、読み取りオペレーションを内部的に発行できる。この内部的な読み取りは、「プレリード（事前読み取り）」または「プレライトリード（書き込み前の読み取り）」と称され得る。内部的な読み取りにより、メモリデバイスは、自身のメモリセルのコンテンツを読み取り、既存のデータを入力データと比較し、変更されているビットのみを書き込むことが可能になる。

10

#### 【0015】

書き込みカウントを格納する選択されたNVメモリアレイは、書き込みカウントを含むそのコンテンツの内部的な読み取りを実行する。選択されたNVメモリアレイは、コントローラへ書き込みカウントをインクリメントさせるために送信することなく、書き込みカウントを内部で自動インクリメントする。選択されたNVメモリアレイは、インクリメントされた書き込みカウントをそのビットセルへライトバックできる。一例において、選択されたNVメモリアレイは、他のNVメモリアレイに書き込まれるべきユーザーデータと共に、書き込みカウントをライトバックする。自動インクリメントにより、コントローラが書き込みカウントを読み取ってインクリメントする必要がなくなり得る。コントローラの関与がなくなり、自動インクリメントにより、NV媒体の書き込みサイクルごとに、コントローラによりNV媒体に対して発行される少なくとも読み取りのサイクルが節約できる。

20

#### 【0016】

一例において、書き込みカウントを格納する選択されたNVメモリアレイは、内部書き込みカウント閾値を含み得る。このNVメモリアレイが、書き込みカウントをインクリメントするとき、このNVメモリアレイは書き込みカウントを閾値と比較して、書き込みカウント閾値に達している場合は、アラートをコントローラへ送信するかまたは渡すことができる。

30

#### 【0017】

一例において、選択されたNVメモリアレイは、メモリデバイス内のモードの選択に応答して、自動インクリメントを実行する。モードは概して、構成設定に基づいて実行されるオペレーションを指し、異なるオペレーションが、異なる構成に基づく同じ状況に応答して行われる。故に、例えば、選択されたNVメモリアレイは、プレリードオペレーションと共に自動インクリメントを実行するように構成され得、他の複数のNVメモリアレイは、自動インクリメントはせずに、単にプレリードオペレーションを実行するように構成される。一例において、当該モードにより、各NVメモリアレイにおいて利用可能な自動インクリメントハードウェアが有効化される。

40

#### 【0018】

図1は、書き込みカウントを格納し、書き込みカウントに対して自動インクリメントを実行する選択されたメモリアレイを有するシステムの例のブロック図である。システム100は、メモリシステムまたはメモリデバイスを表す。システム100は、デバイス[0:10]として識別される複数のメモリデバイス110を含む。11個のデバイスを有するのの一例であり、他のシステムがより多いかまたはより少ないデバイスを有し得ることが理解されよう。図示される各デバイスは、1または複数のメモリデバイスを含み得る。

#### 【0019】

一例において、複数のデバイス110は、システム100の別個の複数のNVメモリアレイを表す。一例において、当該メモリアレイは、3D X P媒体を含み得る。一例におい

50

て、当該メモリアレイは、他のNV記憶媒体を含み得る。一例において、各デバイス110は、複数のアレイを含む。一例において、各デバイス110は、別個のNVメモリアレイを表す。一例において、各デバイス110は、別個のNVメモリチップまたはメモリダイを表す。システム100内のデバイス110の数は、システム100の記憶容量と、内部アーキテクチャと、他の要因とによって決まる。一例において、各デバイス110は、別個の媒体ダイを表す。一例において、各デバイス110は、別個の媒体デバイスを表す。

#### 【0020】

一例において、システム100は、NVデュアルインラインメモリモジュール(DIMM)などのストレージモジュールなどのNVストレージデバイスを表す。一例において、システム100は、ソリッドステートドライブ(SSD)などのデバイスであるか、または当該デバイスの一部である。一例において、コントローラ120は、システム100用の媒体コントローラを表す。媒体コントローラは、システム100の記憶媒体へのアクセスを制御するための制御デバイスを表す。システム100が統合されるホストシステムの視点から見ると、複数のデバイス110は、利用可能なストレージに見えるに過ぎない。媒体コントローラとしてのコントローラ120は、特定のデバイス\_データアドレスへのアクセス、内部コマンドおよびホストコマンドを実行するためのオペレーション\_タイミングの順守並びにデバイス110へのアクセスに対する他の管理を管理する。一例において、以下のとおりである。

#### 【0021】

システム100は、データ130を格納しているものとしてデバイス[0:7]を示す。データ130は、ユーザーデータ、または関連するホストにより作成されてシステム100に格納されるデータを表す。一例において、デバイス[8:9]は、データ130のエラー検査訂正(ECC)データを表すECC132を格納する。一例において、デバイス10は、ECC132およびメタデータ(MD)134を格納する。故に、デバイス10は、ECC132と共に用いるためのECCデータを格納し得るだけでなく、デバイス110へのアクセスの管理のための追加のメタデータを有し得る。一例において、追加のメタデータ134は、ブロック112に対する書き込みの回数を追跡するための書き込みカウントを含む。ブロック112は、データ130、ECC132およびMD134を含み得る。ブロック112から、複数のデバイス110がデータブロックをまとめて格納することが理解されよう。

#### 【0022】

チャネル140は、コントローラ120とデバイス110との間の通信チャネルを表す。一例において、チャネル140は、3DXPチャネルと称され得る。チャネル140により、コントローラ120は、デバイス110と通信することが可能になる。チャネル140は、制御信号線またはコマンド信号線およびデータ信号線を含み得る。

#### 【0023】

一例において、システム100がホストから書き込みオペレーションまたは書き込みコマンドを受信した場合、コントローラ120は、デバイス110に書き込みコマンドを実行させるためのコマンドまたは制御をシステム100内に生成してよい。コマンドは、アドレスと、書き込まれるデータとを含む。コントローラ120は、コマンドをデコードし、書き込まれるデータのアドレスとしてブロック112を識別する。一例において、コントローラ120は、ホストから受信するデータと共に書き込むためのECCデータを生成する。一例において、デバイス[0:7]は、データ130に書き込まれる複数バイトのデータを受信し、また、コントローラ120は、ECC132をデバイス[8:10]に提供する。一例において、コントローラ120は、書き込みカウントをデバイス10に提供しない。メタデータ134が書き込みカウント以外の情報を含む場合、コントローラ120は、そのようなメタデータをデバイス10に提供したであろう。

#### 【0024】

一例において、ブロック112は、複数のデバイス110にわたって書き込まれる、データ130により表されるコードワードを有するものとみなされ得る。一例において、デ

10

20

30

40

50

バイス 10 は、メタデータ内の書き込みカウントの追跡に特化した選択されたデバイスである。一例において、コントローラ 120 は、各デバイス 110 の位置を識別し、メタデータを追跡するための 1 つのデバイスを選択する。システム 100 は、メタデータ 134 を格納するための選択されたアレイとしてデバイス 10 を示す。一例において、コントローラ 120 は、各デバイス 110 に構成設定を提供し、この構成設定において、デバイス 110 が、書き込みカウントの自動インクリメントを実行するための選択されたアレイとして有効化される。故に、構成設定により、選択されたメモリアレイの自動インクリメントが選択的に有効化または無効化され得る。

#### 【 0 0 2 5 】

一例において、全てのコード書き込み、またはコードワードの書き込みについて、複数のデバイス 110 はまず、それらデバイスのそれぞれのデータコンテンツを読み取る。ブレイトリードの一環として、一例において、デバイス 10 は、書き込みカウントを読み取り、デバイス 10 へのライトバックのために当該書き込みカウントをインクリメントする。一例において、デバイス 10 は、書き込まれる他のデータと共に、インクリメントされた書き込みカウントをデータバス上に置く。10

#### 【 0 0 2 6 】

従来であれば、書き込みカウントを追跡するためのロジックは、コントローラ 120 に含まれるであろう。一例において、デバイス 10 は、書き込みカウントを追跡するためのロジックを含む。一例において、ロジックは、デバイス 10 が自動インクリメントモードに入っている場合に有効化される。一例において、コントローラ 120 は、デバイス 10 の自動インクリメントモードへの設定に関連して、書き込みカウント閾値（例えば、レジスタ内の値）を設定する。20

#### 【 0 0 2 7 】

一例においてブロック 112 のブロックサイズは、64 バイト、128 バイト、256 バイト、または 3D X P 媒体用のいくつかの他の数のバイトであり得る。NAND (not AND) フラッシュは通常、4K バイトまたは 2K バイトなどのより大きいブロックサイズを有する。ブロックの書き込みカウントの管理は、より小さいブロックサイズを有するシステムに対し、より高いプラスの性能上の影響を及ぼし得る。

#### 【 0 0 2 8 】

図 2 は、書き込みカウントメタデータに対して自動インクリメントを実行する選択されたメモリアレイを有するシステムのブロック図である。システム 200 は、図 1 のシステム 100 に係るシステムの例を提供する。ストレージ 250 は、システム 100 の例を表し得る。コントローラ 252 は、システム 100 のコントローラ 120 の例である。30

#### 【 0 0 2 9 】

システム 200 は、ストレージ 250 に結合された、メモリコントローラ 220 を有するホスト 210 を含む。ホスト 210 は、ストレージ 250 が結合されたコンピューティングプラットフォームを表す。例えば、ホスト 210 は、コンピュータまたは他のコンピューティングデバイスであり得るか、またはそれを含み得る。メモリコントローラ 220 は、メモリデバイス 230 へのアクセスを管理するためのコントローラを表す。一例において、メモリコントローラ 220 は、ホスト 210 のホストプロセッサ（特に示されない）の一部である。メモリコントローラ 220 は、代替的に、ストレージ 250 の接続に応じてストレージコントローラとみなされ得る。40

#### 【 0 0 3 0 】

一例において、メモリデバイス 230 の不揮発性メモリは、ペリフェラルコンポーネントインターフェクトエクスプレス (PCIe) バスなどのストレージバスに結合され得る。一例において、メモリデバイス 230 の不揮発性メモリは、不揮発性であるが、バイトアドレス指定可能かつランダムアクセス性もあり、ダブルデータレート (DDR) メモリバスなどのシステムメモリバスに結合され得る。ホスト 210 は、I/O (入力 / 出力) インタフェース 212 を含む。I/O 212 は、ストレージ 250 とインターフェースするためのハードウェアを表す。I/O 212 は、コマンドバスもしくはコマンドおよびア

10

20

30

40

50

ドレスバスならびにデータバスへのインターフェースを含み得る。一例において、インターフェースは、メモリデバイス230がアラートをホスト210へ送信するための信号線など、他の信号線を含む。

#### 【0031】

メモリデバイス230は、メモリデバイス用のI/Oを表すI/O240を有するように示される。コントローラ252は特にI/Oを含むように示されないが、コントローラ252は、コマンドを受信し、ホスト210とデータを交換し、かつ、メモリデバイス230をインターフェースするためのI/OハードウェアおよびI/Oファームウェアを含むことが理解されよう。I/O240は、コマンドバスまたはCAバスへのインターフェースを表すコマンド(CMD)242を含む。データ244は、データバスまたはDQバスへのインターフェースを表す。一例において、I/O240は、メモリデバイス230がアラートをホスト210へ送信するための1または複数の信号線へのインターフェースを表すアラート246を含む。例えば、メモリデバイス230が、一群のメモリデバイスのための書き込みカウントを管理するための選択されたデバイスである場合、アラート246により、選択されたデバイスは、書き込みカウントが閾値に達したことに応答してアラートを送信することが可能になる。

10

#### 【0032】

メモリコントローラ220は、ストレージ250に対する一連のコマンドのスケジューリングおよび送信を管理するためのスケジューラ222を含む。スケジューラ222は、コマンドの順序およびコマンドのタイミング要件を決定するためのロジックを含む。メモリコントローラ220は、どのコマンドをどの順序で送信するかについての決定を行う。スケジューラ222は、コマンドの順序を決定することで、タイミング要件への準拠を保証する。

20

#### 【0033】

一例において、ホスト210は、或るデータブロックについて、書き込み閾値に達していることを示すアラートをメモリデバイス230から受信する。一例において、アラートフラグに応答して、メモリコントローラ220は、メモリデバイス230の1または複数のレジスタを読み取ってアラートを識別し得る。アラートに応答して、一例において、メモリコントローラ220は、リフレッシュまたはデータの異なる記憶位置(例えば、ストレージ内の異なるアドレス)への移動等のオペレーションをトリガするためのコマンドを送信するかどうかを決定する。アラートに応答してオペレーションを実行することをメモリコントローラ220が決定した場合、スケジューラ222は、ストレージ250へ送信すべきコマンドをスケジューリングし得る。

30

#### 【0034】

メモリコントローラ220は、メモリデバイス230へ送信すべきコマンドを生成するためのコマンドロジック224を含む。コマンドは、書き込みコマンドまたは読み取コマンドを含み得る。メモリコントローラ220が、コマンドおよびアドレスバスとも称され得るコマンドバスに対して読み取りコマンドを送信し、遅延期間の後に、メモリデバイス230が、データバス上でデータを駆動する。一例において、コマンドロジック224は、リフレッシュコマンド、またはデータを異なる位置へ移動させるためのコマンドを送信し得る。

40

#### 【0035】

ストレージ250は、複数のメモリデバイス230を含む。メモリデバイス230は、不揮発性メモリセルまたはストレージセルのアレイを表すメモリアレイ232を含む。メモリセルは、1ビットのデータ、またはマルチレベルセル用の複数のビットを格納する。一例において、アレイ232は、メモリのバンクまたはメモリの他のサブセットとして分割される。一例において、メモリデバイス230は、1または複数のメモリデバイスがメモリのランクとして編成されるメモリデバイスのグループの一部である。メモリのランクは、チップ選択信号またはイネーブル信号を共有するが故に並列にアクセスされるメモリソースのグループである。

50

**【 0 0 3 6 】**

一例において、アレイ 2 3 2 は、不揮発性メモリセルを含む。不揮発性（N V）メモリは、メモリに対して電力が遮断された場合でも、自らの状態を維持する。揮発性メモリは、メモリに対して電力が遮断された場合、不確定な状態になる。一例において、アレイ 2 3 2 の N V 媒体は、3 D X P 媒体である。

**【 0 0 3 7 】**

システム 2 0 0 は、メモリまたはストレージモジュールを表すストレージ 2 5 0 用の媒体コントローラを表すコントローラ 2 5 2 を含む。一例において、コントローラ 2 5 2 は、ホスト 2 1 0 からコマンドおよびデータを受信し、メモリデバイスへ送信すべき内部コマンドを決定し、メモリデバイスは内部コマンドに応答することになる。また、コントローラ 2 5 2 は、データの特定のある部分を特定のメモリデバイス 2 3 0 へ送ることができる。また、システム 2 0 0 は、メモリデバイス 2 3 0 のコントローラ 2 3 4 を示す。コントローラ 2 3 4 は、コマンドを受信およびデコードするための、メモリデバイスにおけるロジックを表し、コマンドに応答する必要がある回路を駆動できる。10

**【 0 0 3 8 】**

メモリデバイス 2 3 0 は、メモリデバイス 2 3 0 のオペレーションに関連する構成情報または値を格納するための 1 または複数のレジスタまたは記憶位置を表すレジスタ 2 3 6 を含む。一例において、レジスタ 2 3 6 は、1 または複数のモードレジスタを含む。一例において、レジスタ 2 3 6 は、メモリデバイス 2 3 0 の書き込みカウント自動インクリメントモードを制御するための構成情報を含む。20

**【 0 0 3 9 】**

一例において、メモリデバイス 2 3 0 は、メモリデバイス 2 3 0 が内部オペレーション用に用いるための一時的な記憶位置を表すスクラッチパッド 2 6 2 を含む。一例において、メモリデバイス 2 3 0 は、書き込みコマンドに応答して、ブレライトリードオペレーションを実行する。ブレライトリードオペレーションは、アレイ 2 3 2 の或るアドレスの内容を読み取ることと、書き込まれるべきデータのバッファされたコピーとを比較することとを含み得る。書き込みバッファは、特に示されないが、アレイ 2 3 2 との間で交換されるデータのための一時的なバッファを提供する。一例において、当該バッファがアレイ 2 3 2 とデータバスとの間でデータを交換するためのデータ経路に接続しているという点において、当該バッファはデータバスへのインラインであるとみなされ得る。30

**【 0 0 4 0 】**

一例において、当該比較により、スクラッチパッド 2 6 2 に格納され得る結果が生成される。スクラッチパッド 2 6 2 は、コントローラ 2 5 2 へ送信されない内部オペレーション用のストレージを表す。自動インクリメント回路 2 6 4 は、値をインクリメントすることと、インクリメントした値をメモリアレイにライトバックされるべきユーザーデータおよび E C C データと結合し直すこととを実行するためのロジック回路など、自動インクリメントを有効化するためのハードウェアを表す。一例において、自動インクリメント回路 2 6 4 は、メモリデバイス 2 3 0 の構成に基づいて、動的に有効化および無効化され得る。すなわち、選択された書き込みカウントアレイとしてメモリデバイス 2 3 0 が構成される場合、自動インクリメント回路 2 6 4 は、書き込みカウントに対して自動インクリメントオペレーションを実行するよう有効化され得る。40

**【 0 0 4 1 】**

図 3 は、書き込みカウントメタデータに対して自動インクリメントを実行する実装のブロック図である。ダイアグラム 3 0 0 は、説明される不揮発性メモリシステムに係るシステムにより実装され得るフローを表す。

**【 0 0 4 2 】**

一例において、コントローラは媒体コントローラを表し、3 D X P は N V メモリデバイスを表す。中央の列は、全ての 3 D X P または全てのメモリアレイもしくはメモリデバイスにより実行されるオペレーションを表す。右の列は、選択された 3 D X P デバイスにより実行されるオペレーションを表す。50

**【 0 0 4 3 】**

コントローラは、書き込みコマンドおよび当該書き込みコマンドのためのアドレス（ADR）を生成する（ブロック310）。一例において、書き込みコマンドに応答して、全ての3DXPデバイスが当該コマンドのアドレスをデコードする（ブロック320）。当該コマンドを送信した後、コントローラは、適切な遅延の後に、DQバス上にデータを送信する（ブロック312）。当該遅延は、3DXP媒体について定義される書き込み遅延である。

**【 0 0 4 4 】**

一例において、当該コマンドをデコードしたことに応答して、全ての3DXPデバイスが、自身の現在のデータコンテンツをプレリードする（ブロック322）。これらの3DXPデバイスは、プレリードしたデータを、DQバス上で受信したデータと比較する（ブロック324）。

10

**【 0 0 4 5 】**

3DXPデバイスのうちの1つが、書き込みカウントを管理するための選択された3DXPデバイスとして選択されている。一例において、選択された3DXPデバイスは、自動インクリメントモードへ入るように構成される。そのようなモードは、一例において、レジスタまたは構成ビットを設定することにより構成され得る。例えば、構成フィールドまたは構成ビットは、選択されていない3DXPデバイスについて自動インクリメント=0、および選択されたデバイスについて自動インクリメント=1であり得る。

**【 0 0 4 6 】**

一例において、選択された3DXPデバイスは、書き込みカウントをインクリメントする（ブロック330）。一例において、選択された3DXPデバイスは、現在の書き込みカウント（WR\_CNT）を、インクリメントした書き込みカウント（WR\_CNT+1）と比較する（ブロック332）。一例において、選択された3DXPデバイスは、書き込みカウントに加え、ECCデータまたはユーザーデータを格納する。故に、選択された3DXPデバイスは、プレリードしたデータとDQバス上のデータとの比較を実行し得る。

20

**【 0 0 4 7 】**

一例において、選択された3DXPデバイスについて、自動インクリメント書き込みカウントモードが有効化される。これは、システムが、書き込みコマンドについてDQバスの特定のNバイト（例えば、2バイトまたは3バイト）を無視できることを意味する。故に、例えば、一例の複数の3DXPデバイスは、PRE\_RD[15:3]とDQ\_BUS[15:3]との比較をまとめて実行し得る。PRE\_RD[15:3]は、複数の3DXPデバイスのメモリアレイから読み取られた14バイトのデータ（選択された3DXPデバイスからのデータを含み得る）を表し、DQ\_BUS[15:3]は、ホストから受信された14バイトのデータを表す。DQバスの最後の3バイトは、無視され得る。選択された3DXPデバイスは、PRE\_RD[2:0]と（PRE\_RD[2:0]+1）との比較を実行し得る。PRE\_RD[2:0]は書き込みカウントメタデータを表し、（PRE\_RD[2:0]+1）はインクリメントされた書き込みカウントを表す。

30

**【 0 0 4 8 】**

一例において、3DXPデバイスは、書き込みコマンドに応答して変更されるデータのみを書き込む。一例において、ユーザーデータ、ECCデータまたは書き込みカウントメタデータの比較のいずれについても、3DXPデバイスは、データをバス上に戻す。例えば、3DXPデバイスは、データの比較結果を、反転されているビットについて比較すべく、書き込みバッファへ配置し得る。一例において、3DXPデバイスは、反転されているビットのみを書き込む（ブロック326）。

40

**【 0 0 4 9 】**

一例において、選択された3DXPデバイスは、インクリメントされた書き込みカウント（WR\_CNT+1）を閾値カウント（WR\_CNT\_MAX）と比較する（ブロック334）。一例において、閾値に達している場合、3DXPデバイスは、ホストにアラートする（ブロック336）。一例において、媒体コントローラは、構成レジスタ（モード

50

レジスタなど)により閾値または書き込みカウント限界を設定する。故に、カウントが閾値に達している場合、選択された 3 D X P デバイスは、フラグまたは他のアラートを設定できる。アラートに応答して、媒体コントローラは、書き込みカウントが閾値に達したことに応答するための適切な措置を講じることができる(ブロック 338)。

#### 【0050】

図 4 は、書き込みカウント自動インクリメントのための処理の例のフロー図である。自動インクリメント書き込みカウントのための処理 400 は、図 1 のシステム 100 または図 2 のシステム 200 に係るシステムの例により実行され得る。

#### 【0051】

一例において、402 で、3 D X P デバイスなどの不揮発性メモリデバイスが、ホストコントローラから構成コマンドを受信する。NV メモリデバイスが、書き込みカウントを格納するよう選択されたものである場合、構成コマンドは、自動インクリメントを実行するよう NV メモリデバイスを設定できる。

#### 【0052】

404 の YES 分岐で構成コマンドが自動インクリメントを有効化する場合、一例において、406 で、構成コマンドは、書き込みカウントを管理するよう、選択されたデバイスを構成する。404 の NO 分岐で構成コマンドが自動インクリメントを有効化しない場合、デバイスは、書き込みカウントを管理するよう選択されない。デバイスが書き込みカウントメタデータを管理しない場合、一例において、408 で、当該構成は、デバイス上の自動インクリメント回路を無効化する。つまり、全てのデバイスが自動インクリメント回路を含み得、1 つの選択されたデバイスが、有効化された機能を有し、他のデバイスは、無効化された機能を有する。

#### 【0053】

メモリデバイスについていずれの構成が設定されても、メモリデバイスは、アクセスコマンド受信するよう準備できる。410 で、書き込みコマンドを受信したことに応答して、または当該コマンドの受信に応答して、一例において、412 で、メモリデバイスは、書き込みコマンドに関連付けられたアドレスにそれらメモリデバイスが既に格納したデータのプレリードを実行する。

#### 【0054】

複数のメモリデバイスの場合、書き込みカウントを管理するよう選択された 1 つのデバイスが存在する。故に、標準的なオペレーションについての典型的な事例は、1 つのデバイスが、書き込みカウントを管理するための他のオペレーションを有することになる。一例において、自動インクリメントが有効化されていない、414 の NO 分岐の場合、416において、メモリデバイスは、プレリードしたデータを、書き込みコマンドのために受信したデータと比較する。

#### 【0055】

一例において、メモリデバイスは、現在のデータコンテンツ(プレリードしたデータ)と書き込まれるデータとの比較を実行する。なぜなら、メモリデバイスは、書き込みコマンドに起因して反転されることになるデルタまたはビットのみを書き込むからである。故に、一例において、複数のメモリデバイスは各々、書き込まれるべきデータの各ビットについて、ビットが反転されているかどうかを判断する。418 の NO 分岐でビットが反転されていない場合、一例において、420 で、デバイスは、変更されていないビットの書き込みを実行しない。

#### 【0056】

418 の YES 分岐でビットが反転されている場合、一例において、422 で、メモリデバイスは、データバス上のビットを反転する。故に、デバイスは、メモリアレイへの書き込みのために、比較の結果をデータバス上に配置できる。一例において、プレリードされたデータは、データバス上に配置されず、比較のためにのみ用いられ、この場合、書き込まれるべき結果が、データバス上に配置される。ひとたびデータバス上にデータが設定されると、424 で、メモリデバイスは、当該データをアレイに書き込む。

10

20

30

40

50

**【 0 0 5 7 】**

書き込みカウントを格納しているデバイスについては、414のY E S分岐で、自動インクリメントが有効化される。一例において、426で、選択されたデバイスは、書き込みカウントをインクリメントし、インクリメントした書き込みカウントを閾値と比較する。当該閾値は、書き込みディスターープのリスクを示すための閾値、ライフサイクルの終了を示すための閾値またはいくつかの他の閾値であり得る。一例において、当該デバイスは、インクリメントした値を複数の異なる閾値と比較する。

**【 0 0 5 8 】**

428のY E S分岐で1または複数の閾値に達している場合、一例において、430で、デバイスは、アラートをホストへ送信する。一例において、複数の閾値が比較される場合、デバイスは、異なる閾値について異なるアラートを送信できる。一例において、デバイスは、単一のアラートを送信し、ホストは、アラート源を決定するためにデバイスにクエリする。閾値に達しているか否かにかかわらず、一例において、書き込みカウントをインクリメントした後、432で、デバイスは、アレイへのライトバックのために、インクリメントした書き込みカウントをロードできる。選択されたデバイスにとっては、反転されているビットについての比較のために、書き込みカウントは、プレリードされたデータとみなされ得、インクリメントされた書き込みカウントは、D Q バスからの書き込みデータに代わるものである。処理が416へ戻される。

10

**【 0 0 5 9 】**

図5は、書き込みカウント自動インクリメントが実装され得るメモリサブシステムの例のブロック図である。システム500は、コンピューティングデバイス内のメモリサブシステムのプロセッサおよび要素を含む。システム500は、図1のシステム100または図2のシステム200に係るシステムの例を提供する。

20

**【 0 0 6 0 】**

一例において、システム500は、メモリデバイス540内の自動インクリメントロジック590を含む。一例において、メモリデバイス540は、本明細書における任意の例に係る、メモリブロックについてのブロック書き込みカウントを管理するための、メモリモジュール570の複数のメモリデバイスの中から選択され得る。一例において、メモリデバイス540は、書き込みカウントメタデータをメモリアレイ560に格納する。一例において、レジスタ544は、メモリデバイス540が、書き込みカウントを管理するための選択されたメモリデバイスであるかどうかを判断するために書き込まれるフィールドを含む。一例において、自動インクリメントロジック590は、書き込みカウントの自動インクリメントを実行するためのハードウェアを含む。

30

**【 0 0 6 1 】**

プロセッサ510は、オペレーティングシステム(O S)およびアプリケーションを実行し得るコンピューティングプラットフォームの処理ユニットを表し、当該処理ユニットは、メモリのホストまたはユーザと総称され得る。O Sおよびアプリケーションは、メモリアクセスをもたらすオペレーションを実行する。プロセッサ510は、1または複数の別個のプロセッサを含み得る。別個のプロセッサの各々は、シングル処理ユニット、マルチコア処理ユニットまたはそれらの組み合わせを含み得る。処理ユニットは、C P U(中央処理装置)などのプライマリプロセッサ、G P U(グラフィックス処理ユニット)などの周辺プロセッサまたはその組み合わせであり得る。メモリアクセスは、ネットワークコントローラまたはハードディスクコントローラなどのデバイスによっても開始され得る。そのようなデバイスは、バス(例えば、P C Iエクスプレス)を介して、いくつかのシステム内のプロセッサと統合され得るか、もしくはプロセッサに取り付けられ得るか、またはそれらの組み合わせであり得る。システム500は、S C(システムオンチップ)として実装され得るか、またはスタンドアロンコンポーネントと共に実装され得る。

40

**【 0 0 6 2 】**

一例において、メモリデバイスへの言及は、デバイスに対して電力が遮断された場合でも状態が確定している不揮発性メモリデバイスを指し得る。一例において、不揮発性メモ

50

リデバイスは、NAND技術またはNOR技術などのブロックアドレス指定可能メモリデバイスである。故に、メモリデバイスは、3次元クロスポイントメモリデバイス、他のバイトアドレス指定可能不揮発性メモリデバイスなど、将来世代の不揮発性デバイスも含み得る。メモリデバイスは、メモリセルの抵抗状態またはメモリセルの位相に基づいてデータを格納する、不揮発性のバイトアドレス指定可能媒体を含み得る。一例において、メモリデバイスは、カルコゲナイト相変化材料（例えば、カルコゲナイトガラス）を用い得る。一例において、メモリデバイスは、多閾値レベルNANDフラッシュメモリ、NORフラッシュメモリ、シングルもしくはマルチレベル相変化メモリ（PCM）もしくはスイッチ付き相変化メモリ（PCM）、抵抗メモリ、ナノワイヤメモリ、強誘電体トランジスタランダムアクセスメモリ（FeTRAM）、メモリスタ技術を組み込んだ磁気抵抗ランダムアクセスメモリ（MRAM）もしくは回転転送トルク（STT）MRAMもしくは上述のもののいずれかの組み合わせまたは他のメモリであり得るか、またはそれらを含み得る。

#### 【0063】

メモリコントローラ520は、システム500用の1または複数のメモリコントローラ回路またはデバイスを表す。メモリコントローラ520は、プロセッサ510によるオペレーションの実行に応答してメモリアクセスコマンドを生成する制御ロジックを表す。メモリコントローラ520は、1または複数のメモリデバイス540にアクセスする。メモリデバイス540は、上記で言及されたいずれかのものに係るDRAMデバイスであり得る。一例において、メモリデバイス540は、異なるチャネルとして編成および管理される。各チャネルは、複数のメモリデバイスに並列に結合するバスおよび信号線に結合する。各チャネルは、独立して動作可能である。故に、各チャネルは、独立してアクセスおよび制御され、タイミングと、データ転送と、コマンドおよびアドレスの交換と、他のオペレーションとは、各チャネルについて別個である。結合は、電気的結合、通信的結合、物理的結合またはこれらの組み合わせを指し得る。物理的結合は、直接接触を含み得る。電気的結合は、コンポーネント間に電気が流れることを可能にするか、もしくはコンポーネント間のシグナリングを可能にするか、またはそれらの両方を可能にするインターフェースまたは相互接続を含む。通信的結合は、有線または無線を含む、コンポーネントがデータを交換することを可能にする接続を含む。

#### 【0064】

一例において、各チャネルの設定は、別個のモードレジスタまたは他のレジスタ設定により制御される。一例において、各メモリコントローラ520が別個のメモリチャネルを管理するが、システム500は、単一のコントローラにより管理される複数のチャネルまたは単一のチャネル上の複数のコントローラを有するように構成され得る。一例において、メモリコントローラ520は、同じダイ上に実装されるか、またはプロセッサと同じパッケージ空間に実装されるロジックなど、ホストプロセッサまたはホストプロセッサデバイス510の一部である。

#### 【0065】

メモリコントローラ520は、上記で言及したメモリチャネルなどのメモリバスに結合するI/Oインターフェースロジック522を含む。I/Oインターフェースロジック522（およびメモリデバイス540のI/Oインターフェースロジック542）は、ピン、パッド、コネクタ、信号線、トレースもしくはワイヤ、もしくは当該デバイスに接続する他のハードウェア、またはこれらの組み合わせを含み得る。I/Oインターフェースロジック522は、ハードウェアインターフェースを含み得る。示されるように、I/Oインターフェースロジック522は少なくとも、信号線用のドライバ／トランシーバを含む。一般的に、集積回路インターフェース内のワイヤは、パッド、ピンまたはコネクタと結合して、デバイス間の信号線もしくはトレースまたは他のワイヤとインターフェースする。I/Oインターフェースロジック522は、デバイス間の信号線上で信号を交換するためのドライバ、受信機、トランシーバもしくは終端もしくは他の回路または回路の組み合わせを含み得る。信号の交換は、伝送または受信のうちの少なくとも1つを含む。メモリコントローラ520からメモリデバイス540のI/O542へI/O522を結合するように示されるが、

10

20

30

40

50

メモリデバイス 540 のグループが並列にアクセスされるシステム 500 の実装では、複数のメモリデバイスがメモリコントローラ 520 の同じインターフェースへの I/O インタフェースを含み得ることが理解されよう。システム 500 の実装は、1 または複数のメモリモジュール 570 を含む。I/O 542 は、メモリデバイス自体上のインターフェースハードウェアに加え、メモリモジュールのインターフェースハードウェアを含み得る。他のメモリコントローラ 520 は、他のメモリデバイス 540 への別個のインターフェースを含む。

#### 【0066】

メモリコントローラ 520 とメモリデバイス 540 との間のバスは、メモリコントローラ 520 をメモリデバイス 540 へ結合する複数の信号線として実装され得る。バスは通常、少なくとも、クロック (CLK) 532、コマンド / アドレス (CMD) 534 および書き込みデータ (DQ) および読み取りデータ (DQ) 536 ならびにゼロまたはそれより多くの他の信号線 538 を含み得る。一例において、メモリコントローラ 520 とメモリとの間のバスまたは接続は、メモリバスと称され得る。一例において、メモリバスは、マルチドロップバスである。CMD 用の信号線は、「C/A バス」(もしくは ADD/CMD バス、またはコマンド (C または CMD) およびアドレス (A または ADD) 情報の転送を示すいくつかの他の記号表示) と称され得、書き込みおよび読み取り DQ 用の信号線は、「データバス」と称され得る。一例において、独立のチャネルは、異なるクロック信号、C/A バス、データバスおよび他の信号線を有する。故に、システム 500 は、独立のインターフェース経路が別個のバスとみなされ得るという意味において、複数の「バス」を有しているとみなされ得る。明示的に示される線に加え、バスは、ストローブシグナル・リング線、アラート線、補助線もしくは他の信号線またはそれらの組み合わせのうちの少なくとも 1 つを含み得ることが理解されよう。シリアルバス技術は、メモリコントローラ 520 とメモリデバイス 540 との間の接続のために用いられ得ることも理解されよう。シリアルバス技術の一例が、8B10B エンコードおよび各方向における信号の単一の差動ペアを介した埋め込みクロックでの高速データの伝送である。一例において、CMD 534 は、複数のメモリデバイスと並列に共有される信号線を表す。一例において、複数のメモリデバイスが CMD 534 のエンコードコマンド信号線を共有し、各々が、個々のメモリデバイスを選択するための別個のチップ選択 (CS\_n) 信号線を有する。

#### 【0067】

システム 500 の例において、メモリコントローラ 520 とメモリデバイス 540 との間のバスは、補助コマンドバス CMD 534 と書き込みデータおよび読み取りデータを伝達するための補助バス DQ 536 とを含むことが理解されよう。一例において、データバスは、読み取りデータおよび書き込み / コマンドデータ用の双方向線を含み得る。別の例において、補助バス DQ 536 は、ホストからメモリへの書き込みおよびデータのための一方向書き込み信号線を含み得ると共に、メモリからホストへの読み取りデータのための一方向線を含み得る。選ばれたメモリ技術およびシステム設計に従って、他の信号 538 は、ストローブ線 DQ などのバスまたはサブバスに付随し得る。システム 500 の設計、またはある設計が複数の実装をサポートする場合の実装に基づいて、データバスは、メモリデバイス 540 毎に多少の帯域幅を有し得る。例えば、データバスは、x4 インタフェース、x8 インタフェース、x16 インタフェースまたは他のインターフェースのいずれかを有するメモリデバイスをサポートできる。規定「xW」の W は、メモリデバイス 540 のインターフェースサイズまたはインターフェースの幅を指す整数であり、メモリコントローラ 520 とデータを交換するための信号線の数を表す。メモリデバイスのインターフェースサイズは、いくつのメモリデバイスがシステム 500 内のチャネル毎に同時に用いられ得るか、または同じ信号線へ並列に結合され得るかに関する制御要因である。一例において、高帯域幅メモリデバイス、ワイドインターフェースデバイスもしくは積層メモリ構成またはそれらの組み合わせは、x128 インタフェース、x256 インタフェース、x512 インタフェース、x1024 インタフェースまたは他のデータバスインターフェース幅などのより幅広いインターフェースを有効化できる。

#### 【0068】

10

20

30

40

50

一例において、メモリデバイス 540 およびメモリコントローラ 520 は、バーストで、または一連の連續するデータ転送で、データバスを介してデータを交換する。バーストは、バス周波数に関連する転送サイクルの数に対応する。一例において、転送サイクルは、同じクロックまたはストローブ信号エッジ（例えば、立ち上がりエッジ）で生じる転送の全クロックサイクルであり得る。一例において、システムクロックのサイクルを参照する全クロックサイクルは、複数の単位間隔（UI）へ分割される。各UIは、転送サイクルである。例えば、ダブルデータレート転送は、クロック信号の両方のエッジ（例えば、立ち上がりおよび立ち下がり）でトリガする。バーストは、構成された数のUIにわたって続き得る。これは、レジスタに格納される構成またはオンザフライでトリガされる構成であり得る。例えば、一連の8個の連續する転送期間は、バースト長8（BL8）とみなされ得、各メモリデバイス 540 は、各UIでデータを転送できる。故に、BL8で動作する×8メモリデバイスは、54ビットのデータを転送できる（8本のデータ信号線×バーストを介して線毎に転送される8データビット）。この単純な例は、例示に過ぎず、限定的なものではないことが理解されよう。

#### 【0069】

メモリデバイス 540 は、システム 500 用のメモリリソースを表す。一例において、各メモリデバイス 540 は、別個のメモリダイである。一例において、各メモリデバイス 540 は、デバイスまたはダイ毎に複数の（例えば2個の）チャネルを有するインタフェースであり得る。各メモリデバイス 540 は、デバイスの実装により決定される帯域幅（例えば、×16もしくは×8またはいくつかの他のインタフェース帯域幅）を有するI/Oインタフェースロジック 542 を含む。I/Oインタフェースロジック 542 により、メモリデバイスは、メモリコントローラ 520 とインタフェースすることが可能になる。I/Oインタフェースロジック 542 は、ハードウェアインタフェースを含み得、メモリコントローラのI/O522に応じ得るが、メモリデバイス端においてである。一例において、複数のメモリデバイス 540 は、同じコマンドおよびデータバスへ並列に接続される。別の例において、複数のメモリデバイス 540 は、同じコマンドバスへ並列に接続され、異なるデータバスに接続される。例えば、システム 500 は、並列に結合された複数のメモリデバイス 540 を用いて構成され得る。各メモリデバイスは、コマンドに応答し、各内部のメモリリソース 560 にアクセスする。書き込みオペレーションの場合、個々のメモリデバイス 540 は、データワード全体のうちのある部分を書き込むことができ、読み取りオペレーションの場合、個々のメモリデバイス 540 は、データワード全体のある部分をフェッチできる。ワードの残りのビットは、他のメモリデバイスにより並列に提供または受信される。

#### 【0070】

一例において、メモリデバイス 540 は、コンピューティングデバイスのマザーボードまたはホストシステムプラットフォーム（例えば、プロセッサ 510 が配置されるPCB（プリント回路基板））上に直接配置される。一例において、メモリデバイス 540 は、メモリモジュール 570 へ編成され得る。一例において、メモリモジュール 570 は、デュアルINLINEメモリモジュール（DIMM）を表す。一例において、メモリモジュール 570 は、アクセスまたは制御回路のうちの少なくとも一部分を共有するための複数のメモリデバイスの他の編成を表す。当該回路は、ホストシステムプラットフォームとは別個の回路、別個のデバイスまたは別個の基板であり得る。メモリモジュール 570 は、複数のメモリデバイス 540 を含み得ると共に、それらに配置された含まれているメモリデバイスへの複数の別個のチャネルのためのサポートを含み得る。別の例において、メモリデバイス 540 は、例えばマルチチップモジュール（MCM）、パッケージオンパッケージ、スルーシリコンピア（TSV）もしくは他の技術またはそれらの組み合わせなどの技術により、メモリコントローラ 520 として同じパッケージへ組み込まれ得る。同様に、一例において、複数のメモリデバイス 540 は、メモリモジュール 570 へ組み込まれ得る。それら自体が、メモリコントローラ 520 と同じパッケージへ組み込まれ得る。これらの実装および他の実装の場合、メモリコントローラ 520 はホストプロセッサ 510 の

一部であり得ることが理解されよう。

#### 【0071】

メモリデバイス540は各々、1または複数のメモリアレイ560を含む。メモリアレイ560は、アドレス指定可能メモリの位置またはデータの記憶位置を表す。通常、メモリアレイ560は、データの行として管理され、ワード線(行)およびビット線(行内の個々のビット)の制御を介してアクセスされる。メモリアレイ560は、メモリの別個のチャネル、ランク、バンクおよびパーティションとして編成され得る。チャネルは、メモリデバイス540内の記憶位置への独立の制御経路を指し得る。ランクは、並列に並んだ複数のメモリデバイスにわたる共通の位置(例えば、異なるデバイス内の同じ行アドレス)を指し得る。バンクは、メモリデバイス540内のメモリ位置のサブアレイを指し得る。一例において、メモリのバンクは、サブバンク用の共有回路(例えば、ドライバ、信号線、制御ロジック)のうちの少なくとも一部分を有するサブバンクへ分割される。これにより、別個のアドレス指定およびアクセスが可能になる。チャネル、ランク、バンク、サブバンク、バンクグループ、またはメモリ位置の他の編成、および当該編成の組み合わせは、それらの物理リソースへの応用において重複し得ることが理解されよう。例えば、同じ物理メモリ位置は、ランクに属すこともあり得る特定のバンクとしての特定のチャネルを介してアクセスされ得る。故に、メモリリソースの編成は、排他的ではなく、包括的に理解されよう。

10

#### 【0072】

一例において、メモリデバイス540は、1または複数のレジスタ544を含む。レジスタ544は、メモリデバイスのオペレーション用の構成または設定を提供する1または複数のストレージデバイスまたは記憶位置を表す。一例において、レジスタ544は、制御オペレーションまたは管理オペレの一部としてメモリコントローラ520によりアクセスされるデータを格納するためのメモリデバイス540の記憶位置を提供できる。一例において、レジスタ544は、1または複数のモードレジスタを含む。一例において、レジスタ544は、1または複数の多目的レジスタを含む。レジスタ544内の位置の構成により、メモリデバイス540は、異なる「モード」で動作するように構成され得る。コマンド情報により、モードに基づいて、メモリデバイス540内の異なるオペレーションがトリガされ得る。加えて、または代替的に、異なるモードにより、モードに応じて、アドレス情報または他の信号線から異なるオペレーションもトリガされ得る。レジスタ544の設定は、I/O設定の構成(例えば、タイミング、終端またはODT(オンダイ終端)546、ドライバ構成または他のI/O設定)を示し得る。

20

#### 【0073】

一例において、メモリデバイス540は、I/O542に関連付けられたインターフェースハードウェアの一部としてのODT546を含む。ODT546は、上述のように構成され得ると共に、指定された信号線へのインターフェースに適用されるインピーダンスの設定を提供し得る。一例において、ODT546は、DQ信号線に適用される。一例において、ODT546は、コマンド信号線に適用される。一例において、ODT546は、アドレス信号線に適用される。一例において、ODT546は、前述のものの任意の組み合わせに適用され得る。ODT設定は、メモリデバイスがアクセスオペレーションの選択されたターゲットであるか、または非ターゲットデバイスであるかに基づいて変更され得る。ODT546設定は、終端線上のシグナリングのタイミングおよび反映に影響を及ぼし得る。ODT546に対する慎重な制御により、適用されるインピーダンスおよびロードの一一致度が向上した、より高速なオペレーションが可能になり得る。ODT546は、I/Oインターフェース542、522(例えば、DQ線用のODTまたはCA線用のODT)の特定の信号線に適用され得るが、必ずしも全ての信号線に適用されるわけではない。

30

#### 【0074】

メモリデバイス540は、メモリデバイス内の内部オペレーションを制御するためのメモリデバイス内の制御ロジックを表すコントローラ550を含む。例えば、コントローラ550は、メモリコントローラ520により送信されるコマンドをデコードすると共に、

40

50

コマンドを実行したは満足させるための内部オペレーションを生成する。コントローラ 550 は、内部コントローラと称され得、ホストのメモリコントローラ 520 とは別個のものである。コントローラ 550 は、どのモードが選択されているかをレジスタ 544 に基づいて決定でき、メモリリソース 560 へのアクセスのためのオペレーションまたは他のオペレーションの内部での実行を、選択されたモードに基づいて構成できる。コントローラ 550 は、メモリデバイス 540 内のビットのルーティングを制御するための制御信号を生成して、選択されたモード用の適切なインターフェースを提供し、コマンドを適切なメモリ位置またはアドレスへ送る。コントローラ 550 は、コマンド信号線およびアドレス信号線上で受信されるコマンドエンコードをデコードできるコマンドロジック 552 を含む。故に、コマンドロジック 552 は、コマンドデコーダであり得るか、またはコマンドデコーダを含み得る。コマンドロジック 552 を用いることで、メモリデバイスは、コマンドを識別でき、要求されたコマンドを実行するための内部オペレーションを生成できる。

#### 【0075】

メモリコントローラ 520 を再び参照すると、メモリコントローラ 520 は、メモリデバイス 540 へ送信すべきコマンドを生成するためのロジックまたは回路を表すコマンド (CMD) ロジック 524 を含む。コマンドの生成は、スケジューリング前のコマンド、またはキューに入れられたコマンドの送信の準備を整えることを指し得る。概して、メモリサブシステム内のシグナリングは、メモリデバイスがコマンドを実行すべき 1 または複数のメモリ位置を指示または選択するためのコマンド内またはコマンドに付随するアドレス情報を含む。メモリデバイス 540 のトランザクションのスケジューリングに応答して、メモリコントローラ 520 は、メモリデバイス 540 にコマンドを実行させるための I/O 522 を介してコマンドを発行できる。一例において、メモリデバイス 540 のコントローラ 550 は、メモリコントローラ 520 から I/O 542 を介して受信したコマンドおよびアドレス情報を受信およびデコードする。受信したコマンドおよびアドレス情報に基づいて、コントローラ 550 は、メモリデバイス 540 内のロジックおよび回路のオペレーションのタイミングを制御することでコマンドを実行できる。コントローラ 550 は、タイミング要件およびシグナリング要件など、メモリデバイス 540 内の規格または仕様への準拠を担う。メモリコントローラ 520 は、アクセスのスケジューリングおよび制御により、規格または仕様への準拠を実装できる。

#### 【0076】

メモリコントローラ 520 は、メモリデバイス 540 へ送信すべきトランザクションを生成および命令するためのロジックまたは回路を表すスケジューラ 530 を含む。1つの観点から、メモリコントローラ 520 の主な機能はメモリデバイス 540 へのメモリアクセスおよび他のトランザクションをスケジューリングすることと言える。そのようなスケジューリングは、プロセッサ 510 によるデータの要求を実装するために、かつ、( 例えば、リフレッシュに関連するコマンドの利用などで ) データの完全性を維持するためにトランザクション自体を生成することを含み得る。トランザクションは、1 または複数のコマンドを含み得るので、クロックサイクルまたは単位間隔などの 1 または複数のタイミングサイクルでのコマンドもしくはデータまたはそれらの両方の転送をもたらし得る。トランザクションは、読み取りもしくは書き込みもしくは関連するコマンドまたはそれらの組み合わせなどのアクセスのためのものであり得る。他のトランザクションは、構成、設定、データ完全性についてのメモリ管理コマンド、もしくは他のコマンドまたはそれらの組み合わせを含み得る。

#### 【0077】

メモリコントローラ 520 は通常、トランザクションの選択および順序付けを可能にしてシステム 500 の性能を向上させるためのスケジューラ 530 などのロジックを含む。故に、メモリコントローラ 520 は、未処理のトランザクションのうちのどれがどの順序でメモリデバイス 540 へ送信されるべきかを選択できる。これは通常、単純な先入れ先出しアルゴリズムよりもはるかに複雑なロジックを用いて実現される。メモリコントローラ 520 は、メモリデバイス 540 へ送信すべきトランザクションを生成するためのロジックを含む。このロジックは、データの完全性を維持するためのトランザクションの構成、設定、データ完全性についてのメモリ管理コマンド、もしくは他のコマンドまたはそれらの組み合わせを含み得る。

10

20

30

40

50

ラ 5 2 0 は、メモリデバイス 5 4 0 へのトランザクションの伝送を管理すると共に、トランザクションに関連するタイミングを管理する。一例において、トランザクションには決定的なタイミングがある。当該タイミングは、メモリコントローラ 5 2 0 により管理され得ると共に、ストランザクションをスケジューラ 5 3 0 とどのようにスケジューリングするかの決定において用いられ得る。

#### 【 0 0 7 8 】

一例において、メモリコントローラ 5 2 0 は、リフレッシュ (REF) ロジック 5 2 6 を含む。リフレッシュロジック 5 2 6 は、メモリリソースをリフレッシュして決定的な状態を保持するために用いられ得る。揮発性メモリリソースは、状態を維持するために規則的にリフレッシュされる必要があるが、不揮発性メモリリソースは、読み取り / 書き込みディスターブを回避するためにリフレッシュされる必要があり得る。一例において、リフレッシュロジック 5 2 6 は、リフレッシュの位置と、実行すべきリフレッシュのタイプとを示す。リフレッシュロジック 5 2 6 は、メモリデバイス 5 4 0 内でのセルフリフレッシュをトリガできるか、もしくはリフレッシュコマンドを送信することにより外部リフレッシュ (自動リフレッシュコマンドと称され得る) を実行できるか、またはそれらの組み合わせを行うことができる。一例において、メモリデバイス 5 4 0 内のコントローラ 5 5 0 は、メモリデバイス 5 4 0 内でリフレッシュを適用するためのリフレッシュロジック 5 5 4 を含む。リフレッシュロジック 5 5 4 は、内部オペレーションを生成して、内部で、またはメモリコントローラ 5 2 0 から受信する外部リフレッシュに従って、のいずれかでリフレッシュを実行する。

10

#### 【 0 0 7 9 】

図 6 は、書き込みカウント自動インクリメントが実装され得るコンピューティングシステムの例のブロック図である。システム 6 0 0 は、本明細書における任意の例に係るコンピューティングデバイスを表し、ラップトップコンピュータ、デスクトップコンピュータ、タブレットコンピュータ、サーバ、ゲーム制御システムもしくはエンタテインメント制御システム、組み込みコンピューティングデバイスまたは他の電子デバイスであり得る。システム 6 0 0 は、図 1 のシステム 1 0 0 または図 2 のシステム 2 0 0 に係るシステムの例を提供する。

20

#### 【 0 0 8 0 】

一例において、システム 6 0 0 は、メモリサブシステム 6 2 0 内の自動インクリメントロジック 6 9 2 またはストレージサブシステム 6 8 0 内の自動インクリメントロジック 6 9 4 を含むか、またはそれらの両方を含む。一例において、メモリ 6 3 0 の 1 つの NV メモリデバイスもしくは NV メモリアレイまたはストレージ 6 8 4 の 1 つの NV メモリデバイスが複数のデバイスの中から選択され、本明細書における任意の例に係るメモリロックのブロック書き込みカウントを管理し得る。一例において、選択された NV メモリデバイスまたは NV メモリアレイは、書き込みカウントメタデータを格納する。一例において、選択されたデバイスは、書き込みカウントを管理するように構成された構成モードに基づいて選択される。一例において、自動インクリメントロジック 6 9 2 または自動インクリメントロジック 6 9 4 は、書き込みカウントの自動インクリメントを実行するためのハードウェアを含む。

30

#### 【 0 0 8 1 】

システム 6 0 0 は、プロセッサ 6 1 0 を含む。プロセッサ 6 1 0 は、システム 6 0 0 のために命令の処理または実行を提供するための任意のタイプのマイクロプロセッサ、中央処理装置 (CPU)、グラフィックス処理ユニット (GPU)、処理コアもしくは他の処理ハードウェアまたはそれらの組み合わせを含み得る。プロセッサ 6 1 0 は、システム 6 0 0 のオペレーション全体を制御し、1 または複数のプログラム可能な汎用または特定用途向けマイクロプロセッサ、デジタル信号プロセッサ (DSP)、プログラム可能コントローラ、特定用途向け集積回路 (ASIC)、プログラマブルロジックデバイス (PLD) またはそのようなデバイスの組み合わせであり得るか、またはそれらを含み得る。

40

#### 【 0 0 8 2 】

50

一例において、システム 600 は、プロセッサ 610 に結合されたインターフェース 612 を含む。インターフェース 612 は、メモリサブシステム 620 またはグラフィックインターフェースコンポーネント 640 など、より高帯域幅の接続を必要とする、システムコンポーネント用のより高速なインターフェースまたは高スループットインターフェースを表し得る。インターフェース 612 は、スタンドアロンコンポーネントであり得るか、またはプロセッサダイに統合され得るインターフェース回路を表す。インターフェース 612 は、回路としてプロセッサダイ上に統合され得るか、またはコンポーネントとしてシステムオンチップに統合され得る。存在する場合、グラフィックスインターフェース 640 は、システム 600 のユーザに視覚表示を提供するためのグラフィックコンポーネントにインターフェースする。グラフィックスインターフェース 640 は、スタンドアロンコンポーネントであり得るか、またはプロセッサダイもしくはシステムオンチップに統合され得る。一例において、グラフィックスインターフェース 640 は、ユーザに出力を提供する高精細度 (H D) ディスプレイまたは超高精細度 (U H D) ディスプレイを駆動できる。一例において、ディスプレイは、タッチスクリーンディスプレイを含み得る。一例において、グラフィックスインターフェース 640 は、メモリ 630 に格納されたデータに基づいて、もしくはプロセッサ 610 により実行されたオペレーションに基づいて、またはそれらの両方にに基づいて表示を生成する。

#### 【 0083 】

メモリサブシステム 620 は、システム 600 のメインメモリを表し、プロセッサ 610 により実行されるコードまたはルーチンの実行に用いられるデータ値のための記憶領域を提供する。メモリサブシステム 620 は、リードオンリメモリ (R O M)、フラッシュメモリ、D R A Mなどの1または複数の種類のランダムアクセスメモリ (R A M)、3 D X P (3次元クロスポイント) もしくは他のメモリデバイスまたはそのようなデバイスの組み合わせなど、1または複数のメモリデバイス 630 を含み得る。メモリ 630 は、とりわけ、システム 600 内での命令の実行用のソフトウェアプラットフォームを提供するためのオペレーティングシステム (O S) 632 を格納およびホストする。加えて、アプリケーション 634 は、メモリ 630 から O S 632 のソフトウェアプラットフォーム上で実行され得る。アプリケーション 634 は、プログラムを表す。当該プログラムは、1または複数の機能の実行をするためのそれらの独自の動作ロジックを有する。処理 636 は、O S 632 もしくは1または複数のアプリケーション 634 またはそれらの組み合わせに補助機能を提供するエージェントまたはルーチンを表す。O S 632、アプリケーション 634 および処理 636 は、システム 600 用の機能を提供するためのソフトウェアロジックを提供する。一例において、メモリサブシステム 620 は、コマンドを生成してメモリ 630 へ発行するメモリコントローラであるメモリコントローラ 622 を含む。メモリコントローラ 622 は、プロセッサ 610 の物理的部分またはインターフェース 612 の物理的部分であり得ることが理解されよう。例えば、メモリコントローラ 622 は、例えばプロセッサダイまたはシステムオンチップに統合されるなど、プロセッサ 610 と共に回路に統合される統合メモリコントローラであり得る。

#### 【 0084 】

具体的には示されていないが、システム 600 は、メモリバス、グラフィックバス、インターフェースバスまたは他のものなど、デバイス間の1または複数のバスまたはバスシステムを含み得ることが理解されよう。バスまたは他の信号線は、コンポーネントを互いに通信可能にまたは電気的に結合できるか、またはコンポーネントを通信可能にかつ電気的に結合できる。バスは、物理通信線、ポイントツーポイント接続、ブリッジ、アダプタ、コントローラもしくは他の回路またはそれらの組み合わせを含み得る。バスは、例えば、システムバス、ペリフェラルコンポーネント相互接続 (P C I) バス、ハイパートランSPORT アーキテクチャバスもしくは業界標準アーキテクチャ (I S A) バス、スマートコンピュータシステムインターフェース (S C S I) バス、ユニバーサルシリアルバス (U S B) もしくは他のバスのうちの1または複数またはそれらの組み合わせを含み得る。

#### 【 0085 】

10

20

30

40

50

一例において、システム 600 は、インターフェース 612 に結合され得るインターフェース 614 を含む。インターフェース 614 は、インターフェース 612 よりも低速なインターフェースであり得る。一例において、インターフェース 614 は、スタンドアロンコンポーネントおよび集積回路を含み得るインターフェース回路を表す。一例において、複数のユーザインターフェースコンポーネントもしくはペリフェラルコンポーネントまたはそれらの両方がインターフェース 614 に結合する。ネットワークインターフェース 650 は、1 または複数のネットワークを介してリモートデバイス（例えば、サーバまたは他のコンピューティングデバイス）と通信する機能をシステム 600 に提供する。ネットワークインターフェース 650 は、イーサネット（登録商標）アダプタ、無線相互接続コンポーネント、セルラネットワーク相互接続コンポーネント、USB（ユニバーサルシリアルバス）または他の有線もしくは無線規格ベースインターフェースもしくはプロプライエタリインターフェースを含み得る。ネットワークインターフェース 650 は、リモートデバイスとデータを交換できる。当該交換は、メモリに格納されたデータの送信またはメモリに格納されたデータの受信を含み得る。

#### 【0086】

一例において、システム 600 は、1 または複数の入力 / 出力（I/O）インターフェース 660 を含む。I/Oインターフェース 660 は、1 または複数のインターフェースコンポーネントを含み得る。当該インターフェースコンポーネントを通じて、ユーザは、システム 600 とインタラクトする（例えば、音声、英数字、触覚 / タッチまたは他のインターフェース）。周辺インターフェース 670 は、具体的には上述されていない任意のハードウェアインターフェースを含み得る。周辺は概して、システム 600 へ従属的に接続するデバイスを指す。従属的な接続は、システム 600 がソフトウェアプラットフォームもしくはハードウェアプラットフォームを提供する接続であるか、または、当該プラットフォーム上でオペレーションが実行され、当該プラットフォームを用いてユーザがインタラクトする接続である。

#### 【0087】

一例において、システム 600 は、データを不揮発性方式で格納するためのストレージサブシステム 680 を含む。一例において、特定のシステム実装では、ストレージ 680 の少なくとも特定のコンポーネントがメモリサブシステム 620 のコンポーネントと重複し得る。ストレージサブシステム 680 は、ストレージデバイス 684 を含む。ストレージデバイス 684 は、1 または複数の磁気ディスク、ソリッドステートディスク、3DXP ディスクもしくは光ベースディスクまたはそれらの組み合わせなど、大量のデータを不揮発性方式で格納するための任意の従来の媒体であり得るか、または当該媒体を含み得る。ストレージ 684 は、コードまたは命令およびデータ 686 を永続的な状態で保持する（すなわち、システム 600 への電力が遮断されても値が保持される）。ストレージ 684 は一般的に「メモリ」であるとみなされ得るが、メモリ 630 は通常、命令をプロセッサ 610 に提供するための実行メモリまたは動作メモリである。ストレージ 684 は不揮発性であるが、メモリ 630 は揮発性メモリを含み得る（すなわち、システム 600 への電力が遮断された場合、データの値または状態は不確定になる）。一例において、ストレージサブシステム 680 は、ストレージ 684 とインターフェースするためのコントローラ 682 を含む。一例において、コントローラ 682 は、インターフェース 614 またはプロセッサ 610 の物理的部分であるか、またはプロセッサ 610 およびインターフェース 614 の両方に回路またはロジックを含み得る。

#### 【0088】

電源 602 は、システム 600 のコンポーネントに電力を提供する。より具体的には、電源 602 は通常、システム 600 内の 1 または複数の電源 604 とインターフェースして、システム 600 のコンポーネントに電力を提供する。一例において、電源 604 は、壁のコンセントへ差し込むための AC - DC（交流 - 直流）アダプタを含む。そのような AC 電源は、再生可能エネルギー（例えば、太陽光発電）電源 602 であり得る。一例において、電源 602 は、外部 AC - DC 変換器などの DC 電源を含む。一例において、電源

602または電源604は、充電磁場への近接を介して充電するための無線充電ハードウェアを含む。一例において、電源602は、内部バッテリまたは燃料電池電源を含み得る。

#### 【0089】

図7は、書き込みカウント自動インクリメントが実装され得るモバイルデバイスの例のブロック図である。システム700は、コンピューティングタブレット、携帯電話もしくはスマートフォン、ウェアラブルコンピューティングデバイスもしくは他のモバイルデバイスまたは組み込みコンピューティングデバイスなどのモバイルコンピューティングデバイスを表す。これらのコンポーネントのうちの特定のものが一般的に示されているが、そのようなデバイスの全てのコンポーネントがシステム700内に示されているわけではないことが理解されよう。システム700は、図1のシステム100または図2のシステム200に係るシステムの例を提供する。

10

#### 【0090】

一例において、システム700は、メモリサブシステム760内の自動インクリメントロジック790を含む。一例において、メモリ762の1つのNVメモリデバイスまたはNVメモリアレイが、本明細書における任意の例に係る、メモリロックのブロック書き込みカウントを管理するための複数のデバイスの中から選択され得る。一例において、選択されたNVメモリデバイスまたはNVメモリアレイは、書き込みカウントメタデータを格納する。一例において、選択されたデバイスは、書き込みカウントを管理するように構成された構成モードに基づいて選択されている。一例において、自動インクリメントロジック790は、書き込みカウントの自動インクリメントを実行するためのハードウェアを含む。

20

#### 【0091】

システム700は、システム700の主な処理オペレーションを実行するプロセッサ710を含む。プロセッサ710は、マイクロプロセッサ、アプリケーションプロセッサ、マイクロコントローラ、プログラマブルロジックデバイスまたは他の処理手段などの1または複数の物理デバイスを含み得る。プロセッサ710により実行される処理オペレーションは、アプリケーションおよびデバイス機能が実行されるオペレーティングプラットフォームまたはオペレーティングシステムの実行を含む。処理オペレーションは、人間のユーザもしくは他のデバイスとのI/O(入力/出力)に関連するオペレーション、電力管理に関連するオペレーション、別のデバイスへのシステム700の接続に関連するオペレーションまたはそれらの組み合わせを含む。処理オペレーションは、音声I/O、表示I/Oもしくは他のインターフェースまたはそれらの組み合わせに関連するオペレーションも含み得る。プロセッサ710は、メモリに格納されたデータを実行できる。プロセッサ710は、メモリに格納されたデータを書き込むことができるか、または編集できる。

30

#### 【0092】

一例において、システム700は、1または複数のセンサ712を含む。センサ712は、外部センサへの埋め込みセンサもしくはインターフェースまたはそれらの組み合わせを表す。センサ712により、システム700は、システム700が実装される環境またはデバイスの1または複数の条件を監視または検出することが可能になる。センサ712は、環境センサ(温度センサ、動き検出器、光検出器、カメラ、化学センサ(例えば、一酸化炭素センサ、二酸化炭素センサもしくは他の化学センサ)など)、圧力センサ、加速度計、ジャイロスコープ、医療センサもしくは生理機能センサ(例えば、バイオセンサ、心拍数モニタもしくは生理学的な属性を検出するための他のセンサ)もしくは他のセンサまたはそれらの組み合わせを含み得る。センサ712は、指紋認識システム、顔検出もしくは認識システムまたはユーザーの特徴を検出または認識する他のシステムなどの生体認証システム用のセンサも含み得る。センサ712は、幅広く理解されるべきであり、システム700と共に実装され得る多くの異なるタイプのセンサに対する限定として理解されるべきではない。一例において、1または複数のセンサ712は、プロセッサ710に統合されたフロントエンド回路を介して、プロセッサ710に結合する。一例において、1または複数のセンサ712は、システム700の別のコンポーネントを介して、プロセッサ7

40

50

10に結合する。

#### 【0093】

一例において、システム700は、ハードウェア（例えば、音声ハードウェアおよび音声回路）と、コンピューティングデバイスへの音声機能の提供に関連するソフトウェア（例えば、ドライバ、コーデック）コンポーネントとを表す音声サブシステム720を含む。音声機能は、スピーカ出力またはヘッドフォン出力およびマイク入力を含み得る。そのような機能のためのデバイスは、システム700へ統合され得るか、またはシステム700に接続され得る。一例において、ユーザは、プロセッサ710により受信および処理される音声コマンドを提供することにより、システム700とインタラクトする。

#### 【0094】

ディスプレイサブシステム730は、ユーザに表示するための視覚表示を提供するハードウェア（例えば、ディスプレイデバイス）コンポーネントおよびソフトウェアコンポーネント（例えば、ドライバ）を表す。一例において、ディスプレイは、ユーザがコンピューティングデバイスとインタラクトするための触覚コンポーネントまたはタッチスクリーン要素を含む。ディスプレイサブシステム730は、ユーザに表示を提供するために用いられる特定のスクリーンまたはハードウェアデバイスを含むディスプレイインターフェース732を含む。一例において、ディスプレイインターフェース732は、表示に関連する少なくともいくつかの処理を実行するための、プロセッサ710（グラフィックスプロセッサなど）とは別個のロジックを含む。一例において、ディスプレイサブシステム730は、ユーザへの出力および入力の両方を提供するタッチスクリーンデバイスを含む。一例において、ディスプレイサブシステム730は、ユーザに出力を提供する高精細度（HD）ディスプレイまたは超高精細度（UHD）ディスプレイを含む。一例において、ディスプレイサブシステムは、タッチスクリーンディスプレイを含むか、またはタッチスクリーンディスプレイを駆動する。一例において、ディスプレイサブシステム730は、メモリに格納されたデータに基づいて、もしくはプロセッサ710により実行されるオペレーションに基づいて、またはそれらの両方にに基づいて表示情報を生成する。

#### 【0095】

I/Oコントローラ740は、ユーザとのインタラクションに関連するハードウェアデバイスおよびソフトウェアコンポーネントを表す。I/Oコントローラ740は、音声サブシステム720もしくはディスプレイサブシステム730またはそれらの両方の一部であるハードウェアを管理するように動作し得る。加えて、I/Oコントローラ740は、システム700に接続する追加のデバイスのための接続ポイントを示す。当該接続ポイントを通じて、ユーザは、システムとインタラクトし得る。例えば、システム700に取り付けられ得るデバイスは、マイクデバイス、スピーカシステムもしくはステレオシステム、ビデオシステムもしくは他のディスプレイデバイス、キーボードデバイスもしくはキーパッドデバイス、ボタン/スイッチ、もしくは、カードリーダなどの特定の応用品と共に用いるための他のI/Oデバイス、または他のデバイスを含み得る。

#### 【0096】

上述のように、I/Oコントローラ740は、音声サブシステム720もしくはディスプレイサブシステム730またはそれらの両方とインタラクトできる。例えば、マイクまたは他の音声デバイスを通じた入力により、システム700の1または複数のアプリケーションまたは機能についての入力またはコマンドが提供され得る。加えて、音声出力は、ディスプレイ出力の代わりに、またはディスプレイ出力に加えて提供され得る。別の例において、ディスプレイサブシステムがタッチスクリーンを含む場合、ディスプレイデバイスは、少なくとも部分的にI/Oコントローラ740により管理され得る入力デバイスとしても機能する。I/Oコントローラ740により管理されるI/O機能を提供するための追加のボタンまたはスイッチもシステム700上に存在し得る。

#### 【0097】

一例において、I/Oコントローラ740は、加速度計、カメラ、光センサもしくは他の環境センサ、ジャイロスコープ、全地球測位システム（GPS）もしくはシステム700

10

20

30

40

50

0に含まれ得る他のハードウェアまたはセンサ712などのデバイスを管理する。入力は、直接的なユーザインタラクションの一部であり得るだけでなく、そのオペレーション（ノイズのフィルタリング、輝度検出のための表示の調節、カメラ用のフラッシュの適用または他の特徴など）に影響を及ぼすシステムに環境入力を提供することであり得る。

#### 【0098】

一例において、システム700は、バッテリの電力使用量と、バッテリの充電と省電力オペレーションに関連する機能とを管理する電力管理750を含む。電力管理750は、システム700のコンポーネントに電力を提供する電源752からの電力を管理する。一例において、電源752は、壁のコンセントへ差し込むためのAC-DC（交流-直流）アダプタを含む。そのようなAC電源は、再生可能エネルギー（例えば、太陽光発電、動きベース電力）であり得る。一例において、電源752は、外部AC-DC変換器などのDC電源により提供され得るDC電力のみを含む。一例において、電源752は、充電磁场への近接を介して充電するための無線充電ハードウェアを含む。一例において、電源752は、内部バッテリまたは燃料電池電源を含み得る。

10

#### 【0099】

メモリサブシステム760は、情報をシステム700に格納するためのメモリデバイス762を含む。メモリサブシステム760は、不揮発性（メモリデバイスへの電力が遮断された場合に状態が変わらない）メモリデバイスもしくは揮発性（メモリデバイスへの電力が遮断された場合に状態が不確定になる）メモリデバイスまたはそれらの組み合わせを含み得る。メモリ760は、アプリケーションデータ、ユーザーデータ、音楽、写真、文書または他のデータだけでなく、システム700のアプリケーションおよび機能の実行に関連するシステムデータ（長期間のものであるかまたは一時的なものであるかを問わない）を格納できる。一例において、メモリサブシステム760は、メモリコントローラ764（システム700のコントロールの一部ともみなされ得ると共に、プロセッサ710の一部と潜在的にみなされ得る）を含む。メモリコントローラ764は、コマンドを生成および発行してメモリデバイス762へのアクセスを制御するスケジューラを含む。

20

#### 【0100】

接続770は、ハードウェアデバイス（例えば、無線コネクタもしくは有線コネクタおよび通信ハードウェアまたは有線ハードウェアと無線ハードウェアとの組み合わせ）およびシステム700が外部デバイスと通信することを可能にするためのソフトウェアコンポーネント（例えば、ドライバ、プロトコルスタック）を含む。外部デバイスは、他のコンピューティングデバイス、無線アクセスポイントまたは基地局などの別個のデバイス、および、ヘッドセット、プリンタまたは他のデバイスなどの周辺機器であり得る。一例において、システム700は、メモリへの格納のために、またはディスプレイデバイスでの表示のために、外部デバイスとデータを交換する。交換されるデータは、データの読み取り、書き込みまたは編集のためにメモリに格納されるデータまたはメモリに既に格納されているデータを含み得る。

30

#### 【0101】

接続770は、複数の異なるタイプの接続を含み得る。一般化するために、システム700は、セルラ接続772および無線接続774と共に示される。セルラ接続772は概して、例えばGSM（登録商標）（グローバルシステムフォー・モバイルコミュニケーションズ）を介して提供されるなど無線キャリアにより提供されるセルラネットワーク接続もしくはその変形規格もしくは派生規格、もしくはCDMA（符号分割多重アクセス）もしくはその変形規格もしくは派生規格、TDM（時分割多重化）もしくはその変形規格もしくは派生規格、LTE（「4G」、「5G」とも称されるロングタームエボリューション）、または他のセルラサービス規格を指す。無線接続774は、セルラではない無線接続を指し、パーソナルエリアネットワーク（Bluetooth（登録商標）など）、ローカルエリアネットワーク（Wi-Fi（登録商標）など）もしくはワイドエリアネットワーク（WiMAXなど）もしくは他の無線通信またはそれらの組み合わせを含み得る。無線通信は、非固体媒体を通じた変調済み電磁放射線の使用を通じてデータを転送することを

40

50

指す。有線通信は、固体通信媒体によって生じる。

#### 【0102】

周辺接続780は、ハードウェアインターフェースおよびコネクタならびに周辺接続を行うためのソフトウェアコンポーネント（例えば、ドライバ、プロトコルスタック）を含む。システム700は、他のコンピューティングデバイスへの（「外への」782）周辺デバイスおよびシステム700へ（「外から」784）接続される周辺デバイスの両方であり得ることが理解されよう。システム700は一般的に、システム700上のコンテンツの管理（例えば、ダウンロード、アップロード、変更、同期）などの目的で他のコンピューティングデバイスに接続する「ドッキング」コネクタを有する。加えて、ドッキングコネクタにより、例えばオーディオビジュアルシステムまたは他のシステムに出力されるコンテンツをシステム700が制御することを可能にする特定の周辺機器にシステム700が接続することが可能になり得る。

#### 【0103】

プロプライエタリドッキングコネクタまたは他のプロプライエタリ接続ハードウェアに加え、システム700は、一般的なコネクタまたは規格ベースのコネクタを介して周辺接続780を行い得る。一般的なタイプは、ユニバーサルシリアルバス（USB）コネクタ（多数の異なるハードウェアインターフェースのいずれかを含み得る）、MinidisplayPort（MDP）、高精細度マルチメディアインターフェース（HDMI（登録商標））を含むDisplayPortまたは他のタイプを含み得る。

#### 【0104】

概して、本明細書における説明に関し、一例において、不揮発性メモリデバイスは、データブロックをまとめて格納するための複数の不揮発性（NV）メモリアレイであって、各アレイがデータブロックのある部分を格納し、NVメモリアレイのうちの1つがデータブロックの書き込みカウントを格納する、複数のNVメモリアレイと、データブロックをNVメモリアレイに書き込むための書き込みコマンドを受信するためのコマンドバスインターフェースであって、書き込みコマンドの受信に応答して、NVメモリアレイは、NVメモリアレイへのデータブロックの内部先読み書きを実行し、1つのNVメモリアレイは、書き込みカウントの先読み書きを実行し、1つのNVメモリアレイの内部の書き込みカウントをインクリメントし、インクリメントした書き込みカウントを1つのNVメモリアレイに書き込む、コマンドバスインターフェースとを備える。

#### 【0105】

一例において、NVメモリアレイは、別個のNVメモリチップを有する。一例において、1つのNVメモリアレイはさらに、エラー検査訂正（ECC）データを格納する。一例において、NVメモリアレイは、書き込みカウント構成を格納するためのレジスタをさらに有し、1つのNVメモリアレイは、書き込みカウントモードのレジスタ構成を格納し、他のNVメモリアレイは、書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する。一例において、NVメモリアレイは、自動インクリメントハードウェアをさらに有し、書き込みカウントモードは、自動インクリメントハードウェアを選択的に有効化または無効化する。一例において、NVメモリアレイは、NVメモリアレイへのデータの先読み書きを実行し、NVメモリアレイ内のデータを、書き込まれるデータと比較し、書き込みコマンドに起因して異なる値を有するビットのみを書き込む。一例において、1つのNVメモリアレイは、書き込み閾値を格納し、書き込みカウントが書き込み閾値に達したことに応答して、アラートを関連するコントローラへ渡す。

#### 【0106】

概して、本明細書における説明に関し、一例において、システムは、コントローラと、不揮発性メモリデバイスとを備え、不揮発性メモリデバイスは、データブロックをまとめて格納するための複数の不揮発性（NV）メモリアレイであって、各アレイがデータブロックのある部分を格納し、NVメモリアレイのうちの1つがデータブロックの書き込みカウントを格納する、複数のNVメモリアレイと、データブロックをNVメモリアレイに書き込むための書き込みコマンドを受信するためのコマンドバスインターフェースであって、

10

20

30

40

50

書き込みコマンドの受信に応答して、NVメモリアレイは、NVメモリアレイへのデータブロックの内部先読み書きを実行し、1つのNVメモリアレイは、書き込みカウントの先読み書きを実行し、1つのNVメモリアレイの内部の書き込みカウントをインクリメントし、インクリメントした書き込みカウントを1つのNVメモリアレイに書き込む、コマンドバスインターフェースとを有する。

#### 【0107】

一例において、NVメモリアレイは、別個のNVメモリチップを有する。一例において、1つのNVメモリアレイはさらに、エラー検査訂正（ECC）データを格納する。一例において、NVメモリアレイは、書き込みカウント構成を格納するためのレジスタをさらに有し、1つのNVメモリアレイは、書き込みカウントモードのレジスタ構成を格納し、他のNVメモリアレイは、書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する。一例において、NVメモリアレイは、自動インクリメントハードウェアをさらに有し、書き込みカウントモードは、自動インクリメントハードウェアを選択的に有効化または無効化する。一例において、1つのNVメモリアレイは、書き込み閾値を格納し、書き込みカウントが書き込み閾値に達したことに応答して、アラートをコントローラへ渡す。一例において、システムは、不揮発性メモリデバイスに結合されたホストプロセッサデバイス、ホストプロセッサに通信可能に結合されたディスプレイ、ホストプロセッサに通信可能に結合されたネットワークインターフェース、または、システムに電力を供給するバッテリのうちの1または複数をさらに備える。

#### 【0108】

概して、本明細書における説明に関し、一例において、方法は、データブロックを複数の不揮発性（NV）メモリアレイにまとめて格納する段階であって、各アレイがデータブロックのある部分を格納し、NVメモリアレイのうちの1つがデータブロックの書き込みカウントを格納する、格納する段階と、

データブロックをNVメモリアレイに書き込むための書き込みコマンドを受信する段階とを備え、

書き込みコマンドの受信に応答して、NVメモリアレイは、NVメモリアレイへのデータブロックの内部先読み書きを実行し、1つのNVメモリアレイは、書き込みカウントの先読み書きを実行し、1つのNVメモリアレイの内部の書き込みカウントをインクリメントし、インクリメントした書き込みカウントを1つのNVメモリアレイに書き込む。

#### 【0109】

一例において、NVメモリアレイは、別個のNVメモリチップを有する。一例において、1つのNVメモリアレイはさらに、エラー検査訂正（ECC）データを格納する。一例において、NVメモリアレイは、書き込みカウント構成を格納するレジスタをさらに有し、1つのNVメモリアレイは、書き込みカウントモードのレジスタ構成を格納し、他のNVメモリアレイは、書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する。一例において、NVメモリアレイは、自動インクリメントハードウェアをさらに有し、書き込みカウントモードは、自動インクリメントハードウェアを選択的に有効化または無効化する。一例において、1つのNVメモリアレイはさらに、書き込み閾値を格納し、1つのNVメモリアレイは、書き込みカウントが書き込み閾値に達したことに応答して、アラートを関連するコントローラへ渡す。

#### 【0110】

本明細書において示されているフロー図は、一連の様々な処理動作の例を提供する。フロー図は、ソフトウェアまたはファームウェアルーチンにより実行されるオペレーションだけでなく、物理オペレーションを示し得る。フロー図は、ハードウェアおよび／またはソフトウェアに実装され得る有限ステートマシン（FSM）の状態の実装の例を示し得る。動作の順序は、特定のシーケンスまたは順序で示されているが、別段の定めがない限り、修正され得る。故に、示されている図は例としてのみ理解されるべきであり、処理は異なる順序で実行でき、いくつかの動作は並列に実行され得る。加えて、1または複数の動作が省略され得る。故に、全ての実装が全ての動作を実行するわけではない。

10

20

30

40

50

## 【0111】

様々なオペレーションまたは機能が本明細書で説明される範囲において、それらは、ソフトウェアコード、命令、構成および／またはデータとして説明または定義され得る。コンテンツは、直接実行可能なもの（「オブジェクト」形式もしくは「実行可能な」形式）、ソースコードまたは差分コード（「デルタ」コードもしくは「パッチ」コード）であり得る。本明細書において説明されているもののソフトウェアコンテンツは、コンテンツが格納された製造品を介して、または通信インターフェースを動作させて通信インターフェースを介してデータを送信する方法を介して、提供され得る。機械可読記憶媒体は、説明されている機能またはオペレーションを機械に実行させることができ、記録可能／記録不可能な媒体（例えば、リードオンリーメモリ（ROM）、ランダムアクセスメモリ（RAM）、磁気ディスク記憶媒体、光記憶媒体、フラッシュメモリデバイス等）などの機械（例えば、コンピューティングデバイス、電子システム等）によりアクセス可能な形式で情報を格納する任意の機構を含む。通信インターフェースは、例えばメモリバスインターフェース、プロセッサバスインターフェース、インターネット接続、ディスクコントローラ等、別のデバイスと通信するためのハードワイヤード、無線、光等の媒体のいずれかへのインターフェースとなる任意の機構を含む。通信インターフェースは、構成パラメータを提供して、および／または信号を送信して、ソフトウェアコンテンツを記述したデータ信号の提供を通信インターフェースが準備することにより構成され得る。通信インターフェースは、通信インターフェースへ送信される1または複数のコマンドまたは信号を介してアクセスされ得る。

10

## 【0112】

本明細書において説明される様々なコンポーネントは、説明されるオペレーションまたは機能を実行するための手段であり得る。本明細書において説明される各コンポーネントは、ソフトウェアハードウェアまたはこれらの組み合わせを含む。コンポーネントは、ソフトウェアモジュール、ハードウェアモジュール、特定用途向けハードウェア（例えば、特定用途向けハードウェア、特定用途向け集積回路（ASIC）、デジタル信号プロセッサ（DSP）等）、埋め込みコントローラ、ハードワイヤード回路等として実装され得る。

20

## 【0113】

本明細書において説明したこと加え、開示したことおよび本発明の実装に対し、それらの範囲から逸脱することなく、様々な修正が行われ得る。したがって、本明細書における例示および例は、例示的な意味で解釈されるべきであり、限定的な意味で解釈されるべきではない。本発明の範囲は、以下の特許請求の範囲を参照することによってのみ判断されるべきである。

30

## [他の可能な項目]

## [項目1]

データブロックをまとめて格納するための複数の不揮発性（NVRAM）メモリアレイであって、各アレイが上記データブロックのある部分を格納し、上記NVRAMメモリアレイのうちの1つが上記データブロックの書き込みカウントを格納する、複数のNVRAMメモリアレイと、

上記データブロックを上記NVRAMメモリアレイに書き込むための書き込みコマンドを受信するためのコマンドバスインターフェースであって、上記書き込みコマンドの受信に応答して、上記NVRAMメモリアレイは、上記NVRAMメモリアレイへの上記データブロックの内部的なプレライトリードを実行し、1つの上記NVRAMメモリアレイは、上記書き込みカウントのプレライトリードを実行し、上記1つのNVRAMメモリアレイの内部で上記書き込みカウントをインクリメントし、インクリメントした上記書き込みカウントを上記1つのNVRAMメモリアレイに書き込む、コマンドバスインターフェースと

40

を備える不揮発性メモリデバイス。

## [項目2]

上記NVRAMメモリアレイは、別個のNVRAMメモリチップを有する、項目1に記載の不揮発性メモリデバイス。

## [項目3]

上記1つのNVRAMメモリアレイはさらに、エラー検査訂正（ECC）データを格納する、

50

項目 1 に記載の不揮発性メモリデバイス。

[ 項目 4 ]

上記 NV メモリアレイは、書き込みカウント構成を格納するためのレジスタをさらに有し、上記 1 つの NV メモリアレイは、書き込みカウントモードのレジスタ構成を格納し、他の上記 NV メモリアレイは、上記書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する、項目 1 に記載の不揮発性メモリデバイス。

[ 項目 5 ]

上記 NV メモリアレイは、自動インクリメントハードウェアをさらに有し、上記書き込みカウントモードは、上記自動インクリメントハードウェアを選択的に有効化または無効化する、項目 4 に記載の不揮発性メモリデバイス。

10

[ 項目 6 ]

上記 NV メモリアレイは、上記 NV メモリアレイにおける上記データブロックの上記 プレライトリード を実行し、上記 NV メモリアレイ内のデータを、書き込まれるデータと比較し、上記書き込みコマンドに起因して異なる値を有するビットのみを書き込む、項目 1 に記載の不揮発性メモリデバイス。

[ 項目 7 ]

上記 1 つの NV メモリアレイは、書き込み閾値を格納し、上記書き込みカウントが上記書き込み閾値に達したことに応答して、アラートを関連するコントローラへ渡す、項目 1 に記載の不揮発性メモリデバイス。

[ 項目 8 ]

20

コントローラと、

不揮発性メモリデバイスと

を備えるシステムであって、

上記不揮発性メモリデバイスは、

データブロックをまとめて格納する複数の不揮発性 ( NV ) メモリアレイであって、各アレイが上記データブロックのある部分を格納し、上記 NV メモリアレイのうちの 1 つが上記データブロックの書き込みカウントを格納する、複数の NV メモリアレイと、

上記データブロックを上記 NV メモリアレイに書き込むための書き込みコマンドを受信するためのコマンドバスインターフェースであって、上記書き込みコマンドの受信に応答して、上記 NV メモリアレイは、上記 NV メモリアレイへの上記データブロックの内部的な プレライトリード を実行し、1 つの上記 NV メモリアレイは、上記書き込みカウントの プレライトリード を実行し、上記 1 つの NV メモリアレイの内部の上記書き込みカウントをインクリメントし、インクリメントした上記書き込みカウントを上記 1 つの NV メモリアレイに書き込む、コマンドバスインターフェースと

30

を有する、

システム。

[ 項目 9 ]

上記 NV メモリアレイは、別個の NV メモリチップを含む、項目 8 に記載のシステム。

[ 項目 10 ]

上記 1 つの NV メモリアレイはさらに、エラー検査訂正 ( ECC ) データを格納する、項目 8 に記載のシステム。

40

[ 項目 11 ]

上記 NV メモリアレイは、書き込みカウント構成を格納するためのレジスタをさらに有し、上記 1 つの NV メモリアレイは、書き込みカウントモードのレジスタ構成を格納し、他の上記 NV メモリアレイは、上記書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する、項目 8 に記載のシステム。

[ 項目 12 ]

上記 NV メモリアレイは、自動インクリメントハードウェアをさらに有し、上記書き込みカウントモードは、上記自動インクリメントハードウェアを選択的に有効化または無効化する、項目 11 に記載のシステム。

50

## [ 項目 1 3 ]

上記 1 つの N V メモリアレイは、書き込み閾値を格納し、上記書き込みカウントが上記書き込み閾値に達したことに応答して、アラートを上記コントローラへ渡す、項目 8 に記載のシステム。

## [ 項目 1 4 ]

上記不揮発性メモリデバイスに結合されたホストプロセッサデバイス、

ホストプロセッサに通信可能に結合されたディスプレイ、

ホストプロセッサに通信可能に結合されたネットワークインターフェース、または、

上記システムに電力を供給するバッテリ

のうちの 1 または複数をさらに備える、項目 8 に記載のシステム。

10

## [ 項目 1 5 ]

データブロックを複数の不揮発性 ( N V ) メモリアレイにまとめて格納する段階であつて、各アレイが上記データブロックのある部分を格納し、上記 N V メモリアレイのうちの 1 つが上記データブロックの書き込みカウントを格納する、格納する段階と、

上記データブロックを上記 N V メモリアレイに書き込むための書き込みコマンドを受信する段階と

を備え、

上記書き込みコマンドの受信に応答して、上記 N V メモリアレイは、上記 N V メモリアレイへの上記データブロックの内部的な プレライトリード を実行し、1 つの上記 N V メモリアレイは、上記書き込みカウントの プレライトリード を実行し、上記 1 つの N V メモリアレイの内部で上記書き込みカウントをインクリメントし、インクリメントした上記書き込みカウントを上記 1 つの N V メモリアレイに書き込む、

20

方法。

## [ 項目 1 6 ]

上記 N V メモリアレイは、別個の N V メモリチップを含む、項目 1 5 に記載の方法。

## [ 項目 1 7 ]

上記 1 つの N V メモリアレイはさらに、エラー検査訂正 ( E C C ) データを格納する、項目 1 5 に記載の方法。

## [ 項目 1 8 ]

上記 N V メモリアレイは、書き込みカウント構成を格納するレジスタをさらに有し、上記 1 つの N V メモリアレイは、書き込みカウントモードのレジスタ構成を格納し、他の上記 N V メモリアレイは、上記書き込みカウントモードを有効化しないようにするためのレジスタ構成を格納する、項目 1 5 に記載の方法。

30

## [ 項目 1 9 ]

上記 N V メモリアレイは、自動インクリメントハードウェアをさらに有し、上記書き込みカウントモードは、上記自動インクリメントハードウェアを選択的に有効化または無効化する、項目 1 8 に記載の方法。

## [ 項目 2 0 ]

上記 1 つの N V メモリアレイはさらに、書き込み閾値を格納し、上記 1 つの N V メモリアレイは、上記書き込みカウントが書き込み閾値に達したことに応答して、アラートを関連するコントローラへ渡す、項目 1 5 に記載の方法。

40

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4】

50

【図5】

【図6】

10

20

30

40

【図7】

50

---

フロントページの続き

(56)参考文献 特開2005-128817(JP,A)

特開2012-027649(JP,A)

特開2013-246533(JP,A)

特開2016-133874(JP,A)

特開2017-157214(JP,A)

特開2018-120346(JP,A)

特開2019-106174(JP,A)

特表2007-517320(JP,A)

特表2017-504920(JP,A)

国際公開第2019/203995(WO,A1)

(58)調査した分野 (Int.Cl., DB名)

G 06 F 12 / 00